#### PHYSICAL BEHAVIOUR ANALYSIS AND COMPACT TEMPERATURE-DEPENDENT MODELING IN ORGANIC AND IGZO TFTS

#### **Harold Cortes Ordoñez**

ADVERTIMENT. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

### HAROLD CORTÉS ORDOÑEZ

### Physical behaviour analysis and compact temperature - dependent modeling in Organic and IGZO TFTs

### DOCTORAL THESIS

Supervised by:

Dr. Benjamin IÑIGUEZ NICOLAU

Departament d'Enginyeria Electrònica, Elèctrica i Automàtica

Nano-Electronic and Photonic Systems(NePhoS)

UNIVERSITAT ROVIRA i VIRGILI

TARRAGONA JUNE, 2020

I STATE that the present study, entitled "Physical behaviour analysis and compact temperature - dependent modeling in Organic and IGZO TFTs", presented by Harold CORTÉS ORDOÑEZ, for the award of the degree of Doctor in Technologies for Nanosystems, Bioengineering and Energy, has been carried out under my supervision at the Departament d'Enginyeria Electrònica, Elèctrica i Automàtica of this university and it satisfies all requirements to be eligible for the International Doctorate Award.

Dr. Benjamin IÑIGUEZ NICOLAU Doctoral Thesis Supervisor

| Signed: |  |

|---------|--|

|---------|--|

## **Declaration of Authorship**

3

I, Harold CORTÉS ORDOÑEZ, declare that this thesis titled, "Physical behaviour analysis and compact temperature - dependent modeling in Organic and IGZO TFTs" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

| UNIVERSITAT ROVIRA | A I VIRGILI | Γ       |          |          |            |          |    |         |     |      |      |

|--------------------|-------------|---------|----------|----------|------------|----------|----|---------|-----|------|------|

| HYSICAL BEHAVIOUR  | R ANALYSIS  | AND COM | PACT TEM | PERATURE | -DEPENDENT | MODELING | IN | ORGANIC | AND | IGZO | TFTS |

| Marold Cortes Ordo | ñez         |         |          |          |            |          |    |         |     |      |      |

"Everything is theoretically impossible, until it is done"

Robert A. Heinlein

5

"No es cierto que la gente deje de perseguir sus sueños porque envejece, más bien envejece cuando deja de perseguir sus sueños"

Gabriel García Márquez

### **Abstract**

Departament d'Enginyeria Electrònica, Elèctrica i Automàtica

Escola Técnica Superior d'Enginyeria

Doctor in Technologies for Nanosystems, Bioengineering and Energy

Physical behaviour analysis and compact temperature - dependent modeling in Organic and IGZO TFTs

by Harold Cortés Ordonez

In this thesis, we target the drain current modeling for organic thin film transistors (OTFTs) and Indium-Gallium-Zinc-Oxide thin film transistors (IGZO TFTs) from 150K to 370K. Using the current models developed, we analyse the temperature dependences by applying direct parameter extraction methods to experimental I-V characteristics applying temperatures from 150K up to 370K for OTFTs and IGZOs. In addition, we analyse the gate capacitance behaviour ranging the temperature from 200K up to 300K. Most parameters of the gate capacitance model are extracted from I-V characteristics. We successfully validated our models by comparison with experimental I-V characteristics of both OTFTs and IGZO TFTs from 150K up to 370K and C-V characteristics at different frequencies for OTFTs.

# Acknowledgements

9

I would like to thank my supervisor Dr. Benjamin Iñiguez Nicolau, for his enthusiasm for the project, for his total support, patience. Also, I want to thank him for give me the opportunity to enhance my knowledge and my growth as researcher and person. I would like to express my sincere gratitude to Dr. Gerard Ghibaudo and Xavier Mescot for allow me doing the doctoral stay in MINATEC IMEP-LACH laboratories in Grenoble-France and help me to develop the project objectives. Also, I want to thank to the Universitat Rovira i Virgili and Minatec Imep-LACH staff members.

I would like to express my gratitude to the European Commission, the AGAUR of the Generalitat de Catalunya for my predoctoral scholarship. I want to show my gratitude to all of the institutes presents in the DOMINOS project for help me to finish my doctoral project.

I would like to show my gratitude to my wife Lindsay Sidney Paez Daza for her support, encourage, company, love and everything that she can offer me. In difficult situations, she was always, without her everything would be different. Thanks to my family that from the distance took care me. Thanks to my father Orlando Cortes Rodriguez (Mi viejito), my brothers Walter and Orlando, and my step mother, Luz Mary. They and my wife are my life engine.

I want to mention important people that I know along the thesis years as, Karencilla and Joselin (my new brothers), Paulo

10

(my spanish father), Don Jose, Wondwosen. NEPHOS researcher group co-workers. Finally, I would like to show my special gratitude to my cycling coach Tomas Vasquez Amores for learn me how to enhance everyday sports and personally.

## **Contents**

| D  | eclara | tion of Authorship                               | 3  |

|----|--------|--------------------------------------------------|----|

| Αl | bstra  | et                                               | 8  |

| A  | cknov  | wledgements                                      | 9  |

| Co | onten  | ts                                               | 11 |

| Li | st of  | Figures                                          | 13 |

| Li | st of  | Tables                                           | 17 |

| Li | st of  | Abbreviations                                    | 19 |

| Pł | nysica | al Constants                                     | 21 |

| Li | st of  | Symbols                                          | 23 |

| In | trodu  | ıction                                           | 27 |

| 1  | Gat    | e capacitance compact model in Organic Thin Fili | n  |

|    | Tran   | nsistor                                          | 37 |

|    | 1.1    | Capacitance model                                | 39 |

|    | 1.2    | Capacitance compact model validation             | 45 |

|    | 1.3    | First Order Capacitance Derivative               | 49 |

|    |        |                                                  |    |

|    | 1.4          | Review                                           | 51  |

|----|--------------|--------------------------------------------------|-----|

| 2  | Con          | npact modeling of OTFTs at temperatures from     | L   |

|    | <b>150</b> ] | K up to 300K                                     | 53  |

|    | 2.1          | OTFT drain current model and parameter ex-       |     |

|    |              | traction                                         | 58  |

|    | 2.2          | Parameter extraction from I-V characteristics .  | 69  |

|    | 2.3          | Analysis of the temperature dependence in the    |     |

|    |              | gate capacitance                                 | 79  |

|    | 2.4          | Review                                           | 80  |

| 3  | Uni          | fied compact modeling for OTFTs at different tem | 1-  |

|    | pera         | atures                                           | 83  |

|    | 3.1          | Modeling and calculation of physical parameters  | 84  |

|    | 3.2          | Results                                          | 85  |

|    | 3.3          | Review                                           | 89  |

| 4  | Para         | ameter extraction and compact drain current mod  | el  |

|    | for          | IGZO transistor from 210K up to 370K             | 95  |

|    | 4.1          | IGZO modeling and parameter extraction           | 97  |

|    | 4.2          | Model validation and parameter extraction        | 103 |

|    | 4.3          | Review                                           | 108 |

| Co | onclu        | sion                                             | 113 |

| Bi | bliog        | graphy                                           | 119 |

# **List of Figures**

| 1   | First transistor invented by John Bardeen, Wal-     |            |

|-----|-----------------------------------------------------|------------|

|     | ter Brattain and William Shockly at Bell Labs in    |            |

|     | 1947                                                | 28         |

| 2   | Example of a field effect transistor structure      | 29         |

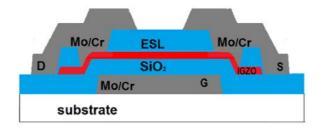

| 3   | Indium-Gallium-Zinc-Oxide thin film transis-        |            |

|     | tor structure                                       | 31         |

| 4   | Organic thin film transistor structure              | 33         |

| 5   | OTFT Roll to roll manufacturing process             | 34         |

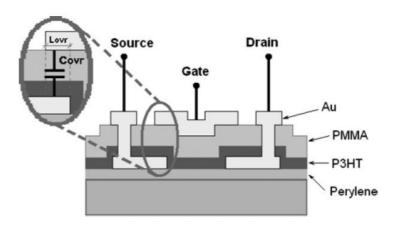

| 1.1 | Capacitance between gate and source terminals       |            |

|     | in PMMA on P3HT thin film transistor structure      | 45         |

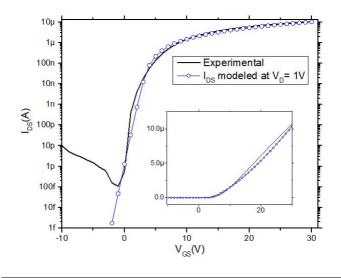

| 1.2 | Modeled and experimental drain to source curren     | $t(I_{DS}$ |

|     | as function of $V_{GS}$                             | 47         |

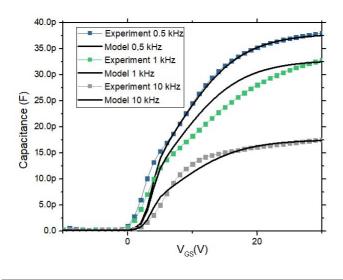

| 1.3 | Modeled and experimental capacitance at 500Hz,      |            |

|     | 1kHz and 10kHz frequencies                          | 48         |

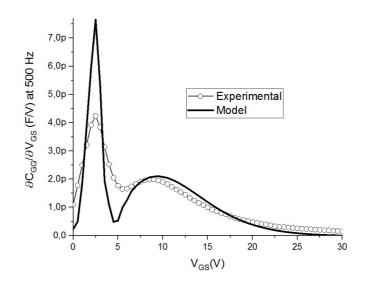

| 1.4 | First derivative of $C_{TOT}$ vs $V_{GS}$ at 500 Hz | 49         |

| 1.5 | First derivative of $C_{TOT}$ vs $V_{GS}$ at 1 kHz  | 50         |

| 1.6 | First derivative of $C_{TOT}$ vs $V_{GS}$ at 10 kHz | 51         |

| 2.1 | Representative structure of electron transport-     |            |

|     | ing of a n-channel thin film transistor             | 54         |

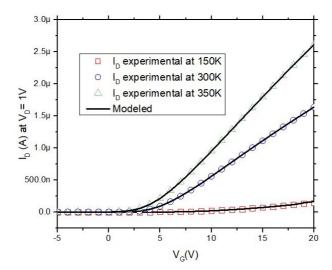

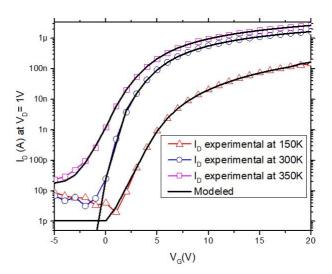

| 2.2  | Modeled and experimental drain to source current( $I_{DS}$ ) |             |  |

|------|--------------------------------------------------------------|-------------|--|

|      | as a function of $V_{GS}$ at $V_{DS} = 1V$ in linear and     |             |  |

|      | logarithmic scales                                           | 70          |  |

| 2.3  | Modeled and experimental drain to source current             | $t(I_{DS})$ |  |

|      | as a function of $V_{GS}$ at $V_{DS}=20V$ in linear and      |             |  |

|      | logarithmic scales                                           | 71          |  |

| 2.4  | Output characteristics in different $V_G$ at 150K .          | 71          |  |

| 2.5  | Output characteristics in different $V_G$ at 260K .          | 72          |  |

| 2.6  | Output characteristics in different $V_G$ at 300K .          | 72          |  |

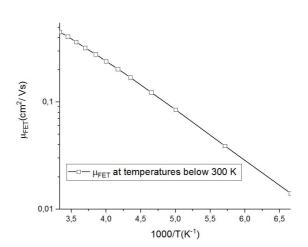

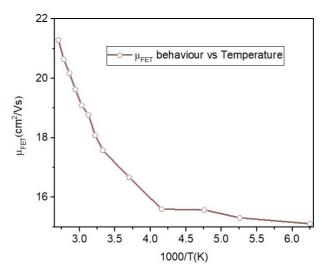

| 2.7  | $\mu_{FET}$ vs Temperature from 150K up to 300K              | 73          |  |

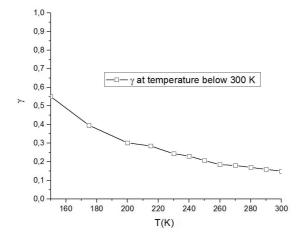

| 2.8  | $\gamma$ vs Temperature from 150K up to 300K                 | 74          |  |

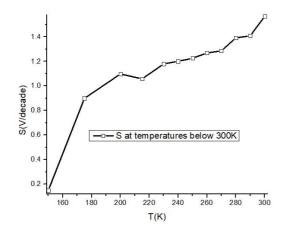

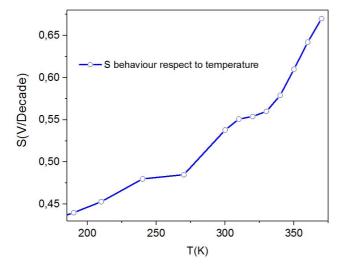

| 2.9  | S vs Temperature from 150K up to 300K                        | 74          |  |

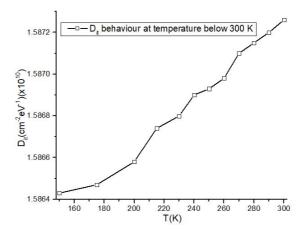

| 2.10 | $D_{it}$ vs Temperature from 150K up to 300K                 | 75          |  |

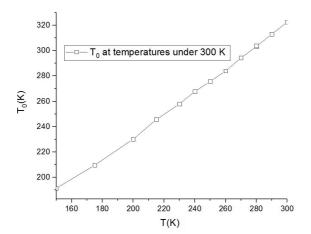

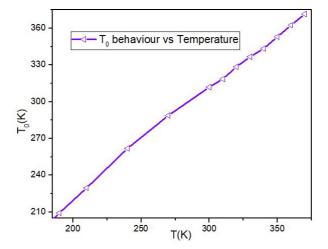

| 2.11 | $T_0$ vs Temperature from 150K up to 300K                    | 76          |  |

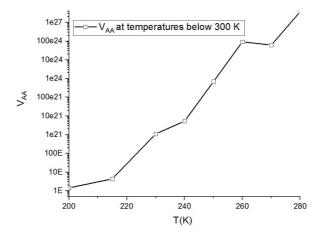

| 2.12 | $V_{aa}$ vs Temperature from 150K up to 300K                 | 77          |  |

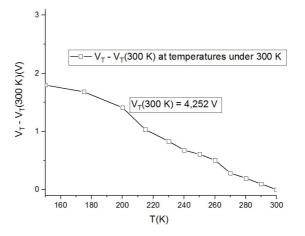

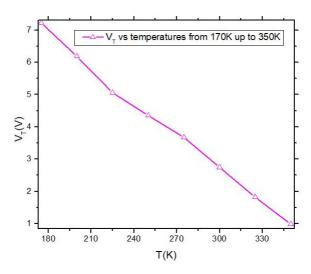

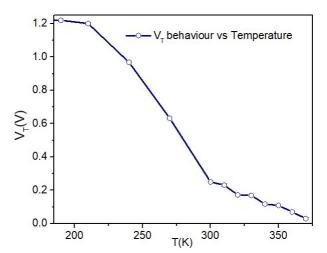

| 2.13 | $V_T$ vs Temperature from 150K up to 300K                    | 77          |  |

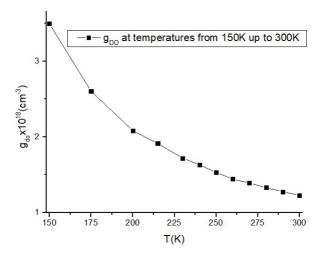

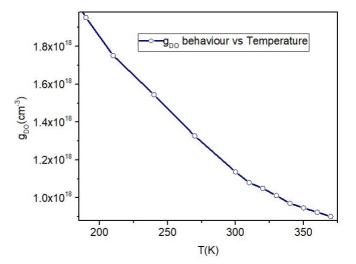

| 2.14 | $G_{do}$ vs Temperature from 150K up to 300K                 | 78          |  |

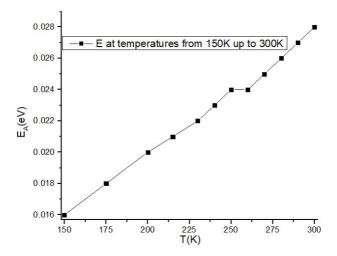

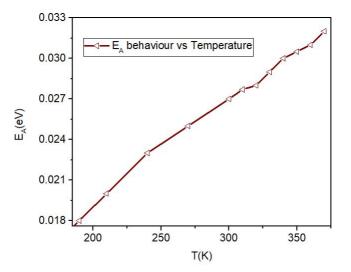

| 2.15 | $E_A$ vs Temperature from 150K up to 300K                    | 78          |  |

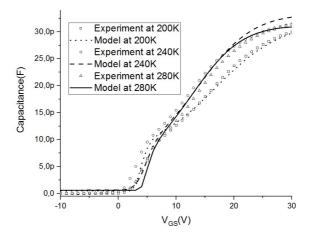

| 2.16 | Capacitance vs Frequency at temperatures from                |             |  |

|      | 200K up to 280K                                              | 79          |  |

| 3.1  | Modeled and experimental drain to source current             | $t(I_{DS})$ |  |

|      | as a function of $V_{GS}$ in linear regime                   | 86          |  |

| 3.2  | Modeled and experimental drain to source current             | $t(I_{DS})$ |  |

|      | as a function of $V_{GS}$ in logarithm scale                 | 87          |  |

| 3.3  | Modeled and experimental drain to source current             | $t(I_{DS})$ |  |

|      | as a function of $V_{GS}$ in logarithm scale                 | 88          |  |

| 3.4  | Modeled and experimental drain to source current             | $t(I_{DS})$ |  |

|      | as a function of $V_{GS}$ in logarithm scale                 | 89          |  |

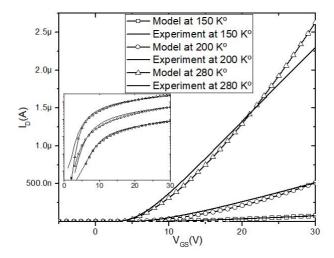

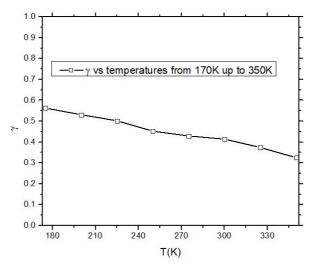

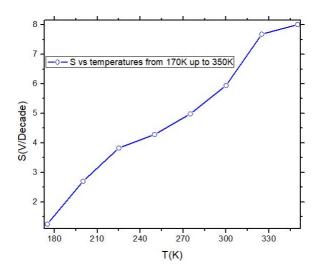

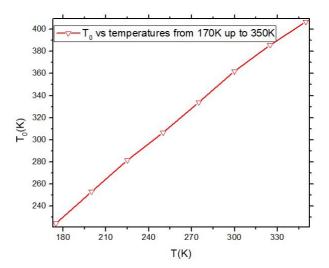

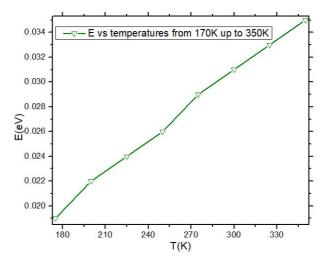

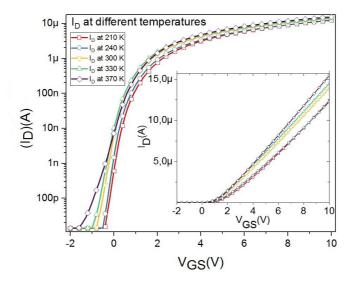

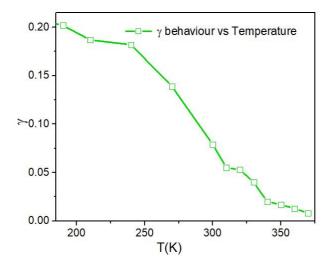

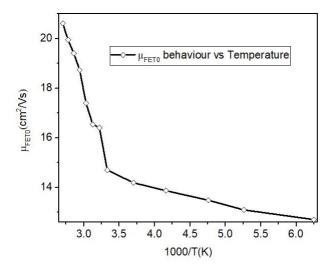

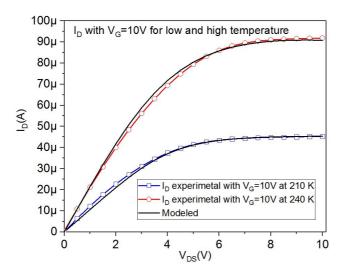

3.5 Modeled and experimental drain to source current( $I_{DS}$ ) as a function of  $V_{GS}$  in logarithm scale . . . . 90 3.6  $\mu_{FET}$  vs Temperature from 150K up to 350K . . 91  $\gamma$  vs Temperature from 150K up to 350K . . . . 3.7 91 3.8 S vs Temperature from 150K up to 350K . . . . 92  $T_0$  vs Temperature from 150K up to 350K . . . 3.9 93 3.10  $E_A$  vs Temperature from 150K up to 350K . . . 93 3.11  $V_T$  vs Temperature from 150K up to 350K . . . 94 4.1 Cross section of the IGZO transistor under study 103 4.2 Experimetal and modeled  $I_D$  at different temperatures in linear and logarithm scale . . . . . 104 4.3 106 4.4  $\mu_{FET}(V_{GS} = 10V)$  vs Temperature . . . . . . 107  $\mu_{FET_0}$ , which has units of  $cm^2/V^{\gamma+1}$  gives the 4.5 numerical value of  $\mu_{FET}$  when  $V_{GS} - V_T = 1V$ 108 4.6 109 4.7 110 4.8 110 4.9 111 4.11 Experimental and modeled  $I_DvsV_{DS}$  for low and

15

## **List of Tables**

| 1.1 | Model parameters extracted from $I - V$ mea-                                                                                |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

|     | surements. They have been used fro drain to                                                                                 |    |

|     | source current, charge channel and gate to ca-                                                                              |    |

|     | pacitance models                                                                                                            | 46 |

| 2.1 | Extracted model parameters from $I-V$ measurements. They have been used for modeling                                        | 70 |

|     | of OTFTs in the range from 150K to 300K                                                                                     | 76 |

| 3.1 | UMEM parameters extracted from $I-V$ measurements. They have been used for modeling of OTFTs in the range from 150K to 350K | 92 |

|     | of OTF is in the range from 150K to 550K                                                                                    | 92 |

| 4.1 | Extracted model parameters from $I - V$ mea-                                                                                |    |

|     |                                                                                                                             |    |

## List of Abbreviations

**TFT** Thin Film Transistor

OTFT Organic Thin Film Transistor

IGZO Indium- Galium- Zinc- Oxide

**DOS** Density Of States

# **Physical Constants**

Boltzmann constant  $kb = 1.38064852x10^{-23} m^2 kg s^{-2} K^{-1}$

Vacuum permittivity  $\epsilon_0 = 8.854x10^{-12} \ CV^{-1}m$

Electric charge  $q = 1.602x10^{-19} C$

# **List of Symbols**

| $I_{DS}$       | Drain to source current            | A              |

|----------------|------------------------------------|----------------|

| W              | TFT width channel                  | m              |

| $C_i$          | Insulator capacitance              | $Fm^{-1}$      |

| $V_{GS}$       | Gate to source voltage             | V              |

| $V_T$          | Threshold voltage                  | V              |

| L              | TFT length channel                 | m              |

| R              | Channel resistance                 | Ω              |

| $V_{DS}$       | Drain to source voltage            | V              |

| $I_0$          | Leakage current                    | A              |

| $V_{DS_{sat}}$ | Saturation drain to source voltage | V              |

| m              | Sharpness of the knee region       |                |

| $V_{FB}$       | Flat band voltage                  | V              |

| $V_{AA}$       | DOS fitting parameter              | V              |

| T              | Transistor operation temperature   | K              |

| $V_{Gte}$      | Effective gate voltage             | V              |

| $V_{Dte}$      | Effective drain voltage            | V              |

| $S_{V_{Gte}}$  | Fitting parameter                  | $C^{-1}$       |

| S              | Subthreshold swing                 | $VDecade^{-1}$ |

| $d_i$          | Insulator thickness                | m              |

| $Q_{CH}$       | Total channel charge               | C              |

| $C_{CH-G}$     | Channel to gate capacitance        | F              |

| $C_{G-G}$      | Gate to gate capacitance           | F              |

|                |                                    |                |

| $W_D$          | Depletion width                      | m                  |

|----------------|--------------------------------------|--------------------|

| $N_B$          | Non intentional doping               | $cm^{-3}$          |

| $C_D$          | Depletion capacitance                | F                  |

| $C_{EQ}$       | Equivalent capacitance               | F                  |

| $C_{G-D}$      | Gate to drain capacitance            | F                  |

| $I_{DSo}$      | Current at $V_{GS} = 0V$             | A                  |

| $R_{CO}$       | Constant resistance                  | Ω                  |

| $E_A$          | Activation energy                    | eV                 |

| 8ato           | Maximum trap density                 | $cm^{-3}$          |

| $D_{it}$       | Interface states density             | $cm^{-2}eV^{-1}$   |

| $E_{FO}$       | Fermi level                          | eV                 |

| E              | Valence band energy                  | eV                 |

| $\mu_{FET}$    | Effective mobility                   | $cm^2V^{-1}s^{-1}$ |

| $\mu_{FET_0}$  | Low per and long mobility            | $cm^2V^{-1}s^{-1}$ |

| λ              | Channel length modulation            | $V^{-1}$           |

| $\mu_0$        | Mobility at $V_{GS} = 1V$            | $cm^2V^{-1}s^{-1}$ |

| $\gamma$       | Deviation from crystalline behaviour |                    |

| α              | Saturation modulation                |                    |

| $\omega$       | Angular frequency                    | Hz                 |

| $\epsilon_i$   | Dielectric constant                  | $Fm_{-1}$          |

| $\epsilon_{s}$ | Semiconductor permittivity           | $CV^{-1}m^{-1}$    |

Dedicated to my mother, Adela Ordoñez Torres (RIP).

25

### Introduction

Before the first transistors appeared (Edgar, 1930)(fig.1) in 1947, electron tubes were used to control the electric current. This component required high voltage, high power consumption, the efficiency was lower and even, it was bulky. This electronic component was called the vacuum tube. Since the Bell Labs in 1946, a group of scientific started to research in a new device that gave solution to fundamental limitations of the vacuum tubes.

27

The transistor is an electron semiconductor device able to conduct and stop current. This component is used to control the flow current thorough a electronic pulses (Edgar, 1930). This semiconductor device can be P and N type. The transistor has a very long life, smaller in size, and it works at low voltages and currents. The first transistor worked using semiconductor junctions instead of heated electrodes in vacuum chamber. The first semiconductor transistor was manufactured with Germanium (Edgar, 1930) (Heil, 1935) (Arns, 1998).

Over the years have new technologies of transistors and their performance is enhanced every time. There are different types of transistors for different engineering applications. Bipolar

FIGURE 1: First transistor invented by John Bardeen, Walter Brattain and William Shockly at Bell Labs in 1947

junction transistors(BJT) (Palmour and Edmond, 1990), heterojunction bipolar transistors(HBT) (Cressler and Niu, 2003), Darlington transistors (Colman and Cotton, 1986), Schottky transistors (Shockley, 1956) are some of the most important types of transistor developed through the years.

One of the most important types of transistors is the field effect transistor (FETs). The majority of the transistors used in integrated circuit are FETs. Some of their advantages are their lower consumption and small size (Bischoff and Krusius, 1985). Also FET transistors are used in RF technologies as amplifier switch (Choi et al., 2009).

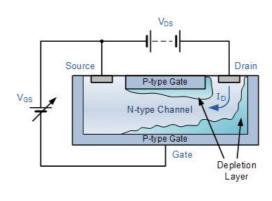

FIGURE 2: Example of a field effect transistor structure

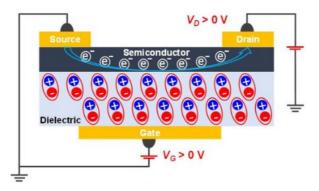

The field effect transistor is composed of three electrode terminals called gate , drain and source. The gate controls the electron or hole carriers located in the semiconductor channel that flow from the source to the drain. This channel can be n-type(electron carriers) or p-type(hole carriers) (Yabuta et al., 2010).

The metal-oxide-semiconductor-field-effect transistor (MOS-FET) is fabricated by the controlled oxidation of the silicon. This silicon oxide layer is p or n type. The metal oxide semiconductor structure works as a parallel plate capacitor where the gate and the substrate are the plates and the silicon oxide is the insulator (Wodarczyk et al., 1992).

One type of transistor are the thin film transistors(TFTs). This transistors are FET devices where the active semiconductor region is a thin film amorphous, nanocrystalline or polycristalline semiconductor, and as in MOSFETs, there is a dielectric between the gate gate and the active semiconductor layer. This

mentioned layers are made by depositing thin film of an amorphous or polycrystalline materials (Tokunaga, 2010).

The amorphous silicon (a-Si:H) TFT nowadays the most used TFT for large area electronic application (Powell, 1989). This a-Si:H TFT is used in displays due to the possibility to depositing over big areas with a high resolution (Nathan et al., 2004). The low cost and their mass manufacturing make a-Si:H transistors a suitable devices for displays and large area electronic applications (Carlson and Wronski, 1976).

Two of the most promising new technologies of TFTs are the Indium-Gallium-Zinc-Oxide thin film transistors (IGZO TFTs) and the organic thin film transistors (OTFTs) (Ito et al., 2008b). Recently, the research community is taking interest in these TFTs technologies and researchers have been considerably improving the performances of these transistors.

The IGZO TFTs and OTFTs are deposited or printed in flexible substrates due to their low deposition temperature(similar to the environment temperature). Thus, these transistor technologies are becoming very interesting in the development of new technologies as flexible and printed electronics (Wong and Salleo, 2009).

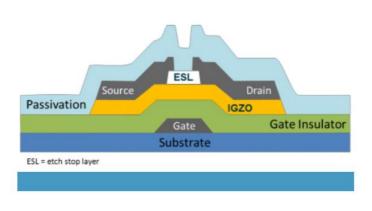

An IGZO TFT has in their semiconductor layer a material based in Indium-Gallium-Zinc-Oxide. This transistor technology was developed by Hideo Hosono in Tokio- Japan in 2003 (Hosono, 2018). This device has an optimal behaviour in display applications. The IGZO devices have a low consumption. The electron mobility of this device is higher than other TFTs technologies. As the electron mobility is high in this

FIGURE 3: Indium-Gallium-Zinc-Oxide thin film transistor structure

kind of transistors, these devices reach higher performances than other TFTs. (Ito et al., 2008a) (Kim et al., 2012) (Ito et al., 2008b). The IGZO TFTs are manufactured by different deposition techniques such as Pulsed Laser Deposition, Solution processing and combustion synthesis. Nowadays, the combustion synthesis technique best known is the Spin coating. In this process, a coating material is applied on the center of the substrate and the coating material is spread due to a centrifugal force applied to the substrate. The substrate rotate at 10000 rpm (Park et al., 2010).

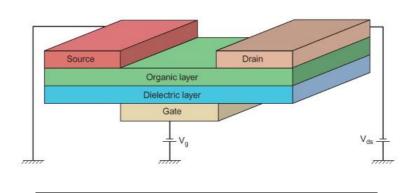

The OTFTs has as semiconductor active layer an organic or small molecule material (Horowitz, 2004). The main advantage of this device is their manufacturing processes. This fabrication methods are low cost and simple (Hirai, 2004) (Klauk, 2006). One important feature of this technology is that its mechanical flexibility makes them compatible with

flexible displays. Other promising applications of this devices are the biosensors (Roberts, Sokolov, and Bao, 2009) (Sheraw et al., 2002) and electronic papers circuitry.

Much effort has been dedicated to the development of electronic devices based on both main types of organic materials: oligomers and polymers. These two kinds of organic materials present important differences related to both their properties and methods of preparation. While oligomers are usually obtained by vacuum deposition techniques, polymers are most frequently deposited by spin coating or inkjet printing. Concerning their properties, conductivity and non-intentionally doping is usually lower for polymers than for oligomers; polymers also present a more disordered structure than oligomers. In polymers, P3HT is the one that has presented highest mobility values, above  $5x10^{-2}\frac{cm^2}{V_S}$  (Lyuleeva et al., 2018). Another feature of organic materials that can vary significantly from one material to another is the energy distributions of localized states (DOS), which, in addition, can be further modified with annealing processes.

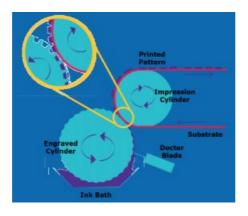

Currently, the OTFTs can be manufactured using printing methods such as inkjet printing process. But, the roll to roll printing process is taking advantage over other printing processes. In this process, a roll with the OTFT structure template spreads the semiconductor ink over another roll that contains the substrate(fig.5). By means of the roll to roll process the OTFTs can be manufactured in mass and their effective manufacturing cost is low.

There are different OTFTs manufacturing processes such as

FIGURE 4: Organic thin film transistor structure

sputtering, chemical and physical vapor deposition, organic evaporation and another solution-based processes. In the sputtering process, energetic ions are accelerated towards a target(substrate or glass). This ions strike the target and atoms are sputtered from the surface. The atoms advance until the substrate and incorporate into the growing film (Lee et al., 2013). The chemical vapor deposition is a process in which precursor gases react to form film deposits on a substrate. The advantage of this manufacturing method is that this process can be carry out at atmospheric pressure and temperature (Chou et al., 2017).

Organic material deposition requires uniform and precise heating with excellent temperature and deposition rate control. This is commonly achieved using a source similar to an effusion furnace (also known as a knudsen cell or k-cell). In this type of source, evaporation of the target material occurs via electrical (Joule) heating of a refractory metal filament

coiled around a metal, ceramic, or quartz crucible. The crucible is heated above the melting or sublimation point of the source material to create adequate vapor pressure for deposition (Taylor, 2015).

FIGURE 5: OTFT Roll to roll manufacturing process

The structure, manufacturing process and performance of the transistor has been evolving over the years, for this reason the used of models that describes relevant physical phenomena, mobility, current, voltage and capacitance in transistors plays a fundamental role in this technological evolution. Without these models, it would be impossible to analyse the behaviour of these devices and then improvements would impossible. Since the first transistor appeared, the physical behaviour models have been evolving as transistor technology evolved.

Nowadays, the models used in circuit simulators are called compact models. This compact models are composed of analytical equations using physical and fitting parameters used to reproduce accurately physical phenomena. An example of parameter extraction and compact model is the Unified Model and Parameter Extraction Method (UMEM) applied to thin film transistor. The UMEM extracts the main electrical parameters (mobility, threshold voltage, temperature characteristic of density if states, etc) from the experimental measurements of the TFT under study. Also, the method works at different transistor geometries, allowing the comparison between two or more device technologies be possible (Estrada et al., 2005).

35

As mentioned before, the compact models have played an important role for the research community in the evolution and new applications of transistors, and the same can be expected for IGZO TFTs and OTFTs.

This doctoral thesis presents the development and improvement of temperature-dependent capacitance and drain current models in OTFTs and IGZO TFTs taking into account different physical phenomena existing in these devices. These models are developed to ease the incorporation of these electron devices in large area and flexible electronics applications.

This document is divided in 4 chapters that show the development of compact models and its validation. In the first part of this work, we present a gate capacitance compact model for OTFTs transistors and the verification of this model by comparison with experimental results from OTFTs manufactured by CEA-Liten (France). In the two next chapters, a compact drain current model for OTFTs transistor valid for both the above and subthreshold regimes is developed. The validation of this model was carried out at different temperatures

from 150K up to 350K. The devices under analysis was manufactured by CEA-Liten. An analysis of the model parameters extracted with different temperatures model is carried out.

Finally, the compact drain current model used for OTFTs is adapted to IGZO devices and validated in IGZO transistors manufactured by TNO Netherlands. We also present an analysis of parameters behaviour at temperatures from 200K to 370K.

#### Chapter 1

## Gate capacitance compact model in Organic Thin Film Transistor

37

In the past years, important research has been made in OTFT modeling (Marinov, Deen, and Iniguez, 2006) (Estrada et al., 2005) (Horowitz and Delannoy, 1991) (Zaki et al., 2014), giving emphasis to develop an accurate I-V model for these devices. However, little attention has been given to model the C-V characteristics of the device (Marinov, Deen, and Iniguez, 2005) (Calvetti, Colalongo, and Kovacs-Vajna, 2005) (Fadlallah et al., 2006) (Li et al., 2010) (Marinov, 2015) (Marinov et al., 2006).

Regarding C - V modeling, there are a few models of capacitance in accumulation regime; some models apply different functions for the accumulation regime and the subthreshold regime (Castro-Carranza et al., 2012). Also, there

are capacitance models which consider the frequency dependence. These models can be used for low, medium and high frequencies (Castro-Carranza et al., 2014). Nevertheless, to the best of our knowledge, there is no capacitance model that works over a wide range of frequencies and valid up to the first capacitance derivative using a analytical expression.

A compact capacitance model has to describe every physical effects present in the capacitance of OTFTs. For example, the compact capacitance model presented by (Horowitz and Delannoy, 1991) reproduces very well the experimental gate to gate capacitance data and it considers each physical behaviour presented in the subthreshold regime, as well, in the accumulation regime, but it is composed of many physical parameter being that the simulation softwares and circuits simulation becomes complicate.

In this chapter, we present a compact capacitance model developed for OTFTs valid from depletion to accumulation regime with continuous and smooth transition as well as for the first order capacitance derivative. This model takes into account the mobility and current at different frequencies. The compact capacitance model uses the UMEM parameter extraction procedure presented in (Estrada et al., 2005); parameters are extracted from I - V data.

The compact capacitance model developed is used to analyze the effect of the parameter related to the density of states (DOS) in the capacitance. In accordance to (Castro-Carranza et al., 2012), OTFTs show a high crystallinity degree when this parameter is close to 0. At the same time, this parameter

The first order capacitance derivative has been considered as a method to extract the threshold voltage ( $V_T$ ) and the flat-band voltage ( $V_{FB}$ ) in crystalline field effect transistors (equivalent to the second derivative method) (Rudenko et al., 2013) (Rudenko et al., 2014) (Rudenko et al., 2005) (Rudenko et al., 2012). Here we study it in OTFTs and from it we discuss the information provided regarding  $V_T$ ,  $V_{FB}$  and the operating regimes in OTFTs.We demonstrate that our model reproduces very well the experimental results of the first order capacitance derivative.

#### 1.1 Capacitance model

The capacitance model developed in this work is based on (Castro-Carranza et al., 2014) with specific improvements in depletion regime. To extract the parameters, we model the I-V characteristics by means of the expression

$$I_{DS} = \frac{-WC_{i}\mu_{FET}(V_{GS} - V_{T})}{L(1 + R\frac{W}{L}C_{i}\mu_{FET}(V_{GS} - V_{T}))}$$

$$\frac{V_{DS}(1 + \lambda V_{DS})}{[1 + [\frac{V_{DS}}{V_{DSsat}}]^{m}]\frac{1}{m}}$$

(1.1)

where W and L are the channel width and length respectively, Ci is the insulator capacitance,  $V_{DS}$  and  $V_{GS}$  correspond

to drain to source voltage and gate to source voltage respectively. R is the resistance between source and drain,  $I_0$  is the leakage current,  $\lambda$  and m control the channel length modulation and the sharpness of the knee region respectively (Estrada et al., 2005). The field effect mobility dependence is modeled as

$$\mu_{FET} = \mu_{FET_0} (V_{GS} - V_T)^{\gamma} \tag{1.2}$$

$$\mu_{FET_0} = \frac{\mu_0}{V_{AA}^{\gamma}} \tag{1.3}$$

being  $\mu_{FET_0}$  related to the value of the mobility for low perpendicular and longitudinal electric field(Cerdeira et al., 2001). $\mu_0$  correspond to the band mobility for the OTFT under study and  $V_{AA}$  is related to the density of states (DOS) (Estrada et al., 2008a) and it is extracted using the UMEM procedure (Estrada et al., 2005).The saturation voltage calculated by 1.5 depends of the saturation modulation parameter ( $\alpha$ ).The  $\gamma$  parameter indicates the deviation from crystalline mobility behaviour. This parameter is related to DOS by means of the characteristic temperature ( $T_0$ ) (Estrada et al., 2008a).This parameter is also extracted through the UMEM procedure.In particular  $\gamma$  parameter is given by eq.1.4.

$$\gamma = 2\frac{T}{T_0} - 2\tag{1.4}$$

On the other hand, the saturation voltage is calculated as

$$V_{DSsat} = \alpha (V_{GS} - V_T) \tag{1.5}$$

As discussed in (Castro-Carranza et al., 2014), to obtain an

expression of the total channel charge( $Q_{CH}$ ), it is necessary to use the non linearized equation of the drain to source current. This current is written as

$$I_{DS} = \frac{-WC_{i}}{L} \frac{\mu_{FET_{0}}}{Vaa^{\gamma}}$$

$$\frac{((V_{GTe} - V_{DSe})^{2+\gamma} - V_{GTe}^{2+\gamma})(1 + \lambda V_{DSe})}{2 + \gamma}$$

(1.6)

where the effective drain to source voltage ( $V_{DSe}$ ) is given by the expression

$$V_{DSe} = \frac{V_{DS}}{[1 + (\frac{V_{DS}}{\alpha V_{GTe}})^m] \frac{1}{m}}$$

(1.7)

41

Actually eq.1.1 is the linearized (in terms of  $V_{DS}$ ) version of eq.1.6. It is important to use an effective gate voltage expression ( $V_{GTe}$ ) because this extends the current model shown in the expression eq.1.6 to subthreshold regime. This equation allows to calculate the drain current in both subthreshold and accumulation regimes making this model more accurate.  $V_{GTe}$  is calculated as

$$V_{GTe} = S_{V_{GTe}} k_b T ln [1 + e^{(\frac{V_{GS} - V_T}{S_{V_{GTe}} k_b T})}]$$

(1.8)

where,  $S_{V_{GTe}}$  is a fitting parameter,  $k_b$  is Boltzmann constant, T is the operation temperature of device.

The insulator capacitance (Ci) is calculated considering gate

insulator thickness ( $d_i$ ), the vacuum permittivity ( $\varepsilon_0$ ) and dielectric constant ( $\varepsilon_i$ ) as

$$Ci = \frac{\varepsilon_0 \varepsilon_i}{d_i} \tag{1.9}$$

The above expression considers the frequency dependence, according to the formula proposed by Cole and Cole (Cole and Cole, 1941) (Castro-Carranza et al., 2014). The dielectric constant as a function of the frequency can be obtained by

$$\varepsilon_{i} = \varepsilon_{i\infty} + \frac{\varepsilon_{i0}\varepsilon_{i\infty}}{1 + (\frac{w}{2\pi n})^{1.78p}}$$

(1.10)

where  $w = 2\pi f$ ,  $\varepsilon_{i\infty}$  and  $\varepsilon_{i0}$  correspond to the permittivity at low and high frequency respectively,  $\eta$  is a fitting parameter has frequency units and p is a fitting parameter with value between 0 and 1 (Castro-Carranza et al., 2014).

The total channel charge expression was derived in (Castro-Carranza et al., 2012)

$$Q_{CH} = \frac{-WC_i^2}{I_{DS}} \mu_{FET} \frac{(V_{GTe} - V_{DSe})^{3+\gamma} - V_{GTe}^{3+\gamma}}{3+\gamma}$$

(1.11)

By differentiating eq.1.6 with respect to  $V_{GS}$ , we obtain the channel to gate and the gate to gate capacitances in accumulation regime as

$$C_{CH-G} = -\frac{\partial Q_{CH}}{\partial V_{CS}} = \frac{\partial Q_G}{\partial V_{CS}} = -C_{GG}$$

(1.12)

The depletion capacitance depends on the depletion width as

$$W_D = -\frac{\varepsilon_S}{Ci} + \sqrt{\frac{\varepsilon_S^2}{Ci^2} + \frac{2\varepsilon_S |V_{GS} - V_T|}{qN_B}}$$

(1.13)

where,  $\varepsilon_S$  represents the permittivity in the semiconductor layer, q is the electron charge and  $N_B$  corresponds to the non intentional doping concentration which is in order of  $10^{14} cm^{-3}$  (Kim et al., 2013). If the film gets the full depletion,  $W_D$  takes the W value.

$$C_D = \frac{\varepsilon_S LW}{W_D} \tag{1.14}$$

43

In the gate capacitance model we consider that the capacitance in the deep subthreshold regime ( $C_D$ ) is due to the film depletion (Castro-Carranza et al., 2014). It is modeled in eq.1.14.

$$C_{EQ} = \begin{cases} \frac{C_D CiWL}{(C_D + Ci)(WL)} & \text{if } V_{GS} < V_T \\ CiWL & \text{if } V_{GS} \ge V_T \end{cases}$$

(1.15)

Then, the final gate capacitance model is the result of a sum of the capacitance in accumulation regime given by the equation eq.1.12 and the depletion capacitance shown in the expression eq.1.15. The complete capacitance model can be calculated by

$$C_{TOT} = \left[ |C_{EQ}| \frac{1 - tanh(\beta)}{2} \right] + \left[ |C_{GG}| \frac{1 + tanh(\beta)}{2} \right] \quad (1.16)$$

where  $\beta = (V_{GT} + \Delta V_T)Q2$ , being  $\Delta V_T$  a correction of the threshold voltage for capacitance in C - V measurements. Q2

correspond to a transition parameter and has units of  $V^{-1}$ . The function Tanh gives a smooth transition between regimes.

Capacitances can be calculated as

$$C_{ij} = -\frac{\partial Q_i}{\partial V_i} \tag{1.17}$$

when i is different to j and

$$C_{ij} = \frac{\partial Q_i}{\partial V_i} \tag{1.18}$$

when i is equal to j

*i* and *j* can be any of the three terminal electrodes(drain-*D*, source-*S* and gate-*G*). In a 3-terminal device such as an OTFT there are 9 independent non reciprocal capacitances.

The gate to drain capacitance ( $C_{GD}$ )for small signal simulation can be calculated from the  $Q_{CH}$  eq.1.11 (Castro-Carranza et al., 2012). $C_{GD}$  is given by

$$C_{GD} = \frac{\partial Q_{CH}}{\partial V_D} \tag{1.19}$$

Finally, the gate to source capacitance (fig.1.1)( $C_{GS}$ ) eq.1.20 can be calculated as the difference between  $C_{TOT}$  and  $C_{GD}$  shown in the expressions eq.1.16 and eq.1.19 respectively (Castro-Carranza et al., 2012).

$$C_{GS} = C_{GG} - C_{GD} (1.20)$$

FIGURE 1.1: Capacitance between gate and source terminals in PMMA on P3HT thin film transistor structure

### 1.2 Capacitance compact model validation

To validate the developed capacitance model, we performed measurements on a polymer p-type polymeric MIS capacitor. Also,to carry out the parameter extraction, we performed I-V measurements (tab.1.1) in OTFTs manufactured in CEA-Liten (Grenoble-France), the layers of which were of the same materials and had same thickness as the targeted MIS capacitors. The semiconductor organic layer is based in the SP400 polymer and the organic dielectric layer is fluorinated. According to eq.1.2 and eq.1.3  $\mu_{FET}$  is not directly extracted, since it depends on  $V_{GS}$ . Using our extracted parameters we obtained  $\mu_{FET}=0.418\frac{cm^2}{VS}$  at  $V_{GS}=30V$ . The bias voltage applied to the capacitance measurement was  $\pm 100mV$ .

TABLE 1.1: Model parameters extracted from I - V measurements. They have been used fro drain to source current, charge channel and gate to capacitance models.

| Parameter             | Value    |

|-----------------------|----------|

| α                     | 0.663    |

| $\gamma$              | 0.386    |

| $\lambda[V^{-1}]$     | -0.029   |

| $\Delta V_T[V]$       | -0.7     |

| т                     | 4.487    |

| $Q_2[V^{-1}]$         | 0.8      |

| $S_{V_{GTe}}[C^{-1}]$ | 5.5      |

| $T[K^{o}]$            | 300      |

| $V_{aa}[V]$           | $5.10^4$ |

| $V_T[V]$              | 3.09     |

| $\eta[Hz]$            | 392      |

| p                     | 0.47     |

The MIS capacitor used in the measurements had as  $L=20\mu m$  and  $W=7860\mu m$ . At low frequencies, we can apply our OTFT capacitance model to organic MIS capacitors with the same layer structure, materials and quicknesses. The charge and capacitance equations of the organic MIS capacitors are calculated from the gate charge and capacitance equations presented in the capacitance model for OTFT, and applying  $V_D=0V$ , which requires to apply the L'Hopital rule to find the analytical expressions which are indicated in (Iñiguez and Moldovan, 2010)(for 3-terminal FETs). We will show in this section that our approach is valid at least up to 10 kHz

The OTFT used to extract the parameters thorough UMEM

procedure from the I-V curves were top gate bottom contact multifingers with 13 fingers, which corresponds to 13 parallel channels with  $W_F=665\mu m$  each. The final channel dimensions are  $W=7980\mu m$  and  $L=20\mu m$ . The source and drain have a width of  $20\mu m$ . The relative permittivity of the dielectric is approximately  $2Fm^{-1}$  and the thickness is 700nm. The semiconductor thickness is 40nm with a relative permittivity close to  $4Fm^{-1}$ . This wafer was manufactured by the roll to roll printing process.

It is important to highlight that we inverted the polarity of the model equations, voltages and the results obtained because the device used are P-type. Therefore, they were treated with the polarity of an N-type device. The manufacturer has not disclosed to the authors the chemical formulas and processing details by the fabrication of the samples.

FIGURE 1.2: Modeled and experimental drain to source current( $I_{DS}$ ) as function of  $V_{GS}$ .

The measurements of the capacitor were taken at three different frequencies: 500Hz, 1kHz and 10kHz in parallel equivalent circuit mode. The equipment used for take this measurements is Agilent 4284A LCR Meter available in IMEP-LAHC Grenoble laboratories. As it can be seen in fig.1.2, the non-linear drain current model calculated data is in excellent agreement with experimental data.

FIGURE 1.3: Modeled and experimental capacitance at 500Hz, 1kHz and 10kHz frequencies.

At 500Hz , the capacitance model reproduces from depletion to accumulation regime the measurement data very well as shown in fig.1.3 .A good agreement between the experimental and modeled values is obtained at 1kHz and 10kHz. This validates the capacitance model presented in this work. Following eq.1.10,  $\epsilon_{i1}=1.989$ ,  $\epsilon_{i2}=1.704$  and  $\epsilon_{i3}=1.182$  are

the values of the permittivity at 500Hz, 1kHz and 10kHz frequencies respectively.

#### 1.3 First Order Capacitance Derivative

We apply the first order derivative to the gate capacitance obtained by our OTFT model and measurements. It was applied at the three targeted frequencies. The fig.1.4 shows the first derivative of  $C_{TOT}$  against  $V_{GS}$  applied to both measurements and model at 500Hz. Our model reproduces reasonably well the experimental results including the position of the observed two peaks taking into account that in every differentiation process usually some accuracy is lost.

FIGURE 1.4: First derivative of  $C_{TOT}$  vs  $V_{GS}$  at 500 Hz

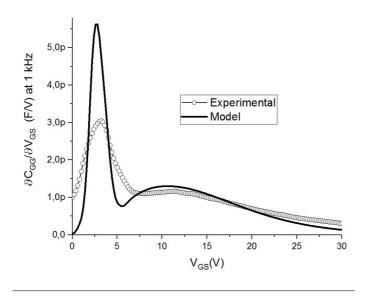

FIGURE 1.5: First derivative of  $C_{TOT}$  vs  $V_{GS}$  at 1 kHz

In fig.1.5, we analyzed the derivative of the gate capacitance at 1kHz. The agreement between model and experimental data is quite good, including the position of the two peaks.

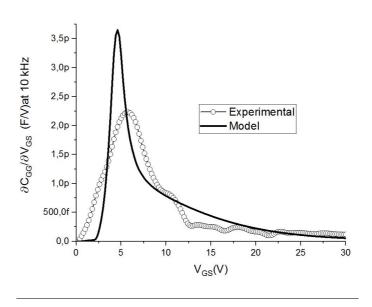

At 10kHz, the agreement between experiment and model is still accurate. At higher frequencies, when non quasi static effects are very significant, we will need to account for them in a more accurate way that just by means of  $\epsilon_i$  (Estrada et al., 2013). Anyway, we still observe in fig.1.6 only traces of the second peak.

The first peak corresponds to  $V_T$  defined as the transition voltage from full to partial depletion. The second peak is related to the transition between the partial depletion and the accumulation regime, which start at flat bland voltage( $V_{FB}$ )

FIGURE 1.6: First derivative of  $C_{TOT}$  vs  $V_{GS}$  at 10 kHz

as it happens in crystalline accumulation mode (or depletion) SOI MOSFETs in accumulation mode (Rudenko et al., 2014). Our model reproduces quite well the transition between these operating models.

#### 1.4 Review

We presented a compact OTFT capacitance model which shows good agreement with experimental C-V data, and their derivatives, for frequencies up to 10kHz, and from the depletion to accumulation regimes. The capacitance model is derived from expressions of total charges compatibles with our previously presented drain current model. Most parameters of

the capacitance expressions were extracted from I-V measurements.

We found that the  $C_{TOT}$  takes the  $C_i$  values in the accumulation regime. We observed that  $C_{TOT}$  decreases as the frequency increases, and we demonstrated that the theory proposed by (Cole and Cole, 1941) is fulfilled. i.e.,  $\varepsilon_i$  is frequency dependent up to 10kHz in our manufacturing OTFT technology under study.

The analysis of the experimentally obtained first order capacitance derivatives shows clear transition behaviours between full and partial depletion, and between partial and accumulation behaviours. The second peak of the plots of the first order derivatives of the gate capacitance versus the gate voltage indicates in which voltage there is not electrical charge in the organic material. In other devices this voltages is called flat band voltage ( $V_{FB}$ ). Our model reproduces quite well the results of the first order derivative of the gate capacitance(including the positions of both peaks) up to 10kHz.

# Compact modeling of OTFTs at temperatures from 150K up to 300K

53

As explained in the Introduction and in Chapter.1, Organic TFTs are very promising devices for flexible and printed electronics. OTFT performances are already comparable to a-Si:H TFTs (fig.2.1). Therefore, OTFTs can be applied not only as sensors in flexible substrates, but also in circuits for sensor driving and interfacing. In order to design OTFTs circuits, physically-based current models for OTFT DC, AC and transient characteristics are needed. This requires a correct understanding of the physical effects affecting OTFT behaviour.

The behavior of I–V characteristics of organic thin film transistors, has been frequently represented using the same expressions as for MOSFETs (Horowitz et al., 1998), to which

FIGURE 2.1: Representative structure of electron transporting of a n-channel thin film transistor

specific effects present in OTFTs as ohmic or non-ohmic resistance at drain and source contacts are added (Necliudov et al., 2003) (Klauk et al., 2003). The presence of leakage current through the dielectric (Shur et al., 2007), or across the channel are other features that have also been considered. The work presented by (Estrada et al., 2005) shows some pentacene OTFTs that can be very accurately modeled using the same expression for mobility as for amorphous silicon TFTs. The transistor model also included series resistance and non-ohmic contacts. Among the advantages of this method are the simple and precise extraction procedures that can be used to determine all model parameters from the electrical characteristics of the devices. At the same time, model parameters are related to physical properties of the device.

In general, mobility in OTFTs increases with gate voltage, although the law of growth may vary from one material to another. Some authors have reported also a dependence of mobility with  $V_{DS}$ , which has been related to a Frenkel–Poole type effect associated to traps in the material (Gupta, Jeon, and Yoo, 2008), as well as to the lowering of the emission barrier in traps located at the boundaries between crystals in polycrystalline materials (Verlaak, Arkhipov, and Heremans, 2003).

55

Material properties of polymers as molecular weight, regioregularity and in general its microstructure (Verilhac et al., 2006) (Sirringhaus et al., 2000), diluents in the case of spin casting deposition techniques (Joung et al., 2005), as well as involuntary or controlled doping (Jiang et al., 2002) (Arkhipov et al., 2003) can significantly modify not only the value of mobility at low fields, but its variation with temperature and voltage. In addition, processing conditions as thermal annealing will affect the properties of the materials and therefore mobility (Joung et al., 2005).

For the above reasons, the electrical behavior of organic devices may vary significantly for different materials and structures, which is something that must be taken into account when models are implemented.

From the theoretical point of view several expressions to model

mobility as function of different parameters have been obtained. For example, in (Arkhipov et al., 2003), the dependence of mobility with regioregularity in P3HT was reproduced, calculating mobility as function of charge carrier concentration, considering hopping as main transport mechanism and a double Gaussian DOS. Adjustment with experimental data was achieved by just fitting DOS parameters until agreement was met. In (Arkhipo et al., 2004), the same approach was used to model the dependence of mobility with doping concentration.

Since, the final goal of these studies is to model the behavior of the transistor, expressions representing the behavior of mobility must be previously obtained to be included in the transistor models.

Nowadays, new research in transistors semiconductor at low temperatures appears with the purpose to study the behaviour of different materials operating at temperatures lower than 300K. For this, it is necessary to develop current models able to analyse physical effects with temperature dependences (Jonscher, 1964).

Very few models have considered the temperature dependence, although temperature analysis is useful to identify relevant physical mechanisms. Most of those temperature studies have been carried out only for I-V characteristics at high temperatures and do not address all parameters. The work by (Estrada et al., 2013) only targets mobility in polymeric transistors.

A recent paper presents results of low temperature I-V characteristics in OTFTs and the temperature dependence of some parameters within a range of low temperatures (Haddad et al., 2018) (Wang, Register, and Dodabalapur, 2019) (Wang and Dodabalapur, 2018). However, the parameter extraction method used is based on crystalline devices, and as a result, parameters which are related to the OTFT Density Of States (DOS) are not studied. Currently, to improves the performance of this devices since the physical point of view, have been developing different manufacturing process to manage the physical parameters explained before in OTFTs (Lodha and Singh, 2001).

57

In the first part of this second chapter, we present a complete analysis of the current in an OTFTs manufacturing technology for temperatures ranging from 150K to 300K. Parameters were extracted using a physically based unified model and extraction method (UMEM), specific for OTFTs, based on assuming an exponential DOS and variable range hopping (Estrada et al., 2008a) (Zaki et al., 2014). The dependence of model parameters with temperature are determined. Lastly, we analyze the C-V behavior at low temperatures from 200K to 280K using the compact capacitance model able to work in both, depletion and accumulation regime (Cortes-Ordonez et al., 2019).

The parameters used in the I-V characteristics are extracted as (Estrada et al., 2005) (Kim et al., 2013). Using the extracted

values of the parameter, our model shows very good agreement with the experimental I-V and C-V curves in both technologies for temperatures ranging from 150K to 300K in two manufacturing technologies and from 200K to 280K respectively.

## 2.1 OTFT drain current model and parameter extraction

In OTFTs, as in inorganic amorphous TFTs, the  $\mu_{FET}$  as function of  $V_{GS}$  is modeled by the following expression

$$\mu_{FET} = \mu_0 \frac{(V_{GS} - V_T)^{\gamma}}{(V_{aa})^{\gamma}} \tag{2.1}$$

rewriting the last expression,

$$\mu_{FET} = \frac{\mu_0}{V_{gg}^{\gamma}} (V_{GS} - V_T)^{\gamma} \tag{2.2}$$

the term  $\frac{\mu_0}{V_{aa}}^{\gamma}$  is extracted from the UMEM procedure.

Eq.2.1 and eq.2.2 can be derived in terms of physical parameters following the works by (Estrada et al., 2008a) and (Vissenberg and Matters, 1998). The model developed by (Vissenberg and Matters, 1998) derived the following expression

of the field effect mobility considering the variable range hopping (VRH) mechanism of carries between localized states.

59

$$\mu_{FET} = \frac{\sigma_0}{q} \left( \frac{\pi (\frac{T_0}{T})^3}{(2\alpha_0)^3 B_C \gamma (1 - \frac{T}{T_0}) \gamma (1 + \frac{T}{T_0})} \right)^{\frac{T_0}{T}} \dots$$

$$\dots \frac{(C_i)^{(2\frac{T_0}{T} - 2)}}{(2k_b T_0 \epsilon_s)^{\frac{T_0}{T} - 1}} (V_{GS})^{2\frac{T_0}{T} - 2}$$

$$(2.3)$$

where  $\sigma_0$  is a fit parameter, q is the electric charge ,  $T_0$  is the characteristic temperature of the localized states,  $\alpha_0$  corresponds to the effective overlap describing hopping,  $B_C$  is around 2.8.  $C_i$ ,  $\epsilon s$  and  $k_b$  are the dielectric capacitance per unit area, the dielectric constant of the dielectric layer and the Boltzmann's constant respectively. The flat band voltage  $(V_{FB})$ , defines the onset of accumulation, and in OTFTs can be identified with the threshold voltage,  $V_T$ .

The expression of the  $\mu_{FET}$  model was obtained from

$$\mu_{FET} = \frac{L}{W} \frac{1}{C_i V_{DS}} \frac{\partial I_{DS}}{\partial V_{GS}}$$

(2.4)

The drain current model was calculated from:

$$I_{DS} = \frac{W}{L} V_{DS} \int_0^t dx \sigma[\delta(x), T]$$

(2.5)

being t the channel thickness.

The work presented by (Vissenberg and Matters, 1998) shows

the calculation of the conductivity ( $\sigma[\delta(x), T]$ ), where  $\delta(x)$  represents the carrier occupation for a given Fermi level. The mobility model shown in eq.2.3 depends on the characteristic temperature  $T_0$  of the exponential DOS described as

$$g_d(E) = g_{d0}exp(-\frac{E}{k_bT_0})$$

(2.6)

being  $\sigma_0$  and  $\alpha_0$  fitting parameters.

The temperature characteristic ( $T_0$ ) is calculated from the  $\gamma$  model as

$$\gamma = 2(\frac{T_0}{T} - 1) \tag{2.7}$$

where T is the operation temperature of the OTFT under study. The  $\gamma$  parameter should indicate the quality of the device technology. Following (Estrada et al., 2005),  $\gamma > 0$  indicates that the behaviour is typical of amorphous and nanocrystalline devices and is related to the trap conduction mechanism.

In order to obtain an analytical expression, the localized charge density in the organic semiconductor layer was considered to be much larger than the free charge density. The resulting expression of the drain current current in the above threshold regime is

$$I_{DS} = \beta(T, T_0) C_i \frac{W}{L} \frac{T}{2T_0} \dots$$

$$\dots [(V_{GS} - V_{FB})] \frac{2T_0}{T} - (V_{GS} - V_{DS} - V_{FB}) \frac{2T_0}{T}],$$

(2.8)

where

$$\beta(T, T_0) = \frac{\sigma_0}{\left[B_c(2\alpha_0)^3\right]} \frac{T_0}{T} \left(\frac{k_b T}{1 - \frac{T}{T_0}}\right) \dots$$

$$\frac{\sin(\frac{\pi T}{T_0})}{2k_b T_0} \frac{T_0}{T} \frac{(C_i)^2 T}{T} \frac{T_0}{(\epsilon_s)^2 T} \frac{T_0}{T}$$

$$(2.9)$$

61

The expression of  $\mu_{FET}$  (eq.2.3) is obtained by applying eq.2.4 to the expression of current in eq.2.8.

Eq.2.8 and eq.2.9 has the same form as the expression of the drain current derived by (Shur and Hack, 1984) for a-Si:H TFTs

$$I_{DS} = P(T, T_0) C_i \frac{W}{L} \frac{T}{2T_0} \dots$$

$$\dots [(V_{GS} - V_{FB}) \frac{2T_0}{T} - (V_{GS} - V_{FB}) - V_{DS}) \frac{2T_0}{T}]$$

(2.10)

where

$$P(T, T_0) = P'(T, T_0) \frac{\frac{2T_0}{T} - 2}{(\epsilon_s)^{\frac{T_0}{T} - 1}}$$

(2.11)

and

$$P'(T, T_{0}) = \frac{qk_{b}TN_{V}exp}{qk_{b}TN_{V}exp} - \frac{E_{Fo} - E_{V}}{k_{b}T} ...$$

$$[\pi qk_{b}g_{d0}exp} - \frac{E_{Fo} - E_{V}}{k_{b}T_{0}} \frac{T_{0}}{T} ...$$

$$sin(\frac{\pi T}{T_{0}}) \frac{T_{0}}{T}$$

$$... [\frac{sin(\frac{\pi T}{T_{0}})}{2k_{b}T_{0}}] \frac{T_{0}}{T}$$

being  $E_{Fo}$  and  $E_V$  the Fermi level and the valence band energy respectively. Therefore, we can make equivalences between parameters in eq.2.8 and eq.2.9 and those in eq.2.10, eq.2.11 and eq.2.12. Equating eq.2.8 and eq.2.10 and replacing  $\beta T$ ,  $T_0$  for  $P(T, T_0)$ , the drain current model when  $V_{DS} << V_{GS} - V_{FB}$  is

$$I_{DS} = \frac{W}{I_c} C_i \mu_{FET} (V_{GS} - V_{FB}) V_{DS}$$

(2.13)

and the  $\mu_{FET}$  is modeled as

$$\mu_{FET} = P'(T, T_0) \frac{(C_i)^{\frac{2T_0}{T} - 2}}{(\epsilon_s)^{\frac{T_0}{T} - 1}} (V_{GS} - V_{FB})^{\frac{2T_0}{T} - 2}$$

(2.14)

The expression of  $\mu_{FET}$  (eq.2.14) has the same form of ( $V_{GS} - V_{FB}$ ) dependence as eq.2.3. By equating both equations we can write the  $\mu_{FET}$  parameters in eq.2.3 in terms of the physical parameters appearing in the expression of eq.2.14.

$$P'(T, T_0) \frac{\frac{2T_0}{T} - 2}{(\epsilon_S)} = \frac{\mu_0}{Vaa^{\gamma}}$$

(2.15)

In OTFTs,  $\mu_0 = 1cm^2/V.s.$

The external voltage applied along drain and source is calculated as

$$V_{DS} = V_{ds} + I_{DS}R (2.16)$$

being  $V_{ds}$  and R the voltage applied to the channel and R the series resistance.

Taking into account the effect of the voltage drop at the series resistance up to first order, the general continuous analytical expression for drain current is modeled as

$$I_{DS} = \frac{-WC_{i}\mu_{FET}(V_{GS} - V_{T})}{L(1 + R\frac{W}{L}C_{i}\mu_{FET}(V_{GS} - V_{T}))}...$$

$$...\frac{V_{DS}(1 + \lambda V_{DS})}{(1 + (\frac{V_{DS}}{V_{DS_{sat}}})^{m})\frac{1}{m}}$$

(2.17)

where L and W are channel length and channel width respectively.  $C_i$  is the insulator capacitance, R is series resistance and it is extracted as in (Cerdeira et al., 2016), m is a fitting parameter related to the sharpness of the knee region.  $I_0$  is the

leakage current. The channel length modulation dependence with the drain source voltage ( $V_{DS}$ ) is given by  $\lambda$  parameter.

To extract the key parameters in the above threshold regime, we calculate the integral function for the current in OTFTs in linear regime (eq.2.19) from the integral function  $H(V_{GS})$  (eq.2.18) shown in (Estrada et al., 2005) and (Kim et al., 2013).

$$H(V_{GS}) = \frac{\int_0^{V_{GS}} I_{DS}(X) dx}{I_{DS}(V_{GS})}$$

(2.18)

$$H_1(V_{GS}) = \frac{1}{2+\gamma}(V_{GS} - V_T)$$

(2.19)

Applying eq.2.19 to the experimental transfer characteristics at low drain-source voltage, and carrying out linear regression of resulting values, we extract  $V_T$  from the intercept and

$\gamma$  from the slope . We obtain the Ss slope from  $(I_{DS})^{1+\gamma}$  vs  $(V_{GS}-V_T)$  and the  $V_{aa}$  parameter is extracted as:

$$V_{aa} = \left[\frac{\binom{W}{L}\mu_0 C_i V_{DS}}{S_S^{1+\gamma}}\right]^{1+\gamma}$$

(2.20)

The parameter  $\alpha$  controls the saturation voltage. The saturation voltage is given by:

$$V_{D_{Sat}} = \alpha (V_{GS} - V_T) \tag{2.21}$$

To calculate the  $\alpha$  parameter it is necessary to calculate the

$S_{sat}$  slope from  $I_{DS_{sat}}^{\frac{1}{1+\gamma}}$  vs  $(V_{GS}-V_T)$ . The parameter  $\alpha$  in saturation regime is extracted by

$$\alpha = \frac{S_{sat}^{2+\gamma} V_{aa}^{\gamma} \sqrt{2}}{\left(\frac{W}{T}\right) \mu_0 C_i} \tag{2.22}$$

65

In the subthreshold regime, the drain current is modeled as (Kim et al., 2013):

$$I_{Dsb} = I_{DS_0} e^{\frac{2.3(V_{GS} - V_T)}{S}}$$

(2.23)

where *S* is the subthreshold swing, and is extracted as:

$$S = \frac{2.3}{Slope(I_{Dsb})} \tag{2.24}$$

$I_{DS_0}$  corresponds to the current when  $V_{GS} = 0V$ .

The non-linear resistance is applied when the output characteristics are deformed at low  $V_{DS}$  by effects of the non-ohmic contact. The non-linear resistance is modeled by

$$R_{C} = R_{CO}e^{-\eta V_{DS}} = \left[\frac{nkT}{q}...\right]$$

$$\frac{log(I_{DS}(V_{GS_{max}}))}{I_{do}} = \frac{-qV_{DS}}{nkT}$$

...(\frac{-qV\_{DS}}{I\_{DS}(V\_{GS\_{max}})} = \frac{-qV\_{DS}}{nkT}

$R_{CO} = 0$  when the non-linear contact is not present. To calculate the parameters n and  $I_{do}$ , it is necessary to plot  $log(I_{DS})vsV_{D1}$ .

$V_{D1}$  is the drain voltage where the non-ohmic phenomenon is present. The slope and the intercept of the curve plotted are calculated and these are rename as  $S_{diode}$  and  $Int_{diode}$  respectively.

The parameter n is calculated following

$$n = \frac{log(e)}{S_{diode} \frac{kT}{q}}$$

(2.26)

and the parameter  $I_{do}$  as

$$I_{do} = 10^{Int_{diode}} (2.27)$$

Having all the parameters extracted, we use a unified expression of the drain current, which tends to eq.2.23 in subthreshold and to eq.3.4 above threshold (Kim et al., 2013). The total drain current is modeled as:

$$I_{DS_T} = |I_{DS}| \left[ \frac{1 + tanh(V_{GS} - (V_T + DV)Q)}{2} \right] \dots$$

$$\dots + |I_{Dsb} + I_0| \left[ \frac{1 - tanh(V_{GS} - (V_T + DV)Q)}{2} \right]$$

(2.28)

Q is a fit parameter and the leakage current( $I_0$ ) is the minimum current value of the experimental data. DV is extracted as:

$$DV = (V_{aa}^{\gamma} I_{DS_0} \frac{L}{WC_i V_D})^{\frac{1}{1+\gamma}}$$

(2.29)

The activation energy is given by:

$$E_A = T_0 kb \tag{2.30}$$

67

where *kb* is the Boltzmann constant.

The maximum trap density ( $g_{d0}$ ) is calculated following (Hernandez-Barrios et al., 2018) and it is apply to calculate an estimate value to  $g_{d0}$  in OTFTs.

$$S_{C} \frac{2}{\sqrt{\pi}} \left( \left( \int_{0}^{\infty} \frac{\sqrt{x}}{\frac{\varphi_{s} - \varphi_{f}}{\varphi_{t}}} dx \right) \right)$$

$$g_{d0} = \frac{1 + e^{\frac{\varphi_{f}}{\varphi_{t}}} ...}{(kbT_{T})\left( \left( \int_{0}^{1} \frac{1}{\frac{T_{T}}{T}} dz.e^{\frac{\varphi_{f}}{kbT_{0}}} \right) \right)} ...$$

$$1 + Z \frac{-(\int 0^{\infty} \frac{\sqrt{x}}{1 + e^{x}} dx.e^{\frac{-\varphi_{f}}{kbT_{0}}} \right)}{-(\int 0^{\frac{\varphi_{f} - \varphi_{s}}{e^{\varphi_{TT}}}} \frac{1}{\frac{T_{T}}{T}} dz.e^{\frac{\varphi_{f}}{kbT_{T}}} \right)}$$

$$1 + Z \frac{T_{T}}{T}$$

$$(2.31)$$

where,  $\varphi_f$  is the fermi level potential,  $\varphi_s$  is the surface potential,  $\varphi_t$  is the thermal potential and  $\varphi_{TT}$  is the characteristic potential.  $N_C$  is the density of the states in the equivalent conduction band in OTFTs.  $T_T = 2T_0 - T$ . The eq.2.31 is used for IGZO devices, and in this case, it is used to calculate an estimated  $g_{d0}$  in OTFTs.

The density of interface states( $D_{it}$ ) is calculated from S and is given by:

$$D_{it} = \frac{\frac{SqC_i}{kbTln(10)} - C_i - C_D}{q}$$

(2.32)

where  $C_D$  is the depletion capacitance of the organic film layer calculated as (Castro-Carranza et al., 2014).

Keeping the parameters obtained through UMEM procedure, the gate capacitance is calculated following the procedure explained in the chapter 1. In this case, the total gate charge model in accumulation regime is given by

$$Q_{CH} = \frac{-WC_i^2}{I_{DS}} \mu_{FET} \frac{(V_{GTe} - V_{DSe})^{3+\gamma} - V_{GTe}^{3+\gamma}}{3+\gamma}$$

(2.33)

where  $V_{GTe}$  is the effective gate voltage overdrive and it is used to model the transition of the non linearised expression of the current between the subthreshold and the accumulation regimes (Chapter 1,(Cortes-Ordonez et al., 2019)).  $V_{DSe}$  is the effective drain voltage,(a continuous function tending to  $V_{DS}$  in the linear regime and to  $V_{DSat}$  in saturation).

The unified expression of the gate capacitance is explained in (Chapter 1, (Cortes-Ordonez et al., 2019)) and it is given by:

$$C_{TOT} = \left[ |C_{EQ}| \frac{1 - tanh(\beta)}{2} \right] + \left[ |C_{GG}| \frac{1 + tanh(\beta)}{2} \right] \quad (2.34)$$

$C_{EQ}$  and  $C_{GG}$  correspond to the depletion and accumulation capacitance, respectively.  $\beta = (V_{GT} + \Delta V_T)Q2$ , being  $\Delta V_T$  a correction of the threshold voltage for capacitance in C - V

measurements. Q2 corresponds to a transition parameter and has units of  $V^{-1}$ . The function Tanh provides a smooth transition between regimes (Cortes-Ordonez et al., 2019).  $C_{GG}$  is calculated from the  $Q_{CH}$  derivative respect to  $V_{GS}$ .

Applying the eq.2.33 is calculated the gate charge as,

$$Q_G = -Q_{CH} \tag{2.35}$$

69

## 2.2 Parameter extraction from I-V characteristics

In the first manufacturing technology, we performed measurements on polymeric p-type based in SP500 polymer OTFTs manufactured in CEA-Liten(Grenoble- France). The OTFTs under study were top gate bottom contact multifingers with  $L\cong 20~\mu\text{m}$  and  $W\cong 2000~\mu\text{m}$ . The total channel length of the transistor consists of 13 parallel fingers with  $W_F\cong 154~\mu\text{m}$ . The dielectric thickness is 700 nm and the relative permittivity is close to 2. The thickness of the organic semiconductor layer(the active layer of the OTFT) is 40 nm and the estimated relative permittivity is 3.

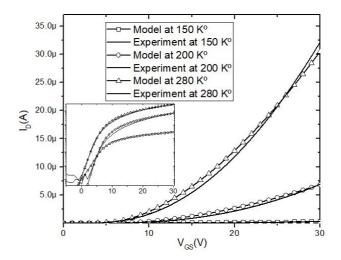

The fig.2.2 shows the experimental and modeled  $I_{DS} - V_{GS}$  characteristics at  $V_{DS} = 1V$  (linear regime), and fig.2.3 at  $V_{DS} = 20V$  (saturation regime) in both linear and logarithm scale .A reasonably good agreement between the experimental data and the  $I_{DS}$  model is observed, at least for  $V_{GS}$  lower than 25V.  $I_{DS}$  increases with temperature due to the field effect mobility increase caused by a carriers increase (Kim et al.,

FIGURE 2.2: Modeled and experimental drain to source current( $I_{DS}$ ) as a function of  $V_{GS}$  at  $V_{DS} = 1V$  in linear and logarithmic scales

2013). A good accuracy between the experimental data and the  $I_{DS}$  model is presented at logarithm scale in the subthreshold regime in both  $V_{DS} = 1V$  and  $V_{DS} = 20V$ .

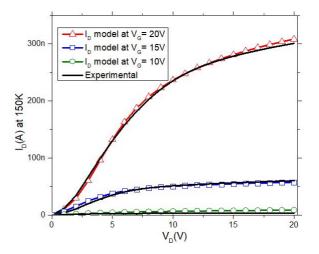

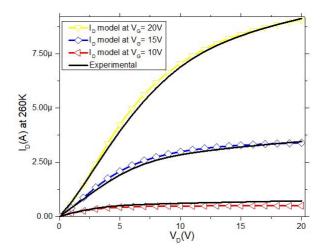

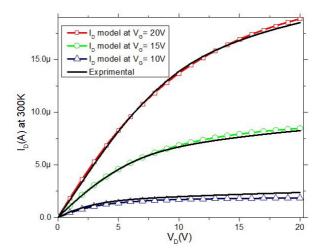

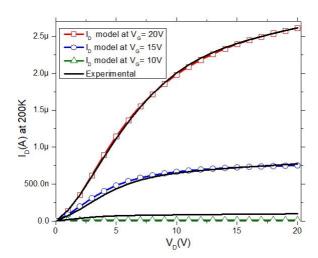

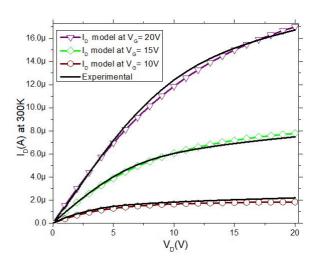

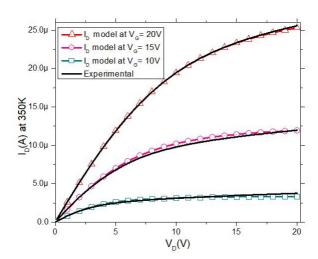

Fig.2.4, fig.2.5 and fig.2.6 show a good agreement between experimental data and the  $I_D$  modelled in the output characteristic at different  $V_G$  changing the temperature from 150K up to 300K . We can observe also that at low temperatures the  $I_D$  model is accurate enough, and it predicts the temperature behaviour very well at different  $V_D$ .

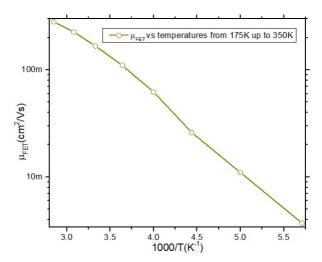

In tab.2.1, we can see the values of the extracted parameters. As seen in fig.2.7, the mobility increases with the temperature within the targeted low temperature range(150K - 300K). As explained above, we associate this phenomenon to the fact

FIGURE 2.3: Modeled and experimental drain to source current( $I_{DS}$ ) as a function of  $V_{GS}$  at  $V_{DS} = 20V$  in linear and logarithmic scales

FIGURE 2.4: Output characteristics in different  $V_G$  at 150K

FIGURE 2.5: Output characteristics in different  $V_G$  at 260K

FIGURE 2.6: Output characteristics in different  $V_G$  at 300K

FIGURE 2.7:  $\mu_{FET}$  vs Temperature from 150K up to 300K

that mobile carrier density increases with increasing temperature. The fig.2.8 shows the dependence of  $\gamma$  for this technology. Usually,  $\gamma$  in OTFTs ranges from 0 to 1, being 0 the value of a crystalline devices (Kim et al., 2013). We observe that  $\gamma$  decreases with increasing temperature, indicating a more crystalline like behavior. If  $\gamma$  is nearly to 0 as in crystalline devices, the generated charge is free.

Overall, the S parameter increases with increasing temperature (fig.2.9). The density of states (DOS) at the interface increases very lightly with increasing the temperature (values shown in fig.2.10 and tab.2.1 as  $D_{it}$ ).S depends monotonically on the interface trap density, and its increase with increasing the temperature is mostly due to the fact that the subthreshold current in mostly due to diffusion, which increases with temperature. The values of  $g_{d0}$  are indicated in tab.2.1.

FIGURE 2.8:  $\gamma$  vs Temperature from 150K up to 300K

FIGURE 2.9: S vs Temperature from 150K up to 300K

FIGURE 2.10:  $D_{it}$  vs Temperature from 150K up to 300K

The temperature dependence of  $T_0$  (DOS characteristic temperature) is shown in the fig.2.11.  $T_0$  usually is constant, in this case we observed that it increases almost linearly with temperature, this effect seems to be the same as for the increase of the characteristic energy of the tail DOS with temperature observed in a-Si:H materials (Cody et al., 1981), which was attributed to the temperature dependence of the dynamic phonon disorder.

Parameter  $V_{aa}$  is related to the mobility and it is extracted using eq.2.20. We can observe in fig.2.12 that the  $V_{aa}$  increases with the temperature. Finally, as seen in fig.2.13, to analyze the behavior of  $V_T$ , we used the expression  $VT(T) - V_T(300K)$ ; it is shown that it decreases with increasing temperatures, which can be related to the change of the trapped charge density.

The maximum trap density (fig.2.14) decreases with increasing temperature.

TABLE 2.1: Extracted model parameters from I-V measurements. They have been used for modeling of OTFTs in the range from 150K to 300K.

|                                         | 150K  | 215K  | 260K             | 280K  | 300K  |

|-----------------------------------------|-------|-------|------------------|-------|-------|

| $\gamma$                                | 0.551 | 0285  | 0.185            | 0.17  | 0.15  |

| S[V/decade]                             | 0.149 | 1.058 | 1.269            | 1.392 | 1.567 |

| $\mu_{FET}[cm^2/Vs]$                    | 0.14  | 0.123 | 0.28             | 0.364 | 0.452 |

| $V_T[V]$                                | 6.05  | 5.28  | 4.76             | 4.45  | 4.25  |

| $T_0[K]$                                | 191   | 246   | 284              | 304   | 322   |

| $g_{do}[cm^{-3}][10^{18}]$              | 3.493 | 1.913 | 1.444            | 1.331 | 1.227 |

| $D_{it}\left[\frac{cm^{-2}}{eV}\right]$ | =     | =     | $1.5968x10^{10}$ | =     | =     |

FIGURE 2.11:  $T_0$  vs Temperature from 150K up to 300K

FIGURE 2.12:  $V_{aa}$  vs Temperature from 150K up to 300K

FIGURE 2.13:  $V_T$  vs Temperature from 150K up to 300K

FIGURE 2.14:  $G_{do}$  vs Temperature from 150K up to 300K

FIGURE 2.15:  $E_A$  vs Temperature from 150K up to 300K

On the other hand, in the fig.2.15 the activation energy increasing with temperature. As  $T_0$  increases almost linearly with temperature. The  $E_A$  is directly proportional to this temperature. The maximum value of  $E_A$  reached at environment temperature (300K) is around 0.30eV.

## 2.3 Analysis of the temperature dependence in the gate capacitance

Analyzing the same device for which we performed the parameter extraction, we studied the temperature dependence of the gate capacitance. The capacitance measurements were done using the Agilent 4284A LCR Meter. To carry out the measurements at different temperature of the capacitance in OTFTs, we used the cryostat station with temperature ranging from 200K up to 280K.

FIGURE 2.16: Capacitance vs Frequency at temperatures from 200K up to 280K

In fig.2.16, we show the total gate capacitance calculated from eq.2.34. We can see in fig.2.16 that the temperature affects the capacitance at low  $V_{GS}$ , i.e the temperature affects the depletion capacitance and the capacitance values at the transition between the depletion and accumulation regimes. In the strong accumulation regime, the gate capacitance is the same as the dielectric capacitance and the temperature does not affects its value. Our capacitance model reproduces well the experimental C-V characteristics.

#### 2.4 Review

We analyzed the temperature dependencies in the I-V and C-V characteristics for polymeric OTFTs in the temperature range from 150K to 300K. We adapted and applied the unified model and parameter extraction method (UMEM) specific for OTFTs, obtaining a reasonable good agreement between the modeled and the experimental I-V characteristics within the targeted temperature range.

For the output characteristics, we obtained a good agreement between the modeled and experimental I-V data. At low  $V_{DS}$  at low temperature, we observed that the non-linear  $R_C$  affects the current. It is to highlight that our model reproduces very well this physical phenomenon at low temperatures as seen in fig.2.4