# Universitat de les Illes Balears

# DOCTORAL THESIS 2017

# METHODOLOGIES FOR HARDWARE IMPLEMENTATION OF RESERVOIR COMPUTING SYSTEMS

Miquel Lleó Alomar Barceló

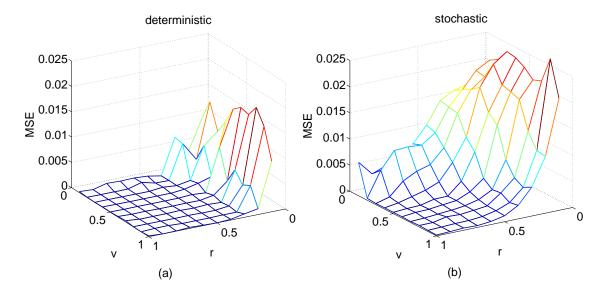

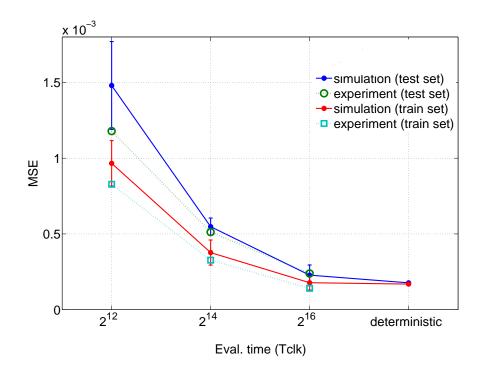

Physics Department Electronics Engineering Group

### Universitat de les Illes Balears

# DOCTORAL THESIS 2017

Doctoral Programme of Physics

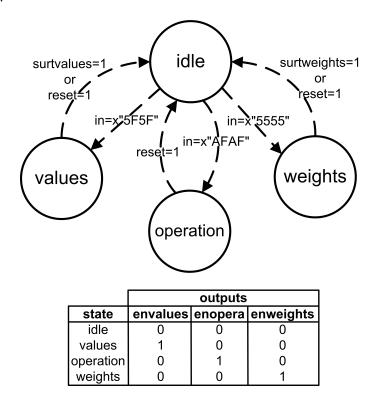

# METHODOLOGIES FOR HARDWARE IMPLEMENTATION OF RESERVOIR COMPUTING SYSTEMS

Miquel Lleó Alomar Barceló

Thesis Supervisor: Josep Lluís Rosselló Sanz

Thesis Co-Supervisor: Vicente José Canals Guinand

Doctor by the Universitat de les Illes Balears

# To Arian and Arsham

# **Contents**

| ΑŁ  | tract                                              | 1                                                            |

|-----|----------------------------------------------------|--------------------------------------------------------------|

| Re  | um                                                 | 3                                                            |

| Re  | umen                                               | į                                                            |

| Lis | of publications                                    | 7                                                            |

| Ac  | nowledgments                                       | 11                                                           |

| I.  | Introduction and objectives                        | 13                                                           |

| 1.  | Motivation and objectives  1.1. Motivation         | . 17                                                         |

| 2.  | ntroduction 2.1. Overview                          | . 21<br>. 25<br>. 30<br>. 33<br>. 36<br>. 37<br>. 40<br>. 50 |

| 11. | Methodologies and results                          | 63                                                           |

| 3.  | Conventional implementation of echo state networks | 65<br>61                                                     |

Contents

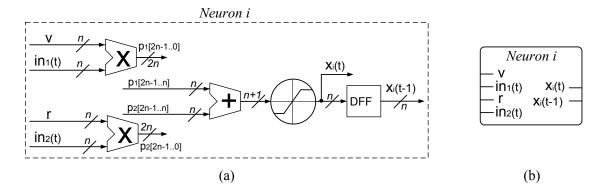

|    | 3.2. | Circuit design of the artificial neuron                  | . 65  |

|----|------|----------------------------------------------------------|-------|

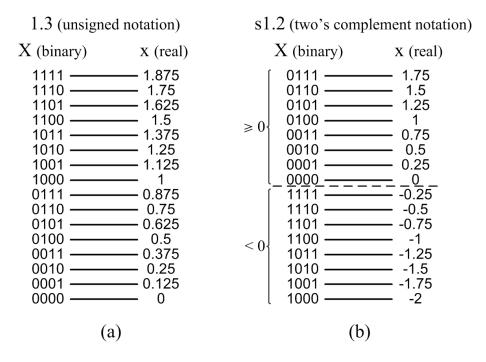

|    |      | 3.2.1. The format of numerical representation            | . 66  |

|    |      | 3.2.2. Arithmetic operations                             |       |

|    |      | 3.2.3. The activation function                           | . 71  |

|    | 3.3. | Implementation of the ESN architecture                   | . 78  |

|    | 3.4. | Experimental results                                     | . 81  |

|    | 3.5. | Discussion                                               | . 83  |

| 4. | Sto  | chastic echo state networks                              | 85    |

|    | 4.1. | Overview                                                 | . 85  |

|    | 4.2. | Stochastic computing                                     | . 85  |

|    |      | 4.2.1. Basic concept                                     | . 85  |

|    |      | 4.2.2. Basic circuitry                                   | . 88  |

|    |      | 4.2.3. Applications                                      | . 96  |

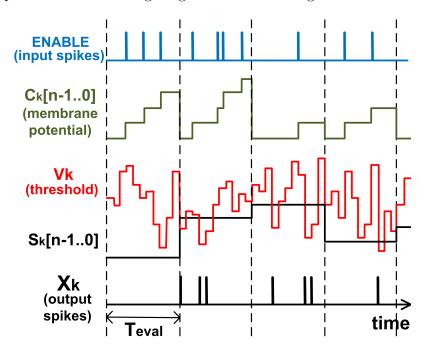

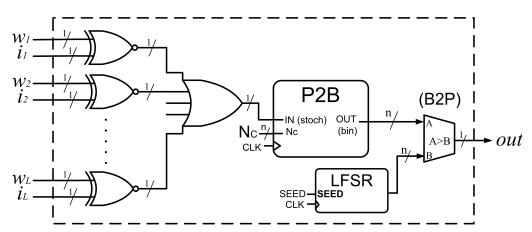

|    | 4.3. | Stochastic implementation of neural networks             | . 98  |

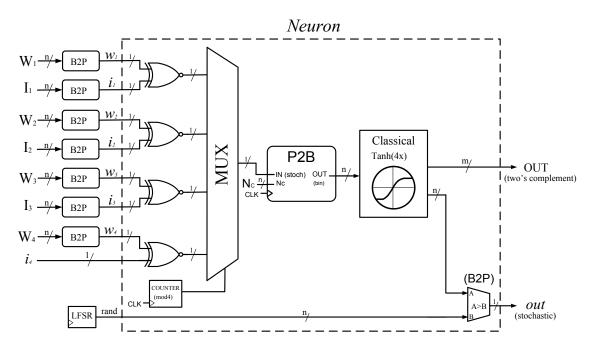

|    |      | 4.3.1. Stochastic design of the neuron                   | . 98  |

|    |      | 4.3.2. Stochastic ESNs                                   | . 101 |

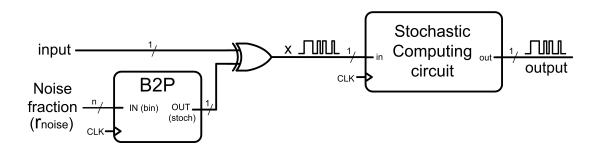

|    | 4.4. | Experimental results                                     | . 104 |

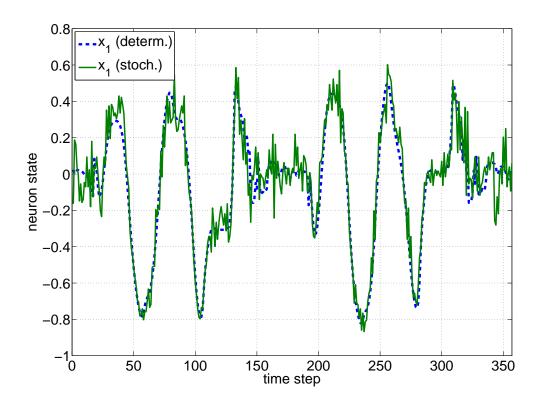

|    |      | 4.4.1. Proof-of-concept example                          | . 104 |

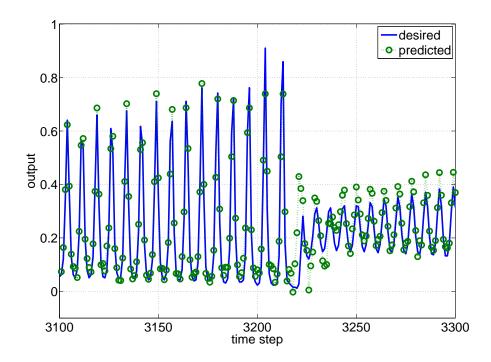

|    |      | 4.4.2. Time-series prediction                            | . 109 |

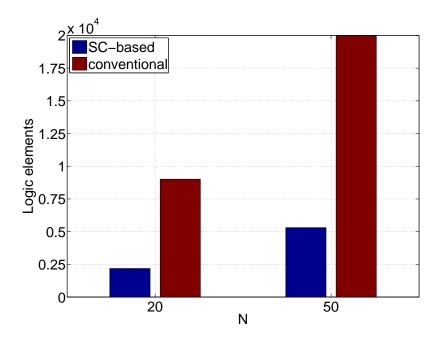

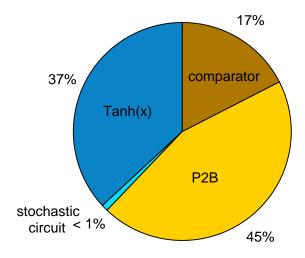

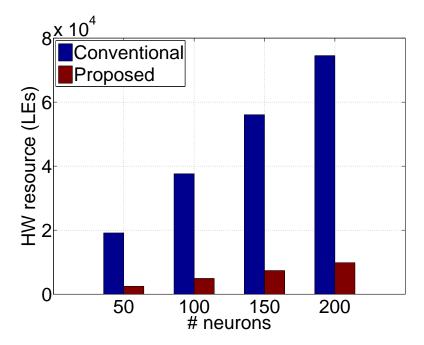

|    |      | 4.4.3. Hardware resource usage                           |       |

|    | 4.5. | Discussion                                               | . 113 |

| 5. | Sto  | chastic echo state networks as liquid state machines     | 115   |

|    | 5.1. | ·                                                        | . 115 |

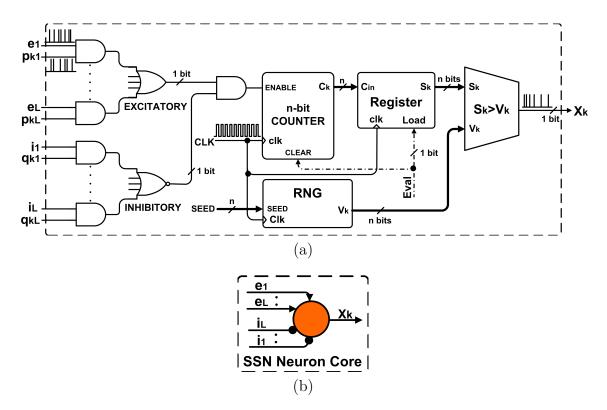

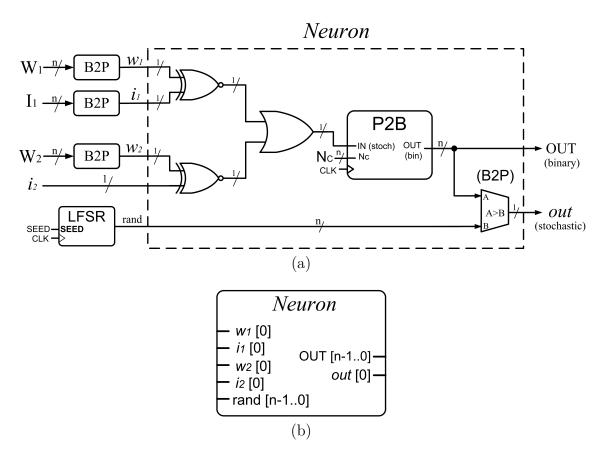

|    | 5.2. | The stochastic spiking neuron model                      | . 116 |

|    |      | 5.2.1. Introduction                                      | . 116 |

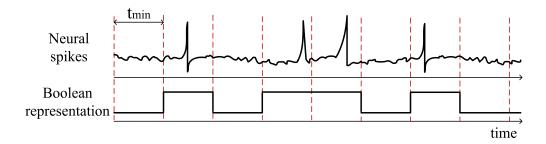

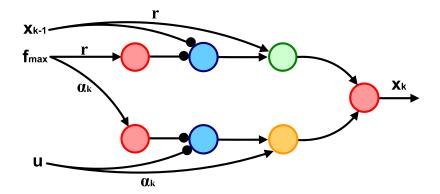

|    |      | 5.2.2. The operation mechanism                           | . 117 |

|    |      | 5.2.3. Neural synchronization                            | . 120 |

|    | 5.3. | The proposed stochastic neuron design                    |       |

|    | 5.4. | Experimental results                                     | . 124 |

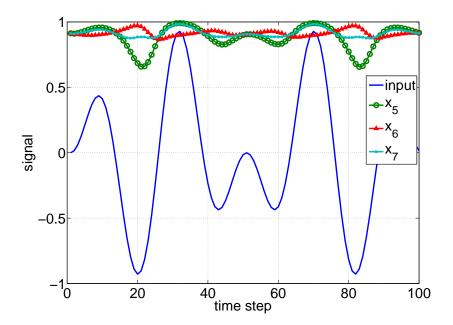

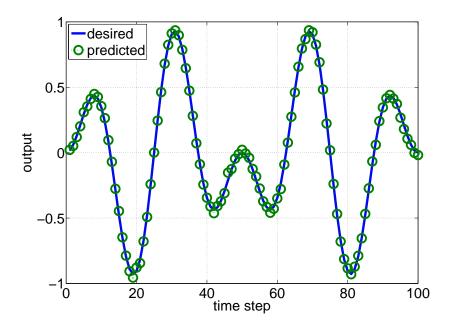

|    |      | 5.4.1. A simple forecasting example                      | . 126 |

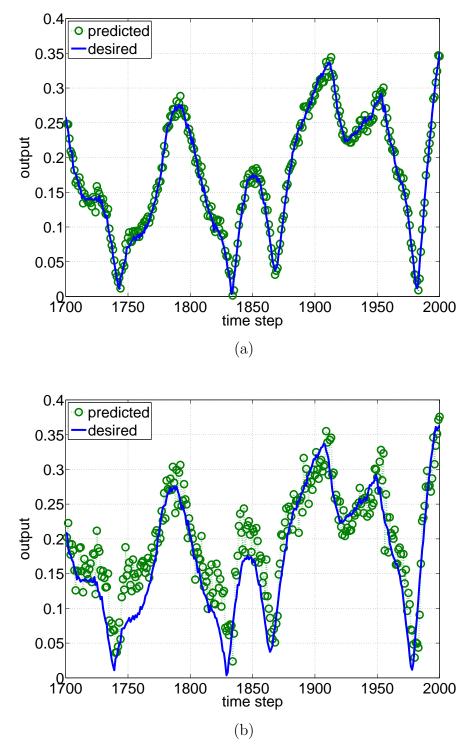

|    |      | 5.4.2. Prediction of real-life sea clutter radar returns | . 126 |

|    |      | 5.4.3. Chaotic time-series prediction task               | . 128 |

|    | 5.5. | Discussion                                               | . 130 |

| 6. | Hard | dware echo state networks without multipliers            | 133   |

|    | 6.1. | Overview                                                 | . 133 |

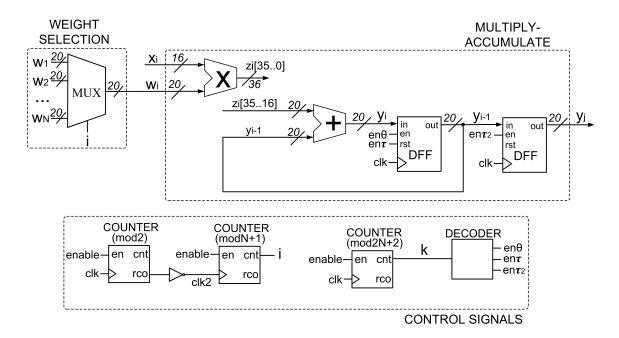

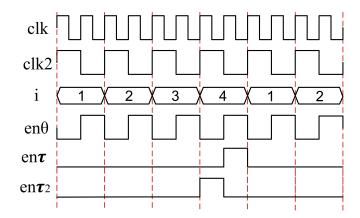

|    | 6.2. | The proposed design without multipliers                  | . 133 |

|    | 6.3. | Experimental results                                     | . 139 |

|    | 6.4. | Discussion                                               | . 141 |

| 7. | Hard | dware implementation of delay-based echo state networks  | 145   |

|    |      | Overview                                                 | 145   |

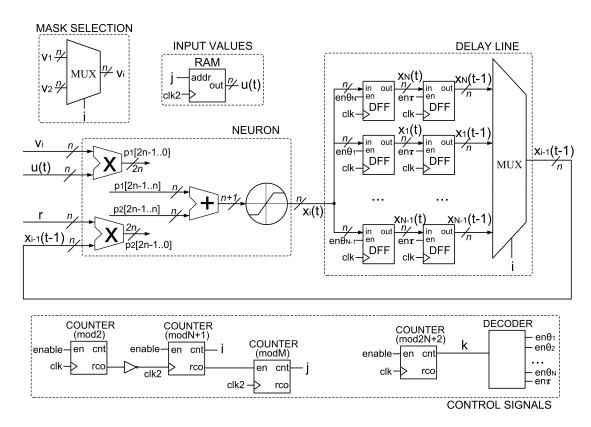

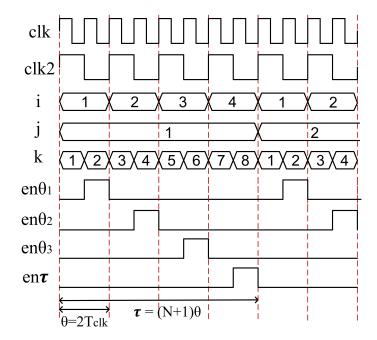

|    | 7.2. | The proposed delay-based design                                                             |                                                     |

|----|------|---------------------------------------------------------------------------------------------|-----------------------------------------------------|

|    |      | 7.2.1. Introduction                                                                         |                                                     |

|    |      | 7.2.2. Hardware implementation                                                              |                                                     |

|    | 7.3. | Experimental results                                                                        |                                                     |

|    | 7.4. | Discussion                                                                                  | . 157                                               |

| 8. |      | single dynamical node reservoir computer                                                    | 159                                                 |

|    |      | Overview                                                                                    |                                                     |

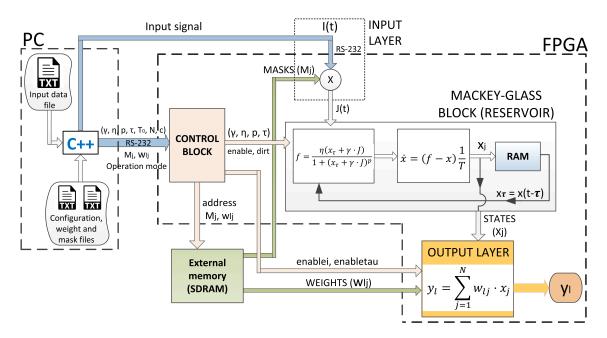

|    | 8.2. | The proposed implementation                                                                 |                                                     |

|    |      | 8.2.1. The control block                                                                    |                                                     |

|    |      | 8.2.2. The external $C++$ program and the configuration files                               |                                                     |

|    |      | 8.2.3. The Mackey-Glass block                                                               | . 167                                               |

|    |      | 8.2.4. The external memory                                                                  |                                                     |

|    |      | 8.2.5. The classification block                                                             | . 171                                               |

|    |      | 8.2.6. System limitations                                                                   | . 172                                               |

|    | 8.3. | Experimental results                                                                        | . 174                                               |

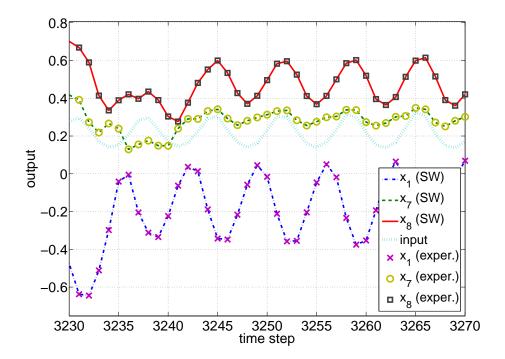

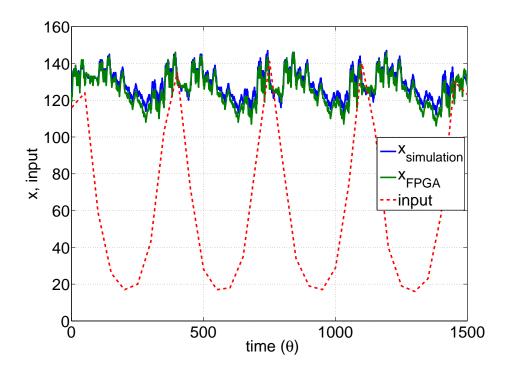

|    |      | 8.3.1. Validation of the differential equation solver                                       | . 174                                               |

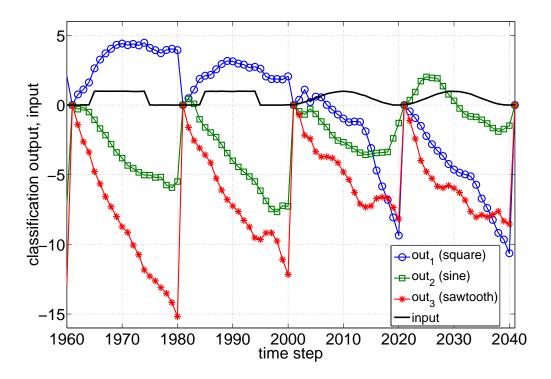

|    |      | 8.3.2. Classification task                                                                  | . 174                                               |

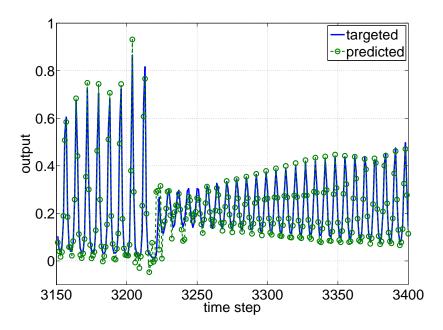

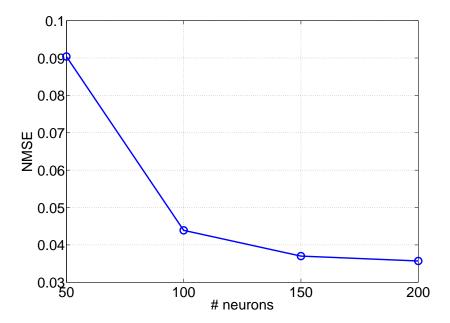

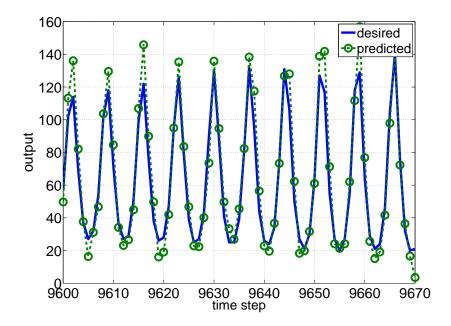

|    |      | 8.3.3. Time-series prediction task                                                          | . 179                                               |

|    |      | 8.3.4. Hardware resources                                                                   | . 181                                               |

|    | 8.4. | Discussion                                                                                  | . 182                                               |

| 9. | Арр  | lications                                                                                   | 185                                                 |

|    |      | Noisy signal classification                                                                 | . 185                                               |

|    |      | 9.1.1. Fault-tolerance analysis                                                             |                                                     |

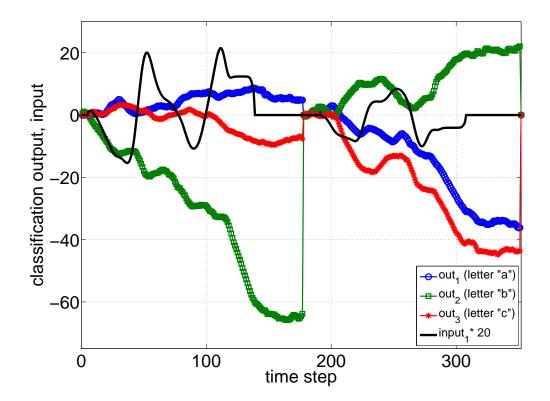

|    | 9.2. | Handwriting recognition                                                                     |                                                     |

|    |      | 9.2.1. Introduction                                                                         |                                                     |

|    |      | 9.2.2. Methodology                                                                          |                                                     |

|    |      | 9.2.3. Results                                                                              |                                                     |

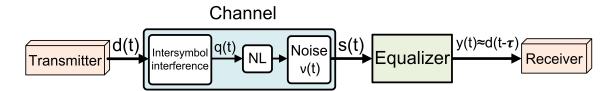

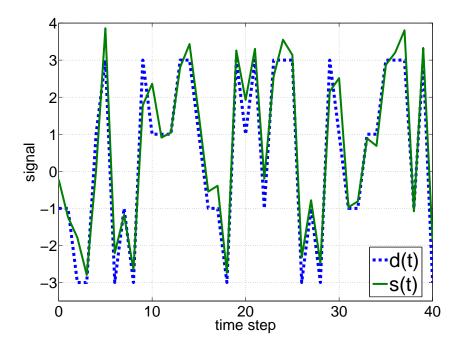

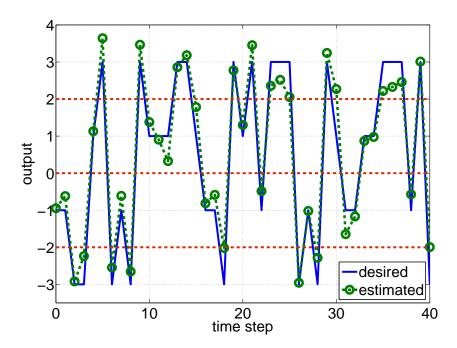

|    | 9.3. | Equalization of a wireless communication channel                                            |                                                     |

|    |      | 9.3.1. Introduction                                                                         |                                                     |

|    |      | 9.3.2. Methodology                                                                          |                                                     |

|    |      | 9.3.3. Results                                                                              |                                                     |

|    | 9.4. | Other applications                                                                          | . 201                                               |

|    |      | 9.4.1. Control                                                                              |                                                     |

|    |      | 9.4.2. Robotics                                                                             |                                                     |

|    |      |                                                                                             |                                                     |

|    |      |                                                                                             | . 204                                               |

|    |      | 9.4.3. Wireless sensor networks                                                             |                                                     |

|    |      | 9.4.3. Wireless sensor networks                                                             | . 205                                               |

|    |      | 9.4.3. Wireless sensor networks                                                             | . 205<br>. 207                                      |

|    |      | 9.4.3. Wireless sensor networks9.4.4. Medical applications9.4.5. Image and video processing | <ul><li>. 205</li><li>. 207</li><li>. 208</li></ul> |

Contents

| III. Conclusions                                                                                                                                                                                                                                                                                 | 213                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

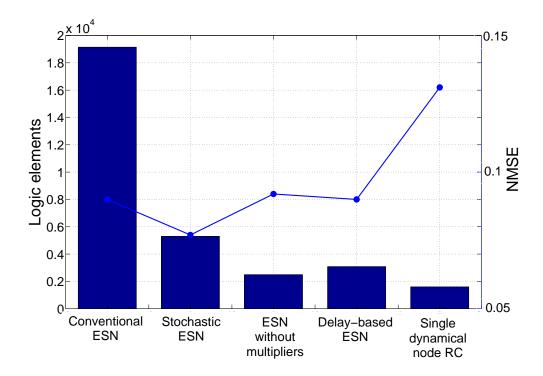

| 10.Conclusions and future work  10.1. Comparative results                                                                                                                                                                                                                                        | . 219                                                                           |

| A. VHDL codes of the digital implementations  A.1. Conventional ESN implementation  A.2. Stochastic ESN implementation  A.2.1. 2-input sigmoid neuron  A.2.2. Neural network  A.3. Proposed SSN implementation  A.4. ESN implementation without multipliers  A.5. Delay-based ESN implementation | <ul><li>. 225</li><li>. 225</li><li>. 227</li><li>. 229</li><li>. 231</li></ul> |

| Bibliography                                                                                                                                                                                                                                                                                     | 239                                                                             |

| Nomenclature                                                                                                                                                                                                                                                                                     | 275                                                                             |

### **Abstract**

Inspired by the way the brain processes information, artificial neural networks (ANNs) were created with the aim of reproducing human capabilities in tasks that are hard to solve using the classical algorithmic programming. The ANN paradigm has been applied to numerous fields of science and engineering thanks to its ability to learn from examples, adaptation, parallelism and fault-tolerance. Reservoir computing (RC), based on the use of a random recurrent neural network (RNN) as processing core, is a powerful model that is highly suited to time-series processing.

Hardware realizations of ANNs are crucial to exploit the parallel properties of these models, which favor higher speed and reliability. On the other hand, hardware neural networks (HNNs) may offer appreciable advantages in terms of power consumption and cost. Low-cost compact devices implementing HNNs are useful to support or replace software in real-time applications, such as control, medical monitoring, robotics and sensor networks. However, the hardware realization of ANNs with large neuron counts, such as in RC, is a challenging task due to the large resource requirement of the involved operations. Despite the potential benefits of hardware digital circuits to perform RC-based neural processing, most implementations are realized in software using sequential processors.

In this thesis, I propose and analyze several methodologies for the digital implementation of RC systems using limited hardware resources. The neural network design is described in detail for both a conventional implementation and the diverse alternative approaches. The advantages and shortcomings of the various techniques regarding the accuracy, computation speed and required silicon area are discussed. Finally, the proposed approaches are applied to solve different real-life engineering problems.

### Resum

Inspirades en la forma en què el cervell processa la informació, les xarxes neuronals artificials (XNA) es crearen amb l'objectiu de reproduir habilitats humanes en tasques que són difícils de resoldre mitjançant la programació algorítmica clàssica. El paradigma de les XNA s'ha aplicat a nombrosos camps de la ciència i enginyeria gràcies a la seva capacitat d'aprendre dels exemples, l'adaptació, el paral·lelisme i la tolerància a fallades. El reservoir computing (RC), basat en l'ús d'una xarxa neuronal recurrent (XNR) aleatòria com a nucli de processament, és un model de gran abast molt adequat per processar sèries temporals.

Les realitzacions en maquinari de les XNA són crucials per aprofitar les propietats paral·leles d'aquests models, les quals afavoreixen una major velocitat i fiabilitat. D'altra banda, les xarxes neuronals en maquinari (XNM) poden oferir avantatges apreciables en termes de consum energètic i cost. Els dispositius compactes de baix cost implementant XNM són útils per donar suport o reemplaçar el programari en aplicacions en temps real, com ara de control, supervisió mèdica, robòtica i xarxes de sensors. No obstant això, la realització en maquinari de XNA amb un nombre elevat de neurones, com al cas de l'RC, és una tasca difícil a causa de la gran quantitat de recursos exigits per les operacions involucrades. Tot i els possibles beneficis dels circuits digitals en maquinari per realitzar un processament neuronal basat en RC, la majoria d'implementacions es realitzen en programari usant processadors convencionals.

En aquesta tesi, proposo i analitzo diverses metodologies per a la implementació digital de sistemes RC fent ús d'un nombre limitat de recursos de maquinari. Els dissenys de la xarxa neuronal es descriuen en detall tant per a una implementació convencional com per als distints mètodes alternatius. Es discuteixen els avantatges i inconvenients de les diferents tècniques pel que fa a l'exactitud, velocitat de càlcul i àrea requerida. Finalment, les implementacions proposades s'apliquen a resoldre diferents problemes pràctics d'enginyeria.

### Resumen

Inspiradas en la forma en que el cerebro procesa la información, las redes neuronales artificiales (RNA) se crearon con el objetivo de reproducir habilidades humanas en tareas que son difíciles de resolver utilizando la programación algorítmica clásica. El paradigma de las RNA se ha aplicado a numerosos campos de la ciencia y la ingeniería gracias a su capacidad de aprender de ejemplos, la adaptación, el paralelismo y la tolerancia a fallas. El reservoir computing (RC), basado en el uso de una red neuronal recurrente (RNR) aleatoria como núcleo de procesamiento, es un modelo de gran alcance muy adecuado para procesar series temporales.

Las realizaciones en hardware de las RNA son cruciales para aprovechar las propiedades paralelas de estos modelos, las cuales favorecen una mayor velocidad y fiabilidad. Por otro lado, las redes neuronales en hardware (RNH) pueden ofrecer ventajas apreciables en términos de consumo energético y coste. Los dispositivos compactos de bajo coste implementando RNH son útiles para apoyar o reemplazar al software en aplicaciones en tiempo real, como el control, monitorización médica, robótica y redes de sensores. Sin embargo, la realización en hardware de RNA con un número elevado de neuronas, como en el caso del RC, es una tarea difícil debido a la gran cantidad de recursos exigidos por las operaciones involucradas. A pesar de los posibles beneficios de los circuitos digitales en hardware para realizar un procesamiento neuronal basado en RC, la mayoría de las implementaciones se realizan en software mediante procesadores convencionales.

En esta tesis, propongo y analizo varias metodologías para la implementación digital de sistemas RC utilizando un número limitado de recursos hardware. Los diseños de la red neuronal se describen en detalle tanto para una implementación convencional como para los distintos métodos alternativos. Se discuten las ventajas e inconvenientes de las diversas técnicas con respecto a la precisión, velocidad de cálculo y área requerida. Finalmente, las implementaciones propuestas se aplican a resolver diferentes problemas prácticos de ingeniería.

## List of publications

### Journal articles

- M. L. Alomar, M. C. Soriano, M. Escalona-Moran, V. Canals, I. Fischer, C. R. Mirasso, and J. L. Rossello. Digital implementation of a single dynamical node reservoir computer. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 62(10): 977–981, Oct 2015.

- M. L. Alomar, V. Canals, N. Perez-Mora, V. Martinez-Moll, and J. L. Rossello. FPGA-based stochastic echo state networks for time-series forecasting. Computational Intelligence and Neuroscience, 2016.

- J. L. Rossello, M. L. Alomar, A. Morro, A. Oliver, and V. Canals. High-density liquid-state machine circuitry for time-series forecasting. *International Journal of Neural Systems*, 26(5), Feb 2016.

- M. L. Alomar, V. Canals, E. Isern, M. Roca, and J. L. Rossello. Efficient parallel implementation of reservoir computing systems. *Neural Computing and Applications*, 2017. Submitted on Jun. 2017 (under review).

These articles represent the basis of chapter 8, chapter 4, chapter 5, and chapter 6, respectively. Throughout my PhD, I have also contributed to the development and writing of some journal publications that have not been directly included in my thesis. These are listed below:

- A. Morro, V. Canals, A. Oliver, M. L. Alomar, and J. L. Rossello. Ultrafast data-mining hardware architecture based on stochastic computing. *PLoS ONE*, 10(5), May 2015.

- V. Canals, A. Morro, A. Oliver, M. L. Alomar, and J. L. Rossello. A new stochastic computing methodology for efficient neural network implementation. *IEEE Transactions on Neural Networks and Learning Systems*, 27(3): 551–564, Mar 2016.

- A. Morro, V. Canals, A. Oliver, M. L. Alomar, F. Galan-Prado, P. J. Ballester, and J. L. Rossello. A stochastic spiking neural network for virtual screening. *IEEE Transactions on Neural Networks and Learning Systems*, pages 1–5, 2017.

- V. Canals, C. F. Frasser, M. L. Alomar, A. Morro, A. Oliver, M. Roca, E. Isern, V. Martinez-Moll, E. Garcia-Moreno, and J. L. Rossello. Noise tolerant

probabilistic logic for statistical pattern recognition applications. *Integrated Computer-Aided Engineering*, 2017. Submitted on Feb. 2016 (accepted with minor changes).

### **Conference papers**

- M. L. Alomar, V. Canals, V. Martinez-Moll, and J. L. Rossello. Low-cost hardware implementation of reservoir computers. In *Power and Timing Modeling*, *Optimization and Simulation (PATMOS)*, 2014 24th International Workshop on, pages 1–5, Sep 2014.

- M. L. Alomar, V. Canals, V. Martinez-Moll, and J. L. Rossello. Advances in Computational Intelligence: 13th International WorkConference on Artificial Neural Networks, IWANN 2015. Proceedings, Part II, chapter Stochastic-Based Implementation of Reservoir Computers, pages 185–196. Springer International Publishing, Cham, Jun 2015.

- M. L. Alomar, V. Canals, A. Morro, A. Oliver, and J. L. Rossello. Stochastic hardware implementation of liquid state machines. In *Neural Networks* (*IJCNN*), 2016 International Joint Conference on, pages 1128–1133, Jul 2016.

- M. L. Alomar, V. Canals, E. Isern, M. Roca, and J. L. Rossello. Fault-tolerant Echo State Networks for temporal signal classification. In *Design of Circuits and Integrated Circuits (DCIS)*, 2017 Conference on, pages 1–5, Nov 2017. Submitted on May 2017 (under review).

These papers cover the topic of the works described in chapter 4, chapter 5 and chapter 9. Other conference publications where I have contributed but which have not been directly included in my thesis are:

- J. L. Rossello, V. Canals, A. Oliver, M. Alomar, and A. Morro. Spiking neural networks signal processing. In *Design of Circuits and Integrated Circuits* (DCIS), 2014 Conference on, pages 1–6, Nov 2014.

- V. Canals, M. L. Alomar, A. Morro, A. Oliver, and J. L. Rossello. Noise-robust hardware implementation of neural networks. In *Neural Networks (IJCNN)*, 2015 International Joint Conference on, pages 1–8, Jul 2015.

- V. Canals, A. Morro, A. Oliver, M. L. Alomar, and J. L. Rossello. An unconventional computing technique for ultra-fast and ultra-low power data mining. In *Power and Timing Modeling, Optimization and Simulation (PATMOS)*, 2015 25th International Workshop on, pages 40–46, Sep 2015.

- M. L. Alomar, V. Canals, J. L. Rossello, and V. Martinez-Moll. Estimation of global solar radiation from air temperature using artificial neural networks based on reservoir computing. In 11th ISES EuroSun Conference, International Conference on Solar Energy for Buildings and Industry, pages 1–6, Oct 2016.

- V. Canals, A. Oliver, M. L. Alomar, N. Perez-Mora, A. Moia, V. Martinez-Moll, M. Roca, E. Isern, E. Garcia-Moreno, and J. L. Rossello. Mid-term photovoltaic plant power generation forecast model using a time delayed artificial neural networks: application for a grid-connected PV plant at Balearic Islands, Spain. In 11th ISES EuroSun Conference, International Conference on Solar Energy for Buildings and Industry, Oct 2016.

- V. Canals, A. Oliver, M. L. Alomar, M. Roca, E. Isern, E. Garcia-Moreno, A. Morro, F. Galan, J. Font-Rossello, and J. L. Rossello. Robust stochastic logic for pattern recognition. In *Design of Circuits and Integrated Circuits (DCIS)*, 2016 Conference on, pages 1–6, Nov 2016.

### **Patents**

V. Canals, A. Morro, J. L. Rosselló, M. L. Alomar, A. Oliver. "Sistemas digitales probabilísticos inmunes al ruido electromagnético". Patent P201331656, May 2015.

# **Acknowledgments**

This work has been supported by a fellowship (FPI/1513/2012) financed by the European Social Fund (ESF) and the "Govern de les Illes Balears (Conselleria d'Educació, Cultura i Universitats)", and by the Spanish Ministry of Economy and Competitiveness (MINECO) under grant contracts TEC2011-23113 and TEC2014-56244-R.

Fons Social Europeu

# Part I. Introduction and objectives

# 1. Motivation and objectives

### 1.1. Motivation

Numerous real-world applications require the execution of tasks that humans can accomplish with apparent ease, but are difficult to perform through standard programmed algorithms. Emblematic examples are speech processing and image recognition. Today's society demands the development of smart methodologies for extracting useful information from the increasingly large amounts of data it generates. The field of "machine learning" investigates systems that are not limited to repeating an explicit set of instructions defined by a programmer, but present the ability of learning by generalization from data. Artificial neural networks (ANNs) are one of such machine learning techniques. They mimic some general features of the brain on the hope to reproduce its capabilities.

ANNs make it possible to automate tasks that are complex to be programmed with sequential computers and represent a useful engineering tool for a variety of technical applications, such as pattern recognition and function approximation. In particular, recurrent neural networks (RNNs), a type of ANN characterized by the presence of closed loops, present the capacity of extracting temporal information from sequential data, which is crucial to perform tasks such as speech recognition or time-series forecasting.

Nevertheless, despite the potential capacities of RNNs for solving complex temporal machine learning tasks, the application of this approach to real-world problems is limited by its complex training procedure, which is relatively time consuming and requires substantial skill to be successfully applied. Reservoir computing (RC) offers a practical alternative to such hard training. With an strategic design of the network, RC reduces the complex training of recurrent networks to a simple linear regression problem facilitating their practical application. The plausibility of RC systems and, in general, of ANNs for modeling biological networks and simulating computation processes in the brain is also an important reason that motivates their development and study. In this thesis, however, I am mainly interested in RC networks as a tool for solving engineering problems. RC has been shown to be a successful approach to perform time-series prediction and classification tasks in many different application fields, such as digital signal processing, robotics, computer vision, medicine and finances. The major advantages of RC over "traditional" RNNs are fast learning speed, ease of implementation and minimal human intervention, which, all in all, allow for a more widespread use of RNNs.

Machine learning techniques such as ANNs and RC systems are usually implemented in software by means of general-purpose sequential processors. However, this is unsatisfactory for certain applications, which require specific hardware to realize such algorithms. More specifically, the development of specialized hardware is crucial to achieve fast, efficient and reliable neural networks. Contrary to software solutions, hardware-based neural networks (HNNs) can exploit the inherent parallelism of ANNs offering a significant speedup in applications that demand a high-volume and real-time processing, such as computer vision tasks and data mining. On the other hand, HNNs allow to reduce the power consumption, which is interesting for applications requiring autonomy and/or mobility, such as robot control, wireless sensor networks and wearable medical devices. In addition, specialized hardware implementing neural networks may offer advantages in terms of cost and reliability (fault-tolerance), which is important for massively produced electronics devices and safety-critical applications, respectively.

RC has received a lot of attention from the research community since its appearance in the last decade. Nevertheless, the development of methods for its hardware implementation still deserves to be extensively explored. Despite the potential benefits of hardware digital circuits to perform RC-based neural processing (e.g., speed gains and power savings), very few implementations of this type have been proposed. It must be noted that the efficient hardware implementation of RC networks using compact devices, such as low-cost field-programmable gate arrays (FPGAs), is not straightforward due to the usually large number of nodes employed in RC networks (typically on the order of 50 to 1000) and the high chip area required by the operations involved with each processing node. Consequently, unconventional techniques must be investigated to obtain smart implementations using reduced hardware resources. The development of efficient dedicated hardware realizations of RC may extend the utility of the approach to a wider range of applications, especially those demanding real-time processing capabilities and/or with constraints on power supply.

The development of specific hardware realizing machine learning algorithms such as ANN models is usually a long process that requires specialized knowledge on digital hardware design. Unlike personal computers or low-cost microcontrollers, hardware devices such as FPGAs cannot be configured using standard sequential programming languages, but require the use of hardware description languages, such as VHDL, which is normally time consuming. It must be considered that each implementation must be tailored to the specific application in order to satisfy the particular requirements and optimally employ the hardware resources. As a result, building such hardware may be expensive. The availability of a tool allowing to easily generate the VHDL code associated with a particular network design for any desired configuration parameters would facilitate the implementation of HNNs. Such a tool for the automatic generation of RC hardware could accelerate the hardware development cycle of these implementations, and even enable their use to non-experts in the field of digital hardware design.

### 1.2. Objectives

These are the general objectives of the present thesis:

- Develop and provide a detailed description of different methodologies for implementing RC systems in digital hardware. The proposed approaches include a binary logic conventional implementation, stochastic computing, a multiplier-less design, and delay-based schemes.

- Implement the proposed designs using programmable hardware devices (FP-GAs) and evaluate their performance for benchmark tasks. Analyze the advantages and shortcomings of each implementation scheme and assess their adequacy for particular applications.

- Develop software programs capable of emulating the different hardware implementations, which is useful to adequately train the systems and also to evaluate them prior to hardware implementation.

- Provide structural hardware description (VHDL) codes of the presented realizations, which may help potential users to develop designs adapted to their particular needs. Further facilitate and accelerate the implementation process of FPGA-based RC systems by developing software programs to automatically generate the VHDL codes of the different proposed designs.

- Demonstrate the usefulness of the developed implementations applying them to solve several real-life engineering problems. Describe additional potential application areas for the proposed hardware-based RC systems.

### 1.3. Structure

The thesis is organized as follows:

Chapter 2 presents an overview of the research field of artificial neural networks, in particular of the reservoir computing technique. The motivation and principles of neural network operation are introduced along with different types of network architectures and applications. Three fundamental versions of reservoir computing (echo state networks, liquid state machines and single dynamical node RC) are described in detail. Special attention is given to the motivations behind the hardware implementation of artificial "intelligent" systems such as those based on the reservoir computing methodology, which is the subject matter of the following chapters.

Chapter 3 presents a "conventional" digital hardware design for a fully-parallel echo state network. Such implementation serves as benchmark for the subsequent alternative designs and also to introduce several issues related to the implementation of neural networks in digital circuitry.

Chapter 4 proposes the use of stochastic computing, a low-cost alternative to conventional binary computing that reduces the circuitry devoted to the arithmetic

operations in echo state networks. The principles and various applications of the stochastic computing approach are presented and applied to build echo state networks. The resulting "stochastic ESN" implementation is benchmarked against the conventional design of previous chapter evaluating the advantages and shortcomings. The design and some results presented in this chapter have been published in the Computational Intelligence and Neuroscience journal ([ACPM+16]). Preliminar results were also presented in the conference papers [ACMMR14] and [ACMMR15].

Chapter 5 also provides an implementation scheme for reservoir networks based on stochastic computing. However, it offers a different view on stochastic ESNs, which are interpreted as an approximation to liquid state machines given the capability of "stochastic neurons" (i.e., sigmoid-like neuron models implemented with the stochastic computing approach) to simplistically emulate the spiking behavior. This chapter is based on the article [RAM<sup>+</sup>16], published in the *International Journal of Neural Systems*, and on the conference paper [ACM<sup>+</sup>16].

Chapter 6 presents a compact digital hardware design for echo state networks based on constraining the resolution of the synaptic weight values, which allows replacing multipliers by simpler operations consuming minimal resource. The proposed implementation is termed "hardware ESN without multipliers". This approach has been presented in the article [ACI+17a], submitted to the *Neural Computing and Applications* journal.

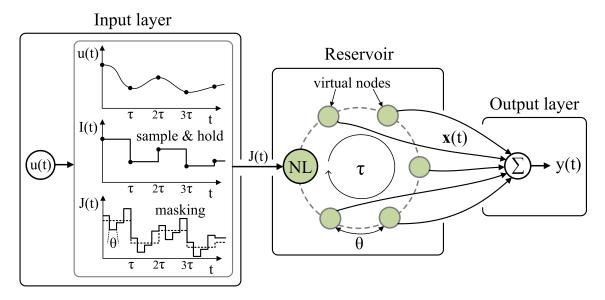

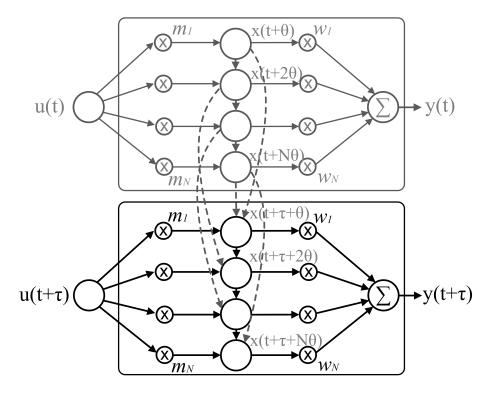

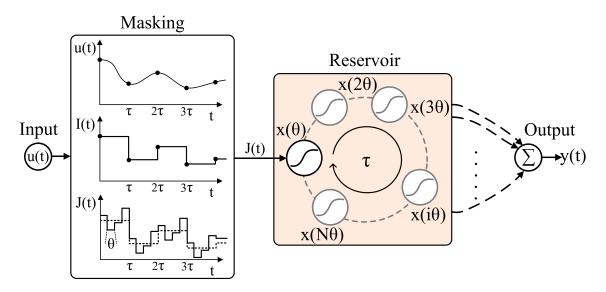

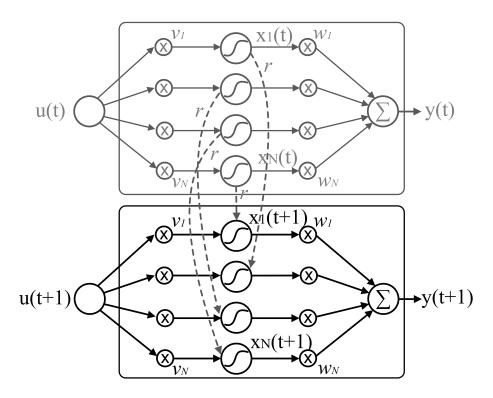

Chapter 7 introduces a design based on the idea of sequentializing the operation of the echo state network so that a single neuron evaluated at different temporal positions emulates the whole network. That is, the hardware requirements are relaxed at the cost of a longer computation time. The approach is referred to as a "delay-based ESN" since the output of the single implemented neuron at a given time is given in terms of its value at a previous time step.

Chapter 8 presents a digital realization of a single dynamical node reservoir computer, which emulates the nodes of a recurrent network by sampling the solutions of a delay differential equation. As in the delay-based ESN, a serial computation scheme is followed so that the output of each "virtual" node of the network is computed as a function of its delayed values. However, in this case, a differential equation is solved to determine the output of each node instead of a simpler discrete-time recursive formula. The information presented in this chapter is partly based on the article [ASEM+15], published in the journal *IEEE Transactions on Circuits and Systems II*.

In chapter 9, the value of the proposed reservoir computing implementations is highlighted applying a selected design to perform different tasks of practical relevance, such as handwriting recognition and the equalization of a communication channel. Furthermore, numerous potential application areas of the systems developed throughout the thesis are described. Some of this chapter's results have been presented in the conference paper [ACI<sup>+</sup>17b].

Finally, chapter 10 compares the proposed designs in terms of area requirements,

accuracy and computation speed. This allows to assess the suitability of the different approaches for certain application fields. The conclusions of the thesis are drawn and some lines for future research are proposed.

### 2. Introduction

### 2.1. Overview

This chapter introduces the research field of artificial neural networks (ANNs) and, in particular, the reservoir computing (RC) technique. Among the recent ANN approaches, RC stands out for its capability to deal with temporal signals while presenting a fast and easy training procedure. Different reasons motivate the study of RC systems and, in general, of ANNs, such as their biological plausibility or their analogy with complex dynamical systems. My main interest in RC networks, however, is their practical utility as a tool for solving engineering problems, such as modeling nonlinear dynamical systems, performing time-series forecasting, temporal pattern recognition or nonlinear regression. More specifically, this thesis is aimed at presenting methodologies for the efficient digital hardware implementation of RC systems, which is crucial for their widespread use in real-time and real-world applications.

Next section presents the general concept of ANNs, the different types of neuron models, network architectures, and their main applications. Then, sec. 2.3 describes the RC approach with its different versions and the applications it is particularly well suited for. Finally, sec. 2.4 describes the motivations behind the realization of ANNs in hardware and presents a brief survey of previous works on this topic.

### 2.2. Artificial neural networks

Artificial neural networks (ANNs) are a computational approach inspired (to a greater or lesser extend) by the way our brain processes information. From the engineering point of view, the reason that motivates the development of ANNs is the necessity to create more "intelligent" systems. Even though there are many tasks that are ideally suited to be solved by conventional sequential computers (e.g., to perform precise and fast arithmetic operations), there are some problems that are unsolvable or difficult to solve in a deterministic way through the use of sequential algorithms.

Let us consider, for example, a problem of visual pattern recognition such as the recognition of handwritten alphanumeric characters or of a particular object in a picture. It is difficult to program a sequential computer system to perform this

Chapter 2 Introduction

type of inherently parallel tasks. A number of sophisticated techniques must be used, perhaps even failing to find an acceptable solution. On the other hand, people and animals are fast and efficient recognizing images. This is more surprising if we take into account that modern electronic devices (with a switching frequency on the order of a few GHz) are more than a million times faster than our neurons (with a response time typically on the order of 1-10 ms). The reason for this is partly answered by the fact that the brain's architecture is significantly different from that of a conventional computer. The massive parallelism and inter-connectivity observed in the biological systems is the key of the many different processing tasks that can be efficiently performed by the brain.

The socially demanded applications that we expect our computers to perform (e.g., speech processing or image recognition) can be easily accomplished by humans, but are too complex to be executed using the classical deterministic algorithms. Given the increasing amount of available information and its importance in today's society, it is necessary to look for alternative methods capable to automatically process such amounts of complex information. The traditional field of computer science deals with the automation of information processing while the areas of computational intelligence and machine learning (ML) are focused on creating methods for solving complex tasks that require some kind of intelligence. That is, systems that can learn from experience instead of repeating an explicit set of instructions so that they are able to give non-trivial responses when they are faced with stimuli they have not seen before.

ANNs are one of the different ML techniques, which present the capability of learning by generalization from training examples (instead of being explicitly programmed). Among other ML algorithms, we can mention support vector machines (SVMs), decision trees, hidden Markov models (HMMs), genetic algorithms, deep learning or cluster analysis ([Mit97], [Kec01]). ANNs borrow features from the brain's behavior to reproduce its flexibility and power by artificial means. A number of different names are used in the literature to refer to the ANN approach ([RM86], [FS91], [Zur92], [Bis95], [MMR97], [Hay01], [Dre05], [Gal07], [MOM12]), such as artificial neural systems (ANSs), neurocomputing, network computation, connectionism, parallel distributed processing, layered adaptive systems, or neuromorphic systems.

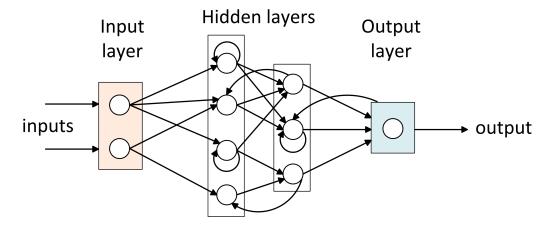

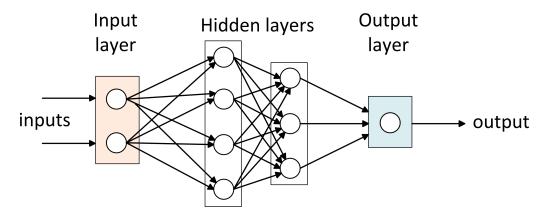

A neural-network structure is a collection of parallel processors connected together in the form of a directed graph. Fig. 2.1 schematically represents a typical network diagram, where the basic processing elements are called *artificial neurons*, or simply neurons. Often we also refer to them as nodes. In some cases, they can be considered as threshold units that fire when their input stimulus exceeds a certain value. The connections are indicated by arcs and the information flow is indicated through the use of arrowheads. Neurons are often organized in layers, and feedback connections both within the layer and toward adjacent layers are, in principle, allowed. Each connection strength is expressed by a numerical value called a weight, which is modified during the training process.

Figure 2.1.: Schematic representation of an artificial neural network (ANN).

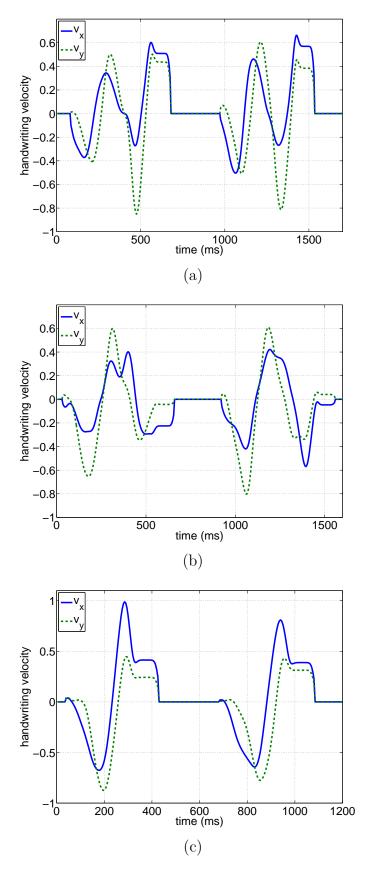

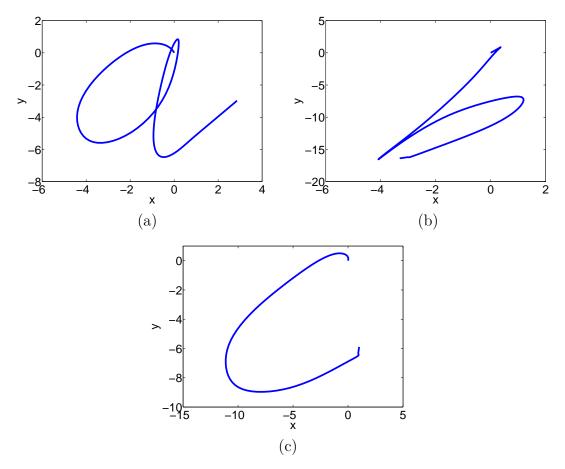

The input and output layer contain the problem's input and desired output variables. For example, in a handwritten character recognition task the inputs may be the pixel intensity values of the image or the trajectories of a pen tip along different directions while the output units represent each one of the characters to be identified (the network must activate the output that most resembles the given input pattern).

In contrast to conventional computers, which are programmed to perform specific tasks, ANNs must be taught, or trained. They have the capability to learn the desired functional dependencies from example data pairs (supervised learning). In this case, the process of training the network corresponds to changing the connection weights systematically to reproduce the desired input-output relationships. Once the network is trained, it is able to reproduce the desired outputs even when stimuli it has never seen before are processed. Moreover, there are different techniques that enable the training of the ANN in an unsupervised way so that the network is able to differentiate stimuli without the presence of a "teacher" indicating which kind of stimulus is sequentially charged in the inputs during the training phase. For this kind of learning, the network is able to produce the same response every time the stimulus is repeating a previously observed pattern. This ability to generalize examples in an "intelligent" way to new inputs is difficult to be reproduced by traditional algorithmic computers.

The field of neural networks is broad and interdisciplinary. The present thesis focuses on their use as learning machines to solve complex engineering problems, but there are more reasons that motivate research in ANNs. From the perspective of computational neuroscience, neural-network models are constructed and simulated to understand better how the brain works and the way it performs computation ([Mac87]). Similarly, psychologists look at artificial neural networks as possible prototype structures of human-like information processing. On the other hand, physicists and mathematicians are interested in studying the properties of neural networks as complex nonlinear dynamical adaptive systems ([Mac02]).

Chapter 2 Introduction

The beginning of neurocomputing goes back to the 1940s when McCulloch and Pitts introduced the first neural network computing model using simple binary threshold functions for the neurons ([MP43]). They noted that many arithmetic and logical operations could be implemented using such models. In 1949, Hebb wrote The Organization of Behavior ([Heb49]), an influential book that pointed out the fact that neural connections are strengthened each time they are used. That is, he proposed a learning rule for synaptic modification. In the late 1950s, Rosenblatt invented a device called the perceptron, a two-layer network (i.e., with no hidden layers) employing the McCulloch-Pitts neuron model, which was capable of learning certain classification tasks by adjusting connection weights ([Ros58]). Slightly later, Widrow developed a different type of neural-network processing element called ADALINE ([Wid60]), which was trained by a gradient descent rule to minimize the mean square error. Such powerful learning method is still nowadays widely used. In 1969, the book *Perceptrons* by Minsky and Papert (MP69) showed the limited capability of simple perceptrons. More especifically, it was demonstrated that the perceptron was not computationally universal as it was unable to solve the classic XOR (exclusive or) problem. This publication is often considered to have caused the decline of the field of neural networks for almost two decades. In the 1980s, the works of Hopfield ([Hop88]) and Rumelhart ([RM86], [RHW86]) with multiple-layered neural networks motivated many researchers to feel renewed interest in neural computation, after which the field exploded again. Nowadays, ANNs still represent an active field of research with relevant applications in various disciplines, such as computer vision ([CMGS10], [JWW15]) and automatic speech recognition ([VSS06], [YD15], [SSR+15]). Recent ANN approaches include long short-term memory (LSTM, [HS97]), reservoir computing (RC, [MNM02], [LJ09]) and deep neural networks (DNNs, [Sch15]) among others. The present thesis deals with the RC technique.

Even though neuroscience has inspired the development of ANSs, this thesis is not directly concerned with biological networks. Rather, my primary interest in ANN models is due to their capability of learning desired input-output relationships from representative data, which makes them a useful engineering tool for a variety of technical applications ([JM99], [Dre05]). ANSs allow us to automate tasks that are complex to be programmed with sequential computers, such as complex pattern recognition. In addition, they provide an arbitrary function approximation mechanism that "learns" from observed data ([Mit16]). That is, they can be used as black-box models to estimate or approximate functions that depend on a number of inputs without the need of deriving an explicit model equation. This is particularly useful in applications where the complexity of the data or task make unfeasible to obtain an analytical model. For example, such black-box models can be used to simulate, predict, filter, classify or control nonlinear dynamical systems, which abound in science and engineering ([JH04]).

There is no doubt that the massively parallel computational networks open a range of opportunities in the areas of artificial intelligence, computational theory, signal processing, modeling and simulation, and others. However, the development of hardware is crucial for the future of neurocomputing since the achievement of fast, efficient and reliable neural networks depends on hardware being specified for its eventual use ([MS10]). This motivates the particular interest of this thesis in the implementation of ANNs (following the RC approach) in digital hardware for building circuit-based intelligent machines.

Next subsections describe the most commonly employed neuron models and how the neural units can be arranged to form different network structures. Finally, the potential application areas of ANNs are described in more detail.

### 2.2.1. The spiking neuron model

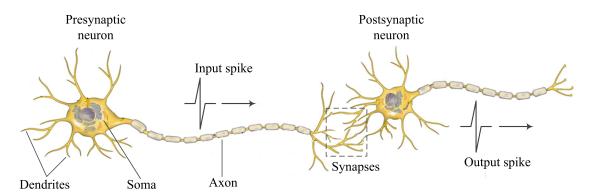

Spiking neural networks represent the last generation of ANNs in an attempt to emphasize the neuro-biological aspects of artificial neural computation. Real biological neurons communicate with each other by means of sequences of electrical pulses, spikes (Fig. 2.2). This is the most characteristic feature of spiking neural models. In addition, the spiking neuron model presents the following general properties ([PK11]):

- The neuron processes the information that comes from the inputs to produce a single spiking signal at the output.

- Its inputs can be excitatory or inhibitory depending on whether they increase or decrease the probability of generating a spike.

- Its dynamics is characterized by at least one state variable. The model produces a spike when the internal variables reach a certain state.

Figure 2.2.: Drawing of two connected biological neurons, which communicate through sequences of spikes. The main parts of the neuron are the dendrites, the axon and the soma (cell body). The presynaptic neuron connects with the postsynaptic one through the synapses. Image adapted from [web16c].

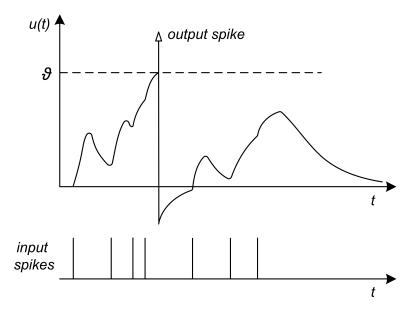

The basic mechanism describing how spiking neurons work is illustrated in Fig. 2.3: the neuron sends out an electrical pulse when it has received a sufficient number of

Chapter 2 Introduction

pulses from other neurons. The membrane potential of a spiking neuron is modeled by a dynamic variable and works as a leaky integrator of the incoming spikes so that newer spikes contribute more to the potential than older ones. If this sum is higher than a predefined threshold, the neuron fires a spike at its output.

**Figure 2.3.:** Basic operation mechanism of the spiking neuron: the incoming pulses (spike trains, represented by vertical lines) increase the membrane potential until it reaches a threshold value and an output spike is fired. Figure adapted from [Boo04].

More specifically, the biological process of spike transmission can be described as follows ([GB14]). The action potentials (spikes) travel along the axons and activate synapses (Fig. 2.2). These synapses release a neurotransmitter that quickly diffuses to the postsynaptic neuron. There, the neurotransmitters affect the neuron's membrane potential. Excitatory Postsynaptic Potentials (EPSPs) increase the membrane potential (depolarize), and in the absence of new stimuli, this excitation leaks away with a typical time constant. On the other hand, Inhibitory Postsynaptic Potentials (IPSPs) decrease the membrane potential (hyperpolarization). When sufficient EPSPs arrive at a neuron, the membrane potential may depolarize enough to reach a certain threshold, and the neuron generates a spike itself while the membrane potential is reset. The generated spike function is the stimulation of other neurons. After the spike emission, the neuron enters a resting state (the refractory period) in which it cannot send out a spike again. Fig. 2.4 illustrates the response of the membrane potential to incoming spikes (only EPSPs are considered).

The neuron's mathematical model is a dynamical system (describing how the input spike train is transformed into an output spike train) that can be given on different levels of abstraction. While some models are very detailed, usually aimed at performing accurate simulations of the biological processes occurring in a single neuron, others are more abstract and generally intended to build networks of neurons and to make them "learn" something. The most famous example of detailed model is the Hodgkin-Huxley model ([HH52]). Other models representing different trade-offs between neuroscientific realism and computational complexity are the Spike Response Model ([MB99], [Boo04]), the Integrate-and-Fire (IF) model ([Ste67], [MB99]), the Leaky-Integrate-and-Fire (LIF) model ([GK02]), the Quadratic-Integrate-and-Fire

**Figure 2.4.:** Response of the membrane potential u(t) to incoming spikes (only excitatory pulses are considered): u(t) increases when spikes arrive to the neuron and decays without new inputs. Whenever u(t) crosses the threshold value  $\vartheta$ , an output spike is generated and u(t) is reset to a low value.

model ([BL03]), the FitzHugh-Nagumo model ([Fit61]), the Morris-Lecar model ([Che93]), the Hindmarsh-Rose model ([HR82]) and the Izhikevich model ([Izh03], [Izh04]).

The most widely employed spiking neuron models are the IF and LIF models as they are relatively simple to implement while capturing generic properties of neural activity ([Vre02]). These consider biological neurons as point dynamical systems, which implies that the properties of biological neurons related to their spatial structure are neglected.

The input and output of a spiking neuron is described by a series of firing times (a spike train), which give the time at which the neuron produces a pulse. The shape of the pulse is neglected since it is generally accepted that all the neural information is carried by the timing of the spikes. Therefore, the output of a spiking neuron can be expressed as in 2.1:

$$S(t) = \sum_{f} \delta(t - t^f) \tag{2.1}$$

Where f=1, 2, ... is the label of the spike and  $\delta(.)$  is the Dirac delta function, which satisfies  $\delta(t) \neq 0$  for t=0 and  $\int_{-\infty}^{\infty} \delta(t) = 1$ .

The LIF model is based on, and most easily explained by, principles of electronics.

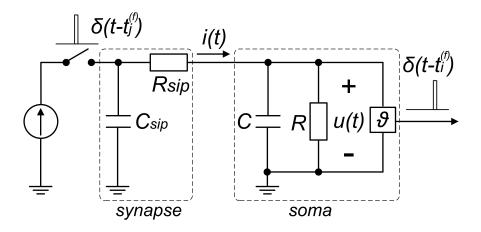

Figure 2.5.: Leaky-integrate-and-fire neuron model.

The schematic circuit representing the LIF unit is illustrated in Fig. 2.5. The incoming spike (presynaptic action potential coming from another neuron) is transformed by a low-pass filter (using the capacitor  $C_{sip}$  and the resistor  $R_{sip}$ ) into a current pulse i(t) that flows into the postsynaptic neuron. This low-pass filter represents the synapse, junction where the presynaptic and postsynaptic neurons communicate with one another. The resulting current pulse charges the leaky integrate-and-fire circuit (composed of a capacitor C in parallel with a resistor R) increasing the membrane potential (voltage over the capacitor) u(t). The neuron fires a spike at time  $t^f$  whenever the membrane potential u(t) reaches a certain threshold value  $\vartheta$ . Immediately after a spike the neuron state is reset to a new value  $u_{res} < \vartheta$  and maintained at that low level for the time interval representing the absolute refractory period  $\Delta^{abs}$ . Therefore, the dynamics of the LIF neuron can be described by equations 2.2, 2.3 and 2.4:

$$C\frac{du(t)}{dt} = -\frac{1}{R}u(t) + (i_o(t) + \sum_{j} w_j \cdot i_j(t))$$

(2.2)

where C represents the membrane capacitance, R is the soma's resistance,  $i_j(t)$  is the input current from the j-th synaptic input and  $w_j$  represents the strength of the j-th synapse. The formula 2.2 also includes an external current  $i_0(t)$  that may drive the neural state. For the particular case in which  $R \to \infty$ , equation 2.2 describes the simpler IF model.

The firing time  $t^{(f)}$  is defined by the threshold criterion :

$$t^{(f)}: u(t^{(f)}) = \vartheta$$

(2.3)

An additional equation is necessary to impose the reset condition immediately after  $t^{(f)}$ :

$$\lim_{t \to t^{(f)}, t > t^{(f)}} u(t) = u_{res} \tag{2.4}$$

The combination of leaky integration (2.2) and reset (2.4) defines the basic integrateand-fire model ([Ste67]). In addition, to incorporate an absolute refractory period, we proceed as follows. If u(t) reaches the threshold at time  $t = t^{(f)}$ , we interrupt the dynamics (2.2) for an absolute refractory time  $\Delta^{abs}$  and restart the integration at time  $t^{(f)} + \Delta^{abs}$  with the new initial condition  $u_{res}$ .

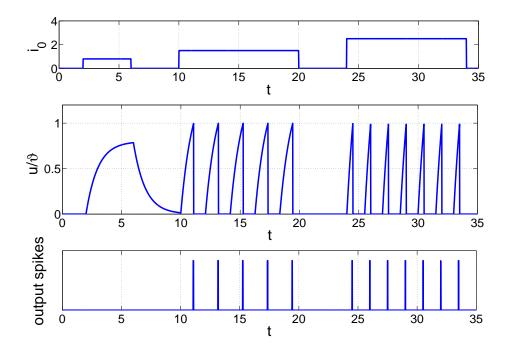

An exemplary simulation of a LIF neuron driven by an external input current  $i_0(t)$  is shown in Fig. 2.6.

Figure 2.6.: Exemplary simulation of a LIF neuron driven by an external input current  $i_0(t)$ . The top panel displays the input current, the middle panel depicts the membrane potential, and the bottom panel shows the firing times of the output spikes. The variables are represented in a dimensionless form as proposed in [LR03]. The current  $i_0(t)$  increases the membrane potential u(t) towards the firing threshold  $\vartheta$ . The neuron emits a spike when u(t) reaches the threshold value, and then u(t) is reset to  $u_{res}$  (here assumed to be  $u_{res} = 0$ ). After firing, u(t) is hold at  $u_{res}$  for a refractory period. It can be observed that higher values of the input current generate output spikes with a higher rate.

#### 2.2.1.1. Spike coding

For spiking neural networks to perform computations, it is necessary to give some meaning to neural spiking. The way how information is represented in biological neural systems is an open question. A number of different neural codes has been proposed based on observations of the nervous system in animals.

Rate coding has been the dominant paradigm of neural information encoding in neuroscience for many years. It considers the rate of spikes in a certain interval as the only measure for the information conveyed. This encoding is motivated by the observation that physiological neurons tend to fire more often for stronger stimuli and in an unpredictable way ([AZ26]). Rate coding is the notion behind standard artificial sigmoidal neurons (sec. 2.2.2). However, recent findings suggest that, at least for some neural systems, information is more likely to be encoded in the precise timing of the spikes ([WRK15]). In particular, findings in the field of neurology show that some neurons perform computations too quickly for the underlying sensory process to rely on the estimation of the neural firing rate over extended time windows (for example, human neurons in the cortex performing facial recognition, [TDVR01]). This does not mean that rate coding is not used, but other pulse encoding schemes are favored when speed is an issue ([Vre02]).

A different neural coding strategy is the "time-to-first-spike" coding, which enables ultra-fast information processing ([PK11]). In this approach, information is carried in the latency time between the beginning of the stimulus and the time of the first spike in the neural response. Other neural coding schemes include (among others) phase coding, population activity coding, rank order coding and neural codes based on correlation, which encode the information by defined correlations between the spike timing of selected neurons. The reader is referred to [PK11], [GB14] and [WRK15] for more detailed information on the different methods to encode analog information in spike trains.

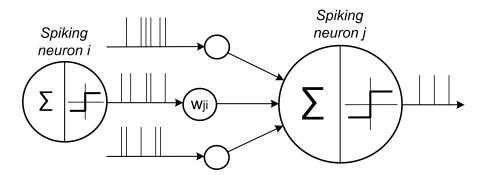

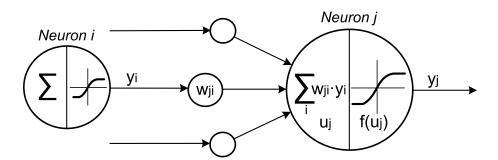

# 2.2.2. The discrete-time (sigmoidal) neuron

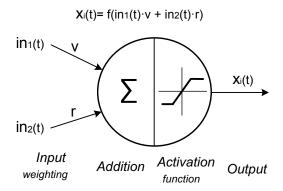

As introduced in sec. 2.2.1.1, a spiking neuron can be modeled by means of the standard artificial sigmoidal neuron when the firing rate is considered to carry the neural information. The operation of the sigmoidal unit is illustrated in Fig. 2.7. In such a discrete-time model, the output of the neuron (activation) is an analog quantity (usually lying between 0 and 1) instead of a train of spikes. The synapse between two neurons is modeled by a weight variable that describes the strength of the impact on the postsynaptic neuron. The weights can be positive or negative to model excitatory or inhibitory synapses, respectively. The sigmoidal neuron sums up all the weighted firing-rates of its presynaptic neurons to get its potential. The neuron's output is calculated from this potential using the activation function, which typically has a sigmoid shape (hence the name sigmoidal neuron). The activation

variable in this model can be seen as the firing rate of the neuron (number of spikes in a certain period of time).

It is worth noting that a single spiking neuron is a dynamical system (where the incoming spikes are integrated over time to produce the output). Its output not only depends on the current input received from other neurons, but also on an internal state which evolves over time. On the other hand, the sigmoidal neuron is static (an output is produced for a given input at each discrete time step).

Figure 2.7.: Basic operation of the sigmoidal neuron. The activation potential  $(u_j)$  is first calculated as the weighted sum of the neuron inputs  $(\sum_i w_{ji}y_i)$ , and then passed to the non-linear activation function (f(.)), typically with sigmoid shape) to get the neuron output  $(y_j)$ . The weight value  $w_{ji}$  represents the strength of the synapse between the presynaptic unit (neuron i) and the postsynaptic one (neuron j). Figure adapted from [Boo04].

Therefore, the behavior of the standard sigmoidal neuron can be formally described as follows:

$$y_j = f(\sum_i w_{ji} y_i + b_j) \tag{2.5}$$

where  $w_{ji}$  is the connection weight between neuron i and neuron j,  $y_i$  is the output (activation level) of the i-th neuron,  $b_j$  is the neuron bias and f is the transfer or activation function.

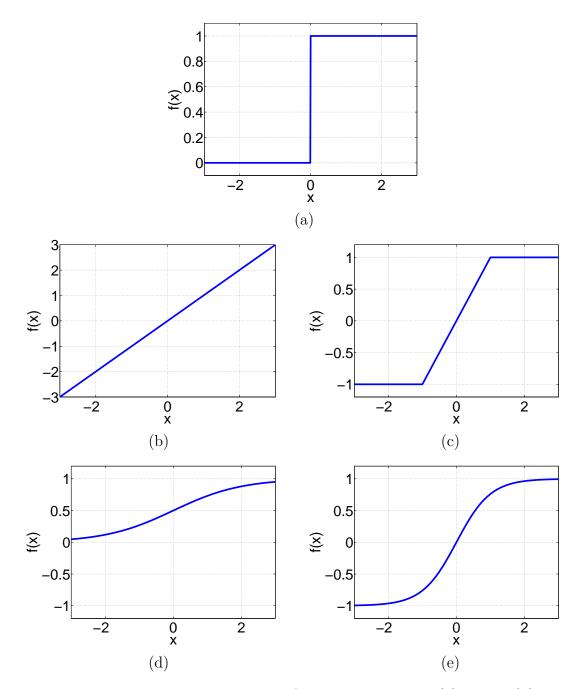

#### 2.2.2.1. The activation function

The transfer function f determines the behavior of the analog (discrete-time) neuron. It usually has a sigmoid shape, that is, an "S" shaped curve. However, it may also take the form of other nonlinear functions, such as the step function or the piece-wise linear function. Even the identity function is sometimes used to build ANNs (in this case, the neuron is called linear). Some typical examples of transfer functions are depicted in Fig. 2.8.

Figure 2.8.: Most common activation functions: threshold (a), linear (b), piecewise linear (c), fermi (d) and hyperbolic tangent (e).

The most commonly used sigmoid functions are the hyperbolic tangent (being [-1, 1] its output range) and the fermi (or logistic) function ([0, 1] range). The fermi function is defined by the formula 2.6 and is related to the hyperbolic tangent function [tanh(.)] according to 2.7:

$$fermi(x) = \frac{1}{1 + exp(-x)} \tag{2.6}$$

$$tanh(x) = 2 fermi(2x) - 1 (2.7)$$

The Heaviside (threshold, or step) function represents the binary neuron, which corresponds to the first generation of neurons proposed by McCulloch and Pitts ([MP43]). In this case, the neuron can only give a digital output: it sends a binary high value ("1") if the sum of the weighted inputs surpasses the threshold level, and a low value ("0") otherwise.

On the other hand, the neurons using a continuous function (instead of the threshold one) belong to the second generation of neurons, which allows analog outputs. Networks of neurons of this type are more powerful than the ones based on first-generation units (they can perform the same functions using fewer nodes). The neurons of the second generation are also more biologically realistic and similar to the spiking neurons (representing the third and last generation) than the first generation ones since they can model the spiking frequency (firing rate) and not only a high or low value.

The second-generation activation functions are often required to be continuous, derivable and bounded. The necessity for being derivable comes from the fact that the most common learning algorithms for training an ANN to perform a certain function need to compute the derivative of the transfer function ([RHW86]).

#### 2.2.3. Network architectures

Given the models of neurons we can define a network of artificial neurons. A network is defined by a set of neurons and the connections between them, determined by a weight matrix  $(\mathbf{W})$ . Network topologies can be classified into two general categories: feed-forward and recurrent.

#### 2.2.3.1. Feed-forward neural networks

A feed-forward neural network (FFNN) has its neurons organized in layers with no feedback or lateral connections. The inputs to the network are fed in through the

input layer and the outputs are read out at the output layer. Intermediate neurons are grouped in the hidden layers. The input signal propagates through the network only in a forward direction, on a layer-by-layer basis as illustrated in Fig. 2.9. Such type of network is often referred to as a multi-layer perceptron (MLP, [MAL88]) although the neurons do not necessarily have to use a Heaviside step function (as in the original perceptron model proposed by Rosenblatt, [Ros58]), but can take on any arbitrary activation function.

Figure 2.9.: Schematic representation of a feed-forward neural network (FFNN).

Adjusting the connection weights alters the information flow through the network. That is, if the strengths of the incoming signals of a neuron are modified, the output signal also changes in strength. The process of training the network corresponds to changing the connection weights systematically to encode the desired input-output relationships. Error backpropagation ([RHW86]) is the most commonly used supervised learning algorithm for FFNNs. Similarly to the least mean squares algorithm, it iteratively adapts the network weights based on corrections that minimize the mean square error between the target values and those produced by the network. Since the change in each weight is calculated through the derivative of the error (gradient-descent approach), a continuous activation function is required for the neurons.

MLPs are universal function approximators ([Cyb89]), so they can be used for mathematical regression and as classifiers. They have been widely studied and employed due to their learning and generalization capabilities. However, a drawback of MLPs is their inability to process temporal information, which is crucial to perform tasks such as speech recognition or time-series forecasting where the order of the input sequences is relevant. A solution to this problem is to take a window of delayed values of the input stream as inputs to the network instead of only one ([WHH<sup>+</sup>89]). Another approach is to add recurrent connections to the network, which leads to a recurrent neural network.

#### 2.2.3.2. Recurrent neural networks

Recurrent neural networks (RNNs) present feedback connections between neurons so that information can propagate forward and backwards through the layers. An example of this topology is illustrated in Fig. 2.1. The layered structure, however, can be substituted by an equivalent architecture with a single hidden layer containing internal recurrent connections as depicted in Fig. 2.10.

The recurrent connections endow the network with "memory" as the activation values of the neurons (states) do not only depend on the current value of the input signal but also on the previous network states, and therefore (recursively) on the entire input history. In an analogy with digital electronics, FFNNs (whose neuron states are fully determined by the values of the inputs) form a combinational circuit while RNNs (depending on previous network states) constitute a sequential one. RNNs are dynamical systems whose states may evolve in time even in the absence of external inputs whereas FFNNs provide passive and reactive functions to the input stimuli.

The major advantage of RNNs over FFNNs is that they can implicitly learn temporal tasks. The states of a RNN are nonlinear transformations of the input history that can be effectively used for processing temporal context information. As a matter of fact, RNNs are universal approximators of dynamical systems ([FN93], [SZ07]), which makes them a promising tool for applications requiring nonlinear time-series processing.

In recent years, RNNs have been extensively used to successfully solve computationally hard problems such as speech recognition, machine control or dynamical system modeling and prediction ([ZB01], [LZPH14], [BM15], [MYWW15], [AGAS+15], [MM15]). RNNs based on different "Deep Learning" schemes ([YD15], [Sch15], [LBH15]) and long short-term memory (LSTM, [HS97], [LW15]) approaches are specially outstanding for their high accuracy.

Nevertheless, RNNs present the shortcoming of being difficult to train. The training procedure for RNNs is complex and very time consuming. As in FFNNs, the training of RNNs is based on gradient descent, a method of gradually adapting all the network weights according to the output error gradients (derivatives with respect to the weights) so that such output training error is minimized. "Backpropagation through time" (BTT, [Wer90]) is one of the most prominent algorithms for RNN training. A review of the numerous existing approaches can be found in [AP00] and [Jae02]. In general, these algorithms suffer from slow convergence and may eventually end in local minima. In some cases, such methods might even not converge due to bifurcations during the training process (i.e., infinitesimally small changes to the network weights lead to drastic discontinuous changes in its behavior, [Doy92]). The calculation of each iteration for updating the weight parameters is computationally intensive and many update cycles are often required. As a result, considerable processing resources need to be dedicated to train large recurrent networks.

The long training time of RNNs can be compensated through parallel computing. In particular, the use of general purpose graphical processing units (GPUs) instead of ordinary CPUs makes possible to reduce the training times for some networks from months to days ([Edw15]). The recent success of recurrent deep neural networks can be partly attributed to the availability of powerful computing architectures such as GPUs ([SSC16]). However, the complex training of RNNs needs very specialized knowledge, substantial skill and experience to be successfully applied.

To sum up, RNNs are a very powerful tool for solving complex temporal machine learning tasks, but its application to real-world problems involves high computational training costs and is reserved for experts in the field. Reservoir computing offers a practical alternative to the hard traditional training of RNNs.

## 2.2.4. Applications of ANNs

ANNs allow to infer a function from observations. That is, they can be used to approximate a target function in a specific task by only using measured data. Prior knowledge about the input-output relationship is not necessary. What is more, when the networks present recurrences (RNNs), they can be employed for building mathematical models of any dynamical system from the experimental data, which is usually referred to as "system identification" or "black-box" modeling. This is of great utility when it is unfeasible to obtain an analytical model due to the complexity of the process. Complex dynamical systems are present in a variety of fields: physics, biology, engineering, economics, medicine, etc. Therefore, ANNs can be applied in many different disciplines ([JM99], [Dre05], [JIM16]).

The general tasks ANNs can be applied to include function approximation, time-series prediction, classification (both pattern and sequence recognition) and data processing such as filtering or clustering. Application areas are (among many others) the control of machines and industrial processes ([BL91], [CR95], [ZL08]), robotics ([Bur05b], [ASD+07]), computer vision (object recognition, face identification, event detection in video sequences, etc., [PDS09], [CMS12], [OZW+16]), radar systems ([WGM+03]), speech and bio-metric feature recognition (e.g., gesture, gait, handwriting, fingerprint, etc., [ASB13], [LW15], [ERG15], [YAT16]), thermal engineering and renewable energy systems ([MJM12], [FFD12]), fault detection ([JM15]), sensor networks ([CSC13], [AMN14]), medical diagnosis (e.g., classification of heart beat and brain activity signals, [AKS05], [SE05], [GTK+14]), finances (e.g., investment support systems based on the prediction of stock markets, [MM15]) and data mining ([LSL96]).

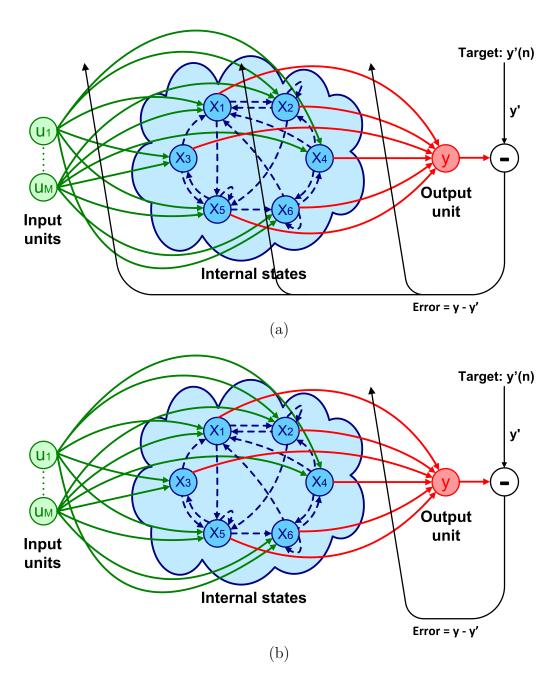

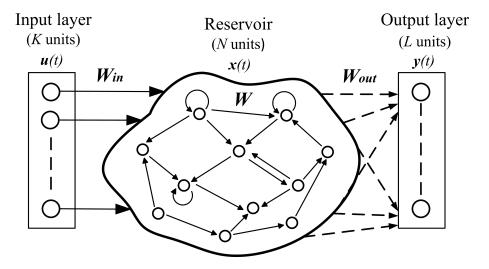

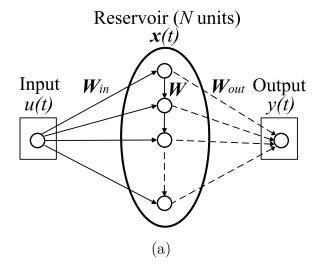

# 2.3. Reservoir computing

Reservoir computing (RC) is a relatively recent technique for implementing and training RNNs. Contrary to conventional RNNs, where all connections need to be adapted to minimize the training error, most connection weights in an RC system are kept fixed and only an output layer is configurable as illustrated in Fig. 2.10. This strategic design reduces the complex and time-consuming training procedure of classical fully-trained RNNs to a simple linear regression problem, which enormously facilitates the practical application of RNNs. In other words, RC takes advantage of the memory properties of recurrent networks while avoiding the difficulties associated with their training ([PK11]).

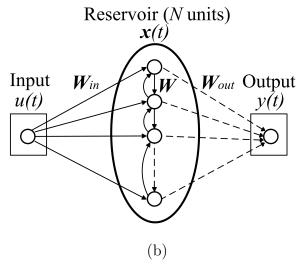

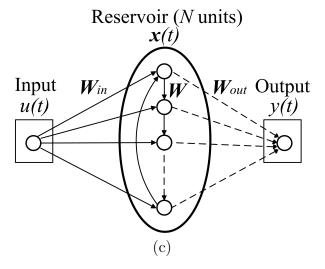

RC avoids the shortcomings of RNN training mentioned in sec. 2.2.3.2 by separating the whole recurrent network in two different parts (Fig. 2.10(b)):

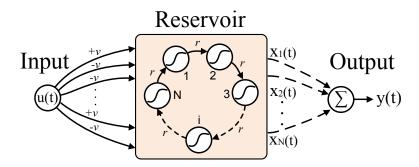

- The reservoir, which consists of a RNN that is randomly generated and remains unchanged throughout the training process. Under the influence of input signals, the neurons in the reservoir exhibit transient responses (nonlinear transformations of the input history).

- The output layer, a linear weighted sum of the input-excited reservoir states. The weights of this linear combination are obtained by linear regression, using the teacher signal as target.

The strategy of treating the recurrent part of the network as a generic device and concentrating the learning efforts on the training of linear readouts from the recurrent circuit was already suggested in the 1960s by Rosenblatt ([Ros62]). In addition, some research works in the field of computational neuroscience also proposed the use of network architectures similar to RC in the 1990s ([Dom95], [BM95]) describing a randomly constructed recurrent network that is left unchanged and connected to an easy-to-train output layer. However, the RC concept was more rigorously investigated and became popular over the last decade, after the publications of Jaeger ([Jae01]) and Maass ([MNM02]). The report of Jaeger ([Jae01]) suggested the concept of RC in the context of non-spiking ANNs under the name of echo state networks (ESNs) while the work of Maass ([MNM02]) adopted RC for spiking networks under the name of liquid state machines (LSMs). The term reservoir computing was proposed ([VSDS07]) to jointly refer to the fundamental idea behind these two independently developed approaches. The ease of use and good performance of the RC methodology led to a fast growth of the field (see, for example, [VSDS07], [JMP07], [LJ09] and [LJS12] for an overview of the related research). Nowadays, RC is regarded as one of the basic paradigms of RNN modeling ([Jae07b]).

As a particular type of RNN, RC represents a promising tool for nonlinear time series applications, such as temporal pattern classification and time-series prediction. For example, RC has been shown to present outstanding performance in predicting chaotic dynamics ([JH04], [RT11], [NR15], [GSS15]) and in speech recognition ([VSSVC05], [JLPS07]). Beside its high modeling accuracy, RC systems present the

Figure 2.10.: (a) General RNN architecture: all connection weights are adapted in order to minimize the training error. (b) RC system: only the connections coupling the RNN to the output unit (in red color) are adapted, the rest remain unchanged allowing a simple training procedure.

advantage that their easy training algorithm, contrary to conventional RNNs, does not need substantial skill and experience to be successfully applied.

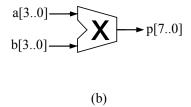

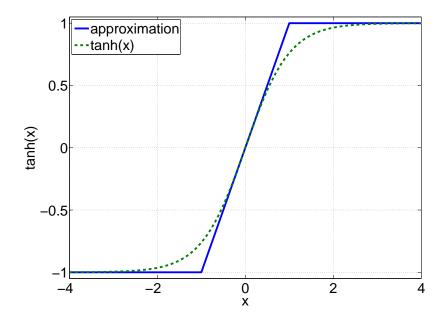

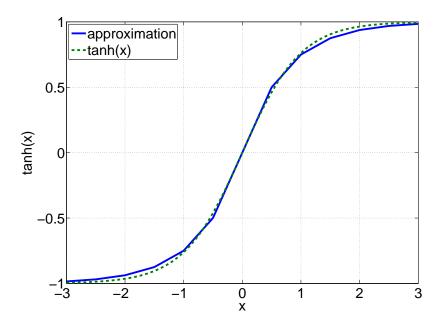

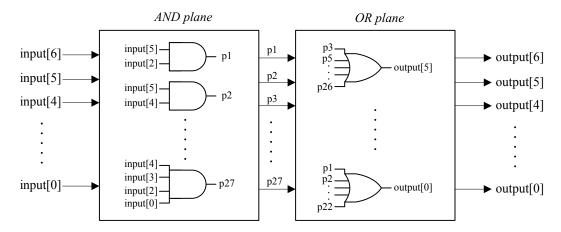

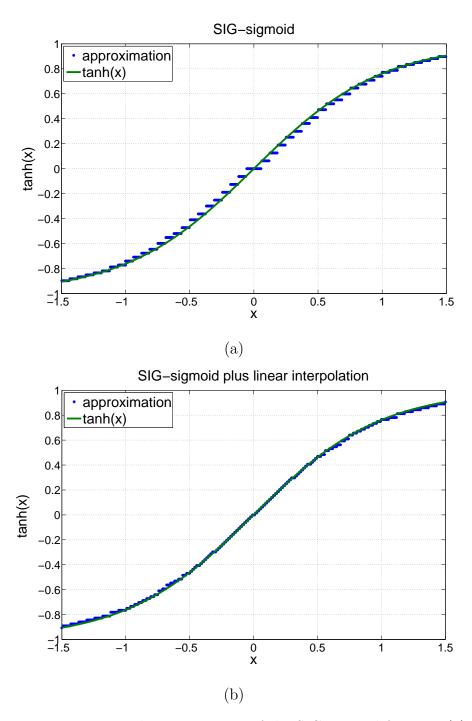

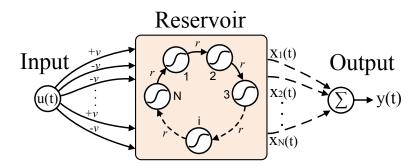

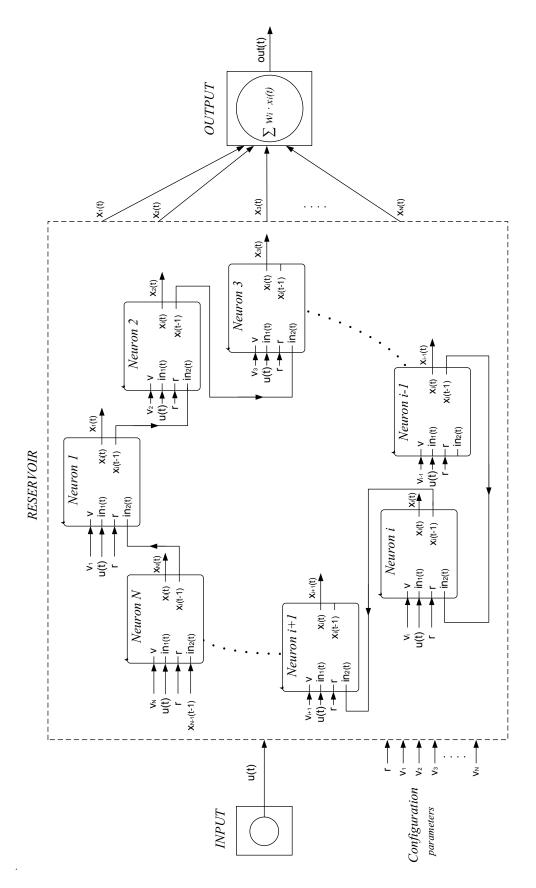

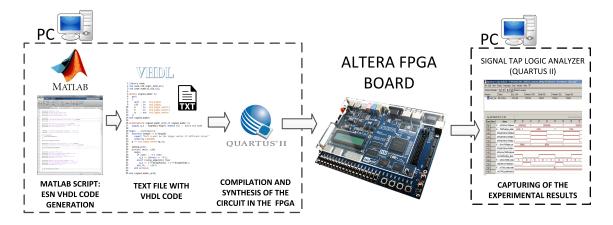

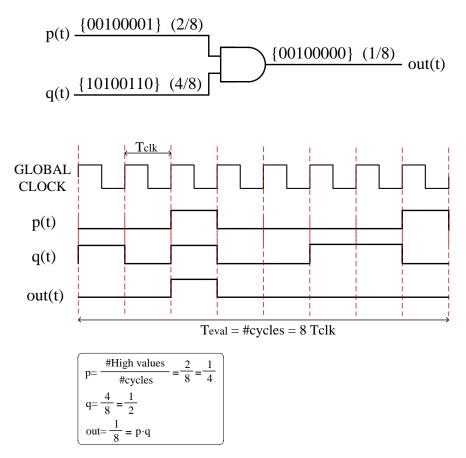

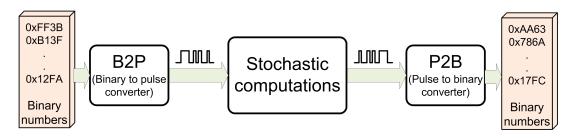

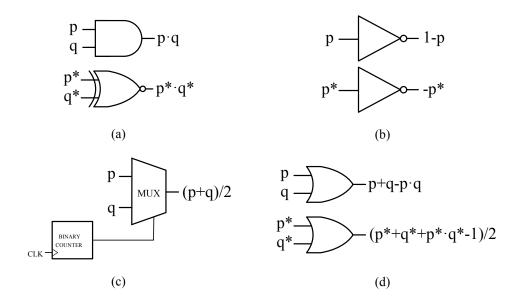

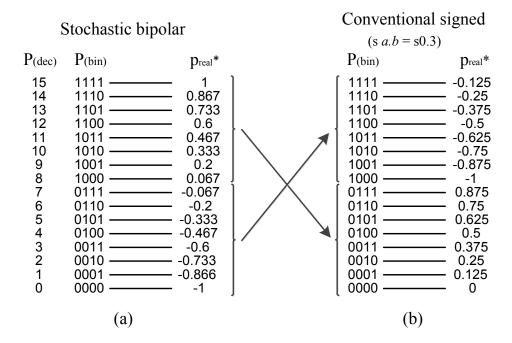

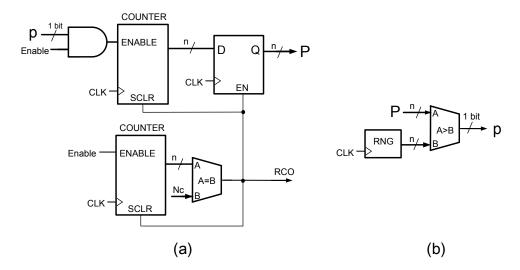

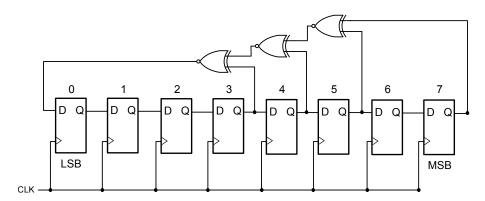

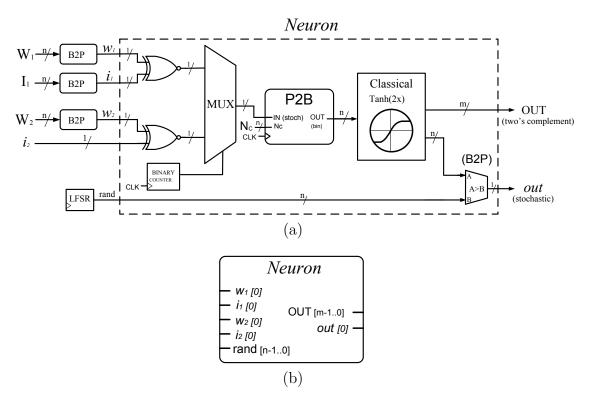

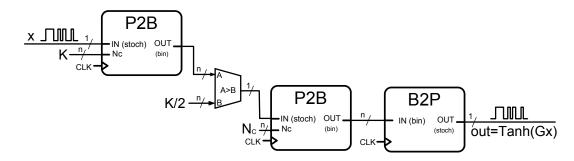

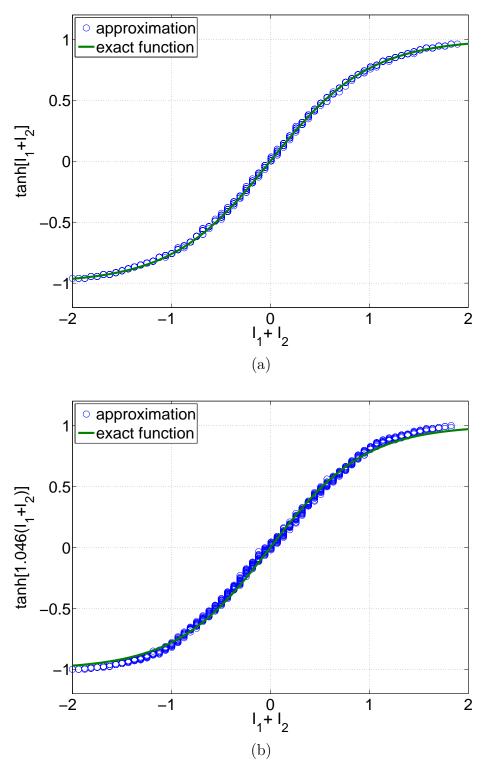

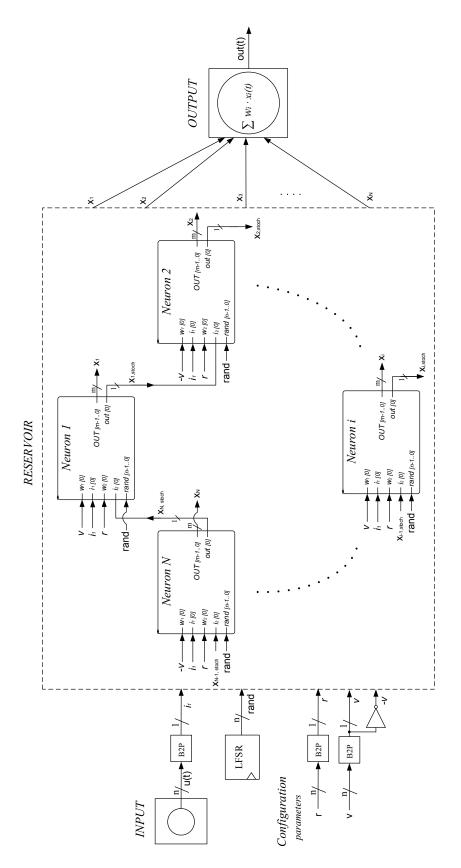

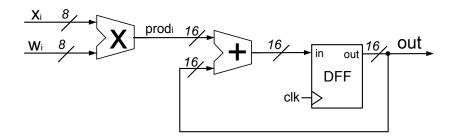

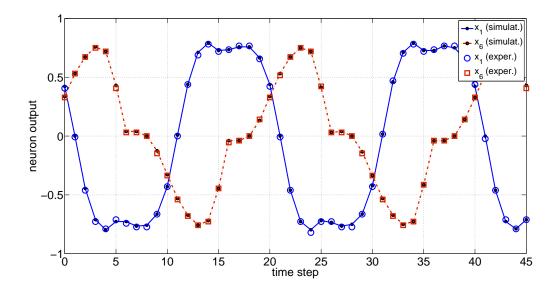

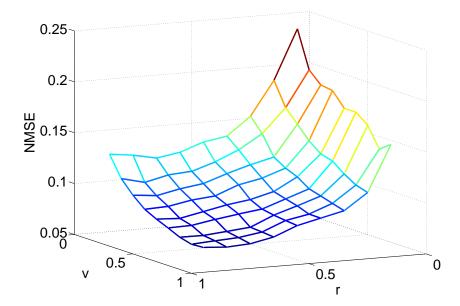

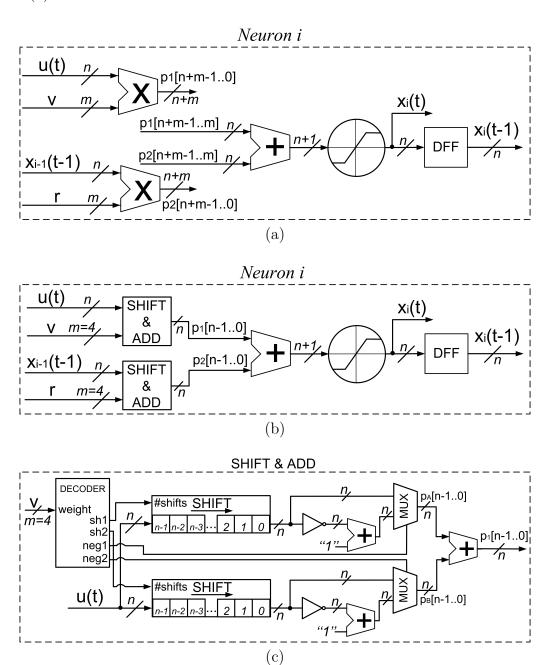

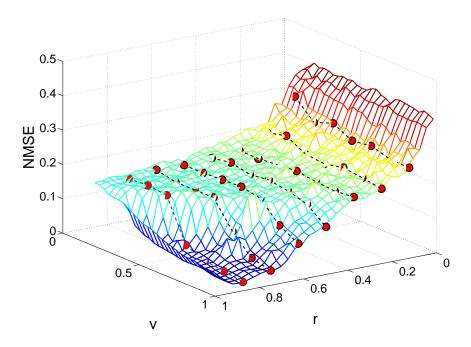

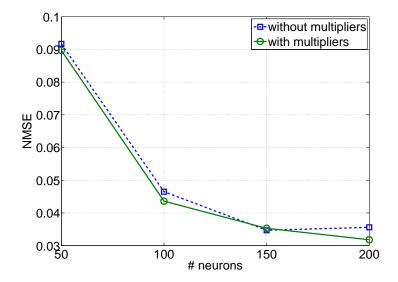

The biological plausibility of RC-based systems has been another reason motivating their development. The basic idea of RC to make use of the transient states generated in an intricate network of neurons (the reservoir) when stimulated by an external input is indeed based on the way our brain seems to process the information arriving from sensory inputs. This was contemplated in the works [BM95] and [MNM02]. Following studies further discussed the neurophysiological reality of the RC scheme. For example, a LSM was proposed in [YT07] for the modeling of the cerebellum. Other works supporting the idea of the brain behaving similarly to a reservoir computer are [RHL08], [NUSM09] and [SvHS+13].