## Reducing Redundancy of Real Time Computer Graphics in Mobile Systems

Enrique de Lucas

Doctor of Philosophy UNIVERSITAT POLITÈCNICA DE CATALUNYA

Department of Computer Architecture Barcelona, 2018

## Reducing Redundancy of Real Time Computer Graphics in Mobile Systems

Enrique de Lucas

ADVISERS Dr. Joan-Manuel Parcerisa Dr. Pedro Marcuello

### ARCO Research Group Department of Computer Architecture UNIVERSITAT POLITÈCNICA DE CATALUNYA Barcelona Spain

Thesis submitted for the degree of Doctor of Philosophy at the Universitat Politècnica de Catalunya

##

## 'Gutta cavat lapidem, [non vi, sed saepe cadendo]'

–Publius Ovidius Naso, in Epistulae ex Ponto IV, 10, 5. Expanded in the Middle Ages.

### Keywords

Collision Detection, GPU, Android, Rasterization, Mobile GPU, Rendering, Image Based Collision Detection, Graphics Rendering Hardware, Object Interference Detection, Rasterizing Graphics Hardware, Overdraw, Overshading, Rendering Order, Front-to-back, GPU microarchitecture, Visibility, Hidden Surface Removal, Deferred Rendering, Deferred Shading, TBR, TBDR, Temporal Coherence, Frame Coherence, Topological Order, Topological Sort, Energy-efficiency

### Abstract

At each new generation the growing computing power of mobile devices has promoted the adoption of more powerful support for graphics and real-time physics simulations with increasing precision and realism. Given the battery-operated and handheld nature of these devices they must use as little energy as possible, because it is crucial to enlarge battery life and to keep a comfortable surface touch temperature. Hence, software and hardware improvements are crucial to deliver a low-power yet rich user experience that satisfies the user demands on the functionality of mobile devices.

The goal of this thesis is to propose novel and effective techniques to eliminate redundant computations that waste energy and are performed in real-time computer graphics applications, with special focus on mobile GPU micro-architecture. Improving the energy-efficiency of CPU/GPU systems is not only key to enlarge their battery life, but also allows to increase their performance because, to avoid overheating above thermal limits, SoCs tend to be throttled when the load is high for a large period of time. Prior studies pointed out that the CPU and especially the GPU are the principal energy consumers in the graphics subsystem, being the off-chip main memory accesses and the processors inside the GPU the primary energy consumers of the graphics subsystem.

In the first place, we focus on reducing redundant fragment processing computations by means of improving the culling of hidden surfaces. During real-time graphics rendering, objects are processed by the GPU in the order they are submitted by the CPU, and occluded surfaces are often processed even though they will end up not being part of the final image. When the GPU realizes that an object or part of it is not going to be visible, all activity required to compute its color and store it has already been performed. We propose a novel architectural technique for mobile GPUs, Visibility Rendering Order (VRO), which reorders objects front-to-back entirely in hardware to maximize the culling effectiveness of the GPU and minimize overshading, hence reducing execution time and energy consumption. VRO exploits the fact that the objects in graphics animated applications tend to keep its relative depth order across consecutive frames (temporal coherence) to provide the feeling of smooth transition. VRO keeps visibility information of a frame, and uses it to reorder the objects of the following frame. Since depth-order relationships among objects are already tested in the GPU, VRO incurs minimal energy overheads. It just requires adding a small hardware to capture the visibility information and use it later to guide the rendering of the following frame. Moreover, VRO works in parallel with the graphics pipeline, so negligible performance overheads are incurred. We illustrate the benefits of VRO using various unmodified commercial 3D applications for which VRO achieves 27% speed-up and 14.8% energy reduction on average.

In the second place, we focus on avoiding redundant computations related to CPU Collision Detection. Graphics animation applications such as 3D games represent a large percentage of downloaded applications for mobile devices and the trend is towards more complex and realistic scenes with accurate 3D physics simulations. Collision detection (CD) is one of the most important algorithms in any physics kernel since it identifies the contact points between the objects of a scene, and determines when they collide. However, real-time highly accurate CD is very expensive in terms of energy consumption. We propose Render Based Collision Detection (RBCD), a novel energy-efficient high-fidelity CD scheme that leverages some intermediate results of the rendering pipeline to perform CD, so that redundant tasks are done just once. Comparing RBCD with a conventional CD completely executed in the CPU, we show that its execution time is reduced by almost three orders of magnitude (600x speedup), because most of the CD task of our model comes for free by reusing the image rendering intermediate results. Although not necessarily, such a dramatic time improvement may result in better frames per second if physics simulation stays in the critical path. However, the most important advantage of our technique is the enormous energy savings that result from eliminating a long and costly CPU computation and converting it into a few simple operations executed by a specialized hardware within the GPU. Our results show that the energy consumed by CD is reduced on average by a factor of 448x (i.e., by 99.8%). These dramatic benefits are accompanied by a higher fidelity CD analysis (i.e., with finer granularity), which improves the quality and realism of the application.

## Acknowledgements

First of all I want to thank my advisers, Joan-Manuel Parcerisa and Pedro Marcuello, who have taught me almost everything I know about Computer Architecture. They always offered me valuable guidance and support as well as they were involved in my day-to-day work. I am truly convinced I could not have had better advisers. I am also very grateful to Prof. Antonio González, who offered me the opportunity to start in this research area, first at Intel Barcelona and then at UPC<sup>1</sup>. Thanks for your sagacious feedback and your wise advise.

I wish to thank the members of ARCO I met these years. Especially to José María Arnau, whose outstanding and pioneering work encouraged me to work in the field of low-power GPUs. I am grateful for all his support and help and for teaching me what an international conference is about. Thanks to Martí -the one- for continuing the research line in ARCO group. Thank you Gem and Emilio for your feedback and friendship. I also wish to thank the "The D6ers": Albert, Franyell, Hamid, Josue, Marc, Martí -the other one- and Reza. I wish you the best of luck. I am lucky to have met all my friends from Campus Nord. Enric, Gemma, Javi, Manu, Marc, Niko and Oscar, who welcomed me to Barcelona and shared with me seminars, meetings, coffees, dinners and parties. However, they did not warn me about where I got when I started the doctorate.

I am really blessed to have so many great friends like Alex, Andrés, David, Guille, Javi, Manu, Oscar and Rubén, who have shared with me many moments for more than 15 years. Thank you for your moral support, motivation and friendship, which made this journey more comfortable and drove me to give my best.

Finally, I would like to express my deepest gratitude to my family for their commitment, their unconditional love, their support and their infinite patience. Especially Jenifer, who closely shared with me joys and celebrations during this thesis, but also had to keep up with me during the endless periods of stress that precede academic deadlines. Thank you for your patience, comprehension, and support during these years of thesis.

<sup>&</sup>lt;sup>1</sup>This work has been supported by the Spanish State Research Agency under grants TIN2013-44375-R, TIN2016-75344-R (AEI/FEDER, EU), and BES-2014-068225.

## Contents

| 1 | Intr | oduct  | ion                                     | 25 |

|---|------|--------|-----------------------------------------|----|

|   | 1.1  | Curre  | nt Trends                               | 25 |

|   |      | 1.1.1  | Real Time Mobile Graphics Software      | 26 |

|   |      | 1.1.2  | Mobile Graphics Hardware                | 28 |

|   | 1.2  | Proble | em Statement                            | 30 |

|   |      | 1.2.1  | Major Energy Consumers                  | 31 |

|   |      | 1.2.2  | Major GPU Energy Consumers              | 33 |

|   |      | 1.2.3  | Occlusion Culling                       | 34 |

|   |      | 1.2.4  | Collision Detection                     | 35 |

|   | 1.3  | State  | of the art                              | 35 |

|   |      | 1.3.1  | Reduction of Redundant Fragment Shading | 35 |

|   |      | 1.3.2  | Collision Detection                     | 39 |

|   | 1.4  | Thesis | s Overview and Contributions            | 42 |

|   |      | 1.4.1  | Visibility Rendering Order              | 42 |

|   |      | 1.4.2  | Render Based Collision Detection        | 44 |

|   |      | 1.4.3  | Other contributions                     | 46 |

| 2 | Bac  | kgrou  | nd                                      | 49 |

|   | 2.1  | Graph  | ics Rendering Pipeline                  | 49 |

|   |      | 2.1.1  | Application Stage                       | 49 |

|   |      | 2.1.2  | Geometry Stage                          | 50 |

|   |      |        |                                         |    |

### CONTENTS

|   |     | 2.1.3   | Rasterization                                                                 | 55       |

|---|-----|---------|-------------------------------------------------------------------------------|----------|

|   | 2.2 | GPU I   | Microarchitecture:                                                            | 59       |

|   |     | 2.2.1   | Immediate Mode Rendering                                                      | 59       |

|   |     | 2.2.2   | Tile Based Rendering                                                          | 60       |

| 3 | Met | thodolo | ogy                                                                           | 63       |

|   | 3.1 | Simula  | ators                                                                         | 63       |

|   |     | 3.1.1   | GPU Simulation                                                                | 63       |

|   |     | 3.1.2   | Collision Detection CPU Simulation with Marss86 and Bullet                    | 67       |

|   | 3.2 | Bench   | marks                                                                         | 68       |

|   |     | 3.2.1   | Benchmarks Set                                                                | 69       |

|   |     | 3.2.2   | Benchmarks Characterization                                                   | 72       |

| 4 |     | •       | Rendering Order: Improving Energy Efficiency on Mobile GPUs throug<br>herence | gh<br>77 |

|   | 4.1 | Visibil | ity Determination and Overshading                                             | 79       |

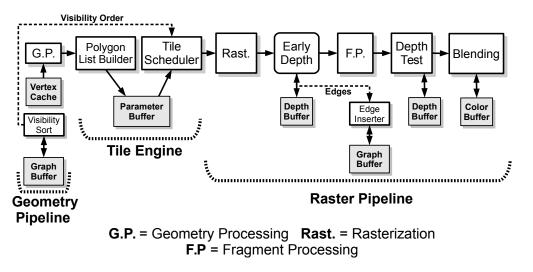

|   | 4.2 | Visibil | ity Rendering Order                                                           | 81       |

|   |     | 4.2.1   | Overview                                                                      | 81       |

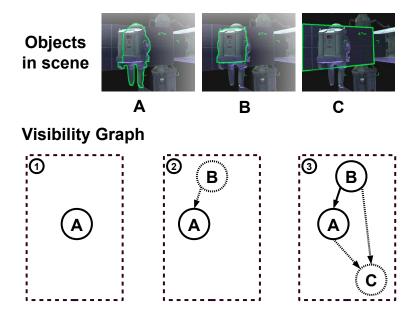

|   |     | 4.2.2   | Graph Generation                                                              | 82       |

|   |     | 4.2.3   | Sort Algorithm                                                                | 83       |

|   |     | 4.2.4   | Heuristics to Sort the Objects in a Scene                                     | 85       |

|   |     | 4.2.5   | Partial Order of Objects                                                      | 87       |

|   |     | 4.2.6   | Visibility Rendering Order Adjustments                                        | 88       |

|   | 4.3 | Microa  | architecture                                                                  | 88       |

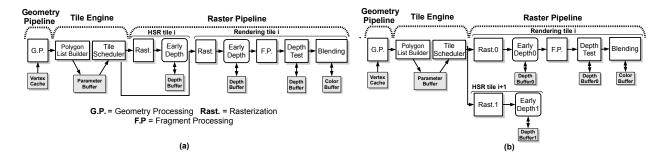

|   |     | 4.3.1   | Deferred Rendering TBR GPU                                                    | 88       |

|   |     | 4.3.2   | Visibility Rendering Order TBR GPU                                            | 90       |

|   | 4.4 | Experi  | imental Framework                                                             | 96       |

|   |     | 4.4.1   | GPU Simulation                                                                | 98       |

|   | 4.5 | Experi  | imental Results                                                               | 98       |

### CONTENTS

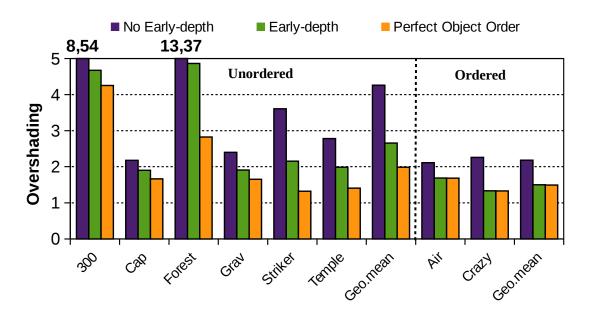

|   |     | 4.5.1   | Effectiveness of VRO                                        | . 98  |

|---|-----|---------|-------------------------------------------------------------|-------|

|   |     | 4.5.2   | Overshading with Different Heuristics to Break Graph Cycles | . 103 |

|   | 4.6 | Conclu  | usion                                                       | . 104 |

| 5 | Ren | ider-B  | ased Collision Detection for CPU/GPU Systems                | 105   |

|   | 5.1 | Collisi | ion Detection                                               | . 105 |

|   |     | 5.1.1   | Image Based Collision Detection                             | . 106 |

|   |     | 5.1.2   | Enabling RBCD in the GPU                                    | . 108 |

|   | 5.2 | Microa  | architecture                                                | . 109 |

|   |     | 5.2.1   | RBCD Overview                                               | . 109 |

|   |     | 5.2.2   | Identification of Collisionable Objects                     | . 109 |

|   |     | 5.2.3   | Deferred Face Culling                                       | . 111 |

|   |     | 5.2.4   | Insertion into the Z-depth Extended Buffer                  | . 111 |

|   |     | 5.2.5   | Z-Overlap Test                                              | . 112 |

|   |     | 5.2.6   | Animation Loop                                              | . 113 |

|   |     | 5.2.7   | Power model of the RBCD unit                                | . 115 |

|   |     | 5.2.8   | CPU Collision Detection Simulation                          | . 115 |

|   | 5.3 | Exper   | imental Results                                             | . 115 |

|   |     | 5.3.1   | Performance and Energy Consumption Benefits                 | . 116 |

|   |     | 5.3.2   | GPU Overheads                                               | . 118 |

|   |     | 5.3.3   | Sensitivity to ZEB List Length                              | . 122 |

|   | 5.4 | Conclu  | usions                                                      | . 123 |

| 6 | Con | clusio  | ns                                                          | 125   |

|   | 6.1 | Conc    | lusions                                                     | . 125 |

|   | 6.2 | Future  | e Work                                                      | . 128 |

|   |     |         |                                                             |       |

### CONTENTS

| Α | Visi | bility | Rendering Order on IMR GPUs            | - | 133 |

|---|------|--------|----------------------------------------|---|-----|

|   | A.1  | Immed  | diate Visibility Rendering Order       |   | 133 |

|   |      | A.1.1  | Visibility Rendering Order Adjustments |   | 135 |

|   |      | A.1.2  | Visibility Rendering Order IMR GPU     |   | 136 |

|   | A.2  | Experi | imental Framework                      |   | 137 |

|   | A.3  | IMR-V  | VRO Results                            |   | 137 |

|   |      | A.3.1  | Software Z-Prepass                     |   | 142 |

|   | A.4  | Conclu | usions                                 |   | 146 |

## List of Tables

| 3.1 | CPU Simulation Parameters                                                                                  |

|-----|------------------------------------------------------------------------------------------------------------|

| 3.2 | Benchmarks Set                                                                                             |

| 3.3 | Geometry Stage Stats                                                                                       |

| 3.4 | Rasterization Stage Stats                                                                                  |

| 4.1 | VRO alternatives                                                                                           |

| 4.2 | GPU Simulation Parameters                                                                                  |

| 5.1 | CPU/GPU Simulation Parameters                                                                              |

| 5.2 | Benchmarks                                                                                                 |

| 5.3 | Percentage of fragment overflow for a ZEB with 4, 8 or 16 entries (each entry holds data for one fragment) |

| A.1 | Benchmarks                                                                                                 |

| A.2 | GPU Simulation Parameters                                                                                  |

# List of Figures

| 1.1 | Millions of units of smartphones and PCs shipped. Source: Gartner [5, 7, 9, 14]. *<br>Projected data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 26 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Monthly OS Market Share from June 2012 to June 2017. Data provided by Statcounter Global Stats [19].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27 |

| 1.3 | Mobile Graphics Hardware Market Share. Data provided by Unity, March 2017 [11].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29 |

| 1.4 | Battery Capacity of Samsung Galaxy S smartphone series                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31 |

| 1.5 | Total Power Consumption, GPU load and CPU load of a mobile device. Measurements made with Trepn Power Profiler [35, 33], with special features for Snapdragon SoCs. The phone employed in the two tests is a Samsung Galaxy J5, equipped with a 720x1280 (5") Super AMOLED display (294 ppi) and powered by a 28nm Qualcomm Snapdragon 410 MSM8916 SoC [34], which includes a 64 bit quad-core 1.2 GHz Cortex-A53 CPU and an Adreno 306 GPU. Both tests were done with screen brightness set to the minimum and WiFi disabled (cellular data enabled).                                                                                                                                       | 32 |

| 1.6 | GPU energy breakdown and main memory BW breakdown of a mobile TBR GPU.<br>Numbers obtained with the set of benchmarks introduced in Section 3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34 |

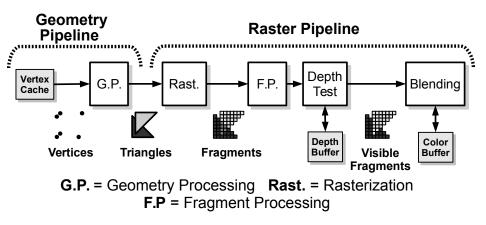

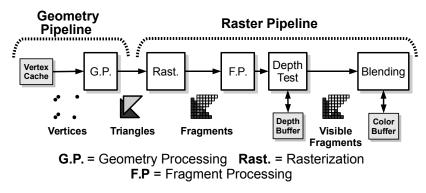

| 1.7 | Simplified version of the Graphics Pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42 |

| 2.1 | Conceptual stages of the Graphics Rendering Pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 |

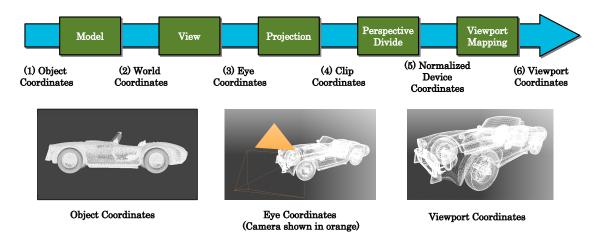

| 2.2 | Vertex-level transformations in the Graphics Rendering Pipeline. (1) The vertices of<br>the 3d model are in Object Coordinates. (2) The vertices are scaled, rotated and<br>translated to World Coordinates. (3) The vertices are positioned in the camera scope<br>transforming them to Eye Coordinates (see detail of camera in orange outline). (4)<br>The vertices transformed to Clip Coordinates by projecting them onto the near clip<br>plane. (5) Perspective correction is applied to transform vertices to Normalized Device<br>Coordinates. (6) Viewport transform is applied to translate vertices to Viewport<br>Coordinates. Car 3D model courtesy of Alexander Bruckner [24] | 51 |

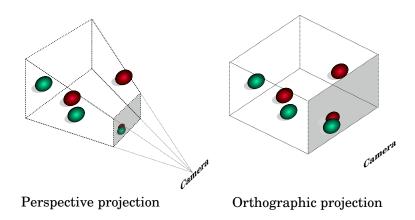

| 2.3 | Perspective (left) and orthographic (right) viewing volumes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52 |

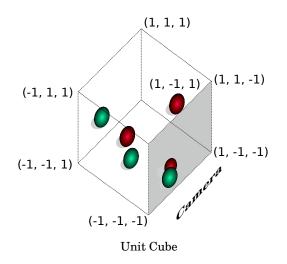

| 2.4 | OpenGL normalized viewing volume.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52 |

### LIST OF FIGURES

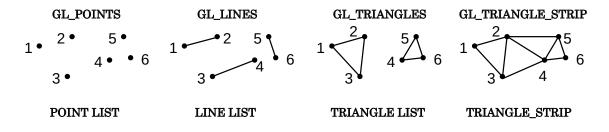

| 2.5  | Examples of common topologies used both by OpenGL and DirectX [167]                                                                                                                                                          | 53 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.6  | View-frustum including viewport.                                                                                                                                                                                             | 54 |

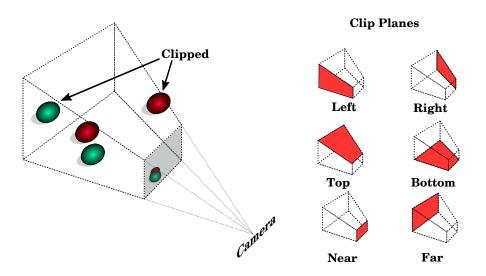

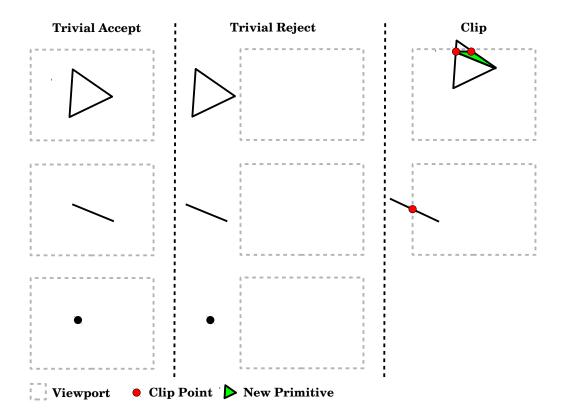

| 2.7  | Clipping cases for triangles (top), lines (middle) and points (bottom).                                                                                                                                                      | 54 |

| 2.8  | Clock wise and counter-clock wise winding triangles.                                                                                                                                                                         | 55 |

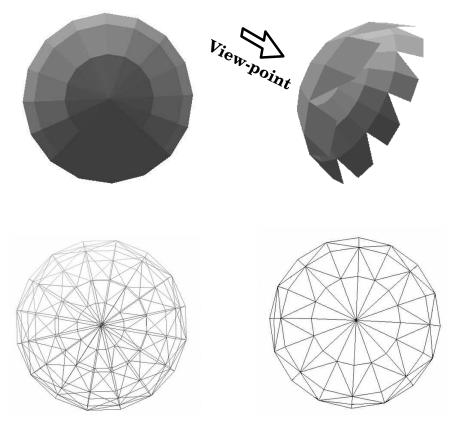

| 2.9  | 3D model of a sphere (top-left), detail showing the effect of face culling (top-right), wire-frame view of the sphere without face culling (bottom-left), wire-frame of the sphere with face culling enabled (bottom-right). | 56 |

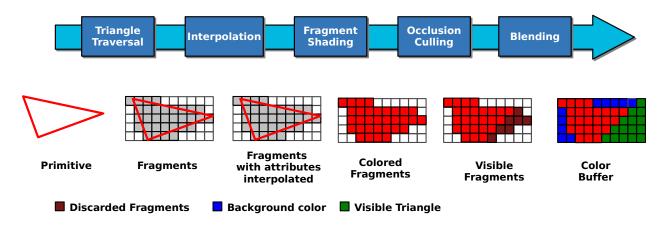

| 2.10 | Sub-stages of the Rasterization stage of the Graphics Pipeline. In this example, a red triangle is rasterized over a blue background, and some fragments of the red triangle are occluded by a green triangle.               | 56 |

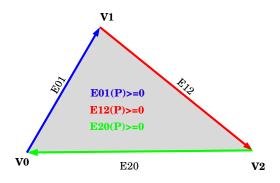

| 2.11 | Edge functions (E01, E12 and E20) of a primitive defined by vertices v0, v1 and v2.                                                                                                                                          | 57 |

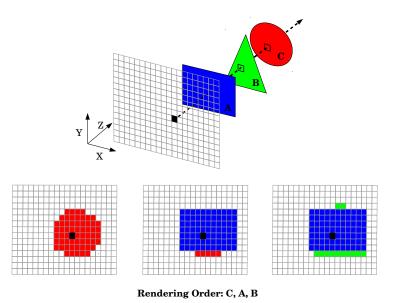

| 2.12 | Detail of scene where three objects A, B and C are rendered in C, A, B order. The image depicts the fragments of every object that pass the Depth Test.                                                                      | 58 |

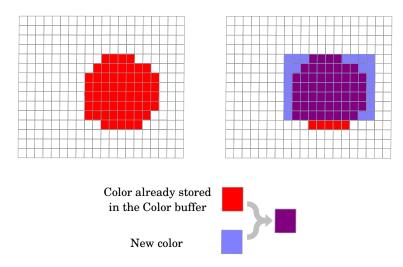

| 2.13 | Detail of scene where two objects are blended. The image depicts how the fragments<br>of a translucent object are blended with the colors already stored in the Color buffer<br>providing a transparency effect.             | 59 |

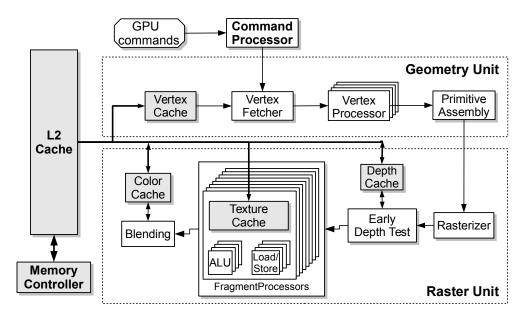

| 2.14 | Microarchitecture of an IMR GPU                                                                                                                                                                                              | 60 |

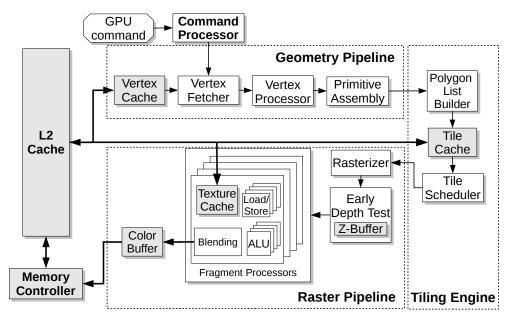

| 2.15 | Microarchitecture of a TBR GPU.                                                                                                                                                                                              | 61 |

| 2.16 | Microarchitecture of a TBR GPU implementing Deferred Rendering                                                                                                                                                               | 62 |

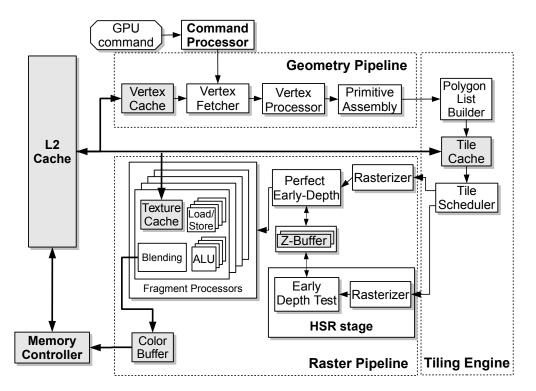

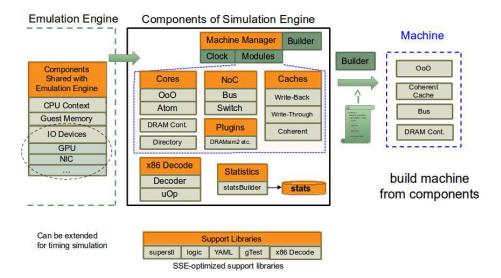

| 3.1  | Overview of Teapot simulation infrastructure.                                                                                                                                                                                | 64 |

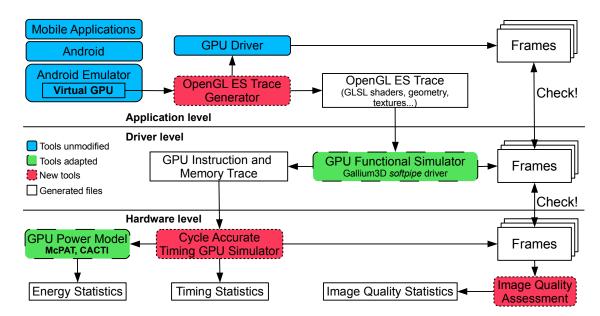

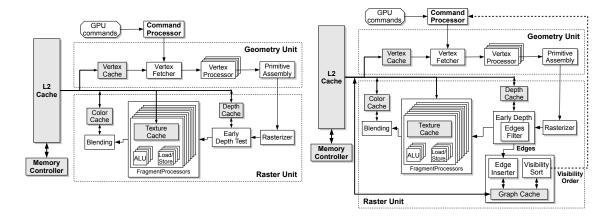

| 3.2  | NVIDIA Tegra like architecture (left), Mali 400 MP like architecture (right). Images from teapot paper [111].                                                                                                                | 66 |

| 3.3  | Overview of Marss components. Source: www.marss86.org                                                                                                                                                                        | 68 |

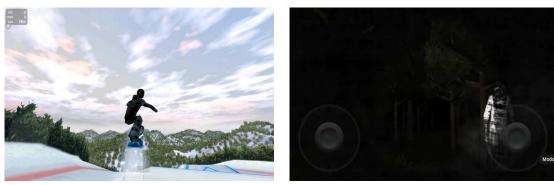

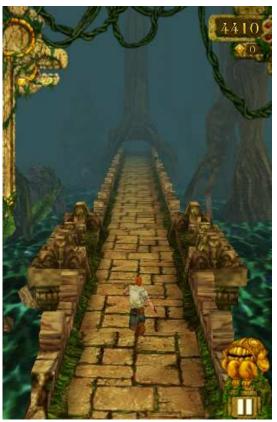

| 3.3  | This figure shows a screenshot for each of the Android games included in our set of benchmarks.                                                                                                                              | 71 |

| 4.1  | Simplified version of the Graphics Pipeline.                                                                                                                                                                                 | 78 |

| 4.2  | Shaded fragments per pixel in a GPU without Early-depth test, with Early-depth test and with perfect front-to-back rendering order at object granularity.                                                                    | 78 |

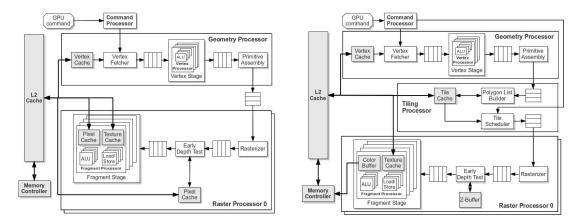

| 4.3  | Graphics pipeline: (a) Sequential DR. (b) Parallel DR                                                                                                                                                                        | 81 |

| 4.4  | Graphics pipeline including VRO                                                                                                                                                                                              | 82 |

### LIST OF FIGURES

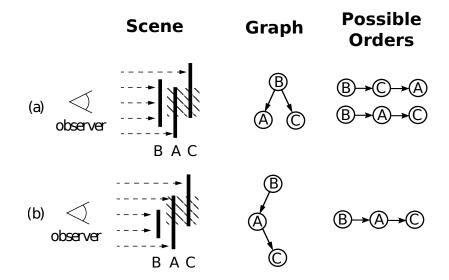

| 4.5  | Visibility Graph generation for the given scene.                                                                                                                                                                                           | 83  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

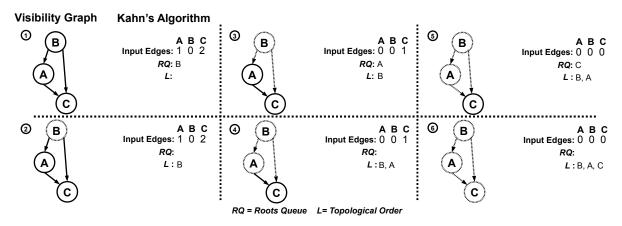

| 4.6  | Sorting a Visibility Graph with the Kahn's algorithm.                                                                                                                                                                                      | 83  |

| 4.7  | Two example cases where object $B$ sits in front of $A$ and $C$ . The shaded region highlights the overlap between $A$ and $C$ .                                                                                                           | 87  |

| 4.8  | Raster Pipeline of a TBR GPU implementing Deferred Rendering.                                                                                                                                                                              | 89  |

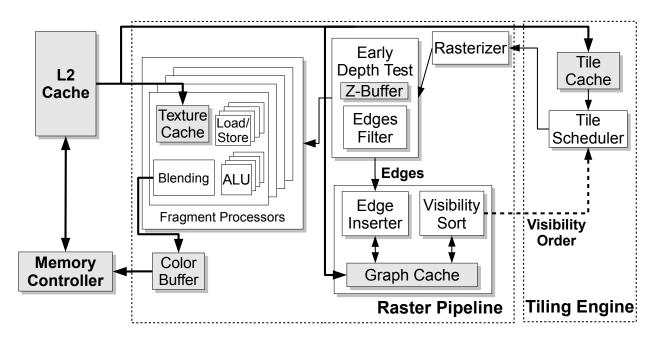

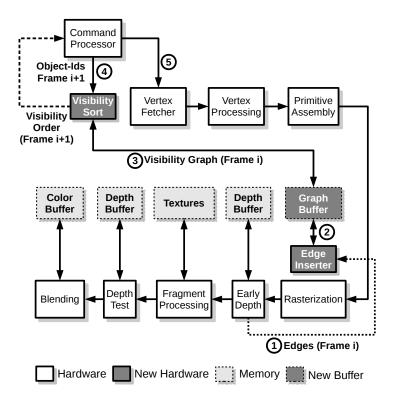

| 4.9  | Raster Pipeline of a TBR GPU implementing VRO.                                                                                                                                                                                             | 90  |

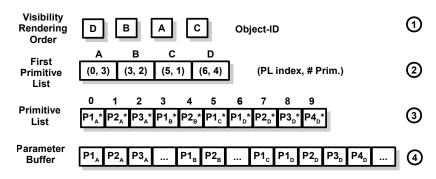

| 4.10 | Detail of Tile Engine structures involved in Geometry Fetching                                                                                                                                                                             | 91  |

| 4.11 | Detail of an entry of the Graph Buffer. Each entry is 512 bits (including 11 bits of padding).                                                                                                                                             | 92  |

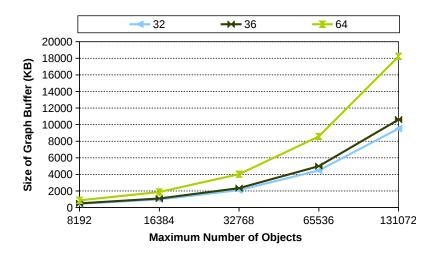

| 4.12 | Size of the Graph Buffer for different number of children nodes (W) and different number of maximum objects (from 8192 to 131072).                                                                                                         | 93  |

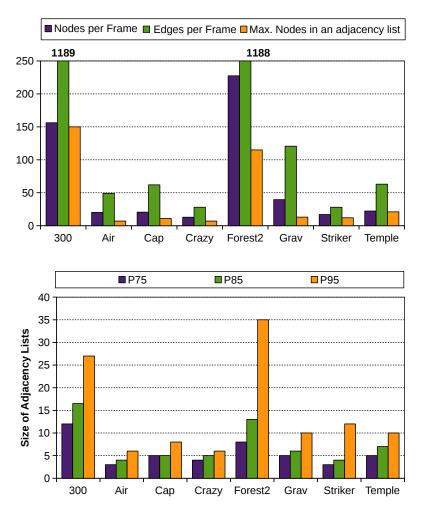

| 4.13 | (Top) Nodes per frame, edges per frame and maximum number of nodes in an adjacency list. (Bottom) 75th, 85th and 95th percentiles of the size of the adjacency-lists of the scene graphs analyzed.                                         | 94  |

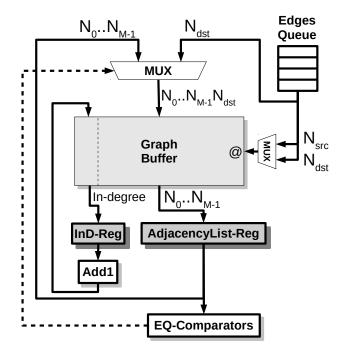

| 4.14 | Edge Insertion Hardware.                                                                                                                                                                                                                   | 95  |

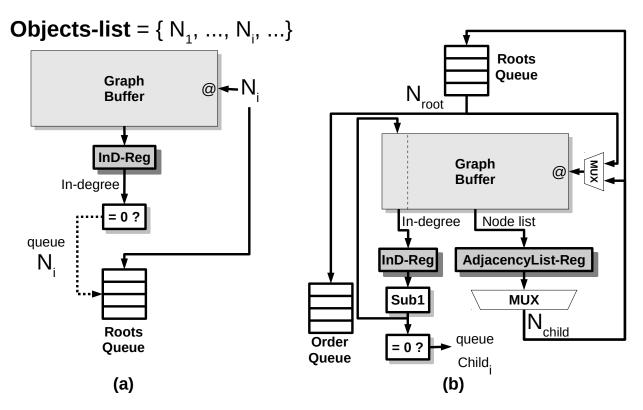

| 4.15 | Visibility Sort Hardware. (a) Initial search (b) Iterative procedure                                                                                                                                                                       | 95  |

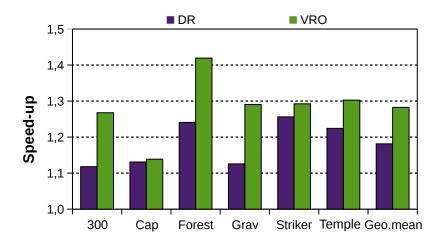

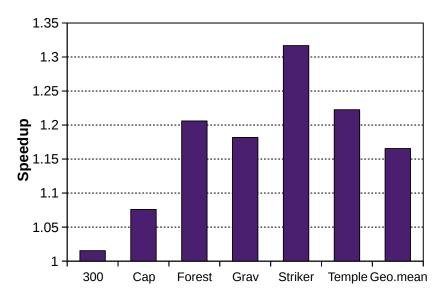

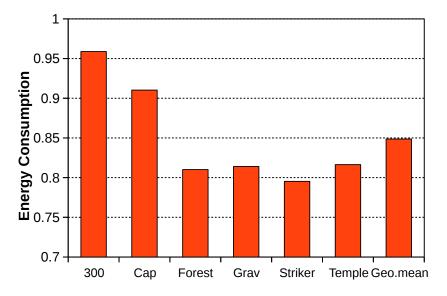

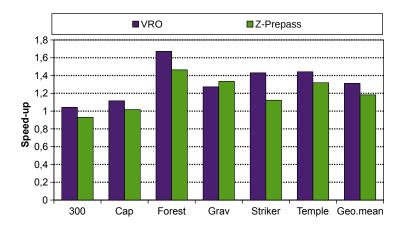

| 4.16 | Speed-up of DR and VRO normalized to the baseline TBR GPU                                                                                                                                                                                  | 99  |

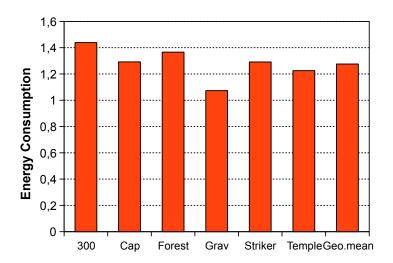

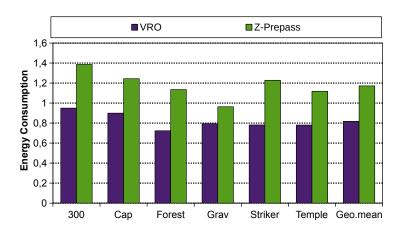

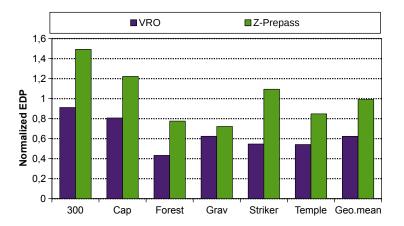

| 4.17 | Energy consumption of DR and VRO normalized to the baseline TBR GPU                                                                                                                                                                        | 99  |

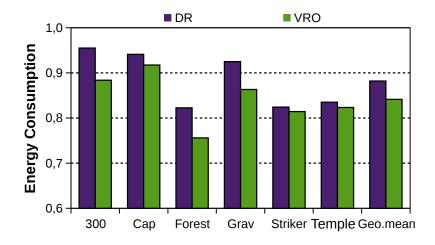

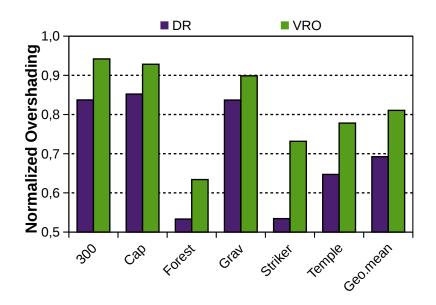

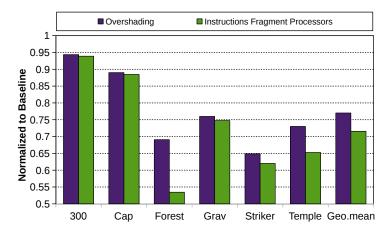

| 4.18 | Overshading of DR and VRO normalized to the overshading of the baseline TBR GPU.1                                                                                                                                                          | 00  |

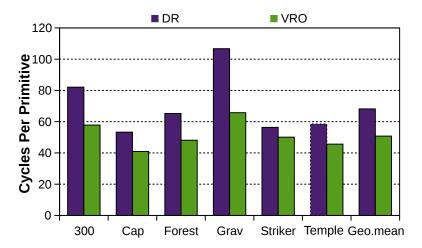

| 4.19 | Number of cycles to read a primitive with DR and VRO                                                                                                                                                                                       | .01 |

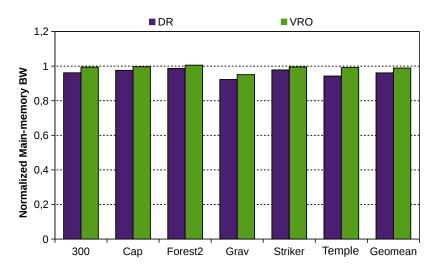

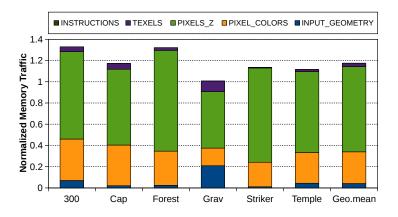

| 4.20 | Normalized memory traffic of DR and VRO with respect to baseline GPU 1                                                                                                                                                                     | .01 |

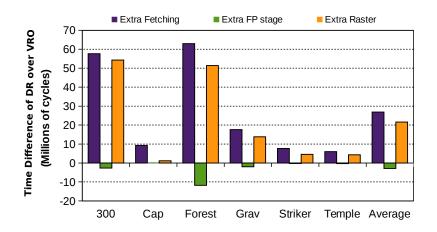

| 4.21 | Increment of cycles reading geometry (first bar), increment of stall cycles caused by the Fragment Processing stage (second bar), and increment of cycles of execution of the Raster Pipeline (third bar) all using DR with respect to VRO | .02 |

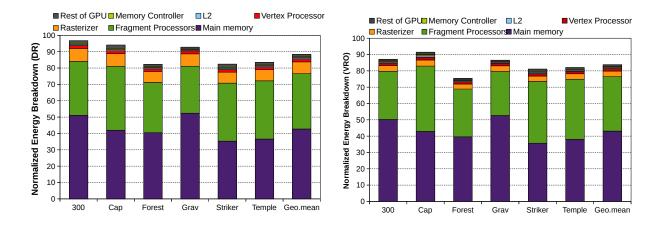

| 4.22 | Energy breakdown for the system Main-Memory/GPU with DR (left) and VRO (right) both normalized to the baseline GPU.                                                                                                                        | .03 |

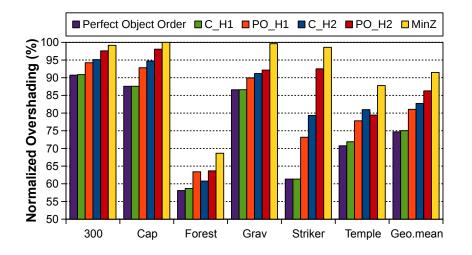

| 4.23 | Normalized Overshading with different Heuristics to break Graph Cycles 1                                                                                                                                                                   | 04  |

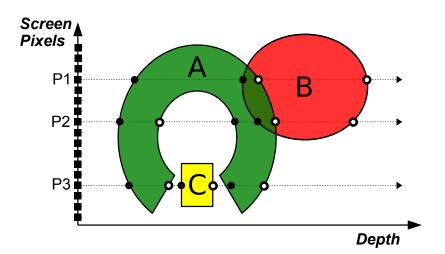

| 5.1  | Discretized representation of the entry and the exit points of the surfaces in a 3D scene for pixels P1, P2 and P3. The Y-axis is a one-dimensional representation of the projection plane and the Z-axis represents depth                 | .07 |

### LIST OF FIGURES

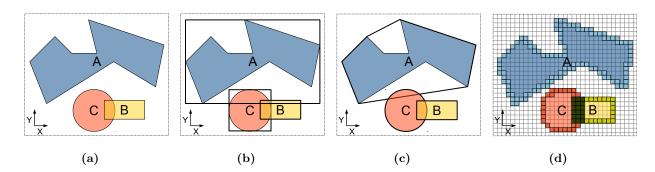

| 5.2  | (a) Front view of a 3D scene (b) AABBs as collisionable shapes (c) Convex hull for GJK algorithm (d) RBCD                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

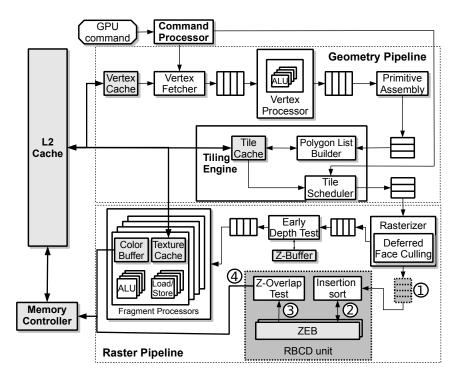

| 5.3  | GPU microarchitecture including an RBCD unit                                                                                                                                                                          |

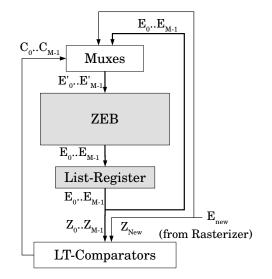

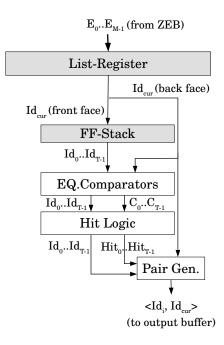

| 5.4  | Sorted insertion hardware                                                                                                                                                                                             |

| 5.5  | Interference cases between front-faces ([) and back-faces (]) of two objects, A and B. 113                                                                                                                            |

| 5.6  | Z-overlap Test hardware                                                                                                                                                                                               |

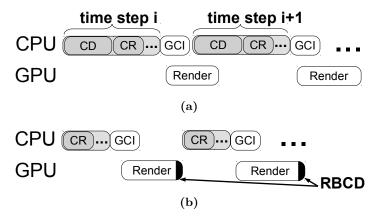

| 5.7  | Example of game loop execution in the CPU/GPU system, (a)without RBCD, (b)with RBCD. CR and GCI stand for Collision Response and GPU Command Issue respectively.114                                                   |

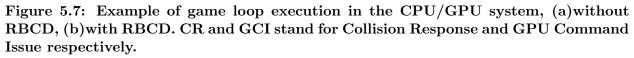

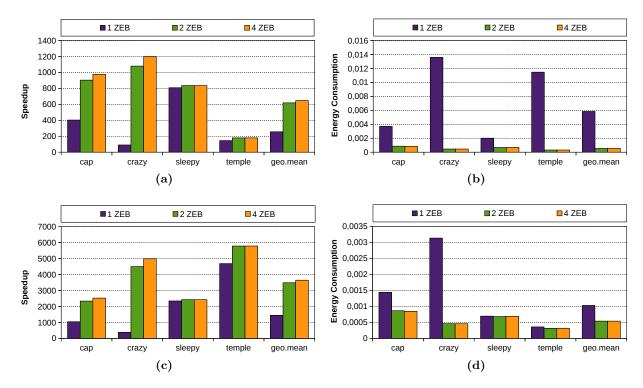

| 5.8  | (a) RBCD speedup regarding Broad-CD, (b) Normalized energy consumption of RBCD regarding broad-CD, (c) RBCD speedup regarding GJK-CD, (d) Normalized energy consumption of RBCD regarding GJK-CD                      |

| 5.9  | (a) Normalized rendering time of the GPU with RBCD w.r.t. the baseline GPU. (b) Normalized energy of the GPU and main memory with RBCD w.r.t. the baseline GPU.119                                                    |

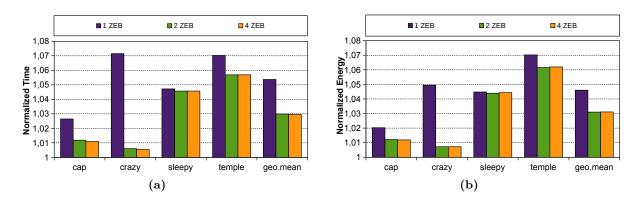

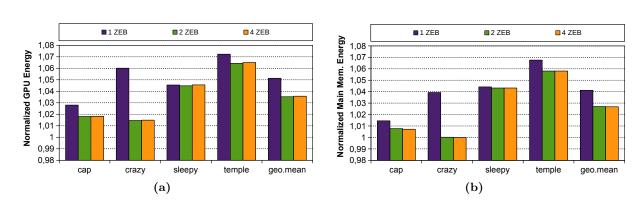

| 5.10 | <ul> <li>(a) Normalized energy consumption of the GPU with RBCD w.r.t the baseline GPU.</li> <li>(b) Normalized main memory energy of RBCD w.r.t. the main memory energy of the baseline GPU.</li> <li>120</li> </ul> |

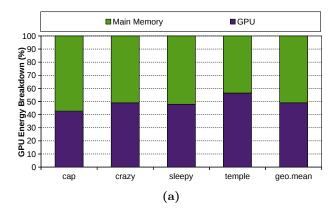

| 5.11 | Energy GPU/Main memory breakdown                                                                                                                                                                                      |

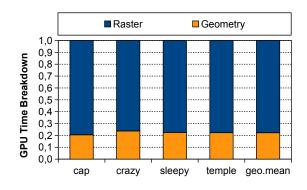

| 5.12 | GPU time breakdown including time of Geometry and Raster pipelines                                                                                                                                                    |

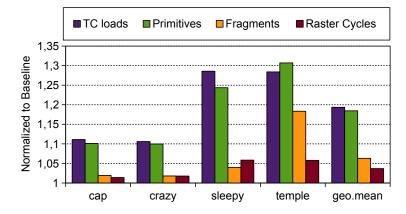

| 5.13 | Tile Cache loads, primitives, fragments, and Raster Cycles with the GPU including RBCD normalized to the GPU baseline                                                                                                 |

| 6.1  | Simplified version of the Graphics Pipeline                                                                                                                                                                           |

| A.1  | Memory bandwidth usage on a mobile GPU for a set of commercial Android games.<br>On average 98.5% of the bandwidth to main memory is caused by operations performed<br>after rasterization                            |

| A.2  | Graphics pipeline including VRO                                                                                                                                                                                       |

| A.3  | Baseline IMR GPU architecture (left) and IMR GPU architecture including VRO (right)                                                                                                                                   |

| A.4  | Speed-up of IMR-VRO normalized to the baseline IMR GPU                                                                                                                                                                |

| A.5  | Energy consumption of IMR-VRO normalized to the baseline IMR GPU 139                                                                                                                                                  |

| A.6  | Energy breakdown of IMR-VRO normalized to the baseline IMR GPU 140                                                                                                                                                    |

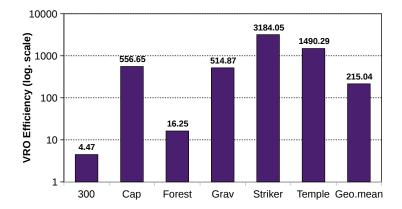

| A.7  | Overshading and Instructions Executed in the Fragment Processors with IMR-VRO normalized to those of the baseline IMR GPU                                                                       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.8  | Ratio between the time savings and the time overhead of VRO (higher is better) 141                                                                                                              |

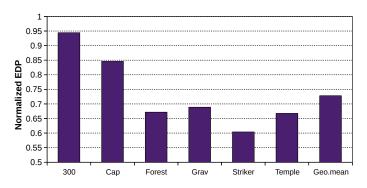

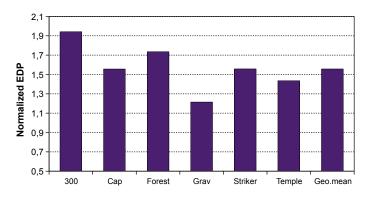

| A.9  | Energy Delay Product of IMR-VRO normalized to the baseline IMR GPU (lower than 1 is better)                                                                                                     |

| A.10 | Memory bandwidth usage of IMR-VRO normalized to baseline IMR GPU 141                                                                                                                            |

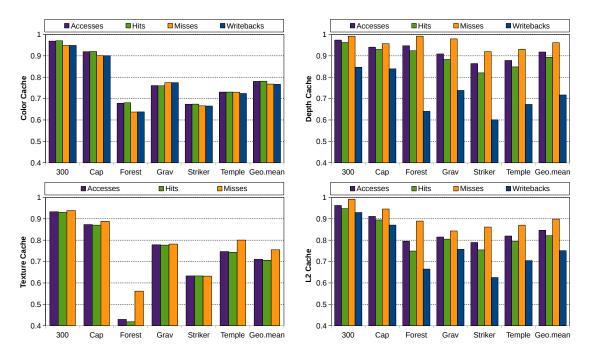

| A.11 | Activity factors with IMR VRO normalized with those of the baseline IMR GPU for<br>Color cache (top left), Depth cache (top right), Texture Caches (bottom left) and L2<br>cache (bottom right) |

| A.12 | Simplified version of the Graphics Pipeline executing Z-Prepass                                                                                                                                 |

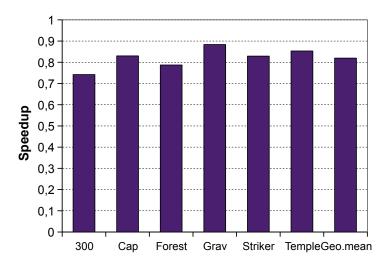

| A.13 | Speed-up of Z pre-pass normalized to the baseline IMR GPU                                                                                                                                       |

| A.14 | Energy consumption of Z pre-pass normalized to the baseline IMR GPU 144                                                                                                                         |

| A.15 | Energy Delay Product of Z pre-pass normalized to the baseline IMR GPU (lower than 1 is better)                                                                                                  |

| A.16 | Memory bandwidth usage of Z pre-pass normalized to baseline IMR GPU 144                                                                                                                         |

| A.17 | Speed-up of VRO and Z pre-pass normalized to the baseline IMR GPU (one FP in all cases)                                                                                                         |

| A.18 | Energy consumption of VRO and Z pre-pass normalized to the baseline IMR GPU (one FP in all cases)                                                                                               |

| A.19 | Energy Delay Product of VRO and Z pre-pass normalized to the baseline IMR GPU (lower than 1 is better, one FP in all cases)                                                                     |

|      |                                                                                                                                                                                                 |

# Introduction

This chapter introduces the main issues in the architectural design of mobile GPUs and how they have evolved over the years. Then, we present the specific problems we approach in this thesis, how these problems have been addressed by other authors and, finally, our proposals to solve them.

### 1.1 Current Trends

In recent years, mobile devices have become powerful and ubiquitous computational engines. They have quickly incorporated graphics and animation capabilities that in the 1980s were only seen in industrial flight simulators and a decade later became popular in desktop computers and game consoles. At each new generation, the growing computing power of mobile devices has promoted the adoption of more powerful support for graphics and real-time physics simulations in all mobile devices, with increasing precision and realism, which does not seem to slow down in the near future. Furthermore, with the rise of Mobile Augmented Reality and Mobile Virtual Reality applications it is expected that the consumers will keep demanding an increasing degree of realism in interactive rendering of images and at higher rendering resolution.

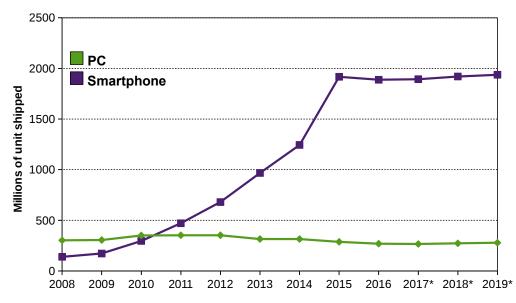

Nowadays, among other uses, we can surf the Internet at high speed, play 3D games, reproduce and record HD video and take high resolution photographs. The evolution of the mobile device from being just a device to make and receive voice calls to being a multimedia and multitasking device, has led the phone to surpass computers for the leisure time we expend in multimedia. As Figure 1.1 shows, sales of mobile devices have dramatically increased from being around 0.97 billion units in 2013, to pass 1.2 billion units in 2014 and reach more than 1.9 billion units in 2015. In 2016 the number of unit shipped decreased, but it is expected to grow in following years. At the same time, the number of downloaded applications was estimated to be above 100 billion in 2013 and it

### CHAPTER 1. INTRODUCTION

is expected to reach around 268 billion in 2017 [3]. Furthermore, the rise of Internet-of-Things and the introduction of Virtual and Augmented Reality may further increase this tremendous growth rate in the near future.

Figure 1.1: Millions of units of smartphones and PCs shipped. Source: Gartner [5, 7, 9, 14]. \* Projected data.

### 1.1.1 Real Time Mobile Graphics Software

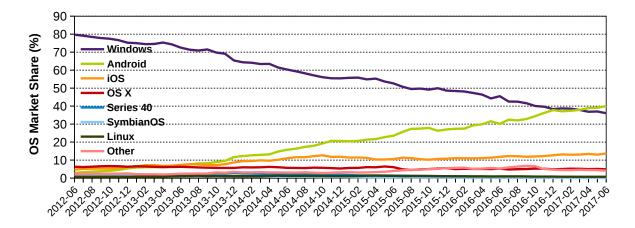

In this section we briefly review the software stack of mobile devices including Operating Systems, applications, Game Engines, Physics Simulation and graphics APIs. The Operating System (OS) is the software that provides services to the applications in current mobile devices. The OS allows to access the rich variety of hardware available in the system, like the screen, the microphone, the speakers, the accelerometer, the GPS, the camera, or the GPU. Note that in current OSs, even the user interface uses GPU acceleration. Android [10] and iOS [12] are the Mobile OSs that have become prevalent with around 72% and 20% of the Mobile OS market share. Moreover, as Figure 1.2 shows, since April 2017 the OS market share of Android (39%) is even bigger than the market share of Windows (37%).

Android is an open source software stack based on Linux, which is meant to work on a great variety of devices (tablets, smart watches, televisions, even phones) from multiple vendors (Samsung, Google, LG, Huaweii, Sony, BQ, etc). Android provides numerous layouts that allow the programmer to add different pre-compiled objects in order to create an interface that provides a rich user experience. However, the developer is responsible for adequately employing Android's resources to deliver applications that provide a flexible user interface to be compatible with different devices.

Regarding applications, there is a plethora of mobile applications available on on-line stores like Google Play Store [44] and Apple App Store [51], being 3D and 2D graphics animation applications the most popular ones [15, 13]. To develop such applications it is common to employ a game engine,

Figure 1.2: Monthly OS Market Share from June 2012 to June 2017. Data provided by Statcounter Global Stats [19].

a SDK that usually includes functionality for graphics rendering, physics simulation, animation, artificial intelligence and sound, among others. Some of the most popular game engines are Unity [21] and Unreal Engine [22], and both of them offer an optimized solution for mobile devices that allows to create 2D and 3D mobile games for iOS and Android.

Regarding physics simulation, the physics engine is the software responsible for providing realistic physical behavior to the objects in a scene, whose velocity and direction must be affected by collisions with other objects and by gravity and other forces. Bullet [129] stands out as an open source framework which simulates collision detection and collision response between objects. Bullet can be used in the Unreal Engine, even though it includes its own physics simulation solution (Physics Assets Tool). Likewise, Unity supplies its own 2D and 3D physics engine as well as a plugin to use Bullet.

Regarding graphics rendering, the game engine offers a rendering method that handles the rendering of a given scene, being an intermediary between the application and the graphics API. The graphics API provides a low-level yet abstract way to access the specific graphics hardware accelerator included in the device. On desktop, the most common real time 3D graphics APIs are OpenGL and DirectX from the Khronos Group [52] and Microsoft respectively [42]. On the mobile side, both iOS and Android include native support for embedded graphics acceleration through OpenGL ES [57], which is a cross-language and multi-platform API that has gone through several versions since its first specification was released in July 2003. Although OpenGL ES 1.0 (based on OpenGL 1.3) is mostly meant to enable software renderers, it also enables basic hardware acceleration. Following versions enable advanced hardware acceleration in order to increase performance and reduce memory bandwidth to save energy. OpenGL ES 1.1 [16] (based on OpenGL 1.5), is meant for fixed-function hardware renderers (configurable but not programmable), and versions 2.X and 3.X enable full programmable 3D graphics by replacing most fixed-function rendering pipeline stages by programmable versions [58, 17].

#### 1.1.2 Mobile Graphics Hardware

Current mobile devices employ SoCs, which are heterogeneous computing systems where the key to enable a low-power yet rich experience is to utilize the right accelerator for every task. The leading industry vendors of SoCs for mobile devices have already integrated new custom designed accelerators such as: Digital Signal Processors; Display, Connectivity and Security controllers; Image Signal Processors (camera support); Video Encoder/Decoders; and, of course, the GPU. In order to further improve energy efficiency, some vendors have already included special cores even into the GPU, like the 2D graphics composition cores [68, 23]. These special hardware accelerators either replace a software implementation that was previously executed in the general purpose hardware CPUs, or expand the capabilities of the SoC. In this section we briefly review the evolution of the main components of the graphics system of a mobile device: the resolution of the display technology and the graphics acceleration hardware.

Regarding the display technology, we have seen an impressive increment in the display resolution as well as the color depth [8]. Back in 2004 the first licensed OpenGL ES 1.0 device, the Imageon 2300 of ATI Technologies, offered 320 x 240 display resolution and 16 bpp of color depth. Today, resolutions of 1920 x 1080 (Full HD) and 32 bpp are quite common and available in devices like iPhone 7 Plus and Samsung Galaxy S5. Other devices like Samsung Galaxy S7 increase the display resolution to 2560 x 1440 (QHD) in 5.1 inches, while Samsung Galaxy S8 goes up to 2960 x 1440 (QHD+) native resolution in 5.8 inches. Regarding mid-end devices, the most common resolution is 1280 x 720 (HD Ready).

At the same time that the screen resolution has increased, the mobile graphics rendering has significantly evolved from being responsible for creating simple text user interfaces mostly implemented in software and executed in the CPU, to creating complex 2D/3D graphics animations that employ a graphics hardware accelerator, the Graphics Processing Unit (GPU). In fact, in many cases the early mobile devices had only hardware support for integer arithmetic [59]. However, with the gradual adoption of higher screen resolutions and the necessity to render high-quality images the graphics system was required to provide higher fill-rates, and subsequently GPUs became an essential requirement.

The Khronos Group consortium maintains a list of products conformant with the different OpenGL ES specifications [18]. According to this list, the first mobile GPUs to support OpenGL ES 1.1 were the Mali-110/Mali-55 [1] in 2005. They were fixed-function hardware pipelines (configurable but non-programmable) for rasterization and Fragment Processing, offering fill rates in the order of 100 Mpix/sec [89]. Although the Geometry Processing might still be performed by software running on the CPU, an optional MaliGP (Geometry Processor) processor could also be added to offload the CPU of the Geometry Processing and enable 3D applications to run faster [190].

The first mobile GPUs to support OpenGL ES 2.0 arrived in 2008 and were PowerVR SGX530 and Mali200, offering fill rates in the order of 200 Mpix/sec [53, 60]. OpenGL ES 2.0 replaced some fixed-function hardware stages of the pipeline by programmable stages with the ability to execute vertex and fragment shader programs written in OpenGL ES Shading Language, to improve energy efficiency. The first mobile GPU to officially support OpenGL ES 3.0 was the Adreno 320 [37] presented in 2013 in the Snapdragon 600 SoC of Qualcomm [67], with a reported fill rate of 1.6 Gpix/sec and able to process 225 Mtri/sec. Following specifications of OpenGL made a big step

towards programmability. Compute Shaders were added in OpenGL ES 3.1, while Geometry and Tessellation Shaders were presented in OpenGL ES 3.2. The former allows to perform computation not directly related to drawing triangles and fragments, while the latter allows to efficiently process complex scenes on the GPU by means of giving the programmer the opportunity to create new geometry not presented in the input stream of vertices. The first GPU to support OpenGL ES 3.1 is the Qualcomm Adreno 510 in 2016. The first GPU to comply with OpenGL ES 3.2 is the ARM Mali-G71 also in 2016 with a fill rate around 1850 Mtri/sec and 27.2 Gpix/sec.

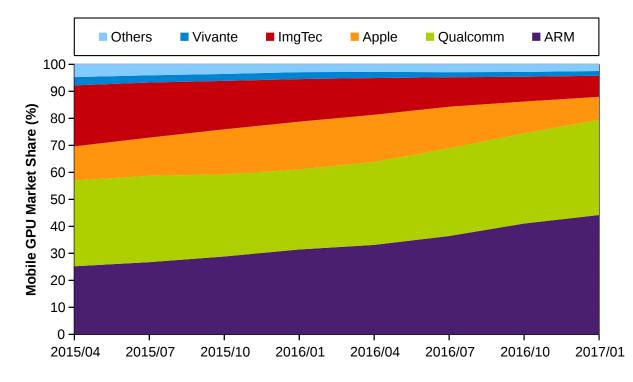

Regarding the current state of the market of Mobile Graphics Hardware (see Figure 1.3), it is worth mentioning that it is not dominated by a single vendor. However, ARM and Qualcomm are clearly ahead of the other ones hoarding 44% and 35% of the market share respectively, followed by the duo formed by Apple and Imagination Technologies with more than 16% of the market (8.5% and 7.8% respectively). The list is closed by Vivante (1.8%), Broadcomm (0.9%), NVIDIA(0.6%) and Intel(0.5%).

Figure 1.3: Mobile Graphics Hardware Market Share. Data provided by Unity, March 2017 [11].

ARM licenses the Mali family of GPUs, with three main lines of GPUs: Ultra-low power (Mali 400 series), high area efficiency (Mali 720) and high performance (Mali G71, T860/880) [55]. The Mali 400 MP [54] is the most deployed Mali GPU with around 19% of the market. It includes OpenGL ES 1.1/2.0 support and is able to process 55 Mtri/sec and 2.0 Gpix/sec. The Mali400 MP is a multi-core Tile Based Renderer, i.e., the rendering view-port (screen) is divided into tiles (bins), which are independently rendered tile by tile using on-chip buffers that minimize main memory bandwidth usage. This architecture is explained in more detail in chapter 2. A Mali G71 GPU can be found in popular smartphones like Samsung Galaxy S8 and S8+, powered by the Samsung

Exynos SoC [65, 63].

Adreno is a series of mobile GPUs produced by Qualcomm included in the Snapdragon SoC [38, 69]. Rather than implementing a Tile Based or an Immediate renderer, Adreno GPUs implement both and are able to switch between the two modes at run-time using the FlexRender technology [43]. Adreno GPUs can be found on commercial devices like Samgung Galaxy S5 [64] or HTC One M9 [47].

PowerVR [61] is the solution provided by Imagination Technologies for embedded devices. PowerVR implements a Tile Based Deferred architecture, which implements Hidden Surface Removal at pixel granularity before computing the pixel colors, i.e., it defers the computation of the pixel colors until the visibility for a pixel is determined. This approach decreases the Fragment Processor computations and further reduces main memory bandwidth. PowerVR GPUs can be found in several Mediatek SoCs, like the Helio x10/x30 [45, 46]. Furthermore, PowerVR designs are also included in Apple SoCs like the Apple A8, Apple A9 and Apple A10 [40, 41, 39], which are employed in popular mobile devices like iPhone 6/6 Plus, iPad Pro and iPhone 7/7 Plus [49, 48, 50]. The Playstation Vita of Sony includes a PowerVR SGX543MP4+ GPU [62].

NVIDIA delivers the Tegra SoC [70], which includes an immediate-mode rendering GPU architecture specially designed and tuned for high-performance and power efficiency. Tegra X1 implements a Maxwell GPU architecture with 256 cores, being the most advanced model that NVIDIA provides for mobile devices [71]. It can be found on devices like the Nintendo Switch game console [56] and the NVIDIA SHIELD TV streaming player [66].

Finally, it is worth to mention a vendor whose GPUs are not so widespread but, like the previous companies, it offers high-quality products that achieve similar performance and power consumption. Vivante develops the Vega GPU architecture included in the GC family of processors [23], which counts with more than hundred successful mass market SoC designs. Samsung Galaxy Ace Plus, Huaweii Ascend P6 and Samsung Galaxy Tab 4 are examples of mobile devices powered by Vega [72].

### 1.2 Problem Statement

In this section we first illustrate the importance of energy-efficient designs to improve battery life per charge and performance in mobile devices. Then, in subsections 1.2.1 and 1.2.2 we point out the main sources of energy drain in mobile SoCs for graphics workloads. Finally, in subsections 1.2.3 and 1.2.4 we introduce the two main aspects focused in this thesis.

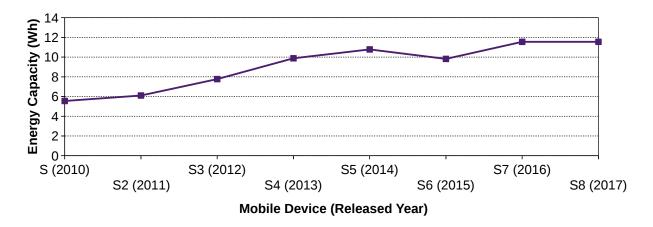

Software and hardware improvements like the ones described in the previous section are crucial to deliver a rich user experience that satisfies the user demands on the functionality of mobile devices. For example, in graphics animation applications the trend is towards supporting more realistic and complex 3D rendering. The direct consequence of supporting these higher computing demands comes with a significant increase in energy consumption. However, the battery capacity does not grow at the same pace as the computing demands, which produces an energy gap that is incremented on each generation [168] and puts pressure on the battery life of mobile devices. It is important to note that for the users of mobile devices the battery life per charge is the third most valued satisfaction factor [32], being critical in the overall satisfaction with the device [31]. Figure 1.4 shows the evolution of the battery capacity of the Samsung Galaxy S family of smartphones. As can be seen, the battery capacity has only been doubled from 2010 to 2017 with an average increment of 11.7% per year. In particular, since 2014 -three generations ago-, the battery capacity of the flagship device of Samsung has only grown slightly above 7%, remaining flat in the last two generations.

Figure 1.4: Battery Capacity of Samsung Galaxy S smartphone series.

Besides battery life per charge, there is another factor that limits energy consumption on current mobile devices. Current mobile devices like smartphones and tablets are extremely thin in order to reduce their weight, as well as make them more attractive and easier to slip into pockets of all sizes. As a direct consequence, these devices cannot be equipped with active cooling mechanisms like fans or conventional and big heat sinks to dissipate heat in order to keep the temperature below the maximum temperature limit of internal components. Moreover, given the handheld nature of these devices, it is critical to keep a comfortable surface touch temperature, otherwise the device may become too hot to handle [195, 102]. In order to avoid overheating above thermal limits, mobile SoCs tend to be throttled when the load is high for a large period of time [178, 85].

### 1.2.1 Major Energy Consumers

Among all the components of the mobile device the GPU and the CPU have been identified by previous works to be the principal energy consumers for common applications [122]. In particular, for graphics applications the GPU has been identified as the principal energy consumer [174]. Further experimental data with the same SoC shows a peak consumption of the GPU 50% higher than the peak consumption of the CPU [30]. We conduct a brief experiment in order to further motivate our work.

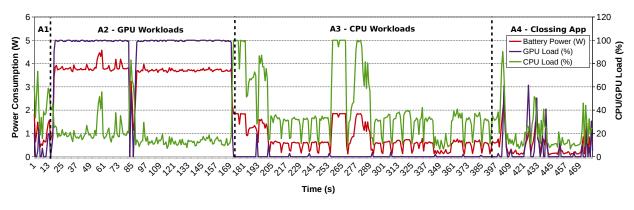

Figure 1.5 shows the total power consumption of a smartphone (left axis) as well as the GPU and the CPU load (right axis) for two different applications: AnTuTu [36]; and Netflix [81] for Android. AnTuTu, with more than 100 M users, is the most popular benchmarking application for mobile devices powered by Android. Netflix is a popular video streaming platform. Let us analyze in detail the results for AnTuTu benchmark. Figure 1.5a shows the results for AnTuTu benchmark.

### **CHAPTER 1. INTRODUCTION**

(a) Full run of AnTuTu [36] benchmark V6.2.7.

(b) Netflix HD video playback using Cellular Data.

Figure 1.5: Total Power Consumption, GPU load and CPU load of a mobile device. Measurements made with Trepn Power Profiler [35, 33], with special features for Snapdragon SoCs. The phone employed in the two tests is a Samsung Galaxy J5, equipped with a 720x1280 (5") Super AMOLED display (294 ppi) and powered by a 28nm Qualcomm Snapdragon 410 MSM8916 SoC [34], which includes a 64 bit quad-core 1.2 GHz Cortex-A53 CPU and an Adreno 306 GPU. Both tests were done with screen brightness set to the minimum and WiFi disabled (cellular data enabled).

The test has been divided into four phases: A1: application startup; A2: GPU workloads; A3: CPU workloads; A4: application end. As can be seen, the peak power consumption (around 4.57 W) is reached when running the graphics workloads (A2 phase). Furthermore, the average power consumption on this phase is around 3.7 W. Note that the power consumption correlates well with the GPU load, which is around 96% on this phase. On GPU workloads phase the CPU load is around 18.9%. Regarding the CPU workloads (A3 phase), the average power consumption is around 0.78 W with an average CPU load of 40%. The average GPU load is smaller than 1% in this phase. Note that even when the CPU load is almost 100% the total power consumption is still below 2 W. These results suggest that the GPU is the principal energy consumer in this mobile device. However, the reader may argue that the figure not only shows the power of the GPU and the CPU, but also the power of all the components of the smartphone such as the screen and the modem, and therefore they could be the principal power consumers in the device. In order to

elucidate the power consumption of the other parts of the device, like the modem and the screen, we have run an additional test playing a streaming video with Netflix (see Figure 1.5b). The span of this figure is split in three different phases: N1: application startup); N2: video playback; N3: application end. When playing the video, the peak energy consumption is right below 1 W, while the average is around 0.36 W. The GPU load is 0%, while the CPU load is around 26% on average, with a maximum of 56%. Note that, like in the previous test, when the GPU is idle (N2) the power consumption is much lower than when the GPU is busy (N3). The GPU load peaks that appear both in A4 and N4 are caused by the activity of the OS, which employs GPU acceleration for desktop transitions and animations. It is clear that the energy consumption of graphics workloads is much greater than the energy consumption of other workloads.

Let us analyze the battery life of a device when running GPU and CPU phases shown above. The Samsung J5 is equipped with a 2600 mAh battery at 3.8 V of nominal voltage, thus its battery capacity is:  $\frac{2600mAh*3.8V}{1000} = 9.88Wh$ . The amount of energy available is: 9.88Wh\*3600s/h = 35568J. As the average power drain is 3.7 W, 0.78 W and 0.36 W for A2 (GPU workloads), A3 (CPU workloads) and N2 (video playback) phases, the corresponding battery life is around 2 hours and 40 minutes, 12 hours and 40 minutes, and 27 hours and 26 minutes respectively. The battery life of the device when running the graphics workloads is heavily reduced being less than three hours, while for the non graphics workloads the battery life is more than ten hours.

Given the huge impact of the graphics workloads and the GPU in the power consumption of mobile devices, the design of energy-efficient techniques for graphics workloads is crucial. Increasing the energy efficiency of the mobile GPU is not only meant to reduce energy consumption but also is an effective way to increase its performance, which makes mobile GPU designers focus on energy-efficient solutions to improve performance per watt rather than raw performance, which is key in making possible the increased computing demands of the users.

### 1.2.2 Major GPU Energy Consumers

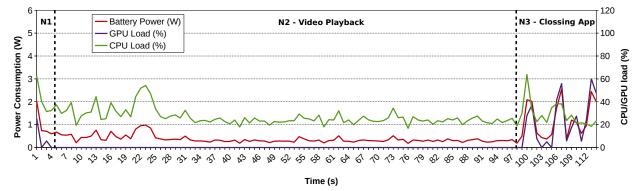

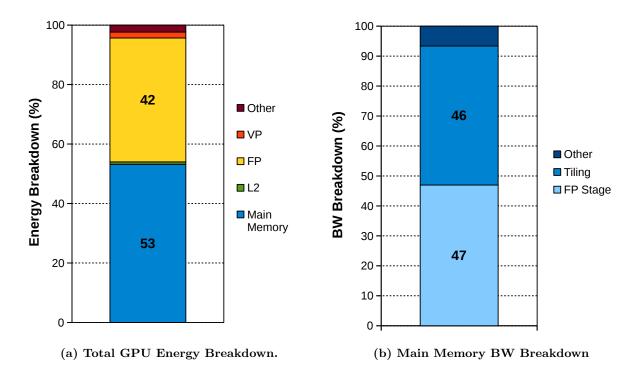

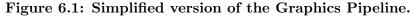

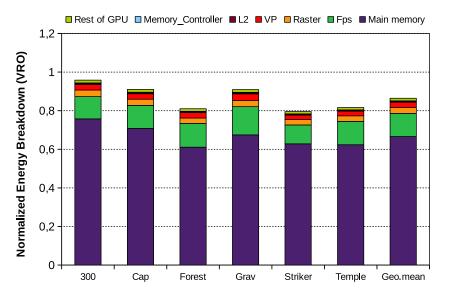

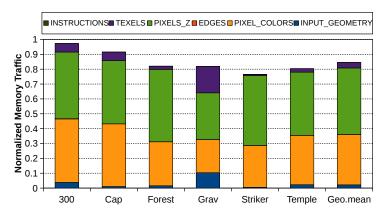

Previous studies pointed out that the principal energy consumers in the graphics subsystem are the off-chip main memory accesses and the processors inside the GPU, in particular the ones devoted to Fragment Processing [102, 105, 165, 177]. The results obtained with our simulation infrastructure are in line with the results of the previous studies. Figure 1.6a shows the power of different structures of the GPU. The principal consumers are the accesses to main memory and the activity of the Fragment Processors (FP) with 53% and 42% of the total energy consumption respectively. The FPs are the main energy consumers mainly due to the fact that in common graphics workloads the number of fragments is usually orders of magnitude higher than the number of vertices. For example, for a rendering resolution of 1280 x 768 the number of instructions executed in the FPs is on average around 94% of the total instructions (numbers obtained with the simulation infrastructure and workloads described in the following chapter). Figure 1.6b shows the main memory BW breakdown originated at different stages of the graphics pipeline. As can be seen, around 47% of the BW with main memory is performed by the FP stage, so a large percentage of the energy consumption of the main memory corresponds to the FP stage.

Given that in our experiments around 53% of the energy breakdown corresponds to main

### **CHAPTER 1. INTRODUCTION**

memory, and due to the fact that around 47% of the traffic is caused by the FP stage, the FP stage consumes around 53% \* 47% = 25% of the total energy performing accesses to the main memory. This 25% along with the 42% of the energy devoted to the FPs (see Figure 1.6a), means that the FP stage is responsible of around 67% of the total energy consumption of the main-memory/GPU system.

Figure 1.6: GPU energy breakdown and main memory BW breakdown of a mobile TBR GPU. Numbers obtained with the set of benchmarks introduced in Section 3.2.

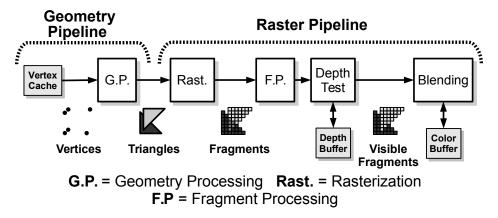

### 1.2.3 Occlusion Culling

During real-time graphics rendering, objects are processed by the GPU in the order they are submitted by the CPU, and occluded surfaces are often processed even though they will end up not being part of the final image. Occlusion culling (aka visibility determination) is an essential process of the graphics rendering pipeline that allows to decide which fragments of a scene are visible and which are not. The most widespread method to resolve visibility at pixel granularity is the Depth Test, which is typically placed at the end of the pipeline. The Depth test compares each fragment's depth against that already stored in the Depth Buffer to determine if the fragment is in front of all previous fragments at the same pixel position. If not, the fragment is discarded. Otherwise, the Depth Buffer is conveniently updated with the new depth, and the color of the fragment is sent to the blending stage, which will accordingly update the Color Buffer (the buffer where the image is stored).

The main advantage of the Depth test is that it ensures correct scene rendering regardless of the order the opaque geometry is submitted by the CPU. The main drawback is that the color of a given pixel may be written more times than necessary (a problem known as overdraw), which wastes a considerable amount of main memory bandwidth and energy [172]. Moreover, when the GPU realizes that an object or part of it is not going to be visible, all activity required to compute its color has already been performed, with the consequent waste of time and energy. Hence, reducing the overshading produced by non-visible fragments can significantly increase the energy-efficiency of the GPU. As we will show, with some adaptations occlusion culling can be employed to reduce redundant fragment shading and therefore increase the energy-efficiency of the GPU.

### 1.2.4 Collision Detection

Collision Detection (CD) is one of the most important algorithms that manage the dynamics of the animations. It identifies the contact points between the objects of a scene and determines when they collide. During the past decade, mobile devices have quickly incorporated graphics and animation capabilities and the trend going forward is towards more powerful support for real-time physics simulations with increasing precision and realism. However, despite high-accurate physics algorithms increase the quality and the realism of the animations, their implementations may be expensive for mobile devices. Furthermore, highly-accurate Collision Detection schemes are control-intensive algorithms [2], known to cause branch divergence in GPGPUs [139] which produces low utilization of the functional units and reduces the performance [147] of the GPU.

### **1.3** State of the art

In this section we introduce techniques that other authors proposed to deal with occlusion culling and collision detection, the principal problems addressed in this thesis.

### 1.3.1 Reduction of Redundant Fragment Shading

Olson [172] studies the effect of overshading in mobile platforms for a set of commercial mobile applications and identifies it as a significant source of wasted energy. Given that the FP stage is the most energy-consuming stage of the graphics rendering pipeline, multiple works aim at reducing the number of instructions executed in the Fragment Processors by means of reducing the number of fragments whose color must be computed to render a frame. Some works make use of visibility determination to achieve some sort of reordering either at geometry or at fragment level granularity. There are other efforts that introduce changes in the GPU microarchitecture in order to reduce the number of fragments executed in the processors. On the other hand, rather than reducing the number of fragments executed in the processors, other studies have focused on improving the energy-efficiency of the GPU in different aspects, like hiding the memory latency or reducing the main memory BW of the GPU [109, 110].

Let us remark some concepts which will help us to better understand this section. When we refer to geometry of a scene we mean vertices and primitives (points, lines, and triangles) formed by those vertices. Such primitives are later discretized in fragments that correspond to pixel positions and whose color is computed in the processors of the GPU. The fragments are usually grouped in 2x2 pixels regions called quad fragments, that represent the unit of execution of the Fragment Processors. All the quad fragments of an object (draw command, drawcall) execute the same program/shader.

### Geometry Level Sorting

Multiple works have analyzed how overshading can be reduced by culling the geometry at primitive level granularity through the use of occlusion queries [118, 187]. When using occlusion queries, the application usually sends a query with a Bounding Volume of the object to the GPU where it is rasterized and depth tested for visibility. Eventually, the result of the query is sent to the driver and if the Bounding Volume was occluded, the application will not send the object to the GPU. Unfortunately, using any kind of feedback from the GPU limits the achievable frame rate unless the scene complexity is above a large threshold [117], which is often not the case on mobile workloads. Moreover, as mobile devices evolve to higher resolutions, testing for occlusion objects that are not fill-rate bound (i.e. with simple fragment programs and textures) may require many more pixels to fill and the GPU will likely spend more time rendering the object's bounding volume than the object itself. Given that at some point the application must know the result of the queries, they may introduce CPU stalls and produce GPU starvation. Furthermore, GPU drivers let the GPU render several frames behind the CPU by actually queuing the rendering commands [130, 92, 90], which exacerbates these problems. One important limitation when using occlusion queries is that it is required to sort the queries of the objects in a front-to-back manner to perform well. Many software approaches require building costly spatial hierarchical data structures to render the scene from any single viewpoint. They are quite effective on walkthrough applications where the entire scene is static and only the viewer moves through it, because the overheads can be amortized along a large number of frames [125].

Govindaraju et al. [141] sort the primitives of every object of a scene in a front-to-back order from a given viewpoint. However, they assume that the objects do not overlap, so the scheme only avoids overshading produced by geometry of the same object (intra-object overshading), and not between different objects (inter-object overshading). Unfortunately, this scheme is not able to handle cycles in the sorting process, which are highly common on dynamic 3D scenes.

Nehab et al. [171] and Sander et al. [185] also propose techniques to reduce intra-object overshading. They propose a pre-processing scheme that sorts the geometry of every object in a scene in a view-independent order that minimizes overshading. They focus on static meshes and produce a single order per mesh. On the other hand, Han et al. [146] propose a technique that is also focused on reducing intra-object overshading but they target animations. They propose a pre-processing scheme that produces a number of view-dependent orders per every object of a scene from different points of view, all of them minimizing the overshading. Then, the application selects at runtime a view-dependent order that minimizes the overshading depending on the orientation of the objects with respect to the camera.

#### Fragment Level Sorting

To reduce overshading, most graphics rendering pipelines perform an "early" visibility determination (Early-depth test) that tests the visibility of fragments before they are sent to the processors. Although the Early-depth can only cull fragments which are hidden by those already tested, it may reduce fragment shading and bring important performance and power benefits.

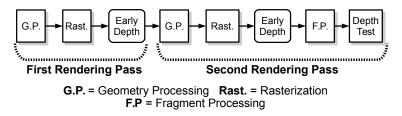

With Z-prepass, Haines et al. [145] address overshading by performing two separate rendering passes with the GPU. First Z-prepass renders the geometry without computing the color of the fragments, just using a null fragment shader in the processors, to determine the visibility of the scene. On a second pass with the real shaders the Early-depth test will perform optimal culling, so overshading will be minimum (just one opaque fragment per pixel will be shaded and written into the Color buffer, the buffer where the rendered image is stored). Unfortunately, this approach doubles several stages of the graphics pipeline like vertex processing, rasterization and visibility determination, which may offset the benefits of the technique. It is only effective for workloads with enough complexity where the overhead of the first rendering pass is compensated by large fragment computation savings, which is not usually the case on mobile applications.