# Ph.D. in Computing

# Structure discovery techniques for circuit design and process model visualization

Javier de San Pedro Martín

Advisor: Jordi Cortadella Fortuny

# **Abstract**

Graphs are one of the most used abstractions in many knowledge fields because of the easy and flexibility by which graphs can represent relationships between objects. The pervasiveness of graphs in many disciplines means that huge amounts of data are available in graph form, allowing many opportunities for the extraction of useful structure from these graphs in order to produce insight into the data.

In this thesis we introduce a series of techniques to resolve well-known challenges in the areas of digital circuit design and process mining. The underlying idea that ties all the approaches together is discovering structures in graphs. We show how many problems of practical importance in these areas can be solved utilizing both common and novel structure mining approaches.

In the area of digital circuit design, this thesis proposes automatically discovering frequent, repetitive structures in a circuit netlist in order to improve the quality of physical planning. These structures can be used during floorplanning to produce regular designs, which are known to be highly efficient and economical. At the same time, detecting these repeating structures can exponentially reduce the total design time.

The second focus of this thesis is in the area of the visualization of process models. Process mining is a recent area of research which centers on studying the behavior of real-life systems and their interactions with the environment. Complicated process models, however, hamper this goal. By discovering the important structures in these models, we propose a series of methods that can derive visualization-friendly process models with minimal loss in accuracy.

In addition, and combining the areas of circuit design and process mining, this thesis opens the area of specification mining in asynchronous circuits. Instead of the usual design flow, which involves synthesizing circuits from specifications, our proposal discovers specifications from implemented circuits. This area allows for many opportunities for verification and re-synthesis of asynchronous circuits.

The proposed methods have been tested using real-life benchmarks, and the quality of the results compared to the state-of-the-art.

# **Acknowledgments**

This thesis would have been impossible without the expertise, guidance, and, sometimes, necessary insistence of my advisor, Prof. Jordi Cortadella. As all his students will attest, including myself, it is quite an opportunity to be able to work with him. I am thus extremely thankful for this opportunity, that has allowed me a firsthand view of both the academic and industrial worlds of Computer-aided design; as well as his ability to make sense even from the most terrible of my explanations.

I would also like to thank every person I have had the pleasure to work with. For the extremely useful guidance during the early days, Nikita Nikitin, Prof. Josep Carmona, and Prof. Jordi Petit. For their insights on Chip multiprocessors and Networks-on-Chip, Francesc Guim, Antoni Roca and Daniel Rivas. For his knowledge on the, for me, novel topic of Process Mining, Jorge Muñoz-Gama. For our discussions on asynchronous circuits and transition systems, Thomas Bourgeat. I hope that I have been as useful to you as you have been to me in, believe me, very stressful times.

And then, I would also like to thank all the people I have not been able to work with, but would have enjoyed to. From my lab colleagues working on similar topics, I would like to thank Alex Vidal, Alberto Moreno, and Lucas Machado. A special gratitude goes to Seppe vanden Broucke, Joos Buijs, and the CoSeLoG, ActiTraC, and 4TU.Datacentrum projects, for providing the benchmarks that have been used to evaluate many of the methods proposed in this thesis. Plus, big thanks to all the excellent people in UPC, including professors, researchers, and administrative staff.

I obviously will not forget about all the support provided by my family, nor from all all the friends made during this experience – Daniel Alonso, Sergi Oliva, Adrià Gascón, Ramón Xuriguera, Josep Lluís Berral, Alberto Gutiérrez, Evelia Lizárraga, Eva Martinez, Carles Creus, Albert Vilamala and M. Àngels Cerveró. Good luck you all in your future endeavors!

This work has been supported by a scolarship from the Catalan Government (FI-DGR 2013).

# **Contents**

| 1 | Intr | oduction                                | 1  |

|---|------|-----------------------------------------|----|

|   | 1.1  | Contributions of this thesis            | 4  |

|   | 1.2  | Structure of this document              | 7  |

| 2 | Prel | iminaries                               | 9  |

|   | 2.1  | Graph mining                            | 9  |

|   | 2.2  | Process mining                          | 16 |

|   | 2.3  | VLSI design flow                        | 23 |

|   | 2.4  | Asynchronous circuits                   | 27 |

|   | 2.5  | Mathematical optimization               | 31 |

| 3 | Phy  | sical planning for chip multiprocessors | 33 |

|   | 3.1  | Motivation                              | 33 |

|   | 3.2  | Related work                            | 40 |

|   | 3.3  | Architectural exploration               | 41 |

|   | 3.4  | Floorplanning methodology               | 43 |

|   | 3.5  | Wire planning                           | 48 |

|   | 3.6  | Results                                 | 51 |

|   | 3.7  | Conclusions                             | 55 |

| 4 | Reg  | ularity-constrained floorplanning       | 57 |

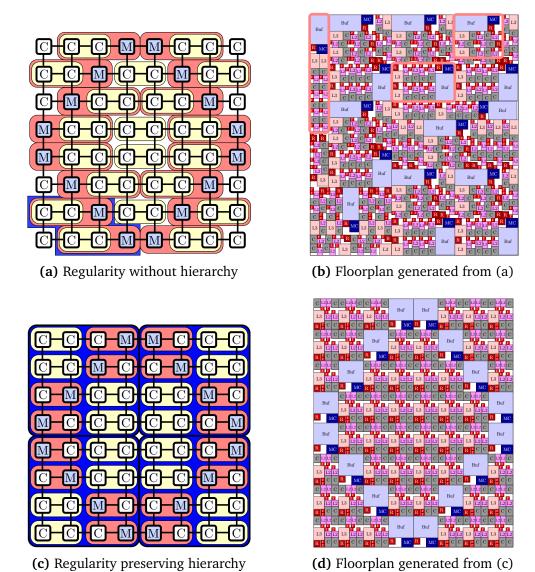

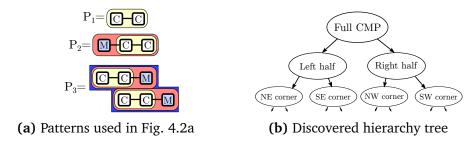

|   | 4.1  | Motivation                              | 58 |

|   | 4.2  | Related work                            | 59 |

|   | 4.3  | Exploring regularity and hierarchy      | 61 |

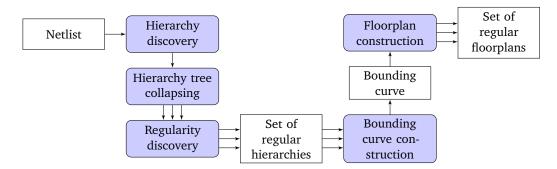

|   | 4.4  | Regular floorplanning algorithm         | 65 |

|   | 4.5  | Results                                 | 73 |

|   | 4.6  | Conclusions                             | 79 |

| 5 | Log  | -based simplification of process models | 81 |

|   | 5.1  | Motivation                              | 82 |

|   | 5.2  | Related work                            | 83 |

|     | 5.3<br>5.4<br>5.5<br>5.6 | Metrics for relevant arcs                     | 88<br>94 |

|-----|--------------------------|-----------------------------------------------|----------|

| 6   | Stru                     | ctured mining of Petri nets                   | 103      |

|     | 6.1                      | Motivation                                    | 103      |

|     | 6.2                      | Related work                                  | 104      |

|     | 6.3                      | Structured mining flow                        | 105      |

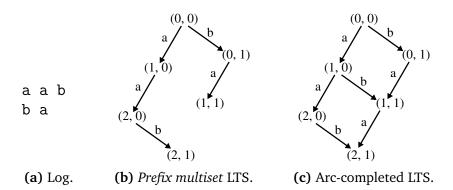

|     | 6.4                      | Construction of an LTS from a log             | 106      |

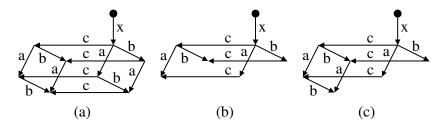

|     | 6.5                      | Extraction of LTS slices                      |          |

|     | 6.6                      | Synthesis of Petri Nets                       | 115      |

|     | 6.7                      | Results                                       | 117      |

|     | 6.8                      | Conclusions                                   | 120      |

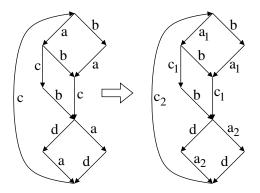

| 7   | Disc                     | overy of duplicate tasks                      | 121      |

|     | 7.1                      | Motivation                                    | 121      |

|     | 7.2                      | Related work                                  |          |

|     | 7.3                      | Local Excitation Sets                         |          |

|     | 7.4                      | Discovering duplicate tasks                   |          |

|     | 7.5                      | Meta-transitions                              |          |

|     | 7.6                      | Results                                       | 134      |

|     | 7.7                      | Conclusions                                   | 137      |

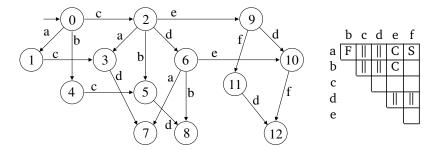

| 8   | Spec                     | cification mining of asynchronous controllers | 139      |

|     | 8.1                      | Motivation                                    | 140      |

|     | 8.2                      | Related work                                  | 144      |

|     | 8.3                      | Circuits with constrained environment         | 144      |

|     | 8.4                      | Specification mining                          | 148      |

|     | 8.5                      | Properties of the specification model         | 151      |

|     | 8.6                      | Results                                       | 153      |

|     | 8.7                      | Conclusions                                   | 159      |

| 9   | Con                      | clusions and future work                      | 161      |

|     | 9.1                      | Summary of contributions                      | 161      |

|     | 9.2                      | Future work                                   |          |

| Bil | oliogi                   | raphy                                         | 165      |

# Chapter 1

# Introduction

The ever increasing amount of information generated and captured during day-to-day activities have firmly entrenched *data mining* as an essential part of almost every sector in the global economy. The goal of data mining is to allow the extraction of useful knowledge from large amounts of data. This data may be generated either as a by-product of other activities, e.g. trails of consumer interactions with both physical and online services, or data expressly captured by all types of sensors.

Data of interest may be represented in various forms. *Unstructured* data is perhaps the most simple, and includes free-form text, untagged audio or video, or any other data that does not reside in fixed fields [105]. On the other hand, *structured* data is organized according to some model. Fixed fields, tags and other types of markers are used to separate the individual data elements.

With the rise of the Internet, relational databases, semantic tagging and other advances, the amount of usable structured data has increased significantly. Furthermore, in many knowledge domains data naturally lends itself to a certain structure. It is common for trails of consumer interactions to be comprised of well-delimited events tagged with timestamps, even if the event information itself is unstructured. It is also common to find data described in terms of relations between objects, such as in relational databases, or any dataset describing a physical structure or a network. *Structure mining*, a subfield of data mining, centers on extracting information from all types of structured and semi-structured data.

*Graphs* provide an ideal abstraction model for structured data. At its core, a graph represents the relationships between a set entities in a specific knowledge domain. Because of the ease and flexibility by which graphs can represent structured data, they are abundant in many topics of interest. Thus, there has been a growing interest in the structured mining of graph data, an area referred as *graph mining* [81].

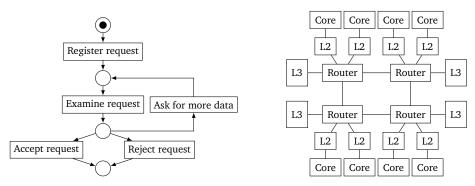

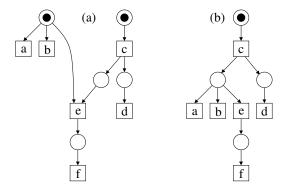

- (a) A graph representing a process (Petri net [112]).

- **(b)** A graph representing a Chip multiprocessor (*block-level netlist*).

Figure 1.1: Examples of graph-based data structures.

The generality of graphs allows graph mining techniques to be used in a variety of different knowledge fields. Figure 1.1 contains two examples of graphs, modeling data sets of the two different domains in which this thesis will primarily operate. However, graph mining is applicable to a myriad of other real-world topics.

Figure 1.1a describes the *control flow* of a business process using a modeling abstraction known as a *Petri net* [112]. Petri nets provide a formalism to describe concurrent systems, effectively describing all possible executions of a system. In the figure, a snippet of the behavior of an online request system is detailed. While the vertices represent the different tasks performed by the system, the edges specify the dependencies of the different tasks, e.g. it is necessary to register the request before examining it.

The area of *Process mining* deals with the discovery of process models, such as the one in Fig. 1.1a, from event logs. Process mining also deals with the analysis and extension of these process models. Process models, Petri nets, and the associated area of Process mining are documented with more detail in Section 2.2.

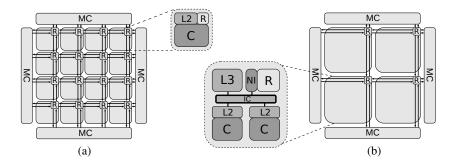

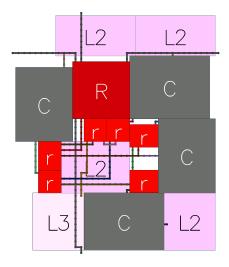

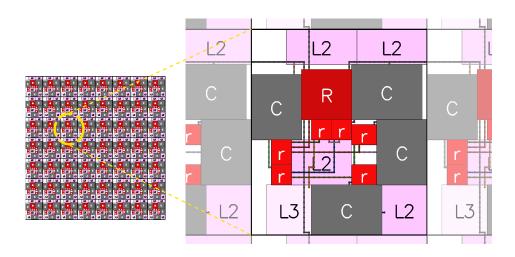

From a different knowledge field, Fig. 1.1a shows a *netlist*, which describes the physical connectivity of an electronic circuit. In this case, the vertices represent the different high-level functional blocks of a Chip multiprocessor: cores, I/O routers, and L2 and L3 cache memory modules. An edge indicates a physical bus, perhaps comprising thousands of individual on-chip wires, between a pair of components. Connectivity graphs like these are used, for example, as inputs during the design stage of chip multiprocessors, to ensure that highly connected components are kept physically close and thus minimize total wire length. Netlists and the general design process of integrated circuits will be further introduced in Section 2.3.

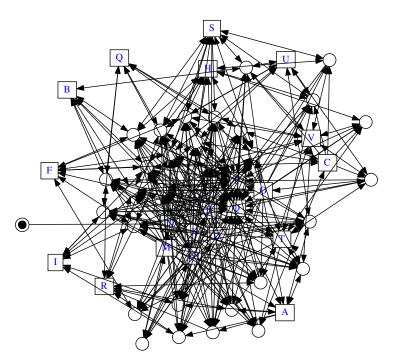

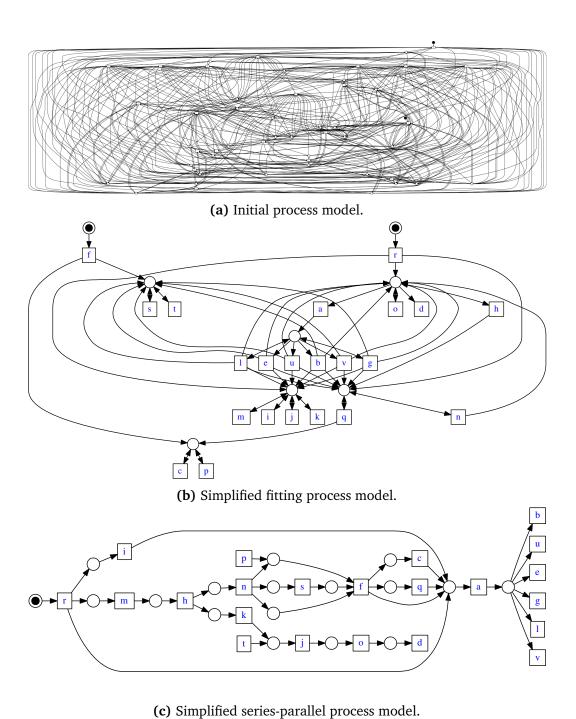

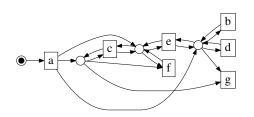

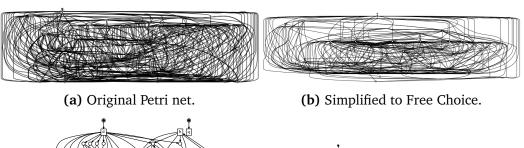

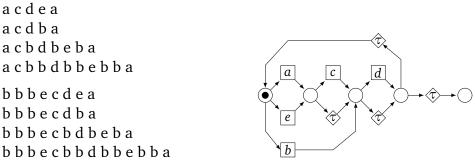

**Figure 1.2:** Process model extracted from consumer interactions with the helpdesk of a telecommunications company.

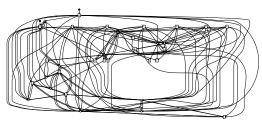

As in other related fields of data mining, one of the significant challenges in graph and structure mining is the ever growing amount of available data [105]. More information is being produced and captured than ever, and the trend for the next decade is towards exponential growth. Such growth can provide new opportunities to gather additional insights from the data. Due to the increased complexity of the data, however, more advanced mining tools are required before these benefits can be reaped. We center on two requirements, that we describe with more detail below.

First, the danger of overwhelming data, i.e. too much 'noise' and not enough 'signal' so as to provide useful insight into the data. In Figure 1.2, we show a process model constructed automatically from the event logs of real-life helpdesk consumer interactions of a large telecommunications company [56]. The graph shown is too complex to provide any insight into the underlying process, and thus fails at one of the primary objectives of data mining: providing useful information. Simplifying or entirely avoiding these types of models is one of the desirable objectives.

Second, larger data sets demand more efficient algorithms to process the available data under reasonable time constraints. Algorithms for graph mining should always consider efficiency in terms of the size of the input dataset.

Circuit netlists, for example, typically contain millions of individual vertices. Algorithms should be scalable in the number of vertices and edges, whenever possible. Alternatively, problems should be partitioned into smaller instances to avoid excessive runtimes.

The ability to apply graph mining strategies to a wide range of problems in the areas of circuit design and process mining, and the challenges and opportunities provided by the ever-increasing available data in graph form motivate this thesis. The rest of this chapter will describe the goals of this thesis with more detail.

#### 1.1 Contributions of this thesis

In this thesis, we propose using graph and structure mining methods to solve various real-life problems in the areas of process mining and circuit design. The underlying idea behind all of the proposed methods is structure discovery, i.e., automatically extracting new structures from structured data, usually in the form of a graph. Specifically, the challenges addressed in this thesis are:

- 1. Finding repeating structures in netlists to optimize regularity in chip floorplans (Chapters 3 and 4).

- 2. Simplifying process models by discovering visually-friendly structures (Chapters 5, 6 and 7).

- 3. Reverse engineering asynchronous circuit specifications from implemented circuits (Chapter 8).

The following subsections provide an high-level summary of each one of these challenges.

### 1.1.1 Physical planning for regular layouts

In circuit design, the floorplanning problem comprises allocating the physical space required to functional blocks in a chip. Structures that are highly connected should be placed close together, so as to minimize the total required length of the wires. The computational complexity of the floorplanning problem highly depends on the number of components of the design.

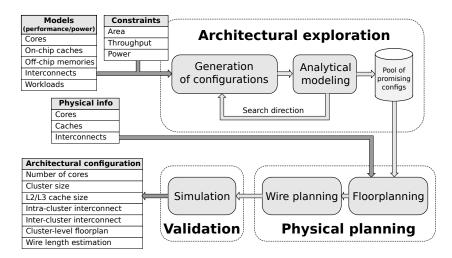

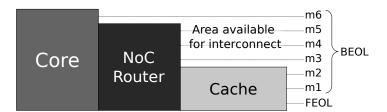

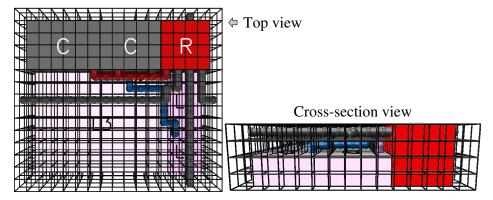

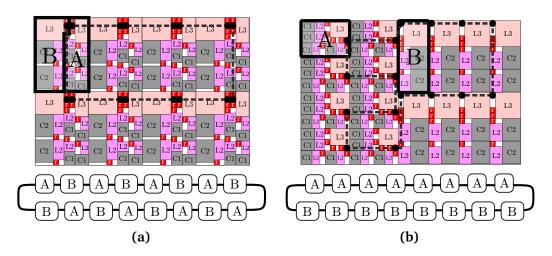

Regular floorplans, which contain runs of repeating subpatterns, each of them with the same subfloorplan, are well-known to provide multiple benefits. Each of the repeating identical parts needs to be designed only once, thereby exponentially reducing the design cost and search space of the problem. In Chip multiprocessors (CMPs), a standard industry practice to exploit regularity is via the use of tiles. A tiled CMP is usually entirely comprised of a single tile design that is replicated tens or hundreds of times, usually in a grid-like fashion. Chapter 3 presents a method to perform efficient floorplanning in presence of these tiles, while still guaranteeing the global physical constraints for manufacturing such as routability or abutability. The goal of the proposed method is to be used during the early exploration of CMP architectures, as an efficient estimator of the physical viability of candidate designs.

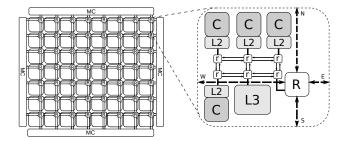

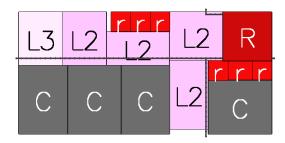

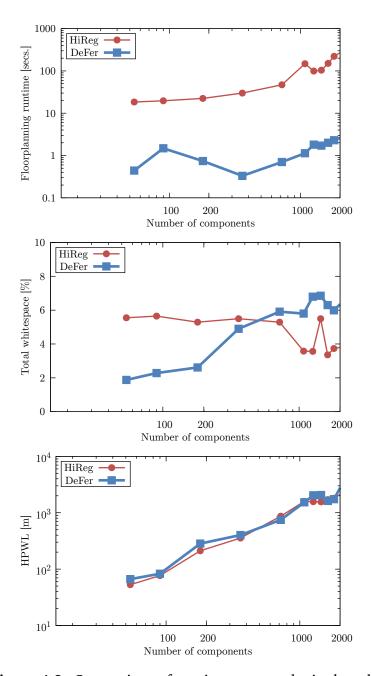

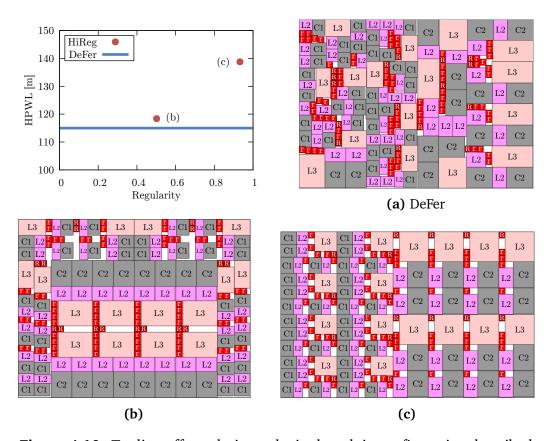

In Chapter 4, on the other hand, we present an approach that is more generally oriented towards all types of circuits. For this, we propose automatically finding repeating subgraphs in the design netlist using frequent subgraph mining techniques. We introduce a floorplanner, *HiReg*, that can use these frequent subgraphs to accelerate floorplanning runtime and automatically produce regular floorplans, with configurable focus on area or wire length minimization. The problem of frequent subgraph mining will be defined in Section 2.1.2, while the algorithm used will be detailed in Chapter 4.

These chapters are based on the following publications:

- J. de San Pedro, N. Nikitin, J. Cortadella, and J. Petit, *Physical Planning for the Architectural Exploration of Large-Scale Chip Multiprocessors*, in Proceedings of the 2013 IEEE/ACM Seventh International Symposium on Networks-on-Chip, Tempe, Arizona, USA, 2013.

- J. Cortadella, J. de San Pedro, N. Nikitin, and J. Petit, *Physical-aware system-level design for tiled hierarchical chip multiprocessors*, in Proceedings of the 2013 ACM International Symposium on Physical Design, New York, NY, USA, 2013, pp. 3–10.

- J. de San Pedro, J. Cortadella, and A. Roca, *A hierarchical approach for generating regular floorplans*, in Proceedings of the 33th IEEE/ACM International Conference on Computer-Aided Design, San Jose, California, USA, 2014.

# 1.1.2 Visualization of process models

As with any other discipline in data mining, a significant challenge in process mining is presenting the results in a way such that new insight may actually be gained from the data. While ever increasing computing power combined with huge data sets provide new opportunities, in practice, there is a big gap between what computers can store and what humans can interpret and use. For crucial areas like health care, extracting value from the data is a challenge [7].

The visualization of process models in a understandable way for a human is a crucial step towards this end.

In this thesis we propose a series of methods with the goal of simplifying existing process models as well as process discovery techniques that allow the direct generation of visually-friendly models. The proposed methods involve applying graph mining techniques on top of either the process models themselves, or derived transition systems. While the methods are primarily oriented towards Petri nets, many of the methods can be extended to other Process model formalisms.

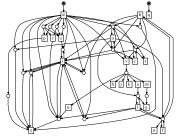

The first proposed approach, described in Chapter 5, introduces a series of methods to simplify existing process models. We also propose a metric that is able to rank the importance of the different control flow structures when reproducing the behavior of the original process. This way, parts of a model that have high visual complexity but only specify infrequent behavior can be identified and removed. The understandability of the model can be enhanced with a minimal impact on its fitness and precision.

Chapter 6 proposes an alternate approach in order to allow the simplification of process models without incurring any cost in precision. Representing all the behavior of a process in a single process model may not be possible without sacrificing simplicity, fitness or precision. This is because real-life processes are usually highly unstructured. The proposed approach automatically discovers multiple process models, each of them satisfying certain structural properties while centering on a specific aspect of the behavior of the process. Therefore, the complexity of the obtained models can be kept under check even for complex event logs.

Duplicate tasks [7] are an extension available in many process model formalisms, which allows two or more vertices in a single model to refer to the same event. Duplicate tasks can be used to simplify process models with minimal impact on their accuracy metrics. However, the automatic discovery of duplicate tasks is an open challenge in Process mining. In Chapter 7, we contribute a method to automatically discover duplicate tasks that is compatible with most process mining discovery algorithms. The proposed method utilizes a graph clustering strategy that is resilient to commonly used control flow structures, such as loops, choice or concurrency. Additional extensions to the formalisms of process models are also discussed.

These chapters are based on the following publications:

• J. de San Pedro, J. Carmona, and J. Cortadella, *Log-Based Simplification of Process Models*, in Business Process Management (BPM), Innsbruck, Austria, September 2015.

- J. de San Pedro and J. Cortadella, *Mining Structured Petri Nets for the Visualization of Process Behavior*, in Proceedings of the 2016 ACM Symposium on Applied Computing (SAC), Pisa, Italy, April 2016.

- J. de San Pedro and J. Cortadella, *Discovering duplicate tasks in transition systems for the simplification of process models*, in Business Process Management (BPM), Rio de Janeiro, Brazil, September 2016.

#### 1.1.3 Specification mining for asynchronous circuits

Asynchronous circuits are not driven by a global clock signal, and offer many potential benefits in terms of lower power consumption and higher performing functional units, specially in light of the modern manufacturing processes and the involved challenges. However, they have since long claimed to be more difficult to design. In the traditional design flow of asynchronous control circuits, the desired behavior of the circuit is formally specified in the form of a *Signal Transition Graph*, from which an implementation can be automatically synthesized [46].

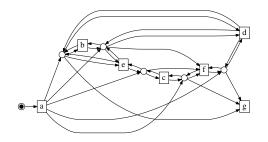

In Chapter 8, we introduce the concept of *specification mining*, in which a formal specification is obtained from the implementation of a circuit. We propose a method to perform specification mining valid for many types of asynchronous controllers and considering several delay models. The proposed method combines both graph mining and process mining techniques, such as the discovery algorithm proposed in Chapter 6.

This chapter is based on the following conference article:

Javier de San Pedro, Thomas Bourgeat and Jordi Cortadella, Specification mining for asynchronous controllers, in Proceedings of the 2016 IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC), Porto Alegre, Brazil, May 2016.

#### 1.2 Structure of this document

This thesis is structured in 9 chapters. This chapter constitutes the introduction to the thesis. Chapter 2 introduces the necessary basic concepts in graphs, circuit design, and process mining required for understanding this thesis.

Chapters 3–4 deal with the explotation of regularity during floorplanning. In Chapter 3, we focus on Chip multiprocessors. Chapter 4 extends the method to all types of circuits by using frequent subgraph mining strategies and providing a more general version of the constraints defined in the previous chapter.

Chapters 5–7 center on the visualization of process models. Chapter 5 introduces a method to simplify process models for visual consumption by directly removing control flow structures that are least important to reproduce the most frequent behavior in the log. In Chapter 6, we propose an alternative method that allows simplification by generating a sequence of visually-friendly process models, each of them centering on specific aspects of the process, rather than constructing a unique model that may be difficult to simplify. Chapter 7 proposes a method to exploit the concept of duplicate tasks for further simplification of process models.

Chapter 8 opens the topic of specification mining for asynchronous circuits, and shows a method to obtain the specifications of asynchronous controllers with specific constraints for various delay models.

# Chapter 2

# **Preliminaries**

This chapter introduces the necessary background of concepts, algorithms and knowledge areas that will be used in the rest of this document.

Section 2.1 introduces the area of graph mining, which is behind most of the algorithms and methods presented in this thesis. Section 2.2 gives an overview of the area of process mining, that will be the basis of Chapters 5, 6, 7. Section 2.3 provides a tour of the basic design flow of VLSI circuits to help understand the context of Chapters 3, 4 and 8. Section 2.4 reviews the area of asynchronous circuit design used in Chapter 8. Finally, Section 2.5 summarizes the area of mathematical optimization, including satisfiability and linear programming.

# 2.1 Graph mining

The domain of *data mining* concerns itself with the extraction of patterns and knowledge from data to facilitate understanding and further use of the data. *Structure mining* is a proper subset of data mining that centers on structured datasets. In particular, *graph mining* centers on providing efficient algorithms to mine structures embedded in graphs [136]. Graphs, being one of the most generic types of structure, are naturally suited to represent most types of structured datasets.

Some examples of popular research areas in graph mining are [81]: frequent subgraph mining; graph classification, clustering, and search; work-flow mining. This section will provide an introduction to two of the most common subareas of graph mining, frequent subgraph mining and graph clustering.

#### 2.1.1 Graph basics

An *undirected graph*  $G = \langle V, E \rangle$  is a two-tuple comprising a set V of vertices and a set E of edges. An edge  $e = \{v_1, v_2\} \in E$  is an unordered pair of vertices  $v_1, v_2 \in V$ . We say that any two vertices  $v_1, v_2 \in V$  are *adjacent* if there is an edge  $e = \{v_1, v_2\} \in E$  connecting them. In this case, we also say that  $v_1$  and  $v_2$  are *incident* to e. The *degree* of a vertex  $v \in V$  is the number of edges incident to v. Note that there can be only one edge between any pair of vertices  $v_1, v_2 \in V$ .

A path in *G* is a finite sequence of different vertices  $v_1, \ldots, v_n \in V$  so that  $e_1 = \{v_1, v_2\}, \ldots, e_n = \{v_{n-1}, v_n\} \in E$ . A path  $v_1, \ldots, v_n \in V$  where  $v_1 = v_n$  is also called a *cycle*. A graph is *connected* if there exists a path between each pair of vertices. It is *cyclic* if contains any cycle.

In a directed graph  $G = \langle V, E \rangle$ , V is the set of vertices, while  $E = V^2$  is a set of ordered pairs of vertices. Every  $e = (v_1, v_2) \in E$  is a directed edge. Unlike undirected graphs, every edge  $e = (v_1, v_2)$  has a direction, with  $v_1, v_2$  being the head and the tail of e respectively. In addition,  $v_2$  is direct successor of  $v_1$ , while  $v_1$  is a direct predecessor of  $v_2$ .

A path in a directed graph respects the direction of the edges:  $v_1, \ldots, v_n \in V$  is a path only if  $e_1 = (v_1, v_2), \ldots, e_n = (v_{n-1}, v_n), \in E$ . Given a directed graph G and two vertices  $v_1, v_2 \in V$ , if there exists a path between  $v_1, v_2$ , we say that  $v_2$  is a *successor* of  $v_1$ , while  $v_1$  is a *predecessor* of  $v_2$ . Similarly to undirected graphs, a *directed cycle* is a path  $v_1, \ldots, v_n \in V$  in which  $v_1 = v_n$ .

A directed graph is *strongly connected* if there is a path between every ordered pair of vertices. Otherwise, a graph is *weakly connected* if there is a path between each unordered pair of vertices. A *directed acyclic graph* (DAG) is directed graph in which there are no cycles.

A subgraph G' of graph  $G = \langle V, E \rangle$  is another graph  $G' = \langle V', E' \rangle$  in which  $V' \subseteq V$  and  $E' \subseteq E$ . We say G' is an *induced subgraph* if for every  $v \in V'$ , all of the incident edges of v in G are in E'.

A graph *vertex labeling* is a function  $\mathcal{L}: V \to \Sigma$  that assigns a label  $l \in \Sigma$  for each vertex, where  $\Sigma$  is the alphabet of labels. Conversely, an *edge labeling*  $\mathcal{L}: E \to \Sigma$  maps a label to every edge. Often the combination of a graph and labeling is referred as *labeled graph*.

#### Planar graphs

An *embedding* or drawing of a graph  $G = \langle V, E \rangle$  on a surface S is an assignment of a unique geometric position to each vertex  $v \in V$  and of a curve to every edge  $e = \{v_1, v_2\} \in E$  so that the starting and ending points of the curve correspond to the positions of  $v_1$  and  $v_2$ . Unless specified, we will always assume S to be the two-dimensional plane,  $\mathbb{R}^2$ . An embedding is *planar* if no two edges

intersect except possibly at the endpoints. A graph is planar if it has no planar embedding in  $\mathbb{R}^2$ .

The *crossing number* of an embedding is the number of all intersections of the curves representing the edges (excluding the common endpoints). For a graph G, its *crossing number* is the minimal crossing number from all of its possible embeddings in  $\mathbb{R}^2$ . Thus, a graph is planar iff its crossing number is 0.

The crossing number of a graph has often been used as a more accurate measure of its complexity than its number of vertices or average degree. For example, the crossing number of a netlist has been used to provide bounds on the area and wire length required for routing a design [102].

Computing the crossing number of an arbitrary graph is a well-known NP-complete problem [68]. Despite that, there are several methods to estimate it. In this thesis we will use a technique derived from the *mincross* procedure as used in the commonly used graph drawing program *dot* [66] from the *Graphviz* suite [67]. As it is only an estimation, *mincross* may sometimes overestimate the number of crossings in large, dense graphs. These pathological cases, most often, are already highly complex even if the crossing number is overestimated.

#### Graph isomorphism

Two graphs  $G_1 = \langle V_1, E_1 \rangle$ ,  $G_2 = \langle V_2, E_2 \rangle$  are *isomorphic* if there exists a bijective function  $f: V_1 \to V_2$  so that if any two vertices  $v_1, v_2 \in V_1$  are adjacent in  $G_1$  iif  $f(v_1), f(v_2)$  are adjacent in  $G_2$ . This forms an equivalence relation on graphs.

Two graphs  $G_1$ ,  $G_2$  labeled respectively with  $\mathcal{L}_1$  and  $\mathcal{L}_2$  are usually only considered isomorphic if the bijection f preserves the labeling of the vertices. That is, if  $\forall v \in V_1$ ,  $\mathcal{L}_1(v) = \mathcal{L}_2(f(v))$ .

The complexity of computing whether two general graphs are isomorphic is currently an open question. There are polynomial-time algorithms for specific types of graphs, such as for planar graphs. However, this not the case for all types of graphs, even if in practice it can often be solved efficiently [44].

Given two graphs  $G_1$ ,  $G_2$ , the *subgraph isomorphism* problem is defined as finding  $G'_1$ , a subgraph of  $G_1$  isomorphic to  $G_2$ . Unlike graph isomorphism, the problem of subgraph isomorphism is well-known to be NP-complete [44].

# 2.1.2 Frequent subgraph mining

Frequent subgraph mining (FSM) [81,90] is one of the most important areas of graph mining. The objective of FSM is to extract all the subgraphs in a given dataset (a labeled graph, or a set of labeled graphs) which satisfy certain constraints. The most common goal is to find frequently recurring patterns, i.e. runs of isomorphic or almost isomorphic subgraphs with high occurrence

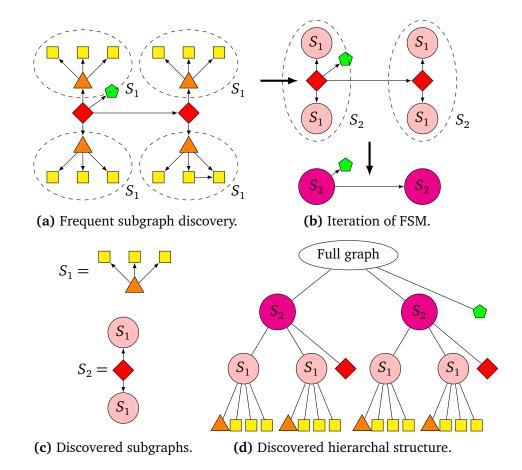

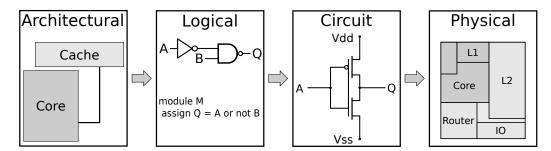

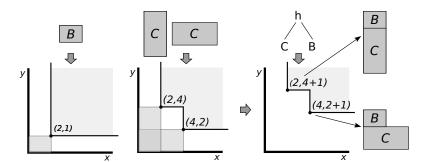

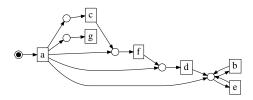

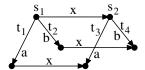

**Figure 2.1:** Frequent subgraph and structure discovery.

counts. However, additional constraints may be used. For example, finding subgraphs that satisfy specific structural properties. Some of the most important applications of FSM have been seen in the domains of chemistry, biology, and web mining [81].

An example of the objectives of FSM can be seen in Fig. 2.1a [90]. We will refer to the graph shown in this figure as G. Different labels for every vertex in G are represented by different visual shapes in the figure. In G, subgraph  $S_1$  has been identified as the most frequent, since there are 4 *instances* of  $S_1$  in G. Any other subgraph of G is either less frequent than  $S_1$ , or has fewer vertices.

Note how the south-west instance of  $S_1$  in Fig. 2.1a contains an additional edge that does not exist in other instances of  $S_1$ . Most FSM algorithms allow for *inexact* isomorphism, in which two subgraphs are not required to be entirely isomorphic to be counted as two instances of the same pattern. Instead, an approximate measure of similarity is used, depending on the nature of the underlying problem.

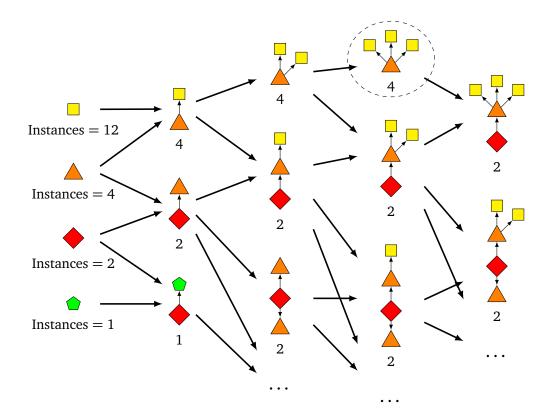

**Figure 2.2:** Partial search tree of frequent subgraph mining.

General-purpose FSM is a high-complexity problem because of its dependence on subgraph isomorphism, an NP-complete problem. The basic idea behind most FSM algorithms is based on two alternating steps: candidate generation and filtering. During candidate generation, each of the candidate subgraphs from the previous iteration is *grown* by adding new vertices and edges. The new, enlarged subgraphs form the set of candidates for the next step. This next step, filtering, *counts* the number of instances of each candidate subgraph: any candidate that is not frequent enough or violates any other constraint is purged. The process iterates until there are no further candidates.

Figure 2.2 illustrates this by showing a potential search tree of FSM in the graph from Fig. 2.1a (G). The first column corresponds to the first subgraph candidate set, composed of all possible 1-vertex subgraphs of G. The number of instances of each subgraph is also shown. On each next iteration (successive columns), every candidate is extended by adding exactly one vertex. Each candidate has multiple extensions, depending on the number of possible vertex labels. Note how, given a candidate, the number of instances of each successor is

| Purpose                          | Input graph      | Desirable subgraphs      |  |

|----------------------------------|------------------|--------------------------|--|

| Optimizing regularity in chip    | Netlist          | Maximally frequent sub-  |  |

| floorplans (Chapter 4)           |                  | graphs.                  |  |

| Visually simplify process models |                  |                          |  |

| (Chapter 5)                      | (e.g. Petri net) | that maximizes an objec- |  |

|                                  |                  | tive function.           |  |

| Mine structurally-simple pro-    | Labeled          | Subgraphs that satisfy   |  |

| cess models (Chapter 6)          | transition       | structural properties.   |  |

| Mine specifications from asyn-   | system           |                          |  |

| chronous circuits (Chapter 8)    |                  |                          |  |

**Table 2.1:** Summary of graph mining variations proposed in this thesis.

always less or equal that of the candidate. The largest, most frequent candidate found in the search tree is indicated by a dashed line.

Different FSM algorithms are distinguished [81] by the candidate generation method (e.g. whether to enlarge a single vertex at at time or by combining multiple graphs), search strategy (e.g. BFS, DFS, ...), and candidate evaluation (metrics used for selecting the best graph, filtering, etc.). Adapting the algorithm to the nature of the specific application domain may allow significant reductions in the search space.

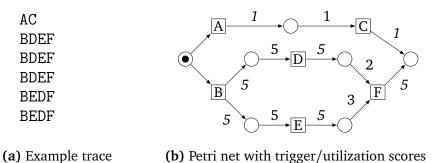

Subgraph mining is a core concept behind many of the approaches proposed in this thesis. In Chapter 4, frequent subgraph mining is used to discover repetitive patterns in netlists in order to increase the regularity of floorplans. Chapter 5 shows how to simplify existing process models by extracting a single subgraph that maximizes the quality of the model while keeping the complexity under check. In both Chapter 6 and Chapter 8, graph mining is performed on top of a labeled transition system An overview of these variations is described in Table 2.1.

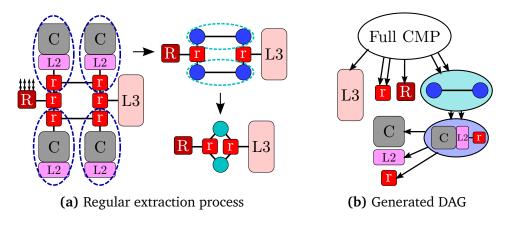

# 2.1.3 Structure discovery

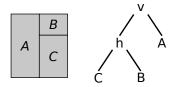

One of the practical applications of FSM is *structure discovery*, sometimes also called *hierarchical clustering*. The goal of structure discovery is to enhance the interpretation of data in graph form by producing a hierarchical description of the structural regularities in the data [43]. While FSM can be used to discover repeated structures in the graph, structure discovery can be used to organize these repeated structures into a hierarchical description of the data, allowing an higher level of abstraction.

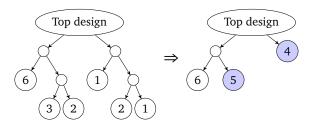

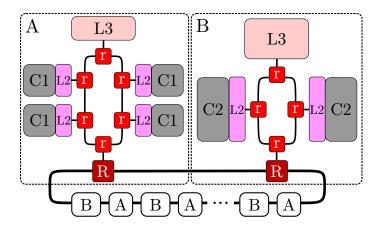

A simple yet common method to perform structure discovery is by performing multiple passes of FSM. This approach is described in Fig. 2.1. Once a frequent subgraph  $S_1$  is discovered in Fig. 2.1a, each of its instances is replaced by a new vertex that acts as a placeholder to the discovered subgraph instance, as seen in Fig. 2.1b. This is commonly referred to as *compressing* the graph, since it reduces the size of the graph.

The better a particular set of frequent subgraphs describe a graph, the more the graph will be compressed by replacing the instances of each subgraph with a placeholder vertex. Repeated iterations will discover additional subgraphs, including hierarchical ones, containing previously compressed subgraphs. This is exemplified by subgraph  $S_2$  in Fig. 2.1b, which comprises two instances of  $S_1$ . Whenever a newly-discovered subgraph is defined in terms of existing identified subgraphs, these form a hierarchy. For example, the hierarchy tree formed by  $S_1$  and  $S_2$  is shown in Fig. 2.1d. This structure describes the graph in a much more compact way, and also provides an abstracted view of the regular patterns in the graph.

Structure discovery has been applied to areas such as data compression [117] or knowledge conceptual clustering [84]. The discovered hierarchies can provide varying levels of interpretation, with increased or decreased detail depending on the goals of the data analysis. As in FSM, inexact compression is often used, even allowing for potentially overlapping subgraphs.

In this thesis, structure discovery is the basis of the method described in Chapter 4 to generate regular floorplans. Existing structure in the input netlist is automatically discovered and used to enhance the quality of floorplans.

# 2.1.4 Graph clustering

Despite the name, *graph clustering* is the problem of trying to find sets of "related" vertices in a graph [124]. It should not be confused with the clustering of graphs themselves.

Clustering in general is one of the main areas of research in data mining. Unfortunately, no single definition of a cluster is universally accepted. Formally, the vertices assigned to a particular cluster should be similar and/or connected in some predefined sense. In some applications, it is desirable for clusters of vertices to be *connected*: the number of edges that remain within a cluster should be high, while there should be few edges that cross cluster boundaries. In this scenario, good clusters usually form dense subgraphs.

Alternatively, it might be desirable for clusters to be composed of *similar* vertices. The higher the similarity index, the more likely two vertices are clustered together. Computing similarities between vertices may not be necessarily

simple. The most straightforward manner to compute a similarity index between two vertices is by using adjacency information, i.e., the overlap of their neighborhoods [124].

The method described in Chapter 7 to simplify process models using duplicate tasks involves clustering vertices on a transition system by their context.

# 2.2 Process mining

The digital data revolution that is taking place worldwide requires new algorithms that enable acquiring value from the vast amount of data stored by the current technology. *Process-Aware Information Systems* (PAIS) are at the center of this revolution, since they are in charge of monitoring processes taking place in our daily life, like banking, municipalities, shopping, health care, etc. Event data, recorded in a PAIS in the form of *event logs*, denotes the footprints of process executions, and is an important source of information for reasoning on how the PAIS interacts with its environment when running its processes.

The area of *Process mining* uses these logs to discover, analyze and extend process models [2]. Process models deliver valuable insight into the execution of the underlying processes. Models can be used to find errors in real-life systems, such as deadlocks. Bottlenecks and other factors influencing the response time of a system can be identified by using simulation techniques. A process model may also be used as description or specification of a PAIS.

*Discovery*, one of the major areas of process mining, fosters this goal by constructing abstract process models that describe the high level structure of the process. These models are automatically learned from the execution traces of the proces, without using any other a-priori information.

An additional important area in process mining is *conformance*, in which existing process models are compared with event logs generated by the same process. Conformance checking verifies if the behavior described by the model corresponds to the behavior observed in the event log. Deviations may be detected in either the model or the event log, indicating potential hazards in the execution of the PAIS. The area of *enhancement*, on the other hand, aims at changing or extending an existing process model to better reflect the behavior observed in the event log.

#### Traces and event logs

Event logs are the starting point to apply process mining techniques, guided towards the discovery, analysis or extension of process models. Informally, an event log is a set of traces, each of them being the footprint of a single execution

| Trace | Parikh vector |   |   |   |  |

|-------|---------------|---|---|---|--|

|       | а             | b | С | d |  |

| abcd  | 1             | 1 | 1 | 1 |  |

| acba  | 2             | 1 | 1 | 0 |  |

| aaaa  | 4             | 0 | 0 | 0 |  |

Table 2.2: Event log and Parikh vectors for each trace.

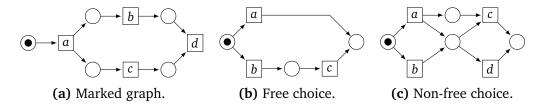

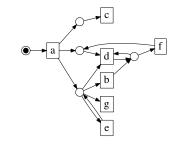

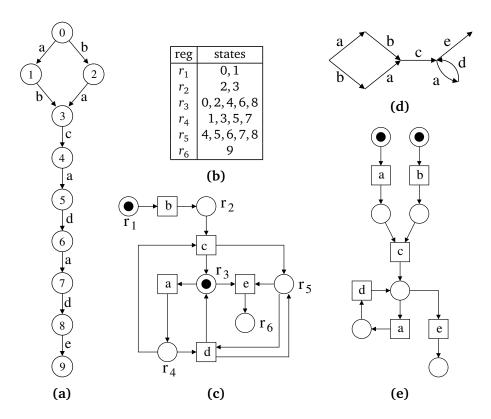

Figure 2.3: Petri net types.

of a process. Traces, thus, are a chronological sequence of events, such as "Request rejected". Usually we will refer to the different types of events with a single letter, e.g.  $A, B, \ldots$

Let  $\Sigma$  be an alphabet of *events*. A *trace* is a word  $\sigma \in \Sigma^*$  that represents a finite sequence of events. An *event*  $\log L \in \mathcal{B}(\Sigma^*)$  is a multiset of traces<sup>1</sup>.

Given a trace  $\sigma \in \Sigma^*$ , the *Parikh vector* of  $\sigma$ ,  $\psi(\sigma) : \Sigma \to \mathbb{N}$  maps every event  $e \in \Sigma$  to the number of times it appears in  $\sigma$ . Table 2.2 illustrates this with an example. Parikh vectors are an important concept in transition systems, as will be seen in the rest of this thesis.

Events usually contain additional attributes, such as the timestamp or the actor that initiated the event. However, this work centers on the control flow itself, and thus event attributes are not used. In many scenarios we propose how the work could be improved by the use of such additional information.

#### 2.2.1 Process models

Process models are formalisms to represent the behavior of a process. Among the different formalisms, Petri nets are perhaps the most popular, due to its well-defined semantics. In this thesis, we will primary focus on Petri nets as a process model, although some of the work may be adapted to other formalisms like BPMN [140], EPC [88] or similar.

#### **Petri Nets**

A Labeled Petri Net [112] is a tuple  $N = \langle P, \Sigma, T, \mathcal{L}, \mathcal{F}, m_0 \rangle$ , where P is the set of places,  $\Sigma$  is the alphabet of labels (corresponding to events), T is the set of transitions,  $\mathcal{L}: T \to \Sigma \cup \{\tau\}$  assigns a label (or the empty label  $\tau$ ) to every transition,  $\mathcal{F}: (P \times T) \cup (T \times P) \to \mathbb{N}$  is the flow relation, and  $m_0$  is the initial marking. A marking is an assignment of a non-negative integer to each place. If k is assigned to place p by marking m, denoted m(p) = k, we say that p is marked with k tokens. Given a node  $x \in P \cup T$ , the set  $\mathbf{v} = \{y | \mathcal{F}(y, x) \geq 1\}$  is the pre-set of x, while  $x^{\bullet} = \{y | \mathcal{F}(x, y) \geq 1\}$  is the post-set of x.

A transition t is *enabled* in a marking m when  $\forall p \in {}^{\bullet} t, m(p) \geq \mathscr{F}(p,t)$ . When t is enabled, it can *fire* by removing  $\mathscr{F}(p,t)$  tokens from each place  $p \in {}^{\bullet} t$  and putting  $\mathscr{F}(t,p)$  tokens to each place  $p \in {}^{\bullet} t$ . A marking m' is reachable from m if there is a sequence of firings  $t_1t_2...t_n$  that transforms m into m', denoted by  $m[t_1t_2...t_n\rangle m'$ . A sequence  $t_1t_2...t_n$  is *feasible* if it is firable from  $m_0$ . A trace  $\sigma$  *fits* N if there exists a feasible sequence in N with the same labels.

A Petri net is *live* if for every marking m reachable from  $m_0$ , and  $\forall t \in T$ , there is a marking m' reachable from m which enables t. A Petri net is k-bounded if for each  $p \in P$  and for every reachable marking m,  $m(p) \le k$ . A 1-bounded Petri net may also be referred to as *safe*.

In a Petri net, a *choice* is a place with more than one output transition. Two transitions are said to be *concurrent* if they do not have dependencies between them, i.e. they can fire in any order.

A transition labeled with the empty label  $\tau$  is called a *silent* transition. A *duplicate* task is a transition with the same label as some other transition in N.

A set of restrictions on the structure of Petri nets define several classes of Petri nets. A Petri net N is a *Marked Graph* if  $\forall p \in P : |{}^{\bullet}p| \leq 1 \land |p^{\bullet}| \leq 1$ . It is a *Free-Choice* net if  $\forall p_1, p_2 \in P : p_1^{\bullet} \cap p_2^{\bullet} \neq \emptyset \Rightarrow |p_1^{\bullet}| = |p_2^{\bullet}| = 1$ . Note that every marked graph is a free-choice net. Figure 2.3 illustrates these concepts. In Fig. 2.3c, the choice between a, b is free, but the choice between c, d is not.

#### Workflow nets

We also introduce two additional two classes of Petri nets in which the starting and ending markings are clearly delimited by special *source* and *sink* places.

A *workflow* net [1] is a Petri net  $N = \langle P, \Sigma, T, \mathcal{L}, \mathcal{F}, m_0 \rangle$  with exactly one source place  $i \in P$ , with  ${}^{\bullet}i = \emptyset$ , and exactly one sink place  $o \in P$  with  $o^{\bullet} = \emptyset$ . In addition, in a workflow net there is a path from i to every other node  $n \in P \cup T$ , and a path from each node  $n \in P \cup T$  to o.

$<sup>^{1}\</sup>mathcal{B}(A)$  denotes the set of all multisets over A.

**Figure 2.4:** LTS corresponding to the Petri nets in Fig. 2.3

The Petri nets in Fig. 2.3b and 2.3c are workflow nets. However, the Petri net in Fig. 2.3a is not, since there is no sink place.

A workflow net is *sound* [6] if and only if it satisfies the following properties:

- Option to completion: from every marking m reachable from  $m_0$ , a marking m' with m'(o) > 0 can always be reached. Thus, the ending marking is always reachable.

- *Proper completion*: for any reachable marking m where m(o) > 0, and  $\forall p \in P$  with  $p \neq o$ , m(p) = 0. That is, once the ending marking has been reached, no other transition can fire.

- *No dead transitions*: every transition  $t \in T$  is enabled in at least one reachable marking.

These properties ensure that a sound workflow net is both bounded and live for all markings except the ending markings, where m(o) > 0. Sound workflow nets are heavily used in process mining because their semantics are similar to real-life processes.

### 2.2.2 Labeled Transition Systems

A finite labeled transition system is a tuple  $A = \langle S, \Sigma, T, s_0 \rangle$  where S is a finite set of states,  $\Sigma$  is the alphabet of labels,  $T \in S \times \Sigma \times S$  are the transition relations between states, labeled with  $\Sigma$ , and  $s_0$  is the initial state. A transition system may also be interpreted as a directed graph where S is the set of vertices and T is the set of edges.

We use  $s \xrightarrow{e} s'$  as a shorthand for the arc  $(s, e, s') \in T$ . Similar to Petri nets, a trace  $\sigma = e_1 e_2 \dots e_n$  fits LTS A if there exists a sequence  $s_1, s_2, \dots, s_n \in S$  with  $s_0 \xrightarrow{e_1} s_2 \xrightarrow{\dots} s_{n-1} \xrightarrow{e_n} s_n$ .

**Definition 2.1** (Excitation Set). For a given LTS A and event  $e \in \Sigma$ , we define the *Excitation Set* of e as the set of states in which e is enabled, i.e.,

$$ES(e) = \{ s \in S \mid \exists s' \in S : s \xrightarrow{e} s' \}.$$

The following definitions formalize causality relations between two events:

**Definition 2.2** (Concurrency and conflict). Two events a, b are *concurrent* if there are four states,  $s_1 ldots s_4$  in S such that  $s_1 \stackrel{a}{\longrightarrow} s_2 \stackrel{b}{\longrightarrow} s_4$  and  $s_1 \stackrel{b}{\longrightarrow} s_3 \stackrel{a}{\longrightarrow} s_4$ . In this case we will also say that a, b are concurrent in  $s_1$ . Two events a, b are in *conflict* if there is a state  $s \in ES(a) \cap ES(b)$  and a, b are not concurrent in s.

**Definition 2.3** (Free-choice conflict). Two events a and b are in *free-choice conflict* if they are in conflict and ES(a) = ES(b). In this situation the two events are always enabled or disabled simultaneously, which corresponds to a similar situation in Free-Choice nets.

**Definition 2.4** (Trigger events). Given two states  $s_1, s_2$  with  $s_1 \stackrel{a}{\longrightarrow} s_2 \in T$ , we say *a triggers* another event *b* iff *b* is enabled in  $s_2$ , but not in  $s_1$ . In a sense, *a* triggering *b* implies a causality relation between the two events. Analogously, we say *a disables b* iff *b* is enabled in  $s_1$ , but not in  $s_2$ .

**Definition 2.5** (Persistence). An event  $e \in \Sigma$  is *persistent* if no event  $f \neq e$  disables it.

A bounded Petri net can be transformed into an LTS by creating a state for every reachable marking in the net, and arcs according to the enabled Petri net transitions in each marking. Figure 2.4 shows the LTS associated to the Petri nets from Fig. 2.3. The opposite problem, however, is known as the *synthesis* problem [45,60], and is not as straightforward for most Petri nets types.

# 2.2.3 Conformance checking

An important set of techniques in process mining is *conformance checking*, which compare the observed (log) and modeled behavior in order to evaluate the model. There are four quality dimensions for comparing model and log: *replay fitness*, *simplicity*, *precision*, and *generalization* [2]. While the four dimensions are not entirely orthogonal, balancing them is an important aspect to produce high-quality models for real-life processes [30].

#### Replay fitness

The *replay fitness* of a model indicates how good the model can reproduce the behavior of the process as observed in the event log. A model has perfect replay fitness if all traces in the log can be replayed by the model from beginning to end. This may not be necessary in all scenarios, e.g., if the event log contain noise [7]. Still, fitness is considered the most important metric.

Several metrics for precision exist in the literature [31]. In this thesis we will use the definition provided by [10], which computes an optimal alignment between the log and trace before calculating the fitness score, providing a more fine-grained evaluation in the presence of small deviations.

#### **Simplicity**

The *simplicity* of a model evaluates how easy it is to analyze and understand it. The simplest model that can explain the behavior seen in the log is the best model, a principle known as Occam's Razor. On the other hand, complicated models, with a high number of elements and dense control flow structure, prevent the extraction of useful insight from process mining. These complicated models are often called *spaghetti models*, such as the one shown in Fig. 1.2.

Process discovery algorithms may derive spaghetti process models in various situations, e.g., when the log represents a complex process with hundreds of different event classes or when the log contains noise. Other problems like concept drift (the log contains the executions of different versions of the process model) or vertical event granularity (event classes from different hierarchies coexist in the log) may also cause the derivation of a dense process model. Unfortunately, the aforementioned situations happen often in real life [79]. Thus, the discovery of simple process models and the simplification of larger models is a significant challenge when presenting data obtained by process mining.

The most common methods to estimate the complexity of a process model involve the size of the model or the average degree of its vertices [108]. In this work, however, we propose the use of the crossing number of a graph as measure of complexity, a concept closely related to the planarity of a graph. For a formal definition, we refer to Section 2.1.1.

#### **Precision**

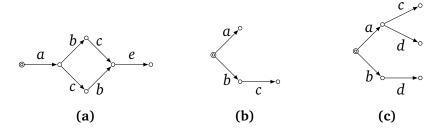

Fitness and simplicity alone are not sufficient to judge the quality of a discovered process model. For example, it is very easy to construct an extremely simple Petri net (*flower* model, as in Fig. 2.5a) that is able to replay all traces in an event log. However, this model also replays any other event log referring to the

Figure 2.5: Underfitting and overfitting Petri net examples.

same set of activities. Thus, the model is not useful for describing the behavior of an specific process.

*Precision* compares how much behavior is reproduced by the model that is not present in the log. A model is precise if it does not contain behavior that has not been observed in the log. A model that is not precise is *underfitting*, such as the flower model.

In this work, we use the metric proposed in [111], based on the concept of *escaping arcs*. A escaping arc represents a choice that is available in the model, but never taken while replaying the event log.

#### Generalization

On the other hand, event logs contain only observed behavior and many traces that are possible may not have been captured in the logs. Thus, it may be undesirable to have a model that only allows for the exact behavior seen in the event log.

In contrast to precision, a model should *generalize* and not restrict behavior to just the examples seen in the log. A model that does not generalize is *overfitting*. Overfitting is the problem that a very specific model is generated whereas it is obvious that the log only holds partial behavior. A good example is a *trace* model (as in Fig. 2.5b). The model may explain a particular sample log with very high precision, but there is a high probability that the model will be unable to explain the next batch of cases.

In this work we will generally use the metric provided in [30], which penalizes models where most parts are visited very infrequently when replaying the logs. If infrequently-visited parts are prevalent in the model, it is unlikely that new, slightly different traces will fit.

Finding a good balance between overfitting and underfitting models is one of the challenges in process mining [5].

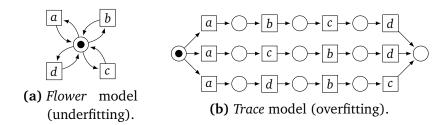

# 2.3 Very-Large-Scale Integration design flow

In this thesis, Chapters 3 and 4 focus on using graph mining during physical design of large-scale chip designs. This section provides a tour of the basic design flow of Very-Large-Scale Integration (VLSI) circuits to help understand the context of these chapters.

Modern chips are extremely huge and complex. In the present day, chip designs with billions of transistors are not uncommon (current commercial designs have well over 7 billion transistors [48]). These designs combine hundreds of cores, on-chip memories, routers, interconnects and many other components in a single chip, possibly pre-designed by third parties. Thus, many of the challenges found during the design of modern chips will revolve around managing this complexity.

Because of such complexity, the design process for any chip is partitioned in interrelated tasks, both in space (e.g. the different modules of the chip) and time (e.g. early core architecture design versus gate-level).

Hierarchy and abstraction are two concepts often used during VLSI design. Large systems are often partitioned into many structures that can be recursively partitioned into smaller, independent units. To save time, it is preferable to have many instances of the same module versus many different modules. Thus, the rise of the Chip multiprocessor (CMP), which allows the construction of highly performant machines at a fraction of the cost by replicating hundreds of pre-designed processing tiles.

Furthermore, different teams usually work concurrently on tasks that normally would be done sequentially. Dependencies between stages are lessened by the use of abstraction mechanisms (e.g., so that the designer of the core does not need to be involved into logic gate internals).

Even with these abstraction mechanisms, however, there are still times when the output of one stage is required as input of another stage. For example, the designer of the core microarchitecture needs to know the characteristics of the physical design, including clock speed, in order to properly create a pipelined architecture. Experienced engineers are required in this case in order to create *estimations* so that all the teams have something to start with. These estimations are refined continuously as the design process advances.

Current VLSI design flows usually split tasks into 4 big stages, each composed of many smaller stages. These are not fixed and it is common for the stages to be rearranged depending on the implementation of the design flow. An overview of the 4 stages [139] can be seen in Fig. 2.6, and in the following list:

1. Architectural design (also functional or black-box design), which is the first stage, involves deciding on the general (or system-level structure) of the

Figure 2.6: Summary of the main VLSI design flow stages.

chip. In the case of CMPs, this stage involves finding the promising configurations (combinations of different core architectures, on-chip memories, etc.) that satisfy the performance, cost and other requirements.

- 2. *Logic design* describes how the diverse components of a chip work. For a core, the behavior of the ALU, floating point, etc. is described.

- 3. *Circuit design* considers how to implement the logic design into an electronic circuit (selection of transistors, etc.)

- 4. *Physical design* layouts all required transistors and wires and thus determines the final geometry of the chip.

Each of these stages will be described in more detail in the following sections.

### 2.3.1 Architectural design

During architectural design the system-level structure of the chip is defined. A designer usually has a set of required metrics (desired performance, etc.) and a limited budget (in cost, chip area, power usage, etc.). In traditional CPU design, this involved deciding on parameters such as the length of the pipeline, the memory hierarchy, whether to use out-of-order execution, etc.

For example, in the case of CMP design, it is generally assumed that the designer has a library of components (cores, caches, etc.) at its disposal, and that he/she needs to decide which (and how many) of those components are to be placed on the CMP, and how to interconnect each of those components.

Because these components may have never been built yet, or have been manufactured before but using different physical parameters, there might be no real-world estimations of their parameters. Additionally, the high number of possible combinations and permutations of the components in the library often generates a design space with billions of possible configurations. For this reason, during architectural design fast estimators for each of the diverse component

metrics are necessary. Interpolation, analytical modeling or simulations are used, depending on the accuracy required. These methods will be discussed in Section 3.3.

#### 2.3.2 Logic design

At this stage, the required functionality is implemented in terms of boolean functions. The interfaces (inputs and outputs) for the different modules are also usually defined during this stage.

However, logic is not necessarily specified in terms of the traditionally used logic gates. This is because during physical design there is a step, technology mapping, in which, depending on the manufacturing technology used, there might be more efficient ways to convey boolean functions that by using the standard logic gates.

### 2.3.3 Circuit design

During circuit design, a electronic circuit is created from the previously created logic. Exactly at which level the circuit is designed depends on the manufacturing technology.

When using HDLs, this process is usually fully automated using a tool called *synthesizer*, which handles an HDL input and converts it to the required representation. The output is usually a list of logic gates and the connections or *nets* between them (a *netlist*). *Technology mapping* is the process by which the high-level logic gets mapped into lower-level elements such as *cells*.

# 2.3.4 Physical design

At the start of physical design, the design is represented in terms of a *netlist* including all low-level components (cells, gates, transistors, ...) with their shapes and the appropriate interconnections between those components. The result of physical design is a physical *layout*, including both the positions of each of the design components (the *placement*) as well as the paths for each of the interconnections (the *routing*).

From this stage and until the final circuit, limitations of the physical world are now taken into account. Depending on the implementation technology, *design rules* prohibit certain layouts. For example, by setting minimum distance between wires or forcing insertion of repeaters whenever wires exceed a certain maximum length [75].

Physical design is often split in the following sub-stages [86]:

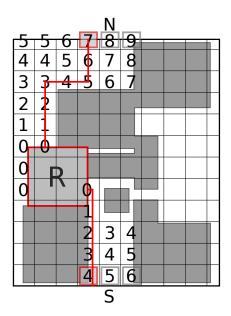

1. Floorplanning is often the first step during physical design. A floorplan provides an estimation of the shapes and locations of the major units in the circuit. For the case of CMPs, this usually confers the locations of the individual cores, memories, etc. In a hierarchic fashion, a single core might also have a floorplan containing the locations for the arithmetic and logic units, etc.

Because no physical information about the innards of the components is available at this early stage of physical design, floorplanning often uses area estimations as inputs. As more accurate estimations become available during later physical design stages, the floorplan is updated.

Additionally, creating a floorplan allows early estimations of the length of the largest nets. This is often called *wire planning*.

- 2. *Placement* defines the final locations for the individual low-level units (e.g. cells) inside each high-level block. Unlike floorplanning, regular structures such as grids are often considered because most of the cells have similar sizes or sizes in multiples of a common base unit.

- 3. *Clock tree synthesis*. In sequential circuits, keeping the propagation delay of the clock signal to a minimum is usually mandatory to avoid *clock skew*. Because of this importance and singularity, the clock signal is usually the first net to be routed.

- 4. *Global routing* estimates and reserves the required routing resources that are required by the interconnections. Usually, global routing considers only those nets that use the most resources. Each net is given a estimated width depending on the design rules and the number of wires composing it, but individual wires are not considered. These estimated paths reduce the search space for the detailed routing stage that will come next.

- 5. *Detailed routing*, on the other hand, calculates the final routes for each individual wire of the chip, at the same time verifying that the previously generated global routing is feasible.

- 6. *Timing analysis* checks that all of the design's timing constraints are satisfied. Different logic paths have different timing requirements, and during this process every factor that alters net delay is taken into account: length of wires, repeaters, transistor sizing, etc. If any of the constraints is not met, the design is reiterated, restructuring the layout of the critical paths. Thus, even the floorplan might need to be changed and the physical design process restarted.

In this thesis, Chapter 3 will center on the topic of physical design oriented towards CMPs, while Chapter 4 will expand the proposed methods towards general VLSI design.

# 2.4 Asynchronous circuits

One the focus of this thesis will be to propose the concept of specification mining for asynchronous controllers (Chapter 8). This chapter introduces the context of this contribution by providing an overview of asynchronous circuit design.

Asynchronous circuits are logic circuits that do not rely on a global synchronization signal, the clock, to dictate when signals are sampled. Instead of clocks, asynchronous circuits favor *handshaking* to synchronize the different components in a circuit. Asynchronous logic offers many advantages [46], among them: increased performance, reduced power consumption, and better composability and modularity.

While early computers were mostly asynchronous, the prevalence of asynchronous design today has significantly decreased in favor of synchronous design and global clocks. In part, this is because of the complexity usually associated with the design of asynchronous circuits. There are few asynchronous design tools in comparison with the huge amount of well-entrenched synchronous tools.

In asynchronous circuits two main parts are often distinguished: the *data path* and the *control*. While the former comprises wide units performing arithmetic or other types of transformations on the data processed by the circuit, the control unit determines and generates the diverse control signals that will configure the data path units. As control manages the synchronization requirements, this thesis will exclusively focus on the analysis of control circuits.

We define a circuit *C* as a tuple  $C = \langle X, G, s_0 \rangle$  where:

- $X = I \cup O \cup Z$  is the set of signals, with I, O and Z being pairwise disjoint sets that represent the input, output and internal signals of the circuit, respectively.

- $G: (O \cup Z) \to f(X)$  is a set of gates that assigns a Boolean function to each non-input signal of the circuit. We denote by  $f_{x_i}(X)$  the Boolean function assigned to signal  $x_i$ .

- *s*<sub>0</sub> is a binary vector representing the value of the signals at the initial state.

The *environment* of a circuit reacts to the outputs from the circuit and sends new inputs to it.

#### 2.4.1 Operating modes and delay models

A *hazard* is a deviation from the expected behavior of a circuit caused by the delay present in real-word gates and wires. Hazards are one of the main challenges during asynchronous circuit design. To help manage the complexity associated with asynchronous circuits, several design styles have been developed. Within each style, different models and assumptions are made about the timing and behavior of physical elements of the circuit: gates, wires, and the environment.

This section overviews some of the common styles. Broadly, we distinguish between *delay models*, i.e. assumptions about the operating delays of gates and wires, and *operating modes*, models about the interaction between a circuit and its environment. For an exhaustive analysis into the design of asynchronous circuits, we refer the reader to existing documentation [17,46].

#### **Operating modes**

Operating modes model the interaction between the circuit and its environment. In *fundamental mode* [77], inputs from the environment are constrained to change only when all the outputs are stable, i.e., the environment allows the circuit to stabilize before generating new inputs.

*Burst mode* [53] is a related operating mode in which a burst of multiple sequential input changes are allowed. However, when all inputs in the burst have changed, the environment must wait for the circuit to stabilize before starting a new burst.

Compare with *input-output mode* [110], in which new inputs may occur at any time, as part of specified responses to changes in the outputs. Thus, input and output changes may be concurrent.

#### **Delay models**

The delay model defines the assumptions made, during the design, about delays in gates and wires. Strong assumptions may simplify the design flow, while less strict ones generally lead to designs that are more robust to manufacturing process variations. In this section we describe some of the common models.

• In the *bounded delay* model, delays of both gates and wires are assumed to be lying within given minimum and maximum bounds. The circuit is guaranteed to work correctly if these bounds are satisfied. While this may lead to smaller circuits, extensive analysis is needed to ensure all bounds are met in all conditions.

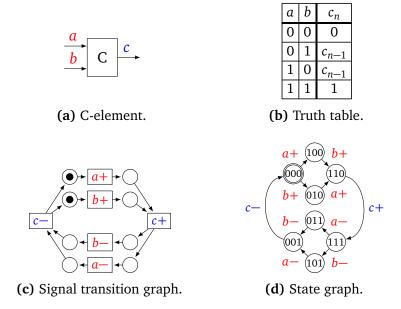

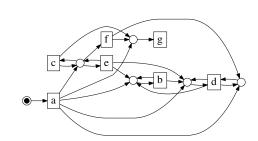

**Figure 2.7:** C-element and specifications.

- A *speed-independent* (SI) circuit works correctly even in the presence of arbitrary but finite delay on its gates. However, it works with the assumption that wires, on the other hand, are ideal, i.e., with zero delay [110].

- A circuit is *delay-insensitive* (DI) when its correct operation does not depend on neither the delays in the gates nor the wires. While this is an extremely interesting class of circuits because of its robustness, unfortunately it has been proven that very few circuits can truly be made delay insensitive [106, 121].

- *Delay-insensitive interfacing* proposes that only inputs to the circuit are required to be handled in a delay-insensitive fashion. This is a compromise in order to alleviate the impracticality of DI circuits while still allowing long interconnects. The assumption is that even if it is not practical to assume that long wires have zero delay, a designer may still keep control on the delays of short internal wires [121].

# 2.4.2 Signal transition graphs

The most common design methodologies for asynchronous controllers involve first specifying the behavior of the circuit and the necessary requirements from the environment. From these specifications, automated tools generate hazard-free implementations of the circuits [46].

Asynchronous circuits are intrinsically concurrent, and thus naturally suited to Petri nets (Section 2.2.1), one of the most powerful formalisms for reasoning about concurrent systems. A *Signal Transition Graph* (STG) is formal model based on Petri nets for conveying the behavior of an asynchronous circuit.

Given a circuit  $C = \langle X, G, s_0 \rangle$ , a Signal Transition Graph is a labeled Petri net  $N = \langle P, \Sigma, T, \mathcal{L}, \mathcal{F}, m_0 \rangle$  in which  $\Sigma = X \times \{+, -\} \cup \tau$ . Thus, each transition label corresponds to either the transition (rising or falling) from a signal of C, or a silent event  $\tau$  that does not change the state of the circuit. By  $x^+$  and  $x^-$ , we will distinguish the rising and falling transitions of signal  $x \in X$  respectively.

Figure 2.7c shows an example STG of a *C-element*, one of the fundamental components in asynchronous circuits, whose truth table is depicted in Fig. 2.7b. The C-element is a stateful element that sets its output to 0 when both inputs are 0, and to 1 when both inputs are set to 1. In any other input combination, the output does not change.

# 2.4.3 State graphs

An STG is just a succinct representation of (a part of) the behavior of the circuit, which focuses on the causality relations amongst events. An *state graph* also represents the behavior of the circuit by enumerating all of its possible states and transitions between states as a Labeled Transition System (LTS). While this may result in a much larger representation than an STG, many algorithms require exhaustive explorations of the state space. For the full definition of an LTS, we refer to Section 2.2.2.

Given a circuit  $C = \langle X, G, s_0 \rangle$ , an state graph of C is an LTS  $A = \langle S, \Sigma, T, s_0 \rangle$  in which:

- $S = \{0, 1\}^n$ , with n = |X|, the set of binary vectors representing all possible states of the signals.

- $\Sigma = X \times \{+, -\}$ , i.e. the set of signals of the circuit plus the direction of the transition.

- $T = \{s_1 \xrightarrow{x} s_2\}$  with  $s_1, s_2 \in S$  and  $x \in \Sigma$ , is the set of transitions.

- The initial state  $s_0$  coincides with the initial state of the circuit.

Given a state  $s=(x_1,\ldots,x_n)$ , we denote by  $s(x_i)$  the value of signal  $x_i$  in s. Given a state  $s=(x_1,\ldots,x_i,\ldots,x_n)$ , we denote by  $s^{\neg x_i}=(x_1,\ldots,\neg x_i,\ldots,x_n)$  the state in which the values of the signals are identical to the ones of s except for  $x_i$ , that has the complementary value. Notice thus that for each  $s_1 \xrightarrow{x} s_2 \in T$ ,  $s_2 = s_1^{\neg x}$  and  $s_1 = s_2^{\neg x}$ .

Figure 2.7d shows an example of the state graph associated to the behavior of the C-element described by the STG in Fig. 2.7c.

# 2.5 Mathematical optimization

Many of the methods described in this thesis involve optimization problems. This section provides a brief introduction to two commonly used subfields of mathematical optimization, albeit it is not indented to cover the finer details. The approaches described in this section will be frequently used in this thesis when encoding, e.g., desired structural constraints in graphs.

An optimization problem involves finding the *best* solution out of a set of feasible solutions. The search space of feasible solutions is delimited by a set of constraints, such as formulas, inequalities, etc. Generally, the best solution is that which maximizes (or minimizes) the *value*, usually defined as a real function.

# 2.5.1 Boolean satisfiability

A *formula P* is a combination of boolean variables (denoted by p, q, ...) built using the 3 logical operators and, or, not (represented respectively by  $\land$ ,  $\lor and \lnot$ ). An *interpretation I* of *P* is an assignment of  $\{0,1\}$  to each variable in *P*. *I* satisfies *P* iff the evaluation of *P* under *I* is 1. *P* is satisfiable if it is satisfied by at least one interpretation. Generally, formulas are written as conjunctions of *clauses*, which are disjunctions of (possibly negated) variables.

Satisfiability (SAT) is the problem of determining, given a formula P, whether there is an interpretation I that satisfies it. SAT is a well-known NP-complete problem, with all known algorithms having worst-case exponential cost on the size of P [24].

The *maximum satisfiability problem* (MaxSAT) is the optimization version of SAT. Given an formula *P*, MaxSAT involves finding an interpretation that maximizes the number of clauses that evaluate to 1. Inversely, the *minimum satisfiability problem* (MinSAT) finds satisfying interpretations that minimize the number of clauses that evaluate to 1. As typical extensions, weights can be added to individual clauses, allowing for arbitrarily complicated optimization goals [24]. MaxSAT and MinSAT are heavily used as a natural way to model many optimization problems.

# 2.5.2 Linear programming

A linear inequality  $a \cdot x \le b$  is defined by a vector  $a \in \mathbb{R}^n$  and a constant  $b \in \mathbb{R}$ . A *linear programming problem* (LP) is a set of linear inequalities plus a linear function that needs to be maximized, called the *objective function*. It is usually represented as:

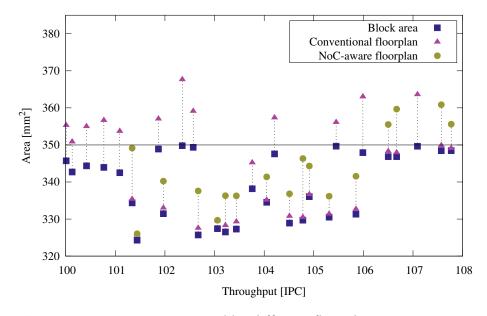

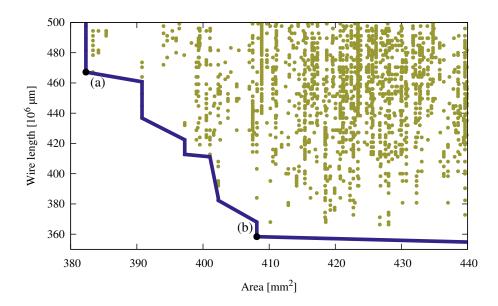

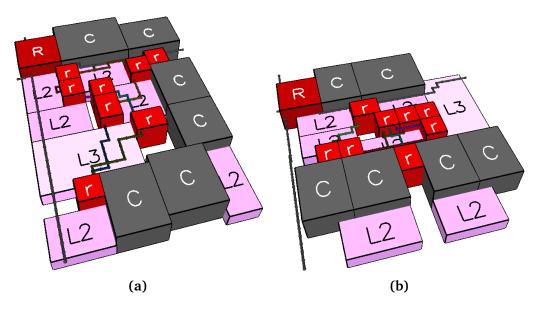

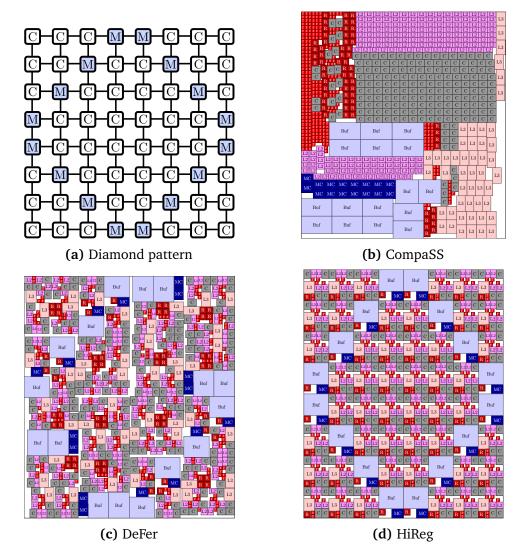

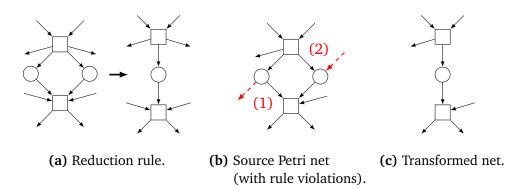

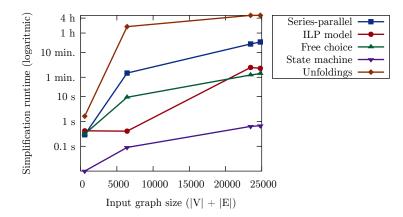

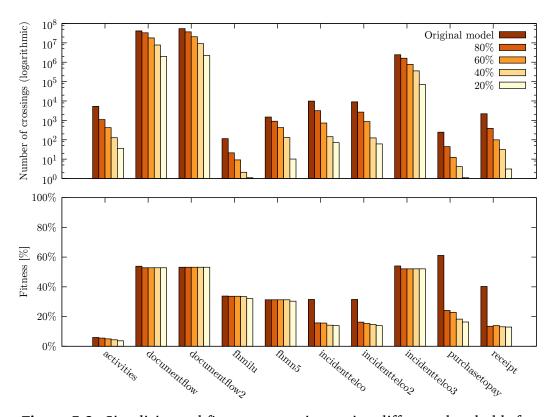

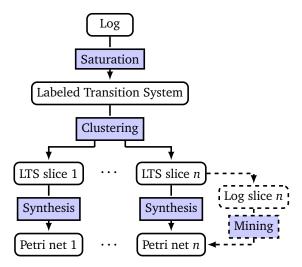

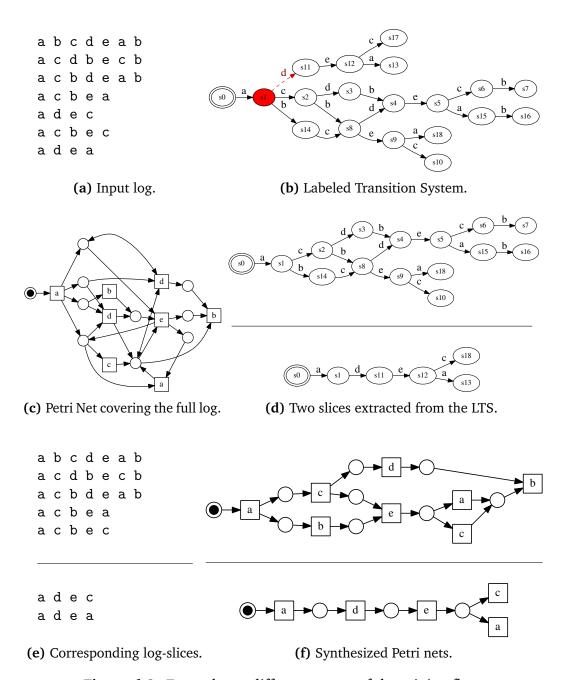

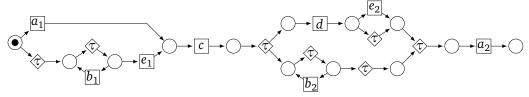

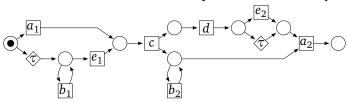

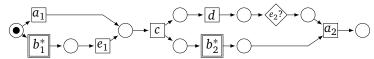

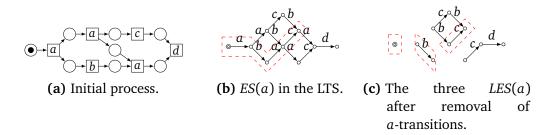

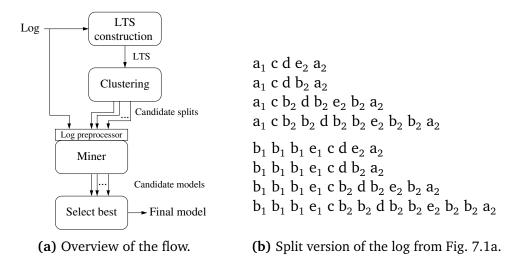

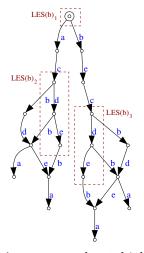

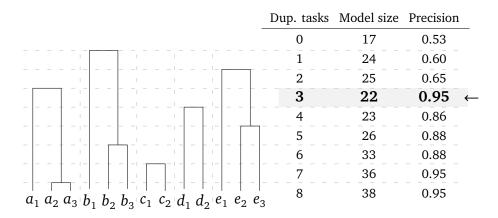

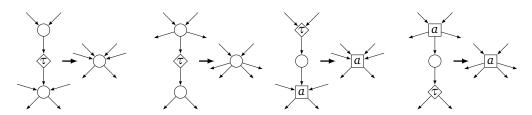

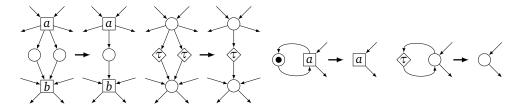

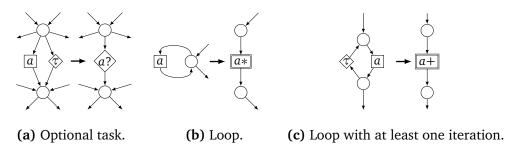

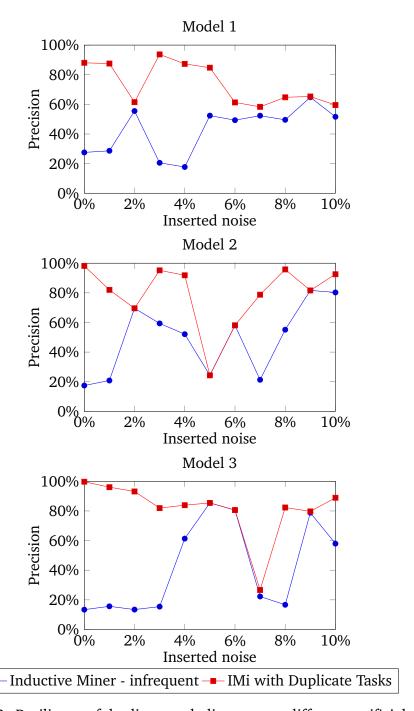

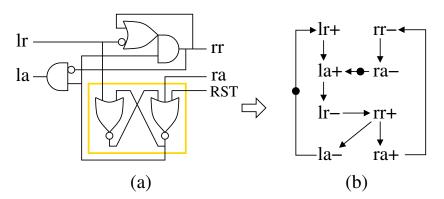

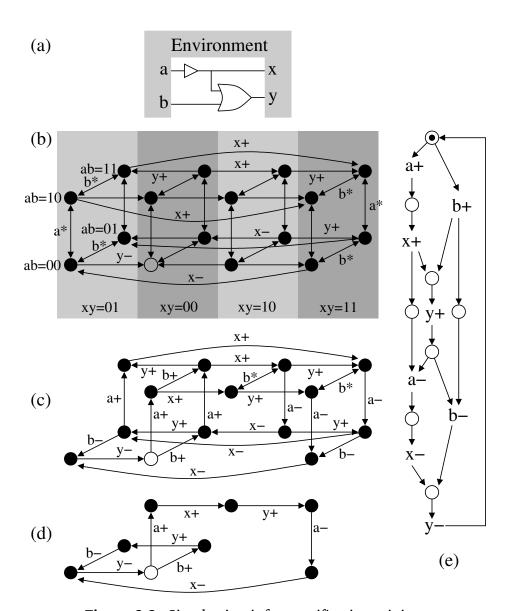

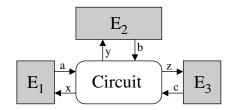

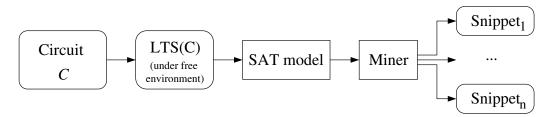

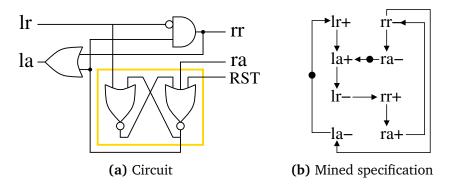

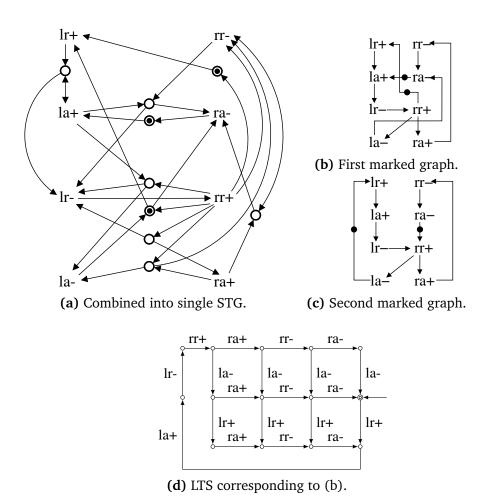

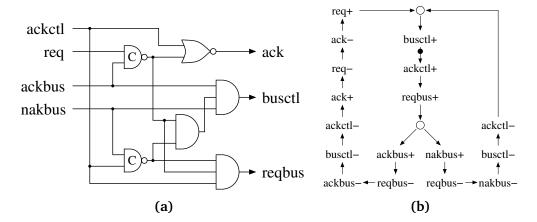

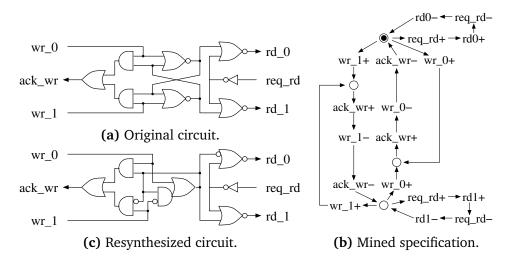

$maximize c^T \cdot x$  $subject to A \cdot x \le b$