# Design exploration and measurement benchmark of integrated-circuits based on graphene field-effect-transistors: towards wireless nanotransceivers

## Mario Enrique Iannazzo Soteras

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del repositori institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) i el repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (\*framing\*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="https://raming/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing/framing

WARNING On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the institutional repository UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) and the cooperative repository TDX (<a href="http://www.tdx.cat/?locale-attribute=en">http://www.tdx.cat/?locale-attribute=en</a>) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# Design Exploration and Measurement Benchmark of Integrated-Circuits based on Graphene Field-Effect-Transistors: Towards Wireless Nanotransceivers

Thesis submitted in partial fulfilment of the requirement for the PhD Degree issued by the Universitat Politècnica de Catalunya, in its Electronic Engineering Program.

By

Mario Enrique Iannazzo Soteras

Advisors:

Prof. Eduard Alarcón Cot

Scientific Co-director, N3Cat Head of the EPIC Group, DEE, UPC BarcelonaTech Spain

Prof. Max Christian Lemme

Chair for Electronic Devices, RWTH Aachen University

Director, AMO GmbH

Germany

July 2017

| To my parents and friends, thanks for your endless support and love                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| To Eva Pradas (1973-2017)                                                                                                                                    |

| To Eduard and Max, thanks for this unique opportunity                                                                                                        |

|                                                                                                                                                              |

| It is perfectly true, as the philosophers say, that life must be understood backwards. But they forget the other proposition, that it must be lived forwards |

| Søren Kierkegaard                                                                                                                                            |

|                                                                                                                                                              |

| Never let schooling interfere with your education                                                                                                            |

| Grant Allen                                                                                                                                                  |

|                                                                                                                                                              |

|                                                                                                                                                              |

## **English Abstract**

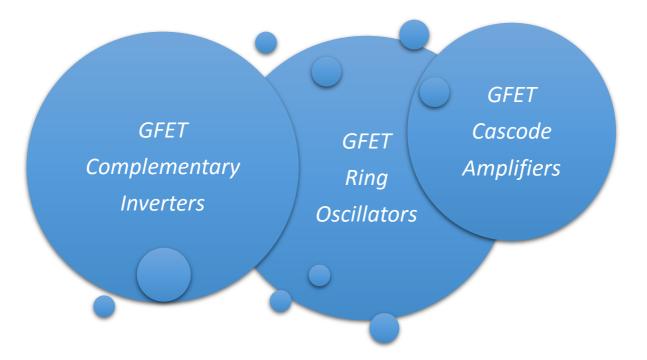

This doctoral thesis approaches the design requirements for future high / ultrahigh data rate (from 100 Mbps to 100 Gbps) nanotransceivers (nanoTRx) applied to wireless nanonetworks which imply short/ultra-short distance ranges (3 cm - 3 m). It explores graphene field-effect-transistors (GFET), by simulation against measurement benchmarks, as a potential solution for implementing large-signal high-frequency circuits, by virtue of graphene's one-atom thickness and high carrier-mobility extraordinary properties. Finally, the thesis discusses the challenges faced by GFETs, such as zero-bandgap and high metal-graphene contact-resistance, to be able to propose improvements for achieving the initial proposed goals. Chemical-Vapour-Deposition (CVD) GFET fabrication is considered, which is very promising for large-scale manufacturing (CMOS process compatible), and for that fast-computing large-signal compact modeling for complex circuit design is analysed in depth and optimized, and consequently a set of diverse large-signal static and dynamic GFET circuits are simulated and benchmarked against available measurements assessing the accuracy of the proposed models and deriving scaling prospects. An optimization of the current-tovoltage (I-V) characteristic of a GFET compact model, based upon drift-diffusion carrier transport, is presented. The improved accuracy at the Dirac point extends the model usability for GFETs when scaling parameters such as voltage supply  $(V_{dd})$ , gate length (L), dielectric thickness ( $t_{ox}$ ) and carrier mobility ( $\mu$ ) for large-signal design exploration in circuits. The model accuracy is demonstrated through parameters fitting to measurements taken from CVD GFETs fabricated in the University of Siegen and Technical University of Milan. The script has been written in a standard behavioural language (Verilog-A), and extensively run in a commercial analog circuit simulator (Cadence environment) demonstrating its robustness. Besides a simple capacitance-tovoltage model (C-V), a small-signal parasitic capacitance model fitted to dynamic measurements for self-aligned CVD GFETs available in the literature is added, enabling to forecast maximum-frequency-of-oscillation (f<sub>max</sub>) trends for future scaling. A designoriented characterization of complementary inverter circuits (INV) based on GFETs is presented as well. Our proposed compact model is benchmarked at the circuit level against another compact model based on a virtual-source approach. Furthermore, a benchmark between simulations and measurements of already fabricated CVD GFET INVs is performed, and performance trends when scaling are derived. The same process is repeated for a more complex circuit, namely GFET ring-oscillators (RO). The transient regime simulations yield performance metrics in terms of oscillation frequency (fosc) and dynamic voltage range ( $\Delta V_{osc}$ ), and consequently, against these metrics, a comprehensive design space exploration covering as input design variables parameters as tox, L, and Vdd is carried out. Being aware of the lack of voltage amplification shown by existing GFETs, the design exploration of a cascode amplifier (CAS) targeted to increase voltage gain (A<sub>v</sub>) by decreasing its output conductance (g<sub>o</sub>) is presented. GFET CAS are simulated to provide design guidelines, they are accordingly fabricated and consequently measured. Performance metrics are provided in terms of go, transconductance (g<sub>m</sub>) and hence A<sub>v</sub>. Against these metrics, a quantitative comparison between CAS and GFETs is performed and conclusions are derived. Finally, conclusions on GFETs suitability for future nanoTRX are elaborated. The derived publications come from international collaborations with the Royal Institute of Technology (KTH) in Sweden from 2012 to 2014, and the University of Siegen in Germany from 2014 to 2016.

## Resumen en Español

Esta tesis doctoral trata de identificar los requisitos de diseño para nanotransceptores (nanoTRx) para datos de alta velocidad (de 100 Mbps a 100 Gbps) aplicados a nano-redes inalámbricas que implican rangos de alcance cortos u ultracortos (3 cm - 3 m ). Se exploran transistores de efecto de campo basados en grafeno (GFET), mediante simulaciones y mediciones, como una solución potencial para la implementación de circuitos de alta frecuencia de gran señal, gracias a las extraordinarias propiedades del grafeno como son su espesor de un solo átomo y sus portadores de alta movilidad. Finalmente, se discuten los desafíos a los que se enfrentan los GFETs, como la falta de banda prohibida y la alta resistencia del contacto entre metal y grafeno, para lograr proponer alternativas y poder alcanzar los objetivos iniciales propuestos. Se introducen la técnica CVD como un proceso de fabricación de GFETs a gran escala, compatible con tecnología CMOS. Se introduce el modelado compacto de gran señal y computación veloz para el diseño de circuitos complejos, que es optimizado y analizado en profundidad, y consecuentemente se proponen diversos circuitos de gran señal (estáticos y dinámicos) basados en GFET, que son simulados y comparados con las mediciones disponibles para evaluar la precisión de los modelos propuestos y derivar prospecciones de escalado. Se propone una optimización de la característica corrientevoltaje (I-V) de un modelo compacto GFET basado en el transporte de portadores difusión-deriva. La precisión mejorada en el punto de Dirac extiende la usabilidad del modelo para GFETs cuando se dimensionan parámetros para la exploración en diseños de circuitos de gran señal, tales como el voltaje de alimentación (V<sub>dd</sub>), la longitud de puerta (L), el espesor dieléctrico (t<sub>ox</sub>) y la movilidad de portadores (μ). La precisión del modelo se demuestra a través de parámetros que se ajustan a mediciones tomadas a partir de CVD GFETs fabricados en la universidad de Siegen y en la universidad politécnica de Milán. El programa se ha escrito en un lenguaje estándar (Verilog-A) y se ejecuta extensivamente en un simulador de circuitos analógico comercial (entorno Cadence) donde se demuestra su robustez. Además, se lleva a cabo la parametrización de un modelo capacidad-voltaje (C-V) añadiendo un modelo de capacidades parásitas de pequeña señal que son ajustados a las mediciones de alta frecuencia de CVD GFETs disponibles en la literatura científica, lo que permite la predicción de la frecuencia máxima de oscilación (f<sub>max</sub>) para el escalado de futuros GFETs. También se presenta una caracterización orientada al diseño de circuitos inversores (INV) basados en GFETs. Nuestro modelo compacto propuesto se compara a nivel de circuito con otro modelo compacto basado en un enfoque diferente (fuente-virtual). A continuación, se lleva a cabo una comparación a nivel de circuito entre las simulaciones y las medidas de INVs ya fabricados basados en CVD GFET, y se obtienen las tendencias de comportamiento al escalarlos. Se repite el mismo proceso para un circuito más complejo, los llamados osciladores-en-anillo GFET (RO). Las simulaciones basadas en transitorios producen métricas de rendimiento en términos de frecuencia de oscilación (fosc) y rango dinámico de voltaje (ΔV<sub>OSC</sub>), por lo tanto, contra estas métricas, se lleva a cabo una exploración exhaustiva de diseño que abarca parámetros de variables de diseño como tox, L y Vdd. Al ser conscientes de la falta de amplificación de voltaje mostrada por los GFETs existentes, se presenta la exploración del espacio de diseño de un amplificador cascodo (CAS) diseñado para incrementar la amplificación de voltaje (A<sub>v</sub>) disminuyendo su conductancia de salida ( $g_o$ ). Los GFET CAS son simulados para proporcionar guías de diseño, luego fabricados y finalmente medidos. Se proporcionan métricas de rendimiento en términos de  $g_o$ , transconductancia ( $g_m$ ), y consecuentemente Av. Frente a estas métricas, se realiza una comparación cuantitativa entre CAS y GFETs y se derivan las conclusiones. Finalmente, se elaboran las conclusiones sobre la idoneidad de los GFET para futuros nanoTRx. Las publicaciones derivadas provienen de colaboraciones internacionales con el Instituto Real de Tecnología (KTH) en Suecia de 2012 a 2014, y la Universidad de Siegen en Alemania de 2014 a 2016.

## Thesis Partially Funded by

## **European Comission =>**

- Specific Targeted Research Project, GRADE (*Grant Nº317839*): Graphene-Based Devices and Circuits for Radio Frequency Applications

- European Research Council, InteGraDe (Starting Grant N°307311): Integrating Graphene Devices

## Deutsche Forschungsgemeinschaft =>

• LE 2440/1-1 und LE 2440/2-1: Skalierung und Performancepotential von Bilagengraphen Feldeffekttransistoren für Analoganwendungen

## Ministerio de Economía, Industria y Competitividad de España =>

- Programa Consolider-Ingenio, CSD2009-00046 Proyecto: Dispositivos Semiconductores Avanzados de Band-Gap Ancho para el Uso Racional de la Energía

- Programa Estatal de Investigación, Desarrollo e Innovación Orientada a los Retos de la Sociedad, Proyecto DPI2013-47799-C2-2-R: Transferencia de Energía Inalámbrica - Acoplamiento Inductivo Resonante

- Subprograma de Proyectos de Investigación Fundamental no Orientada,

Proyecto TEC2010-15765: Circuitos de Gestión de Energía Adaptativos y

Miniaturizados para Recolectores de Energía en Redes de Sensores Inalámbricos

## Acknowledgements

# At Department of Electronic Engineering *DEE*, Technical University of Catalonia *UPC*, Barcelona, Spain =>

Valerio Lo Muzzo, Santiago Pérez, Mohamed Saad, David Cavalheiro and Prof. Alberto Poveda

# At Nano-Networking Center in Catalonia Center *N3CAT*, Technical University of Catalonia *UPC*, Barcelona, Spain =>

Dr. Sergi Abadal, Dr. Raúl Gómez, Dr. Ignacio Llátser, Albert Mestres, Prof. Albert Cabellos-Aparicio and Prof. Josep Solé-Pareta

# At Remote Sensing Laboratory, Technical University of Catalonia, Barcelona *UPC*, Spain =>

Elisenda Bou-Balust, Carles Araguz, Alberto Saez, Adrià Amézaga, and Prof. Adriano Camps

# At Graphene based Technology Group *GNT*, University of Siegen, North Rhine-Westphalia, Germany =>

Himadri Pandey, Dr. Vikram Passi, Amit Gahoi, Daniel S. Schneider, Melkamu Belete, Jasper Ruhkopf, Stefan Wagner, Dr. Satender Kataria and Dr. Andreas Bablich

# At School of Information and Communication Technology, Royal Institute of Technology KTH, Stockholm, Sweden =>

Prof. Saúl Rodríguez, Dr. Anderson David Smith, Dr. Sam Vaziri, and Prof. Ana Rusu

# At Institute of Electronics, Microelectronics and Nanotechnology, University of Lille *IEMN*, Nord-Pas-de-Calais, France =>

Prof. Henri Happy, Dr. Emiliano Pallechi and Vanessa Abramovic

# At Department of Electronic Engineering, Autonomous University of Barcelona *UAB*, Catalonia, Spain =>

Francisco Pasadas and Prof. David Jiménez

# At Department of Electronic and Computer Technology, University of Granada, Andalusia, Spain =>

Prof. Francisco J. García Ruiz

## At Barcelona Supercomputing Center BSC, Catalonia, Spain =>

Prof. Mario Nemirovsky

## At Interuniversity Center Como, Technical University of Milan, Italy =>

Prof. Roman Sordan

## List of Figures

| Figure 1.1 (a) Global mobile devices and connections growth. (b) Global machine-to-machine growth an                                                         |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| migration from 2G to 3G and 4G [5] 1                                                                                                                         |     |

| Figure 1.2 An indoor-location tag: DWM1000 module is based on a 90 nm CMOS IC TRx, integrated with                                                           |     |

| a dielectric-chip antenna, DC/DC converter and xOSC on-board. Edited figure from [10] 1                                                                      |     |

| Figure 1.3 Nanomachine modules. First prototypes are envisioned beyond 2030. The scope of this thesis                                                        |     |

| is the nanoTRx module                                                                                                                                        |     |

| Figure 1.4 Wireless nanomedia / nanosensor networks [18] 1                                                                                                   | 18  |

| Figure 1.5 Wireless network-on-chip schematic [20]1                                                                                                          | 19  |

| Figure 1.6 Power consumption versus data rate for the communication module of different wireless                                                             |     |

| networks. The blue boxes are the targeted requirements. Edited figure from [21]                                                                              | 20  |

| Figure 2.1 Diagram of the nanoTRx modules integrated on a common substrate. The target of this thesis                                                        | s   |

| is the RF FE                                                                                                                                                 |     |

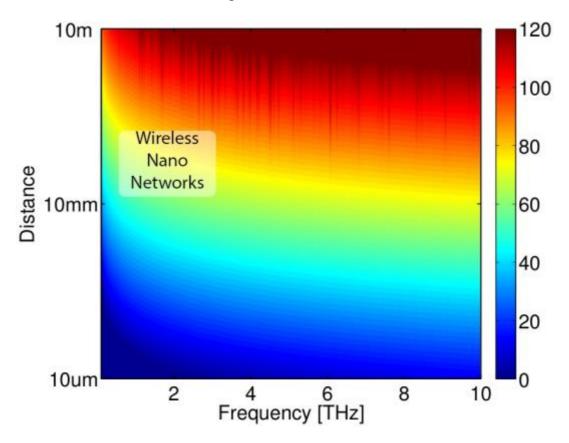

| Figure 2.2 Total path-loss in dB as a function of frequency & distance for our targeted WNNs. Edited                                                         |     |

| figure from [18]                                                                                                                                             | 28  |

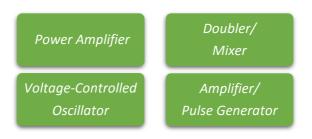

| Figure 2.3 Diagram of the IR/UWB Rx-FE main modules integrated on a common substrate                                                                         |     |

| Figure 2.4 Diagram of the IR/UWB FE-Tx main modules integrated on a common substrate 3                                                                       |     |

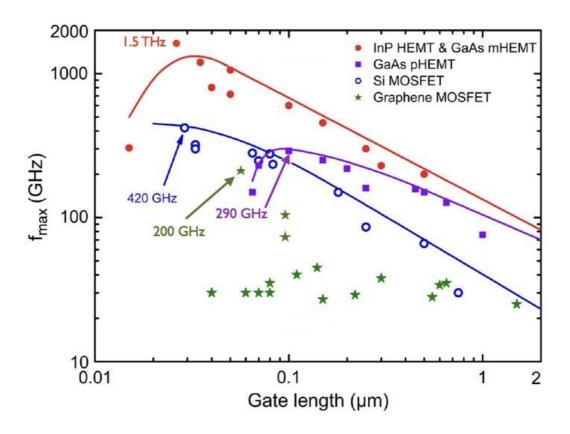

| Figure 2.5 $f_{MAX}$ (L) for different types of transistors: InP and GaAs HEMTs, MOSFETs, and graphene FETs.                                                 |     |

| Edited from [47]                                                                                                                                             |     |

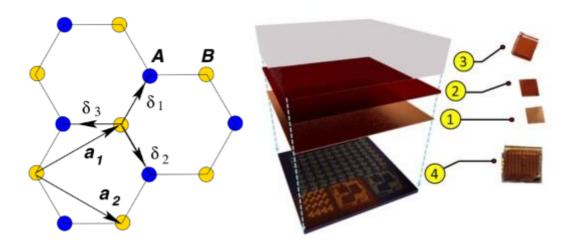

| Figure 3.1 (a) Graphene is made of carbon atoms arranged in hexagonal structure, made out of two                                                             | , 1 |

|                                                                                                                                                              |     |

| interpenetrating triangular lattices ( $a_1$ , $a_2$ are the lattice unit vectors, and $\partial_1$ , $\partial_2$ , $\partial_3$ are the nearest            |     |

| neighbour vectors) [56]. (b) Process flow for the dry transfer of graphene using both a polymer layer as                                                     |     |

| well as a photoresist layer [58]                                                                                                                             |     |

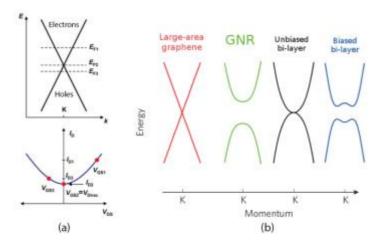

| Figure 3.2 Graphene bandgap. (a) GFET ambipolar conduction, where $E_f$ is the Fermi energy level, $I_d$ is the figure 3.2 Graphene bandgap.                 | ıe  |

| drain-to-source current, and $V_{gs}$ is the gate to source voltage. (b) Different graphene band structures.                                                 | _   |

| Edited from [47].                                                                                                                                            | 37  |

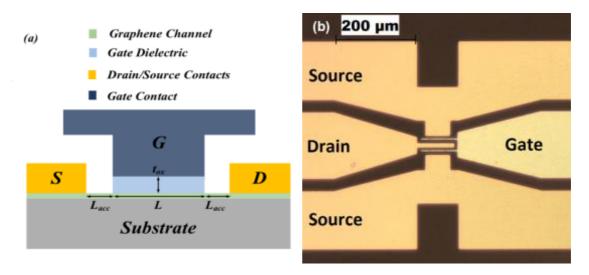

| Figure 3.3 GFET device. (a) Cross-section layout. (b) Top-section optical image of a device processed in                                                     |     |

| University of Siegen3                                                                                                                                        | 38  |

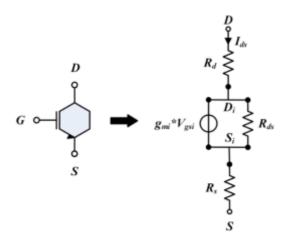

| Figure 3.4 GFET symbol and I-V compact model, including extrinsic parasitics ( $R_s$ and $R_d$ ) modeling                                                    |     |

| graphene-metal contact and non-gated graphene resistances4                                                                                                   | 14  |

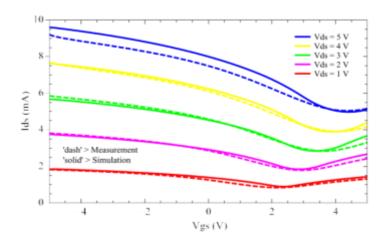

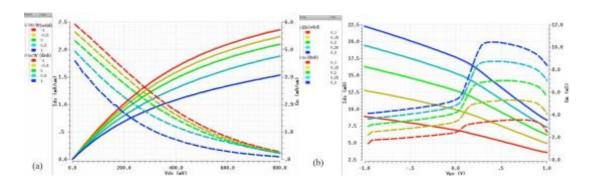

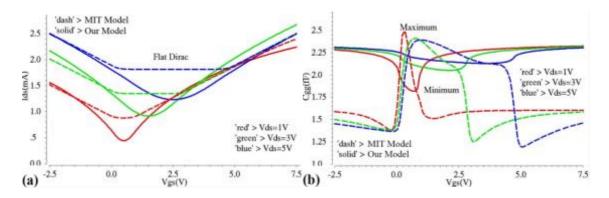

| Figure 3.5 $I_{ds}$ ( $V_{gs}$ ) for selected $V_{ds}$ . Our model proposal (solid) has been fitted to the data (dash)                                       |     |

| measured from a CVD GFET fabricated in University of Siegen. The device dimensions are: $W$ = 40 $\mu$ m, $L$                                                |     |

| 4 μm, and t <sub>OX</sub> = 20 nm                                                                                                                            | 17  |

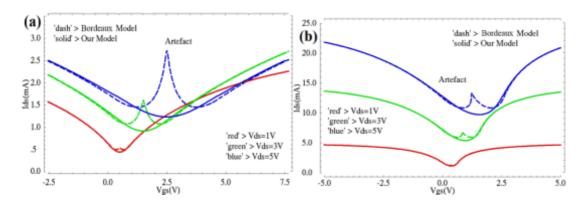

| Figure 3.6 GFET I <sub>ds</sub> (V <sub>gs</sub> ) for selected V <sub>ds</sub> . A comparison between Bordeaux model (dash-lines) and our                   |     |

| model proposal (solid-lines). (a) Fitted to an exfoliated GFET with $W=1~\mu m$ , $L=440~nm$ , and $t_{OX}=8.5$                                              |     |

| nm. (b) Fitted to an epitaxial GFET with $W$ = 4 $\mu$ m, $L$ = 294 nm, and $t_{OX}$ = 28 nm                                                                 | 18  |

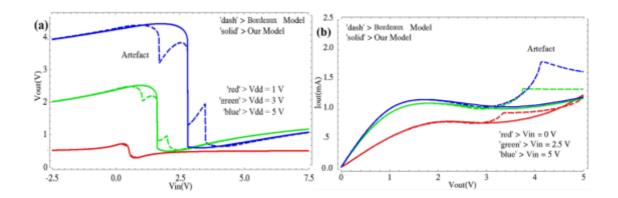

| Figure 3.7. Circuit-level comparison between Bordeaux model (dash lines) and our model proposal (solid                                                       | d   |

| lines). (a) INV $V_{out}(V_{in})$ for selected $V_{dd}$ . (b) CAS $I_{out}(V_{out})$ for selected $V_{in}$ with $V_{bias} = 2.5 \text{ V}$ . Model fitted to | )   |

| an exfoliated GFET with W = 1 $\mu$ m, L = 440 nm, and $t_{OX}$ = 8.5 nm                                                                                     | 19  |

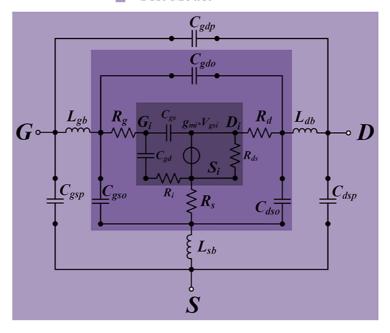

| Figure 3.8 GFET model (I/V + $C/V$ ) where the intrinsic model is based on our large-signal drift-diffusion                                                  |     |

| model, the extrinsic model is based on lumped components which scale with size, and the test model is                                                        |     |

| based on lumped components that do not scale5                                                                                                                | 51  |

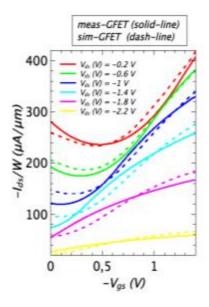

| Figure 3.9 $I_{ds}/W$ ( $V_{qs}$ ) for selected $V_{ds}$ . Parameter model fitting between a measured CVD GFET with                                          |     |

| alumina top-gate (solid-line) and our simulated GFET model (dash-line). The GFET dimensions are: W =                                                         |     |

| 10 μm, L = 2 μm, t <sub>OX</sub> = 4 nm                                                                                                                      | 52  |

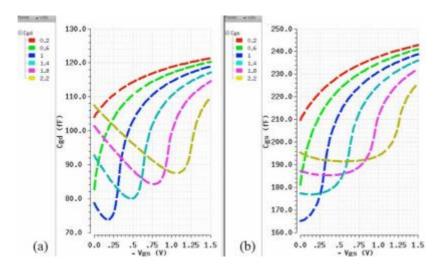

| Figure 3.10 Simulated GFET capacitances against voltage. (a) $C_{qd}$ ( $V_{qs}$ ) for selected $V_{ds}$ . (b) $C_{qs}$ ( $V_{qs}$ ) for                     | _   |

| selected $V_{ds}$ . Model fitted to a measured CVD GFET with alumina top-gate and W = 10 $\mu$ m, L = 2 $\mu$ m, $t_{OX}$                                    | =   |

| 4 nm                                                                                                                                                         |     |

| Figure 3.11 GFET DC simulations (a) $I_{ds}/W$ ( $V_{ds}$ ) (solid-line) and $g_o/W$ ( $V_{ds}$ ) (dash-line) for selected $V_{qs}$ . (b)                    |     |

| $I_{ds}$ ( $V_{qs}$ ) and $g_m$ ( $V_{qs}$ ) for selected $V_{ds}$ . Model fitted to the measurements of a self-aligned CVD GFET with                        |     |

| $W = 2 \times 10 \mu\text{m}$ , $L = 60 \text{nm}$ , $t_{OX} = 10 \text{nm}$                                                                                 | :2  |

| Figure 3.12 GFET S-parameters simulation setup.                                                                                                              |     |

| . 1941 C 3.12                                                                                                                                                | , — |

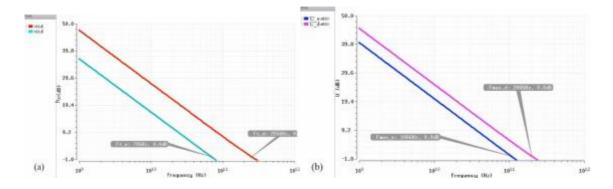

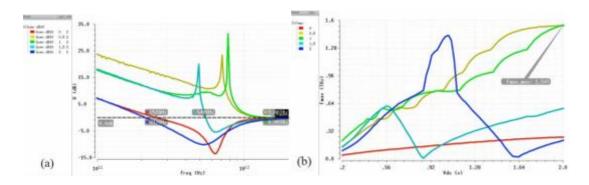

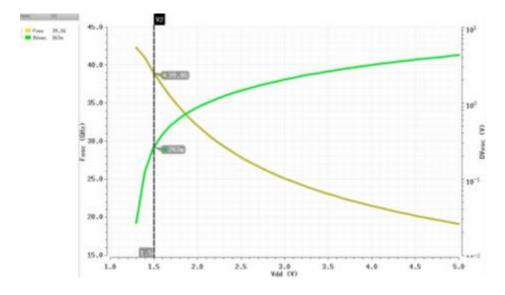

| Figure 3.13 $f_T$ and $f_{MAX}$ simulations. (a) Embedded (light blue) $h_{21e}$ (f) and de-embedded (red) $h_{21d}$ (f). (b)                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Embedded (blue) $U_e$ (f) and de-embedded (violet) $U_d$ (f). Model fitted to the measurements of a selfaligned CVD GFET with $W=2 \times 10 \ \mu m$ , $L=60 \ nm$ , $t_{OX}=10 \ nm$ 54                                                           |

| Figure 3.14 GFET FoMs optimization (a) $f_t$ ( $V_{ds}$ ) for different $V_{gs}$ . (b) $f_{max}$ ( $V_{ds}$ ) for different $V_{gs}$ . The                                                                                                          |

| compact-model parameters are fitted to the measurements of a self-aligned CVD GFET with $W = 2 \times 10$                                                                                                                                           |

| $\mu$ m, L = 60 nm, and $t_{OX}$ = 10 nm                                                                                                                                                                                                            |

| Figure 3.15 GFET FoMs prospects (a) $U(f)$ for different $V_{gs}$ and $V_{ds} = 2 V$ . (b) $f_{MAX}(V_{ds})$ for different $V_{gs}$ . The compact-model parameters are fitted to the measurements of a self-aligned CVD GFET with $W = 2 \times 10$ |

| $\mu$ m, L = 15 nm, and $t_{OX}$ = 10 nm                                                                                                                                                                                                            |

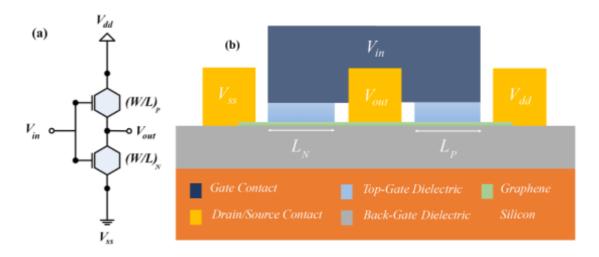

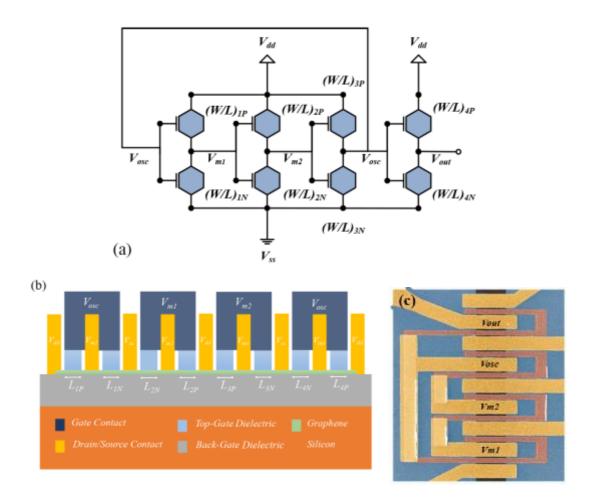

| Figure 4.1. GFET INV. (a) Circuit schematic. (b) Cross-section layout                                                                                                                                                                               |

| Figure 4.2. GFET comparison between a drift-diffusion compact model (solid) and a virtual-source                                                                                                                                                    |

| compact model (dash), where the exfoliated GFET dimensions are $W = 1 \mu m$ , $L = 440 nm$ , and $t_{OX} = 8.5$                                                                                                                                    |

| nm. (a) $I_{ds}(V_{qs})$ for selected $V_{ds}$ . (b) $C_{qq}(V_{qs})$ for selected $V_{ds}$                                                                                                                                                         |

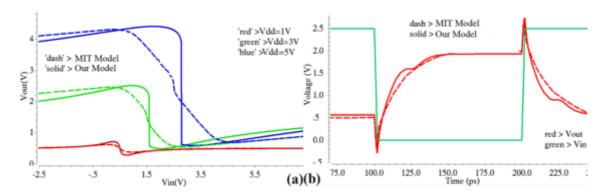

| Figure 4.3. GFET INV comparison between a drift-diffusion compact model (solid) and a virtual-source                                                                                                                                                |

| compact model (dash) with (W/L) $_{N-P}=1~\mu m$ / 440 nm, $t_{OX}=8.5~nm$ , $f_{CLK}=5~GHz$ , and $V_{dd}=2.5~V$ as circuit                                                                                                                        |

| parameters. (a) $V_{out}$ ( $V_{in}$ ) for selected $V_{dd}$ . (b) $V_{out}$ (t) and $V_{in}$ (t) transient simulations                                                                                                                             |

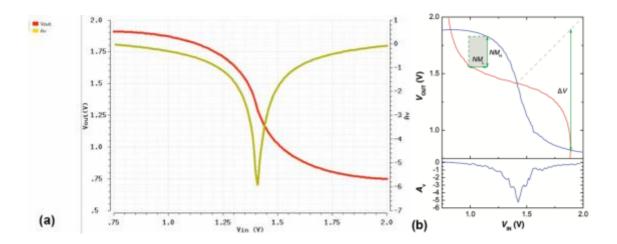

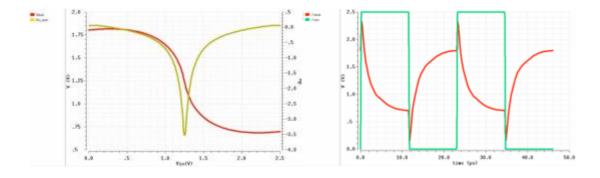

| Figure 4.4. GFET INV $V_{out}$ ( $V_{in}$ ) and $A_{v}$ ( $V_{in}$ ). (a) Simulated INV with model parameters fitted to (b)                                                                                                                         |

| Measured INV fabricated with CVD GFETs, edited from [85]. The circuit parameters are (W/L) $_{N-P}$ = 5 $\mu$ m /                                                                                                                                   |

| 800 nm, $t_{OX} = 4$ nm and $V_{dd} = 2.5$ V                                                                                                                                                                                                        |

| Figure 4.5 GFET INV $V_{out}(t)$ and $V_{in}(t)$ transient simulations. The circuit parameters are: $(W/L)_{N-P} = 5 \mu m / 800 \text{ nm}$ , $t_{OX} = 4 \text{ nm}$ , $f_{CLK} = 1.7 \text{ GHz}$ , and $V_{dd} = 2.5 \text{ V}$                 |

| Figure 4.6 Two cascaded INVs schematic for transient simulations                                                                                                                                                                                    |

| Figure 4.7 GFET INV $V_{out}(t)$ and $V_{in}(t)$ transient simulations. The circuit parameters are: $(W/L)_{N-P} = 5 \mu m/L$                                                                                                                       |

| 50 nm, $t_{OX}$ = 4 nm, $f_{CLK}$ = 40 GHz, and $V_{dd}$ = 2.5 V                                                                                                                                                                                    |

| Figure 4.8 GFET INV DC and transient simulations. (a) $V_{out}$ ( $V_{in}$ ) and $A_{v_{out}}$ ( $V_{in}$ ). (b) $V_{out}$ (t) and $V_{in}$ (t)                                                                                                     |

| transient simulations. The circuit parameters are fitted to the measurements of a fabricated self-aligned                                                                                                                                           |

| CVD GFET with the following values: $(W/L)_{N-P} = 2 \times 10 \mu m$ , $t_{OX} = 10 \text{ nm}$ , and $V_{dd} = 2.5 \text{ V}$                                                                                                                     |

| Figure 4.9 GFET RO based on three GFET INVs acting as delay stages and one GFET INV acting as an                                                                                                                                                    |

| output buffer. (a) Circuit schematic (b) Cross-section layout. (c) Top-section layout fabricated by the                                                                                                                                             |

| Technical University of Milan with $W = 5 \mu m$ , $L = 800 nm$ , $t_{OX} = 4 nm$ . Edited from [85]                                                                                                                                                |

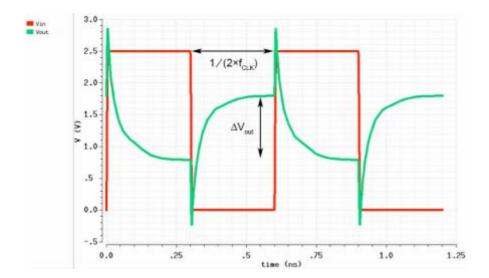

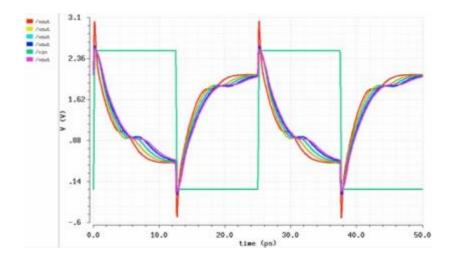

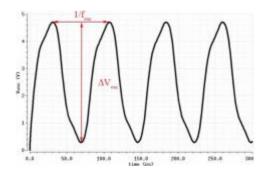

| Figure 4.10 GFET RO $V_{ m osc}$ (t) transient simulation. Our compact model parameters are fitted to a                                                                                                                                             |

| fabricated exfoliated GFET. The circuit parameters are (W/L) $_{N-P}$ = 3 $\mu$ m / 300 nm, $t_{OX}$ = 20 nm, and $V_{dd}$ =                                                                                                                        |

| 5                                                                                                                                                                                                                                                   |

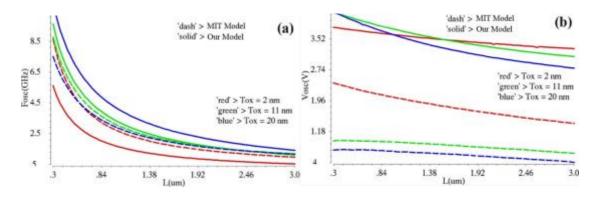

| Figure 4.11 GFET RO comparison between a drift-diffusion compact-model (solid) and a virtual-source                                                                                                                                                 |

| compact-model (dash) with $(W/L)_{1N-3N} = (W/L)_{1P-3P} = 10$ , and $V_{DD} = 5$ V as circuit parameters. (a) $f_{OSC}(L)$ for different $t_{OX}$ . (b) $\Delta V_{OSC}(L)$ for different $t_{OX}$ .                                               |

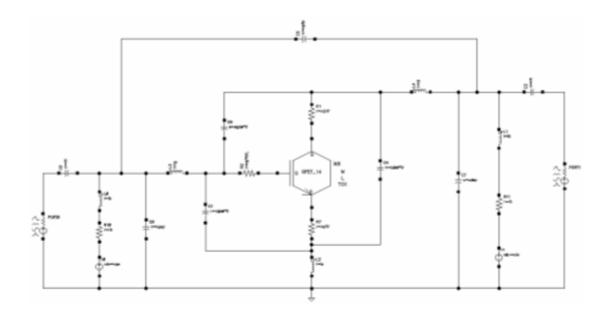

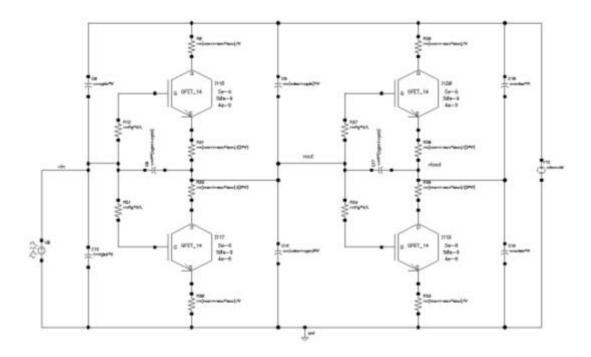

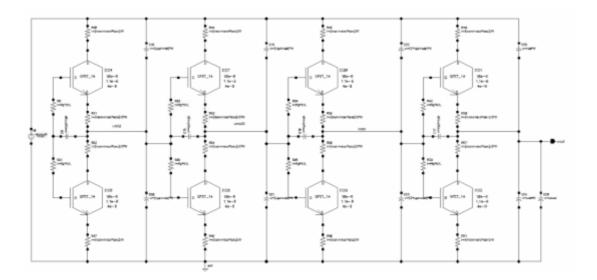

| Figure 4.12 Simulator schematic of a GFET RO based on three GFET INVs acting as delay stages and one                                                                                                                                                |

| GFET INV acting as an output buffer and its correspondent pad load                                                                                                                                                                                  |

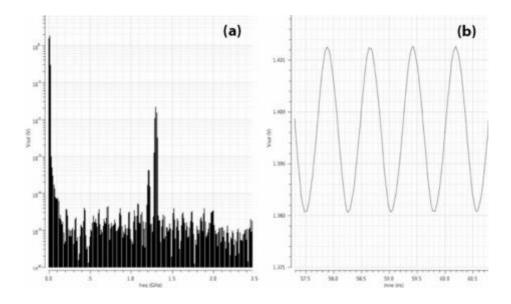

| Figure 4.13 GFET RO simulation. (a) $V_{out}(f)$ spectrum. (b) $V_{out}(t)$ transient. Our compact model                                                                                                                                            |

| parameters are fitted to a measured CVD GFET RO (not shown). The circuit main parameters are $(W/L)_{N-1}$                                                                                                                                          |

| $_{P}$ = 10 $\mu$ m / 1.1 $\mu$ m, $t_{OX}$ = 4 nm, and $V_{dd}$ = 2.5                                                                                                                                                                              |

| Figure 4.14 GFET RO $f_{osc}$ and $\Delta V_{osc}$ against $V_{dd}$ . Our compact model parameters are fitted to a self-aligned                                                                                                                     |

| CVD GFET. The circuit main parameters are (W/L) $_{N-P}$ = 20 $\mu$ m / 60 nm and $t_{OX}$ = 10 nm                                                                                                                                                  |

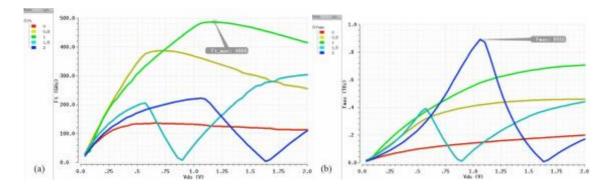

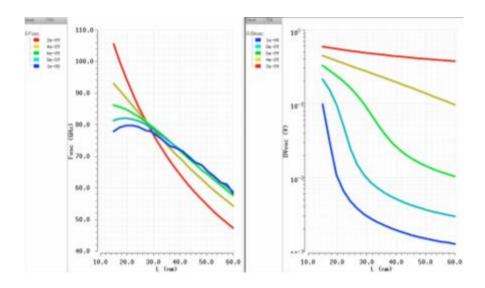

| Figure 4.15 GFET RO FoMs simulations. (a) $f_{OSC}$ (L) and (b) $\Delta V_{OSC}$ (L) for different $t_{OX}$ values. The compact-                                                                                                                    |

| model parameters are fitted to the measurements of a self-aligned CVD GFET with W = 1 $\mu$ m and V <sub>dd</sub> =                                                                                                                                 |

| 0.9 V                                                                                                                                                                                                                                               |

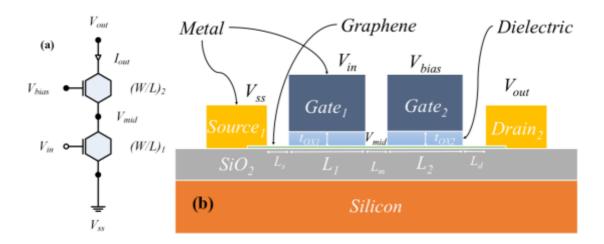

| Figure 4.16 GFET CAS. (a) Circuit schematic. (b) Cross-section layout. A common-gate GFET₂ is cascaded                                                                                                                                              |

| to a common-source GFET <sub>1</sub> to increase its $A_v$ by tuning $V_{bias}$ 71                                                                                                                                                                  |

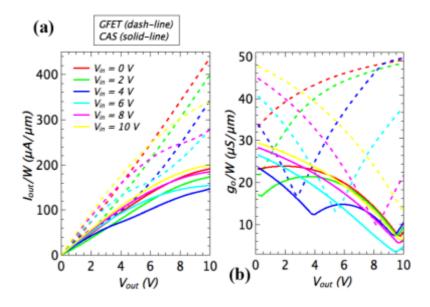

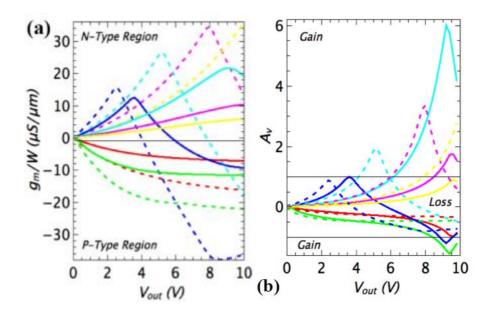

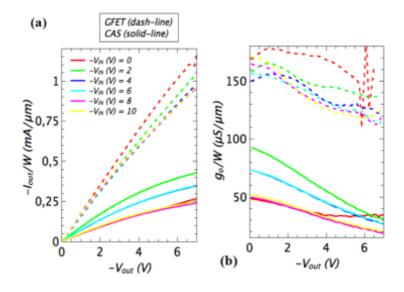

| Figure 4.17 A simulated comparison between a graphene-FET device (dash-line) and a GFET cascode-                                                                                                                                                    |

| amplifier (solid-line), where $W=40~\mu m$ , $L=4~\mu m$ , $t_{ox}=20~nm$ and $V_{bias}=10~V$ . (a) $I_{out}/W$ ( $V_{out}$ ) for selected                                                                                                          |

| $V_{in}$ . (b) $g_o/W$ ( $V_{out}$ ) for selected $V_{in}$                                                                                                                                                                                          |

| Figure 4.18 A simulated comparison between a GFET device (dash-line) and a GFET CAS (solid-line),                                                                                                                                                   |

| where $W = 40 \mu m$ , $L = 4 \mu m$ , $t_{OX} = 20 nm$ and $V_{bias} = 10 V$ . (a) $g_m/W$ ( $V_{out}$ ) for selected $V_{in}$ . (b) $A_v$ ( $V_{out}$ ) for selected $V_{in}$ .                                                                   |

| selected V <sub>in</sub>                                                                                                                                                                                                                            |

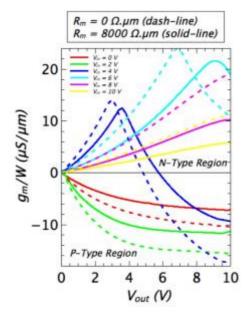

| Figure 4.19 A comparison between the normalized transconductance of a GFET CAS with $R_m = 8000 \Omega \cdot \mu m$                                                                                                                                 |

| (solid-line) and $R_m = 0$ $\Omega$ . $\mu$ m (dot-line), where $W = 40$ $\mu$ m, $L = 4$ $\mu$ m, $t_{OX} = 20$ nm and $V_{bias} = 10$ $V$                                                                                                         |

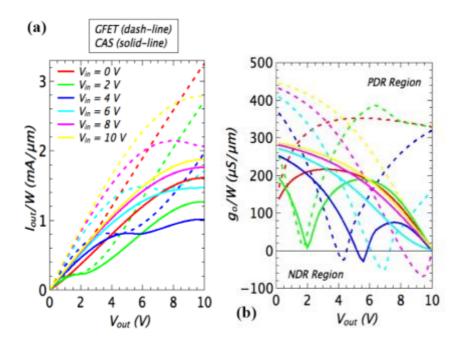

| Figure 4.20 A simulated comparison between a GFET device (dash-line) and a GFET CAS (solid-line),                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| where $W = 10 \mu m$ , $L = 2 \mu m$ , $t_{OX} = 4 nm$ and $V_{bias} = 10V$ . (a) $I_{out}/W$ ( $V_{out}$ ) for selected $V_{in}$ values. (b) $g_o/W$                                         |

| $(V_{out})$ for selected $V_{in}$ values, where NDR/PDR stands for negative/positive differential resistance 74                                                                               |

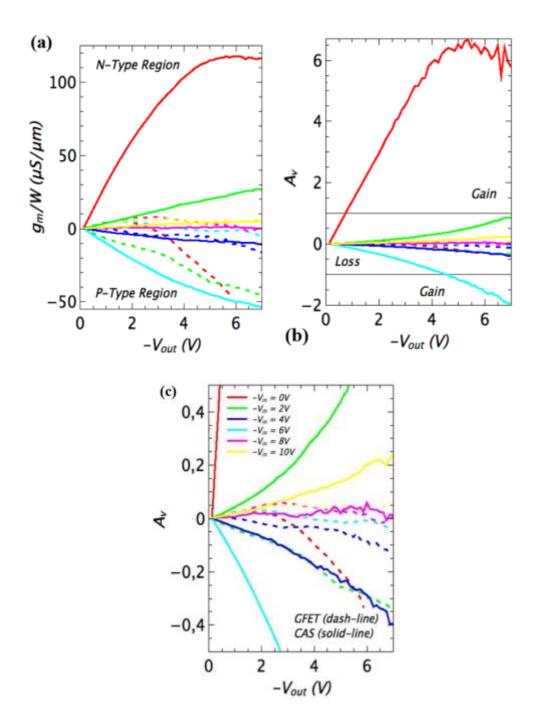

| igure 4.21 A simulated comparison between a GFET device (dash-line) and a GFET CAS (solid-line) where                                                                                         |

| $N = 10 \mu m$ , $L = 2 \mu m$ , $t_{OX} = 4 nm$ and $V_{bias} = 10V$ . (a) $g_m/W$ ( $V_{out}$ ) for different $V_{in}$ . (b) $A_v$ ( $V_{out}$ ) for different                              |

| / <sub>in</sub> . (c) A zoom-in of A <sub>v</sub>                                                                                                                                             |

| Figure 4.22 (a) A scanning electron microscopy image of a GFET CAS fabricated in the Institute of                                                                                             |

| Electronics Microelectronics and Nanotechnology in Lille with graphene synthesized at University of                                                                                           |

| Siegen. (b) Zoom-In                                                                                                                                                                           |

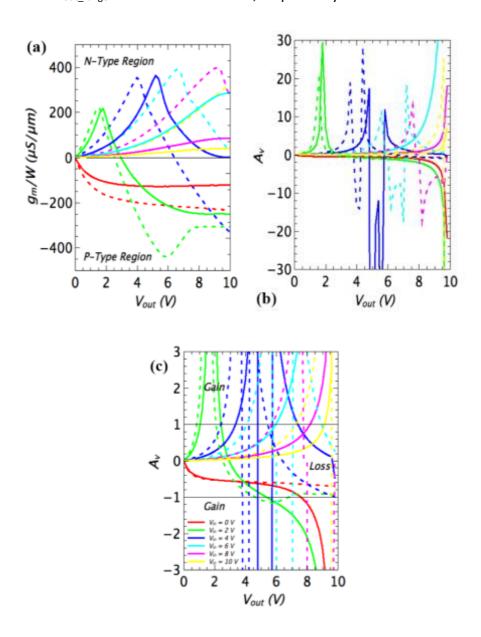

| Figure 4.23 A measured comparison between a GFET device (dash-line) and a GFET CAS (solid-line) where                                                                                         |

| $N=20~\mu m$ , $L=1.5~\mu m$ , $t_{OX}=25~/~15~nm$ and $V_{bias}=0~V$ . (a) $I_{out}/W$ ( $V_{out}$ ) for selected $V_{in}$ . (b) $g_o/W$ ( $V_{out}$ ) for                                   |

| selected V <sub>in</sub>                                                                                                                                                                      |

| Figure 4.24 A measured comparison between a GFET device (dash-line) and a CAS circuit (solid-line)                                                                                            |

| where W = 20 $\mu$ m, L = 1.5 $\mu$ m, t <sub>OX</sub> = 25 / 15 nm and V <sub>bias</sub> = 0 V. (a) $g_m/W$ (V <sub>out</sub> ) for selected V <sub>in</sub> . (b) $A_v$ (V <sub>out</sub> ) |

| for selected V <sub>in</sub> . (c) A zoom-in of A <sub>v</sub>                                                                                                                                |

## List of Tables

| Table 1.1 Communication module specifications for a wireless sensor network. Energy efficiency = Power                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| consumption / Data rate. <sup>a</sup> Integrated circuit (IC), <sup>b</sup> Printed circuit board (PCB)                                                |

| Table 1.2 Wireless nanomedia/nanosensor networks communication module specifications                                                                   |

| Table 1.3 Wireless network-on-chip communication module specifications                                                                                 |

| Table 1.4 Wireless networks vs communication module's data rate and distance range. The targeted                                                       |

| wireless networks for this thesis are highlighted in green colour21                                                                                    |

| Table 2.1 WNN feasibility vs high-speed short-range wireless TRx specifications. Green colour stands for                                               |

| 'partially achievable', yellow colour for 'very challenging' and red colour for 'not possible'                                                         |

| Table 2.2 SHF and EHF high-speed short-range wireless TRx. Green colour = Antenna integrated on-chip.                                                  |

| Blue colour = Antenna integrated in-package. Yellow colour = Antenna integrated on-board. Red color =                                                  |

| External antenna. PR = Pad Ring                                                                                                                        |

| Table 2.3 EHF and THF high-speed short-range wireless transceivers. Green colour = Antenna integrated                                                  |

| on-chip. Blue colour = Antenna integrated on-package. Yellow colour = Antenna integrated on-board.                                                     |

| Red colour = External antenna. PR = Pad Ring                                                                                                           |

| Table 2.4 RF nanotransistors against $f_{MAX}$ and digital CMOS compatibility. Green colour stands for 'very                                           |

| high', Blue colour stands for 'high', yellow colour for 'medium' and red colour for 'low'32                                                            |

| Table 3.1 Electron $\mu$ , $v_{sat}$ , and $E_g$ for several types of graphene, 2D and conventional semiconductors                                     |

| [60][48][61]                                                                                                                                           |

| Table 3.2 Extrinsic transconductance record-high values $g_{m\_max}$ for top-gate GFETs fabricated by different                                        |

| research groups. n.a: Parameter non-applicable 41                                                                                                      |

| Table 3.3. Extrinsic output conductance record-low values $g_{o\_min}$ for top-gate GFETs fabricated by                                                |

| different research groups. n.d: Data non-available. n.a: Parameter non-applicable 42                                                                   |

| Table 4.1 GFET INV $f_{CLK}$ and $\Delta V_{out}$ (V) achieved for different $L_{N-P} = L$ . The circuit parameters are fitted to                      |

| the measurements of a fabricated INV based on CVD GFETs with the following values: $W_{N-P} = 5 \mu m$ , $t_{OX} =$                                    |

| 4 nm, and V <sub>dd</sub> = 2.5 V                                                                                                                      |

| Table 4.2 Self-aligned CVD GFET INV maximum $f_{CLK}$ and $\Delta V_{in}$ (V) achieved for different channel lengths $L_P$                             |

| = $L_N$ = $L$ . The circuit main parameters are fitted to the measurements of a fabricated self-aligned CVD                                            |

| GFET with the following values: $W_{N-P} = 2 \times 10 \mu\text{m}$ , $t_{OX} = 10 \text{nm}$ , $R_g = 124 \text{m}\Omega$ and $V_{dd} = 2.5 \text{V}$ |

## Contents

| <u>1</u> N        | ANONETWORKS                                                     | 15 |

|-------------------|-----------------------------------------------------------------|----|

| 1.1               | THE INTERNET OF THINGS                                          | 16 |

| 1.1.1             | Wireless Sensor Network                                         | 16 |

| 1.2               | TOWARDS WIRELESS NANONETWORKS                                   | 18 |

| 1.2.1             | Wireless Nanomedia/Nanosensor Network                           | 18 |

| 1.2.2             | WIRELESS NETWORK ON CHIP                                        | 19 |

| 1.3               | Conclusions                                                     | 20 |

| <u>2</u> <u>N</u> | ANOTRANSCEIVERS                                                 | 22 |

| 2.1               | TOWARDS WIRELESS NANOTRANSCEIVERS                               | 22 |

| 2.1.1             | HIGH DATA RATE TRANSCEIVERS FOR SHORT DISTANCE RANGES           | 23 |

| 2.1.2             | Impulse-Radio Front-Ends at Low Terahertz Frequencies           | 28 |

| 2.2               | RADIO-FREQUENCY NANOTRANSISTORS                                 | 30 |

| 2.2.1             | Maximum Frequency of Oscillation                                | 30 |

| 2.2.2             | Two-Dimensional Semiconductors                                  | 32 |

| 2.3               | CONCLUSIONS                                                     | 32 |

| <u>3</u> <u>N</u> | ANOTRANSISTORS: GRAPHENE FETS                                   | 34 |

| 3.1               | GRAPHENE SEMIMETALS                                             | 34 |

| 3.1.1             | LARGE-SCALE FABRICATION TECHNIQUES                              | 35 |

| 3.1.2             | HIGH MOBILITY AND SATURATION VELOCITY CARRIER TRANSPORT         | 36 |

| 3.1.3             | The Zero-Bandgap Challenge                                      | 37 |

| 3.2               | GRAPHENE FETS                                                   | 38 |

| 3.2.1             |                                                                 | 38 |

| 3.2.2             | Transconductance, Output Conductance and Voltage Gain           | 39 |

|                   | GFET COMPACT MODELS                                             | 43 |

| 3.3.1             | •                                                               | 43 |

|                   | CURRENT-TO-VOLTAGE MODEL OPTIMIZATION FOR DEVICE SCALING        | 44 |

|                   | Capacitance-to-Voltage Model Including Extrinsic Parasitics     | 49 |

|                   | FITTING GFET MODEL PARAMETERS TO GFET MEASUREMENTS              | 51 |

|                   | CVD GFET BASED ON ALUMINA TOP-GATES                             | 51 |

|                   | SELF-ALIGNED CVD GFET BASED ON ALUMINA TOP-GATES                | 53 |

|                   | GFET MAXIMUM FREQUENCY OF OSCILLATION                           | 55 |

| 3.6               | CONCLUSIONS                                                     | 56 |

| <u>4</u> N        | ANOCIRCUITS: GFET CIRCUITS                                      | 58 |

| 4.1               | GFET COMPLEMENTARY INVERTERS                                    | 59 |

| 4.1.1             | GFET COMPACT MODELS BENCHMARK BASED ON EXFOLIATED GFETS         | 59 |

|                   | INV SIMULATION BENCHMARK BASED ON EXFOLIATED GFETS              | 61 |

|                   | INV SIMULATION AGAINST MEASUREMENT BENCHMARK BASED ON CVD GFETS | 61 |

|                   | INV DESIGN EXPLORATION BASED ON SELF-ALIGNED CVD GFETS          | 64 |

|                   | GFET RING-OSCILLATORS                                           | 65 |

| 4.2.1             | RO SIMULATION BENCHMARK BASED ON EXFOLIATED GFETS               | 67 |

| 4.2.2 RO SIMULATION AGAINST MEASUREMENT BENCHMARK BASED ON CVD GFETS           | 68   |

|--------------------------------------------------------------------------------|------|

| 4.2.3 RO DESIGN EXPLORATION BASED ON SELF-ALIGNED CVD GFETS                    | 69   |

| 4.3 GFET CASCODE AMPLIFIERS                                                    | 70   |

| 4.3.1 CAS SIMULATION BASED ON CVD GFETS FABRICATED WITH SILICA TOP-GATES       | 71   |

| 4.3.2 CAS SIMULATION BASED ON CVD GFETS FABRICATED WITH ALUMINA TOP-GATES      | 74   |

| 4.3.3 CAS FABRICATION BASED ON CVD GFETs WITH SILICA/ALUMINA COMBINED TOP-GATE | s 76 |

| 4.4 Conclusions                                                                | 78   |

| 5 FINAL CONCLUSIONS: FUTURE OUTLOOK                                            | 80   |

| 5.1 FUTURE OUTLOOK                                                             | 82   |

## 1 Nanonetworks

Information and communication technology achieved its major breakthrough in human history with the foundation of telecommunications in the 19<sup>th</sup> century, although the invention of electronics in the 20th century was the key enabler for transforming our past industrial society, mainly sustained by manufactured goods, to our present information society, mainly sustained on services. In the short run, our future as humans lies on building up a knowledge society [1] where raw information is transformed into usable knowledge for improving and creating more valuable services, and in the long run, humanity might foresee a rather utopian wisdom society where the existing and newly generated wisdom is applied and equally distributed between all members of society. Without any kind of doubts the future of our civilization will be a more interconnected one, with ever increasing person-to-person, machine/machine-to-person and machine-to-machine (M2M) connections through ubiquitous networks. To make this vision a reality, M2M communication modules cost, size, and power consumption need to be reduced further more than actual technologies allow. Nanotechnology, first envisioned by Richard Feynman in 1959 [2], is giving rise to devices and systems in a scale ranging from one to a few hundred nanometers, and will be fundamental in overcoming the future challenges. This thesis is trying to interconnect and shed a bit of light on two rather new and disrupting nanotechnology disciplines that have gained momentum among the researchers during the last decade: twodimensional materials [3] and nanonetworks [4]. This chapter briefly introduces a few concepts on networking as wireless sensor networks (WSN) that are just starting to be deployed, and wireless nanonetworks (WNN) that could become the main objective for the research work presented through the following chapters.

## 1.1 The Internet of Things

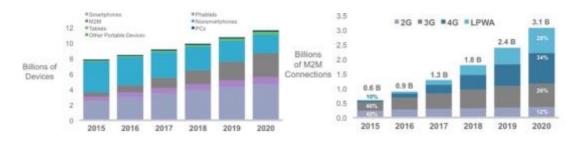

The human population estimations for 2017 are around 7.5 billion. Figure 1.1a is showing that by 2020 there will be 1.5 mobile devices per capita which will translate into 11.6 billion mobile devices including phones, M2M modules, tablets and others [5]. These devices will be connected through computer networks with different distanceranges and data-rates depending on their target-applications: mobile networks like for example 4G, 5G; wireless local-area-networks (WLAN) like for example WiFi; wireless personal-area-networks (WPAN) like for example Bluetooth, Zigbee and Ultra-Wide-Band; wireless body-area-networks (WBAN) like for example the IEEE 802.15.6 standard; low-power wide-area-networks (LPWAN), and new types of networks to be developed in the near future.

Figure 1.1 (a) Global mobile devices and connections growth. (b) Global machine-to-machine growth and migration from 2G to 3G and 4G [5].

As seen in Figure 1.1b, the number of M2M modules are expected to grow five-fold in only 5 years, reaching 3.1 billion connections. In a few years, the amount of M2M modules will surpass all the mobile phones around the planet. Low-power wide-area will be the second most common M2M connection by 2020 [5]. M2Ms modules are the core of the internet of things IoT, defined as the worldwide network of interconnected machines uniquely addressable based on standard communication protocols. The applications are endless: home automation, smart metering and maintenance, assisted driving, logistics tracking, environment monitoring, healthcare bio-sensing, and many more [6]. From all plethora of existing wireless networks, this thesis will focus on high-speed short-range networks.

#### 1.1.1 Wireless Sensor Network

WSN consist of hundreds of interconnected sensor-modules that are able to retrieve and process information while consuming low power, such networks are already starting to gain relevance on the complex IoT ecosystem [7]. An example of WSN based applications are the indoor-location solutions provided by Decawave Inc., a small start-up company where the author had the opportunity to work with. A low-rate WPAN LR-WPAN, fully IEEE 802.15.4-2011 compliant, is implemented to locate tags with unprecedented resolutions under 10 cm, this new application is already revolutionizing the logistics sector [8]. The communication module, i.e. transceiver (TRx) + antenna, is a low-power innovative impulse-radio/ultra-wide-band (IR/UWB) solution and the

achieved specifications are shown in Table 1.1 to pinpoint the state-of-the-art (SoA) and to compare with the module specifications for WNNs introduced in next section 1.2.

| Distance     | Data           | Power               | Energy                 | Module         |

|--------------|----------------|---------------------|------------------------|----------------|

| Range<br>(m) | Rate<br>(Mbps) | Consumption<br>(mW) | Efficiency<br>(nJ/bit) | Size<br>(mm²)  |

| 50 - 200     | 0.11 - 6.8     | 115.5 - 415.8       | 61.15 – 1005           | $36^a - 299^b$ |

Table 1.1 Communication module specifications for a wireless sensor network. Energy efficiency = Power consumption / Data rate. <sup>a</sup> Integrated circuit (IC), <sup>b</sup> Printed circuit board (PCB).

Shrinking further the footprint of these tags would be beneficious for improving the location accuracy, increasing the data rate, reducing the power consumption and bringing down fabrication costs. As seen in Figure 1.2, the biggest component of the tag is the external dielectric-chip antenna radiating at the 3.5 - 6.5 GHz frequency range. Reducing the antenna size will force the TRx to work at higher frequencies and to make this happen transistors need to operate faster. With existing complementary-metal-oxide-silicon (CMOS) technologies, the straightforward way to achieve higher operation frequencies is reducing the gate length L, that implies jumping from 90 nm node to smaller ones (65 nm, 45 nm, 32 nm, 22 nm, 14 nm or 10 nm). The challenge ahead is that the physical limit for device scaling is already approaching: shrinking metal-oxide-silicon field-effect-transistors (MOSFET) gates below 3 nm theoretically (5 nm practically) will not be possible due to direct-tunnelling current appearing between drain and source [9], therefore new disruptive technologies are a must to overcome silicon limitations in nanoelectronics.

Figure 1.2 An indoor-location tag: DWM1000 module is based on a 90 nm CMOS IC TRx, integrated with a dielectric-chip antenna, DC/DC converter and xOSC on-board. Edited figure from [10].

#### 1.2 Towards Wireless Nanonetworks

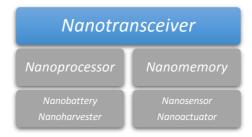

A WNN, defined as an interconnection of nanomachines, are expected to expand the capabilities of single nanomachines by allowing them to cooperate and share information. A nanomachine is a device consisting of nanoscale components able to perform a specific task at nanolevel, such as communicating, computing, data storing, and sensing. The tasks performed by one nanomachine are very simple and restricted to its close environment due to its low complexity and small size. A nanomachines (Figure 1.3) consists of the following modules shown below: Nanotransceiver (nanoTRx) [11], Nanoprocessor [12], Nanomemory [13], Nanosensor [14] / Nanoactuator [15], and Nanobattery [16] / Nanoharvester [17]. Many breakthroughs in several branches of science (chemistry, physics, mechanics, electronics, telecommunications and computing) will be needed to make this vision reality in the long run. Examples of potential applications are: intra human-body monitoring, biodiversity control, biodegradation assistance, harmful chemicals monitoring, biological weapons monitoring, on chip networking, home/office organization, and many more [4].

Figure 1.3 Nanomachine modules. First prototypes are envisioned beyond 2030. The scope of this thesis is the nanoTRx module.

In the next sections, three different types of WNNs are presented: wireless nanomedia network (WnMN) targeted to multimedia applications, wireless nanosensor network (WnSN) targeted to ubiquitous-sensing applications, and wireless network-on-chip (WNoC) targeted to parallel-computing applications.

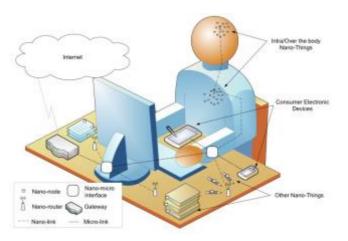

## 1.2.1 Wireless Nanomedia/Nanosensor Network

Figure 1.4 Wireless nanomedia / nanosensor networks [18].

In Figure 1.4, an example of WnMN and WnSN are depicted. For WnMN, small office-utensils (pencils, papers, books) are able to communicate multimedia data between them. For WnSN, fixed nanomachines over the body are able to communicate health-monitoring data between them or even mobile nanomachines inside the body are able to measure low chemical concentrations and drugs are delivered locally if needed. The design specifications of the communication module are shown below:

|      | Distance<br>Range<br>(cm) | Data<br>Rate     | Power<br>Consumption<br>(mW) | Energy<br>Efficiency | Module<br>Size    |

|------|---------------------------|------------------|------------------------------|----------------------|-------------------|

| WnMN | 30 - 300                  | (Gbps)<br>1 - 10 | 10 – 100                     | (pJ/bit)<br>10       | (mm²)<br>10 - 100 |

| WnSN | 10 - 30                   | 0.1 - 1          | 1 – 10                       | 10                   | 1 - 10            |

Table 1.2 Wireless nanomedia/nanosensor networks communication module specifications.

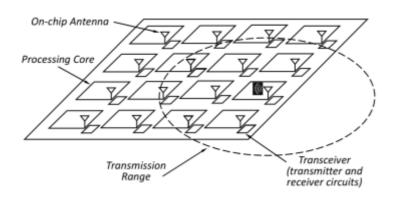

## 1.2.2 Wireless Network on Chip

A network-on-chip (NoC) consists in a mesh of wireline-routed interconnections and has been proposed as a solution to the very-limited scalability of the buses used in multi-core processors. However, as the number of cores per chip increases, traditional NoCs suffer from fundamental issues that will render them impractical in future multi-processors. The concept of WNoC (Figure 1.5) is proposed to reduce communication latency and power consumption, by reducing the number of hops between any pair of cores, thanks to the implementation of broadcast and multicast data-traffic through antennas integrated on the same die [19].

Figure 1.5 Wireless network-on-chip schematic [20].

The targeted communication module specifications for WNoCs are shown below:

| Distance | Data     | Power       | Energy     | Module  |

|----------|----------|-------------|------------|---------|

| Range    | Rate     | Consumption | Efficiency | Size    |

| (cm)     | (Gbps)   | (mW)        | (pJ/bit)   | (mm²)   |

| 3 - 10   | 10 – 100 | 1 – 10      | 0.1        | 0.1 - 1 |

Table 1.3 Wireless network-on-chip communication module specifications.

## 1.3 Conclusions

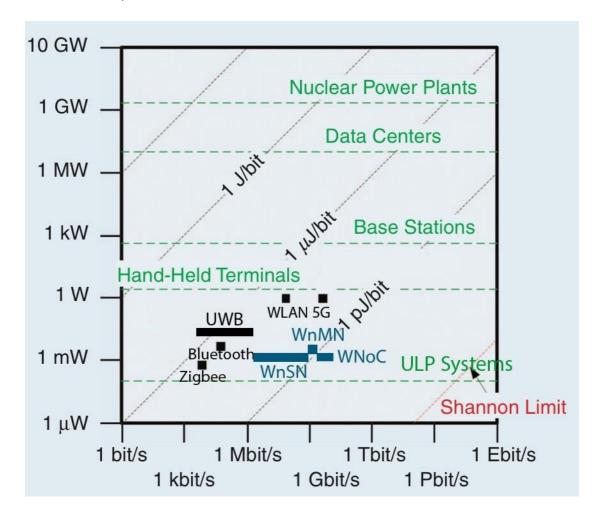

In Figure 1.6, a power consumption against data rate graph is shown [21]. The four types of wireless networks (UWB, WnMN, WnSN, and WNoC) already presented are pinpointed and compared to other types of networks (WLAN, 5G, Bluetooth and Zigbee). WLAN and 5G are considered 'high-power' wireless networks; and Bluetooth, Zigbee and UWB are considered 'long-distance' wireless networks, therefore both types are discarded as targeted applications for this thesis. Our aim is paving the way for new networks concepts as WnMN, WnSN, and WNoC.

Figure 1.6 Power consumption versus data rate for the communication module of different wireless networks. The blue boxes are the targeted requirements. Edited figure from [21]

.

UWB is consuming more power than Bluetooth because is a wideband (500 MHz) network that delivers more data rate and also needs longer ranges to locate tags in large indoor buildings (like for example in warehouses). Our particular interpretation of WnSN is consuming less power than Bluetooth and its data rates are similar to WLAN. WNoC is consuming more power than Zigbee and it is offering faster data rates than 5G. WnMN are consuming the same power as Bluetooth but the offered data rates are a bit less

than 5G. Below a final summary of all the networks regarding their distance range and data rate is presented to highlight the characteristics of the targeted new WNNs:

|          | 5G    | WLAN  | UWB           | Bluetooth | Zigbee |  |

|----------|-------|-------|---------------|-----------|--------|--|

| Distance | Very  | Long  | Long          | Short     | Short  |  |

| Range    | Long  | Long  | Long          | SHOTE     | SHOLL  |  |

| Data     | Ultra | Lliah | Very Low      | Low       | Very   |  |

| Rate     | High  | High  | ligh /Low Low |           | Low    |  |

|          | WnMN  | WnSN  | WNoC  |

|----------|-------|-------|-------|

| Distance | Very  | Very  | Ultra |

| Range    | Short | Short | Short |

| Data     | Very  | Hiah  | Ultra |

| Rate     | High  | High  | High  |

Table 1.4 Wireless networks vs communication module's data rate and distance range. The targeted wireless networks for this thesis are highlighted in green colour.

Future high/ultra-high data rate TRx applied to WNN which imply short/ultra-short distance ranges (3 - 300 cm) requirements have been detected. WNN need smaller (0.1 - 100 mm²), faster (0.1 - 100 Gbps), more energy efficient (0.1 - 10 pJ/bit) and less power hungry (1 - 100 mW) TRx than classical wireless networks to become a reality. We are talking about 2 - 3 orders of magnitude reduction in size, data rate and power consumption which is **not** possible with commercial technologies available at the present. This enormous challenge will be discussed in detail in chapter 2 and new proposals will be introduced.

## 2 Nanotransceivers

Analysing the requirements for our targeted WNN applications, it becomes clear that faster and more energy efficient TRx will be needed to implement the communication modules, consequently miniaturisation at device level and architecture level is a must to target future wireless nanoTRx introduced in section 2.1. In section 2.2, the SoA of radio-frequency (RF) nanotransistors is analysed; once it is shown that with existing transistors is extremely challenging if not impossible to design the architectures required, recently discovered two-dimensional (2D) materials are proposed as channels for future nanotransistors. Chapter 3 will focus on Graphene [22] which is exhibiting extraordinary carrier-mobilities and could fulfil the speed demands for future front-end (FE) nanocircuits.

## 2.1 Towards Wireless Nanotransceivers

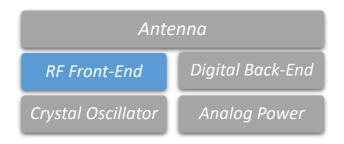

A wireless nanoTRx is defined as an ultra-small communication module targeted to WNN, which it is fully integrated on a common insulator substrate consisting of five modules: analog FE, digital back-end (BE), antenna, energy management, and crystal oscillator schematized in Figure 2.1. What marks out a nanoTRx from a classical communication module is: (1) the small size which lies in the range from 0.1 mm² to 100 mm² which requires a high level of compatibility between the technology used by the different modules to integrate all of them on the same die; (2) the low power consumption which lies in the range from 1 mW to 100 mW due to the tiny amount of energy available for them; and (3) the short access distance which lies in the range from 3 cm to 3 m constrained by their size and power limitations. Both transmitter (Tx) and

receiver (Rx) are divided into a FE implemented with RF circuits and a BE implemented with digital circuits. The antenna is the transductor that is adapting the metal-guided RF signals of the Tx to the shared medium (air), and from the air to the Rx. The function of a Rx is to amplify and filter the ultra-low RF signals sensed by the antenna that arrive from the air, also it is able to discern between the targeted signal and the discarded noise/interference signals. The Tx amplifies and filters the RF signal to power levels that are enough to overcome attenuation/noise/interferences which may arise on the air during the communication. The xOSC is needed for generating a stable and accurate clock reference. The analog power module efficiently provides clean direct-current (DC) supply-voltage for both FE and BE modules.

Figure 2.1 Diagram of the nanoTRx modules integrated on a common substrate. The target of this thesis is the RF FE.

In the following section, the SoA wireless TRx for high-speed at short-range communication is reviewed and analysed. Once it is shown that with existing TRx architectures is extremely challenging if not impossible to comply with the specifications defined for the targeted WNN, a potential solution is proposed based on the combination of two arising wireless communication technologies: terahertz (THz) [23] and IR/UWB technologies [24], which will imply a change of paradigm for future nanotransistors technology as explained in section 2.2.

#### 2.1.1 High Data Rate Transceivers for Short Distance Ranges

A wide variety of wireless TRx solutions can be found in the literature covering many alternatives in terms of technology, modulation, or architecture. For transmission ranges of up to a few meters, these provide multi-gigabit data rates, and it is expected that these figures will keep increasing as technology evolves (Conference C). In Table 2.2 and Table 2.3, the most relevant high-speed and short-range TRx are presented. They are classified in 3 groups depending on their frequency-band operation: super high-frequency SHF (1 cm <  $\lambda^1$  < 10 cm), extremely high-frequency EHF (1 mm <  $\lambda$  < 10 mm), and tremendously high-frequency THF (100  $\mu$ m <  $\lambda$  < 1000  $\mu$ m). The following TRx characteristics are defined: frequency band, center frequency (f<sub>C</sub>) in GHz, chip partitioning, transistor technology, digital modulation, power consumption (mW), data rate (Gbit/s), energy efficiency = power consumption / data rate (pJ/bit), distance range (cm), FOM<sub>com</sub> = energy efficiency / distance range (pJ/bit. $\sqrt{cm}$ ) introduced by [25],

•

<sup>&</sup>lt;sup>1</sup> Electromagnetic Wavelength

integration level, module size (mm<sup>2</sup>), antenna type, n (bit-error-ratio BER = 10<sup>-n</sup>) and maturity factor = (data rate / center frequency) x 100 (%). A new figure of merit is introduced: The maturity factor (MF), not to be confused with the concept of spectral efficiency = data rate / bandwidth (BW), tries to evaluate the efficiency of implementing a given modulation and BW in order to yield a target data rate operating at a target frequency band. As technology matures, highly optimized TRx are expected leading to increasing MFs, that is, higher data rates for similar area and energy values (Journal III). The maximum MF value observed is 26.3 % at 190 GHz [26] which is really an outstanding value for electronics at such high frequencies considering that the average for all shown TRx is 12.9 %. The MF can be interpreted as a 'digitalization' of the fractional BW concept for antennas (FB = BW / fc), where data rate is used instead of BW to include the impact of digital modulation. While the frequency-band operation is increased, the antenna size becomes smaller which is beneficious for integrating them on chip. We can classify antennas in four different types from bigger to smaller sizes: external (red), on-board (yellow), on-package (blue) and on-chip (green). As it can be noticed, from 8 GHz to 135 GHz is not possible to integrate antennas on-chip due to their excessive dimensions. The aim in this thesis is to target on-chip antennas that is why it is so important to build nanoTRx beyond 200 GHz bands. The highest frequency band achieved by a digital TRx is 400 GHz, and this is happening thanks to the improved carrier mobility offered by SiGe heterojunction-bipolar-transistors (HBT) compared to CMOS FETs [27]. The highest integration is achieved at 8 GHz, where RF FE and digital BE are integrated on the same 90 nm CMOS process [28]. The ultimate goal of our vision is to achieve similar level of integration at hundreds of GHz with a common process (including different kinds of devices with specific functionalities), this is **not** possible with existing technologies. The lowest power consumption 13.3 mW and longest distance range 1.2 m is achieved at 8 GHz [29], this is achievable due to the use of the most simple digital modulation on-off-keying OOK; this case seems suitable for WnSN specifications, nevertheless the main problem is that the antenna is not integrated, so it is not feasible to keep the module size under 100 mm<sup>2</sup>. The highest data rate 50 Gbps is achieved at 190 GHz [26], which seems suitable for WNoC although power consumption is exceeding the 10 mW limit by far. The lowest energy efficiency 5.3 pJ/bit is also achieved at 190 GHz [26] and the lowest FOMcom 1.98 pJ/bit is achieved at 60 GHz [30], the first TRx seems suitable for WnMN, but its short distance range fall behind the minimum 10 cm required; and the second TRx seems suitable for WnSN, nevertheless its distance range also fall behind the minimum 30 cm required. The smallest modulesize achieved is 0.31 mm<sup>2</sup> at 142 GHz [31], which seems appropriated for WNoCs, although the drawback is the used technology (BiCMOS) which does not scale properly for integrating the massive number of gates required to fabricate nanoprocessors. The lowest BER 10<sup>-12</sup> is achieved at 210 GHz [32], which seems adequate for WNoC that needs very reliable transmission to be competitive against wired connections, but the problem is the power consumption that is well above the 10 mW allowed limit.

For these reasons, it becomes clear that to comply with **all** the specifications at the **same** time for each one of our targeted WNNs is not possible with the available technology, new semiconductor processes and architectures need to be developed for the long run. As a summary, the suitability of actual TRx to specified WNN is shown in Table 2.1. The most demanding specifications come clearly from WNoCs, and in terms of requirements lowering power-consumption is the most pressing challenge.

|         | Maximum<br>Distance<br>(mm) | Data<br>Rate<br>(Gbps) | Power<br>Consumption<br>(mW) | Energy<br>Efficiency<br>(pJ/bit) | Module<br>Size<br>(mm²) |  |

|---------|-----------------------------|------------------------|------------------------------|----------------------------------|-------------------------|--|

| SoA TRx | 0.6 – 1200                  | 0.5 - 50               | 13.3 - 1900                  | 5.3 – 117.3                      | 0.31 - 26.64            |  |

| WnMN    |                             |                        |                              |                                  |                         |  |

| WnSN    |                             |                        |                              |                                  |                         |  |

| WNoC    |                             |                        |                              |                                  |                         |  |

Table 2.1 WNN feasibility vs high-speed short-range wireless TRx specifications. Green colour stands for 'partially achievable', yellow colour for 'very challenging' and red colour for 'not possible'.

|                                 | Geng et al.  | Abe et al.                           | Chen et al.                | Chen et al. Kawasaki et al. |               | Okada et al.                 |                               | Byeon et al.         | Byeon et al. Pang et al. |              | Lee et al.    |       |

|---------------------------------|--------------|--------------------------------------|----------------------------|-----------------------------|---------------|------------------------------|-------------------------------|----------------------|--------------------------|--------------|---------------|-------|

|                                 | [29]         | [28]                                 | [33]                       | [34]                        |               | [35]                         |                               | [30]                 | [36]                     |              | [37]          |       |

| Year                            | 2015         | 2012                                 | 2009                       | 2010                        |               | 2013                         |                               | 2016                 | 2017                     |              | 2015          |       |

| Frequency Band                  | SHF          | SHF                                  | EHF                        | EI                          | ЧF            | EHF                          |                               | EHF                  | EHF                      |              | EHF           |       |

| Center Frequency<br>(GHz)       | 8            | 8                                    | 43                         | 50                          | 56jj          |                              | 60                            |                      | 60                       |              | 80            |       |

| Chip Partitioning               | Front-End    | Front-End +<br>Back-End              | Front-End                  | Front-End                   |               | Front-<br>End                | Back-End                      | Front-End            | nd Front-End             |              | Front-End     |       |

| Transistor Technology           | 65 nm CMOS   | 90 nm CMOS                           | 180 nm SiGe<br>BiCMOS      | 40 nm<br>CMOS               |               | 65 nm<br>CMOS                | 40 nm<br>CMOS                 | 90 nm<br>CMOS        | 65 nm<br>CMOS            |              | 65 nm<br>CMOS |       |