## Performance-aware Energy Optimizations in Networks for HPC

by KARTHIKEYAN P. SARAVANAN

A thesis submitted in fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Architecture

Departament d'Arquitectura de Computadors (DAC) Universitat Politècnica de Catalunya (UPC) Barcelona, Spain

PhD Supervisors: Dr. Alex Ramirez & Dr. Paul M. Carpenter

This page has been intentionally left blank.

## Performance-aware Energy Optimizations in Networks for HPC

KARTHIKEYAN P. SARAVANAN Universitat Politècnica de Catalunya (UPC)

#### (ABSTRACT)

Energy efficiency is an important challenge in the field of High Performance Computing (HPC). High energy requirements not only limit the potential to realize next-generation machines but are also an increasing part of the total cost of ownership of an HPC system. While at large HPC systems are becoming increasingly energy proportional in an effort to reduce energy costs, interconnect links stand out for their inefficiency. Commodity interconnect links remain "always-on", consuming full power even when no data is being transmitted. Although various techniques have been proposed towards energy- proportional interconnects, they are often too conservative or are not focused toward HPC. Aggressive techniques for interconnect energy savings are often not applied to HPC, in particular, because they may incur excessive performance overheads. Any energy-saving technique will only be adopted in HPC if there is no significant impact on performance, which is still the primary design objective.

This thesis explores interconnect energy proportionality from a performance perspective. First a characterization of HPC applications makes a case for the enormous potential for interconnect energy proportionality with HPC applications. Next, an HPC interconnect with on/off based links, modeled after the IEEE 802.3az Energy Efficient Ethernet protocol, is evaluated. This evaluation, while presenting a relationship between performance impact and energy over HPC applications, also emphasizes the need for performance focused designs in energy efficient interconnects. Next, an adaptive mechanism, *PerfBound*, is presented that saves link energy subject to a bound on application performance overheads. Finally this evaluation structure is applied into an intermediate link power state - *Fast-Wake*, in addition to the traditional on and off states. Results of this study, over 15 production HPC applications show that, compared to current day always-on HPC interconnects, link energy can be reduced by unto 70% while application performance overhead is bounded to only 1%.

This page has been intentionally left blank.

Dedicated to Amma, Appa, Tangi, Thambi and my Sai

This page has been intentionally left blank.

# Acknowledgments

I start by thanking my advisors Dr. Alex Ramirez and Dr. Paul M. Carpenter for their support and guidance. I consider myself lucky to have had advisors whom, as I finish my PhD still make me wonder how much more I could have learned from them. I will always be grateful to Alex for instilling in me a methodology for research and critical thinking which has driven this thesis and will continue to guide my career forward. Alex is an inspiring and visionary supervisor, being under him has taught me to be ambitious and work on hard problems. He has always provided my PhD with a sense of purpose and why it matters.

I cannot thank Paul enough for the last five years of weekly meetings and guidance which has morphed into every word in this thesis. His guidance, generosity with his time, willingness to engage and patience during our discussions when it sometimes takes me literally minutes to get to his level of thinking, is behind all ideas in this thesis. Working on my PhD has been often times hard, with many paper rejects and many more ideas that didn't work, sometimes with months of investigation amounting to nothing, it's Paul's encouragement and support that has been vital in helping me persist and push through.

I want to thank Barcelona Supercomputing Center (BSC) and its director Prof. Mateo Valero for giving me an opportunity to be part of such a prestigious institution. During a time of economic recession in Spain, the mental freedom and financial security BSC provided me cannot be understated. I thank BSC for providing an environment filled with brilliant and accomplished professors and peers, especially with regards to my research group HetroArch. I will always fondly remember my time with the members of HetroArch, especially, Rico, Carlos, Rajo, Puzo, Renan, Dani, Milan, Thomas, Petar, Victor and Ugi, with whom I've had both intellectually challenging conversations as well as IQ-dulling parties. I also thank BSC for all of its resources from support teams to HR to its cutting-edge facilities and access to one of the world's fastest supercomputers.

I thank the Department of Computer Architecture (DAC) at the Universitat Politecnica de Catalunya (UPC) and its administration for their support in all my PhD requirements. I thank my funding institutions Universitat Politecnica de Catalunya (UPC) and the Generalitat de Catalunya for providing me with the FPI-UPC and the FI-AGAUR grants for PhD research. I thank the institution HiPEAC for their various workshops and internship opportunities, which lead to an internship and my first job at Samsung Electronics, UK.

I thank my Guru, undergraduate research advisor, Prof. Waran, whom I will always

be indebted to for my interest in research that drove me into taking up a PhD.

My time in Barcelona could not have been half as fun or memorable without my friends. I thank in no particular order, Shrikanth, Vinoth, Ramnath, Hasini, Aswin, Rajagopal, Dharshan, Sundaramoorthy, Sudhanshu, Manish, Rahul, Gaurang and Martha for memories I will always cherish. I can in specific never forget my first years living in Avinguda de Madrid with Shrikath and Aswin; and living in Rossend Arus with Vinoth Sudhanshu, Hasini and Marta; and with Raja, Dharshan and Sundhar visiting. Going back home after a hard day's work or the disappointment due to the lack thereof, has been so much easier due to these guys. I want to give special thanks to my friend Javed back home for his support and especially for enduring through my rants and complaining when I didn't get the results I wanted from my research.

I want to thank Sai, my fiance, for she's been incredibly supportive especially when I've been down and the going got tough. She's often times the first to celebrate my success and the first to cheer me up when I'm down. I want to give special thanks to my cousin Yogesh and my sister-in-law Lans, for I've never made a major decision or celebrated a success without telling them or turning to their guidance. I want to thank Suresh mamma, Jayanthi athai and Ashwin for their constant encouragement throughout my PhD.

I finally want to thank my family, for without their support none of this would have been possible (and I would have found myself a real job sooner). I want to thank my wonderful brother and sister, Kathir and Krithigha, for their love and support, for making it so much fun to visit India after a year's work. I thank my father and mother, Mr. P.M. Saravanan and Mrs. P.S. Rupavathy, who are my pillars of support. They believed in me when I didn't believe in myself. My father's emphasis on facing challenges head-on and bravely gave me the confidence to pursue and persevere during my PhD. I cannot express the encouragement and confidence my mother can impart after just a phone call with her. For their selfless sacrifice, love and encouragement throughout my education, I dedicate this thesis.

# **Table of Contents**

| List of | Figures                                               | Хi   |

|---------|-------------------------------------------------------|------|

| List of | Tables                                                | xiii |

| Chapte  | r 1. Introduction                                     | 1    |

| 1.1     | Grand Challenge Problems and Impact                   | 2    |

| 1.2     | Supercomputers - Past, Present and Future             | 5    |

| 1.3     | The Problem of Energy                                 | 6    |

| 1.4     | HPC Fabrics - Is Ethernet Relevant?                   | 8    |

| 1.5     | Energy Efficiency in Ethernet (EEE)                   | 11   |

|         | 1.5.1 Performance-aware Energy Proportionality        | 12   |

| 1.6     | Contributions and Organization of this Thesis         | 13   |

| Chapte  | r 2. Background and Literature                        | 15   |

| 2.1     | Adaptive Link Rate                                    | 15   |

| 2.2     | Energy Efficient Ethernet: Low Power Idle/ Deep-Sleep | 16   |

| 2.3     | Moving forward - EEE on 40, 100, 400Gb Ethernet       | 18   |

| 2.4     | Energy Saving in Infiniband                           | 20   |

| 2.5     | Other Related Work                                    | 20   |

| Chapte  | r 3. Methodology                                      | 23   |

| 3.1     | Experimental Infrastructure                           | 23   |

| 3.2     | HPC Applications and Benchmarks                       | 25   |

|         | 3.2.1 Trace collection                                | 25   |

|         | 3.2.2 Trace processing                                | 27   |

| Chapte  | r 4. Energy Efficient Ethernet on HPC                 | 29   |

| 4.1     | Summary                                               | 29   |

| 4.2     | Methodology                                           | 30   |

| 4.3     | Interconnect sensitivity analysis                     | 32   |

| 4.4     | Idle link event time analysis                         | 34   |

| 4.5     | Performance and power analysis                        | 37   |

| 4.6     | Conclusions                                           | 41   |

TABLE OF CONTENTS x

| Chapte  | r 5. PerfBound: Bounding Performance Overheads                     | 42  |

|---------|--------------------------------------------------------------------|-----|

| 5.1     | Summary                                                            | 42  |

| 5.2     | Methodology                                                        | 44  |

| 5.3     | Motivation                                                         | 45  |

|         | 5.3.1 Understanding the overhead behind link wake-up               | 48  |

| 5.4     | PerfBound: Bounding performance overheads in on/off HPC links      | 52  |

| 5.5     | PerfBoundPredict: Prediction over PerfBound for On/Off networks    | 56  |

| 5.6     | Results                                                            | 61  |

| 5.7     | Conclusions                                                        | 63  |

| Chapte  | r 6. FastWake: Intermediate Power State                            | 64  |

| 6.1     | Summary                                                            | 64  |

| 6.2     | Approach to investigating Fast-Wake in HPC                         | 65  |

|         | 6.2.1 Methodology specifics                                        | 69  |

| 6.3     | Deep-Sleep and Fast-Wake vs Stall-time                             | 69  |

| 6.4     | Pareto optimal analysis of Fast-Wake and Deep-Sleep                |     |

| 6.5     | Fast-Wake on higher level links - L1, L2                           | 74  |

| 6.6     | Fast-Wake energy ratio - 40/60/80% and Fast-Wake timing analysis - |     |

|         | 500 ns                                                             | 76  |

| 6.7     | Ratio of energy savings between Fast-Wake and Deep-Sleep           | 78  |

| 6.8     | Conclusions                                                        | 79  |

| Chapte  | r 7. Double PerfBound: PerfBound on Fast-Wake                      | 80  |

| 7.1     | Summary                                                            | 80  |

| 7.2     | Motivation                                                         | 81  |

| 7.3     | Relating link wake-ups to the Stall-Timer                          | 83  |

| 7.4     | DoublePerfBound: Fast-Wake + PerfBound                             | 84  |

|         | 7.4.1 Single Stall-Timer case                                      | 85  |

|         | 7.4.2 Extending PerfBound to hybrid Fast-Wake + Deep-Sleep         | 85  |

|         | 7.4.3 Stall-Timer Error Correction                                 | 89  |

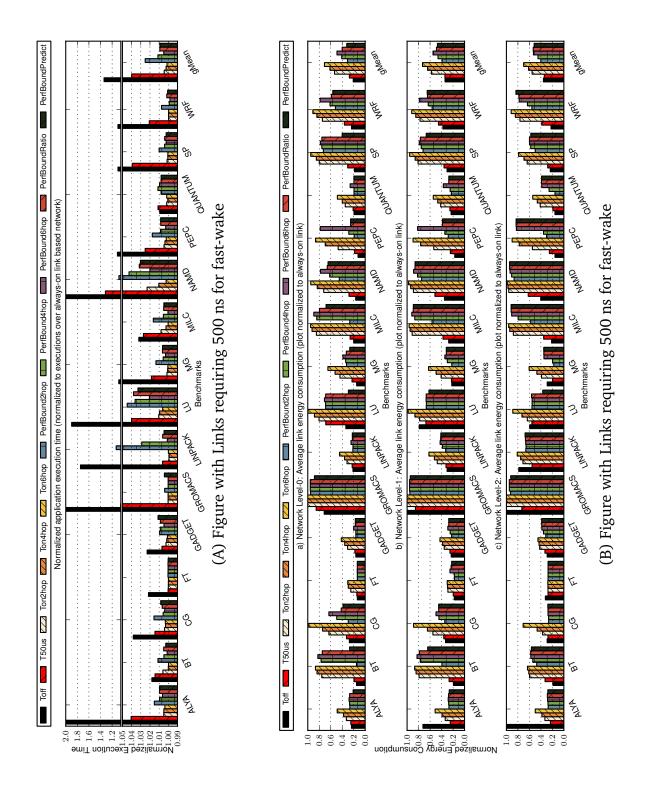

| 7.5     | Results                                                            | 91  |

|         | 7.5.1 Discussion                                                   | 94  |

| 7.6     | Conclusions                                                        | 95  |

|         | r 8. Conclusions                                                   | 96  |

|         | General discussion and Potential extensions                        |     |

| 8.2     | Work published                                                     | 99  |

| Referen | aces                                                               | 100 |

# **List of Figures**

| Figure 1.1                           | System share of Interconnects in TOP500 supercomputers                                                                                                                                                                                                                                                                              | 7  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2                           | System share of Interconnects in TOP500 supercomputers stacked                                                                                                                                                                                                                                                                      | 9  |

| Figure 1.3                           | System share of Interconnects in TOP500 supercomputers - Ethernet                                                                                                                                                                                                                                                                   |    |

| based                                | machines constitute about 40% every year                                                                                                                                                                                                                                                                                            | 10 |

| Figure 2.1<br>Efficie                | State transitions between active and low-power modes in Energy nt Ethernet (EEE): Low Power Idle (LPI)                                                                                                                                                                                                                              | 17 |

| ergy c                               | oad (figure reproduced from literature (23)); Figure shows how enonsumption of Energy Efficient Ethernet links quickly increases with                                                                                                                                                                                               |    |

|                                      | se in load                                                                                                                                                                                                                                                                                                                          | 18 |

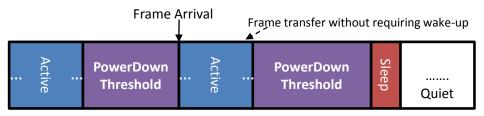

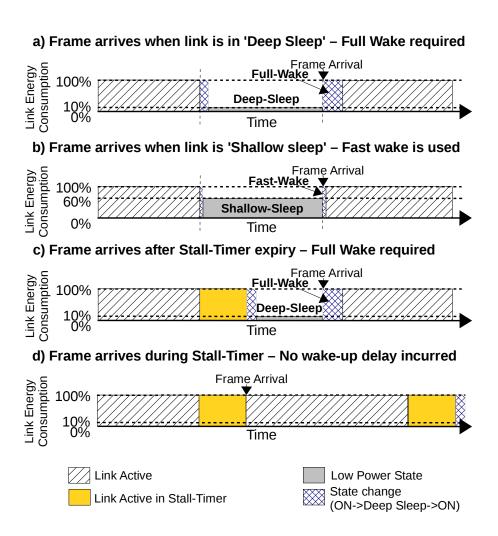

| •                                    | Example timeline illustrating various low power states of an EEE link.                                                                                                                                                                                                                                                              | 19 |

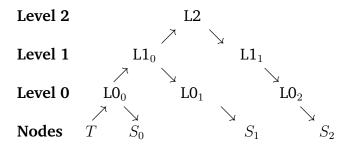

| Figure 3.1 Bound                     | Network organization used in the discussion and analysis of Perfl, Fast-Wake and Double PerfBound discussed in Chapters 5, 6 & 7                                                                                                                                                                                                    |    |

|                                      | tively                                                                                                                                                                                                                                                                                                                              | 25 |

| Figure 3.2                           | Visualization of application FT, a sample Extrae generated trace on                                                                                                                                                                                                                                                                 |    |

| Parave                               |                                                                                                                                                                                                                                                                                                                                     | 27 |

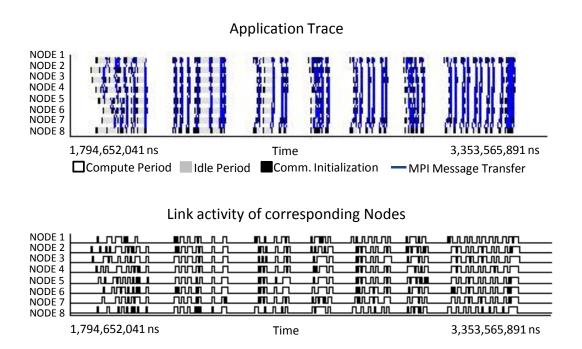

| a) A o                               | Execution and Link activity pattern of WRF application. Sub-figure cut of the actual application run showing execution patterns. Sub-b) Link activity corresponding to execution - peaks represent data mission. Note that communication occurs in phases and are corre-                                                            |    |

| lated.                               |                                                                                                                                                                                                                                                                                                                                     | 33 |

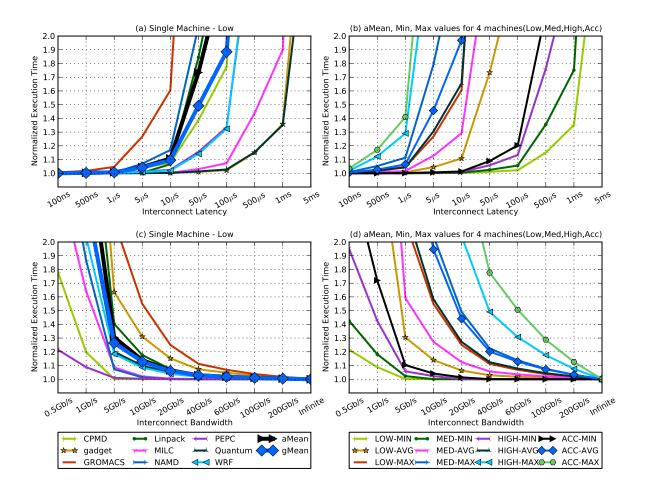

|                                      | Bandwidth and Latency sensitivity of the applications executed on ur test machines (Low, Med, High and Acc).                                                                                                                                                                                                                        | 34 |

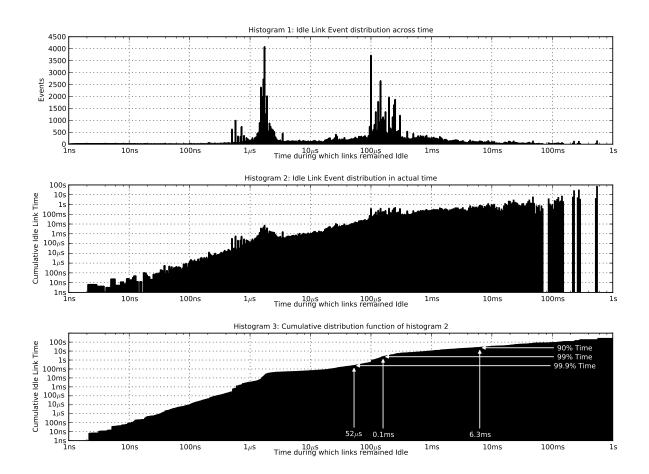

| <i>GET</i> ru<br>link ev<br>idle lin | Histograms show Idle Link Event distribution for application <i>GAD</i> -unning on Machine-Mid. Histogram 1 (top) shows the number of idle vents as a function of time. Histogram 2 shows a product of total nk events by idle link time for the corresponding events. Histogram 3 the cumulative distribution graph of Histogram 2 | 36 |

| Figure 4.4                           |                                                                                                                                                                                                                                                                                                                                     |    |

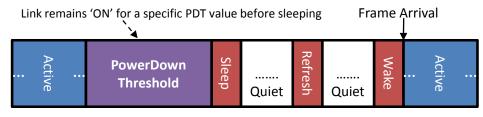

| Idle in                              | Energy Efficient Ethernet - Link remains in 'on' state after frame hission for specific PDT time. Frame arrival within PDT time does not                                                                                                                                                                                            |    |

|                                      | additional latencies for the turning off and on the link                                                                                                                                                                                                                                                                            | 39 |

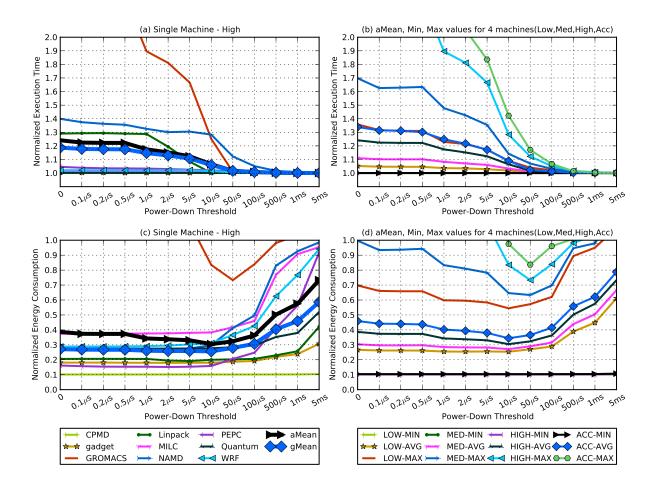

| Figure 4.5                           | Performance and power graphs of Energy Efficient Ethernet over                                                                                                                                                                                                                                                                      |    |

| U                                    | sed Power-Down Threshold                                                                                                                                                                                                                                                                                                            | 40 |

LIST OF FIGURES xii

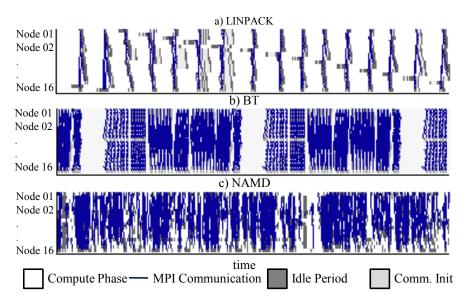

| Figure 5.1  | Communication behavior in HPC applications - LINPACK[78], BT[74]         |    |

|-------------|--------------------------------------------------------------------------|----|

| and N       | AMD[80]                                                                  | 46 |

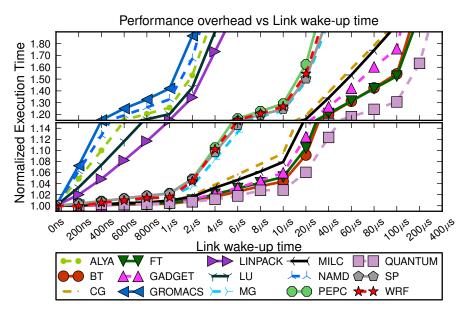

| Figure 5.2  | Application performance overhead as a function of wake-up delay          | 47 |

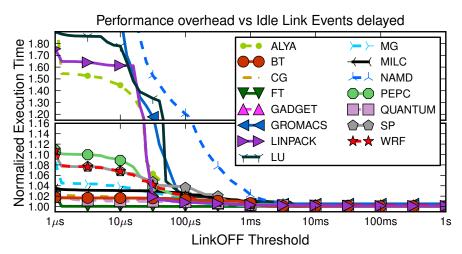

| Figure 5.3  | Application performance overhead as LinkOFF threshold is varied -        |    |

| norma       | lised to execution over an always-on network                             | 49 |

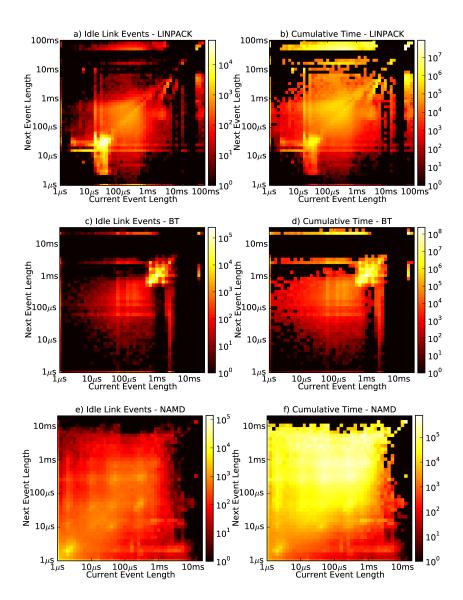

| Figure 5.4  | Idle Link Event distributions of LINPACK(a,b), BT(c,d), NAMD(e,f)        |    |

|             | c),(e) Heat map of the idle link event duration; (b),(d),(f) Heat map    |    |

| of tota     | l idle time (Number events $\times$ duration)                            | 50 |

| Figure 5.5  | Example network topology                                                 | 53 |

| Figure 5.6  | Snapshot of an Idle Link Event Histogram                                 | 55 |

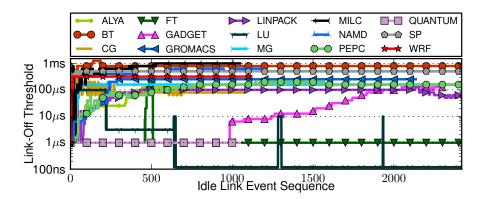

| Figure 5.7  | LinkOFF threshold convergence over time                                  | 56 |

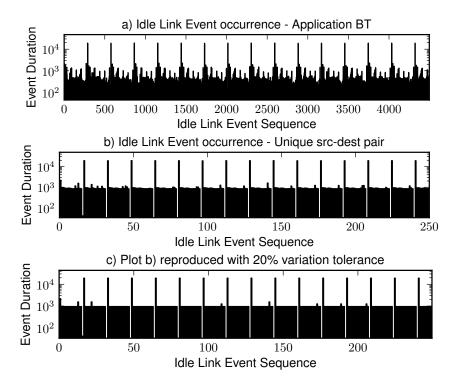

| Figure 5.8  | Idle link events sequence of occurrence                                  | 57 |

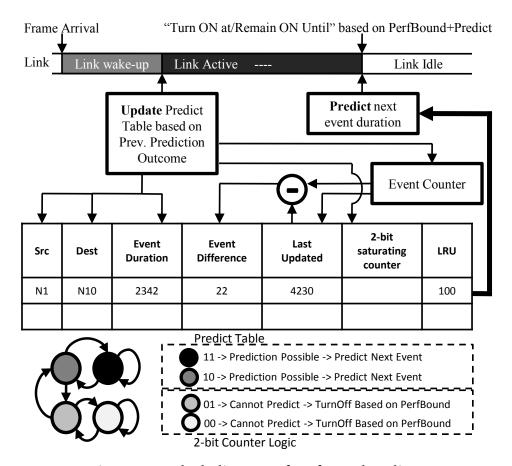

| Figure 5.9  | Block diagram of PerfBoundPredict                                        | 58 |

| Figure 5.10 | Application incurred performance overheads over techniques pro-          |    |

| posed.      |                                                                          | 60 |

| Figure 6.1  |                                                                          |    |

|             | of an EEE link                                                           | 67 |

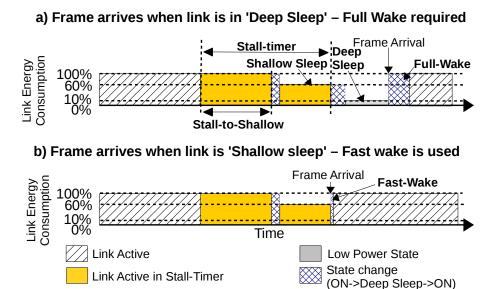

|             | Timeline illustrating hybrid Fast-Wake+Deep-Sleep                        | 68 |

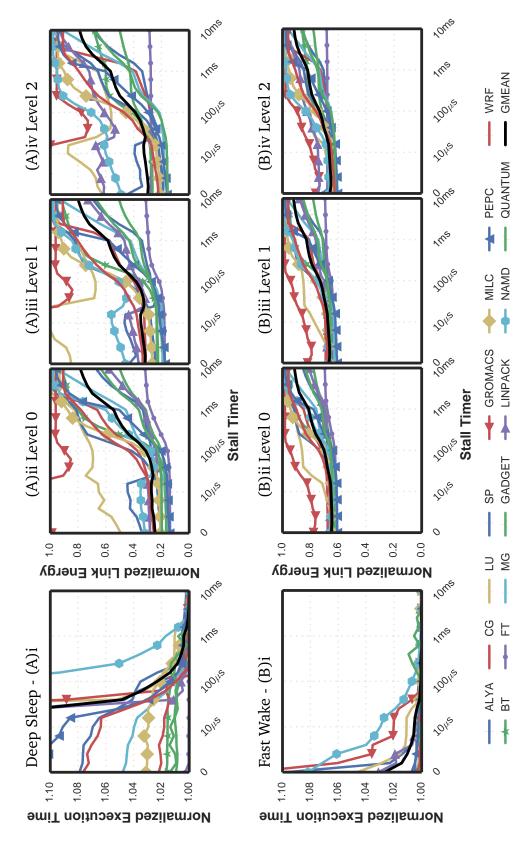

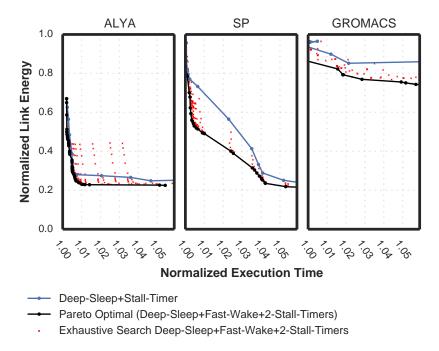

| _           | Power and Performance of using Deep-Sleep and Fast-Wake as a             |    |

| function    | on of their Stall-Timers                                                 | 71 |

| Figure 6.4  |                                                                          |    |

|             | using both Deep-Sleep and Fast-Wake along with their correspond-         |    |

| ing Sta     | all-Timers compared to only using Deep-Sleep and its Stall-Timer         | 73 |

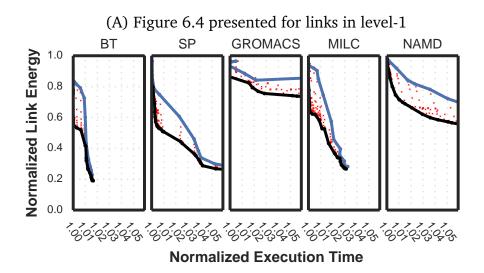

| Figure 6.5  | Fast-Wake analysis on upper layer network links                          | 75 |

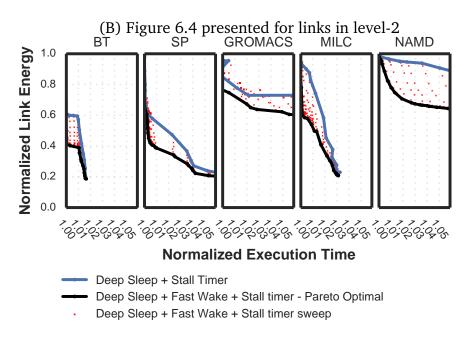

| Figure 6.6  | Fast-Wake analysis on link energy consumption and link wake-up           |    |

|             |                                                                          | 77 |

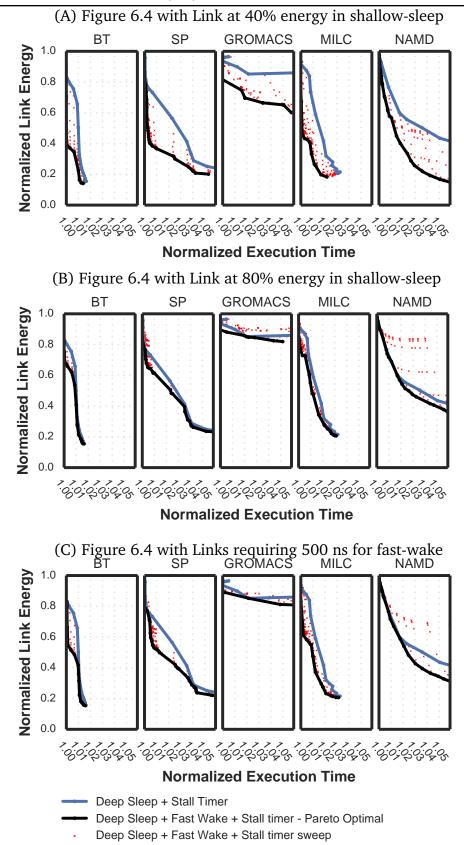

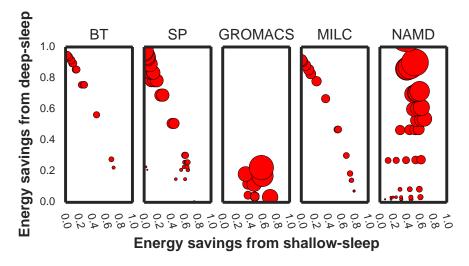

|             | Contribution of energy savings with Pareto-optimal points from Fig-      |    |

|             | 4 between Shallow-Sleep and Deep-Sleep                                   | 78 |

| Figure 7.1  |                                                                          |    |

| -           | and Fast-Wake vs. only using Deep-Sleep with Stall-Timers                | 83 |

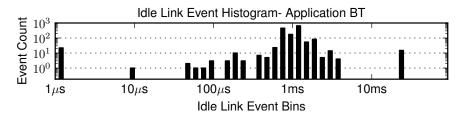

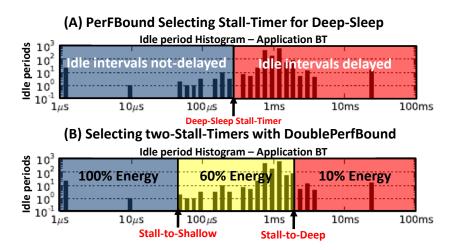

|             | Idle period histograms for Application BT, illustrating effect of Stall- |    |

|             | placement on link delay and energy savings                               | 86 |

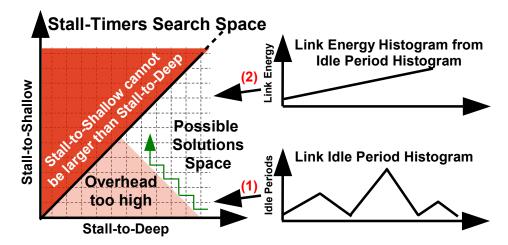

| Figure 7.3  | , , , ,                                                                  |    |

| _           | n used to find possible solutions and (2) for each possible solution,    |    |

|             | histogram is used to find lowest energy solution                         | 87 |

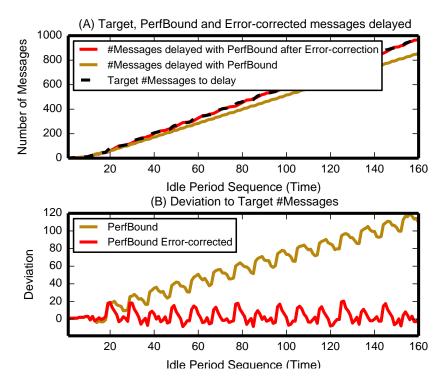

| Figure 7.4  | Stall-Timer Error Correction and #Target messages to actual mes-         |    |

| _           | delayed by PerfBound and DoublePerfBound for BT                          | 90 |

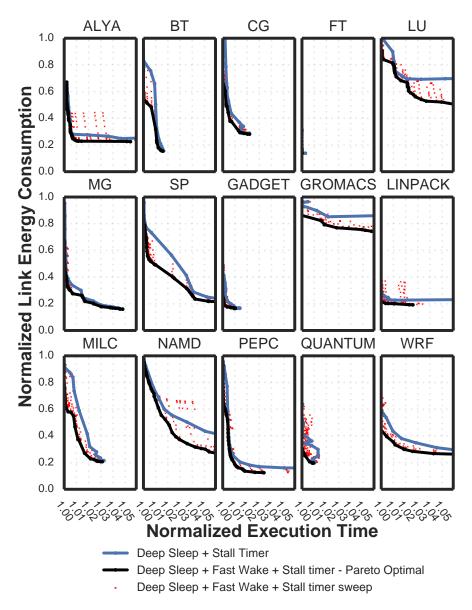

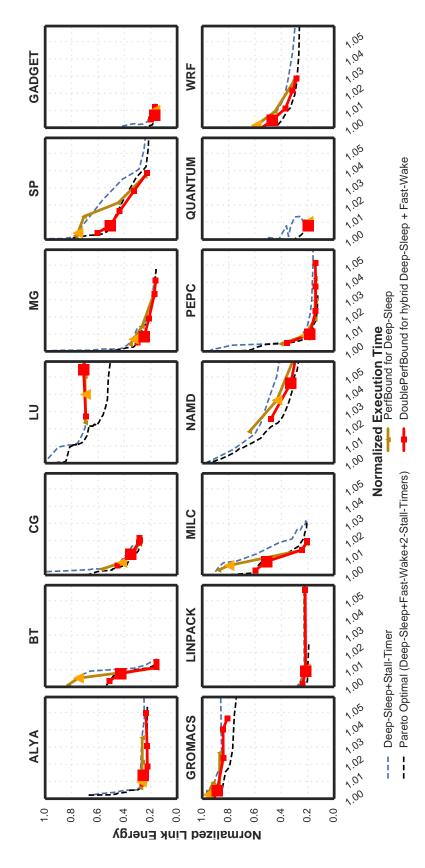

| Figure 7.5  | ē.                                                                       |    |

|             | and PerfBound (0.5%, 1% (large square and triangle), 2%, 3%              |    |

|             | %) compared to sweep analysis of Deep-Sleep and the Pareto-optimal       |    |

|             | of the hybrid Deep-Sleep+Fast-Wake mechanisms                            | 92 |

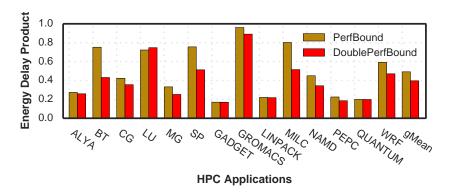

| Figure 7.6  | Energy Delay Product obtained from Figure 7.5                            | 94 |

# **List of Tables**

| Table 2.1 | Link parameters (wake, sleep, frame transmission time)                  | 17 |

|-----------|-------------------------------------------------------------------------|----|

| Table 3.1 | HPC Workloads used in simulations                                       | 26 |

| Table 4.1 | Network and node parameters for EEE evaluation                          | 31 |

| Table 4.2 | Distribution of link Idle times: The numbers indicate that 90%, 99%     |    |

| or 99     | .9% of the total time a link remains idle during the entire application |    |

| exect     | ition, comes from events where the link remains idle for a period above |    |

| the ta    | able specified time for their respective machines                       | 38 |

| Table 5.1 | PerfBoundRatio: Example calculation of local state, when 50%, 40%       |    |

| and 1     | 10% of messages reach levels 0, 1 and 2, respectively                   | 53 |

|           |                                                                         |    |

This page has been intentionally left blank.

# Chapter 1 Introduction

Theory and experimentation are often known as the pillars of the scientific method. Advancements pushing the limits of the traditional experimental methods have lead to computational sciences now constituting a *third pillar* to scientific inquiry. Many fields including physics, chemistry, biology, astronomy, climatology, economics, social science and engineering rely on computational sciences to explore and test uncharted possibilities where traditional experimentation is either not possible or too expensive in cost or time. The success of computational sciences is driven by High Performance Computers (HPC) or Supercomputers. Exponential improvement in processor technology has in turn made it possible to exponentially improve the computing throughput of supercomputers for decades. This improvement translates to simulating ever larger models and problems to solve large questions in science.

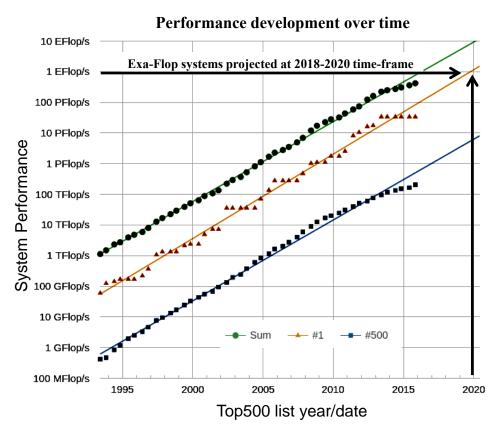

Since the 1990s, HPC performance has increased at an exponential rate, doubling roughly every 1.2 years. The fastest machine in the November 2015 TOP500 list [3], Tianhe-2 achieves 33 PF (Peta-FLOPS) on the TOP500's HPL benchmark, which is 33 quadrillion floating point operations per second. The next milestone for HPC performance is 1 EF (Exa-FLOP which is 1000 PF), which is expected to be achieved around the year 2018 [9, 11, 12]. Several challenges lie ahead in reaching Exa-FLOP performances, however, one of the key challenges is energy efficiency and proportionality<sup>1</sup>.

This thesis makes a case for a *performance-aware* approach to energy proportionality in HPC interconnects. Research focusing energy proportionality has made several strides over the compute components of the HPC system, making interconnect energy prominent. Interconnects are especially far from energy proportionality because their links (which constitute a significant proportion of the overall network energy) are always-on consuming energy regardless of their usage. Although several proposals have been made for energy proportionality in interconnects, they have not been adopted in HPC due to their possible unknown performance overheads. While energy

<sup>&</sup>lt;sup>1</sup>Energy proportional systems consume energy proportional to their usage

efficiency is a key challenge, performance is still the primary design objective in HPC and hence proposals are unlikely to be accepted unless the performance overheads are limited and well understood. This thesis explores HPC applications and interconnect energy savings from a performance perspective, building and analyzing techniques not only for energy saving but also for containing limiting performance overheads within acceptable bounds.

# 1.1 Grand Challenge Problems and Impact

HPC based research has a profound impact on science and technology advancements. Grand challenge problems are fundamental problems in science or engineering with broad applications, with solutions aimed to be obtained by HPC. [21] The following are few examples of Grand Challenge Problems and their potential Impact. However, besides the examples below, HPC also has wide applications in engineering fields in the research of more efficient manufacturing, automobile, aerospace, transportation management, in energy with nuclear research, efficient wind turbines and oil discovery, in Astronomy, in material sciences, etc. Considering the above, as discussed in the following sections and chapters, the benchmarks and applications used in this research are actual production applications from the fields of biomechanics, quantum chemistry, weather modeling, molecular dynamics, particle interactions, N-body simulation, etc.

#### Prediction of weather, climate global change

Research over the decades has provided unequivocal evidence for the warming the global climate system. Compelling evidence for rapid climate change comes from several sources that include, records of sea level rise, global temperature rise, warming oceans, shrinking ice sheets, etc. [20] From sea level rise threatening coastal regions to warming oceans and melting ice sheets changing entire ecosystems and food producing patterns, understanding and accurately predicting climate change is more important now than ever.

HPC is one of the foremost technologies in use towards the fight against global climate change. Supercomputers are widely used by multiple research centers around the world to run climate and weather models that predict global climates many decades

into the future to even predicting the odds of rain the next day. [20] These models extrapolate current and past patterns to give insights as to the impact of climate change in the future. Supercomputers are also widely used in number crunching (*Big Data*) and visualization, in obtaining meaning from data gathered by climate sensors and satellites. Modeling and simulating hurricanes and wind patterns are crucial to preparing for and averting natural disasters. Climate and weather modeling research while using the fastest supercomputers in the world, still require even faster machines for more accurate predictions and results [20]. Similar to the above, the aplication WRF - Weather Research and Forecasting Model, a numerical weather prediction system designed for both atmospheric research and operational forecasting needs is a part of the list of applications evaluated in this thesis.

#### Human Brain Project, Molecular Dynamics and Biomechanics

The Human Brain Project (HBP) [16] is a European Commission Future and Emerging Technologies flagship project that is primarily aimed at gaining a deep understanding of the workings of the Human Brain <sup>2</sup>. Understanding the Human Brain is critical to solving neurological disorders and brain diseases. HPB involves many sub-projects and research divisions, however primary objectives include modeling and simulating the brain. The project also includes research on HPC since the computing infrastructure required for simulating a human brain does not currently exist.

Simulating the brain over a computer provides for a non-invasive method of drug testing and discovery. While drug testing on animals is the norm, extensive drug testing on human brains involve legal and ethical complications. A computational model of the brain will speed up the process of drug testing and a better understanding of disease progression. Pattern in the data or biological signatures of diseases such as Alzheimer's will led to better classification, more accurate diagnoses and a more personalized medicine [16].

Several workloads evaluated in this thesis have applications in biology, specifically ALYA, GROMACS and NAMD. ALYA is a HPC based computational Biomechanics model for Supercomputers. Its designed to simulate and study the working of the human heart, Respiratory System, Skeletal Muscles among others. GROMACS stands for GROningen MAchine for Chemical Simulations and is a molecular dynamics package designed for simulating proteins, lipids, and nucleic acids. It is used to study protein

<sup>&</sup>lt;sup>2</sup>A similar project at the United States is the BRAIN Initiative [19]

folding, which in itself has applications in understanding and solving diseases. NAMD is a scalable molecular dynamics program used to study chemical interactions and for biomolecular modeling.

#### **CERN and HPC in Physics**

Research in CERN with its Large Hadron Collider (LHC) run experiments that probe into the fundamental nature of the universe. the Large Hadron Collider is the largest and the most powerful particle collider in the world. It is also the largest experimental facility ever built and is the largest machine in the world. Built by CERN - European Organization for Nuclear Research, LHC allows physicists to test predictions and theories from particle and high energy physics. It was instrumental in the discovery of the Higgs boson particle, which explains the existence of mass in the universe. Along with experiments into understanding the nature of the Higgs boson, many other particle predictions and unsolved questions in physics are expected to be solved with the use of the LHC [17].

The data produced by particle collisions at LHC is enormous and unprecedented and hence has one of the world's largest high performance computing facilities in the world, to store, distribute and analyze points of interest. While CERN by itself does not have the computing resources to compute the produced data, the data is computed by *Worldwide LHC Computing Grid*, a distributed computing infrastructure with supercomputers from around the world.

The above example in relation to CERN and LHC provides for one example in the role of HPC in the field of Physics. However, several applications and modelled to simulate and test theories in physics and cosmology. This thesis evaluates applications GADGET and MILC which both have their applications in Physics. GADGET specifically is a N-body simulation package used to simulate dark matter and gas interactions. MILC is used to study Quantum ChromoDynamics (QCD), the theory of the strong interactions of subatomic physics.

Besides the above, several other applications are used in this work and are discussed in the following chapters. Reaching exa-flop performances is key to solving several key challenges and problems. The following is a brief introduction to the evolution of supercomputers, leading up the the problem of exa-scale and energy as a key challenge.

## 1.2 Supercomputers - Past, Present and Future

Grand challenge problems have perpetually inspired faster and higher throughput supercomputers. Faster machines usually enable better and more accurate results and a possibility to simulate larger problem sets.

Although supercomputing dates back to 1960's, they only used a few processors [15] until 1990's which marked the beginning of massively parallel computers with thousands of processors. Performance increased from about 120 GF in 1993 with Fujitsu's Numerical Wind Tunnel machine to about 2.3 TF with the Intel ASCI machines from DoE-Sandia National Labs. The 1990s also marked the shift from vector processors to the use of commodity microprocessors in supercomputers, due to their better price to performance ratio of the latter.

Exponential improvement in performance continued through the 2000s. The years between 2000 and 2010 brought about several advances in technology with 1000x performance increase reaching Tera-FLOP to Peta-FLOP performances. The previous generation counterparts and the introduction of several of current day flagship machines where introduced during this period. The NEC Earth Simulator was the first supercomputer to reach 35 TFLOPS in throughput. Earth Simulator consisted of 640 nodes with 8 vector processors and 16 gigabytes of memory in each node. It was the fastest supercomputer in the world from 2002 and was surpassed by the Blue Gene/L machine in 2004.

The IBM's Blue Gene/L launched its landmark Blue Gene series of machines towards the end of 2004. The Blue Gene series introduced machines that had unprecedented scaling powered by a large number of relatively low performance but highly energy efficient processors. The Blue Gene/L introduced several unique innovations including, trading performance per core for lower power, dual processors per node, System-on-achip design, highly scalable machine that scales up to 65 thousand processors enabled by a 3-D torus interconnect and a light weight operating system. With unprecedented scaling, Blue Gene/P ranked, first in the Top500 list of the worlds fastest supercomputers, from November 2004 with 70 TFLOPS until November 2007 reaching nearly half a PFLOPS performance[3].

Following the BlueGene/P, the IBM Roadrunner was released in 2008, the first supercomputer to reach the PETA-FLOPS performance milestone. The Roadrunner was the first machine to use accelerators along with conventional processors, calling it then, a "hybrid approach". Alongside the Roadrunner, Cray Jaguar in 2009 and the Chinese

Tianhe-1A from 2010 reached 1.7 PFLOPS and 2.5 PFLOPS respectively.

In 2011, the K-Supercomputer from Japan was the first to reach 10 PFLOPS. Between 2011 and 2015, three other supercomputers BlueGene/Q, Titan and Tianhe-2 surpassed the K-Supercomputer with performance higher then 10 PFLOPS, with 17.1, 17.5 33.8 PFLOPS respectively (as of November 2015). The years between 2010 to 2015 also saw the emergence of GPU accelerator based supercomputers. From only nine supercomputers in the Top500 list[3] in 2010, that were built with accelerators, GPU based accelerator adoption has seen a steady increase with 89 machines as of November 2015.

Apart from performance improvements, last 10 years have also seen an increased emphasis on energy and power efficiency. The Green500 [4] list was established in 2006 to list 500 of the most energy and power efficient supercomputers in the world measured in FLOPS/WATT. From BlueGene/P ranking first with 357 MFLOPS/W in the first Green500 list in November 2007, energy/power efficiency has come a long way with the top machines in November 2015 measuring in with up to 7000 MFLOPS/W in the list. One key factor in driving increases in power/energy efficiency can be attributed to the use of accelerators. For example all of the top 40 systems in November 2015 Green 500 list use accelerators namely NVIDIA GPUs, AMD FirePro GPUs, Intel Phi or PEZY-SC. Even following the top 40, the next 40-100 systems are still primarily a mix of the above mentioned accelerators based systems or the BlueGene/Q.

The increase in emphasis in energy and power efficiency is critical to building future HPC. Past trends in exponential growth in HPC performance point to a 1 Exa-FLOP machine by the year 2018. Several challenges lie ahead of building exa-scale machines as seen in the subsequent sections.

# 1.3 The Problem of Energy

The Top500 trend-line for the fastest machine in the world, in Figure 1.1 <sup>3</sup> predicts Exa-FLOP HPC performance at about 2018-2020 time period. Several reports including DARPA [11] in 2008 and PRACE[18] in 2012 have called for addressing the several challenges and barriers that require crossing before reaching Exa-scale performance.

<sup>&</sup>lt;sup>3</sup>Obtained from the Top500 statistics page [3]

Architecture, micro-architecture, energy efficiency, power consumption, memory bandwidth/capacity, system and interconnect scaling, I/O bandwidth, resilience and reliability, algorithm and application scaling to state a few, require several innovations to allow for Exa-scale performance [11, 18].

Figure 1.1: System share of Interconnects in TOP500 supercomputers.

Of the mentioned challenges energy/power efficiency, in particular, is one of the key design criterion for modern supercomputers. Today's fastest supercomputer (as of June 2015, at 33.8 PF/ 17.8 MW [3] gives 1.9 GF/W), if extrapolated to a sustained ExaFlop performance, would have a total power consumption of about 500 MWatts. In contrast, US DOE, DARPA and other exa-scale HPC programs target the deployment of an ExaFlop machine by 2018 with power consumption of 20 MWatts [11, 12]. Building future supercomputers at such stringent power budgets requires eliminating every inefficiency throughout the system. Much effort in bringing about energy efficiency and energy proportionality to systems, has gone into optimizing the compute elements and memory, which constitute the majority of the system power consumption. However, recent trends show an increased emphasis on interconnects.

#### **Energy Proportionality in HPC Interconnects**

With compute nodes being power optimized and energy proportional, the interconnection network power has become increasingly significant. Power consumption of HPC interconnects can contribute to up to 12% of the overall energy costs of the system [34, 48] and even more when the system is not fully utilized. As with supercomputers, reducing interconnect power has become a pressing issue for Internet and IT infrastructure as well as servers and high-end data centers. Studies suggest an annual power consumption of 6 TWh consumed by networking devices alone in the US, and this figure is expected to further increase [55]. Since Ethernet is the dominant interconnect technology in commercial and IT infrastructure, improvements in its energy efficiency are estimated to bring about energy savings of over 3 TWh [55].

Interconnection links can be attributed to consuming a substantial portion of the total interconnect power. Links take up 64% of the power budget of the IBM InfiniBand 8-port 12X switch [32, 71] and 63%, 65% of the Dell PowerConnect 5324 and 6248 respectively [71]. In addition, conventional network links are essentially always on, thereby dissipating power, regardless of whether or not data is being transmitted. The average power consumption of the IBM InfiniBand 12X link, for example, is almost identical to its worst-case power [54, 71]. In the case of Ethernet, its design require both the transmitters and receivers to operate continuously to keep the link aligned. In order to mitigate such waste, the IEEE 802.3az Energy Efficient Ethernet (EEE) task force was setup and an energy efficiency standard for Ethernet was approved in September 2010. This thesis in specific, discusses interconnect energy proportionality as modeled based on Energy Efficient Ethernet for reasons discussed below.

## 1.4 HPC Fabrics - Is Ethernet Relevant?

This research specifically focuses on evaluating the use of Energy Efficient Ethernet for energy proportionality in HPC interconnects, its challenges and their solutions. Since Energy Efficient Ethernet is based on Ethernet technology, the question of whether Ethernet is relevant to HPC is discussed below.

Over the period of this research, between 2011 and 2015, HPC has seen the use of numerous interconnect technologies, broadly falling into the following categories, Ethernet based, InfiniBand based, proprietary and custom interconnects. Both proprietary

Figure 1.2: System share of Interconnects in TOP500 supercomputers stacked

and custom interconnects are as their name implies interconnects specifically built for their respective machines rather than off-the-shelf solutions such as Ethernet and Infini-Band. The K-Supercomputer from Japan's Tofu interconnect [38] is one such example of a custom as well as a proprietary interconnect. The Tofu is a 6-D mesh/torus built specifically for the K-Supercomputer. Its six dimensions interconnect, racks scaling the entire system at the lower dimension, boards at the middle and the processors on each system board at the highest dimensions of the network. Interconnects of the Cray systems - Aries and Gemini and the interconnects of Blue Gene series machines fall into this category.

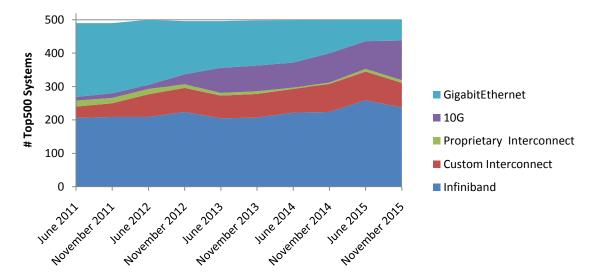

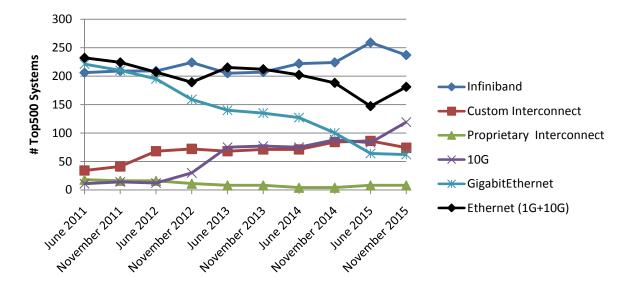

Figures 1.2 and 1.3 lists the system share of interconnects in the Top500 systems list. The Figure 1.2 is stacked showing the evolution of the above mentioned categories of interconnects over the years. In June 2011 GigaBit Ethernet, 10G Ethernet, Infini-Band, custom and proprietary interconnects add up to 490 systems, while the other 10 systems contained networks such as Myrinet [6], NUMAlink [7] and Quadrics [8].

#### **InfiniBand**

InfiniBand, over the years has held a large system share in the Top500 systems. Infini-Band is widely used in HPC for featuring very low latency, very high throughput high scalability and quality of service. Similar to Ethernet, InfiniBand is operated by a consortium with its standards organization called the InfiniBand Trade Association (IBTA)

Figure 1.3: System share of Interconnects in TOP500 supercomputers - Ethernet based machines constitute about 40% every year

publishing its first InfiniBand architecture in the year 2000. Since 2000, InfiniBand has seen steady increase in bandwidth and decrease in latency. The signaling rate has increased from 2.5 Gb/s in 2001 to 5, 10, 14 and 25Gb/s with SDR (Single Data Rate), DDR (Double Data Rate), QDR (Quadruple Data Rate), FDR (Fourteen Data Rate), and EDR (Enhanced Data Rate) respectively. These signaling rates are the theoretical throughputs for a single link (1x) and can be paired with 4x or up to 12x links, known as **Link Aggregation**, reaching up to 290 Gb/s with 12xEDR. The latencies from SDR to EDR has decreased over the years from  $5\mu s$  to  $0.5\mu s$  respectively. The Top500 system share of InfiniBand has steadily increased from about 200 in June 2011 to about 250 systems in November 2015.

#### **Ethernet - Gigabit Ethernet and 10G**

Ethernet compared to InfiniBand is an older and most widely used interconnect technology commonly used in local area networks (LANs) and metropolitan area networks (MANs). Dating back to first introduction as early as 1980s, Ethernet has become the standard for networking. Ethernet is a part of the IEEE 802 family of standards maintained by the IEEE 802 LAN/MAN Standards Committee (LMSC). Ethernet was introduced in HPC and featured in the Top500 machines list in the early 2000s with 10/100Mb/s and soon followed by the Gigabit Ethernet in 2002. Both Infiniband and

Ethernet saw increasing adoption in HPC markets over the years with the rise of commodity components based supercomputers. Ethernet specifically is popular for its wide spread use in LANs and MANs and its extremely cost- effective solutions, i.e., Ethernet based networking solutions are cheaper than the above mentioned Infiniband, proprietary and custom solutions. Traditionally Ethernet has lagged behind Infiniband and custom networks in latency and bandwidth, however, the gap between them has reduced over the years with the introduction of technologies such as iWarp [23] and RoCE (RDMA over Converged Ethernet) [24] and the recent standardization efforts targeting up to 400Gbit Ethernet. The most compelling reason for Ethernet's large adoption in HPC is its low cost and high performance.

Figure 1.3 presents system share of interconnects in the Top500 machines and as shown, Gigabit Ethernet has seen a steady decline over the years in its use. First featuring in the Top500 systems list in 2002, and by 2011, Gigabit Ethernet was used by more than 200 systems. As seen in the Figure 1.3, Gigabit Ethernet has seen a steady decline in its use between 2011 to 2015, however 10G Ethernet as shown has seen consistent rise in adoption. Combined, both Gigabit and 10G Ethernet (shown in black) is the most popular interconnect technology along side Infiniband. The share of Ethernet based machines over the years from 2011 to 2015 is shown in Figure 1.3. It is clear from the figure that a large proportion (about 40%) of HPC and Top500 machines are deployed with Ethernet.

# 1.5 Energy Efficiency in Ethernet (EEE)

As mentioned previously network links are traditionally always-on consuming power regardless of their usage. The ubiquitous nature of Ethernet with its wide spread use throughout the computing spectrum meant that optimization of the power consumption of Ethernet links translated directly to global energy savings from network infrastructure. The IEEE 802.3az Energy Efficient Ethernet (EEE) task force formed in 2007 aimed to make Ethernet links energy proportional. In considering several proposals, two approaches where most popular, Adaptive Link Rate (ALR) and Low Power Idle (LPI). The task force eventually adopted Low Power Idle (LPI) as the standard for Energy Efficient Ethernet (EEE). The Low Power Idle (LPI) converts the always-on link to an on/off based link where the link saves power at its low power off state. The standard published in 2010 provided mechanisms for implementing on/off based links to Ethernet switches.

The original Energy Efficient Ethernet (EEE) protocol, discussed thus far, provides specifications for energy savings on 100Mb, 1Gb and 10Gb links (Gigabit and 10G Ethernet). The success of EEE, current and recent efforts for the standardization of 40Gb, 100Gb and 400Gb backplanes and optical Ethernet, have opted to include and have included energy savings mechanisms from EEE. While incorporating EEE for 40Gb, 100Gb and 400Gb links, the standard further introduced alongside the older on/off based EEE, an additional intermediate sleep state. The intermediate sleep state is targeted towards a faster transition to fully active state in order to avoid excessive performance degradation due to state transitions.

These protocols, specifically IEEE 802.3bj and 802.3bm, providing standards for 40Gb and 100Gb backplanes and optical Ethernet, respectively, were ratified as recently as March 2015, and IEEE 802.3bs for 400Gb is expected to be ratified in 2017. As with the original EEE protocol, products based on the recent standards, may be deployed for HPC within a year, but it is likely that EEE will be disabled by default. With about 40% of Top500 HPC machines using Ethernet based interconnects every year, that could potentially have these protocols in their switches; it is imperative to understand the need for EEE, its performance impact and possible configuration parameters in the context of HPC applications.

## 1.5.1 Performance-aware Energy Proportionality

HPC applications require a high-performance interconnect to support their peak communications demand, but the average utilization of the network is low. Considering this, it is thus especially wasteful in HPC for its network links to remain always-on when its average the network utilization is low. A number of studies have proposed mechanisms to save interconnect link energy [13, 31, 48, 49, 63, 68]. These proposals fall into one of two main categories. Firstly, *on/off links* are powered down during idle periods. An important example is the above mentioned IEEE 802.3az Energy Efficient Ethernet (EEE) [2, 54]. Alternatively, *bandwidth tunable links* adapt the network bandwidth to the communication requirements, reducing the frequency or the number of channels when demand is low, and therefore also reducing the power consumption. An important example is InfiniBand, which implements variable bandwidth as well as a variable number of active  $1 \times 1$  links.

In both cases, changing power state incurs a delay; for example, EEE on a 10Gbps link requires about  $4\mu$ s to switch states. A similar delay in changing bandwidth has

been reported for Infiniband [48]. The physical layer specification provides the underlying mechanisms, but the decisions as to when to enter and leave power-saving states are left to the vendor. In EEE specifically, the protocol does not specifically define the heuristics behind state transitions. This is an area of active research where different heuristics targeting different workloads (including data centers) have been proposed [64]. These state change heuristics are critical, especially in HPC, for which, although energy- efficiency is increasingly important, the primary design objective is still performance. Any proposed energy-saving technique will only be adopted if there is no significant reduction in performance.

# 1.6 Contributions and Organization of this Thesis

This thesis discusses energy proportionality in HPC networks from a performance perspective. There are several challenges as discussed above that this thesis addresses in this context. The following are the broad novel contributions of this thesis, specific contributions are further discussed in the following chapters.

- 1. Evaluation of the Energy Efficient Ethernet protocol on HPC is presented. This thesis was the first to evaluate the potential of Energy Efficient Ethernet for link energy savings in the context of HPC. The presented analysis concludes that HPC applications have high potential for network energy savings however the wake-up and sleep delay introduced by EEE can cause performance overheads unless properly controlled.

- 2. Any technique used for energy savings can only be used if their performance overheads are controlled. The second contribution of this thesis proposes the use of PerfBound A technique that automatically manages on/off links such that performance overheads are limited, while savings link energy. An extension to PerfBound, PerfBoundRatio is presented that distributes an accepted the application overhead across all links of the network. This work also discusses a prediction method for saving link energy by predicting idle periods between messages.

- 3. Third contribution of this thesis evaluates and extension to the original Energy Efficient Ethernet protocol, Fast-Wake. Fast-Wake was added to EEE as a faster wake-up mechanism but that which also saves energy. This work shows that Fast-Wake on its own does not provide substantial benefits however, used along side the original on/off states proposed by EEE, can provide better energy savings.

4. The evaluation of Fast-Wake showed energy savings benefits in using an intermediate energy state. This benefit however cannot be realized unless the on/off states are properly managed. For this reason, the final contribution of this thesis presents DoublePerfBound that extends the previously proposed PerfBound to work for an intermediate state, alongside the original on/off states. DoublePerfBound automatically manages on/off links to obtain pareto-optimal energy savings to performance values.

The organization of the rest of this thesis is as follows. The next chapter presents background and literature, which discusses the necessary background behind Energy Efficient Ethernet and relevant related work. Chapter 3 presents the methodology used in the work. Chapters 4, 5, 6 and 7 discuss the four contributions of this thesis as presented above. Finally Chapter 8 concludes this work.

# Chapter 2 Background and Literature

By the year 2010, the Internet and specifically data centers accounted for 1.1% to 1.5% of global energy consumption, with this percentage having doubled since 2005 [46]. The growing energy cost of Internet infrastructure and data centers have pushed for energy proportionality <sup>1</sup> across the computing spectrum. Addressing the above, in 2010, the IEEE 802.3az Energy Efficient Ethernet Task Force published its standard for Ethernet energy efficiency [2, 54]. The goal of the task force was to reduce the significant contribution of network devices to the national power budget, especially since large sections of the Internet and data center infrastructure are built using Ethernet [54]. While a number of proposals for energy efficiency were considered, Adaptive Link Rate and Low Power Idle [2, 54] were the most popular choices. In following sections, we briefly discuss Adaptive Link Rate and Low Power Idle.

# 2.1 Adaptive Link Rate

From data centers to HPC to Internet communications, Interconnects in general are sparsely used. However, the power consumption of links (which takes up the majority of the interconnect power) remains the same regardless of whether or not there is data transmission [2, 54]. This led to studies focusing on building energy proportional links whose energy consumption roughly proportional to link usage. Many initial proposals in energy proportional interconnects were concepts similar to Adaptive Link Rate (ALR) [40, 41, 42, 43]. The idea behind ALR comes from the fact that a link's power increases with bandwidth. Example, a 100 Mb/s transceiver consumes about 0.25 W, whereas 1 Gb/s and 10 Gb/s transceivers consume about 0.7 W and 6 W respectively [35]. Furthermore, since these links typically consume the same power whether active and idle, it is beneficial to reduce the Ethernet link rate from 10 Gb/s link to 100 Mb/s link (say) during periods of inactivity.

<sup>&</sup>lt;sup>1</sup>Energy proportionality signifies energy consumption proportional to usage.

Although ALR promised large energy savings by making links energy proportional, its process of changing link rate required time in the range of milliseconds to a few seconds, which is far too large for many applications. This is in agreement with results presented in Chapter 4 which evaluates HPC applications for their sensitivity to increases in latency. While other alternatives to accelerate rate change were proposed [44], ALR still contained two major disadvantages. Firstly, despite the proposals to accelerate rate change, the time taken for rate change was still higher than acceptable ranges. The second disadvantage is that, although lesser power, Adaptive Link Rate still consumes power during idle periods of the interconnect. To illustrate, if a 10Gb/s link is rate adjusted to 1Gb/s during periods of inactivity, the inactive 1Gb/s link consumes power, even though no data is being transmitted.

# 2.2 Energy Efficient Ethernet: Low Power Idle/ Deep-Sleep

To solve the above conundrum, an alternative known as Low Power Idle [2, 54] was proposed. Low Power Idle (LPI) essentially switches *off* the links during periods of inactivity and turns them back *on* when needed. The key point is that switching *on* and *off* links with LPI is relatively much faster (order of microseconds) and the link speed is not changed. This scheme was chosen to be the standard accepted to be a part of IEEE 802.3az Energy Efficient Ethernet standard.

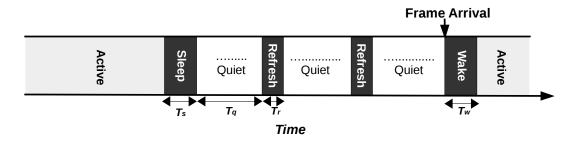

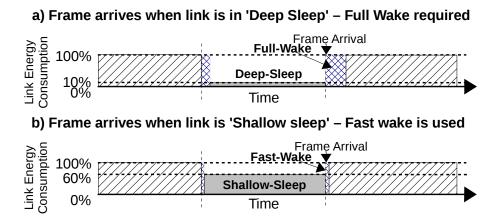

The Low Power Idle (LPI) mode of EEE proposes the use of "Sleep" and "Wake" modes to conserve power during periods of inactivity. Unlike complex mechanisms required to change the link speed in the case of ALR, Low Power Idle freezes the states of the transceiver when it enters the low power mode and restores it when links are powered back up. This operation can be performed in a few microseconds compared to milliseconds required for ALR [2]. Figure 2.1 shows a state transition example of a link that uses Low Power Idle. Here, the  $T_s$ ,  $T_w$  and  $T_r$  are the time taken to put the link to sleep, wake the link and refresh the link respectively. The periodic refresh in Figure 2.1 is to ensure the receiver elements are aligned with the channel during low power mode.

With regard to energy efficiency, link's power consumption during  $T_s$ ,  $T_w$  and  $T_r$  consumes the same power as when a link is in its *on* state and  $T_q$  consumes about 10% of the total power consumption of the link (here,  $T_r \ll T_q$ ) [2, 55]. Table 2.1 shows

Figure 2.1: State transitions between active and low-power modes in Energy Efficient Ethernet (EEE): Low Power Idle (LPI)

| Protocol              | $T_w$       | $T_s$       | $T_{Frame}$ (1500B)  | Frame eff. |

|-----------------------|-------------|-------------|----------------------|------------|

| 100Base-Tx (100 Mb/s) | 30 μs       | 100 μs      | 120 μs               | 48 %       |

| 1000Base-T (1 Gb/s)   | $16 \mu s$  | $182 \mu s$ | $12  \mu \mathrm{s}$ | 5.7%       |

| 10GBase-T (10 Gb/s)   | $448 \mu s$ | $288 \mu s$ | $12\mu\mathrm{s}$    | 14.6 %     |

Table 2.1: Link parameters (wake, sleep, frame transmission time)

the values for  $T_s$ ,  $T_w$  and frame transmission efficiencies based on IEEE 802.3az draft [1]. It is to be noted from Table 2.1 that the sleep and wake times are relatively large for small frames. This is to show that, EEE would typically work best for large bursts of communication activity followed by large periods of inactivity.

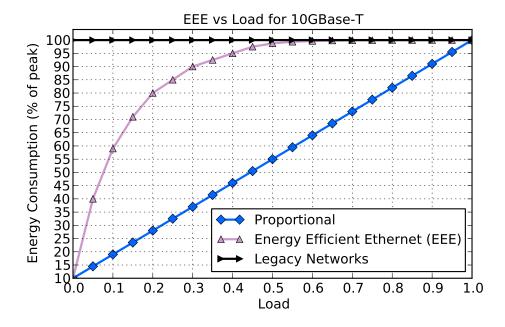

P. Reviriego et al., published an evaluation of Energy Efficient Ethernet [55]. Their results, as shown in figure 2.2, suggested that power savings with EEE links decrease quickly with an increase in link utilization above zero. According to their results, when the link utilization is at 20%, the corresponding link power consumption is greater than 70%. The results obtained were for 1000-bit frames arriving into the link following a Poisson process. The poor performance is shown to be a result of large wake-up and sleep overheads compared to actual frame transmission. Essentially, a majority of the time is being spent switching on and off the links leading to decreased performance. To solve the above problem, frame buffering was proposed which holds frames (without waking up the link) up to a certain number of frames or a time-out period. With an increase in time-out periods and/or by increasing the number of frames held in buffers, the results can be made more energy proportional. However this method comes with the cost of increased packet delay leading to performance degradation of latency sensitive applications. Results show that a time-out period of  $120 \,\mu s$  [54, 55] is required for the link to be energy proportional with increased link utilization. In the later chapters, we analyze the impact of such delays on HPC application performance.

# 2.3 Moving forward - EEE on 40, 100, 400Gb Ethernet

Energy Efficient Ethernet (EEE) with Fast-Wake: the 1Gb and 10Gb variant of Energy Efficient Ethernet (EEE) ratified in 2010, subsequent standardization efforts, which focused on building specifications for 40Gb, 100Gb and 400Gb backplane and optical Ethernet, adopted the energy savings mechanisms from EEE. In the process of integrating the aforementioned Low Power Idle or **Deep-Sleep** (as it is currently known and renamed), an additional sleep state, **Fast-Wake**, was first introduced by the IEEE 802.3bj task force in charge of the 100Gb Backplane and copper cable standardization effort.

Figure 2.2: Energy consumption vs load for 10Gb/s Link on data center-like workload (figure reproduced from literature (23)); Figure shows how energy consumption of Energy Efficient Ethernet links quickly increases with increase in load.

The motivation for a Fast-Wake mode came from the relatively high wake-up time of the Deep-Sleep mode, whose effect on performance is more pronounced at higher link speeds. The possible increase in latency due to Deep-Sleep is considered to be too high, so it is expected to be disabled for 100Gb links. The long wake-up delay in the original EEE standard comes from signaling components, specifically the Physical Medium Attachment (PMA) and Physical Medium Dependent (PMD) components in the PHY,

Figure 2.3: Example timeline illustrating various low power states of an EEE link

that are required to synchronize the transmitting and receiving links before data transmission. In the case of Fast-Wake, while some components are powered down, the PMA and PMD remain active, continually transmitting signals between transceiver and receiver, hence maintaining synchronization. This allows for a link wake-up in a few hundred nanoseconds, rather than microseconds. Specifically, studies show that the link could wake up from Fast-Wake mode in 250 ns to 500 ns, with power savings of 20–40%, compared to an active link [58]. Recent specifications show that Deep-Sleep may not be currently compatible with Optical Transport Network (OTN) based optical networks, however, the standards expect to incorporate Deep-Sleep in these devices in the future.

Figure 2.3 illustrates the working of the above described mechanisms using an EEE-based on/off link. In Figure 2.3(a), the link remains active during frame transfer, which is followed by a state change that turns off the link, reducing power consumption to 10%. The later frame arrival during Deep-Sleep requires a **Full-Wake**  $(4.48\,\mu\text{s})$  to power up the link to 100% before transmission. Figure 2.3(b) is similar to that of the Figure 2.3(a) except that the link powers down to **Shallow-Sleep**, which reduces power consumption to 60%. The link powers back to 100% faster with Fast-Wake, since it only requires a few hundred nanoseconds to do so.

Products supporting Fast-Wake may be deployed in HPC systems within a year. The standards supporting Fast-Wake are IEEE 802.3bj and 802.3bm, for 40Gb/100Gb backplanes and optical Ethernet, respectively, ratified as recently as March 2015, and IEEE 802.3bs for 400Gb, which is expected to be ratified in 2017. Switches that support EEE, targeting data centers, were commercially available within a year from the date

of standardization. Without investigation and understanding of Deep-Sleep and Fast-Wake on HPC applications with especially emphasis on their performance impact, HPC vendors are likely to disable these mechanisms by default. In the following chapters, this thesis discusses the performance and energy impact and benefits of these mechanisms respectively.

# 2.4 Energy Saving in Infiniband

Infiniband, as in the case of Ethernet is widely used in HPC. While the system share of Infiniband is about the same as Ethernet, its performance share is usually higher. Typically Infiniband supports two mechanisms that can be used for energy savings and they both focus on changing its operating bandwidth to save energy. First example is similar to the above mentioned Adaptive Link Rate (ALR) with link operating at different data rates, example Quad Data Rate at 10Gbit/s per serial lane and Single Data Rate (SDR) at 2.5 Gbit/s per lane. Lower data rates as in ALR require lower energy. Secondly, it is common for Infiniband to aggregate several serial lanes to form a single link as a means to increase effective bandwidth [56, 61]. In both the above cases, when the traffic is low, the idea behind saving link energy is to lower the operating frequency or number of lanes to their respective minimum since lower bandwidth and fewer operating lines consume lower power. This thesis specifically focuses on the Energy Efficient Ethernet for the following two reasons, 1. the results obtained are directly applicable to Ethernet vendors building EEE for HPC and 2. at the lowest energy state, Low Power Idle (LPI) and/or Deep-Sleep of Energy Efficient Ethernet consumes 10% power while even at lowest bandwidth Infiniband links consume 40% energy [48, 56, 61]. However, the results presented and approaches in turning links from active state to sleep state with EEE may directly be applicable to Infiniband in changing between fewer active links and a fully active link.

## 2.5 Other Related Work

In this section, we discuss other proposals related to Energy Efficient Ethernet (EEE) and energy-proportional interconnects. Jian Li et al.,[49] proposed a similar on/off based interconnect, which makes use of system events to overlap link *on* transaction delay. Their approach requires a control network which sends messages that switch

on the links prior to sending the message and thereby overlaps the link on transaction delay with the pre-processing of messages. The control network in their approach is required to be always powered on, in order to receive and transmit control signals. They evaluate their methodology over three power on modes, each with  $1\mu$ s,  $2\mu$ s and  $1\mu$ s as their wake-up delays over a simulated PowerPC-like 32 node machine. In our approach, we evaluate four different machines, over corresponding EEE standard defined wake-up and sleep delays, their effect on power and performance. Our model uses power estimates and energy efficiency schemes as proposed by EEE which does not assume the need for extra control networks. Alonso et al.,[66] in their work propose the use of traffic information to switch on or off networks to save power. Similar to the above, their approach requires an always-on control link to maintain connectivity.

Dannis et al.,[48] proposed energy proportional interconnects based on a similar method of reducing link power consumption. In their work on energy proportional interconnects, they evaluate the idea of reducing power consumption during periods of inactivity. However, their approach towards energy efficiency involves reducing the link rates of aggregated links. Aggregated links are typically networks built using multiple links of lower rate, aggregated to a single logical high bandwidth link. In their approach, during periods of inactivity, link rates are reduced to a lower link bandwidth to save power. This work is similar to Adaptive Link Rate proposals for EEE, mentioned in the section. We do not analyze Adaptive Link Rate due to the scheme's above mentioned technology disadvantages.

In the work by Vassos et al.,[65], they provide a design space analysis for On/Off based links. They evaluate two different machines for the power saving capability of On/Off interconnects. For their first machine, they use a fast interconnect similar to an on-chip interconnect, using corresponding on-chip benchmarks. In their second machine, they evaluate a slow network, similar to cluster networks using synthetic benchmarks, with messages arrival following a Poisson process. Similar Ethernet evaluation reports [54, 55] also use synthetic benchmarks to evaluate on/off networks.

Work by Kim, et al., [68] evaluate energy proportional networks and compare links based on dynamic voltage scaling and on/off links. They show that dynamic voltage scaling in links causes significant increase in latency and show that on/off based techniques perform comparatively better

S Miwa et al., [62] propose an evaluation method for EEE supported HPC systems. They show that their model can be used to anticipate performance of future systems that use EEE. Taylor et al., [59] explore dynamic energy saving features in Infiniband

networks and show potential for power savings.

Gupta, et al., in their work [67], show opportunistic sleeping of links is possible, their technique however increases mean latency. Totoni, et al., [72] show that not all links of a network executing an HPC application are utilized hence propose runtime techniques to find links in networks that are never utilized and turn them off. However, their work does not adaptively turn on/off links.

R. Bertran et al., [13], evaluate the power and performance trade- offs on the Blue Gene/Q. Among other results, their work shows that the links of Blue Gene/Q are also 'always-on' similar to that of Ethernet and Infiniband. Their work clearly makes a case of how the work presented in this thesis can also be applicable to non-Ethernet but on/off based networks.

J.A. Maestro et al., in their work [35] evaluate EEE for its potential over industrial Ethernet based systems using analytical models. Similarly, Sergio et al., in their work, analytically model and analyze the potential of EEE for energy savings[36]. They provide models for Ethernet standards with frame buffering. Their results suggest that frame buffering offers increased energy savings, however, with the cost of increased packet delays.

Relevant work on Energy Efficient Ethernet [2, 40, 41, 42, 43, 44, 54, 55, 57, 71] provide detailed evaluations on EEE for its potential for desktop and IT based systems; however, they do not give a sense of its performance over HPC.

Yoshi, et al., [70], propose ATPT - a prediction mechanism to find message sizes with src-dest pairs. The show that src-dest pairs could be used to improve prediction accuracy. When the size of the next message size is known, they tune the network frequency to the requirements of the next message size. Their work however does not predict idle link periods which are required for on/off based networks.

### Chapter 3 Methodology

This chapter presents the experimental methodology used in this work. Briefly, the simulation infrastructure used in this work, Dimemas Cluster simulator is discussed, followed by the model and configuration of the network and simulation parameters. HPC application traces were used to evaluate ideas presented in this thesis and its instrumentation and collection methods are discussed.

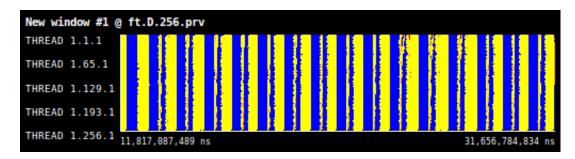

#### 3.1 Experimental Infrastructure

An extension of *Dimemas* [26, 27] cluster simulator is used for this work. Dimemas has been found to be accurate to within 10% and validated against production supercomputers, including Blue Gene/L, P, Q, and three generations of the MareNostrum supercomputer [27, 28, 29]. The simulation infrastructure supports the execution of *Paraver* [26] traces that for this work were obtained from a production supercomputer - MareNostrum II [53] built with PowerPC970MC blades. The simulator reconstructs the behavior of the actual application from traces that contain CPU intervals and MPI/communication event information (message size, identifiers, type, source-destination etc) from the original execution.

The simulator models simple node modules that contain CPUs, memory and onboard interconnect. Simulated CPUs based on their performance parameters operate relative to the actual application CPU (PowerPC970) intervals recorded in the traces. The default cluster network is modeled as a point-to-point bus based network with duplex independently operating ports, simulating a fully- connected mesh. The communication is based on a linear performance model, however non-linear effects are also considered [27]. More specifically, network conflicts are modeled, with messages queued before transmission when resources are unavailable. Any network conflict intern affects subsequent execution of compute events over CPUs delaying overall execution. Essentially, traces replayed in Dimemas contain inherent communication and

execution dependencies that are used to maintain coherency and correctness in simulations. Dimemas supports the execution of both point- to-point and collective MPI events however our simulations are based on traces while collective communication were mapped to represent their individual point-to- point messages. When representative network resources are allocated, messages transmission time is calculated using the latency, message size and bandwidth. Similar parameters are used in projecting the performance of CPU, Node and Memory.

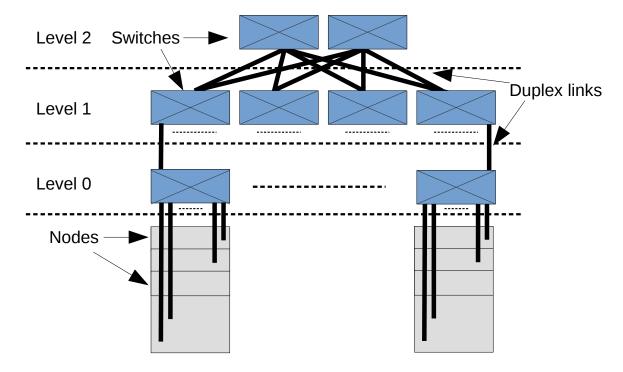

The first work on Energy Efficient Ethernet, presented in Chapter 4 uses the above mentioned point-to-point network modified support on/off links modeled for after Energy Efficient Ethernet. Carrying this work forward, work on all subsequent chapters 5, 6 and 7 uses a hierarchical network as discribed below. The simulator is configured to model a cluster with a three- level hierarchical network. Applications are executed on 64, 128 or 256 nodes, grouped into 8, 16, or 32 nodes per rack, respectively, forming eight racks in total. Nodes are connected to the top-of-rack switch, which is in-turn connected to a two-level fat tree (4-ary 2-tree) [30]. The architecture of the network used is shown in Figure 3.1.

The network was modified to support static routing with cut-through flow-control and full-duplex links. Each switch in the network routes incoming messages to corresponding outgoing links and requires a switching latency to be configured for the same. Routing decision is statically determined to be the shortest path between source and destination and when multiple paths of equal distance are available the route chosen is simply the modulo of destination times the number of available paths. The system and network parameters were chosen to emulate a high-end HPC system based on analysis of systems in the TOP500 list. Each node is a two-socket high-end CPU with  $225\,\text{GF}$  (based on June 2012 TOP500 list machines with two Intel Xeon sockets). The switch latency is configured at  $320\,\text{ns}$  for the first hop and  $80\,\text{ns}$  for subsequent hops to emulate about  $1\,\mu\text{ss}$  in end-to-end worst-case network latency. Edge links are configured at  $20\,\text{Gb/s}$ , and the higher two levels are  $40\,\text{Gb/s}$  and  $100\,\text{Gb/s}$  respectively. Wake-up and sleep timers for low power states were obtained from Energy Efficient Ethernet specifications and were set to  $4.48\,\mu\text{s}$  and  $3.88\,\mu\text{s}$  for Deep- Sleep [2, 54] and  $250\,\text{ns}$  for Fast- Wake [58] respectively.