# TRANSPARENT MANAGEMENT OF SCRATCHPAD MEMORIES IN SHARED MEMORY PROGRAMMING MODELS

# Lluc Álvarez Martí

Barcelona, 2015

**ADVISORS:**

**Xavier Martorell Bofill**

Universitat Politècnica de Catalunya Barcelona Supercomputing Center

Miquel Moretó Planas

Universitat Politècnica de Catalunya Barcelona Supercomputing Center

**Marc Casas Guix**

Barcelona Supercomputing Center

A thesis submitted in fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

# **Abstract**

Cache-coherent shared memory has traditionally been the favorite memory organization for chip multiprocessors thanks to its high degree of programmability. In this organization the cache hierarchy is in charge of moving the data and keeping it coherent between all the caches in the system, enabling the usage of shared memory programming models where the programmer does not need to carry out any data management operation. Unfortunately, performing all the data management operations in hardware causes severe problems, being the primary concerns the power consumption originated in the caches and the amount of coherence traffic in the interconnection network.

A good solution to these problems is to introduce ScratchPad Memories (SPMs) alongside the cache hierarchy, forming a hybrid memory hierarchy. SPMs are more power-efficient than caches and do not generate coherence traffic, but they degrade programmability. In particular, SPMs require the programmer to partition the data, to program data transfers, and to keep coherence between different copies of the data.

A promising solution to exploit the benefits of the SPMs without introducing programmability difficulties is to allow the programmer to use shared memory programming models and to automatically generate code that manages the SPMs. Unfortunately, current compilers and runtime systems encounter serious limitations to automatically generate code for hybrid memory hierarchies from shared memory programming models.

This thesis proposes to transparently manage the SPMs of hybrid memory hierarchies in shared memory programming models. In order to achieve this goal this thesis proposes a combination of hardware and compiler techniques to manage the SPMs in fork-join programming models and a set of runtime system techniques to manage the SPMs in task programming models. The proposed techniques allow to program hybrid memory hierarchies with these two well-known and easy-to-use forms of shared memory programming models, capitalizing on the benefits of hybrid memory hierarchies in terms of power consumption and network traffic without harming the programmability of the architecture.

The first contribution of this thesis is a hardware/software co-designed coherence protocol to transparently manage the SPMs of hybrid memory hierarchies in fork-join programming models. The solution allows the compiler to always generate code to manage the SPMs with tiling software caches, even in the presence of unknown memory aliasing hazards between memory references to the SPMs and to the cache hierarchy. On the software side, the compiler generates a special form of memory instruction for memory references with possible aliasing hazards. On the hardware side, the special memory instructions are diverted to the correct copy of the data using a set of directories that track what data is mapped to the SPMs.

The second contribution of this thesis is a set of runtime system techniques to manage the SPMs of hybrid memory hierarchies in task programming models. The proposed runtime system techniques exploit the characteristics of these programming models to map the data specified in the task dependences to the SPMs. Different policies are proposed to mitigate the communication costs of the data transfers, overlapping them with other execution phases such as the task scheduling phase or the execution of the previous task. The runtime system can also reduce the number of data transfers by using a task scheduler that exploits data locality in the SPMs. In addition, the proposed techniques are combined with mechanisms that reduce the impact of fine-grained tasks, such as hardware runtime systems or large SPM sizes.

The forthright accomplishment of the contributions of this thesis is that hybrid memory hierarchies can be programmed with fork-join and task programming models. Consequently, architectures with hybrid memory hierarchies can be exposed to the programmer as a shared memory multiprocessor, taking advantage of the benefits of the SPMs in power consumption and network traffic while maintaining the programming simplicity of shared memory programming models.

# **Contents**

| Al | bstrac | et       |            |                                           | i   |

|----|--------|----------|------------|-------------------------------------------|-----|

| C  | onten  | ts       |            |                                           | iii |

| 1  | Intr   | oductio  | n          |                                           | 1   |

|    | 1.1    | Thesis   | Objective  | es and Contributions                      | 4   |

|    |        | 1.1.1    | Automat    | ic Management of SPMs in Fork-Join Models | 5   |

|    |        | 1.1.2    | Automat    | ic Management of SPMs in Task Models      | 5   |

|    | 1.2    | Thesis   | Structure  |                                           | 6   |

| 2  | Stat   | e of the | Art        |                                           | 7   |

|    | 2.1    | Shared   | l Memory   | Multiprocessors                           | 7   |

|    |        | 2.1.1    | Shared N   | Memory Programming Models                 | 8   |

|    |        |          | 2.1.1.1    | Thread Libraries                          | 8   |

|    |        |          | 2.1.1.2    | OpenMP                                    | 8   |

|    |        |          | 2.1.1.3    | Task Programming Models                   | 10  |

|    |        | 2.1.2    | Cache-C    | oherent Shared Memory Hierarchies         | 11  |

|    |        |          | 2.1.2.1    | Cache Memories                            | 12  |

|    |        |          | 2.1.2.2    | Cache Coherence Protocol                  | 13  |

|    |        | 2.1.3    | Inefficie  | ncies of Cache Hierarchies                | 14  |

|    |        |          | 2.1.3.1    | Power Consumption                         | 14  |

|    |        |          | 2.1.3.2    | Coherence Traffic                         | 17  |

|    |        | 2.1.4    | Future D   | Pirections                                | 19  |

|    | 2.2    | Multip   | processors | with Scratchpad Memories                  | 20  |

|    |        | 2.2.1    | Embedde    | ed Processors                             | 20  |

|    |        | 2.2.2    | Cell B.E   |                                           | 22  |

|    |        | 2.2.3    | GPGPUs     |                                           | 25  |

## **CONTENTS**

|   |      | 2.2.4   | Stream A   | Architectures                         | 28 |

|---|------|---------|------------|---------------------------------------|----|

|   |      | 2.2.5   | Other Ar   | chitectures                           | 29 |

|   |      | 2.2.6   | Summar     | y                                     | 31 |

| 3 | Metl | hodolog | <b>y</b>   |                                       | 33 |

|   | 3.1  | Simula  | tion Infra | structure                             | 33 |

|   |      | 3.1.1   | Simulato   | ors                                   | 33 |

|   |      | 3.1.2   | Baseline   | Architecture                          | 34 |

|   |      | 3.1.3   | Operatin   | g System Support                      | 36 |

|   |      | 3.1.4   | Runtime    | Systems                               | 37 |

|   | 3.2  | Benchi  | marks      |                                       | 38 |

|   | 3.3  | Metric  | s          |                                       | 39 |

| 4 | SPM  | I Manaş | gement in  | Fork-Join Models                      | 41 |

|   | 4.1  | Tiling  | Software ( | Caches                                | 42 |

|   |      | 4.1.1   | Coherence  | ce Problem                            | 44 |

|   | 4.2  | Cohere  | ence Proto | col                                   | 44 |

|   |      | 4.2.1   | Compile    | r Support                             | 45 |

|   |      |         | 4.2.1.1    | Classification of Memory References   | 45 |

|   |      |         | 4.2.1.2    | Code Transformation                   | 46 |

|   |      |         | 4.2.1.3    | Code Generation                       | 46 |

|   |      | 4.2.2   | Hardwar    | e Design                              | 48 |

|   |      |         | 4.2.2.1    | Implementation of Hardware Structures | 49 |

|   |      |         | 4.2.2.2    | Execution of Memory Accesses          | 50 |

|   |      |         | 4.2.2.3    | Tracking SPMs Contents                | 54 |

|   |      |         | 4.2.2.4    | Maintaining Sequential Consistency    |    |

|   | 4.3  | Data C  | oherence   | Management                            | 57 |

|   |      | 4.3.1   |            | tes and Operations                    |    |

|   |      | 4.3.2   |            | ction                                 |    |

|   | 4.4  | Evalua  |            |                                       |    |

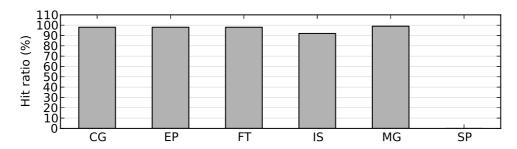

|   |      | 4.4.1   |            | ark Characterization                  |    |

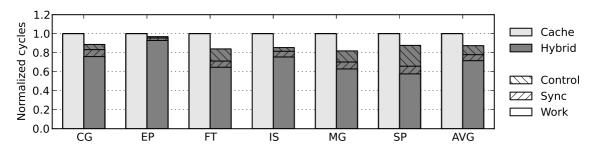

|   |      | 4.4.2   | Coherence  | ce Protocol Overheads                 | 61 |

|   |      | 4.4.3   |            | son with Cache Hierarchies            |    |

|   |      |         | 4.4.3.1    | Performance Evaluation                |    |

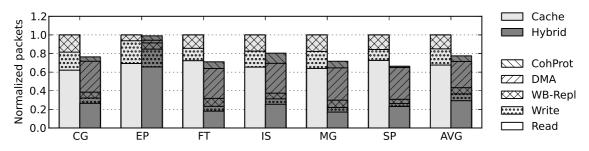

|   |      |         | 4.4.3.2    | NoC Traffic Evaluation                |    |

## **CONTENTS**

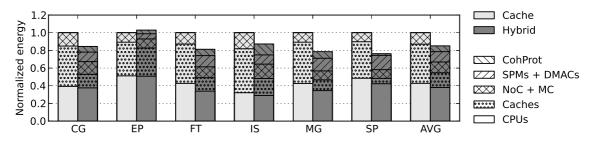

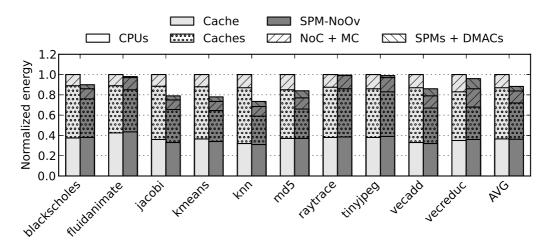

|    |         |               | 4.4.3.3     | Ene    | ergy ( | Consu   | ımpt  | ion I  | Eval | uat  | ion  |      |    |  |  |  |       | 65  |

|----|---------|---------------|-------------|--------|--------|---------|-------|--------|------|------|------|------|----|--|--|--|-------|-----|

|    | 4.5     | Summ          | ary and Co  | onclu  | ding   | Rema    | arks  |        |      |      |      |      |    |  |  |  |       | 66  |

| 5  | SPM     | I Mana        | gement in   | Task   | k Mo   | dels    |       |        |      |      |      |      |    |  |  |  |       | 67  |

|    | 5.1     | Suitab        | ility       |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 68  |

|    |         | 5.1.1         | Suitabilit  | ty of  | Other  | r Prog  | gram  | min    | g M  | ode  | els  |      |    |  |  |  |       | 69  |

|    | 5.2     | SPM N         | Manageme    | nt in  | Task   | Runt    | ime   | Syst   | ems  |      |      |      |    |  |  |  |       | 70  |

|    |         | 5.2.1         | Mapping     | g Data | a Dep  | ende    | nces  | to th  | ne S | PM   | Is   |      |    |  |  |  |       | 70  |

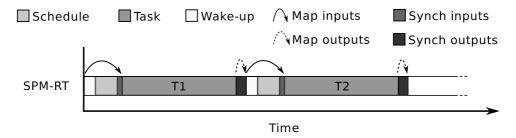

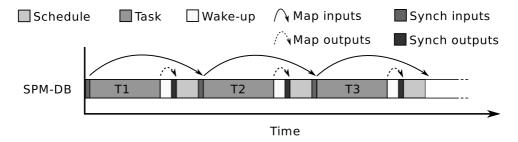

|    |         | 5.2.2         | Overlapp    | oing I | DMA    | Tran    | sfers | wit    | h Co | omj  | put  | atio | on |  |  |  |       | 73  |

|    |         | 5.2.3         | Locality-   | -Awa   | re Sc  | hedul   | ing . |        |      |      |      |      |    |  |  |  |       | 74  |

|    |         | 5.2.4         | Discussion  | on .   |        |         |       |        |      |      |      |      |    |  |  |  |       | 75  |

|    | 5.3     | Evalua        | ation       |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 76  |

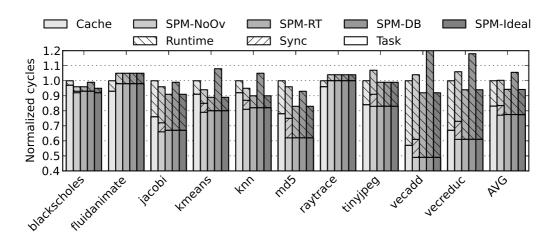

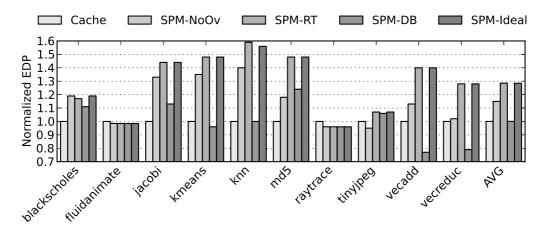

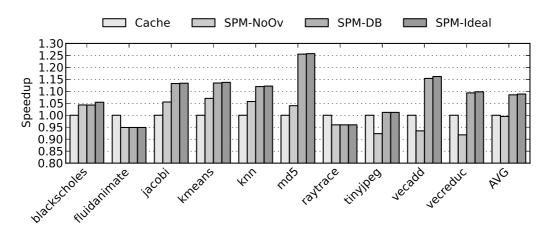

|    |         | 5.3.1         | Performa    | ance l | Evalu  | ıation  | ٠.    |        |      |      |      |      |    |  |  |  |       | 76  |

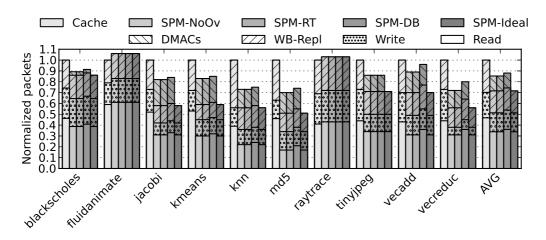

|    |         | 5.3.2         | NoC Tra     | ffic E | Evalua | ation   |       |        |      |      |      |      |    |  |  |  |       | 78  |

|    |         | 5.3.3         | Energy C    | Consu  | ımpti  | on Ev   | valua | ition  |      |      |      |      |    |  |  |  |       | 79  |

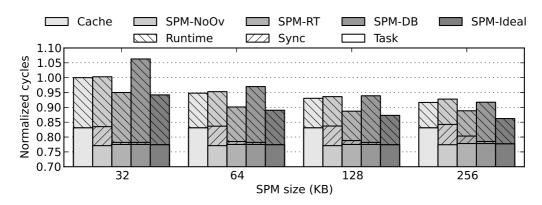

|    |         | 5.3.4         | Mitigatin   | ng the | e Effe | ects of | f Fin | e-Gı   | aine | ed T | Tas! | ks   |    |  |  |  |       | 80  |

|    | 5.4     | Summ          | ary and Co  | onclu  | ding   | Rema    | arks  |        |      |      |      |      | •  |  |  |  | <br>• | 82  |

| 6  | Con     | clusions      | S           |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 85  |

|    | 6.1     | Goals,        | Contributi  | ions a | and N  | Aain (  | Conc  | clusio | ons  |      |      |      |    |  |  |  |       | 85  |

|    | 6.2     | Future        | Work        |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 87  |

|    | 6.3     | Public        | ations      |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 88  |

|    |         | 6.3.1         | Publicati   | ions c | of the | Thes    | is .  |        |      |      |      |      |    |  |  |  |       | 88  |

|    |         | 6.3.2         | Other Pu    | ıblica | tions  |         |       |        |      |      |      |      |    |  |  |  |       | 89  |

|    | 6.4     | Financ        | cial Suppor | rt     |        |         |       |        |      |      |      |      | •  |  |  |  | <br>• | 90  |

| Bi | bliogi  | aphy          |             |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 93  |

| Li | st of I | Figures       |             |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 113 |

| Li | st of T | <b>Fables</b> |             |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 115 |

| Gl | ossar   | y             |             |        |        |         |       |        |      |      |      |      |    |  |  |  |       | 117 |

# Chapter 1

# Introduction

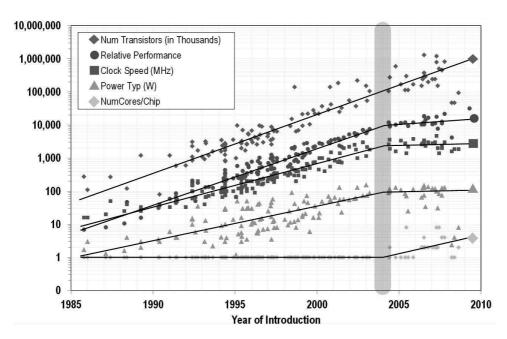

The evolution of microprocessors design has changed significantly in the last few decades. For many years the Moore's law drove the progress of every new generation of processors by increasing the number of transistors in the chip and its clock frequency, allowing to build faster and more complex single-core processors that could exploit the Instruction Level Parallelism (ILP) of sequential programs. As shown in Figure 1.1, this trend continued until the early 2000s, when the Moore's law encountered two fundamental obstacles: the ever increasing latency of memory accesses due to the speed gap between the processor and the main memory, known as the Memory Wall [156], and the ever increasing power consumption of chips with higher number of transistors and clock rates, known as the Power Wall [105] or the end of Dennard's scaling [44].

Figure 1.1: Evolution of microprocessors

In the early 2000s, to overcome the stagnation of single-core processors' performance, the landscape of microprocessors design entered the multicore era. Multicore processors can potentially provide the desired performance gains by exploiting the Task Level Parallelism (TLP) of parallel programs, but they have to face problems concerning the orchestration of parallel workloads such as the communication between cores or the concurrency in memory accesses. For this reason, a key element of multicore designs is the memory hierarchy that connects the different computing elements in the chip.

Cache-coherent shared memory has traditionally been the favorite on-chip memory hierarchy for multicore processors. The major reason for the success of this approach is its high programmability, which is achieved by moving data and keeping it coherent between all the caches of the system at the microarchitecture level, without any intervention from the programmer. This is accomplished by a hierarchy of caches, that exploit locality to keep the data close to the core that is accessing it, and by a cache coherence protocol, which manages the validity of the contents of all the caches in the chip to ensure that memory accesses are always served with non-stale values. Unfortunately, the cost of performing these actions in hardware becomes an obstacle to scale up the number of cores [136], being the primary concerns the power consumption originated in the caches and the amount of coherence traffic in the interconnection Network on-Chip (NoC) that is required to maintain all the data in a coherent state.

ScratchPad Memories [14] (SPMs) are a well-known alternative to cache hierarchies in domains where power-efficiency is of paramount importance. SPMs are simple pieces of memory with their own address space, directly addressable by the software and incoherent with the rest of memories in the chip. These memories are less complex than caches because they do not implement any mechanism to automatically request data or to track the state of the data that is being kept, so they can serve memory accesses as fast as caches but in a much more power-efficient way and without originating any coherence traffic. However, SPMs suffer from poor programmability as they require the software to explicitly transfer data between the SPMs and any other memory in the system and to keep coherence between different copies of the data in different address spaces.

The trend in the High Performance Computing (HPC) domain towards massively parallel manycore processors makes not possible to keep relying neither in purely cachecoherent memory hierarchies, due to their power consumption and scalability issues, nor in pure SPMs designs, due to their programmability issues. Instead, computer architecture for HPC is exhibiting a trend towards more heterogeneity, which has been shown

#### **CHAPTER 1. INTRODUCTION**

effective in architectures such as the Cell B. E. [79] or GPGPUs [66]. These designs have different kinds of cores and hybrid memory hierarchies that combine caches and SPMs to provide performance under an affordable power budget, but the programmability issue is still not solved [136]. Processors with hybrid memory hierarchies have very complex memory models that move away from the shared memory paradigm, which imposes serious limitations for the widespread usage of these systems. First, redefining the memory model breaks backwards compatibility, so every new architecture requires adapting scientific and industrial codes. Second, exposing deep and hybrid memory hierarchies to the programmer significantly degrades programmability, as the programmer needs to partition the data, explicitly transfer data between memory spaces, and handle potential data replications. Giving these responsibilities to the programmer complicates the process of writing the code and, more importantly, requires the programmer to have advanced knowledge of the architecture to perform the data management operations efficiently.

A promising solution to solve the programmability issues of hybrid memory hierarchies is to allow the programmer to use well-known shared memory programming models and to automatically generate code that manages the memory hierarchy. Shared memory programming models have been widely used since the first multicore architectures appeared, and they are easy to use because they rely on simple memory models exposed by multicores with cache-coherent memory hierarchies, so the programmer does not need to explicitly manage the data. Unfortunately, current compilers and runtime systems encounter serious limitations to automatically generate code for hybrid memory hierarchies from shared memory programming models.

Fork-join models like OpenMP [114] are the most traditional form of shared memory programming models. In these models sequential execution phases are interleaved with parallel phases that are specified by the programmer at designated points of the program. It has been shown in the past that a good way to manage SPMs in fork-join models is to use tiling software caches [55, 56, 67, 133]. Tiling software caches take advantage of the predictability of strided memory accesses to efficiently map them to the SPMs, while unpredictable random memory accesses are served by the cache hierarchy. Even though compilers succeed in transforming code to use tiling software caches when the computation is based on predictable memory access patterns, in the presence of unpredictable memory accesses they encounter important limitations [55, 56, 67]. Due to the incoherence between the SPMs and the cache hierarchy, the compiler cannot generate code for the SPMs if it cannot ensure that there is no aliasing between two memory references that

may target copies of the same data in the SPMs and in the cache hierarchy. This memory aliasing problem greatly restricts the ability of the compiler to generate code for hybrid memory hierarchies in non-trivial cases.

The expected heterogeneity of future manycore architectures has caused that, in recent years, task programming models such as the task extensions introduced in OpenMP 4.0 [115] have emerged. In these programming models the programmer exposes the available parallelism of an application by splitting the code in sequential pieces of work, called tasks, and by specifying the data and control dependences between them. With this information the runtime system manages the parallel execution of the workload following a data-flow scheme, scheduling tasks to cores and taking care of synchronization between tasks. In addition to the programmability advantages for complex heterogeneous architectures, a very important benefit of task programming models is that decoupling the application from the architecture also allows to take advantage of the available information in the runtime system to drive optimizations in a generic and application-agnostic way [146, 28, 119, 100, 101, 61]. Following this trend, a promising solution to manage the SPMs of hybrid memory hierarchies without affecting the programmability of the architecture is to adopt task programming models and to give the runtime system the responsibility of exploiting task annotations to map the data specified in the task dependences to the SPMs, so memory accesses to this data are served more efficiently during the execution of the tasks.

# 1.1 Thesis Objectives and Contributions

The main goal of this thesis is to propose a combination of hardware, compiler and runtime system techniques to manage the SPMs of hybrid memory hierarchies from shared memory parallel programming models, transparently to the programmer.

The contributions of this dissertation settle the most important limiting factors for the widespread usage of hybrid memory hierarchies. The forthright benefit of the proposed techniques is that they allow architectures with hybrid memory hierarchies to be programmed with well-known and easy-to-use shared memory parallel programming models, to keep the simplicity of memory models exposed by cache-coherent shared memory multiprocessors, and to preserve code portability. This allows to capitalize on the benefits of hybrid memory hierarchies in terms of power consumption and NoC traffic without affecting the programmability of the architecture.

#### **CHAPTER 1. INTRODUCTION**

In order to achieve these goals, this thesis proposes two different approaches for the automatic management of SPMs in the two most prominent forms of shared memory programming models: fork-join and task models.

### 1.1.1 Automatic Management of SPMs in Fork-Join Models

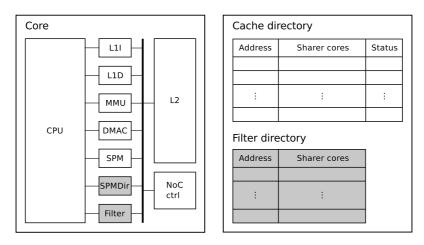

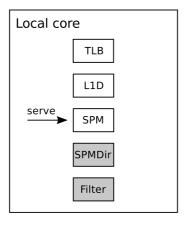

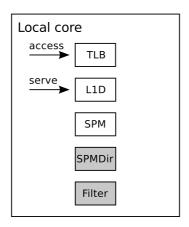

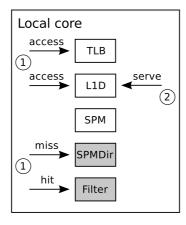

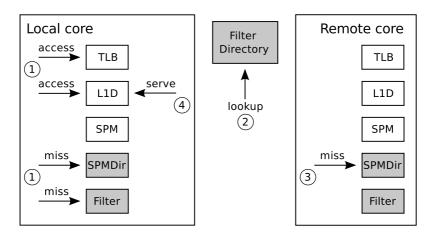

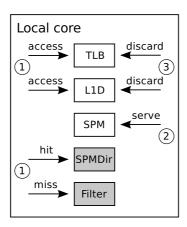

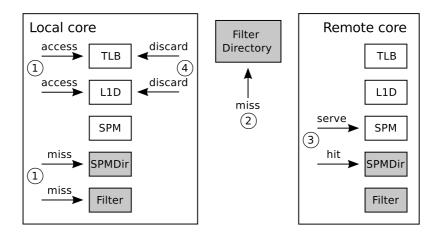

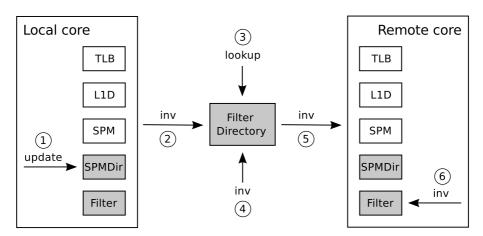

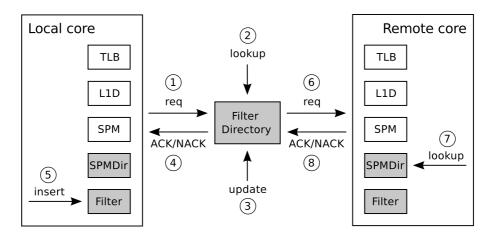

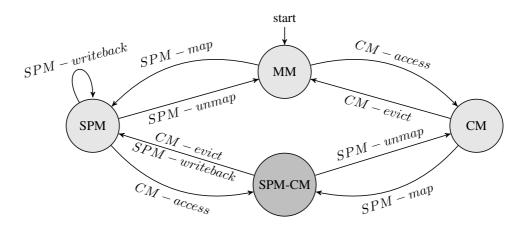

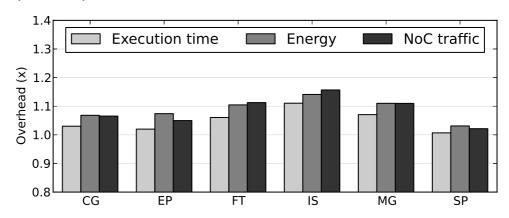

The first contribution of this thesis is a hardware/software co-designed coherence protocol that allows the compiler to always generate code to manage the SPMs of hybrid memory hierarchies in fork-join programming models, even if it encounters memory aliasing hazards between memory references to the SPMs and memory references to the cache hierarchy. On the software side, the proposed solution consists of simple modifications to the compiler analyses so that it can classify memory references in three categories: strided memory references, random memory references that do not alias with strided ones, and random memory references with unknown aliases. The compiler then transforms the code for the strided memory references to map them to the SPMs using tiling software caches while, for the random memory references that do not alias with strided ones, it generates memory instructions that access the address space of the cache hierarchy. For the random memory references with unknown aliasing hazards the compiler generates a special form of memory instruction that gives the hardware the responsibility to decide what memory is used to serve them. On the hardware side, a coherence protocol is proposed so that the architecture can serve the memory accesses with unknown aliasing hazards with the memory that keeps the valid copy of the data. For this purpose the hybrid memory hierarchy is extended with a set of directories and filters that track what part of the data set is mapped and not mapped to the SPMs. These new elements are checked at the execution of memory accesses with unknown aliases to divert them to the correct copy of the data, so all memory accesses can be correctly and efficiently served by the appropriate memory.

## 1.1.2 Automatic Management of SPMs in Task Models

The second contribution of this thesis is a set of techniques for runtime systems of task programming models to transparently manage the SPMs of hybrid memory hierarchies. The proposed extensions in the runtime system exploit the characteristics of task programming models to manage the SPMs very efficiently. Since the data dependences of a task are specified in the source code, the runtime system is aware of what data is going to be accessed by the task before it is executed, so it can exploit this information to map

the task dependences to the SPM of the core that is going to execute the task. In addition, the runtime system can take advantage of the execution model of task programming models to hide the communication costs of the data transfers required by the SPMs, either by overlapping them with other execution phases or by exploiting data locality in the task scheduling decisions. The proposed techniques also take into account that the size of the SPMs has a direct impact on the granularity of the tasks, so the study contemplates pairing the proposed SPM management strategies with different SPM sizes and task runtime systems with hardware support, analyzing the trade-offs of each solution in terms of performance, power consumption and NoC traffic.

## 1.2 Thesis Structure

The contents of this thesis are organized as follows:

Chapter 2 reviews the state of the art in cache-coherent shared memory multiprocessors and in shared memory programming programming models, exposing their main characteristics and problems. Then it describes the existing multiprocessors with hybrid memory hierarchies, explaining their architectural details, how each of them is programmed, and highlighting their programmability issues.

Chapter 3 introduces the simulation infrastructures and software environments used to perform the experiments described in this thesis, as well as the benchmarks and the metrics used for the evaluation of the proposals.

Chapter 4 presents the hardware/software co-designed coherence protocol to transparently manage the SPMs of hybrid memory hierarchies in fork-join programming models. The chapter first explains the internals of tiling software caches and the coherence problem they expose to then describe the compiler support and the hardware extensions of the proposed solution.

Chapter 5 proposes to manage the SPMs of hybrid memory hierarchies from the runtime system of task programming models. The chapter highlights the suitability of task programming models for SPMs, describes the extensions in the runtime system to manage them and analyses several techniques to minimize the overheads of the runtime system and the data transfers.

Chapter 6 concludes this dissertation by remarking its main contributions and by providing a brief summary of the future work.

# Chapter 2

# State of the Art

This chapter gives an overview of the state of the art in the area of chip multiprocessors and parallel programming models. The first section reviews shared memory multiprocessors, explaining the most relevant shared memory programming models that are used to program them, the cache-coherent shared memory organization that is used to support these programming models, the inefficiencies of current cache hierarchies, and the solutions proposed in the literature. The second section analyzes multiprocessors that incorporate SPMs in their memory hierarchies, discussing the architectural details of the different memory organizations, their implications on the programmability of the architecture, and the techniques proposed to automatically manage the SPMs without the intervention of the programmer.

## 2.1 Shared Memory Multiprocessors

Shared memory multiprocessors are the most genuine representatives of chip multiprocessors. This family embraces a wide number of chips, from the first commercial multicore processors that emerged in the early 2000s such as the IBM POWER4, the Intel Core Duo or the AMD Opteron, to current high-end manycore architectures for HPC such as the Intel Xeon Phi or the IBM Blue Gene/Q. The distinctive characteristic of shared memory multiprocessors is its memory organization, composed by a hierarchy of caches with a cache coherence protocol. This scheme allows the different cores to share data without any intervention from the programmer, enabling the usage of shared memory programming models to program the architecture.

## 2.1.1 Shared Memory Programming Models

Shared memory programming models offer a global virtual address space to allow multiple tasks to implicitly share data. These programming models have been the preferred option to program shared memory multiprocessors since they first appeared. Compared to other parallel programming paradigms, the shared memory approach is usually considered more productive, more intuitive, easier to learn, and easier to use, since it releases the programmer from the burden of explicitly distributing the data set of the application among tasks and explicitly communicating data between them. Instead, data is shared in the global address space and can be accessed by any task at any time and from any core. In addition, shared memory programming models are supported in most multicore and manycore architectures, so the same code can be executed in a broad range of processors. Although some tuning in the code is required to get the maximum performance of each particular architecture, code portability is a major advantage for the community as it drastically reduces development costs.

#### 2.1.1.1 Thread Libraries

The most basic representatives of shared memory programming models are the thread libraries offered by the Operating Systems (OSs). These libraries are used to expose the capabilities of shared memory multiprocessors to the software, offering low level functionalities to create threads, assign tasks to threads, and synchronize them. Examples of thread libraries are POSIX threads [29] as implemented in Linux [106], a slight variation for SUN Solaris platforms called Solaris threads [140], or the Win32 threads library [23] available in the different versions of Microsoft Windows.

Some programming languages offer thread libraries with similar characteristics, aiming to provide a low level thread interface that is portable across OSs. For instance, Java threads [111] are included as part of the standard Java Development Kit, and C++ [139] includes classes for thread management since its revision from 2011.

#### 2.1.1.2 **OpenMP**

OpenMP is the most commonly used programming model for shared memory multiprocessors. OpenMP allows to specify parallel constructs in C, C++ and Fortran using simple and portable compiler directives. These directives are supported by the vast majority of modern compilers and OSs for shared memory multiprocessors.

The core elements of OpenMP are the directives to specify parallel regions, workload distribution, data-environment management and thread synchronization. OpenMP uses a fork-join parallel execution model, where a single thread is used in sequential regions and the execution branches off in parallel at designated points in the program, specified by the programmer with the #pragma omp parallel directive. OpenMP also allows to specify how the work is distributed between threads in a parallel region, either assigning independent blocks of code to each thread using the #pragma omp section directive or distributing the loop iterations among threads using the #pragma omp for directive. The latter form is the one that exploits loop parallelism, which is the most commonly used parallelization pattern in OpenMP programs. In this model the schedule directive can be used to control how the iterations are distributed between the threads: a static assignment of iterations to threads, a dynamic scheme where threads request fixed-size blocks of loop iterations from a work queue, or a guided approach where threads dynamically request variable-size blocks of iterations. In addition, OpenMP allows to specify the sharing attributes of the data in any parallel region, that can be shared or private between threads, and supports synchronization directives such as critical for critical sections, atomic to update values in memory atomically or barrier to synchronize all threads in a point of the program.

The directives introduced by the programmer are processed by the compiler to generate parallel code. In this process the compiler arranges the code so that the parallel regions are encapsulated in separate functions, it sets up the declaration of the variables according to its sharing attributes, and it adds function calls to the runtime system in the points of the code where the parallelism is forked, joined and synchronized. When the code is executed the runtime system is in charge of managing the threads and the shared variables. For this purpose the runtime system provides routines to create threads, synchronize them, and destroy them. In order to assign tasks to threads the runtime system implements schedulers and work queues that support all the forms of parallelism allowed by the OpenMP directives. In addition, the runtime system maintains the versions of the shared variables as well as other internal control variables.

This coordinated effort between the compiler and the runtime system is what allows OpenMP to generate parallel code and to manage the parallel execution from simple directives. This model has been very successful because it allows to exploit the capabilities of shared memory multiprocessors with a programming interface that is easy to use for programmers and portable across many architectures and systems.

#### 2.1.1.3 Task Programming Models

Several task programming models have emerged in recent years to face the expected complexity of future heterogeneous multicore and manycore architectures. These programming models conceive the execution of a parallel program as a set of tasks with dependences among them.

In task programming models the programmer only has to split the serial code in tasks and to specify the dependences between the tasks. With this information the runtime system manages the parallel execution of the tasks, taking care of scheduling tasks to cores and synchronizing them without any intervention from the programmer. In order to manage the execution of the tasks the runtime system constructs a Task Dependence Graph (TDG), which is a directed acyclic graph where the nodes are tasks and the edges are dependences between them. Similarly to how an out-of-order processor schedules instructions, the runtime system schedules a task on a core when all its input dependences are ready and, when the execution of the task finishes, its output dependences become ready for the next tasks.

Task data-flow programming models are a subcategory of task programming models where the task dependences are represented with the data sets accessed by each task. In these models the programmer specifies the tasks and its associated data sets, which define three types of dependences: input dependences are memory regions read by a task, output dependences are memory regions written by a task, and input-output dependences are memory regions both read and written by a task. Many task data-flow programming models have been proposed recently. OpenMP 3.0 [9] provides compiler directives to support basic tasking constructs, that are extended with data dependences in OpenMP 4.0 [115], while OmpSs [51] extends OpenMP 4.0 with additional directives to specify task priorities and special tasking constructs. Other task programming models add language extensions to specify tasks and its associated data. The Codelets model [164] breaks applications into tasks with data and control dependences, and relies on this decomposition to improve load balancing and reduce data motion. Unlike in OpenMP 4.0, in Codelets the programmer needs to explicitly specify not only data dependences but also the particular codelet each dependence is associated with. StarPU [8] is a C API that allows to declare tasks and assign functions and data to them. Legion [16] programs are decomposed in tasks that access data partitions manually specified by the programmer, while in Sequoia [58] tasks have their private address space and it is the programmer who organizes them hierarchically. Charm++ [80] is a C++ based asynchronous message driven programming model where the programmer decomposes a program into message-driven objects called chares. Chares are distributed among the processors and the runtime system is in charge of sending messages to the chares to trigger the execution of the code within them. The Habanero [134] project proposes language extensions to C and Java to create tasks, express data locality and explicit communication between tasks.

Other task programming models allow to decompose a program in tasks, but they are not data-flow since tasks do not have data dependences between them. Intel TBB [126] is a C++ template library that implements a task execution model where the programmer splits the serial code into tasks that have implicit control dependences with their parents and children tasks. Cilk [26] extends C and C++ with keywords to spawn and synchronize tasks, and uses a simple fork-join model enhanced with work-stealing primitives to balance the load efficiently. Although it is not part of the standard language, Vandierendonck et al. [150] propose to extend Cilk with data dependences between tasks to ease programming parallel patterns such as pipelines. These extensions would turn Cilk into a task data-flow programming model.

The characteristics of task programming models make them very suitable for current and future heterogeneous architectures. The main reason is that these models allow the programmer to specify parallelism in an architecture-agnostic way, hiding to the programmer the complex architectural details and enabling the same code to be executed in very different platforms. In addition, the data dependences of task data-flow programming models can be used to program not only shared memory multiprocessors but also heterogeneous architectures that require explicit data transfer between address spaces, such as architectures with SPMs. Section 2.2 explains the most representative architectures with SPMs and also describes how task data-flow programming models are used to manage the memory hierarchy of some of these architectures.

## 2.1.2 Cache-Coherent Shared Memory Hierarchies

The cache-coherent memory hierarchy found in shared memory multiprocessors is the key element to implement a single address space where all the cores in the architecture can efficiently share data, which is the fundamental requirement to support shared memory programming models. This memory organization is composed of a set of cache memories organized hierarchically and a cache coherence protocol.

#### 2.1.2.1 Cache Memories

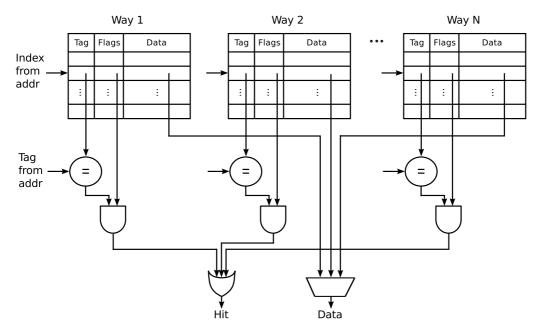

A fundamental part of cache-coherent shared memory hierarchies are the cache memories, or simply caches. Caches are pieces of memory that keep data close to the CPU that is accessing it. Figure 2.1 shows a scheme of a modern cache organization. A cache is a collection of cache blocks that contain the data, flag bits, and the tag of the block, which contains part of the address to which the data belongs to. Caches organize the blocks in different ways, that are accessed in parallel when a cache block is requested. In addition, since caches are self-managed, they also implement replacement algorithms to automatically allocate and evict cache blocks.

Figure 2.1: Cache memory organization

Shared memory multiprocessors incorporate multiple caches in a hierarchical organization. Current cache hierarchies usually implement two or thee levels of caches, where the first level uses small and fast caches and subsequent lower levels use bigger and slower caches. For example, the processors based on the Intel Broadwell microarchitecture have a cache hierarchy of three levels, where each core has separate L1 caches for data and instructions, each of 32 KB and 8-way associative, and an 8-way associative L2 cache of 256 KB, and all cores share a L3 cache of up to 6 MB that is 16-way associative. On the other hand, the Intel Xeon Phi uses a cache hierarchy of two levels where every core has separate 8-way associative L1 caches of 32 KB for data and instructions and an 8-way associative L2 cache of 512 KB.

#### 2.1.2.2 Cache Coherence Protocol

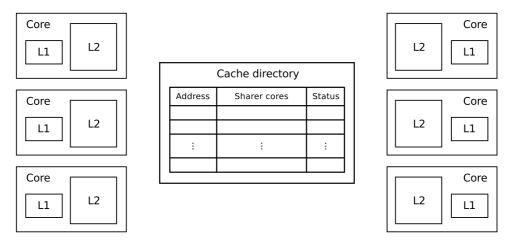

The cache coherence protocol is the mechanism that ensures that changes in the values of shared operands are propagated throughout the cache hierarchy. As a result, every core observes the last produced value and never consumes stale data. Current shared memory multiprocessors generally implement directory-based cache coherence protocols. In this scheme the data held in the caches is tracked by a cache directory that maintains coherence between all the caches.

The cache directory of the cache coherence protocol records the state of each cache block. As shown in Figure 2.2, the cache directory keeps, for each cache block, its state and a bit vector of sharer cores that tracks which cores have the cache block in its cache. Current shared memory multiprocessors typically use the MOESI cache coherence protocol, which uses five states for the cache blocks: modified (M), owned (O), exclusive (E), shared (S) and invalid (I). The cache directory acts as a manager to which the cores ask permission to request or write back a cache block and notify evictions and updates of a cache block. When the cache directory receives a message from a core it performs the actions defined in the cache coherence protocol to ensure coherence. Depending on the type of the request and the state of the cache block, the actions may involve reading data from memory or from some other cache, changing the state of the cache block, updating its sharer cores, invalidating cache blocks in other caches, etc.

Figure 2.2: Directory-based cache coherence protocol

#### 2.1.3 Inefficiencies of Cache Hierarchies

Cache-coherent memory hierarchies present many inefficiencies, specially when a large number of cores is integrated in the architecture. The primary concerns are the power consumption originated in the caches and the amount of NoC traffic generated by the cache coherence protocol to keep all the data in a coherent state.

#### 2.1.3.1 Power Consumption

The power consumption originated in the cache hierarchy is one of the most important problems of current shared memory multicore architectures. Caches dissipate a significant fraction of the overall power budget of the whole chip, up to 45% in current manycore architectures [136], due to their hardware complexity and their high utilization. In order to alleviate this problem a vast number of techniques have been proposed to reduce both the static and the dynamic power consumed in the caches.

Numerous works aim to save static power (also called leakage power) by powering down or off parts of the cache. Powell et al. [122] propose a Gated-Vdd technique to power off unused cache blocks, which drastically reduces their leakage power at the cost of losing their contents. Alternatively, Flautner et al. [59, 60] propose Drowsy Caches, which power down unused cache blocks by putting them in drowsy mode (a kind of sleep mode) to reduce their leakage power without losing their contents. Agarwal et al. [2] propose a gated-ground scheme that allows powering off cache blocks but still preserving their contents at the cost of minor performance and area overheads. The problem of these mechanisms is that, when a cache block is accessed, a cache miss occurs if the block is powered down or off, even if the cache has the block in valid state. Many heuristics have been proposed to overcome this problem, deciding when and which parts of the cache can be deactivated with minimal performance degradations.

Some heuristics aim to deactivate cache blocks individually. Cache Decay [83, 84] cuts off the power supply of cache blocks if a pre-set number of cycles have elapsed since their last access. Zhou et al. [162, 163] propose to deactivate only the data array of cache blocks so the tag array can be accessed to calculate the increase of the cache miss rate caused by turning off blocks, allowing fine-grained control of the performance losses and to re-activate cache blocks if needed. Drowsy Instruction Caches [87] monitor unconditional branches and subroutine calls and returns to predict and selectively wake up only the blocks that are going to be accessed in the instruction cache, allowing most

of the cache to stay in drowsy mode without significant performance losses. Li et al. [96] propose to deactivate L2 cache blocks when their data also exists in the L1 cache.

Other works propose more aggressive heuristics to deactivate complete cache ways. Albonesi [3] proposes Selective Cache Ways, a cache design that enables only a subset of the ways when the cache requirements of the running applications are low. In this design it is the software who explicitly turns on and off the cache ways using special instructions. C. Zhang et al. [157, 158] show that a very similar technique can be utilized in embedded processors, and W. Zhang et al. [160] propose two compiler algorithms to apply the same idea to instruction caches. Totoni et al. [144] use formal language theory to identify program phases and propose a runtime system that turns off cache ways at the start of each phase. Without any software support, Balasubramonian et al. [13] propose to detect program phases in the microarchitecture and to monitor the CPI, cache and TLB usage of each phase to turn off whole cache ways according to its requirements. Dhodapkar and Smith [47, 48] refine this approach by introducing a hardware structure that saves the appropriate configuration for each program phase.

The dynamic energy dissipated in the caches is another important concern in modern processors. This problem has also been widely studied, and various techniques have been proposed to alleviate it. In general, these approaches try to minimize the number of operations or the amount of data read and written on every cache access.

Way prediction is a technique that has been proposed to reduce the dynamic power consumption of caches. It consists on predicting which way of the cache will contain the data and accessing only the predicted way instead of all the ways in parallel. Way prediction was initially proposed by Calder et al. [30] to reduce the access time of sequential associative caches, analyzing different sources for the prediction such as the effective address, the registers used in the address calculation or the program counter of the instruction. Batson and Vijaykumar [15] show that very similar way prediction techniques can also achieve significant savings in dynamic energy. Inoue et al. [75] propose to keep the most recently accessed way to perform the prediction, and Powell et al. [123] show that combining way prediction in L1 instruction caches and selective direct-mapping in L1 data caches can further reduce the dynamic energy of the first level of the cache hierarchy. The main problem of way prediction is that it adds performance penalties when the accessed way is misspredicted and, moreover, it is mainly proposed for L1 caches because they present very predictable access patterns but, for lower level caches, it is not very effective since locality is hidden by previous cache levels.

Instead of prediction, way caching records the way of recently accessed cache blocks to reduce the dynamic energy of highly associative caches. Min et al. [102] propose to use a small Way Cache, a cache that stores the way accessed by previously observed cache accesses. If there is a hit in the Way Cache the data cache is accessed as a direct-mapped cache, otherwise it is referenced as a conventional associative cache. Nicolaescu et al. [109] propose to add coherence between the Way Cache and the data cache, invalidating Way Cache entries when blocks are evicted or invalidated from the data cache. This feature makes the contents of the Way Cache always correct, so the outcome is not a prediction but a determination. An important problem of these two works is that the Way Cache is accessed before the cache access, adding delays to the critical path of data accesses. Zheng et al. [161] propose Tag Check Elision, which determines the correct cache way early in the pipeline by doing a simple bounds check to decide if a memory access is to the same block as an earlier access. The bounds check occurs as soon as the virtual address is available, so it does not add any pipeline delay or performance degradation, and the TLB access can also be eliminated in a physically-tagged cache.

Other techniques are proposed to filter unnecessary accesses to cache ways. Zhang et al. [159] propose the Way-Halting Cache, that compares the four least significant bits of the tag during the index decoding to filter way accesses. This approach performs a fullyassociative search in the first comparison which negatively affects power consumption. Ghosh et al. [65] propose Way Guard, a mechanism for large associative caches that employs bloom filters to reduce dynamic energy by skipping the lookup of cache ways that do not contain the requested data according to the bloom filter. This scheme requires the addition of a large decoder and two fields per way: one segmented bloom filter, previously proposed by the same authors to filter accesses to the whole cache [64], and another bloom filter to filter accesses to ways. Although Way Guard shows performance gains with respect to the Way-Halting Cache, it suffers from higher overheads in terms of area and adds significant complexity. The main problem of these techniques is that a new structure must be accessed serially after the address translation in the TLB and before accessing the cache, hence either increasing cycle time or adding an extra cycle to the memory access latency in virtually-indexed physically-tagged caches. In order to overcome this problem, Valls et al. [147, 148] propose PS-Cache, a mechanism that filters the ways looked up on each cache access by classifying each block as private or shared, according to the page table information. On a cache access, only the ways containing blocks that match with the classification of the requested block are searched. The same authors also propose the

Tag Filter Cache [149], a cache architecture that uses the least significant bits of the tag part of the address to discern which ways may contain the accessed block.

Including way information in the TLB is another approach to reduce the energy consumed in the caches. The goal is to prevent doing one lookup in the tag array of the cache to determine the way of the cache block and another lookup in the TLB to provide the address translation. Instead, the idea is to do a single lookup in the TLB that provides both the address translation and the way where the block is located in the cache. In order to do so each TLB entry is extended with a field that contains, for each cache block belonging to the page, the way where it is located in the cache. Boettcher et al. [27] propose to use this scheme to predict or determine the way of the accessed block in the L1 cache, but the way information in the TLB is not always deterministic, so it is sometimes treated as a hint and the tag array of the cache has to be kept. The Tag-Less Cache [132] introduces a valid bit along with the way information to make it deterministic, so the tag array of the cache can be eliminated. Although these two approaches achieve substantial energy gains, they require significant area to store the way information for each cache block of the page (specially if big page sizes are supported), they require changes in the cache replacement policy, they affect miss ratios and performance in unpredictable ways, and they need very costly reverse address translation mechanisms to handle cache coherence and virtual address synonyms because they use virtual indexing. An extension of the Tag-Less Cache [130, 131] uses a physically-tagged hub per core to handle virtual address synonyms and external coherence requests and, in addition, they store not only the way but also the cache where the block is kept, so the whole cache hierarchy can be navigated with a single lookup.

#### 2.1.3.2 Coherence Traffic

Some research works propose to eliminate the unnecessary coherence traffic that is generated by memory accesses to private data. The technique consists on distinguishing what data is private and what data is shared, and deactivating the cache coherence protocol for the private data. The deactivation of the coherence protocol implies that cache hits to private data do not send invalidation coherence messages to the other caches, and cache misses to private data do not request the cache block to the other caches but are directly served by the main memory. The proposed techniques differ significantly one from each other, specially in the way the private data is identified, the granularity at which it is identified and the hardware mechanisms that keep track of the privateness.

Cuesta et al. [40, 41] propose to track private virtual memory pages at the OS level, extending the functionality of the page fault handler. When a page is accessed for the first time in an application, the OS sets a private bit in the page table and in the TLB of the core that is accessing it. Memory accesses from the same core to the private page are served without requiring any coherence messages to the caches nor to the cache directory of the cache coherence protocol. When another core accesses the page the OS marks the page as shared and triggers a flush of the cache blocks and the TLB entries of the page in the first core. Subsequent accesses by any core to the shared page trigger the coherence actions defined by the cache coherence protocol. In another paper [39], the authors extend this mechanism to work also for shared read-only pages. Almost identical data categorization methods and hardware mechanisms have been proposed to filter snoop requests [86] and to optimize the data placement in NUCA caches [71, 72]. Although this technique only requires small changes in the TLB and the OS, changing the state of the data from private to shared is very costly because it requires to flush the TLBs and the caches. Moreover, it does not eliminate coherence traffic completely because it suffers from false positives due to the granularity used to track the memory regions and because, even if some data is only shared in a small phase of the program, it never transitions from shared back to private.

Other works propose to track private data at the granularity of memory regions of arbitrary size that are managed at the microarchitecture level, transparently to any software layer. In these works new hardware structures are used to classify a memory region as private when a core first accesses it, and subsequent accesses by other cores to the same memory region make it shared. Cantin et al. [31, 32] add a separate hardware structure called the Region Coherence Array that directly interacts with an ad-hoc coherence protocol. RegionScount [103, 104] also identifies private and shared memory regions of arbitrary size at the microarchitecture level, and additional hardware support is used to filter broadcasts in snoop-based cache coherence protocols. Alisafaee [4] proposes to extend the cache directory of the cache coherence protocol with special entries to track private memory regions and, additionally, timing is taken into account to do the data classification. The reasoning is that, even if the data is shared, coherence is not needed if two cores do not access it at the same time. The first memory access by a core to a region makes it private, and subsequent accesses from the same core keep this categorization. A region is marked as shared when another core accesses it, and it is marked back as private when all the cache blocks of the region are evicted from the caches of all the cores but one. On the one hand, the advantage of these mechanisms compared to the ones that use a fixed page size granularity with OS and TLB support is that they work transparently to the software, and the size of the memory regions can be dynamically adapted to improve the accuracy of the data classification. Moreover, transitioning from shared to private further improves accuracy, although relying on cache block evictions causes that the transition does not happen immediately when the data stops being shared. On the other hand, these techniques introduce significant hardware complexity and more power is consumed in the execution of memory instructions, as they need to access an additional hardware structure.

#### 2.1.4 Future Directions

Although the combination of shared memory programming models and cache-coherent memory hierarchies has dominated the landscape of parallel computing for many years, the aforementioned power consumption and scalability problems are becoming a severe obstacle to scale up the number of cores in future shared memory manycore architectures [7, 136].

The different solutions discussed in the previous sections can reduce the power consumption or the NoC traffic in some cases, but they all have some limitations or introduce new difficulties. In addition, the solutions target very specific parts of the problem, so many of them have to be combined to make cache hierarchies power-efficient and scalable enough to fulfill the requirements of future shared memory manycore architectures. Combining the different techniques requires significant complexity, and even some solutions are incompatible between themselves, so it is unclear that these approaches will end up solving the problems of cache hierarchies in the long term.

A more disruptive way to solve the inherent inefficiencies of cache hierarchies is to move away from the pure shared memory paradigm [1, 7]. The main reasoning behind this approach is that, fundamentally, doing an efficient management of the data of a parallel application is a very challenging problem, and solving it at the microarchitecture level is very costly. Instead, giving the software layers the responsibility of performing certain data management operations opens the door to designing much more efficient memory hierarchies.

# 2.2 Multiprocessors with Scratchpad Memories

Many commercial processors and research projects have adopted memory organizations different than cache-coherent shared memory hierarchies. These different memory organizations are frequent in the embedded domain, where processors have strong power consumption constraints, and in the HPC domain, where power efficiency and scalability are of paramount importance.

The key element of the efficient memory hierarchies used in the embedded and the HPC domain are the ScratchPad Memories (SPMs). SPMs are a simple arrays of memory exposed to the software layers in a part of the virtual and physical address spaces. Compared to caches, SPMs provide three main advantages. First, SPMs do not need a tag array, a hit/miss logic, nor a replacement policy logic, so they are more power-efficient and they occupy less area than caches. Second, memory accesses to the SPMs never miss, so performance penalties due to cache misses do not happen and the access time to the SPMs is deterministic. Third, SPMs are not coherent with the rest of memories in the system, so memory accesses to them do not generate coherence traffic. Although these advantages are very appealing to overcome the power consumption and scalability problems of muliprocessors, the main problem of SPMs is that they have to be managed by software, which degrades programmability because they require the programmer, the compiler or the runtime system to perform memory management operations.

Despite their programmability difficulties, SPMs have been successfully adopted by many architectures in numerous ways, either as the only on-chip memory or alongside a cache hierarchy. The next subsections explain how SPMs have been integrated in relevant architectures, with the architectural details of the different memory organizations and their implications on the programmability of the architecture.

#### 2.2.1 Embedded Processors

SPMs have been widely used in embedded systems for many years. SPMs provide key advantages over caches in this domain, as they are more energy- and cost-efficient and they provide predictable access time, which is critical in hard real-time systems. For these reasons SPMs have been included in embedded processors in different ways. In processors such as the Motorola Dragonball, the Infineon XC166 or the TI TMS370CX7X SPMs are used as the only on-chip memory, while in other embedded processors like the ARM10E or the ColdFire MCF5 SPMs are introduced alongside caches.

Although in the embedded domain it is common that the programmer explicitly selects data or code to be placed in the SPMs, some works propose techniques to do it automatically in order to improve code portability. Existing approaches for automatic SPM management can be divided in two classes: static and dynamic. In static schemes designated parts of the program are allocated in the SPMs at load time, and their contents do not change during the execution of the program. In dynamic approaches parts of the program are mapped to the SPMs during the execution, dynamically changing their contents. Both categories can be further classified into techniques that consider only code, only data, or both.

Static allocation methods decide at compile time what program objects are allocated in the SPMs. The main advantage of static allocations is that they do not add any overhead at execution time. However, the amount of data or code that can be allocated in the SPMs is constrained by the size of the SPMs so, depending on the characteristics of the workload, the amount of memory accesses served by the SPMs is limited. Panda et al. [117, 118] allocate scalar constants and variables in the SPM and use heuristics to allocate those arrays that minimize cache conflicts. Angiolini et al. [5, 6] propose an algorithm based on dynamic programming to select code blocks which promise the highest energy savings. Banakar et al. [14] solve the static assignment with a knapsack algorithm for both code and data blocks. Verma et al. [151] select memory objects based on a cache conflict graph obtained through cache hit/miss statistics, selecting the optimal set of memory objects with an integer linear program variant of the knapsack algorithm. Nguyen et al. [108] propose to delay the decision of which blocks should be allocated in the SPM until the application is loaded, making it independent from the size of the SPM at the cost of embedding profiling information into the application binary.

Another approach is to dynamically map code or data to the SPMs. This method allows to map to the SPMs as much data or code as desired, but adds overheads to transfer data or code between the SPMs and the main memory during the execution of the program. Kandemir et al. [82, 81] propose to map arrays accessed in well-structured loops. Arrays are split into tiles to allow that parts of the arrays are mapped to the SPM, so arrays bigger than the SPM size can be mapped to the SPM in chunks. Li et al. [95] also focus on assigning data arrays to the SPM. To determine the most beneficial set, they first divide the SPM in partitions of different sizes and, using a conflict graph of live ranges for the arrays, a graph-coloring algorithm determines which array is mapped to which partition of the SPM at what program points. Udayakumaran and Barua [145] map data to the SPM

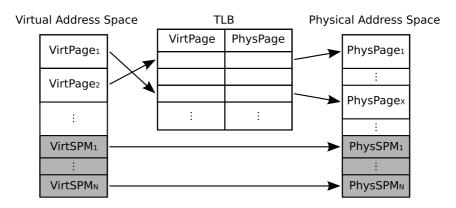

by constructing the control-flow graph of the program, that is annotated with timestamps to form a data program relationship graph. Using greedy heuristics, the pieces of data that maximize performance are mapped to the SPM at defined copy points in the program. Steinke et al. [137] propose to dynamically map blocks of code to the SPM before entering a loop, determining the optimal set using an integer linear program. The same technique is proposed by Egger et al. [53] but using a post-pass optimizer that operates on the binary of the program instead of the source code. Another dynamic SPM management scheme for code is proposed by Janapsatya et al. [78], where the blocks of code to be mapped to the SPM are selected based on a metric called concomitance, which indicates how correlated in time the execution of various blocks of code are. Egger et al. [54] propose to map code to the SPM using the MMU, in such a way that code is transparently mapped on demand to the SPM when a page fault happens. Cho et al. [37] apply the same MMU technique to map data to the SPM on demand.

#### 2.2.2 Cell B.E.

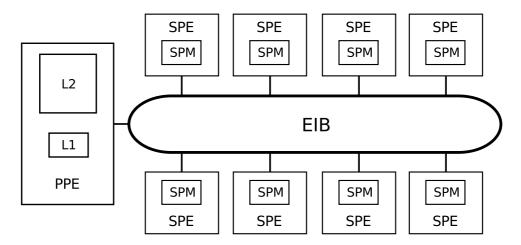

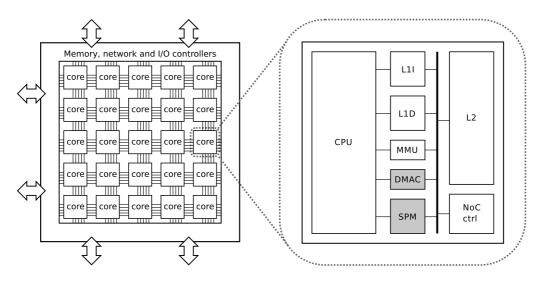

The Cell B.E. [79] is one of the first and more breakthrough heterogeneous multicore processors for HPC and multimedia workloads. The architecture consists of a general-purpose core called Power Processor Element (PPE) and eight accelerator cores called Synergistic Processor Elements (SPEs) connected through a high bandwidth NoC named Element Interconnect Bus (EIB). A scheme of the architecture is shown in Figure 2.3.

Figure 2.3: Cell B.E. architecture

The memory hierarchy of the Cell B.E. combines a hierarchy of caches and SPMs. The PPE has a private 32 KB L1 cache and a private 512 KB L2 cache, while each SPE has a private SPM of 256 KB. The SPMs of the SPEs have their own private virtual and physical address spaces and are incoherent with the rest of memories in the architecture. Each SPE can issue load and store instructions only to its private SPM and a DMA controller is used to transfer data from or to the rest of memories in the architecture. The DMA transfers are coherent with the cache hierarchy of the PPE.

Although the Cell B.E. was able to achieve significantly higher performance than the rest of processors of its time, obtaining the expected performance was complex due to the programmability difficulties the Cell B.E. suffered from. First, the programmer is in charge on distributing the computation between the PPE and the SPEs, writing the code for each element in a separate source code file. The PPE is in charge of running the OS and to start processes, which can initiate one or more SPE threads using an API to create the SPE context (spe\_context\_create), load the code and the data for the SPE context (spe\_program\_load), launch the execution of the SPE thread (spe\_context\_run), and finish the SPE thread when the execution finishes (spe\_context\_destroy). Second, the programmer has to partition the data between the tasks. The limited size of the SPMs of the SPEs makes unfeasible to statically partition the data and embed it in the SPE context so, most of the times, SPE threads use DMA transfers to dynamically transfer the data from the main memory to the SPM, perform the computation, and write the data back to the main memory if needed. An API is offered to trigger asynchronous DMA transfers (mfc\_get from the main memory to the SPM and mfc\_put from the SPM to the main memory) and to synchronize them (mfc\_write\_tag\_mask and mfc\_read\_tag\_status\_all). Third, the programmer needs to perform explicit thread synchronization, and typical synchronization primitives are not supported in this architecture, so explicit messages have to be exchanged between threads. The Cell B.E. offers mailboxes to perform inter-thread communication (spe\_in\_mbox\_write and spe\_in\_mbox\_read), which are 32-bit messages intended to exchange program status, completion flags or memory addresses.

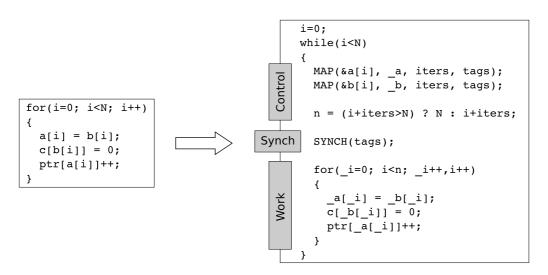

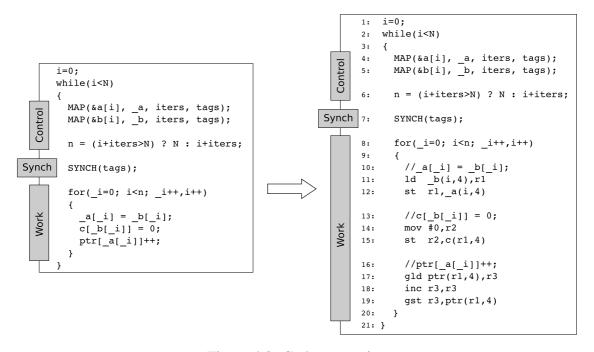

Several approaches have been proposed to support shared memory programming models on the Cell B.E., aiming to overcome its programmability issues. The IBM XL compiler for the Cell B.E. supports OpenMP constructs [112] in two ways. In both approaches the idea is to use a software cache on each SPE to automatically transfer data between its SPM and the main memory. The first technique [55, 56] introduces a software cache

that surrounds every memory reference with a piece of code that mimics the operation of a cache: lookup of the address, placement, replacement of an old entry, data transfer and synchronization. Although some optimizations such as using asynchronous data transfers [12] can improve the initial design, the amount of code executed prior to every memory access imposes severe performance overheads. The second technique [36, 67] drastically reduces the overheads for strided memory references by applying loop tiling, in such a way that strided memory references are handled in the outermost loop by a software cache that tracks data at the granularity of big blocks, while random memory references are handled by a second software cache at every access in the innermost loop.

COMIC [92] is a low level shared memory interface for the Cell B.E. that can be used directly by the programmer or as a target of compilers for shared memory programming languages. COMIC uses a centralized coherence protocol on the PPE and wraps all memory references of the SPE code with a software cache that requests memory pages if needed, and proposes optimizations to reduce communication for read-only and single writer pages. Although these optimizations enable important performance improvements over the techniques introduced in the IBM XL compiler, applying them at compile time requires the compiler to ensure that there are no memory aliasing hazards between the memory references of the code. This can be done in simple codes but, in the presence of pointers and functions, it becomes a very challenging problem for the compiler.

As an alternative, other works propose to program the Cell B.E. using task data-flow programming models. An initial version of OmpSs for the Cell B.E., called CellSs [17, 120], allows programmers to annotate functions as tasks and to specify their dependences, and a source to source compiler uses this information to generate code for the PPE and for the SPEs. Similarly, Sequoia allows to model the memory hierarchy of the Cell B.E. and to decompose the program in a hierarchy of tasks that are executed on the SPEs. In both approaches a runtime system manages the execution of the tasks in a data-flow fashion and orchestrates the DMA transfers for the task dependences, transferring the input dependences of a task to the SPM of the SPE that is going to execute it and writing back the output dependences to main memory when the task finishes. The runtime system of the CellSs also uses a locality aware scheduling policy to reduce data motion and applies renaming on the output dependences to remove Write after Read (WaR) and Write after Write (WaW) dependences between tasks. Further optimizations for the CellSs include SPE-to-SPE DMA transfers [18], lazy write back of output dependences [19] or distributed scheduling among SPEs [20].

#### 2.2.3 GPGPUs

General-Purpose Graphics Processing Units (GPGPUs) are accelerators designed to execute massively parallel workloads very efficiently. These architectures have received a lot of attention in the HPC domain during the last years, specially the ones manufactured by NVIDIA.

In HPC systems GPGPUs are attached to a general-purpose processor (called the host processor), and they have different address spaces. The host processor is in charge of running the OS, starting applications and executing the sequential parts of the applications. The GPGPU executes parts of the applications that expose a high degree of parallelism, which are encapsulated in kernels. When the application encounters a kernel, the host processor transfers the code of the kernel and the data accessed by the kernel to the GPGPU, triggers its execution, and transfers the data back to the main memory if needed.

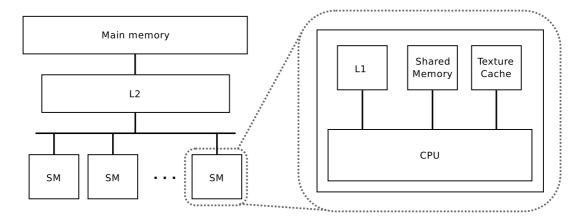

A scheme of the architecture of a NVIDIA GPGPU is shown in Figure 2.4. The architecture consists of many cores (called Streaming Multiprocessors or SMs in NVIDIA's nomenclature) that execute groups of threads in lock-step. The cores have the ability to perform very fast context switches between groups of threads so that the memory latency is not a limiting factor for performance. The memory hierarchy of the GPGPU consists of a main memory and a L2 cache shared between all the SMs. Each SM has a SPM, called shared memory, and two first level caches: the L1 cache and a read-only texture cache. The L1 cache, the texture cache and the SPM of every SM are incoherent with the rest of memories in the system. In order to manage this complex memory hierarchy the main memory is divided in five memory spaces, that operate as follows:

Figure 2.4: GPGPU architecture

#### 2.2. MULTIPROCESSORS WITH SCRATCHPAD MEMORIES

- The global memory is a memory space where the programmer can explicitly transfer data. When a SM issues a memory request to the global memory the data is cached in the shared L2 cache and either in the L1 or in the texture cache of the SM. If the request is read-only it is cached in the texture cache, otherwise it is cached in the L1 cache.

- The constant memory is a read-only memory space where the programmer can explicitly allocate data. When a SM issues a memory request to the constant memory the data is cached in the shared L2 cache and in the texture cache of the SM.

- The texture memory is a read-only memory space where the programmer can explicitly allocate data. When a SM issues a memory request to the texture memory the data is cached in the shared L2 cache and in the texture cache of the SM.

- The shared memory is a memory space where the programmer can explicitly allocate variables that are shared between the threads. The compiler allocates the necessary space in the SPM of the SM for the variable, and memory requests from a SM to the shared memory only access its SPM.

- The local memory is a memory space where the compiler can reserve space for register spilling. When a SM issues a memory request to the local memory the data is cached in the shared L2 cache and in the L1 cache of the SM.

The most common way to program heterogeneous systems with GPGPUs in HPC is using CUDA [110]. In this programming language the programmer has to distribute the computation between the host processor and the GPGPU, synchronize the execution between the two processing elements, and explicitly manage the memory hierarchy of the accelerator. CUDA provides language extensions to C, C++ and Fortran to perform these actions. In order to specify kernels for the GPGPU CUDA provides the \_\_global\_\_ function specifier, and kernels are launched with a special syntax <<< ... >>> to specify the number of threads that execute the kernel. In addition, the code of the kernels is not written in traditional imperative form. Instead, the code of the kernel only specifies the computation that has to be performed by one thread, and this code is replicated among all the threads in a transparent way, so the parallelism is implicit. For synchronization, CUDA offers the function \_\_syncthreads to synchronize the threads within a kernel, and methods such as cudaDeviceSynchronize to synchronize the execution of the kernels with the host code. CUDA also offers functions and variable specifiers

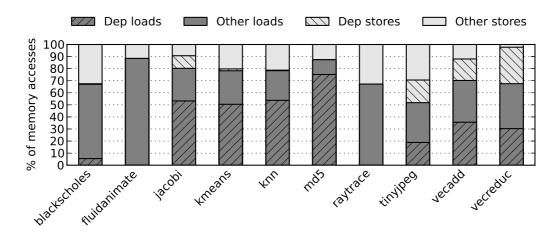

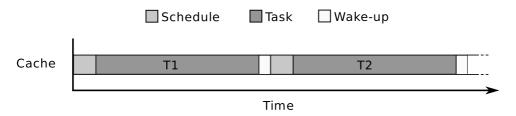

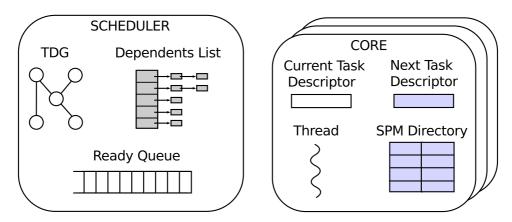

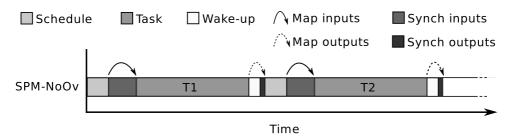

memory the programmer has to allocate space using <code>cudaMalloc</code>, transfer the data using <code>cudaMemcpy</code> and free the space using <code>cudaFree</code>. CUDA also offers the variable specifiers <code>\_\_constant</code> and <code>\_\_shared</code> to statically allocate data to the constant memory and to the shared memory, respectively. To allocate data in the texture memory the programmer has to define a texture handler that specifies the memory layout of the data, while the local memory is transparently managed by the compiler. In addition, in order to decide if the memory accesses to the global memory are cached in the L1 cache or in the texture cache, the compiler applies alias analyses between the memory references of the code to guess if the data being accessed is read-only, and generates a different type of instruction (LDG) for memory accesses to read-only data. In non-trivial cases the compiler does not succeed in ensuring the data is read-only so the programmer has to use the <code>\_\_ldg</code> intrinsic in the memory references to the global memory to enable the usage of the texture cache for these memory accesses.