# PROGRAMMING MODELS AND SCHEDULING TECHNIQUES FOR HETEROGENEOUS ARCHITECTURES

Judit Planas Carbonell

PhD Thesis

Departament d'Arquitectura de Computadors - DAC Universitat Politècnica de Catalunya - UPC

> Advisors: Eduard Ayguadé Rosa M. Badia

> > July 2015

# Abstract

There is a clear trend nowadays to use heterogeneous high-performance computers, as they offer considerably greater computing power than regular homogeneous CPU systems. Extending regular CPU systems with specialized processing units (accelerators such as GPGPUs or Intel Xeon Phi) has become a tremendous revolution in the High Performance Computing world. Not only the traditional *performance per Watt* ratio has been increased with the use of such systems, but also the *performance per Euro/Dollar* has significantly been raised.

Heterogeneous machines can adapt better to different application requirements, as each architecture type offers different characteristics. Thus, in order to maximize application performance in these platforms, applications should be divided into several portions according to their execution requirements. These portions should then be scheduled to the processing unit that best fits their requirements.

Hence, heterogeneity introduces complexity in application development, up to the point of forming a programming wall: on the one hand, source codes must be adapted to fit new architectures, and sometimes they must even be rewritten from scratch. On the other hand, resource management becomes more complicated. For example, multiple memory spaces may exist and require explicit memory movements and, moreover, additional synchronization mechanisms must be added between different code portions that run on different processing units. For all these reasons, efficient programming and code maintenance in heterogeneous systems has been extremely complex and expensive.

Although several approaches have been proposed for accelerator programming, like CUDA and OpenCL, these models do not solve the aforementioned programming challenges, as they expose low level hardware characteristics to the programmer. Ideally, programming models should be able to hide all these complex accelerator programming by providing a homogeneous development environment.

In this heterogeneous context, this thesis makes two major contributions: first, it proposes a general design to efficiently manage the execution of heterogeneous applications and second, it presents several scheduling mechanisms to spread application execution among all the processing units of the system and maximize performance and resource utilization.

Regarding the first contribution, this work proposes an asynchronous design to manage execution, data movements and synchronizations on accelerators. This approach has been developed in two steps: first, a semi-asynchronous proposal and then, a fully-asynchronous proposal in order to fit contemporary hardware restrictions. The experimental results from different multi-accelerator platforms showed that these approaches could reach the maximum expected performance. Even if compared to native, hand-tuned codes, they could get the same results and outperform native versions in selected cases.

Regarding the second contribution, four different scheduling strategies are presented. They combine different aspects of heterogeneous programming to minimize the execution time of applications. For example, minimizing the amount of data shared between processing units and their local memory spaces, or maximizing resource utilization by scheduling each portion of code on the processing unit that fits better. The experimental results were performed on different heterogeneous platforms, including general purpose CPUs, GPGPU and Intel Xeon Phi accelerators. As shown in these tests, it is particularly interesting to analyze how all these scheduling strategies can impact application performance.

Three general conclusions can be extracted from the research work derived from this thesis. First, application performance is not guaranteed across new hardware generations. Therefore, source codes must be periodically updated as hardware characteristics evolve. Second, the most efficient way to run an application on a heterogeneous platform is to divide it into smaller portions and pick the processing unit that fits better to run each portion. Hence, system resources can cooperate together to execute the application. Finally, and probably the most important, the requirements derived from the first and second conclusions can be implemented inside runtime frameworks, so the complexity of programming heterogeneous architectures is completely hidden from the programmer point of view.

# Acknowledgements

This work has been supported by the following institutions: the European Commission through the ENCORE project (FP7-248647), the TERAFLUX project (FP7-249013), the TEXT project (FP7-261580), the HiPEAC-2 Network of Excellence (FP7/ICT 217068) and the HiPEAC-3 Network of Excellence (FP7-ICT 287759), the support of the Spanish Ministry of Education (CSD2007-00050 and FPU program), the projects of Computación de Altas Prestaciones V and VI (TIN2007-60625, TIN2012-34557), the Generalitat de Catalunya (2009-SGR-980, 2014-SGR-1051), the Intel-BSC Exascale Lab and IBM/BSC Exascale Initiative collaboration and the Severo Ochoa recognition SEV-2011-0067.

I would also like to thank the Universitat Jaume I from Castelló and KAUST IT Research Computing for granting access to their machines.

# Contents

| Al | ostrac  | t             |                                                                                      | ii  |

|----|---------|---------------|--------------------------------------------------------------------------------------|-----|

| Ac | cknow   | ledgem        | ents                                                                                 | iii |

| Co | ontent  | ts            |                                                                                      | v   |

| Li | st of ] | Figures       |                                                                                      | ix  |

| Li | st of ' | <b>Fables</b> |                                                                                      | xi  |

| 1  | Intr    | oductio       | n                                                                                    | 1   |

|    | 1.1     |               | xt and Motivation                                                                    | 1   |

|    | 1.2     | Progra        | amming Challenges in Heterogeneous Systems: One code does not fit all                | 3   |

|    | 1.3     | Contri        | butions                                                                              | 6   |

|    |         | 1.3.1         | Accelerator Support and Management                                                   | 8   |

|    |         |               | 1.3.1.1 Semi-asynchronous Approach                                                   | 9   |

|    |         |               | 1.3.1.2 Fully asynchronous Approach                                                  | 10  |

|    |         |               | 1.3.1.3 Accelerator Compiler Support                                                 | 10  |

|    |         | 1.3.2         | Scheduling Techniques for Heterogeneous Architectures                                | 10  |

|    |         |               | 1.3.2.1 Task Priority Propagation                                                    | 10  |

|    |         |               | 1.3.2.2 Affinity-ready Scheduler                                                     | 11  |

|    |         |               | 1.3.2.3 Versioning Scheduler                                                         | 11  |

|    |         |               | 1.3.2.4 SSMART Scheduler                                                             | 11  |

|    | 1.4     | Thesis        | Organization                                                                         | 12  |

| 2  | Dev     | -             | nt Environment                                                                       | 13  |

|    | 2.1     | OmpS          | s programming model                                                                  | 13  |

|    |         | 2.1.1         | Execution Model                                                                      | 13  |

|    |         | 2.1.2         | Memory Model                                                                         | 14  |

|    |         | 2.1.3         | OmpSs Syntax Extensions                                                              | 14  |

|    |         | 2.1.4         | Nanos++ Library                                                                      | 15  |

|    |         |               | 2.1.4.1 Nanos++ Independent Layer $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 16  |

|    |         |               | 2.1.4.2 Nanos++ Dependency Support                                                   | 17  |

|    |         |               | 2.1.4.3 Nanos++ Task Scheduler                                                       | 17  |

|    |         |               | 2.1.4.4 Nanos++ Coherence Support                                                    | 18  |

# CONTENTS

|   |      | 2.1.5    | Mercurium Compiler                                 |

|---|------|----------|----------------------------------------------------|

|   |      | 2.1.6    | OmpSs Application Example    20                    |

|   | 2.2  | Applic   | ations                                             |

|   |      | 2.2.1    | Black-Scholes                                      |

|   |      | 2.2.2    | Cholesky Factorization                             |

|   |      | 2.2.3    | FFT1D 24                                           |

|   |      | 2.2.4    | Krist                                              |

|   |      | 2.2.5    | N-Body Simulation                                  |

|   |      | 2.2.6    | PBPI 25                                            |

|   |      | 2.2.7    | Perlin Noise                                       |

|   |      | 2.2.8    | STREAM Benchmark                                   |

|   |      | 2.2.9    | Tiled Matrix Multiply    28                        |

| 3 | Stat | e of the | Art                                                |

| J | 3.1  |          | based Programming Models and Languages             |

|   |      | 3.1.1    | OpenMP                                             |

|   |      | 3.1.2    | Cilk Plus                                          |

|   |      | 3.1.3    | Chapel                                             |

|   |      | 3.1.4    | Sequoia                                            |

|   | 3.2  |          | rator Programming                                  |

|   |      | 3.2.1    | CUDA                                               |

|   |      | 3.2.2    | OpenCL                                             |

|   |      | 3.2.3    | HSA                                                |

|   |      | 3.2.4    | OpenACC                                            |

|   |      | 3.2.5    | Intel Offload                                      |

|   |      | 3.2.6    | StarPU                                             |

|   |      | 3.2.7    | Offload                                            |

|   | 3.3  | Hetero   | geneous Schedulers                                 |

|   |      | 3.3.1    | MDR                                                |

|   |      | 3.3.2    | Qilin                                              |

|   | 3.4  | Tools f  | for Heterogeneous Platforms 34                     |

|   |      | 3.4.1    | hiCUDA                                             |

|   |      | 3.4.2    | CAPS HMPP                                          |

|   |      | 3.4.3    | ispc 35                                            |

|   |      | 3.4.4    | OpenMPC 35                                         |

|   |      | 3.4.5    | CUDA-lite                                          |

|   |      | 3.4.6    | UPC for GPU Clusters                               |

| 4 | Acce | lerator  | Support for OmpSs 37                               |

| - | 4.1  |          | synchronous Accelerator Support                    |

|   | 1.1  | 4.1.1    | Accelerator Agnostic Design                        |

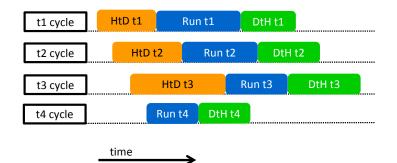

|   |      |          | 4.1.1.1 Overlap of Data Transfers and Computations |

|   |      |          | 4.1.1.2 Data Prefetch                              |

|   |      |          | 4.1.1.3 Task Execution Flow                        |

|   |      | 4.1.2    | OmpSs GPU Support                                  |

|   |      |          | 4.1.2.1 GPU Accelerator Initialization             |

|   |      |          | 4.1.2.2 GPU Memory Management                      |

|   |      |          |                                                    |

|                  | 4.1.2.3 Overlap of Data Transfers and GPU Computations                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------|

|                  | 4.1.2.4 Data Prefetch and Task Execution Flow                                                               |

|                  | 4.1.2.5 GPU Computation Offload                                                                             |

|                  | 4.1.3 CUDA Device Profile for Mercurium Compiler                                                            |

|                  | 4.1.4 OmpSs Example Using GPUs                                                                              |

|                  | $4.1.5$ Evaluation $\ldots$ $4.1.5$                                                                         |

|                  | 4.1.5.1 Methodology                                                                                         |

|                  | 4.1.5.2 Results                                                                                             |

| 4.2              |                                                                                                             |

| 1.2              | 4.2.1 AMA Design                                                                                            |

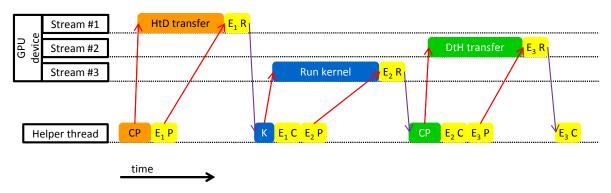

|                  | 4.2.1.1 Event-driven Flow                                                                                   |

|                  | 4.2.1.2 FTFR                                                                                                |

|                  | 4.2.2 OmpSs GPU Support with AMA                                                                            |

|                  | 4.2.2 Ompose of e support with mint                                                                         |

|                  | 4.2.3 OmpSs Xeon Phi Support with AMA                                                                       |

|                  | 4.2.3 Xeon Phi Accelerator Initialization                                                                   |

|                  | 4.2.3.2 Xeon Phi Memory Management                                                                          |

|                  | 4.2.3.3 Event-driven Flow                                                                                   |

|                  |                                                                                                             |

|                  | 4.2.4       OmpSs Example Using Intel Xeon Phi       6         4.2.5       Evaluation of AMA Design       6 |

|                  |                                                                                                             |

|                  | 4.2.5.1 AMA Evaluation on GPGPU Accelerators                                                                |

|                  | 4.2.5.2 AMA Evaluation on Intel Xeon Phi Accelerators 6                                                     |

| Ru               | ntime Scheduling Policies for Heterogeneous Environments                                                    |

| 5.1              | Task Priority Propagation    6                                                                              |

| 5.2              | Affinity-ready Scheduler                                                                                    |

| 5.3              | Versioning Scheduler                                                                                        |

|                  | 5.3.1 Syntax and Compiler Support                                                                           |

|                  | 5.3.2 Data Collection                                                                                       |

|                  | 5.3.3 Runtime Scheduling Policy                                                                             |

|                  | 5.3.4 Example                                                                                               |

|                  | 5.3.5 Evaluation                                                                                            |

|                  | 5.3.5.1 Methodology                                                                                         |

|                  | $5.3.5.2$ Results $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                     |

| 5.4              | SSMART Scheduler                                                                                            |

|                  | 5.4.1 Data Collection                                                                                       |

|                  | 5.4.2 Runtime Scheduling Policy                                                                             |

|                  | 5.4.3 Evaluation                                                                                            |

|                  | 5.4.3.1 Methodology                                                                                         |

|                  | $5.4.3.2$ Results $\ldots$                                                                                  |

| C                |                                                                                                             |

| <b>Co</b><br>6.1 | nclusions and Future Work       9         Programmability and Accelerator Support       9                   |

| 0.1              | 6.1.1 Future Work                                                                                           |

| 6 9              |                                                                                                             |

| 6.2              | 0                                                                                                           |

|                  | 6.2.1 Future Work                                                                                           |

| Bi | Bibliography                                                                             |     |

|----|------------------------------------------------------------------------------------------|-----|

| Α  | Nanos++ Runtime OptionsA.1Nanos++ GPU Runtime OptionsA.2Nanos++ Xeon Phi Runtime Options |     |

| В  | Application Source Code Comparison                                                       | 111 |

# List of Figures

| 1.1  | A simple CUDA implementation of scale function                                 | 3  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | A simple C implementation of matrix multiply                                   | 4  |

| 1.3  | A simple CUDA implementation of matrix multiply calling CUBLAS library         | 5  |

| 1.4  | A simple hStreams implementation of matrix multiply for Intel Xeon Phi         | 5  |

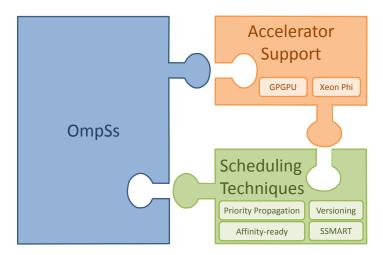

| 1.5  | Illustration of thesis contributions                                           | 7  |

| 1.6  | Simple OmpSs matrix multiply code using the GPGPU to offload the computation   | 9  |

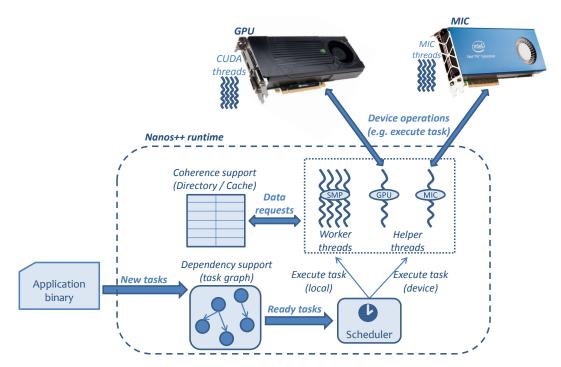

| 2.1  | Nanos++ runtime components and execution flow                                  | 18 |

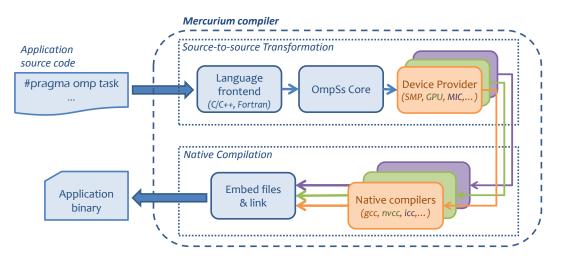

| 2.2  | Mercurium file compilation flow                                                | 20 |

| 2.3  | OmpSs tiled matrix multiply calling CBLAS                                      | 20 |

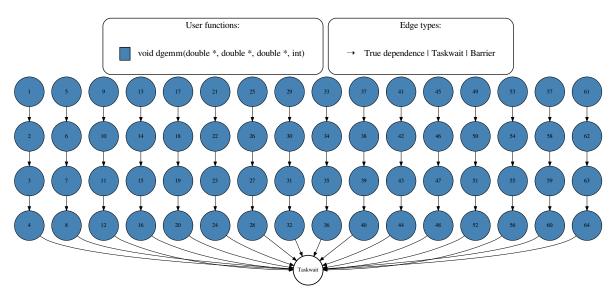

| 2.4  | Data-dependency graph for a tiled matrix multiply algorithm                    | 21 |

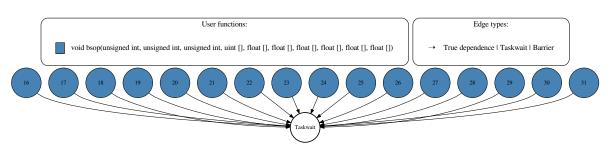

| 2.5  | Data-dependency graph for a Black-Scholes algorithm                            | 22 |

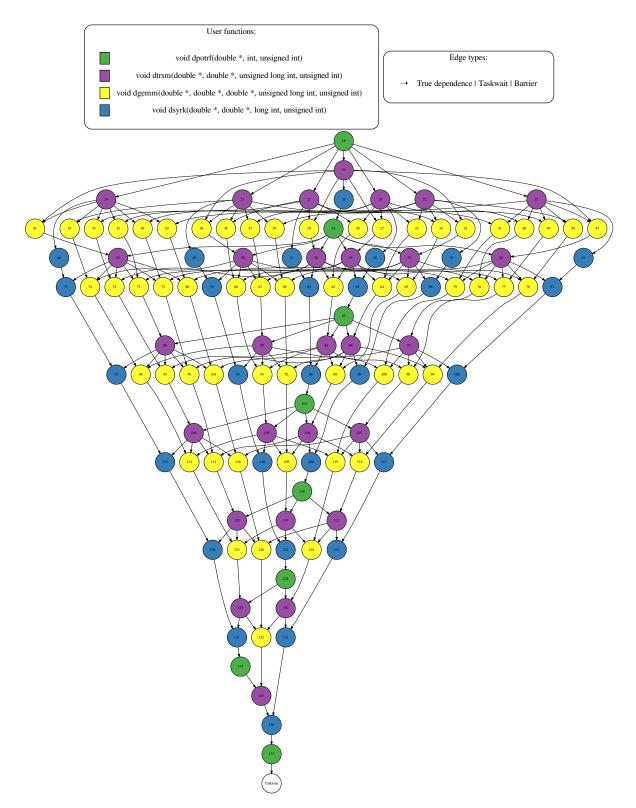

| 2.6  | Data-dependency graph for the Cholesky factorization                           | 23 |

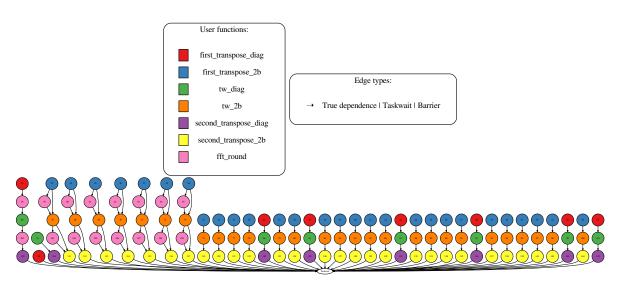

| 2.7  | Data-dependency graph for the FFT1D transformation                             | 24 |

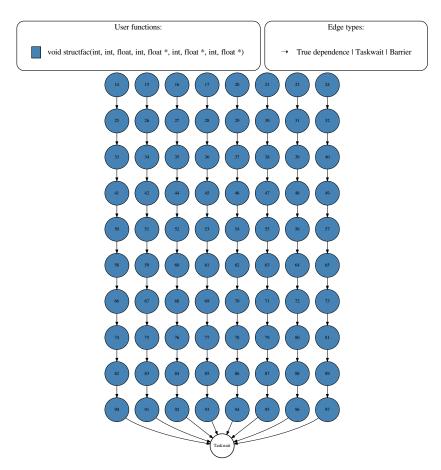

| 2.8  | Data-dependency graph for Krist application                                    | 25 |

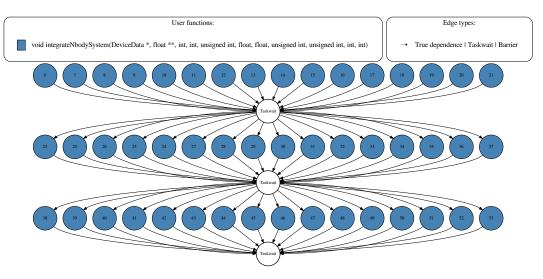

| 2.9  | Data-dependency graph for N-Body simulation                                    | 26 |

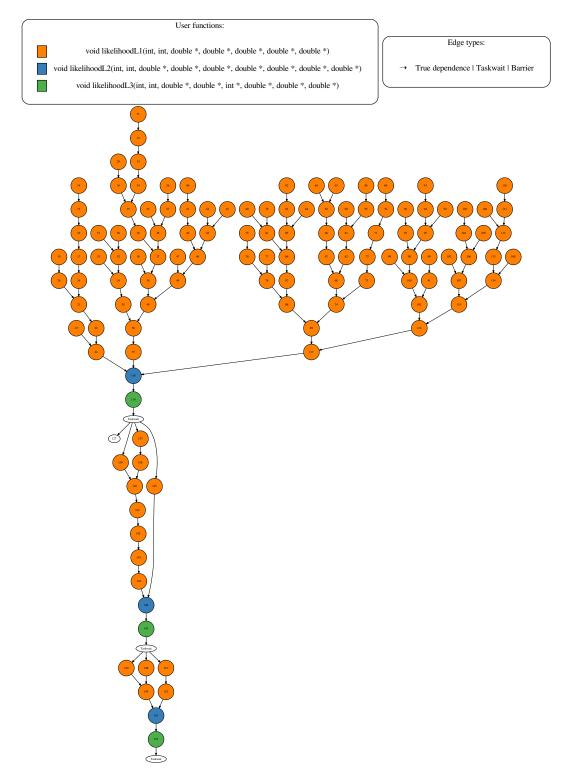

| 2.10 |                                                                                | 27 |

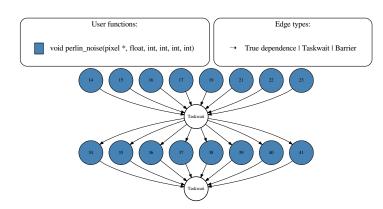

|      | Data-dependency graph for Perlin Noise application                             | 28 |

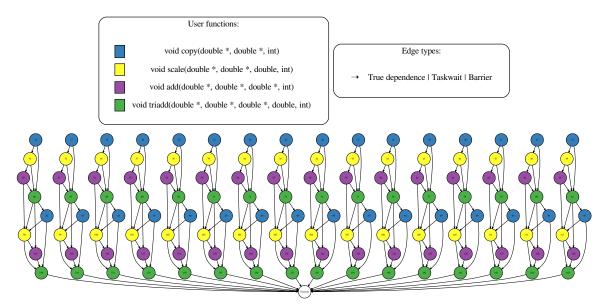

| 2.12 | Data-dependency graph for STREAM benchmark                                     | 28 |

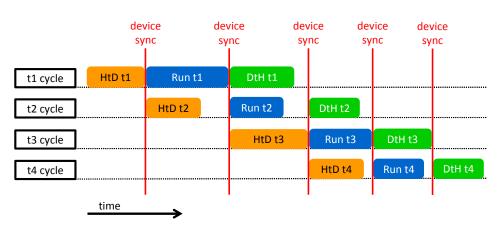

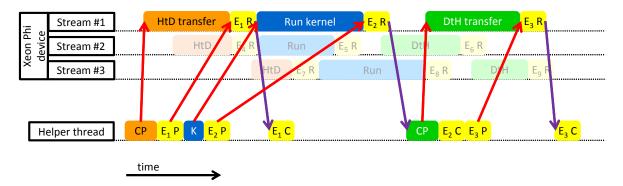

| 4.1  | Semi-asynchronous task execution flow                                          | 40 |

| 4.2  | Nanos++ API functions for allocating and deallocating page-locked memory $\$ . | 42 |

| 4.3  | Nanos++ API additional functions to manage GPU computation offload             | 43 |

| 4.4  | Task source code example calling a CUBLAS library function                     | 44 |

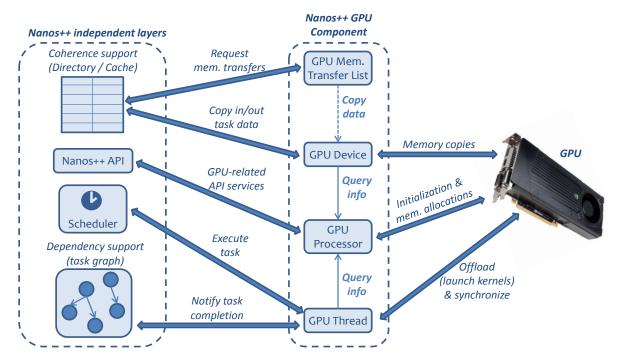

| 4.5  | Interaction between Nanos++ independent layers and GPU dependent component     | 44 |

| 4.6  | Comparison between original and modified kernel calls by Mercurium             | 45 |

| 4.7  | OmpSs tiled matrix multiply example using the GPU to offload the computation   | 47 |

| 4.8  | Matrix multiply performance results for OmpSs with GPU support                 | 48 |

| 4.9  | STREAM performance results for OmpSs with GPU support                          | 49 |

|      | N-Body simulation performance results for OmpSs with GPU support               | 50 |

|      | Perlin Noise performance results for OmpSs with GPU support                    | 50 |

|      | Black-Scholes execution time with OmpSs with GPU support                       | 51 |

|      | Krist execution time with OmpSs with GPU support                               | 51 |

| 4.14 | Event-driven flow of AMA                                                       | 54 |

| 4.15 | Task execution flow with AMA                                                   | 55 |

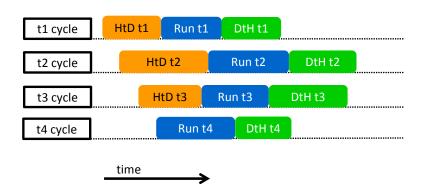

|      | Distribution of asynchronous operations and events on GPGPU device streams .<br>Task execution comparison between semi-asynchronous and AMA approaches on | 56 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.11 | a GPGPU device                                                                                                                                            | 57 |

| 4 18 | Nanos++ API functions for allocating and deallocating Xeon Phi memory                                                                                     | 58 |

|      | Distribution of asynchronous operations and events on Xeon Phi device streams.                                                                            | 59 |

|      | Task execution flow on a Xeon Phi device                                                                                                                  | 60 |

|      |                                                                                                                                                           | 61 |

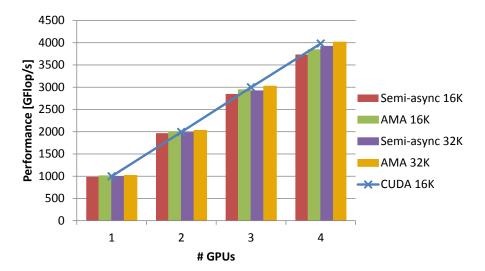

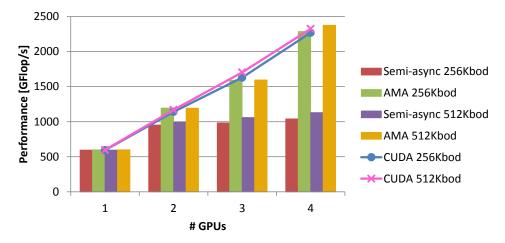

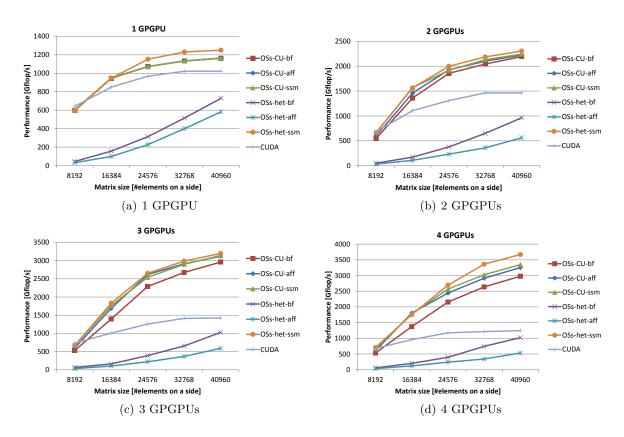

|      | Matrix multiply performance results for OmpSs with GPGPU AMA support                                                                                      | 62 |

|      | Cholesky factorization performance results for OmpSs with GPGPU AMA support                                                                               | 64 |

|      | N-Body simulation performance results for OmpSs with GPGPU AMA support.                                                                                   | 65 |

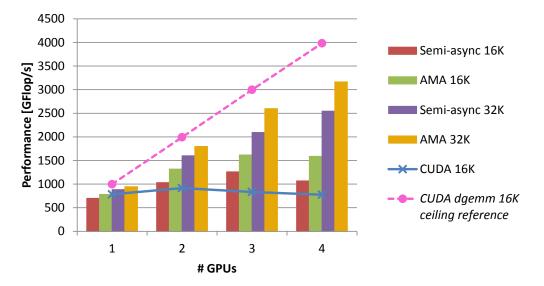

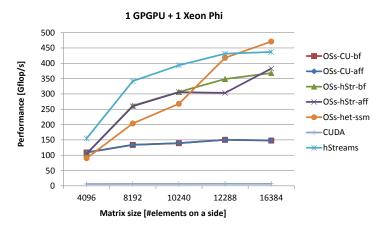

|      | Matrix multiply performance results for OmpSs with Xeon Phi support                                                                                       | 66 |

|      | Cholesky factorization performance results for OmpSs with Xeon Phi support                                                                                | 68 |

|      |                                                                                                                                                           |    |

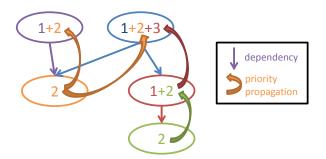

| 5.1  | Task priority propagation in the OmpSs runtime                                                                                                            | 70 |

| 5.2  | Affinity-ready task scheduling in the OmpSs runtime                                                                                                       | 72 |

| 5.3  | Example of different task versions                                                                                                                        | 74 |

| 5.4  | Example of a scheduling decision by versioning                                                                                                            | 76 |

| 5.5  | Versioning scheduler flow                                                                                                                                 | 77 |

| 5.6  | OmpSs Matrix Multiply task calling CUBLAS                                                                                                                 | 78 |

| 5.7  | OmpSs Matrix Multiply task calling a hand-coded CUDA kernel                                                                                               | 78 |

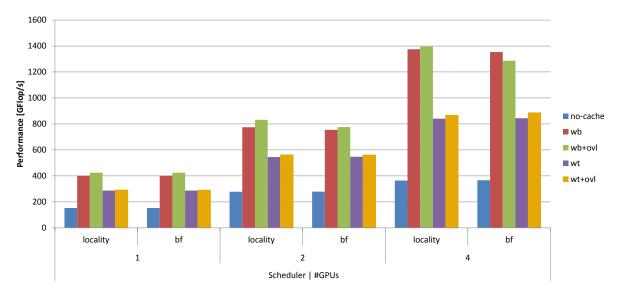

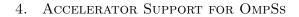

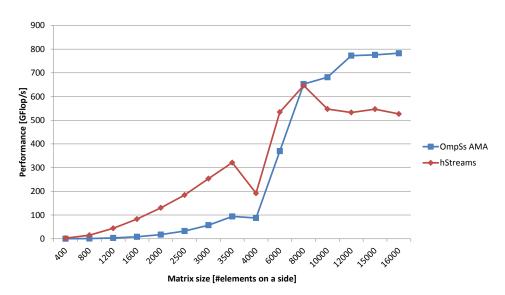

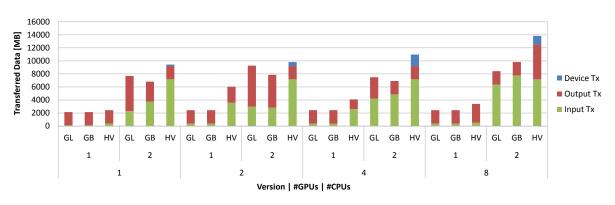

| 5.8  | Matrix multiply performance results with versioning scheduler                                                                                             | 81 |

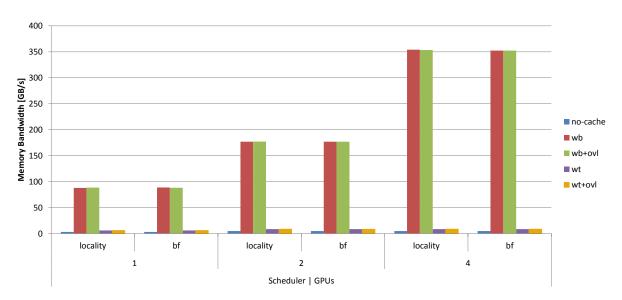

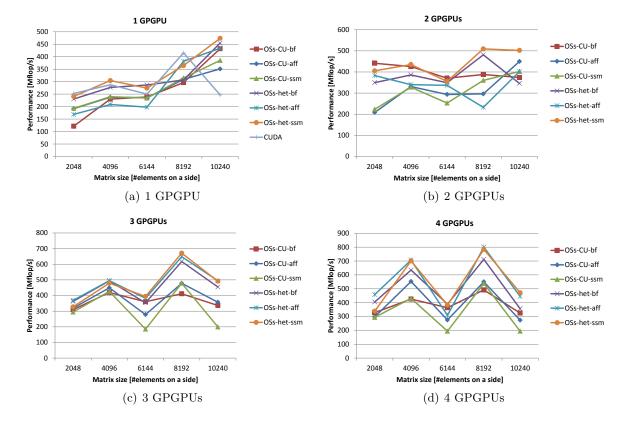

| 5.9  | Transferred data for matrix multiply with versioning scheduler                                                                                            | 81 |

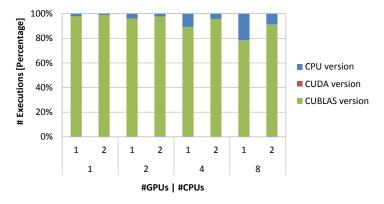

| 5.10 | Matrix multiply task statistics with versioning scheduler                                                                                                 | 82 |

|      | Cholesky factorization performance results with versioning scheduler                                                                                      | 83 |

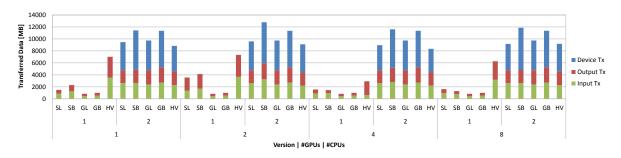

|      | Transferred data for Cholesky with versioning scheduler                                                                                                   | 83 |

|      | Cholesky task statistics with versioning scheduler                                                                                                        | 84 |

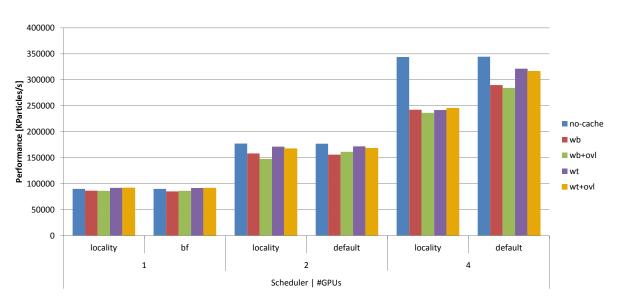

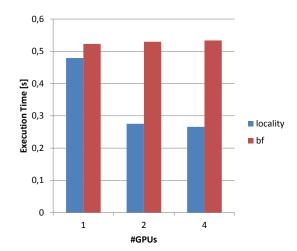

|      | PBPI execution time results with versioning scheduler                                                                                                     | 85 |

|      | Transferred data for PBPI with versioning scheduler                                                                                                       | 85 |

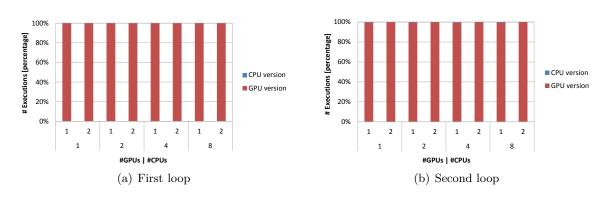

|      | PBPI task statistics for first and second loops with versioning scheduler                                                                                 | 86 |

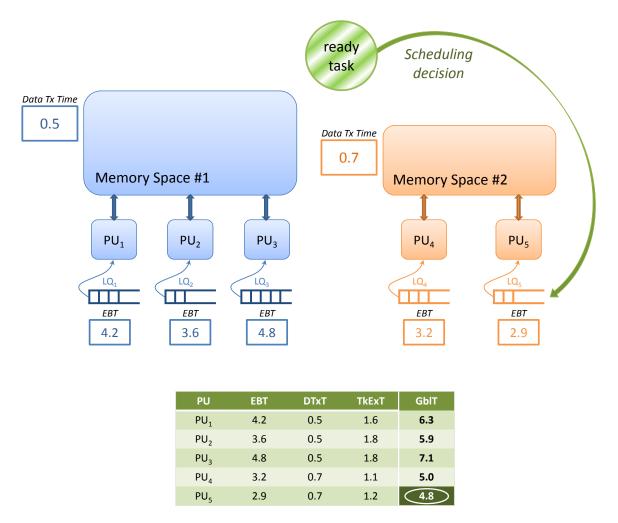

|      | SSMART scheduling decisions and timing table                                                                                                              | 88 |

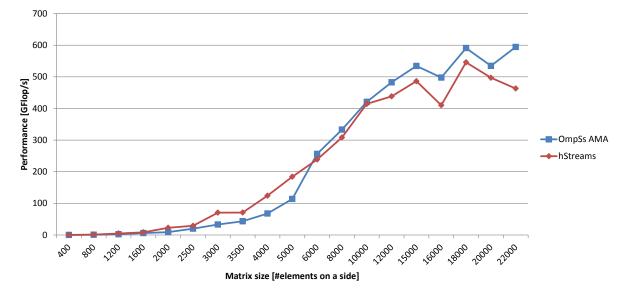

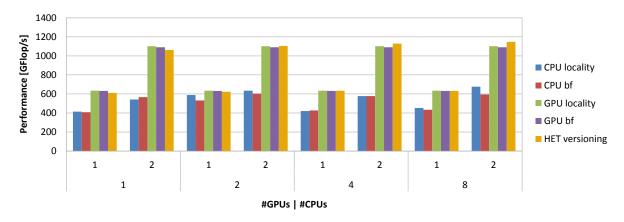

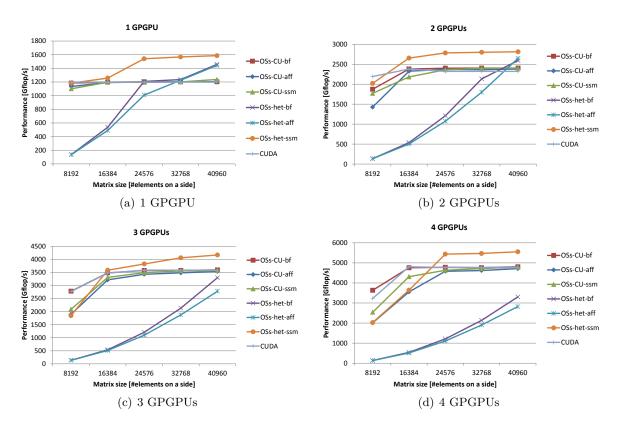

|      | Matrix multiply performance results of SSMART on a multi-GPU system                                                                                       | 92 |

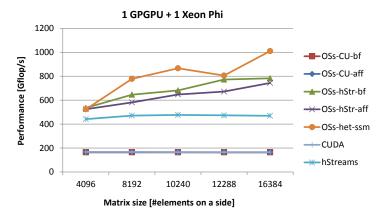

|      | Matrix multiply performance results of SSMART on a multi-accelerator system .                                                                             | 93 |

|      | Cholesky factorization performance results of SSMART on a multi-GPU system .                                                                              | 94 |

|      | 0 <b>1</b> 0                                                                                                                                              | 95 |

| 5.22 | FFT1D performance results of SSMART on a multi-GPU system                                                                                                 | 96 |

# List of Tables

| 1.1 | Comparison between different architecture product characteristics  | 1   |

|-----|--------------------------------------------------------------------|-----|

| 4.1 | Matrix multiply configurations                                     | 62  |

| 4.2 | Cholesky factorization configurations                              | 63  |

| 4.3 | N-Body simulation configurations                                   | 65  |

| 5.1 | Versioning's data structure for heterogeneous tasks                | 74  |

| 5.2 | Description of the different application configurations used       | 91  |

| A.1 | OmpSs GPU-related configuration options                            | 108 |

|     | OmpSs Xeon Phi-related configuration options                       |     |

| B.1 | Source code comparison between OmpSs, sequential C and native CUDA | 114 |

| B.2 | Source code comparison between OmpSs, OpenMP and native hStreams   | 117 |

| B.3 | Summary of the source code comparison                              | 117 |

# Chapter 1 Introduction

# 1.1 Context and Motivation

**H**ETEROGENEOUS high-performance computers have become a key evolution of regular homogeneous CPU systems due to their computing power. The addition of specialized processing units (accelerators) to regular CPU systems has led a tremendous revolution in the High Performance Computing (HPC) world: on the one hand, the ratio between performance and energy consumption, also known as *performance per Watt*, has significantly increased. On the other hand, vendors offer such kind of devices at very competitive prices, so the ratio between performance and hardware prices, also known as *performance per Euro/Dollar*, has considerably raised as well. The main examples of these recent hardware accelerators include General Purpose GPUs (GPGPUs) [1, 2], the Intel Xeon Phi [3] or FPGAs [4].

Table 1.1 compares the peak performance (single and double precision), power consumption and cost of three different accelerators from nVIDIA, AMD and Intel and one general purpose CPU from Intel respectively [5, 6, 7, 8, 9, 10]. The general purpose CPU has clearly the lowest performance per Watt and performance per Dollar ratios: while its performance is two orders of magnitude lower than the accelerators, it consumes around half the power of accelerators. Moreover, it is the most expensive architecture.

| Architecture         | Peak Perf. | (GFlop/s) | Power Consumption (W) | Cost $(\$)^a$ |

|----------------------|------------|-----------|-----------------------|---------------|

|                      | SP         | DP        |                       |               |

| nVIDIA GTX 980 Ti    | 6144       | 192       | 250                   | 806           |

| AMD FirePro S9150    | 5070       | 2530      | 235                   | 3323          |

| Intel Xeon Phi 7120P | 2416       | 1208      | 300                   | 3883          |

| Intel Xeon E7-8770   | 96         | 48        | 130                   | 5402          |

The current TOP500 list (from June 2015) [11] reflects the popularity of heterogeneous com-

Table 1.1: Comparison between different architecture product characteristics

<sup>&</sup>lt;sup>a</sup> Reference prices were extracted from US Amazon website as of July 2015.

#### 1. INTRODUCTION

puters, as four of the top 10 machines have either GPGPUs or Xeon Phi coprocessors, the top 2 being heterogeneous computers. Moreover, this trend has held for the last two years. We can then expect that future many-core chips will be heterogeneous (different type of processors, including accelerators) and may be organized in a certain hierarchy (for example, organized in clusters of cores, possibly with associated local memory).

Heterogeneity adds adaptability to a machine, as different processing units of a system may offer better capabilities for specific computations. For example, compute-intensive algorithms fit perfectly on GPGPUs, as they offer a peak performance that can be up to 2 orders of magnitude greater compared to a normal CPU. To make the most of heterogeneous systems, applications should be split into different portions depending on their computational characteristics and requirements. Then, ideally, each portion, should be executed on the processing unit that will run it in the most efficient way.

However, heterogeneity makes the programming task more difficult, especially for programmers that want to fully exploit machine resources. Firstly, some accelerators, like GPGPUs, may not be able to run regular CPU code; others, like the Intel Xeon Phi, are able to run CPU code directly, but it may not exploit its massively-parallel hardware. So, in any case, applications targeting traditional CPU architectures may have to be redesigned and rewritten. Secondly, even in single-node systems, accelerators may have their own separated memory space with limited capacity and access restrictions. From the programmer's point of view, CPUs usually have a single memory space with several transparent mechanisms that speed-up memory accesses, like the different levels of hardware caches. But accelerators, like GPGPUs, expose their memory hierarchy to programmers and leave them the decision of where to put each piece of data as well as the responsibility of moving data from one memory space to another. This forces programmers to include additional code to manage data movements across different memory spaces and to keep data coherency. Finally, distributing the execution of an application among all the computing resources of a system is a non-trivial task and heterogeneity makes it even more complex: synchronizations become particularly complicated if we want to split the computation between multiple devices and still want to get optimal performance. Therefore, code maintenance and performance portability become more complex (and expensive) as source codes must be adapted to fit new architectures. In other words, heterogeneity has raised the programming wall up to an unaffordable level for programmers.

Several proposals have arisen in the last years to program accelerators, the most important being CUDA [12], which targets NVIDIA GPUs, and OpenCL [13], which works with Intel Xeon Phi cards and GPGPUs as well. However, none of them addresses the aforementioned challenges, since they both expose the underlying hardware to the programmer and only offer a resource management API. Consequently, programming models should be able to hide heterogeneity and hierarchy in a way that applications are unaware of the underlying hardware and that can dynamically adapt to it. Moreover, this would allow programmers focus on their application development and forget about the management of available resources, data movements and synchronizations.

The code in Figure 1.1 implements the scale function in CUDA: it multiplies vector A by the scalar sc. The figure illustrates the additional actions that programmers must add in their source codes in order to offload a computation to a GPGPU in CUDA: first, allocate and transfer memory to the device. Then, offload the computation and synchronize with the

```

global___ void scale_kernel (int n, double *A, double sc)

2 \\ 3 \\ 4 \\ 5

int idx = blockIdx.x * blockDim.x + threadIdx.x;

if

(idx < n)

\begin{array}{l} & & \text{A[idx]} = \text{A[idx]} * \text{sc;} \\ & & \text{A[idx]} = \text{A[idx]} * \text{sc;} \\ & & \text{8} \\ & & \text{9 void scale (int n, double *A, double sc)} \end{array}

10 \{

Allocate device memory

11

12

double *dA;

cudaMalloc(&dA, n * sizeof(double));

13

14

// Transfer data to device memory

cudaMemcpy(&dA, &A, n * sizeof(double), cudaMemcpyHostToDevice);

15

16

17

18

Offload computation

19

dim3 dimBlock (256);

dim3 dimGrid ((n / dimBlock.x) + 1);

20

21

scale_kernel <<< dimGrid , dimBlock >>>(n , dA , sc);

22

Synchronize with device

23

24

cudaDeviceSynchronize();

25

26

Copy result back to host

27

cudaMemcpy(&A, &dA, n * sizeof(double), cudaMemcpyDeviceToHost);

28

Free device memory

29

30

cudaFree(dA);

31 }

```

Figure 1.1: A simple CUDA implementation of scale function

device. In addition, the device kernel implementation (*scale\_kernel*) must be provided by the programmer. Finally, copy the result back to the host and free all the allocated resources. This source code is not optimized and its only objective is to show all the additional steps that must be done to offload a computation to a GPGPU. In order to optimize this code, these operations should be split into smaller parts, each one processing smaller pieces of the vector, so that computations and data transfers can be overlapped. Writing a code that splits the computation across multiple devices would even be more complex.

# **1.2** Programming Challenges in Heterogeneous Systems: One code does not fit all

In general, there is not a single piece of code that fits all the existing hardware architectures, and even if we find that code, it will not be the best (in terms of performance, energy consumption, etc.) for all of them. Thus, it is not unusual to find different ways of implementing the same algorithm. As an example, there are uncountable versions of the matrix multiply algorithm. Figure 1.2 shows a simple CPU implementation of a tiled matrix multiply algorithm that could run in different architectures. However, this is not the optimal version for any of them.

There are many libraries that implement highly optimized versions of this algorithm for CPUs, like BLAS [14], LAPACK [15] or MKL [16]. The matrix multiply implementation found in these libraries has vectorized code to fully exploit the CPU hardware capabilities and is usually optimized for particular matrix sizes (e.g. power-of-two matrix sizes or square matrices).

```

1 void dgemm (int m, int l, int n, double *tileA, double *tileB, double *tileC)

\frac{2}{3}

{

for (int i = 0; i < m; i++)

for (int j = 0; j < n; j++)

for (int k = 0; k < 1; k++)

4

5

\begin{bmatrix} 6\\7 \end{bmatrix}

tileC[i*n+j] += tileA[i*l+k] * tileB[k*n+j];

8

9 void matmul (int m, int l, int n, double **A, double **B, double **C, int tm, int tl, int tn)

10 {

for

(int i = 0; i < m; i++)

11

12

for (int j = 0; j < n; j++)

for (int k = 0; k < 1; k++)

13

14

dgemm(tm, tl, tn, A[i*l+k], B[k*n+j], C[i*n+j]);

15 }

```

Figure 1.2: A simple C implementation of matrix multiply

However, none of the aforementioned CPU libraries will work on GPGPUs. Instead, there are specific GPU-compatible implementations that can be found in libraries like CUBLAS [17] or MAGMA [18]. Indeed, these implementations are carefully designed to fully exploit GPU capabilities and massively parallel hardware. Thus, these codes are highly parallelized, take into account how memory accesses are performed (as certain sequences of memory accesses give higher memory bandwidths), make use of GPU registers and shared memory to reduce memory latency, etc. Also, these codes are usually optimized for certain matrix sizes and, depending on that, different kernel configurations (thread grid size and block size) are selected as well. In addition, some libraries, like CUBLAS, have several internal implementations optimized for a particular GPGPU hardware family, as different hardware families may present different characteristics and require different optimizations.

For example, the code in Figure 1.3 illustrates a simple CUDA implementation of matrix multiply. In contrast with the scale function presented before, there is no need to provide the kernel code in this case, as the application calls CUBLAS to offload the computation to the GPGPU. However, CUBLAS requires additional initialization and clean-up operations that must be done by the programmer. In this case, implementing a tiled version of this algorithm would make it possible to overlap operations or even split the computation across several GPGPUs. However, this would introduce much more complexity in terms of programmability.

To make things even more complicated, the Xeon Phi cards present a combination of CPU and GPGPU properties: on the one hand, Xeon Phi cards are built with regular CPUs, so vectorization is a key factor for any code to achieve good performance. On the other hand, it offers a massively parallel hardware where hundreds of threads can run simultaneously. Then, all these hardware properties must be taken into account to write optimized codes. In this case, the native MKL library for Xeon Phi [19] provides a matrix multiply implementation especially designed for this type of architecture.

The source code in Figure 1.4 shows the same simple matrix multiply algorithm targeting the Xeon Phi architecture. The hStreams [20] library provided by Intel is used to manage the offloading and call the native MKL library to perform the computation on the device. Like the CUDA version, this code is not optimized and a more complex tiled structure would be needed to make it more efficient. These codes reflect the diversity and complexity that programmers must face when writing applications for heterogeneous systems.

```

1 void matmul (int m, int l, int n, double *A, double *B, double *C)

2 {

// Allocate device memory

double *dA, *dB, *dC;

3

4

cudaMalloc(&dA, m * 1 * sizeof(double));

cudaMalloc(&dB, 1 * n * sizeof(double));

5

6

7

cudaMalloc(&dC, m * n * sizeof(double));

8

// Initialization needed by device libraries

cublasHandle_t handle;

cublasCreate(&handle);

9

10

11

12

13

Transfer data to device memory

cudaMemcpy(&dA, &A, m * 1 * sizeof(double), cudaMemcpyHostToDevice);

cudaMemcpy(&dB, &B, 1 * n * sizeof(double), cudaMemcpyHostToDevice);

14

15

cudaMemcpy(\&dC, \&C, m * n * sizeof(double), cudaMemcpyHostToDevice);\\

16

17

Offload computation

18

cublasDgemm(handle, CUBLAS_OP_T, CUBLAS_OP_T, m, n, l, &alpha, dA, l, dB, n, &alpha, dC, m);

19

20

21

22

// Sunchronize with device

cudaDeviceSynchronize();

23

24

25

// Copy result back to host

26

cudaMemcpy(&C, &dC, m * n * sizeof(double), cudaMemcpyDeviceToHost);

27

28

Free device memory and clean-up device libraries

cudaFree(dA);

29

cudaFree(dB);

30

31

cudaFree(dC);

cublasDestroy(handle);

32

33 }

```

Figure 1.3: A simple CUDA implementation of matrix multiply calling CUBLAS library

```

1 void matmul (int m, int l, int n, double *A, double *B, double *C)

2 \{

3

Initialize hStreams library and allocate device memory

hStreams_app_init(1, 1);

hStreams_app_create_buf(A, m * 1 * sizeof(double));

4

5

\frac{6}{7}

hStreams_app_create_buf(B, l * n * sizeof(double));

hStreams_app_create_buf(C, m * n * sizeof(double));

8

9

All \ operations \ are \ asynchronous\,, \ but \ use \ the \ same \ stream\,,

10

\not/ so hStreams will control data dependences between them

11

int stream = 1;

12

Transfer data to device memory

13

hStreams_app_xfer_memory(A, A, m * 1 * sizeof(double), stream, HSTR_SRC_TO_SINK, NULL);

hStreams_app_xfer_memory(B, B, 1 * n * sizeof(double), stream, HSTR_SRC_TO_SINK, NULL);

hStreams_app_xfer_memory(C, C, m * n * sizeof(double), stream, HSTR_SRC_TO_SINK, NULL);

14

15

16

17

// Offload computation, native MKL will be invoked on device

hStreams_app_dgemm(CblasRowMajor, CblasNoTrans, CblasNoTrans

1.0, A, m, B, l, 1.0, C, m, stream, NULL);

18

CblasNoTrans, m, n, l,

19

20

21

22

' Copy result back to host

23

hStreams_app_xfer_memory(C, C, m * n * sizeof(double), stream, HSTR_SINK_TO_SRC, NULL);

24

Sunchronize with device

25

26

hStreams_app_thread_sync();

27

28

Free device memory and finalize hStreams library

29

hStreams_DeAlloc(A);

30

hStreams_DeAlloc(B);

31

hStreams_DeAlloc(C);

32

hStreams_app_fini();

33 }

```

Figure 1.4: A simple hStreams implementation of matrix multiply for Intel Xeon Phi

Despite these software development problems, accelerators have become very popular thanks to its capabilities: a small amount of them can give the same computational power as a supercomputer at a considerably lower price. Unfortunately, they are not the universal solution to accelerate existing applications, as they can perform very well at compute-intensive algorithms, but we can find a large set of applications where accelerators get no speed-up, or even perform worse than CPUs.

Nowadays, it is the programmer responsibility to consider whether their code (or a part of it) can benefit from accelerator capabilities and to add all the necessary operations to perform such offloading. Nevertheless, there are many research lines opened in software systems for heterogeneous computers. Hopefully, these software systems will become smart enough in the future to make all these decisions automatically and transparently to help programmers. The work developed in the context of this thesis is an example and other research proposals are illustrated in Chapter 3 as well. For example, the OpenMP and OpenACC directive-based programming models are two high-level proposals that seek lowering the programming wall by offering code portability across different architectures.

# **1.3** Contributions

The main goal of this PhD thesis is to design the appropriate scheduling techniques and resource management for heterogeneous systems. The objective is to include them into a runtime system, so that they are completely automatic and transparent to programmers. In order to prove the validity of this work and increase its impact on the scientific community, the research has been focused on the two most common accelerators that exist nowadays: GPGPUs and Intel Xeon Phi.

In recent years, task programming has become popular and fits perfectly well in heterogeneous programming, as each task can be seen as the sequential piece of code that is run by one of the machine resources. However, developing a new programming model from scratch is out of the scope of this thesis. OmpSs is an OpenMP-like task-based programming model. It has been carefully designed in a modular way and can be extended easily with new features. OmpSs offers flexibility to programmers and adaptability to current and future hardware architectures. For these reasons, OmpSs was chosen as the basis of this work and all thesis contributions have been developed and tested on top of it.

The contributions of this thesis can be divided into two main areas described below:

- □ Accelerator support and management: we demonstrate that it is possible to hide the difficulties of accelerator programming from the programming model side. In this sense, we have designed an approach capable of performing all the accelerator-related management (like execution offloading, data movements or synchronizations) that is completely transparent and needs no additional effort from the programmer. This approach mainly targets task-based programming frameworks and adds the specific support needed to offload task execution to GPGPU and Xeon Phi accelerators.

- □ Scheduling techniques for heterogeneous architectures: we provide a set of scheduling techniques especially designed for heterogeneous architectures. Each technique focuses on a different objective (like minimizing the amount of data transfers, prioritizing the

execution of critical paths, or maximizing the resource utilization) and they can also be combined together. We prove that our scheduling techniques can dynamically decide the best task execution order and distribution for a particular objective.

Figure 1.5: Illustration of thesis contributions

Figure 1.5 pictures the thesis contributions and how they are integrated in the OmpSs framework. The accelerator support and scheduling techniques have been added into the OmpSs framework and can be combined to execute OmpSs applications.

The publications that support this thesis are listed below in chronological order.

- [21] Javier Bueno, Judit Planas, Alejandro Duran, Xavier Martorell, Eduard Ayguadé, Rosa M. Badia and Jesús Labarta. Productive Programming of GPU Clusters with OmpSs. Paper presentation, 26th IEEE International Parallel and Distributed Processing Symposium. May 21-25, 2012. Shangai, China.

- [22] Judit Planas, Rosa M. Badia, Eduard Ayguadé and Jesús Labarta. Self-Adaptive OmpSs Tasks in Heterogeneous Environments. Paper presentation, In proc. of 27th IEEE International Parallel & Distributed Processing Symposium (IPDPS 2013). Boston, Massachusetts, USA. May 2013.

- □ [23] Judit Planas, Rosa M. Badia, Eduard Ayguade, and Jesus Labarta. AMA: Asynchronous Management of Accelerators for Task-based Programming Models. Paper presentation, International Conference on Computational Science (ICCS 2015), Volume 51, Pages 130-139. Reykjavik, Iceland. June 2015.

- □ Judit Planas, Rosa M. Badia, Eduard Ayguadé and Jesús Labarta. SSMART: Smart Scheduling of Multi-ARchitecture Tasks on Heterogeneous Systems. Submitted to Second Workshop on Accelerator Programming using Directives (WACCPD). 2015.

The contributions of this thesis have also been published as part of a collective group work. The related publications are listed below in chronological order.

- [24] Eduard Ayguadé, Rosa M. Badia, Pieter Bellens, Daniel Cabrera, Alejandro Duran, Marc Gonzalez, Francisco Igual, Daniel Jimenez-Gonzalez, Jesús Labarta, Luis Martinell, Xavier Martorell, Rafael Mayo, Jose M. Perez, Judit Planas and Enrique S. Quintana-Ortí. *Extending OpenMP to Survive the Heterogeneous Multi-core Era.* Journal publication, International Journal of Parallel Programming, Vol. 38, No. 5-6, 440-459. June 2010.

- [25] R. Ferrer, J. Planas, P. Bellens, A. Duran, M. Gonzalez, X. Martorell, R. Badia, E. Ayguadé and J. Labarta. Optimizing the Exploitation of Multicore Processors and GPUs with OpenMP and OpenCL. Paper presentation, In proceedings of the 23rd International Workshop on Languages and Compilers for Parallel Computing. October, 2010. Houston, Texas, USA.

- [26] Alejandro Duran, Eduard Ayguadé, Rosa M. Badia, Jesús Labarta, Luis Martinell, Xavier Martorell and Judit Planas. OmpSs: A proposal for programming heterogeneous multi-core architectures. Journal publication, Parallel Processing Letter, Volume 21, Issue 2, pp. 173 - 193. June, 2011.

- [27] Eduard Ayguade, Rosa M. Badia, Pieter Bellens, Javier Bueno, Alex Duran, Yoav Etsion, Montse Farreras, Roger Ferrer, Jesus Labarta, Vladimir Marjanovic, Lluis Martinell, Xavier Martorell, Josep M. Perez, Judit Planas, Alex Ramirez, Xavier Teruel, Ioanna Tsalouchidou and Mateo Valero. *Hybrid/Heterogeneous Programming With OmpSs And Its Software/Hardware Implications*. Book chapter, In Programming Multicore and Many-core Computing Systems (Wiley Series on Parallel and Distributed Computing), ed. John Wiley & Sons, Inc. January 2012.

- □ Chris J. Newburn, Gaurav Bansal, Judit Planas, Alejandro Duran, Paulo Souza, Leonardo Borges and Jesus Labarta. *Heterogeneous Streaming. Under submission process.*

The next sections describe the contributions in more detail and link them with the publications.

#### 1.3.1 Accelerator Support and Management

This thesis contributes with the design and implementation of an efficient way to give support and manage task execution on accelerators. Our design is based on the asynchronous property that most accelerators present and focuses on minimizing the amount of time spent in host-device synchronization. As explained before, it mainly focuses task-based programming frameworks. With our contribution, we add all the necessary support to the target framework to be able to offload tasks to a given accelerator. This support includes (i) runtime operations such as device initialization and configuration (if needed), data movements, host-device synchronization and task offloading and (ii) compiler capabilities to apply the appropriate source code transformations to enable task offloading to accelerators. This model has been presented in several publications [24], [26] and [27].

Figure 1.6 illustrates the OmpSs implementation of the simple matrix multiply code presented before. By just inserting the **target**, **task** and **taskwait** directives, OmpSs will offload the computation to a GPGPU and will handle all the necessary memory movements. In this

```

1 #pragma omp target device (cuda) copy_deps

2 \# pragma omp task inout([m][n]tileC) in([m][1]tileA,

[1][n]tileB)

3 void matmul_kernel (int m, int l, int n, double *A, double *B, double *C)

4 \ \{

\mathbf{5}

double alpha = 1.0;

6

7

Get the appropriate execution stream and CUBLAS context from OmpSs runtime

cublasHandle_t handle = nanos_get_cublas_handle();

\frac{8}{9}

cudaStream_t stream = nanos_get_kernel_execution_stream();

{\tt cublasSetStream\,(\,handle\,,\ stream\,)\,;}

10

11

12

cublasDgemm(handle, CUBLAS_OP_T, CUBLAS_OP_T, m, n, l, &alpha,

13

A, m, B, l, &alpha, C, m);

14 }

15

16 void matmul (int m, int l, int n, double *A, double *B, double *C)

17 {

18

No need to allocate nor transfer device memory

19

// CUBLAS library is initialized inside OmpSs runtime

20

21

// Offload computation

22

matmul_kernel(m, l, n, A, B, C);

23

24

Synchronize with device

25

This synchronization also brings output data back to the host

26

#pragma omp taskwait

27

// No need to free device memory nor clean-up CUBLAS library % \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}

28

29 }

```

Figure 1.6: Simple OmpSs matrix multiply code using the GPGPU to offload the computation

case, since the CUBLAS library is used, the code in lines 8-10 is required by the runtime to properly manage the offloading. This CUBLAS particularity is explained and justified in detail in Section 4.1.2.5.

Regarding the runtime contribution, two different prototypes where explored: first, a semiasynchronous approach and, second, a fully asynchronous approach.

#### 1.3.1.1 Semi-asynchronous Approach

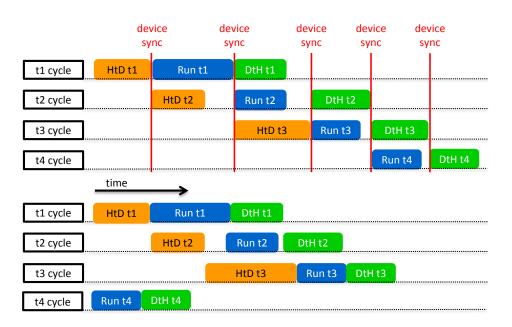

The semi-asynchronous approach interleaves asynchronous periods with fully blocking synchronized points because the existing technologies, by the time it was implemented, did not offer any possibility for a fully asynchronous host-device communication behavior.

Having blocking synchronizations negatively affects performance, because this means that the CPU has to block at some points and waste its time while it is waiting for the device to finish its operations (data transfers and computations). But this was the only way to check for the state of operations that were issued to the device. So, we found a compromise between the number of blocking synchronization points and the level of control the host had over the device.

The semi-asynchronous approach was only implemented and tested on GPGPUs devices because it was the most famous and almost the only type of accelerators that existed by that time. This work was published as a conference paper [21].

## 1.3.1.2 Fully asynchronous Approach

Although the semi-asynchronous approach was good enough for its time, as the technology evolved, accelerators offered new features that could clearly improve our first approach. Thus, a second prototype, called AMA (Asynchronous Management of Accelerators), was designed with the property of being completely asynchronous.

AMA is able to completely remove the previous blocking synchronizations and establish and event-driven communication between host and device. This approach clearly enhances the existing design because it completely decouples the operations done on both host and device sides. The main idea behind this design is to use the CPU to do some other useful work while it is waiting for the device to finish its computations.

We have proved the validity of the fully asynchronous approach with two of today's most famous accelerators: GPGPUs and Intel Xeon Phi. This model and its GPGPU implementation were presented as a conference paper [23]. The Intel Xeon Phi related work is under publication process.

# 1.3.1.3 Accelerator Compiler Support

In order to make the accelerator programming task easier, the accelerator compiler support tries to minimize as much as possible the source code differences between calling a regular CPU task or an accelerator task. For example, in the case of GPGPUs, the compiler inserts calls to the runtime that will decide at run time which execution stream is used for each kernel, being this completely transparent from the programmer point of view. This work was published as a conference paper [25].

# **1.3.2** Scheduling Techniques for Heterogeneous Architectures

The second thesis contribution is a set of scheduling techniques designed and optimized for heterogeneous architectures. Also targeting task-based programming frameworks, each of our scheduling technique focuses on a specific objective and finds the best task execution order and distribution to accomplish such objective.

The set of scheduling techniques focuses on the following objectives: prioritize the execution of the critical path of an application (task priority propagation), minimize the amount of data transferred (affinity-ready scheduler), maximize system's resource utilization (versioning scheduler) and a combination of maximizing resource utilization while minimizing the amount of data transfers (SSMART scheduler).

# 1.3.2.1 Task Priority Propagation

Assuming that we have a task graph where tasks that belong to the critical path<sup>1</sup> are assigned higher priorities than those outside the critical path, the task priority propagation mechanism helps finding such tasks with higher priority in advance.

$<sup>^{1}</sup>$  The critical path of an application task graph is the sequence of tasks determining the minimum time needed to execute the application.

We do not consider this mechanism a scheduling technique itself, but it can be combined with any other scheduling technique to help it improve the order in which tasks are being run. This work was published in a conference paper [23].

# 1.3.2.2 Affinity-ready Scheduler

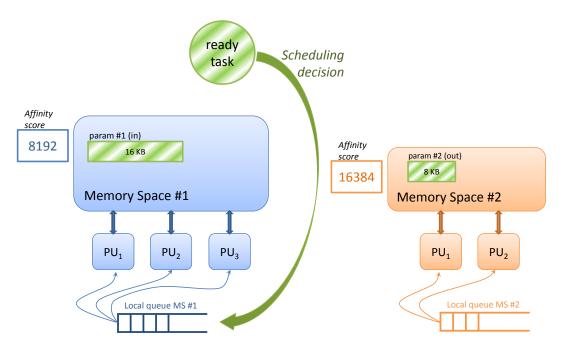

This scheduling technique checks for task data locality and assigns each task to the processing unit that needs less data to be transferred to run the given task. It is especially designed for accelerators by carefully accounting the number of total bytes that need to be transferred for each task.

In addition, it can be combined with the task priority mechanism to enhance the order in which tasks are selected. This work was published in a conference paper [23].

### 1.3.2.3 Versioning Scheduler

The versioning scheduling technique contributes in two aspects of the programming framework. First, it adds the ability to join separate pieces of code (i.e. new or alternative task implementations) to the original application without having to modify it. And second, proposes a new scheduling strategy to evaluate these new added pieces. The aim of this contribution is performance portability at low-cost maintenance: programmers can add different task implementations of the same algorithm (that can also target different architectures) and let the runtime dynamically explore and decide which implementation is chosen each time a task is called.

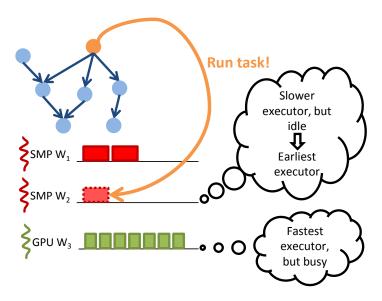

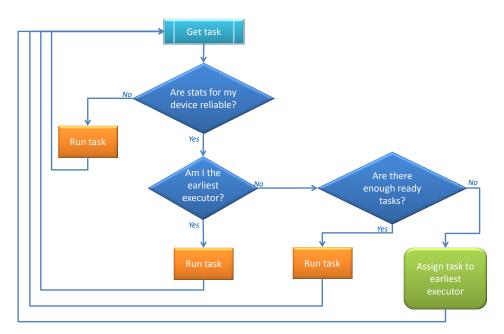

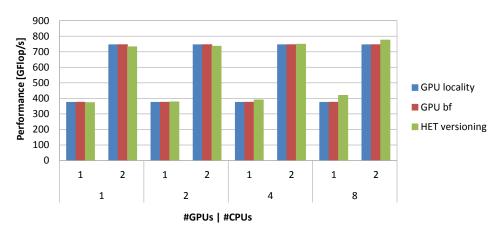

The main objective of the scheduling strategy is to increase application performance by maximizing resource utilization: task<sup>2</sup> performance is monitored on each processing unit and a look-ahead scheduling is done to find the best distribution of future tasks on system resources. Since all system resources cooperate to run the application, its performance can be potentially increased. This work was presented as conference paper [22].

#### 1.3.2.4 SSMART Scheduler

The SSMART scheduler completes the set of scheduling techniques by combining and improving some of the aforementioned scheduling objectives. On the one hand, it enhances the versioning scheduler in several aspects and, on the other hand, combines both versioning and affinity-ready objectives.

In short, SSMART extends the versioning scheduler characteristics in the following aspects: first, SSMART takes into account data locality to decide which processing unit is the most suitable to run a task as well as the estimated time needed for data transfers. Second, for each pair task-processing unit, SSMART creates a rank of suitability (how good is a processing unit to run the given task, taking into account its workload and task data locality). Then, if needed, the scheduler is able to decide the most suitable device within a subset of the processing units of the whole system. Third, SSMART allows stealing tasks that were already assigned to a certain processing unit. Fourth, it supports task priority propagation. Finally,

$<sup>^{2}</sup>$  Only those tasks that have more than one implementation are taken into account in the monitoring and scheduling process. The rest of the tasks are scheduled following a breadth-first strategy.

versioning only profiles tasks with more than one implementation, while SSMART profiles all tasks of the application. This work is under publication process.

# 1.4 Thesis Organization

This thesis document is structured in the following way: this chapter, Chapter 1, is the introduction and describes the motivations, the context and the contributions of this thesis. Chapter 2 gives an overview of OmpSs, the programming model and framework used as the basis to develop the contributions of the thesis. It also includes a description of the applications that have been used to evaluate the implementations. The following chapter, Chapter 3, summarizes the state of the art with respect to each thesis contribution. Then, Chapters 4 and 5 give a detailed description of the contributions and present their evaluation. The conclusions and future work of this thesis are discussed in Chapter 6. Finally, the reader can find the bibliography at the end of this document.

In addition, as a complement of the preceding chapters, Appendix A shows the specific OmpSs runtime options for GPGPU and Xeon Phi devices and Appendix B compares the source codes of an OmpSs version of a tiled matrix multiply algorithm with sequential C, CUDA, OpenMP and hStreams versions.

# Chapter 2 Development Environment

$\mathbf{T}^{\mathrm{HIS}}$  chapter introduces the OmpSs programming model and describes the applications that have been used in the context of this thesis.

# 2.1 OmpSs programming model

The OmpSs programming model [24] defines a single task-based programming model for homogeneous and heterogeneous architectures and is open to support new architectures that may appear in the future.

OmpSs combines ideas from OpenMP [28] and StarSs [29]: on the one hand, it enhances OpenMP with support for irregular and asynchronous parallelism and heterogeneous architectures and, on the other hand, it incorporates StarSs dependence support [30] and data-flow concepts that allow the framework to automatically move data as necessary and perform different kinds of optimizations. OmpSs is currently able to run applications on clusters of nodes that combine shared memory processors (SMPs) and other external devices, for example, FPGA, GPU and Xeon Phi [21, 23, 31], being the last two contributions of this thesis.

#### 2.1.1 Execution Model

OmpSs uses a thread-pool execution model instead of the traditional OpenMP fork-join model. There is a master thread that starts the execution of the application and several other threads that cooperate executing the work it creates from worksharing or **task** constructs. Therefore, unlike OpenMP, there is no need for a **parallel** region. Nesting of constructs allows other threads to generate work as well.

An application's inherent parallelism is exploited from **task** constructs at runtime: a datadependency graph is dynamically built with the information extracted at compile time from parameter directionality clauses (**in**, **out** and **inout**). This task graph construction is essential to keep application's data coherence and correctness. Then, only ready tasks (i.e. tasks that do not depend on other tasks) can be run in parallel.

#### 2.1.2 Memory Model

From the application point of view, there is a single address space. However, internally, OmpSs assumes that multiple address spaces may exist. Then, data can be shared between these address spaces and may reside in memory locations that are not directly accessible from some of the computational resources. Thus, all parallel code can only safely access private and shared data that has been marked explicitly with OmpSs extended syntax. This assumption is true even for SMP machines as the implementation may reallocate shared data to improve memory accesses in, for example, NUMA systems [32].

The runtime takes care of where data resides by means of a directory structure. The architecture support manages data transfers between memory spaces as tasks consume or produce them. Data can be replicated on different memory spaces and coherency is transparently managed by the runtime.

#### 2.1.3 OmpSs Syntax Extensions

OmpSs supports OpenMP directives in general, but, additionally, it defines several extensions to OpenMP's syntax that are explained below:

Dependency synchronization: OmpSs integrates the StarSs dependence support. It allows annotating tasks with three clauses: in, out and inout. They allow expressing, respectively, that a given task depends on some data produced before, that it will produce some data, or both. The clause allows specifying arrays, pointers and pointed data. Data addresses and sizes do not need to be constant at compile time since they are computed at execution time. In addition, the **taskwait** construct is extended with the **on** clause, which allows the encountering task to block only until the set of data specified in this clause is produced. **taskwait** has been extended as well with the **noflush** clause which allows synchronizing tasks without flushing all the data on remote devices.

Dependence clauses have been recently introduced in OpenMP 4.0: the OpenMP depend clause is now very similar to the OmpSs in, out and inout clauses. However, OmpSs is able to detect dependences between non-contiguous or strided regions whereas OpenMP uses the initial address of a region to detect task dependencies. Therefore, partially overlapping or strided regions cannot be detected [33, 34].

- □ The target construct: This extension was introduced to support heterogeneity and data motion and it is represented by the target construct [35]. It can be applied to tasks and accepts the following clauses:

- device: It specifies which devices can run the associated code (e.g., fpga, gpu, smp). SMP device (for CPUs) is assumed by default. The construct target device can also be applied to other functions that are not necessarily tasks.

- **copy\_in**: It specifies that some data must be accessible to the task when running. This may imply a data transfer between memory spaces.

- **copy\_out**: It specifies that some data that was accessible to the task when running will be the only valid version when the task finishes its execution.

- **copy\_inout**: This clause is a combination of **copy\_in** and **copy\_out**.

- copy\_deps: It specifies that any task's dependence clause will also have copy semantics (i.e., in will be also considered copy\_in, out will be also copy\_out and inout will be also copy\_inout). To make sure that data that were moved to a device are valid again in the host, SMP tasks (for CPUs) must also use the copy clauses or appear after an either implicit or explicit OpenMP flush.

- implements: This clause is used to specify that the annotated task is an implementation of another task and has been developed in the context of this thesis.

Since OpenMP 4.0, the **target** construct is accepted in OpenMP as well. But the semantics are very different: while the OpenMP construct forces the programmer to specify which data movements must be performed, OmpSs offers the possibility to deduct the necessary data transfers from the data-dependency clauses (**copy\_deps** clause). Moreover, The OpenMP **device** receives an integer parameter that identifies the physical unit where the task will be run. In contrast, OmpSs **device** clause is used to specify the architecture type of the task; the runtime will transparently decide which physical unit (of the appropriate architecture type) executes the task. This approach is more flexible and the same source code can run in different machine configurations regarding the number and type of available processing units. In addition, OmpSs is not able to generate device code, so the appropriate kernel code (e.g. in CUDA, OpenCL, etc.) is required.

The different copy clauses do not necessarily imply a copy before and after the execution of each task. This allows the runtime to take advantage of devices with access to the shared memory or implement different data caching and prefetching techniques without the user needing to modify their code.

The OmpSs framework is distributed with two different components: the Nanos++ runtime library and the Mercurium source-to-source compiler, both explained below.

### 2.1.4 Nanos++ Library

Nanos++ [36] is an extensible runtime library that supports the OmpSs programming model. Its responsibility is to schedule and execute *parallel tasks* as specified by the compiler, based on constraints specified by the user: order, coherence, etc.

Most of the runtime components are independent from the actual target architectures, so general runtime characteristics are explained in this chapter and the specific architecture support developed in the context of this thesis is described in Chapter 4. As of today, Nanos++ supports the following *conceptual* architectures:

- □ **smp**: targets general purpose CPUs.

- □ **smp-numa**: used in Non-Unified Memory Access (NUMA) systems with general purpose CPUs.

- $\hfill\square$  gpu [37]: offloads tasks in CUDA-capable GPGPUs.

- □ opencl: offloads tasks to any architecture that supports OpenCL (currently CPUs, GPGPUs and Xeon Phi).

- □ hstreams: offloads tasks to any architecture supported by the hStreams library (currently Xeon Phi, general purpose CPUs will be supported in the future as well).

- **fpga**: offload tasks to FPGA devices.

- □ cluster [38]: distributes tasks among the different nodes of a cluster system and can be combined with other conceptual architectures that the hardware system may offer.

- □ mpi: distributes tasks among the different nodes of a cluster system using the Message Passing Interface (MPI) [39] library.

- $\Box$  tasksim [40]: used in a simulated architecture.

The following sections give an overview of the most important independent mechanisms of the library that serve as glue between the different architectures.

#### 2.1.4.1 Nanos++ Independent Layer

When a piece of code annotated as a **task** is reached, the runtime creates a new task. The data environment of the task is captured from the function arguments or scope variables and is used to dynamically build a task data-dependency graph to ensure program's correctness. When the task data dependencies are satisfied (usually by the completion of its predecessor tasks), the task becomes ready and can be run.

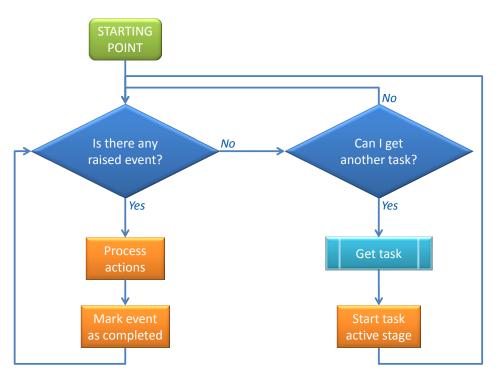

The task life can be divided into five stages (from its creation to its completion), described in chronological order:

- □ Instantiation: OmpSs creates the task and all its related data structures. The dependency support computes task data dependencies and adds a new node to the task graph representing this task. The appropriate connections between the task and its predecessors are created.

- □ **Ready**: task's data dependencies are satisfied, typically as a result of the completion of the predecessor tasks. Task scheduling usually occurs in this stage<sup>1</sup>.

- □ Active: this stage includes all the operations needed once the task has been scheduled to a system's processing unit and before the task can be run. The coherence layer is invoked in this stage to ensure that all necessary data is available in the appropriate memory space. Then, if needed, data allocations and input data transfers are issued.

- **Run**: the task is executed. The corresponding architecture dependent layer is the responsible for this action and will notify the system when the execution is finished.

<sup>&</sup>lt;sup>1</sup> Most schedulers decide the unit where the task will be run at this stage, but, for example, the localityaware scheduler (explained later in this chapter) computes the affinity score and makes this decision in the instantiation stage for performance reasons.

□ Completion: all the operations needed once the task has been run occur in this stage. The coherence layer is invoked again to process task's output data. Depending on the configuration of this layer, data transfers and data deallocations may occur or not. The dependency support updates the task graph by removing the corresponding task node and its connections. Then, task successors that have no other dependence will become ready.

# 2.1.4.2 Nanos++ Dependency Support

The runtime maintains a directed acyclic graph where tasks are connected following the dependencies extracted from the directionality clauses specified by the user. Edges between nodes are created for different kinds of dependencies: *read-after-write*, *write-after-read*, *write-after-write*.

The OmpSs model does not allow data dependencies outside the dynamic extent of a given task. This means that only sibling tasks will be connected together. This is particularly important as it allows a hierarchical implementation of the graph for applications with multiple levels of task parallelism.

The dependency support is implemented as a runtime plug-in, so, different behaviors can be implemented and chosen at run time.

### 2.1.4.3 Nanos++ Task Scheduler

Nanos++ allows changing the scheduler used for each execution and, thus, experimenting with different scheduling strategies. The runtime offers several scheduling policies, explained below. The ones included in this thesis contributions are explained in Chapter 5:

- □ Breadth-first: It follows a simple first in, first out (FIFO) scheduling strategy, but before picking the first task from the ready task queue, it tries to schedule a successor of the task that just finished. The idea behind this is that the successor task will share data and it will likely minimize the number of data transfers between disjoint memory spaces.

- □ Locality-aware: In this strategy, when a new task is submitted, the scheduler computes an affinity score for each system memory space. This score is based on where each piece of data specified by the task clauses is located and also takes into account the size of that data. Then, the score is used to place the task in any of the computing units with direct access to the memory space with the highest affinity. Unlike the other schedulers, affinity-aware makes the decision in the task instantiation stage for performance reasons.

- □ NUMA-aware: The aim of this strategy is to minimize memory latency in NUMA systems. It takes into account the physical location of data and assigns tasks to those processing units that are physically attached to the memory bank where task data resides. Task stealing is allowed as well to reduce load imbalance between processing units.

Figure 2.1: Nanos++ runtime components and execution flow

Many schedulers support task priorities<sup>2</sup> to establish a task execution order while preserving data dependencies: tasks with higher priority will be executed earlier.

# 2.1.4.4 Nanos++ Coherence Support

During the task active stage, just before the task is executed, the coherence support is invoked to ensure that an up-to-date copy of the data is available in the address space where the task is going to run.