# ON THE PROGRAMMABILITY OF MULTI-GPU COMPUTING SYSTEMS

### by Javier Cabezas Rodríguez

Advisor: Prof. Nacho Navarro Co—advisor: Prof. Wen—mei Hwu

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Architecture

> Universitat Politècnica de Catalunya 2015

> > Barcelona, Spain

## Abstract

Multi-GPU systems are widely used in High Performance Computing environments to accelerate scientific computations. This trend is expected to continue as integrated GPUs will be introduced to processors used in multi-socket servers and servers will pack a higher number of GPUs per node. GPUs are currently connected to the system through the PCI Express interconnect, which provides limited bandwidth (compared to the bandwidth of the memory in GPUs) and it often becomes a bottleneck for performance scalability. Fortunately, the utilization of integrated GPUs that share the physical memory with CPUs, or higher-bandwidth interconnects such as NVLink, will help to address this problem.

Current programming models present GPUs as isolated devices with their own memory, even if they share the host memory with the CPU. Programmers need to copy the required data to the GPU memory before it is used in a GPU computation, and copy the generated results to host memory before they are accessed by the CPU code. Moreover, complex data transfer schemes (e.g., prefetching or speculative updates) are required to efficiently exploit GPUs, but they are difficult to maintain, especially across different system topologies. This problem is aggravated when using multiple GPUs. Multi-GPU systems are programmed like distributed systems in which each GPU is a node with its own memory. Programmers explicitly manage allocations in all GPU memories and use primitives to communicate data between GPUs. Furthermore, programmers are required to use mechanisms such as command queues and inter-GPU synchronization. This explicit model harms the maintainability of the code and introduces new sources for potential errors.

The first proposal of this thesis is the HPE model. HPE enables multi-GPU applications to efficiently exchange data while preserving developer productivity and application maintainability. HPE builds a simple, consistent programming interface based on three major features. (1) All device address spaces are combined with the host address space to form a Unified Virtual Address Space, or UVAS. (2) Programs are provided with an Asym-

metric Distributed Shared Memory (ADSM) system for all the GPUs in the system. It allows applications to allocate memory objects that can be accessed by any GPU or CPU. HPE exploits the UVAS to easily keep track of the location and the state of the copies for each object. (3) Every CPU thread can request a data exchange between any two GPUs, through simple memory copy calls. Such a simple interface allows HPE to automatically optimize data exchanges between devices; eliminating the need for application code to handle different system topologies.

Experimental results show that the HPE model eases programming of multi-accelerator applications while providing performance improvements of  $2\times$  compared to the best data transfer scheme implemented on top of CUDA 3. Improvements on real applications range from 5% in compute-bound benchmarks and up to  $2.6\times$  in communication-bound benchmarks. HPE transparently implements sophisticated communication schemes that can deliver up to a  $2.9\times$  speedup in I/O device transfers.

The second proposal of this thesis is a shared memory programming model that exploits the new GPU capabilities for remote memory accesses to remove the need for explicit communication between GPUs. This model turns a multi-GPU system into a shared memory system with NUMA (i.e., Non-Uniform Memory Access) characteristics. In order to validate the viability of the model we also perform an exhaustive performance analysis of remote memory accesses over PCIe. We show that the unique characteristics of the GPU execution model and memory hierarchy help to hide the costs of remote memory accesses.

Results show that PCI Express 3.0 is able to hide the costs of a 10% of remote memory accesses if the kernels produce high GPU core occupancy and the accesses are spread through the whole kernel execution. We also show that caching of remote memory accesses can have a large performance impact on kernel performance.

Finally, we introduce AMGE, a programming interface, compiler support and runtime system that automatically executes computations that are programmed for a single GPU across all the GPUs in the system. The programming interface provides a data type for multidimensional arrays that allows for robust, transparent distribution of arrays across all GPU memories. The compiler extracts the dimensionality information from the type of each array, and is able to determine the access pattern in each dimension of the array. The runtime system uses the compiler-provided information to automatically choose the best computation and data distribution configuration to minimize inter-GPU communication and memory footprint. This model effectively frees programmers from the task of decomposing and distributing computation and data to exploit several GPUs.

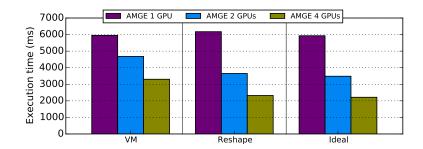

AMGE achieves almost linear speedups for a wide range of dense computation benchmarks on a real 4-GPU system with an interconnect with moderate bandwidth. We show that irregular computations can also benefit from AMGE, too, if kernels do not suffer from computation distribution imbalance across thread blocks. We believe that AMGE can be used in shared memory multi-GPU systems to automatically scale the performance of GPU kernels to multiple GPUs.

Thanks to the results obtained in the experiments of this thesis we demonstrate that careful programming interface design and efficient implementation of our proposals enable applications with not only simpler and more maintainable codebases, but also a performance scalability similar to hand-tuned low-level implementations especially designed for multi-GPU systems.

# Contents

| 1 | Intr                 | roduction                                                | 1  |

|---|----------------------|----------------------------------------------------------|----|

|   | 1.1                  | Objectives and contributions                             | 3  |

|   |                      | 1.1.1 Multi-GPU Reverse Time Migration                   | 3  |

|   |                      | 1.1.2 Data sharing between the CPU and multiple GPUs     | 4  |

|   |                      | 1.1.3 Shared memory programming for multiple GPUs        | 5  |

|   |                      | 1.1.4 Transparent parallelization of GPU programs to run |    |

|   |                      | on multiple GPUs                                         | 6  |

|   | 1.2                  | Organization                                             | 7  |

| 2 | $\operatorname{Ref}$ | erence Hardware and Software Environment                 | 9  |

|   | 2.1                  | Graphics Processing Units                                | 9  |

|   |                      | 2.1.1 Memory technologies                                | 11 |

|   | 2.2                  | Multi-GPU systems                                        | 12 |

|   |                      | 2.2.1 Interconnect                                       | 13 |

|   |                      | 2.2.2 GPU NUMA systems                                   | 14 |

|   | 2.3                  | Programming models for GPU-based systems                 | 15 |

|   |                      | 2.3.1 C for CUDA                                         | 15 |

|   |                      | 2.3.2 OpenCL                                             | 17 |

| 3 | Sta                  | te of the Art                                            | 19 |

|   | 3.1                  | Automatic CPU/GPU memory coherence                       | 19 |

|   | 3.2                  | System support and GPU virtualization                    | 20 |

|   | 3.3                  | Automatic multi-GPU execution                            | 22 |

|   |                      | 3.3.1 Compiler-based transparent multi-GPU execution     | 22 |

|   |                      | 3.3.2 Compiler-based multi-GPU code generation           | 23 |

|   |                      | 3.3.3 Multi-GPU libraries                                | 24 |

|   | 3.4                  | Languages for multi-GPU execution                        | 25 |

| 4 | Gui                  | ding Example: Reverse Time Migration                     | 29 |

|   | 4.1                  | The Reverse Time Migration computation                   | 29 |

|   |                      | 4.1.1 Seismic imaging                                    | 30 |

|   | 4.2      | RTM base implementation                                  |

|---|----------|----------------------------------------------------------|

|   |          | 4.2.1 Memory                                             |

|   |          | 4.2.2 Input/Output                                       |

|   |          | 4.2.3 Computation                                        |

|   | 4.3      | Porting RTM to GPUs                                      |

|   |          | 4.3.1 Data I/O schemes                                   |

|   |          | 4.3.2 GPU kernels                                        |

|   | 4.4      | RTM implementation on other architectures                |

|   |          | 4.4.1 General purpose CPUs                               |

|   |          | 4.4.2 Cell B.E                                           |

|   |          | 4.4.3 FPGA                                               |

|   | 4.5      | Performance evaluation                                   |

|   | 4.6      | Summary                                                  |

| 5 | Het      | erogeneous Multi-GPU Execution 45                        |

|   | 5.1      | Programmability issues under CUDA                        |

|   |          | 5.1.1 RTM on multiple GPUs 40                            |

|   |          | 5.1.2 Performance considerations                         |

|   | 5.2      | The Heterogeneous Parallel Execution model               |

|   |          | 5.2.1 Multi-threaded GPU sharing                         |

|   |          | 5.2.2 UVAS and remote memory access 54                   |

|   |          | 5.2.3 Multi-threaded ADSM                                |

|   | 5.3      | Performance evaluation of the HPE model 60               |

|   |          | 5.3.1 Experimental methodology                           |

|   |          | 5.3.2 Benchmarks                                         |

|   |          | 5.3.3 Inter-GPU data transfers                           |

|   |          | 5.3.4 Application benchmarks                             |

|   |          | 5.3.5 Communication with I/O devices 67                  |

|   |          | 5.3.6 Inter-node communication (MPI) 67                  |

|   | 5.4      | Summary                                                  |

|   | 5.5      |                                                          |

| 6 | Sha      | red Memory GPU Programming 71                            |

| • | 6.1      | Multi-GPU NUMA systems                                   |

|   | 6.2      | Experimental methodology                                 |

|   | <b>.</b> | 6.2.1 Hardware setup                                     |

|   |          | 6.2.2 Microbenchmarks                                    |

|   |          | 6.2.3 Multi-GPU applications                             |

|   | 6.3      | Performance analysis of the remote access mechanism      |

|   | 6.4      | GPU-SM: towards shared memory multi-GPU programming . 83 |

|   | J.1      | 6 4 1 Distributed memory vs shared memory 84             |

|   |     | 6.4.2 Writing code for GPU-SM                          | 84  |

|---|-----|--------------------------------------------------------|-----|

|   |     | 6.4.3 Current limitations                              | 87  |

|   | 6.5 | Implementation and performance evaluation of GPU-SM ap | )-  |

|   |     | plications                                             |     |

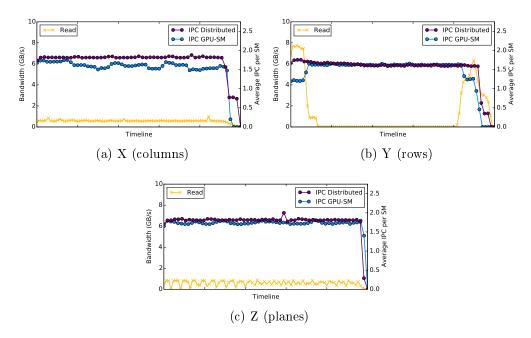

|   |     | 6.5.1 FDTD                                             | 88  |

|   |     | 6.5.2 Image filtering                                  | 91  |

|   | 6.6 | Summary                                                |     |

| 7 | Aut | omatic Multi-GPU Execution                             | 99  |

|   | 7.1 | AMGE overview                                          | 99  |

|   |     | 7.1.1 An example: matrix multiplication                | 101 |

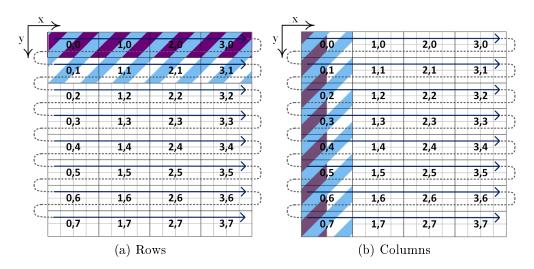

|   | 7.2 | Computation and data distribution                      |     |

|   |     | 7.2.1 Compiler analysis                                | 103 |

|   |     | 7.2.2 Run-time distribution                            | 106 |

|   | 7.3 | AMGE implementation details                            | 108 |

|   |     | 7.3.1 Array data type                                  | 108 |

|   |     | 7.3.2 Source-to-source transformations                 | 110 |

|   |     | 7.3.3 Run-time distribution selection policy           | 111 |

|   | 7.4 | Experimental methodology                               | 113 |

|   | 7.5 | Performance evaluation                                 | 115 |

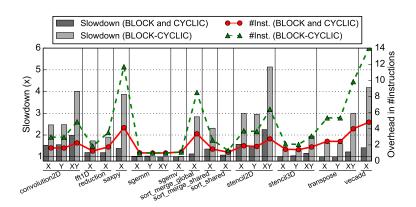

|   |     | 7.5.1 Indexing overhead                                | 115 |

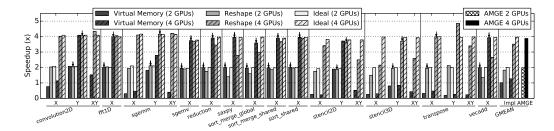

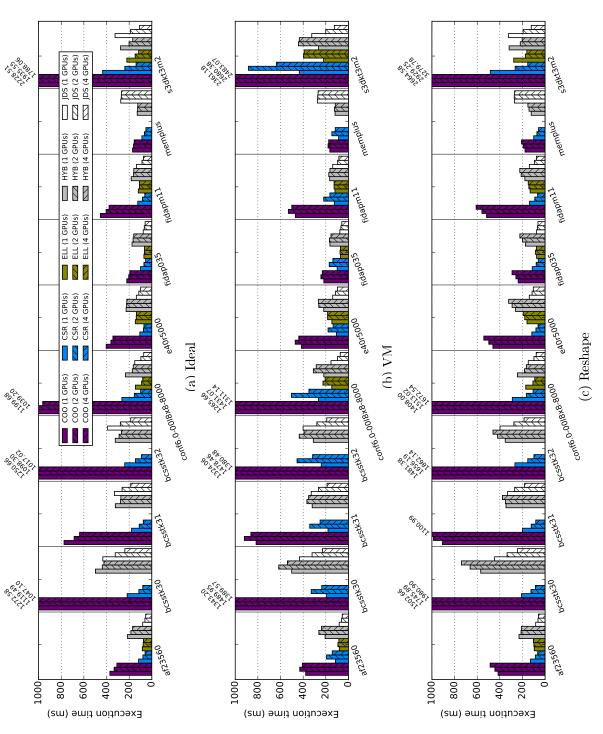

|   |     | 7.5.2 Multi-GPU performance                            | 118 |

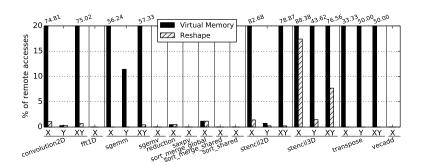

|   |     | 7.5.3 Impact of remote accesses on performance         | 119 |

|   |     | 7.5.4 Comparison with previous works                   | 123 |

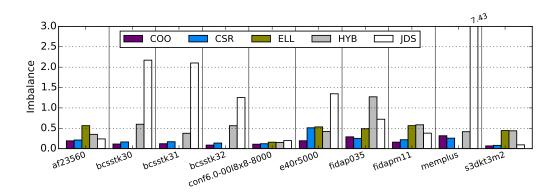

|   |     | 7.5.5 Sparse benchmarks                                | 124 |

|   | 7.6 | Summary                                                | 127 |

| 3 | Con | clusions and Future Work                               | 129 |

|   | 8.1 | Conclusions                                            |     |

|   |     | 8.1.1 Impact                                           | 130 |

|   | 8.2 | Future work                                            |     |

|   |     | 8.2.1 Full system memory coherence                     |     |

|   |     | 8.2.2 Hiding the costs of remote accesses              |     |

|   |     | 8.2.3 Memory placement                                 |     |

|   |     | 8.2.4 Extensions to other environments                 | 133 |

| A | Pub | lications                                              | 135 |

|   | A.1 | Conference papers                                      | 135 |

|   | A.2 | Journal papers                                         | 135 |

|   | A.3 | Workshops                                              | 136 |

|   | Λ 1 | Side publications                                      | 126 |

# List of Figures

| 2.1 | Multi-GPU system architectures                                                                   | 10 |

|-----|--------------------------------------------------------------------------------------------------|----|

| 2.2 | Microarchitecture of AMD and NVIDIA GPU cores                                                    | 10 |

| 2.3 | Multi-GPU NUMA system targeted in this thesis                                                    | 12 |

| 2.4 | PCIe transfer rates for different data sizes                                                     | 14 |

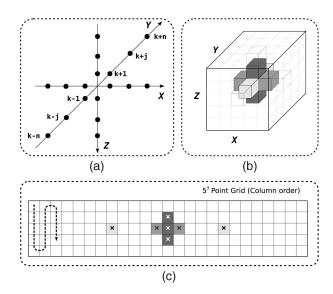

| 4.1 | Computation and memory access patterns of RTM                                                    | 32 |

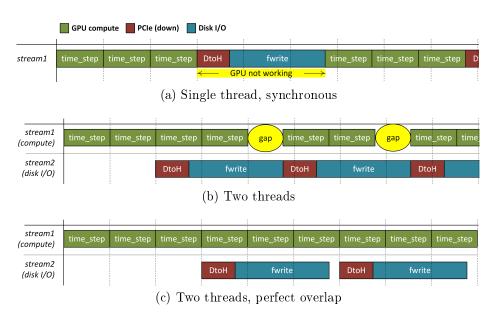

| 4.2 | Execution timelines of the GPU implementation of RTM for different data I/O schemes              | 35 |

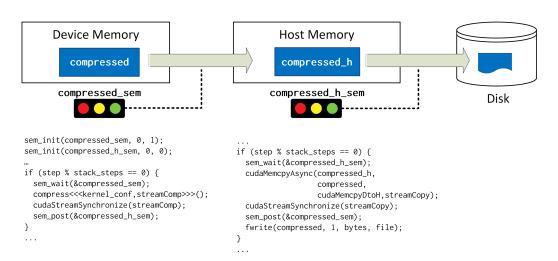

| 4.3 | Synchronization scheme used to overlap I/O and communica-                                        |    |

|     | tion in the GPU implementation of RTM                                                            | 36 |

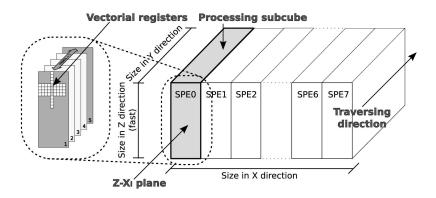

| 4.4 | Data access and vectorization pattern for the Cell B.E                                           | 41 |

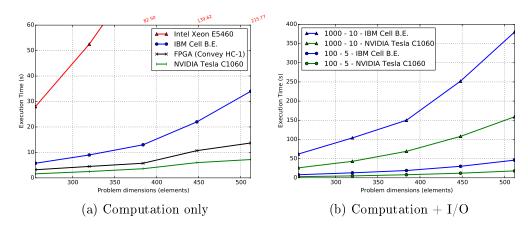

| 4.5 | Elapsed times for different platform implementations of RTM.                                     | 42 |

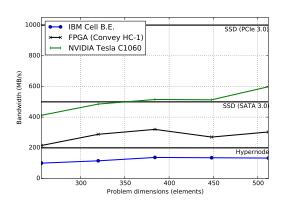

| 4.6 | I/O requirements of RTM using a stack rate 5, and high level                                     |    |

|     | of compression                                                                                   | 43 |

| 5.1 | Execution timeline for the multi-GPU implementation of RTM.                                      | 47 |

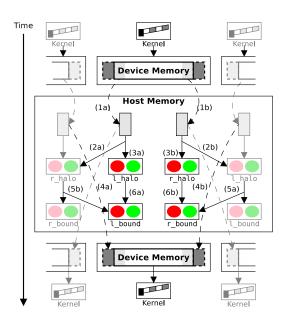

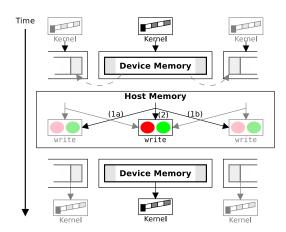

| 5.2 | Exchange steps and synchronization in the RTM computation using the CUDA 3 programming interface | 49 |

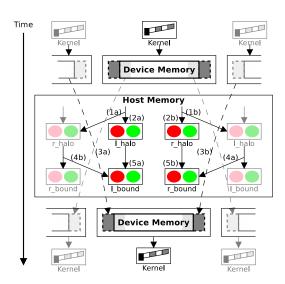

| 5.3 | Exchange steps and synchronization in the RTM computation                                        |    |

|     | when GPUs are shared across CPU threads                                                          | 51 |

| 5.4 | Exchange steps and synchronization in the RTM computation                                        |    |

|     | when UVAS is available                                                                           | 54 |

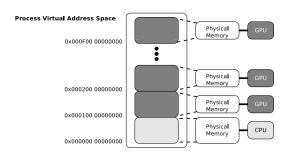

| 5.5 | Software-based Unified Virtual Address Space implementation                                      |    |

|     | using segmentation                                                                               | 57 |

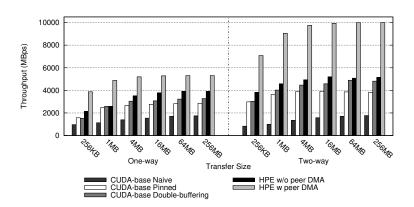

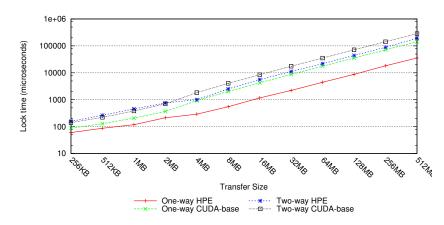

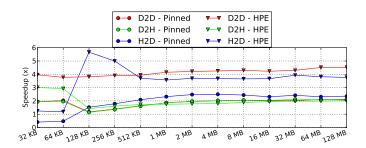

| 5.6 | Measured throughput for different data communication sizes                                       | 62 |

| 5.7 | CPU thread wait time for different inter-GPU data communi-                                       |    |

|     | cation sizes                                                                                     | 62 |

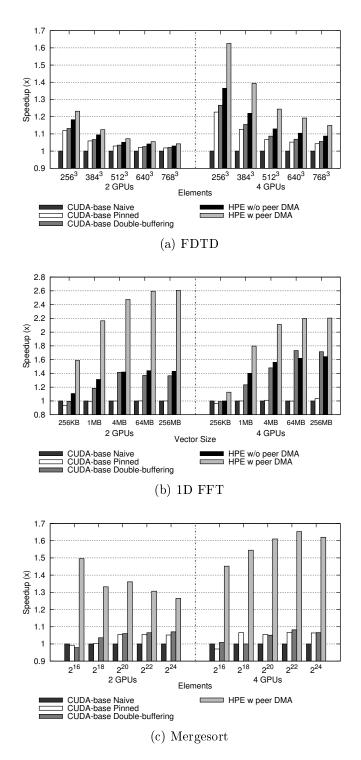

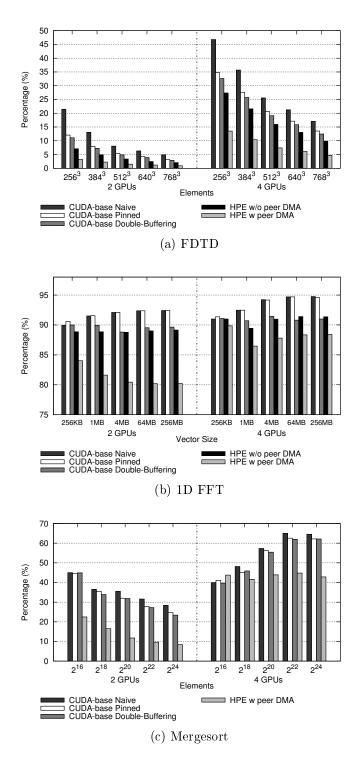

| 5.8 | Speedup over single GPU execution different input dataset sizes.                                 | 64 |

| 5.9 | Percentage of time devoted to memory transfers over the total                                    |    |

|     | execution time.                                                                                  | 66 |

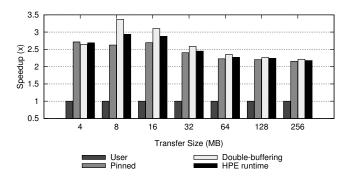

| 5.10       | Disk↔GPU transfer speedups of HPE compared to the base synchronous version                                         | 67       |

|------------|--------------------------------------------------------------------------------------------------------------------|----------|

| 5.11       | MPI transfer speedups of HPE compared to the base synchronous version                                              | 68       |

| 6.1        | Multi-GPU systems used to evaluate GPU-SM                                                                          | 73       |

| 6.2        | Data dependences in a 4-point 3D stencil computation                                                               | 75       |

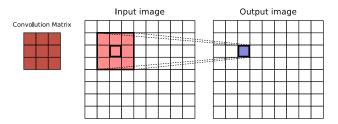

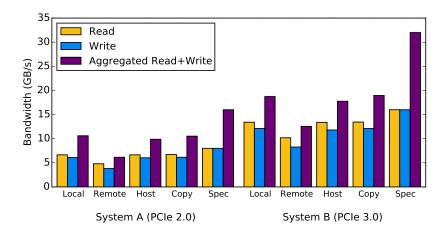

| 6.3<br>6.4 | Data needed to compute an output pixel in a convolution Memory bandwidth achieved by remote accesses for different | 76       |

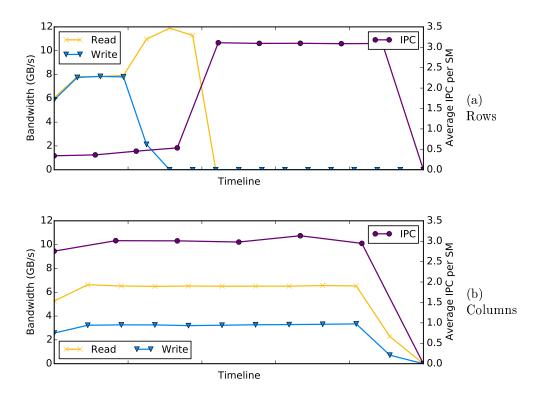

| 6.5        | PCIe generations                                                                                                   | 77       |

| 6.6        | grid                                                                                                               | 78       |

|            | remotely                                                                                                           | 79       |

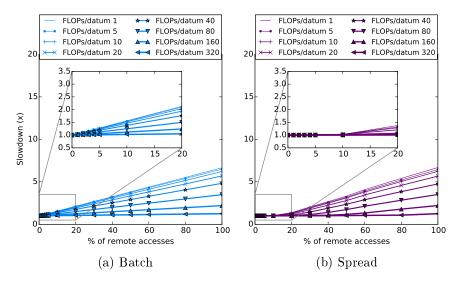

| 6.7        | Performance overhead imposed by remote accesses for different computation intensities                              | 80       |

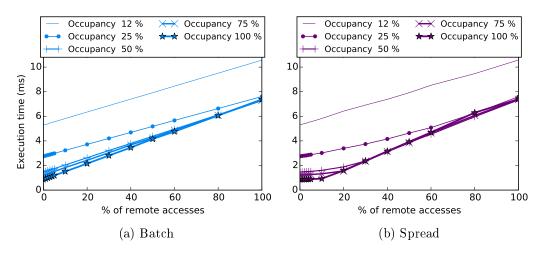

| 6.8        | Execution time for different remote accesses and SM occupancies.                                                   | 81       |

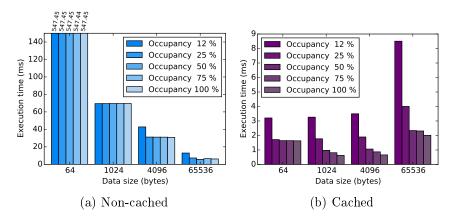

| 6.9        | Execution time for different sizes of the remotely accessed                                                        | <u> </u> |

|            | read-only data structure and different occupancies                                                                 | 82       |

| 6.10       | Distributed and shared memory multi-GPU system models                                                              | 83       |

|            | Inter-domain data dependences for FDTD                                                                             | 88       |

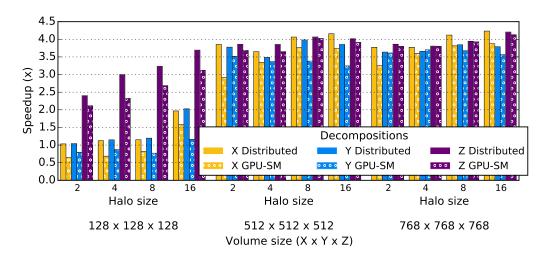

|            | FDTD: speedups of the multi-GPU implementations for 4 GPUs compared to the original implementation on a single     |          |

|            | GPU                                                                                                                | 90       |

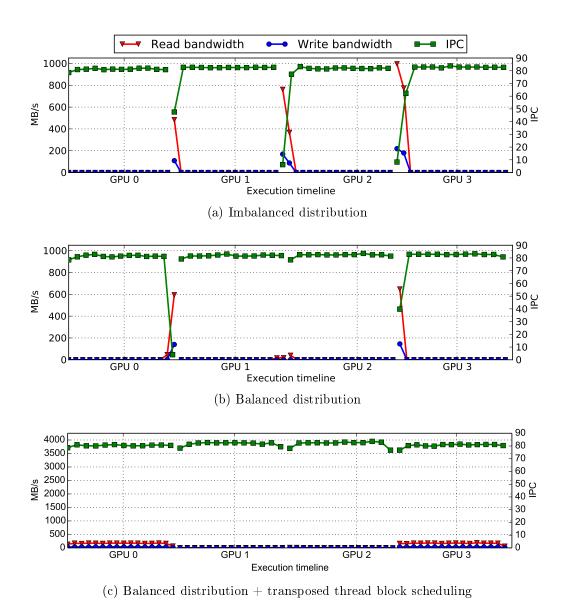

| 6.13       | FDTD: execution timeline for different decompostion configurations                                                 | 91       |

| 6.14       | Image filtering: speedups of the multi-GPU GPU-SM implementation for 4 GPUs compared to the original implementa-   |          |

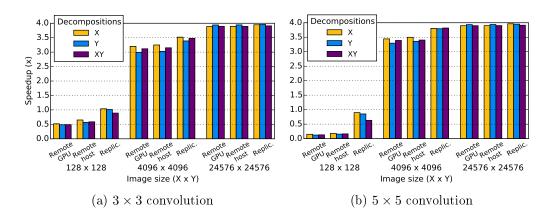

|            | tion on a single GPU                                                                                               | 92       |

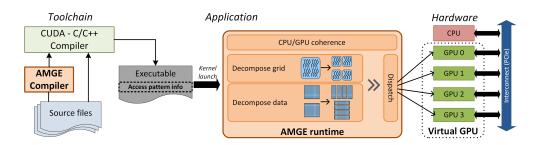

| 7.1        | Overview of AMGE components                                                                                        | 100      |

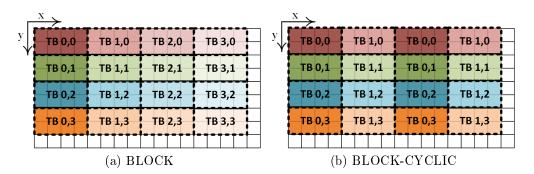

| 7.2        | Computation-to-data mapping examples                                                                               | 104      |

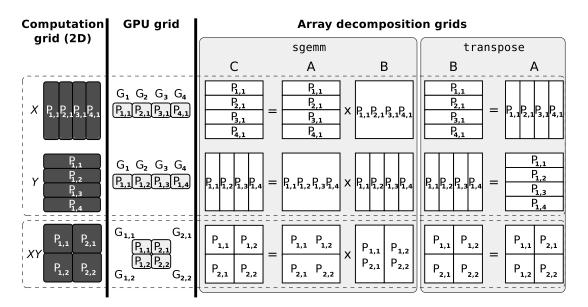

| 7.3        | Data and computation distribution configurations for sgemm                                                         |          |

|            | and transpose on a 4-GPU system                                                                                    | 107      |

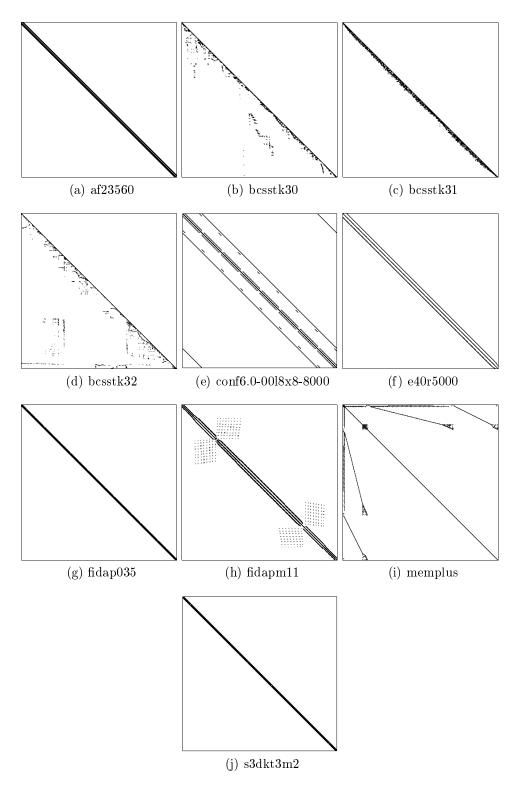

| 7.4        | Sparse matrices used in the SpMV benchmarks                                                                        | 116      |

| 7.5        | Overhead imposed by indexing routines of the proposed multi-<br>dimensional array type                             | 117      |

| 7.6        | Speedup over baseline for different computation decomposition                                                      |          |

|            | configurations using reshape and VM implementations                                                                | 118      |

| 7.7  | Memory requests served by remote GPUs                         |

|------|---------------------------------------------------------------|

| 7.8  | Execution timeline of stencil2D for 4 GPUs                    |

| 7.9  | Overhead of the coherence mechanisms in AMGE and in the       |

|      | related work [57]                                             |

| 7.10 | Execution time of different implementations of the sparse ma- |

|      | trix vector computation on AMGE for 1, 2 and 4 GPUs 125       |

| 7.11 | Computation imbalance in the SpMV benchmark (4 GPUs) 126      |

| 7.12 | Performance scalability in the BFS benchmark                  |

# List of Tables

| 2.1 | Memory and interconnection network characteristics                                    | 14  |

|-----|---------------------------------------------------------------------------------------|-----|

| 4.1 | Hardware configuration used for the evaluation of the GPU implementation of RTM       | 37  |

| 4.2 | Hardware configuration used for the evaluation of the CPU implementation of RTM       | 39  |

| 4.3 | Hardware configuration used for the evaluation of the Cell B.E. implementation of RTM | 40  |

| 4.4 | Hardware configuration used for the evaluation of the FPGA implementation of RTM      | 41  |

| 6.1 | Analyzed configurations for the GPU-SM implementation of FDTD                         | 75  |

| 6.2 | Analyzed configurations for the GPU-SM implementation of image filtering              | 76  |

| 7.1 | Dense benchmarks used for the evaluation of AMGE                                      | 112 |

| 7.2 | Sparse benchmarks used for the evaluation of AMGE                                     | 114 |

| 7.3 | Maximum problem size for a 4-GPU system in AMGE and in the related work               | 199 |

|     |                                                                                       | 144 |

# Listings

| 4.1 | Pseudocode of the RTM algorithm                             | 31  |

|-----|-------------------------------------------------------------|-----|

| 5.1 | Simplified host code of the RTM computation using the CUDA  |     |

|     | 3 programming interface                                     | 48  |

| 5.2 | Simplified host code of the RTM computation when GPUs are   |     |

|     | shared across CPU threads                                   | 53  |

| 5.3 | Simplified host code of the RTM computation when UVAS is    |     |

|     | available                                                   | 55  |

| 5.4 | Simplified host code of the RTM computation when ADSM is    |     |

|     | available                                                   | 58  |

| 6.1 | FDTD: distributed implementation (simplified version of the |     |

|     | kernel)                                                     | 93  |

| 6.2 | FDTD: distributed implementation (host)                     | 94  |

| 6.3 | FDTD: GPU-SM implementation (simplified version of the      |     |

|     | $\mathrm{kernel}). \ . \ . \ . \ . \ . \ . \ . \ . \ . \$   | 95  |

| 6.4 | FDTD: GPU-SM implementation (host)                          | 96  |

| 7.1 | Multi-GPU sgemm GPU code with AMGE                          | 101 |

| 7.2 | Multi-GPU sgemm host code with AMGE                         | 102 |

## Chapter 1

# Introduction

In the last years, massively-parallel accelerators have experienced widespread adoption in different environments due to their outstanding performance in many types of computations. Companies and research centers that rely on High Performance Computing (HPC) to solve complex scientific simulations were the first to embrace the utilization of such processors. Further improvements in the manufacturing technologies of chips have also made possible the integration of accelerators and general purpose processors in a single (heterogeneous) chip; and they can now be found in mobile devices, desktops, and servers. Thus, this types of accelerators are becoming ubiquitous and this trend is expected to continue in the next years.

The most common type of massively-parallel accelerator is the Graphics Processing Unit (i.e., GPU). GPUs have traditionally excelled at executing fixed-function primitives that process in parallel data such as vertices, edges and pixels. With the introduction of user-defined shaders (user-defined computations on the geometry or color of 3D objects), GPUs were extended to be programmable processors. At the beginning, this capabilities were only accessible through extensions of the most popular graphics' application program interfaces (e.g., OpenGL and DirectX). Many scientists saw the potential of GPUs to be used for general purpose computing, and started to develop programming frameworks such as Lib Sh [67], BrookGPU [31], and Accelerator [90]. Since then, GPU vendors have created new programming languages and frameworks such as NVIDIA®CUDA<sup>TM</sup> [74] or OpenCL<sup>TM</sup> [56] to enable true general purpose computing on GPUs.

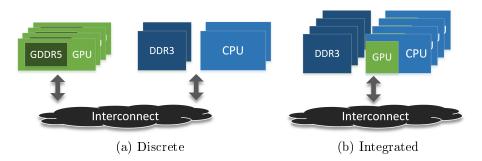

The preferred form factor in HPC environments is discrete GPUs because they provide their own specialized memories (e.g., GDDR5) that deliver much higher bandwidth than host memory. Examples of discrete GPUs are NVIDIA Tesla and AMD FirePro. Discrete GPUs are connected to the

system through standard I/O interconnects like PCI Express. Many manufacturers also couple a general purpose processor and an *integrated* GPU in the same die. This type of chip is common in desktop and mobile systems. Examples of integrated CPU/GPU processors include Intel Haswell, AMD Kaveri, and NVIDIA K1. In these systems, CPUs and GPUs share the host memory. This has two effects: (1) Integrated GPUs have lower performance than their discrete counterparts (due to the lower memory bandwidth). (2) On the other hand, they benefit from faster CPU $\leftrightarrow$ GPU communication since they do not rely on I/O interconnects.

Oftentimes, problems are too computationally demanding or the required data is too big to be run on a single GPU. In such cases, the problem is decomposed into smaller subproblems (e.g., using domain decomposition) that are executed on several GPUs in parallel. Many HPC systems systems install several discrete GPUs per node<sup>1</sup>. GPUs installed in the same node benefit from lower-latency and higher-bandwidth communication. In order to pack as many GPUs as possible in the same node, some manufacturers have announced products that include several GPUs in the same board (e.g., NVIDIA Pascal). Nevertheless, the increased performance of multiple GPUs comes at the cost of higher programming complexity.

Current programming models present GPUs as isolated devices with their own memory. This is the case even if they share the host memory with the GPU, because most chips with integrated GPUs do not implement hardware memory coherence between the CPU and the GPU cores. However, exposing separate memories hurts programmability. Programmers need to copy the required data to the GPU memory before it is used in a GPU computation, and copy the generated results to host memory before they are accessed by the CPU code. Moreover, simple data transfer schemes are likely to incur into performance penalties. On the other hand, elaborated schemes (e.g., prefetching or speculative updates) require complex implementations that are difficult to maintain, especially across different system topologies.

This problem is aggravated when using multiple GPUs. Multi-GPU systems are programmed like distributed systems in which each GPU is a node with its own memory. Programmers need to manage allocations in all GPU memories and explicitly use primitives to communicate data between GPUs, which can be difficult in computations with complex data dependencies between GPUs. Furthermore, in order to manage several GPUs efficiently, programmers are required to use mechanisms such as command queues and inter-GPU synchronization. This, again, further harms the maintainability

<sup>&</sup>lt;sup>1</sup>No integrated multi-GPU systems have been released so far, but they are expected to appear in the next years.

of the code and introduces new sources for potential errors.

### 1.1 Objectives and contributions

The main objective of this thesis is to facilitate the utilization of GPUs so that they can be adopted by a broader community. More specifically, improvements to the current programming models for GPUs are proposed in order to simplify the management of multiple GPUs and the data transfers between the host and GPU memories. Some of these changes require support from the Operating System or the GPU architecture, too.

### 1.1.1 Multi-GPU Reverse Time Migration

In order to accomplish our goals, we first analyze the GPU programmability issues in real applications. The RTM (i.e., Reverse Time Migration) application is used as a guiding example in this thesis. It is a key application in the oil and gas industry with much higher computing power requirements than previous algorithms, that can only be fulfilled thanks to multi-GPU execution.

We present an optimized implementation of the RTM that is specifically designed to exploit the architectural characteristics of the GPUs. The work is divided in two parts:

- 1. An optimized implementation of the different computational kernels on the GPU.

- 2. A multi-GPU multi-node execution framework for RTM. This work was done using CUDA 3, which imposes several restrictions on how CPU threads can access the GPUs in the system (e.g., each CPU thread can access 1 GPU only).

This implementation is measured against three reference HPC platforms: one that employs traditional cache-coherent cores, another one that uses Cell B.E. accelerators [53], and a Convey HC-1 FPGA system. Results show that GPUs outperform any other accelerator. However, PCIe and disk I/O needs to be carefully performed to overlap them with computation to hide the costs. Limitations in the GPU programming model makes this a difficult task, and we identify several programmability issues that we try to address in the thesis.

### 1.1.2 Data sharing between the CPU and multiple GPUs

To effectively utilize a multi-GPU computing system, application developers need to distribute large data sets across GPU memories. Within a heterogeneous computing cluster, application-level data exchange between GPUs involves interactions between node-level APIs such as CUDA or OpenCL, and inter-node APIs such as MPI. While MPI hides the complexity of the system interconnect topology and inter-node routing, there is currently no similar node-level interface. Therefore, developers are left with the challenging task of code versioning needed to effectively use a wide variety of hardware and drivers with very different capabilities.

Moreover, CPU and GPU have separate memory spaces and developers are in charge of managing separate copies on host and GPU memories for each data structure, and keeping them coherent through explicit memory transfers. Some solutions propose a single virtual memory space that is shared between CPU and GPU [45, 52]. In these solutions, each object is allocated once although memory is allocated both in host and GPU memory; and a runtime system transparently keeps the different copies of the object coherent. However, they target systems with a single GPU.

We propose the Heterogeneous Parallel Execution (HPE) programming interface and its runtime system. HPE enables multi-GPU applications to efficiently exchange data while preserving developer productivity and application maintainability. HPE is available to CUDA and OpenCL developers as a user-level library. It allows applications to allocate memory objects that can be accessed by any GPU or CPU in the system. The HPE runtime transparently handles data copies.

Both CUDA and OpenCL allow applications to interact with all devices in the system. However, the physical bus topology of the system dictates the level of interaction and data exchanges allowed between GPUs. As a result, programmers write application code to discover the physical system topology and implement different code paths for each type of system configuration. This represents a significant effort resulting in large, hard-to-maintain application code base.

HPE builds a simple, consistent programming interface based on three major features.

- 1. All GPU address spaces are combined with the host address space to form a Unified Virtual Address Space, or UVAS. Starting with the Fermi generation, all NVIDIA GPUs support UVAS based on virtual memory.

- 2. Programs are provided with an Asymmetric Distributed Shared Mem-

ory (ADSM) system [45] for all the GPUs in the system. HPE exploits the UVAS to easily keep track of the location and the state of the copies for each object. The simple relation between a GPU address and its corresponding host address allows a lock-free implementation of the HPE runtime.

3. Every CPU thread can request a data exchange between any two GPUs, through simple memory copy calls. The HPE runtime manages thread-to-GPU connection and performs intermediate data copies when necessary to realize this abstraction. Such a simple interface allows HPE to automatically optimize data exchanges between GPUs; eliminating the need for application code to handle different system topologies.

We have been working with NVIDIA to include many of the features of HPE in the latest versions of CUDA.

### 1.1.3 Shared memory programming for multiple GPUs

The common approach to multi-GPU programming is to use each GPU as an isolated device with its own memory. This imposes the utilization of explicit memory transfers between GPU memories every time a GPU needs data that is located on the memory of a different GPU. Further, these memory transfers must be overlapped with computation to minimize their overhead, thus increasing the complexity of the code. While HPE takes care of some of these optimizations, we would like to remove all explicit data transfers.

Modern NVIDIA GPUs provide the capability of accessing the memories of all the GPUs connected to the same PCI Express root complex [5]. They also present a single Unified Virtual Address Space (i.e., UVAS) that includes all the GPU memories in the system and the host memory. Thanks to these features, CUDA kernels can access any memory in the system through regular load/store instructions. While these features have been available for some time they have gone unnoticed among application developers, and their utilization has been mainly restricted to accelerate bulk data transfers between GPU memories and to enable better integration with I/O devices.

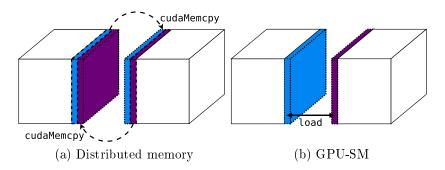

In this dissertation, we propose GPU-SM, a shared memory programming model that exploits the new GPU capabilities to remove the need for explicit communication between GPUs. The memory of multiple GPUs is aggregated to form a shared memory system with NUMA (i.e., Non-Uniform Memory Access) characteristics. In this type of systems computation can be freely decomposed and distributed across all the GPUs in the system, because any GPU can access all the memory in the system, although with a lower bandwidth and higher latency.

We also perform an exhaustive performance analysis of remote memory accesses over PCIe and their viability as a mechanism to implement the shared memory model in multi-GPU systems. Different PCIe revisions (i.e., 2.0 and 3.0) and topologies are studied. We show that the highly-multi-threaded GPU execution model helps to hide the costs of remote memory accesses. Other features introduced in the latest GPU families such as read-only caches can minimize the amount of accesses to remote GPUs. The importance of the thread block scheduling and its relation with data decomposition is also discussed, as they determine how remote memory accesses are distributed along kernel execution.

# 1.1.4 Transparent parallelization of GPU programs to run on multiple GPUs

While using a shared memory model improves programmability of multi-GPU systems, programmers are still in charge of decomposing the problem and distributing it across several GPUs. Moreover, memory placement needs to be performed in such a way that remote memory accesses are minimized, in order to avoid the impact on the performance. This has shown to be a challenging task in the past in other type of systems [30, 66, 65, 38] and usually rely on hardware mechanisms not available in current GPUs such as paging.

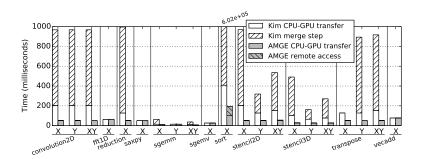

In this dissertation, we propose exposing to programmers a single virtual GPU that aggregates the resources of all GPUs in the system. Similar solutions have been proposed [57, 61], but their design imposes fundamental limitations. (1) Memory footprint overhead: these solutions replicate portions of the arrays that are never accessed. This is because they do not take into account the dimensionality of the arrays. For example, consider a kernel that performs n-dimensional tiling (a common pattern in dense GPU computations [83, 92, 21]) where each computation partition accesses a noncontiguous memory region of a matrix. In such a case, they transfer the whole memory address ranges accessed by each computation partition, which may include large portions of the array that are never used. This limits the size of the problems that can be handled and imposes performance overheads due to larger data transfers. (2) Data coherence overhead: replicated output memory regions need to be merged in the host memory after each kernel call. In many cases, this merge step leads to large performance overheads. (3) Applications that use atomic and global memory instructions, resort to single-GPU execution.

In this thesis, we introduce AMGE (Automatic Multi-GPU Execution), a

programming interface, compiler support and runtime system that automatically executes computations that are programmed for a single GPU across all the GPUs in the system. The programming interface provides a data type for multidimensional arrays that allows for robust, transparent distribution of arrays across all GPU memories. The compiler extracts the dimensionality information from the type of each array, and is able to determine the access pattern in each dimension of the array. The runtime system uses the compiler-provided information to automatically choose the best computation and data distribution configuration to minimize inter-GPU communication and memory footprint.

AMGE assumes non-coherent non-uniform shared memory accesses (NCC-NUMA) between GPUs through a relatively low-bandwidth interconnect, such that all GPUs can access and cache any partition of the arrays. Thus, we ensure that arrays can be arbitrarily decomposed, distributed and safely accessed from any GPU in the system. In current systems based on discrete GPUs, we utilize Peer-to-Peer [5] and Unified Virtual Address Space [74] technologies that enable a GPU to transparently access the memory of any other GPU connected to the same PCIe domain. While remote GPU memory accesses have been used in the past [89], this is the first work to use them as an enabling mechanism for automatic multi-GPU execution.

Results show that AMGE can effectively provide linear speedups for a wide reange of dense computations a 4 GPU system. Moreover, the size of the problems that can be handled is much larger than previous solutions. Furthermore, AMGE can also be beneficial to irregular workloads.

## 1.2 Organization

This dissertation is organized as follows:

**Chapter 1: Introduction** Provides an overview of the programmability problems we are trying to solve and outline the proposed solutions.

Chapter 2: Reference Hardware and Software Environment The chapter explains the unique characteristics of the GPU architecture and the technologies (e.g., PCI Express, GDDR5 memory) in multi-GPU systems, that are used in the proposals. This is followed with a discussion of current programming models for GPUs, their features, and their limitations. Since the RTM algorithm is used as a guiding example, it is introduced here, too.

Chapter 3: State of the Art Several works have been proposed to simplify the programmability of GPU-based systems. These previous works are discussed and their limitations are highlighted. We focus on memory management and automatic multi-GPU execution.

Chapter 4: Guiding Example: Reverse Time Migration Reverse Time Migration (RTM) is used as a guiding example in this thesis to illustrate programmability problems in multi-GPU systems. The RTM computation is composed of a number of computational kernels and has high I/O requirements. We explain the implementation optimizations for GPUs and compare them with previous approaches for different architectures.

Chapter 5: Heterogeneous Multi-GPU Execution Multi-GPU execution is required to handle real-world problem sizes. This chapter introduces a multi-GPU paralelization strategy in CUDA for RTM with support for several nodes through MPI. We identify and analyze the programmability problems that arise and propose the HPE model that eliminates or minimizes them.

Chapter 6: Shared Memory GPU Programming Discusses the hardware requirements and the characteristics to enable shared memory programming in multi-GPU systems. The chapter also includes an analysis of the performance characteristics of PCI Express and the capabilities of current GPUs to hide the costs of remote memory accesses.

Chapter 7: Automatic Multi-GPU Execution This chapter introduces a programming framework that transparently decomposes computation and data and distributes them across all the GPUs in the system.

Chapter 8: Conclusions and Future Work Sumarizes the discoveries made in this thesis and outlines future directions to achieve simpler and more efficient multi-GPU execution.

## Chapter 2

# Reference Hardware and Software Environment

This thesis proposes improvements in the programmability of systems that install several GPUs. This chapter introduces the details of the GPU hardware and programming models which are important to understand the performance trade-offs and the implementability of our proposals. It also presents the terminology used in the rest of the thesis.

### 2.1 Graphics Processing Units

Modern GPUs are presented in two different form factors.

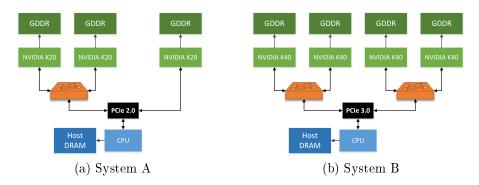

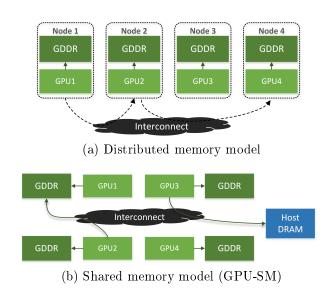

- Discrete GPUs are dedicated boards connected to the rest of the system through expansion slots such as PCI Express (shown in Figure 2.1a). They have their own high-bandwidth memory, which is explicitly managed by the programmers.

- Integrated GPUs are included in the same die as the CPU and both share the host memory (shown in Figure 2.1b). They may also share some levels of the cache memory hierarchy with the CPU cores. For example, the CPU and GPU in the Intel Ivy Bridge [49] chip share the L3 cache. AMD APU [2] provides both coherent (which shares the L2 cache) and non-coherent interconnects for the integrated GPU, which are chosen at programmer's request. On the other hand, the GPU in the NVIDIA K1 [14] chip does not share any level of the cache memory hierarchy with the CPU cores.

Figure 2.1: Multi-GPU system architectures.

Discrete designs are preferred in High Performance Computing environments due to their much higher memory bandwidth. Moreover, several discrete GPUs can be installed in each node, while there are no multi-GPU designs that use integrated GPUs yet. Since this thesis targets the programmability of multiple GPUs, we mainly focus on discrete GPUs, although many of the presented concepts and analyses can be applied to integrated GPUs, too.

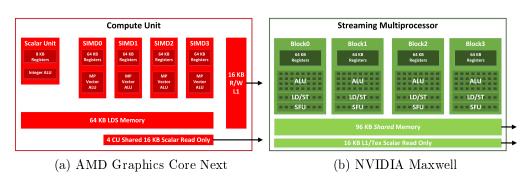

Figure 2.2: Microarchitecture of AMD and NVIDIA GPU cores.

Current GPUs have several highly-multithreaded cores that contain wide vector units. They use a SIMT (i.e., Single Instruction Multiple Threads) execution model in which threads are organized in fixed-length groups (i.e., warps in NVIDIA GPUs, wave fronts in AMD GPUs) that execute the same instruction concurrently on the different lanes of the vector units. The current size of a warp is 32 threads in NVIDIA GPUs and 64 threads in AMD GPUs. When threads in the same warp take different execution paths they produce thread divergence. Since all threads in the warp execute in lockstep, each path is executed by all the threads, although predication is used to disable the lanes of the threads that are not in the executed path. Divergence degrades the throughput of the GPU up to as many times as the number

of diverging execution paths and must be minimized. GPU cores switch execution between different warps to hide the cost of long latency operations such as memory requests. NVIDIA refers to each of this cores as *Streaming Multiprocessor* (i.e., SM) and uses *CUDA core* to refer to each of the lanes of the vector unit [46, 4, 12] (Figure 2.2b). AMD uses *Computing Unit* (i.e., CU) for the cores, *SIMD* for the vector unit and *work item* for the vector lane [1] (Figure 2.2a). In this thesis we use the terms warp, GPU core, vector unit and vector lane.

GPUs typically include a cache memory hierarchy, but it serves a different purpose than CPU caches. In CPUs, threads compute coarse grain tasks and CPU caches exploit spatial/temporal locality within each thread to minimize the access latency by reducing the number of off-chip memory requests. GPUs, however, use a large number of threads that perform fine grain computations which result in much lower data locality within each thread. On the other hand, neighboring threads tend to access to contiguous data elements. Thus, the main purpose of caches in GPUs is to serve as a coalescing point: memory accesses from different threads in a warp to elements within the same cache line are *coalesced* into a single request. In order to maximize performance, data must be laid out in such a way that memory accesses are always coalesced. A scratchpad memory is also commonly provided for programmers to exploit inter-thread locality.

NVIDIA GPUs implement a two-level hierarchy with a first level composed of a non-coherent private cache per core, and a shared second level cache. L1 caches are write-through and, therefore, modifications from different cores to the same cache line are consolidated in the L2 cache. The cache hierarchy supports atomic operations, which are implemented in the L2 cache, too. The Kepler family of GPUs added a second private cache per SM for read-only data. Each core also contains a scratchpad memory (96 KB in the Maxwell family, 48 KB in previous families). AMD Core Next architecture use a similar two-level memory hierarchy with a local 64 KB scratchpad per core. The main difference with respect to NVIDIA GPUs is that L1 caches are coherent. AMD GPUs also provide a scalar core that handles the execution of common scalar operations (e.g., branches, pointer arithmetic) across threads in a wave front and has its own L1 read-only cache.

### 2.1.1 Memory technologies

CPUs use DDR SDRAM (i.e., Double Data Rate Synchronous Dynamic Random Access Memory) or simply DDR. The revision of this technology that is currently used is DDR3, although many vendors are already shipping DDR4 modules. High-end systems provide several independent communi-

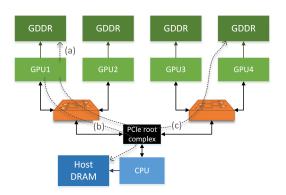

Figure 2.3: Multi-GPU NUMA system targeted in this thesis.

cation channels with the memory modules (AMD Socket G34 supports up to 4 channels). Each channel uses a 64-bit bus and many channels can be combined to build a wider bus (i.e., ganged mode) although this mode is not commonly used. Read and write accesses to the SDRAM are burst oriented; an access starts at a selected location and consists of a total of four or eight data words. For write operations a mask can be used to specify which individual bytes are actually written to memory.

Conversely, discrete GPUs use GDDR5 (i.e., Graphics DDR version 5), which presents some differences with respect to DDR3. GDDR5 devices are always directly soldered down on the board and are not mounted on a memory module (e.g., DIMM). They operate at a much higher frequency than DDR devices. Each channel uses a 32-bit bus, and channels are always ganged by the GPU memory controller to form a much wider bus (up to 512 bits). Bursts in GDDR5 always have a size of eight data words.

## 2.2 Multi-GPU systems

The base system targeted in this thesis is composed of several discrete GPUs connected to the system through a PCI Express (i.e., PCIe) interconnect (Figure 2.3). Besides having access to their own memories, since the Fermi microarchitecture [46], NVIDIA GPUs can access other memories through the PCIe interconnect (i.e., GPUDirect[5]) without host code intervention. At the same time, they introduced a single Unified Virtual Memory Address Space (i.e., UVAS) for all the GPUs in the system. The goal of UVAS is to allow every object in the system, no matter which physical memory it resides in, to have a unique virtual address to be used by application pointers. Combining these two features allows regular load/store instructions to transparently generate local or remote requests, based on the translation of

virtual address to the physical location of the data being accessed. Several of the designs proposed in this thesis take advantage of the remote memory access mechanism to implement shared memory programming on multiple GPUs. As far as we know, AMD does not currently support remote memory access between GPU memories.

#### 2.2.1 Interconnect

Practically all current discrete GPUs use the PCIe interconnect to interface with the host. However, interconnects that offer higher bandwidth have been announced.

#### **PCI Express**

PCIe is a expansion bus that uses a point-to-topology that connects the devices to the root complex [76]. It uses a separate link per device, which can contain several lanes (currently from 1 to 16 lanes are commonly used). The root complex can interface with PCIe endpoints (i.e., devices) or switches that multiplex the link among several devices. This flexibility allows to create complex device hierarchies. Data is transmitted in packets, that can be stripped accross lanes. Therefore, bandwidth increases with the number of lanes. Moreover, PCIe supports full-duplex communication between any two endpoints. Current PCIe 3.0 provides up to 16 GB/s per direction. The encoding used to transmit data in previous PCIe versions reduced the effective bandwidth by a 20%, but PCIe 3.0 uses a different encoding that introduces a 2% overhead, only.

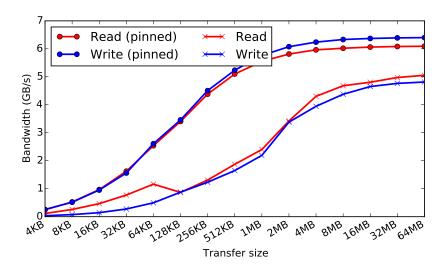

The PCIe standard packets support up to 30-byte headers and up to 4KB payloads (although most PCIe controllers in current processors limit it to 256 bytes or less [50]). The overhead imposed by the size of the headers makes PCIe not well suited for very small transfers. On the other hand, transfers larger than the payload size are broken by the PCIe controller to several packets (which is more efficient than breaking the transfer to smaller transfers in software). Another source of overhead is due to PCIe transactions not being able to use pageable host memory. To solve this problem, the GPU driver copies data to temporary non-pageable (or pinned) buffers before transmitting them to the GPU memory. While double-buffering can be used to hide this cost, they are only effective for large data transfers. Figure 2.4 shows the achieved memory transfer rates for different data sizes in a system with a NVIDIA C2050 and a PCIe 2.0 x16 interconnect. Lines with circles represent transfers using pinned memory buffers instead of regular pageable allocations.

Figure 2.4: PCIe transfer rates for different data sizes.

| Memory                            | Latency                | Bandwidth               |

|-----------------------------------|------------------------|-------------------------|

| DDR3 (CPU, 2 channels)            | $\sim 50\mathrm{ns}$   | $\sim 30\mathrm{GBps}$  |

| GDDR5 (GPU, 4-8 channels)         | $\sim 500\mathrm{ns}$  | $\sim 250\mathrm{GBps}$ |

| HBM                               | $\sim 500\mathrm{ns}$  | 500–1000 GBps           |

| Interconnect                      | Latency                | Bandwidth               |

| Hypertransport 3                  | $\sim 40  \mathrm{ns}$ | $25{+}25\mathrm{GBps}$  |

| QPI                               | $\sim 40~\mathrm{ns}$  | $25{+}25\mathrm{GBps}$  |

| PCIe 2.0                          | $\sim 200\mathrm{ns}$  | $8+8\mathrm{GBps}$      |

| PCIe 3.0                          | $\sim 200\mathrm{ns}$  | $16{+}16\mathrm{GBps}$  |

| NVLink (4 interconnection points) | _                      | $80\mathrm{GBps}$       |

Table 2.1: Memory and interconnection network characteristics.

#### NVLink

NVIDIA will introduce a new interconnect called NVLink [13] in the Pascal GPU family (to be released in 2016), in an effort to replace PCIe with a faster bus. NVLink also uses a point-to-point bus and includes one or several NVLink interconnection points in each device. Devices can bond together several interconnection points to increase the bandwidth. Preliminary studies show 80 GB/s per direction for a device using four interconnection points.

### 2.2.2 GPU NUMA systems

The interconnects and memories in the system have different different latency and bandwidth characteristics (Table 2.1). GPUs access their local memory (Figure 2.3, arc a) with full-bandwidth (e.g.,  $\sim 250\,\mathrm{GBps}$  in GDDR5). They

access other memories in the system through the PCIe interconnect: host memory (arc b) or another GPU memory (arc c)<sup>1</sup>. Remote accesses can traverse any PCIe switch found between the client and the server GPUs. Both CPU memory and the inter-GPU interconnects like PCIe deliver a memory bandwidth which is an order of magnitude lower than the local GPU memory (e.g.,  $\sim 12\,\text{GBps}$  in PCIe 3), thus creating a Non-Uniform Memory Access (i.e., NUMA) system. Future interconnects such as NVLink will increase the bandwidth, but memory interfaces with higher bandwidths have been announced too (HBM [6] will deliver up to  $1\,\text{TB/s}$ ).

#### Remote access characteristics

Besides the lower bandwidth and increased latency, remote accesses present some other peculiarities compared to regular memory accesses. They are not cached in the regular memory hierarchy because modifications from different GPUs to the same cache line could produce coherence problems. However, remote accesses to data that is only read in the computation can be safely cached in the read-only (R/O) cache (currently, this must be specified by programmers by using the \_\_ldg intrinsic provided by CUDA).

# 2.3 Programming models for GPU-based systems

GPUs are typically programmed using a Single Program Multiple Data (SPMD) programming model, such as NVIDIA CUDA [74] or OpenCL [56]. Unless stated otherwise, the CUDA naming conventions are used in the rest of the thesis.

#### 2.3.1 C for CUDA

Although the programming framework is called C for CUDA, we refer to it simply as CUDA in the rest of the thesis. CUDA [74] is divided into two parts:

1. A C/C++ API that exposes GPUs to programs and allows them to manage their memory and launch computations to be run on the GPUs.

<sup>&</sup>lt;sup>1</sup>In systems with multiple CPU sockets, the inter-CPU interconnect (e.g., HyperTransport/QPI) might need to be traversed, too. Unfortunately, current systems do not support routing remote GPU↔GPU requests over the inter-CPU interconnect. Therefore, all the experiments presented in this thesis that require the remote memory access capability are performed on systems with a single CPU socket.

2. A C++-like programming language to write computations that run on the GPU.

#### CPU-GPU interface

Programmers need to manage GPU and host memories. Although they are presented with a UVAS, they control in which GPU memory is physically allocated. They need to copy the necessary data to the GPU memory before launching any GPU computation that uses it. Conversely, output data computed on a GPU needs to be copied back to host memory before it can be accessed by the CPU. Thanks to the UVAS, pointers to data allocated on one GPU can be passed to a different GPU, since it can be transparently accessed through the PCIe interconnect (although with much higher latency and much lower bandwidth).

The GPU is a passive device that executes asynchronous commands pushed by the host code: mainly kernel launches and memory transfers. The GPU address space is abstracted with a CUDA context. By default, a single CUDA context is assigned to each GPU, but additional contexts can be created. GPUs provide several command queues which are abstracted as CUDA streams. Commands pushed to a stream are executed in order, but commands from different streams can execute in any order and, if there are enough available resources, concurrently. Therefore, several streams must be used to overlap computation and data transfers. CUDA provides different levels of synchronization: device, stream, and individual operation (using CUDA events). Event barrier operations can be also pushed to streams to guarantee inter-stream command ordering. All these abstractions need to be used in most cases in order to achieve high performance, thus greatly increasing coding complexity.

#### GPU programming model

Programmers encapsulate computations in functions (called kernels) that are executed in parallel by a potentially large number of threads, although each thread might take a completely different control flow path within the kernel. All these threads are organized into a computation grid of groups of threads (i.e., thread blocks). Each thread block has an identifier and each thread has an identifier within the thread block, that can be used by programmers to map the computation to the data structures. CUDA provides a weak consistency model: memory updates performed by a thread block might not be perceived by other thread blocks, except for atomic and memory fence (GPU-wide and system-wide) instructions.

Each thread block is scheduled to run on an SM, and threads within a thread block are issued in fixed-length groups (the previously described warps). Each thread has its own set of private registers and threads within the same thread block can communicate through a shared user-managed scratchpad and using synchronization instructions. The number of thread blocks that can execute concurrently on the same SM (i.e., occupancy) depends on the number of threads and other resources needed by each block (i.e., scratchpad memory and registers). Hence, the utilization of these resources must be carefully managed to achieve full utilization of the GPU.

### 2.3.2 OpenCL

OpenCL [56] is an open programming framework maintained by the Khronos standardization organization. It shares many design principles with CUDA but its scope is far more ambitious since it targets virtually any type of computing device. However, its genericity makes it more cumbersome than CUDA to use in applications. Instead, OpenCL is more commonly used to create higher-level development frameworks or in commercial applications that need to run on a wide variety of hardware platforms.

Although being more generic than CUDA, it provides higher abstractions in some areas like memory management. For example, memory is allocated in a *context* instead of a device. A context can be bound to several devices and it is the OpenCL runtime who decides in which physical memory it is allocated. Due to the different capabilities of the devices that support OpenCL, mechanisms like remote memory accesses are not supported either. Since the proposed techniques heavily rely on these mechanisms, we use CUDA in the rest of the thesis.

# Chapter 3

# State of the Art

Programmability of multi-GPU systems can be tackled at different levels, ranging from system support to memory management and transparent computation decomposition and distribution.

# 3.1 Automatic CPU/GPU memory coherence

GPUs use different memories or separate memory subsystems than CPUs. This provides a performance advantage but, on the other hand, programmers are forced to use several copies of data and keep them coherent. Some solutions have been proposed to automatize the CPU/GPU memory coherence.

The ADSM model proposed by Gelado et al. [45] presents a Unified Virtual Address Space (UVAS) which is shared by CPU and GPU. ADSM allows programmers to declare objects once and use them both in GPU and CPU functions with no need for explicit memory transfers at all. The ADSM runtime transparently creates the needed copies of the objects and makes sure that they are coherent at consistency points. It uses acquire/release consistency at kernel call boundaries. ADSM is implemented in the GMAC user-level library [10] that provides eager GPU memory update to transparently overlap CPU computation (e.g., data initialization) and data transfers. GMAC uses the memory protection mechanism of modern CPUs to detect with pages are accessed in the host code. However the work in these thesis targets multi-GPU systems while ADSM is restricted to a single GPU. In Chapter 5, we present the HPE model that extends ADSM to multi-GPU systems.

While ADSM greatly simplifies GPU development, programmers still need to use a specialized allocation/free functions for data that is shared between CPU and GPU. Jablin et al. propose compiler analysis in [52] to

automatically determine which data structures are shared. They also add support for stack allocations and global variables, while GMAC is limited to heap allocations. The runtime system inspects the parameters at kernel call boundaries and keeps track of the location of data to determine when data transfers are required. This approach prevents the utilization of complex data types that use pointers, as they should be recursively inspected. Jablin et al. extend this work in [51] by replacing the parameter inspection with the memory protecting mechanism like the one used in GMAC. These works, like ADSM, target systems with a single GPU, only.

Some higher-level languages have been proposed to simplify memory management in GPU programs. C++ AMP [3] provides a multi-dimensional array data type to represent the data that is used in the GPU kernels. Objects created from this type can be used in the CPU code, too. Using this type instead of raw pointers allows the compiler to detect the memory objects passed to each GPU kernel and insert the appropriate coherence annotations for the runtime system. The solution proposed in Chapter 7 uses the same approach of using a special data type, but the proposal in Chapter 5 works for any type of memory allocation.

# 3.2 System support and GPU virtualization

GPUs are commonly presented as isolated compute-only devices that cannot interact with other devices (e.g., network interfaces or disks). Moreover GPU programs are not well integrated with many of the mechanisms offered by Operating Systems such as inter-process communication and memory paging.

Silberstein et al. propose GPUfs in [82], a POSIX-like API for GPU programs that makes the file system directly accessible to GPU code. The API is designed to exploit structured data parallelism such that threads in the same warp cooperate to perform read/write operations. GPUfs is mostly implemented as a library that works with the host OS on the CPU to coordinate the file system's namespace and data. The GPU sends file operation requests to the CPU while the kernel is running, by using a shared communication buffer. A kernel module component enables caching both in the CPU and GPU memories by distributing the buffer cache in the OS. Different GPUs and CPUs can concurrently work on the same file and changes are consolidated using diffing<sup>1</sup> at synchronization points.

Kim et al. present GPUnet in [58], a native networking layer that provides a socket abstraction and high-level networking APIs to GPU programs.

<sup>&</sup>lt;sup>1</sup>Diffing is a technique that compares a memory buffer with its original copy to find the values that have changed.

GPUnet removes the need for programmers to coordinate NIC, CPU and GPU in order to transfer data that resides on the GPU memory. Further, GPU kernels can trigger network transfers and, therefore, programs no longer need to wait for kernel finalization in order to transfer data. GPUnet takes advantage of GPUDirect, enabling direct communication between NIC buffers and GPU memories, and avoiding intermediate copies to host memory. Optimized paths are implemented for communication between sockets of GPUs that reside in the same node (and do not require using the NIC).

Rossbach et al. [78] propose a new abstraction called PTask for processes that run on the accelerator and the addition of ports and channels to represent the communication graph among regular processes and PTasks. Using this scheme, unnecessary memory transfers among CPU and GPU memories can be avoided since the placement of memory objects is known to the system runtime. Moreover, more intelligent scheduling policies can be implemented by taking advantage of the features provided by the accelerators in the system (e.g., concurrent GPU execution and memory transfers).

Duato et al. propose the rCUDA middleware. rCUDA virtualizes the CUDA-RT API and implements a client/server architecture to execute applications on remote GPUs. In [40], authors use rCUDA to manage all the GPUs in a cluster. This allows applications to use remote GPUs in a similar way as if they were local GPUs. It also enables cluster-level scheduling, which leads to higher GPU utilization. In [39], rCUDA allows programs in guest Virtual Machines to access the GPUs on the physical machine. Compared to our work, rCUDA is limited to and requires a complete implementation of the CUDA-RT API, while the HPE model proposal in Chapter 5 can be implemented in different programming models (versions exist for CUDA and OpenCL).

Similarly to rCUDA, Shi et al. propose vCUDA in [80] to implement GPU sharing for programs running in guest Virtual Machines. It provides a virtual GPU view to each application running on the node, though multiple applications actually share a single physical GPU. Instead of sharing among applications, our solution in Chapter 7 aggregates all the GPU resources into a single virtual GPU to transparently scale the performance of applications.

Virtualization proposals for OpenCL-based clusters also exist. Barak et al. introduce VCL in [25], a solution based on MOSIX that exposes all the GPUs in the cluster to standard OpenCL programs. Xiao et al. present VOCL in [98, 99]. Besides the transparent access to remote GPUs, VOCL is able to perform live migration of *virtual GPUs* between different physical GPUs in a cluster. Like rCUDA, these solutions are limited to applications that use the OpenCL API.

Kato et al. propose in [55] a more generic GPU virtualization solution

by implementing GPU-aware resource management in the OS, called Gdev. Gdev integrates virtual memory management in the OS kernel, thus allowing to implement mechanisms such as shared memory between processes. It also implements preliminary support for paging although GPUs do not provide support for restartable page faults (needed to implement on demand paging). Instead, when a process requests more memory than is available on the GPU, Gdev evicts data from other processes using the GPU and moves it to host memory.

HSA [16] (i.e., Heterogeneous System Architecture) is a industry standard for heterogeneous systems that defines a set of features that need to be supported by devices. Many of the members of the HSA Foundation are major silicon vendors such as AMD, ARM and Samsung. One of the main objectives of HSA is to completely remove the need for programmers to explicitly manage all the memories in the system. Similarly to our proposal in Chapter 5, HSA provides a single flat virtual address space in which all the memory can be accessed by any processor in the system. HSA also requires support for context switching and paging to implement system-wide policies. Currently, only a few devices have support for HSA and support in GPUs is limited to integrated designs such as the ones in AMD APUs. While HSA theoretically supports any high-level programming language, current HSA-compliant GPUs use OpenCL.

### 3.3 Automatic multi-GPU execution

# 3.3.1 Compiler-based transparent multi-GPU execution

Kim et al. [57] introduce an OpenCL framework that combines multiple GPUs and treats them as a single compute device. Thus, when a kernel is launched, they decompose computation and data across the GPUs in the system. The computation grid of the kernel is decomposed into uniform partitions that are distributed across GPUs. In order to perform data decomposition, they compute the array range accessed by each computation partition by performing a sampling run of the kernel on the CPU. This step is only performed if array references are affine transformations of the thread and block identifiers, which is determined using compiler analysis; otherwise the whole array is replicated in all GPU memories. This solution does not detect the dimensionality of the arrays used in the GPU kernels. Therefore, even in cases where data can be decomposed, any array decomposition not performed on its highest-order dimension will produce tiles whose memory address ranges overlap, replicating big portions of the array in all memories.

The main problem of using replication is that it reduces the size of the problems that can be handled. Another drawback is that replicated array regions that are potentially modified from different computation partitions need to be merged after every kernel execution. This step is executed on the CPU, thus increasing CPU $\leftrightarrow$ GPU traffic and imposing a large overhead in many computations. Furthermore, atomic operations do not on replicated data, either.

Lee et al. [61] propose SKMD, which extends the same idea to heterogeneous systems with CPUs and GPUs. SKMD performs a profile of the different devices in the system to distribute the computation partitions according to their capabilities. They do not use the sampling runs on the CPU and solely rely on the compiler to detect the array region accessed by each partition, which leads to replication in more cases than in [57]. On the other hand, they generate a merge kernel (based on the original kernel code) for replicated data, that is more efficient. However, this step is still performed on the CPU, requiring all the replicated copies to be transferred to host memory (which is the part of the merge step that incurs the most overhead).

The solution proposed in Chapter 7 exploits the support for remote access across GPU memories thus avoiding, in most cases, data replication and merge operations that are required in these previous works.

### 3.3.2 Compiler-based multi-GPU code generation

Lee et al. [63, 62] provide automatic GPU code generation called OpenMPC, which relies on standard OpenMP annotations for the host code. It detects the variables accessed in each loop (that can be explicitly specified through clauses or implicitly), the access type, and implicit synchronization points. A second phase divides parallel regions at synchronization points to enforce correctness (there are no kernel-wide synchronization primitives in CUDA). The next phase transforms the CPU-oriented kernel into a CUDA kernel and performs CUDA-specific optimizations. The compiler inserts calls for GPU memory allocation and data transfers between CPU and GPU memories. Sabne et al. [79] extend OpenMPC to support out of core computations and multi-GPU execution. It also provides communication and computation overlap. The achieved speedups are competitive with hand-written CUDA versions for a single GPU but they do not scale when several GPUs are used.

PGI proposes custom directives for Fortran programs to automatically generate optimized code for accelerators in [97]. Clauses are included to explicitly specify data transfers to the GPU memory. The compiler performs

strip-mining<sup>2</sup> on the program loops to generate inner loops and assign the different loops to block-level and thread-level parallelism offered in CUDA. These directives have been later extended and published as the OpenACC standard [75] which is supported by many hardware and systems vendors. OpenACC, however, requires programmers to manually decompose computations so that they can be executed on multiple GPUs.

Our solution presented in Chapter 7 uses compiler analysis to automatically determine how computation and data can be decomposed and distributed, achieving linear speedups.

#### 3.3.3 Multi-GPU libraries

Using libraries is a simple way for programs to transparently be able to run efficiently on different computer architectures. Programmers only need to express computations in terms of calls to library functions, with no knowledge of the characteristics of the hardware. Libraries can implement optimized versions of these computations for different accelerator architectures and system topologies.

MAGMA [93] is a widely-used linear algebra library with support for large systems. It implements heterogeneous execution of computation kernels that uses both CPUs and GPUs. Unfortunately, only a subset of the provided functions is able to exploit several GPUs.

Nukada et al. [73] present a 3D FFT library for CUDA. It uses autotuning to generate CUDA kernels that are optimized for different transform sizes.

Babich et al. [24] propose QUDA, a library for numerical lattice quantum chromodynamics (LQCD) calculations. Thanks to a multi-dimensional decomposition of the problem, they are able to scale the performance to up to 256 GPUs.

ArrayFire [17] is a C/C++/Fortran library that provides abstractions for multidimensional arrays and a number of libraries that use them (e.g., data analysis, linear algebra, image and signal processing). However, the utilization of these arrays is limited to the functions offered in their libraries and cannot be used in custom user-defined kernels.

In the latest versions of CUDA, NVIDIA offers cuBLAS-XT [8], an extension of their cuBLAS [7] library that is able to decompose and spread work across several GPUs for a set of Level 3 BLAS calls. Moreover, they also provide NVBLAS [11], which provides automatic multi-GPU acceleration for applications that use regular BLAS calls. NVBLAS builds on cuBLAS-XT

<sup>&</sup>lt;sup>2</sup>Strip-mining reshapes a multi-dimensional space to create additional dimensions from the elements of one of the original dimensions. It is commonly used to perform blocking.

and intercepts calls from the application to regular BLAS libraries, and replacing them with GPU calls, transparently.

The main problem of the library approach is that only the computations provided in the library are able to transparently use multiple GPUs.

# 3.4 Languages for multi-GPU execution

Several languages (that mainly use the PGAS model) have been proposed or extended to ease the exploitation of multiple accelerators in large systems. These PGAS (Partitioned Global Address Space) languages require a complete rewrite of the program and are not typically used to port existing codebases.

Universal Parallel C (UPC) has been extended in [100] to transparently access data allocated in GPUs. UPC uses a Hybrid PGAS in which each CPU thread is bound to one shared segment, that can be either in host memory or in GPU memory, but not both. Each thread is bound to the same memory segment during its lifetime.