# ANALYTICAL COMPACT MODELING OF NANOSCALE MULTIPLE-GATE MOSFETS.

### **Thomas Holtij**

Dipòsit Legal: T 1670-2014

ADVERTIMENT. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

## Thomas Holtij

# ANALYTICAL COMPACT MODELING OF NANOSCALE MULTIPLE-GATE MOSFETS

### DOCTORAL THESIS

Supervised by Prof. Dr. Benjamín Iñíguez and Prof. Dr.-Ing. Alexander Kloes

Department of Electronic, Electrical and Automatic Control Engineering

Universitat Rovira i Virgili

Tarragona 2014

# Statement of Supervision

# Department of Electronic, Electric and Automatic Engineering (DEEEA)

Av. Paisos Catalans 26, Campus Sescelades 43007, Tarragona, Spain

Phone: +34 977 558524 Fax: +34 977 559605

I STATE that the present study, entitled: "ANALYTICAL COMPACT MODELING OF NANOSCALE MULTIPLE-GATE MOSFETS", presented by Thomas Holtij for the award of the degree of the Doctor, has been carried out under my supervision at the Department of Electronic, Electrical and Automatic Control Engineering of this university, and that it fulfills all the requirements to be eligible for the European Doctorate Award.

Tarragona (Spain), August 19, 2014

Prof. Dr. Benjamín Iñíguez, Doctoral Thesis Supervisor

Prof. Dr.-Ing. Alexander Kloes, Doctoral Thesis Co-Supervisor

# Statement of Authorship

# Research Group Nanoelectronics / Device Modeling

Wiesenstrasse 14

35390, Giessen, Germany Phone: +49 641 309-1968 Fax: +49 641 309-2901

I STATE that this document has been composed by myself and describes my own work, unless otherwise acknowledged in the text. Parts that are direct quotes or paraphrases are identified as such. It has not been accepted in any previous application for a degree. All sources of information have been specifically acknowledged.

Giessen (Germany), August 19, 2014

Thomas Holtij, M. Eng.

### Acknowledgments

This doctoral study would not have been possible without the help of many people. I wish to express my deepest thanks to all those who have made this thesis become materialized. First of all, I want to thank my supervisors Prof. Dr. Benjamín Iñíguez and Prof. Dr.-Ing. Alexander Kloes, who supported me throughout the entire thesis. I want to thank them for directing me to interesting topics of research and at the same time encouraged me to follow my own ideas. The many useful discussions and advices on compact modeling and device simulations made me stay confident and helped me to finalize this work.

Thanks to my former colleague Dr. Mike Schwarz for the many discussions on modeling the electrostatic potential of MOSFETs and the enjoyable time we had at several conferences.

I say thank you to my colleague Michael Graef who helped me handling different TCAD simulations and modeling problems, Fabian Hosenfeld for supporting me solving several complex mathematical tasks and to the complete Research Group Nanoelectronics / Device Modeling, at the Technische Hochschule Mittelhessen for the productive time.

Special thanks go to Dr. Ghader Darbandy (Technical University Dresden, Germany), Dr. Francois Lime, Dr. Nae Bogdan Mihai (University Rovira i Virgili, Tarragona, Spain) and Dr. Romain Ritzenthaler (IMEC at Brussels, Belgium) for the useful collaboration during the last three years. The discussions on technical topics made me see problems from a different angle. Thanks for your help concerning technical matters and the administrative procedures. To Dr. Maria Mendez Malaga and Dr. Ghader Darbandy for the nice time we had at our meetings. And to Dr. Daniel Tomaszewski (ITE Warsaw, Poland) for the many helpful discussions about junctionless MOSFETs during several conferences and via e-mail.

To all my colleagues at the Technische Hochschule Mittelhessen, in particular Frank Wasinski, Michael Hof, Johannes Friedrich and Fabian Hosenfeld for making the lunch time at work an enjoyable and relaxing atmosphere. Also to Martin Jung, who supported me during my diploma studies at the Fachhochschule Giessen-Friedberg, Giessen, Germany. Special thanks also to my colleague Michael Graef and to Dr. Ghader Darbandy for proofreading this thesis.

Last but not least I wish to express my deepest thanks to my family and my beloved fiancée Wibke Fuhrberg. You strongly supported me not only during these doctoral studies, but also during all other, sometimes difficult, chapters of my life!

... and many others...

| UNIVERSITAT ROVIRA I VIRGILI<br>ANALYTICAL COMPACT MODELING OF NANOSCALE MULTIPLE-GATE MOSFETS.<br>Thomas Holtij<br>Dipòsit Legal: T 1670-2014 |

|------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

| "Where Do We Come From? What Are We? Where Are We Going?                                                                                       |

| Paul Gaugui                                                                                                                                    |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

|                                                                                                                                                |

## List of Publications

#### **Journals**

- T. Holtij, M. Graef, A. Kloes, B. Iñíguez, "3-D Compact Model for Nanoscale Junctionless Triple-Gate Nanowire MOSFETs, Including Simple Treatment of Quantization Effects", submitted to: Special Issue of Solid-State Electronics, dedicated to EUROSOI 2014

- T. Holtij, M. Graef, A. Kloes, B. Iñíguez, "Modeling and Performance Study of Nanoscale Double Gate Junctionless and Inversion Mode MOSFETs Including Carrier Quantization Effects", available online and accepted for publication in a future issue of: Elsevier Microelectronics Journal

- T. Holtij, M. Graef, F. Hain, A. Kloes, B. Iñíguez, "Compact Model for Short-Channel Junctionless Accumulation Mode (JAM) Double Gate MOSFETs", IEEE Trans. Electron Devices, Vol. 61, No 2, February 2014, Special Issue on Compact Modeling of Emerging Devices

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "Threshold Voltage, and 2D Potential Modeling Within Short-Channel Junctionless DG MOSFETs in Subthreshold Region", Solid State Electron, Vol. 90, pp. 107-115, December 2013, Selected Papers from EUROSOI 2012

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "2D Analytical Calculation of the Parasitic Source/Drain Resistances in DG MOSFETs Using the Conformal Mapping Technique", IETE Journal of Research, Vol. 38, No. 3, 2012

#### Conferences

- T. Holtij, M. Graef, A. Kloes, B. Iñíguez, "3-D Compact Model for Nanoscale Junctionless Triple-Gate Nanowire MOSFETs", accepted for an oral presentation at ESSDERC/ESS-CIRC 2014, Venice, Italy, 2014

- T. Holtij, M. Graef, F. Hain, A. Kloes, B. Iñíguez, "Modeling of Quantization Effects in Nanoscale DG Junctionless MOSFETs", EuroSOI 2014, Tarragona, Spain, 2014

- T. Holtij, M. Schwarz, M. Graef, F. Hain, A. Kloes, B. Iñíguez, "Unified Charge Model for Short-Channel Junctionless Double Gate MOSFETs", MIXDES 2013, Gdynia, Poland, 2013

- T. Holtij, M. Schwarz, M. Graef, F. Hain, A. Kloes, B. Iñíguez, "Model for investigation of Ion/Ioff ratios in short-channel junctionless double gate MOSFETs", ULIS 2013, Warwick, UK, 2013

- T. Holtij, M. Schwarz, M. Graef, F. Hain, A. Kloes, B. Iñíguez, "2D Current Model for Junctionless DG MOSFETs", EuroSOI 2013, Paris, France, 2013

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "Analytical 2D Modeling of Junctionless and Junction-Based Short-Channel Multigate MOSFETs", ESSDERC/ESSCIRC 2012, Bordeaux, France, 2012

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "2D Analytical Potential Modeling of Junctionless DG MOSFETs in Subthreshold Region Including Proposal for Calculating the Threshold Voltage", ULIS 2012, Grenoble, France, 2012

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "2D Analytical Modeling of the Potential within Juntionless DG MOSFETs in the Subthreshold Regime", EuroSOI 2012, Montpelier, France, 2012

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "2D Analytical Modeling of the Potential in Doped Multiple-Gate-FETs Including Inversion Charge", ESSDERC/ESSCIRC 2011, Helsinki, Finland, 2011

- T. Holtij, M. Schwarz, A. Kloes, B. Iñíguez, "2D Analytical Calculation of the Source/ Drain Access Resistance in DG MOSFET Structures", ULIS 2011, Cork, Ireland, 2011

# Contents

| List of Symbols |               |                                                             | xvii |  |

|-----------------|---------------|-------------------------------------------------------------|------|--|

| Ac              | ronyn         | ns                                                          | xxi  |  |

| 1               | Intro         | oduction                                                    | 2    |  |

|                 | 1.1           | History of Semiconductor Technology                         | 2    |  |

|                 | 1.2           | Current MOSFET Technologies                                 | 3    |  |

|                 | 1.3           | Circuit Design and Device Modeling                          | 5    |  |

|                 |               | 1.3.1 Device and Circuit Simulations                        | 5    |  |

|                 |               | 1.3.2 Properties of Models for Circuit Simulators           | 6    |  |

|                 | 1.4           | Challenges and Outline of Thesis                            | 7    |  |

| 2               | MOSFET Basics |                                                             |      |  |

|                 | 2.1           | Operation Principle of Inversion Mode MOSFETs               | 10   |  |

|                 | 2.2           | State-of-the-Art - Inversion Mode MOSFETs                   | 12   |  |

|                 | 2.3           | Operation Principle of Junctionless MOSFETs                 | 17   |  |

|                 | 2.4           | State-of-the-Art - Junctionless MOSFETs                     | 20   |  |

| 3               | Mat           | hematical Basics                                            | 26   |  |

|                 | 3.1           | Poisson's and Laplace's Equation                            | 26   |  |

|                 | 3.2           | Complex Potential Theory                                    | 27   |  |

|                 | 3.3           | Conformal Mapping Technique                                 | 29   |  |

|                 |               | 3.3.1 Transformation of a Potential                         | 30   |  |

|                 |               | 3.3.2 Transformation of a Closed Polygon                    | 30   |  |

|                 | 3.4           | Strategy of Decomposition                                   | 31   |  |

|                 | 3.5           | Potential Solution of Boundary Value Problems of First Kind | 32   |  |

|                 |               | 3.5.1 Single Vertex Approach                                | 32   |  |

|                 |               | 3.5.2 Poisson's Integral in W-Plane                         | 33   |  |

| 4 | DC                                               | Model   | 34                                              |  |  |  |  |

|---|--------------------------------------------------|---------|-------------------------------------------------|--|--|--|--|

|   | 4.1                                              | Model   | ing Preliminaries                               |  |  |  |  |

|   |                                                  | 4.1.1   | Poisson's Equation                              |  |  |  |  |

|   |                                                  | 4.1.2   | Model Simplifications                           |  |  |  |  |

|   |                                                  | 4.1.3   | Conformal Mapping of the Device Structure       |  |  |  |  |

|   |                                                  | 4.1.4   | Application of Poisson's Integral in W-Plane    |  |  |  |  |

|   | 4.2                                              | Closed  | -Form Solution of the 2-D Potential             |  |  |  |  |

|   |                                                  | 4.2.1   | 1-D Particular Solution                         |  |  |  |  |

|   |                                                  | 4.2.2   | 2-D Laplace Solution                            |  |  |  |  |

|   |                                                  | 4.2.3   | Superposed 2-D Potential Solution               |  |  |  |  |

|   | 4.3                                              | 2-D P   | otential Model Verification                     |  |  |  |  |

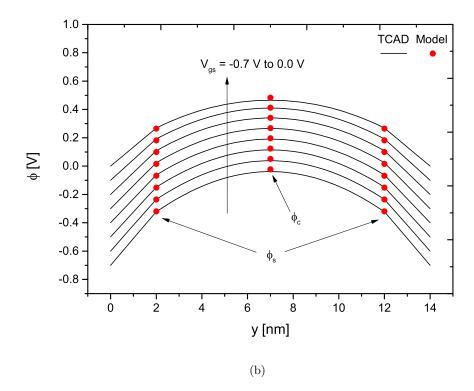

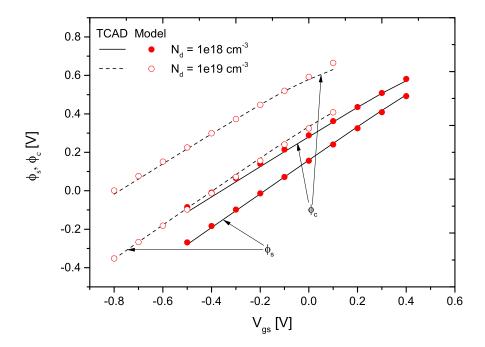

|   |                                                  | 4.3.1   | 2-D Potential of Junctionless DG MOSFETs        |  |  |  |  |

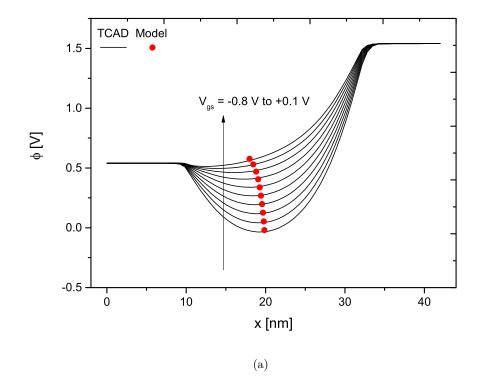

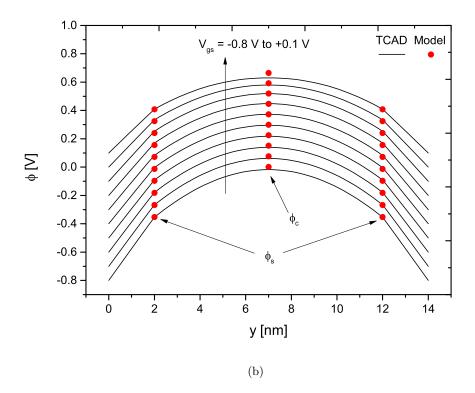

|   |                                                  | 4.3.2   | 2-D Potential of Inversion Mode DG MOSFETs      |  |  |  |  |

|   | 4.4                                              | Electri | ical Model Parameters                           |  |  |  |  |

|   |                                                  | 4.4.1   | Threshold Voltage                               |  |  |  |  |

|   |                                                  | 4.4.2   | Drain-Induced Barrier Lowering                  |  |  |  |  |

|   |                                                  | 4.4.3   | Subthreshold Slope                              |  |  |  |  |

|   | 4.5                                              | Unifie  | d Charge Density Model                          |  |  |  |  |

|   |                                                  | 4.5.1   | Charges in Depletion                            |  |  |  |  |

|   |                                                  | 4.5.2   | Charges in Accumulation                         |  |  |  |  |

|   | 4.6                                              | Model   | ing the Drain Current                           |  |  |  |  |

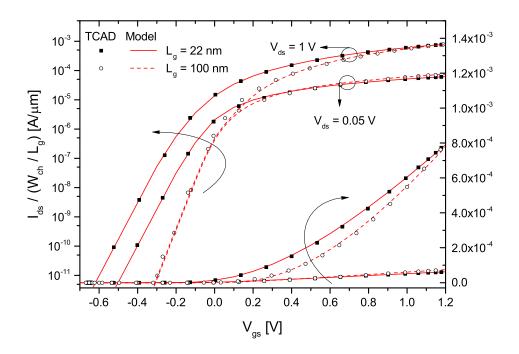

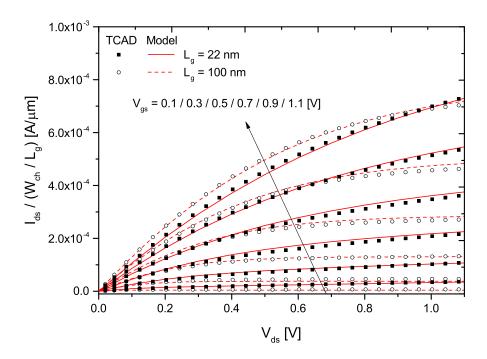

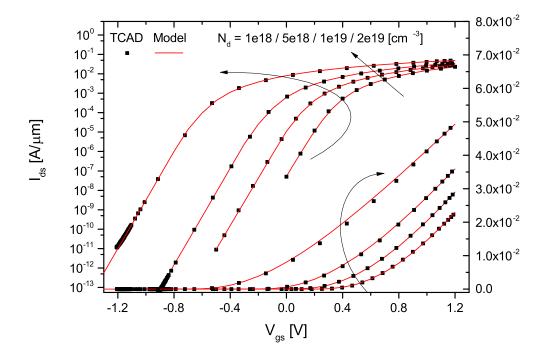

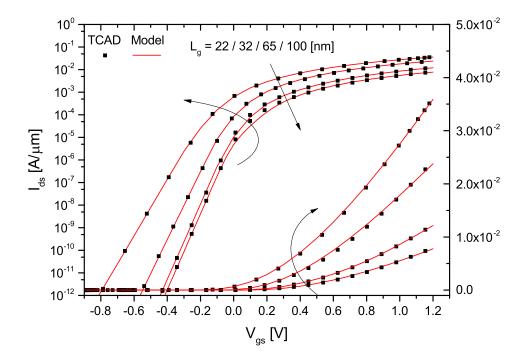

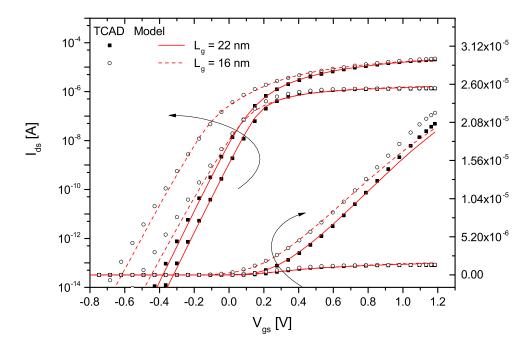

|   | 4.7 DC Model Validation and Discussion           |         |                                                 |  |  |  |  |

|   |                                                  | 4.7.1   | odel Validation and Discussion                  |  |  |  |  |

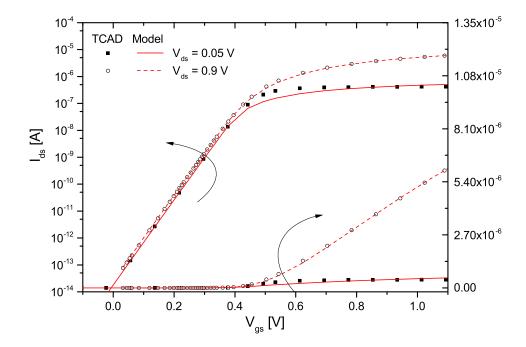

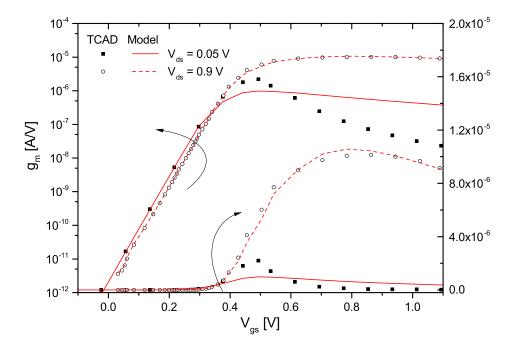

|   |                                                  | 4.7.2   | Drain Current in Inversion Mode DG MOSFETs      |  |  |  |  |

|   | AC Model                                         |         |                                                 |  |  |  |  |

| 5 |                                                  |         | 90                                              |  |  |  |  |

|   | 5.1                                              | _       | e-Based Capacitance Models                      |  |  |  |  |

|   | 5.2                                              |         | ing the Total Charges                           |  |  |  |  |

|   | 5.3                                              | •       | itance Modeling                                 |  |  |  |  |

|   |                                                  | 5.3.1   | Intrinsic Capacitances                          |  |  |  |  |

|   |                                                  | 5.3.2   | Extrinsic Capacitances                          |  |  |  |  |

|   | 5.4                                              |         | odel Validation and Discussion                  |  |  |  |  |

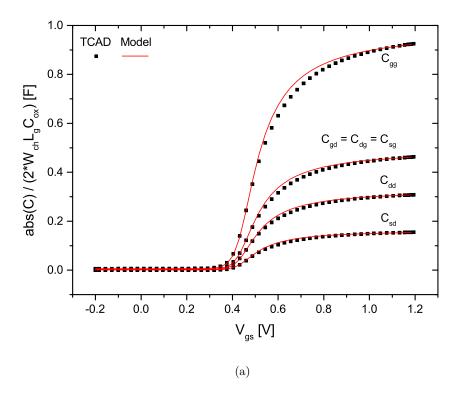

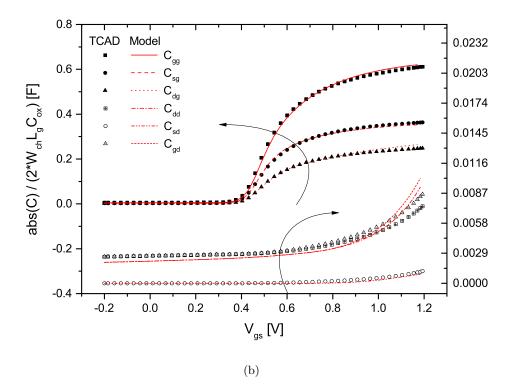

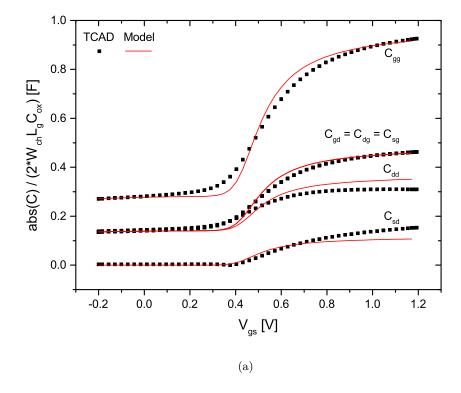

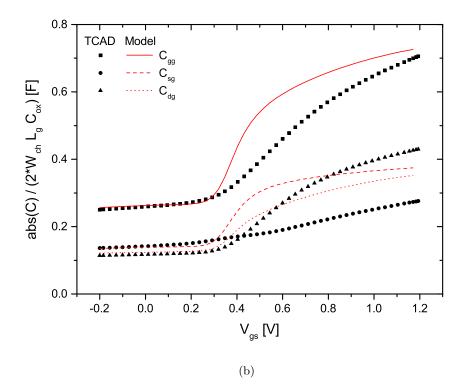

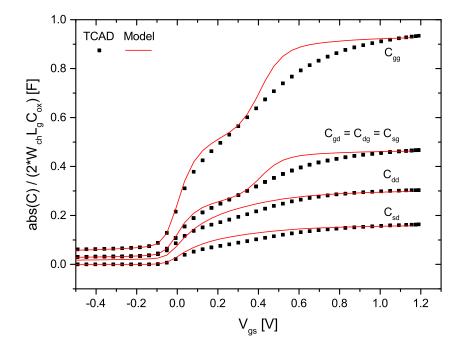

|   |                                                  | 5.4.1   | Capacitances in Inversion Mode DG MOSFETs       |  |  |  |  |

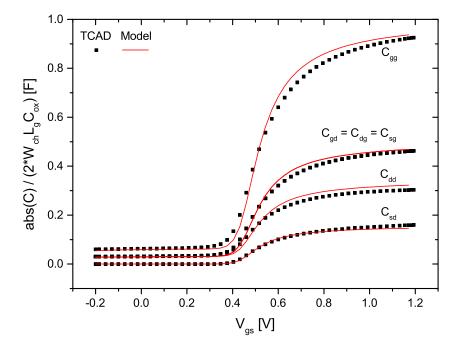

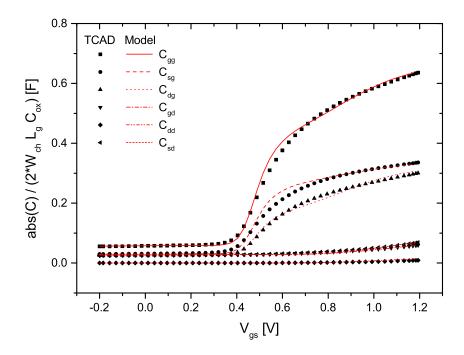

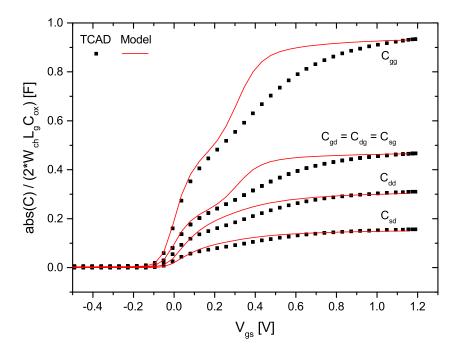

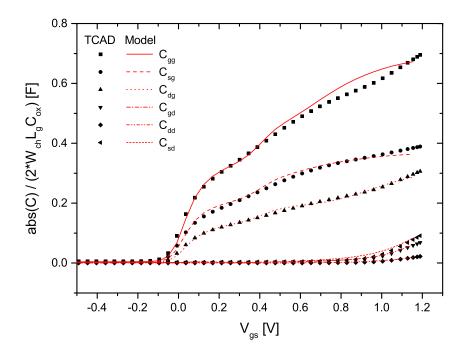

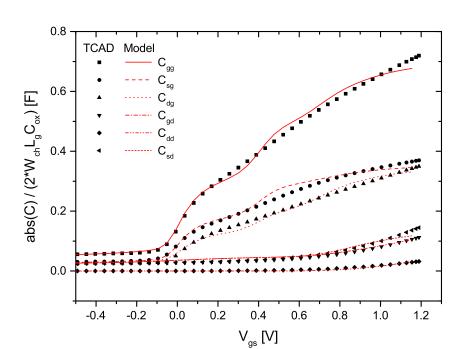

|   |                                                  | 5.4.2   | Capacitances in Junctionless DG MOSFETs         |  |  |  |  |

| 6 | Quantization Effects in Nanoscale DG MOSFETs 106 |         |                                                 |  |  |  |  |

|   | 6.1                                              | Model   | ing of Carrier Quantization Effects             |  |  |  |  |

|   |                                                  | 6.1.1   | Quantum Corrected Threshold Voltage             |  |  |  |  |

|   |                                                  | 6.1.2   | Quantum Corrected 2-D Mobile Charge Density 109 |  |  |  |  |

| UNIVERSITAT ROVIRA I VIRGILI                                    |  |

|-----------------------------------------------------------------|--|

| ANALYTICAL COMPACT MODELING OF NANOSCALE MULTIPLE-GATE MOSFETS. |  |

| Thomas Holtij                                                   |  |

| Dipòsit Legal: T 1670-2014 Contents                             |  |

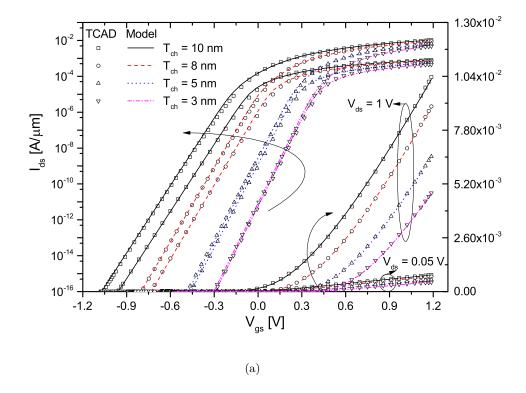

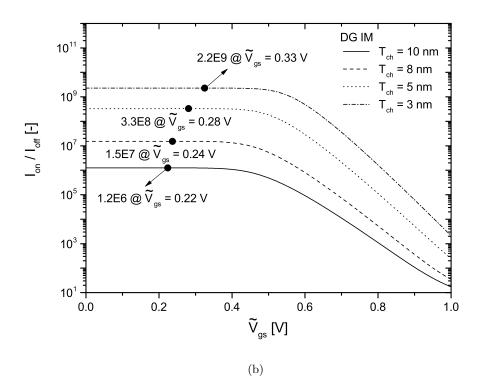

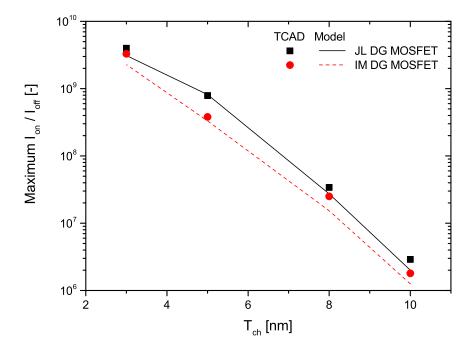

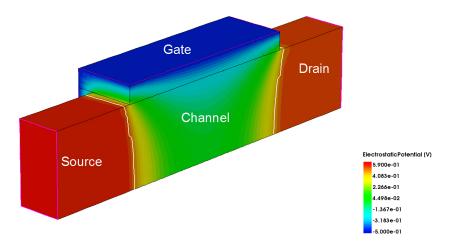

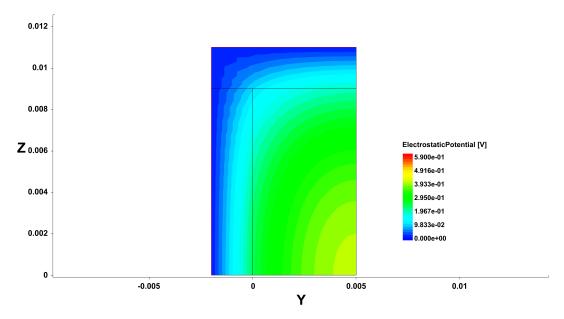

|    | 6.2                | Performance Analysis and Discussions                         | 110 |

|----|--------------------|--------------------------------------------------------------|-----|

| 7  | Mod                | eling of Nanoscale Junctionless Triple-Gate Nanowire MOSFETs | 122 |

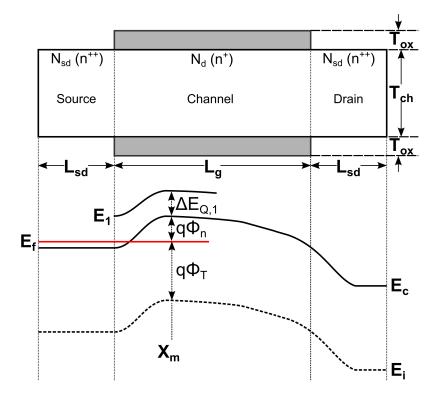

|    | 7.1                | Device Analysis                                              | 123 |

|    | 7.2                | 3-D Potential Modeling Extension                             | 125 |

|    | 7.3                | Mobile Charge Density and Drain Current Model                | 127 |

|    | 7.4                | 3-D Model Validation and Discussion                          | 129 |

| 8  | Cond               | clusion                                                      | 136 |

| Α  | A Equation Package |                                                              | 140 |

| Re | feren              | ces                                                          | 142 |

xvi

# List of Symbols

| Symbol     | Description                                            | ${f Unit}$           |

|------------|--------------------------------------------------------|----------------------|

| $C_{dep}$  | Depletion capacitance per unit area                    | $[F/cm^2]$           |

| $C_{eff}$  | Effective gate capacitance per unit area               | $[\mathrm{F/cm^2}]$  |

| $C_{ext}$  | Extrinsic capacitances                                 | [F]                  |

| $C_{if}$   | Inner fringing capacitance per unit width              | $[{ m F}/\mu{ m m}]$ |

| $C_{ij}$   | Intrinsic or trans-capacitance $(i,j=G,S,D)$           | [F]                  |

| $C_{of}$   | Outer fringing capacitance per unit width              | $[{ m F}/\mu{ m m}]$ |

| $C_{ov}$   | Gate overlap capacitance per unit width                | $[{ m F}/\mu{ m m}]$ |

| $C_{ox}$   | Oxide capacitance per unit area                        | $[\mathrm{F/cm^2}]$  |

| $	ilde{C}$ | Modified effective oxide capacitance per unit area     | $[\mathrm{F/cm^2}]$  |

| $D_{ox}$   | Dielectric displacement density                        | $[{ m C/cm^2}]$      |

| $E_c$      | Energy level for the lower edge of the conduction band | [eV]                 |

| $E_{crit}$ | Critical electric field                                | [V/cm]               |

| $E_f$      | Fermi-energy or Fermi level                            | [eV]                 |

| $E_{f,m}$  | Fermi-energy or Fermi level of gate electrode          | [eV]                 |

| $E_{f,Si}$ | Fermi-energy or Fermi level of silicon                 | [eV]                 |

| $E_g$      | Energy gap of semiconductor                            | [eV]                 |

| $E_i$      | Intrinsic energy level                                 | [eV]                 |

| $E_p$      | Electric field at pinch-off point                      | [V/cm]               |

| $E_v$      | Energy level for the lower edge of the valence band    | [eV]                 |

| $ec{E}$    | Electric field in the space charge region              | [V/cm]               |

| $E_0$      | Electric field at silicon-to-oxide interface           | [V/cm]               |

| $E_1$      | First discrete sub-band energy level                   | [eV]                 |

| $g_d$      | MOSFET small signal drain conductance                  | [A/V]                |

| $g_m$      | MOSFET small signal transconductance                   | [A/V]                |

| h          | Planck's constant                                      | [Js]                 |

| $H_{ch}$   | Effective channel height                               | [nm]                 |

| $I_{ds}$   | Drain current in a 2-D or 3-D MOSFET structure         | $[A/\mu m]$ or $[A]$ |

| $I_{off}$  | Off-current (2-D or 3-D structure)                     | $[A/\mu m]$ or $[A]$ |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Intrinsic carrier concentration [cm $^{-3}$ ] $N_a$ Impurity (acceptor) doping concentration in $p$ -type silicon [cm $^{-3}$ ] $N_b$ Impurity doping concentration in $n$ - or $p$ -type silicon [cm $^{-3}$ ] $N_d$ Impurity (donor) doping concentration in $n$ -type silicon [cm $^{-3}$ ] $N_{sd}$ Impurity (donor) doping concentration in source/drain [cm $^{-3}$ ] $q$ Magnitude of electronic charge [C] $Q_d$ Mobile charge density at drain end per unit area [C/cm $^2$ ] $Q_f$ Fixed charge per unit area [C/cm $^2$ ] $Q_m$ Mobile charge per unit area [C/cm $^2$ ] $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm $^2$ ]           |

| $N_a$ Impurity (acceptor) doping concentration in $p$ -type silicon [cm <sup>-3</sup> ] $N_b$ Impurity doping concentration in $n$ - or $p$ -type silicon [cm <sup>-3</sup> ] $N_d$ Impurity (donor) doping concentration in $n$ -type silicon [cm <sup>-3</sup> ] $N_{sd}$ Impurity (donor) doping concentration in source/drain [cm <sup>-3</sup> ] $q$ Magnitude of electronic charge [C] $Q_d$ Mobile charge density at drain end per unit area [C/cm <sup>2</sup> ] $Q_f$ Fixed charge per unit area [C/cm <sup>2</sup> ] $Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ] $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ] |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $N_d$ Impurity (donor) doping concentration in $n$ -type silicon [cm <sup>-3</sup> ] $N_{sd}$ Impurity (donor) doping concentration in source/drain [cm <sup>-3</sup> ] $q$ Magnitude of electronic charge [C] $Q_d$ Mobile charge density at drain end per unit area [C/cm <sup>2</sup> ] $Q_f$ Fixed charge per unit area [C/cm <sup>2</sup> ] $Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ] $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                               |

| $N_{sd}$ Impurity (donor) doping concentration in source/drain [cm <sup>-3</sup> ] $q$ Magnitude of electronic charge [C] $Q_d$ Mobile charge density at drain end per unit area [C/cm <sup>2</sup> ] $Q_f$ Fixed charge per unit area [C/cm <sup>2</sup> ] $Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ] $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $Q_d$ Mobile charge density at drain end per unit area [C/cm <sup>2</sup> ] $Q_f$ Fixed charge per unit area [C/cm <sup>2</sup> ] $Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ] $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                              |

| $Q_f$ Fixed charge per unit area [C/cm <sup>2</sup> ]<br>$Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ]<br>$Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $Q_m$ Mobile charge per unit area [C/cm <sup>2</sup> ]<br>$Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $Q_{m,acc}$ Mobile charge in accumulation per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $Q_{m,dep}$ Mobile charge in depletion per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $Q_{m,Q}$ Quantum corrected mobile charge per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $Q_s$ Mobile charge density at source end per unit area [C/cm <sup>2</sup> ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $Q_C$ Total charge inside channel region [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $Q_D$ Total charge at drain [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $Q_F$ Total fixed charge inside channel region [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $Q_G$ Total charge at gate [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $Q_{OX}$ Total fixed charge at silicon-to-oxide interface [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $Q_S$ Total charge at source [C]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| S Subthreshold slope [mV/dec]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T Absolute temperature [K]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $T_{ch}$ Effective channel thickness [nm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $T_{gate}$ Effective gate thickness [nm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $T_{ox}$ Effective oxide thickness [nm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\tilde{T}_{ox}$ Scaled effective oxide thickness [nm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $v_{sat}$ Carrier saturation velocity [cm/sec]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{bi}$ Built-in potential [V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $V_{bi,eff,s/d}$ Effective built-in potential at source/drain [V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_d$ Drain potential [V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

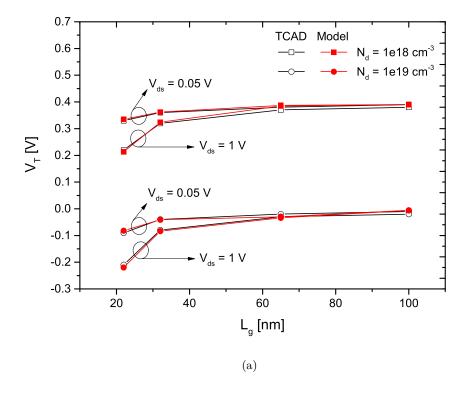

| $V_{ds}$ Drain to source voltage [V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{dsat}$ Drain saturation voltage [V]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $V_{dss}$                 | Saturation voltage                                                                       | [V]                     |

|---------------------------|------------------------------------------------------------------------------------------|-------------------------|

| $	ilde{V}_{dss}$          | Modified saturation voltage                                                              | [V]                     |

| $V_{fb}$                  | Flat-band voltage                                                                        | [V]                     |

| $V_{fit}$                 | Transition voltage between depletion and accumulation region                             | [V]                     |

| ·                         | (Junctionless MOSFET)                                                                    |                         |

| $V_g$                     | Gate potential                                                                           | [V]                     |

| $V_{gs}$                  | Gate to source voltage                                                                   | [V]                     |

| $V_{gs}$ $\tilde{V}_{gs}$ | Gate to source voltage at extracted $I_{on}$                                             | [V]                     |

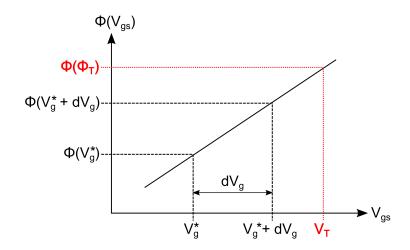

| $V_g^*$                   | Gate voltage in subthreshold region                                                      | [V]                     |

| $V_s$                     | Source potential                                                                         | [V]                     |

| $V_{th}$                  | Thermal voltage $(kT/q)$                                                                 | [V]                     |

| $V_{ox}$                  | Voltage drop across the oxide                                                            | [V]                     |

| $V_{DD}$                  | Power supply voltage ( $\underline{V}$ oltage $\underline{d}$ rain $\underline{d}$ rain) | [V]                     |

| $V_T$                     | Threshold voltage                                                                        | [V]                     |

| $V_{T,Q}$                 | Quantum corrected threshold voltage                                                      | [V]                     |

| $W_{ch}$                  | Effective channel width                                                                  | $[\mu \mathrm{m}]$      |

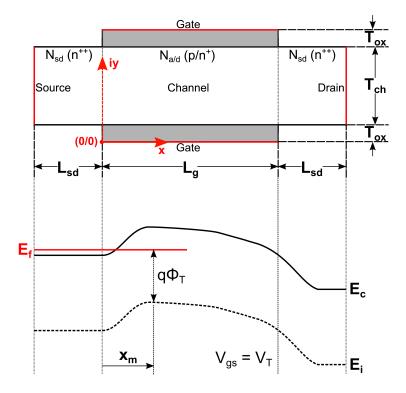

| $x_m$                     | Position of potential barrier within the channel region                                  | [nm]                    |

| $\alpha$                  | Subthreshold slope degradation factor                                                    | [-]                     |

| $	ilde{lpha}$             | Modified subthreshold slope degradation factor                                           | [-]                     |

| $\Delta y$                | Geometry parameter for the conformal mapping technique                                   | [nm]                    |

| $\Delta E_Q$              | Difference between conduction band and first discrete sub-                               | [eV]                    |

|                           | band energy level inside channel region at the potential barrier                         |                         |

| $\Delta V_T$              | Threshold voltage roll-off                                                               | [V]                     |

| $\varepsilon$             | Material dependent permittivity                                                          | [F/cm]                  |

| $\varepsilon_{ox}$        | Dielectric permittivity of oxide                                                         | [F/cm]                  |

| $arepsilon_{Si}$          | Dielectric permittivity of silicon                                                       | [F/cm]                  |

| $arepsilon_0$             | Permittivity of vacuum                                                                   | [F/cm]                  |

| $\theta$                  | Mobility degradation factor                                                              | [1/V]                   |

| $\lambda$                 | 1-D natural length                                                                       | [nm]                    |

| $\mu$                     | Effective channel mobility                                                               | $[{\rm cm}^2/{\rm Vs}]$ |

| $\mu_0$                   | Low-field channel mobility                                                               | $[{\rm cm}^2/{\rm Vs}]$ |

| $\mu_{\perp}$             | Mobility below threshold                                                                 | $[{\rm cm}^2/{\rm Vs}]$ |

| $\Xi$                     | Electric flux                                                                            | [C]                     |

| ho                        | Space charge density                                                                     | $[\mathrm{C/cm^{-3}}]$  |

| $\phi$                    | Electrostatic potential                                                                  | [V]                     |

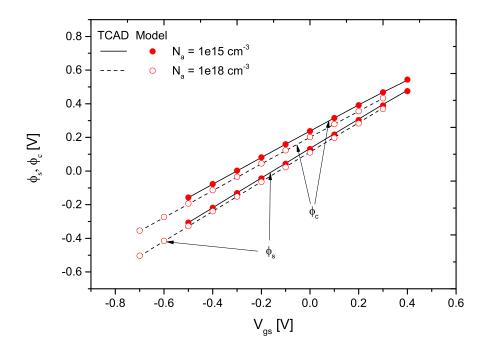

| $\phi_c$                  | Electrostatic potential at channel center (center potential)                             | [V]                     |

| $\phi_{fn}$               | Electron quasi-Fermi level                                                               | [V]                     |

| $\phi_n$                  | Difference between Fermi level and conduction band inside                                | [V]                     |

|                           | channel region at potential barrier                                                      |                         |

| $\phi_p$  | Electrostatic potential of particular solution                 | [V] |

|-----------|----------------------------------------------------------------|-----|

| $\phi_s$  | Electrostatic potential at silicon-to-oxide interface (surface | [V] |

|           | potential)                                                     |     |

| $\phi_T$  | Difference between Fermi level in source region and intrinsic  | [V] |

|           | level inside channel region at potential barrier               |     |

| $\varphi$ | Electrostatic potential of Laplace solution                    | [V] |

# Acronyms

| Symbol                    | Description                                         |

|---------------------------|-----------------------------------------------------|

| ADG                       | Asymmetric double-gate                              |

| CLM                       | Channel length modulation                           |

| CMOS                      | Complementary metal oxide semiconductor             |

| CMP                       | Chemical mechanical polishing                       |

| CPU                       | Central processing unit                             |

| DG                        | Double-gate                                         |

| $\overline{\mathrm{DGM}}$ | Density gradient model                              |

| DIBL                      | Drain-induced barrier lowering                      |

| EDA                       | Electronic design automation                        |

| EI                        | Electrostatic integrity                             |

| EOT                       | Equivalent oxide thickness                          |

| FEM                       | Finite-element-method                               |

| FET                       | Field-effect transistor                             |

| GAA                       | Gate-all-around                                     |

| GCA                       | Gradual-channel approximation                       |

| GIDL                      | Gate-induced drain leakage                          |

| IC                        | Integrated circuit                                  |

| ITRS                      | International technology roadmap for semiconductors |

| HDL                       | Hardware description language                       |

| IFM                       | Impedance-field method                              |

| IM                        | Inversion mode                                      |

| JAM                       | Junctionless accumulation mode                      |

| JL                        | Junctionless                                        |

| JLT                       | Junctionless transistor                             |

| JNT                       | Junctionless nanowire transistor                    |

| LDD                       | Lightly-doped drain                                 |

| LSPE                      | Lateral solid-phase epitaxy                         |

| LTO                       | Low temperature oxide                               |

MOSFET Metal-oxide-semiconductor field-effect transistor

NQS Non-quasi-static NR Newton-Raphson

NW Nanowire

PDE Partial differential equation

PP Perturbation potential

QE Quantization effect

QG Quadruple-gate

QHO Quantum harmonic oscillator QME Quantum mechanical effect

QS Quasi-static

QW Quantum well

UTB Ultra-thin body

RF Radio frequency

RDF Random dopant fluctuation

RSD Raised source/drain

SB Schottky barrier

SCE Short-channel effect

SEG Selective epitaxial growth SDG Symmetric double-gate SOI Silicon on insulator

TCAD Technology computer aided design

TG Triple-gate

VLSI Very-large-scale integration

# CHAPTER 1

### Introduction

The continuous development of very-large-scale integrated (VLSI) devices has a significant impact on the semiconductor technology. In that field, the metal-oxide-semiconductor field-effect transistor (MOSFET) is the most promising device, due to its good scalability, high performance and low power consumption in standby mode. To improve the performance of the MOSFET, its channel length has been reduced from  $\mu$ m to the sub 20 nm region during the past 30 years. Modern central processing units (CPUs) can therefore contain more than two billion (US) transistors [1]. For that reason, circuit design without the help of device simulators, which for example use the finite element method (FEM) and circuit simulators like SPICE [2] or ELDO [3] has become impossible nowadays.

This chapter introduces the reader to the history of the semiconductor technology, its continuous development process, current MOSFET technologies, circuit design and the special demands on the device modeling. In the last section of this chapter the thesis' challenges and its outline are discussed.

# 1.1 History of Semiconductor Technology

Over the past nine decades the semiconductor technology was boosted by inventions like a patent called: "Method and Apparatus for Controlling Electric Currents", from Julius Edgar Lilienfeld in 1926 [4]. He proposed a three-electrode structure using copper-sulfide semiconductor material, but at this time was unable to fabricate working devices. Today his idea is formally known as the field-effect transistor.

Later, derived from Ohl's serendipitous discovery of the pn-junction in 1940 [5, 6], William Shockley presented a pn-junction based transistor in 1948 [7, 8]. This device became the most common form of rectifier used in the electronics industry and has since grown to a key element in the design of semiconductor devices. The first bipolar junction-based transistor was then successfully manufactured in 1951 at Bell Laboratories [9].

In 1958, Jack Kilby of Texas Instruments demonstrated the first integrated circuit (IC) and

an amplifier [10]. Two years after John Atalla and Dawon Kahng fabricated working metal-oxide semiconductor field-effect transistors and demonstrated the first successful MOS field-effect amplifier [11], which today is one of the most common devices used in electrical circuits. In the same year Texas Instruments introduced its first commercial device, the Type 502 Binary Flip-Flop and in 1961, the Series 51 DCTL "fully-integrated circuit" family [12].

The complementary MOS circuit was invented by C. T. Sah and Frank Wanlass, who were with the Fairchild R & D laboratory in 1963 [13, 14]. They showed that logic circuits, combined of p- and n-channel MOS transistors in symmetric, complementary circuits, do not suffer from power losses in standby mode. Today this ground-breaking concept is called CMOS technology.

A very important step in the development of integrated circuits was done by Gordon Moore in 1965. He claimed that the number of components per chip would double every 12 months [15]. This idea was edited for publication with title: "Cramming more components onto integrated circuits" [16]. Later in 1975 he corrected his claim by saying the number of components will double every 24 months [17]. This prediction is commonly known as Moore's law nowadays and is still used as a guideline in the semiconductor industry.

The first integrated microprocessors were fabricated in 1971. One of them was Intel's 4004, developed by Ted Hoff and Stanley Mazor [18–20]. The device contained 2300 transistors in a 16-pin package and can be recognized as the first commercial microprocessor available. Compared to these days' state-of-the-art technology, where Intel launches microprocessors containing more than two billion (US) transistors on a single chip [1], the ongoing development process in that area becomes clearly visible.

## 1.2 Current MOSFET Technologies

One of the most important challenges in recent semiconductor research is to increase the number of devices on a single chip, the storage density of memories and to raise the speed (clock frequency). At the same time the power consumption must be reduced to prevent operational failures, due to self-heating problems. To stand the pace with these requirements, which are stated by the International Technology Roadmap for Semiconductors (ITRS) [21], the dimensions of the MOSFET are continuously shrunk (device scaling) even below 20 nm channel length [1].

At this point, the close proximity between the source and the drain regions of such devices reduces the ability of the gate electrode to sufficiently control the potential distribution and the flow of current in the device's channel region. For that reason, undesired short-channel effects (SCEs) start to bother the device's electrostatic characteristics immensely [22]. Like for example, the threshold voltage roll-off due to the charge sharing effect, the subthreshold slope degradation caused by the punch-through effect or the drain-induced barrier lowering (DIBL) caused by the close proximity of the source and drain, resulting in a decreased barrier formation for electron injection from source into the channel region [23]. In order to cope with

Dipòsit Legal: T 1670-20141 Introduction

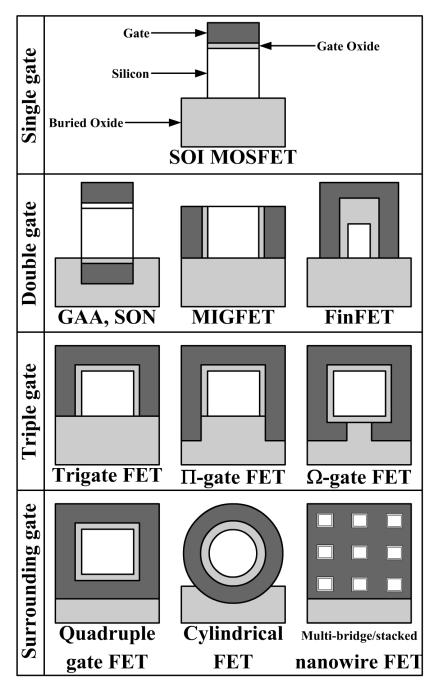

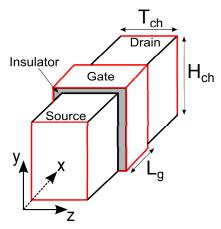

these problems multiple-gate structures, such as the double-gate (DG), the triple-gate (TG) and the quadruple-gate (QG) MOSFET [24, 25], which are illustrated in Fig. 1.1, were analyzed, modeled and fabricated [26–30]. These new devices are reported to have vastly improved electrostatic characteristics (less SCEs) compared to their single-gate counterparts, since the increased electric field of the multiple-gates and therefore, the control of the channel by the gates is stronger than in bulk MOSFETs [26]. This fact makes the multiple-gate MOSFET

Figure 1.1: Possible device and gate structures [26].

an attractive candidate to improve the performance of future CMOS technology. Additionally to SCEs, quantization effects (QEs) must be taken into account in such scaled devices if their channel thickness ranges in the same order of magnitude as the de Broglie wavelength of the charge carriers [31], which complicates the understanding and manufacturing of such devices even more.

Another big challenge remaining is the fabrication of such devices at the nanometer scale. Novel doping and ultra-fast annealing techniques are required to form the ultra-shallow and abrupt pn-junctions in order to avoid a possible fluctuation of dopants from the source/drain into the channel region [32]. This fact gives rise to the development of new, more simple, device structures like the junctionless transistor [33].

The reader can find detailed information about the state-of-the-art technologies and models of the different devices in sections 2.2 and 2.4.

### 1.3 Circuit Design and Device Modeling

A major challenge of nowadays circuits, which contain millions or even billions of connected transistors, is the designing and manufacturing time and also the production costs. To reduce both time and costs several software tools for high-level digital design, mask level synthesis, simulation and modeling of discrete devices are available (electronic design automation (EDA) tools). These tools enable the chip designer to analyze entire semiconductor chips. To ensure proper function, the device or the circuit is running through a bunch of simulation cycles until all malfunctions are eliminated. The advantage of such an EDA tool is that any possible environment can be simulated, like: altering temperature, illumination, variations in the power supply, the influence of statistical variations due to line-edge roughness or random dopant fluctuation effects [34].

#### 1.3.1 Device and Circuit Simulations

Some of the most important discrete device simulators are ATLAS [35], TCAD Sentaurus [34] and Minimos-NT [36]. They provide the user with the ability to simulate a broad range of fully featured 2-D and 3-D devices. These simulators incorporate advanced physical models and robust numeric methods for the simulation of most common types of semiconductor device. Based on a 2-D or 3-D surface or volume grid, respectively, each point on the grid is solved with the help of a partial differential equation (PDE) solver, using certain iteration steps. If a 3-D structure is considered, this method can take several hours or even days depending on the applied settings for the desired accuracy for the results. For that reason, this iterative method is not suitable for circuit simulations, wherefore compact models are commonly used to approximate the device's electrical and thermal behavior as accurate as possible.

Nowadays, the most famous circuit simulators are SPICE [2] and ELDO [3]. For both exist a

Dipòsit Legal: T 1670-20141 Introduction

wide range of different models, which take into account different physical effects. These models can be divided into three groups [37]:

- Threshold voltage  $V_T$  based models assume that the surface potential is a simple function of input voltage  $V_{gs}$ : constant if  $V_{gs} > V_T$  and linear if  $V_{gs} < V_T$ . This results in separate solutions for the different operating regimes and therefore, requires smoothing functions in order to connect the regions. Such models were successfully used in BSIM3 [38], BSIM4 [39] and MOS Model 9 [40].

- Surface-potential-based models solve for the input equation the surface potential at the two ends of the device's channel. The terminal charges, the current and its derivatives are then calculated from the solution of the surface potential. Examples are the SP model [41], MOS Model 11 [42], HiSIM [43–46] and PSP [47, 48].

- Charge-based models find the density of the inversion charge at the two ends of the device's channel and express the model outputs in terms of these charge densities. The conductance and the capacitances are directly derived from the calculated charge densities. Examples for such models are the EKV [49], ACM [50] and BSIM5 [51] and BSIM6 [52] model.

### 1.3.2 Properties of Models for Circuit Simulators

Generally, compact models for circuit simulations should describe the electrical behavior of the transistor in all operating regimes as good as possible. The compact models can be separated into three categories [22, 53, 54]:

- Physical-based models only use physics-based equations to describe the behavior of

the transistor. Such models have the advantage that even downscaled devices can be

described. In literature, physics-based models without empirical parameters are often

introduced to describe the behavior of long-channel devices or single electrical device

characteristics, like threshold voltage and subthreshold slope.

- Numerical-fit models use mathematical expressions without any relation to the physics of the device. By introducing many fitting parameters, the expression is fit to the result from the simulation. On the one hand, this process is technology independent, but on the other hand this approach gives no physical insight into the behavior of the device. Additionally, the model validity outside the data range is uncertain.

- Empirical-based models represent a combination of the physical-based and numerical-fit models. In addition to the physical equations, numerical fitting parameters are added. This reduces the complexity of the model in order to enhance its performance. However, the disadvantage, due to the fitting parameters, is the reduced ability to predict the transistors behavior when the device physics are changed.

It should be clarified that a compact model, to be used in a circuit simulator, should always meet the following requirements [22, 55]:

- High accuracy in order to properly predict the electrical behavior of the transistor over all regions of device operation.

- Not only being accurate, but simple as well (trade-off between accuracy and simplicity).

- To avoid convergence problems, the drain current expressions must prove continuity in its derivative of first-order (for analog applications up to third-order).

- A single model should fit all device sizes used in state-of-the-art design practice.

### 1.4 Challenges and Outline of Thesis

In this thesis the main focus is on the development of an analytical, physics-based and predictive compact model for nanoscale multiple-gate MOSFETs, which should be derived in closed-form to be suitable for circuit simulators. The investigated devices are the standard inversion mode (IM) MOSFET and a new device concept called junctionless (JL) MOSFET. The main scientific objectives are:

- Development of a complete DC model for nanoscale multiple-gate MOSFETs (1-D, 2-D and 3-D MOSFET structures). The model must be derived in closed-form in order to be suitable for circuit simulators. If possible, fitting parameters should be avoided.

- Based on the solutions obtained from the DC model, a charge-based AC model should be derived by using the Ward-Dutton partition method [56].

- Since downscaling does not only affect the device's channel length, quantization effects must be taken into account when the channel thickness is scaled below 10 nm [31].

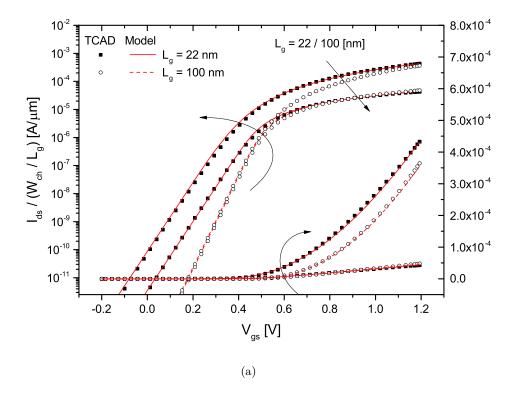

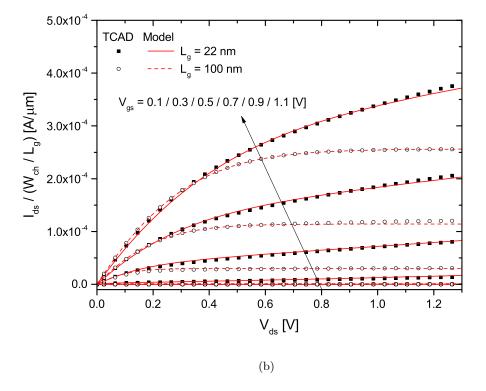

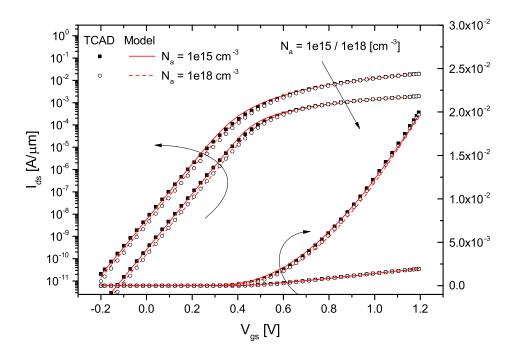

- Verification of the developed model versus TCAD simulation data. Additionally, the 3-D model is to be compared versus measurement data of nanoscale triple-gate nanowire (TG-NW) MOSFETs.

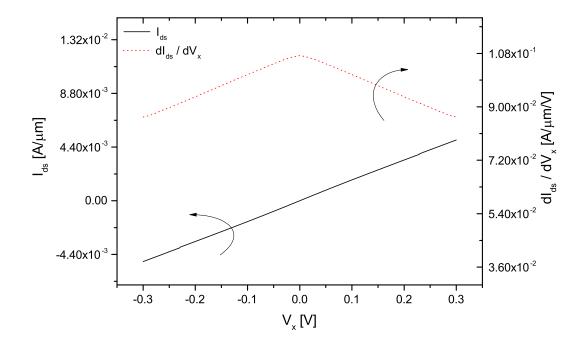

Briefly, the physics-based model for the potential is derived with the help of Poisson's equation and the conformal mapping technique by Schwarz-Christoffel [57]. From this closed-form solution, simple equations for the calculation of the threshold voltage  $V_T$  and the subthreshold slope S are derived. By using Lambert's W-function and a smoothing function to model the transition between the device's different operating regimes, a unified charge density model valid in all regions of device operation is developed. A modified drain current expression is presented and a dynamic model is derived based on the calculated charge densities inside the device. The dependencies between the physical device parameters and their impact on the

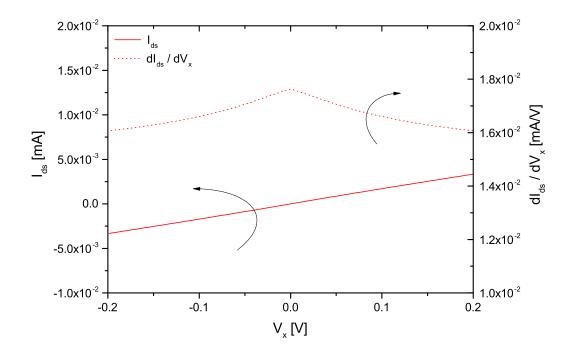

device performance are worked out. Important device characteristics such as threshold voltage  $V_T$ , drain-induced barrier lowering (DIBL), subthreshold slope S and the  $I_{on}/I_{off}$  ratios are addressed and discussed. Additionally, symmetry around  $V_{ds} = 0$  V and continuity of the drain current  $I_{ds}$  at derivatives of higher-order (up to third-order) are in focus of this work.

To stand the pace with recent ITRS [21] requirements for future CMOS technology, we, among other things, will target extremely scaled devices with a minimum channel length of 16 nm and thicknesses down to 3 nm. At this point quantization effects (QEs) play an important role, whereby in the case of a junctionless device, the modeling of QEs differs from their common treatment in inversion mode devices and therefore, requires some special attention. A performance comparison between the inversion mode and the junctionless MOSFET is performed. Finally, an extension for 3-D triple-gate nanowire devices is presented and discussed. Throughout the thesis, intermediate results such as electrostatics and drain current are verified versus TCAD simulations and measurement data.

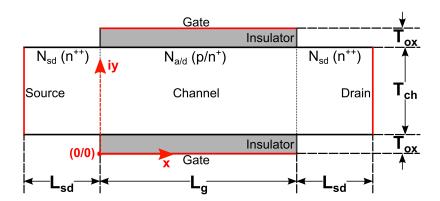

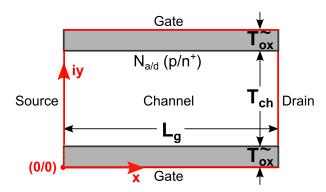

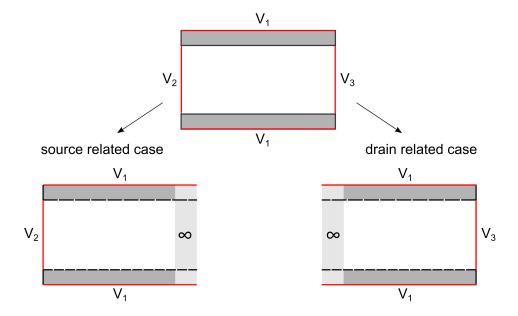

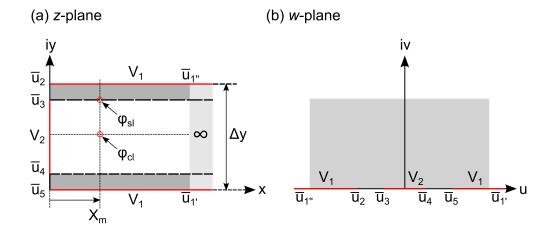

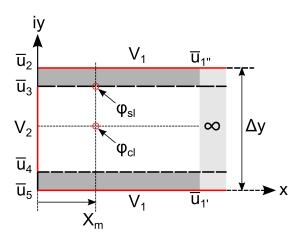

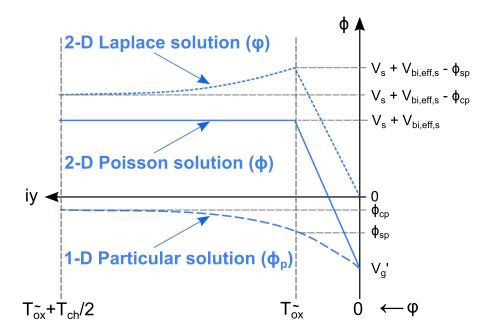

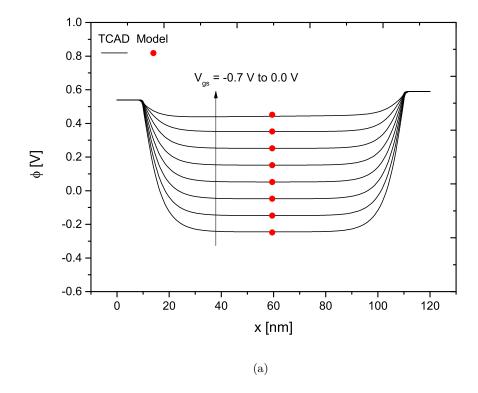

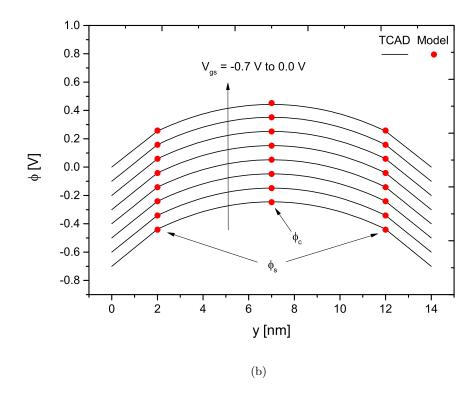

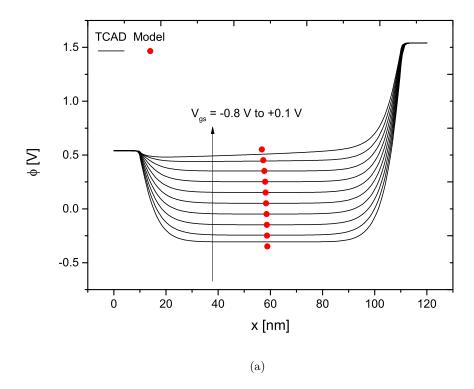

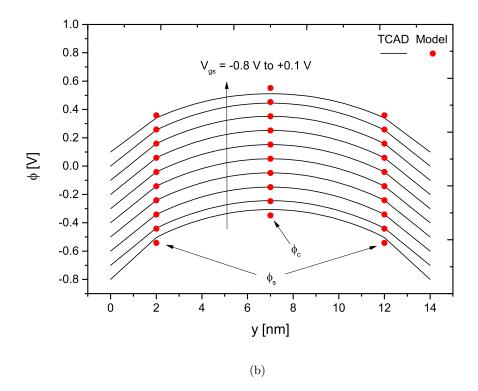

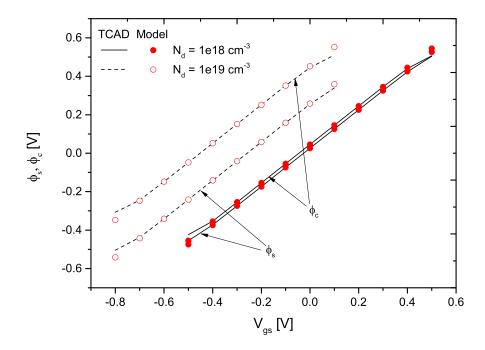

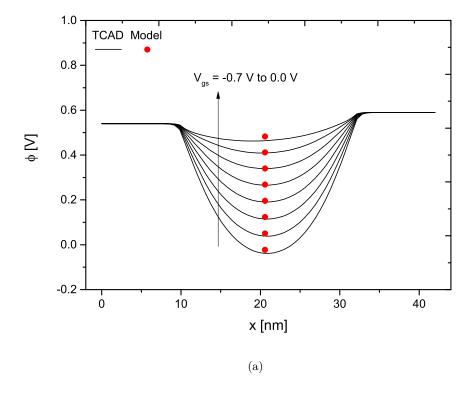

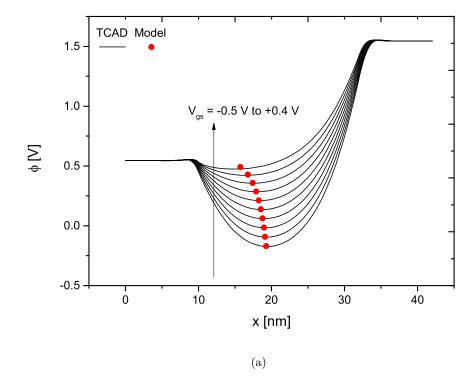

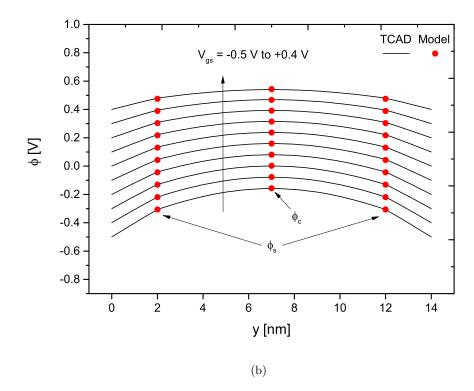

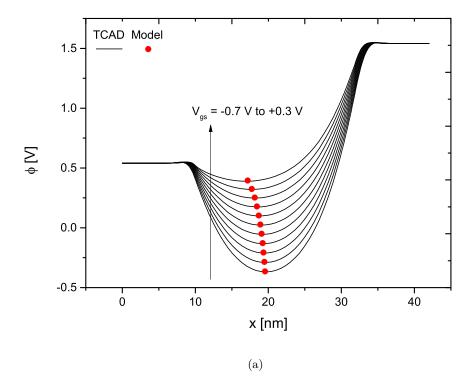

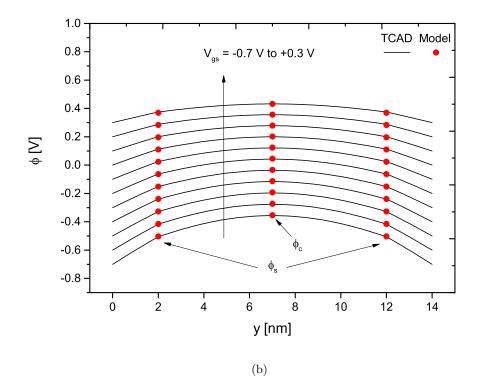

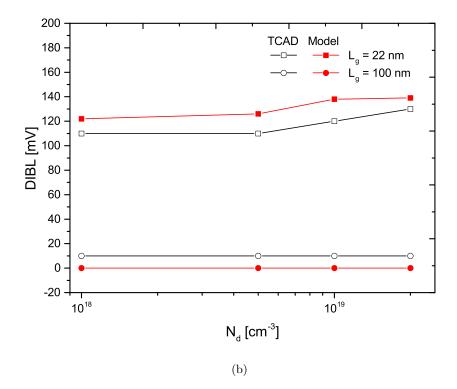

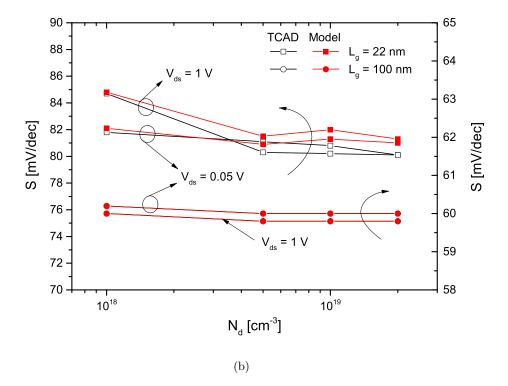

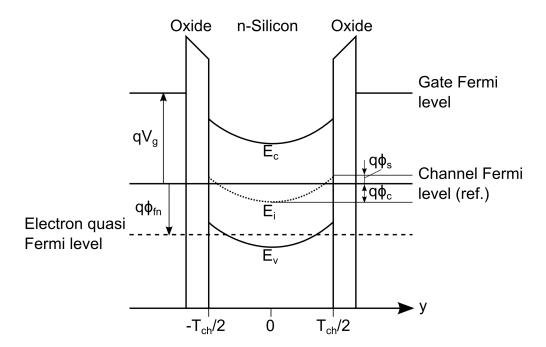

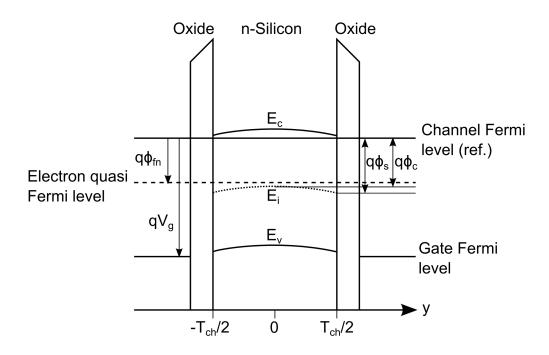

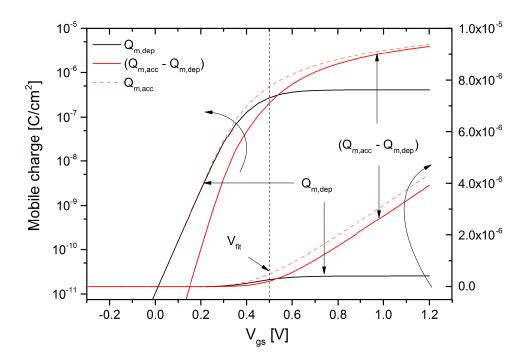

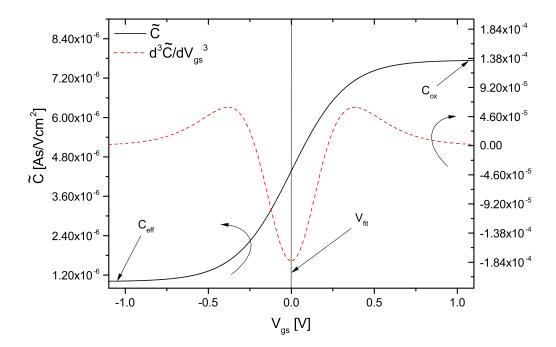

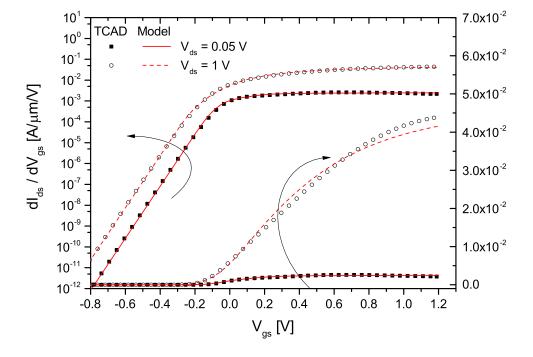

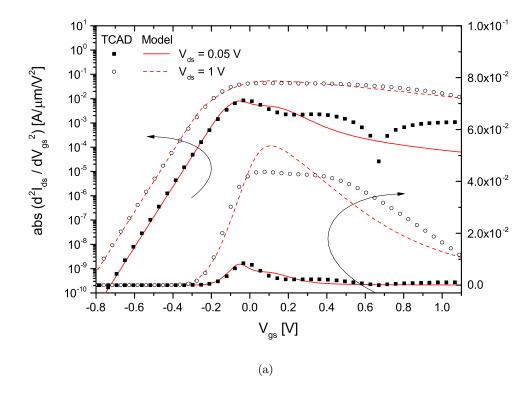

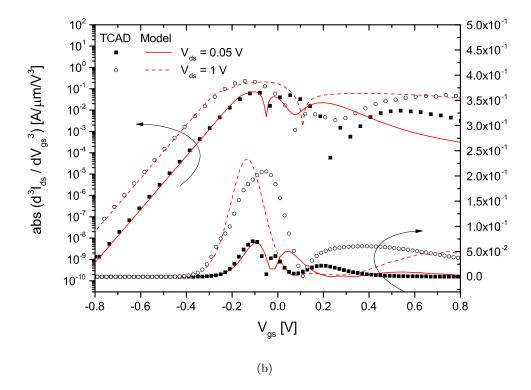

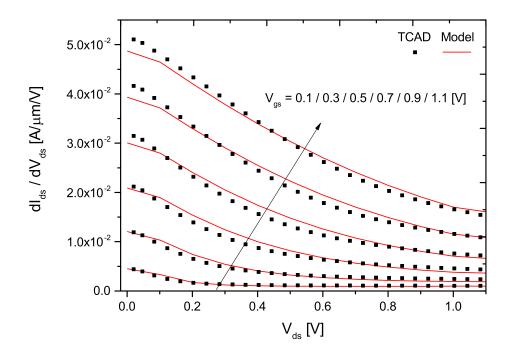

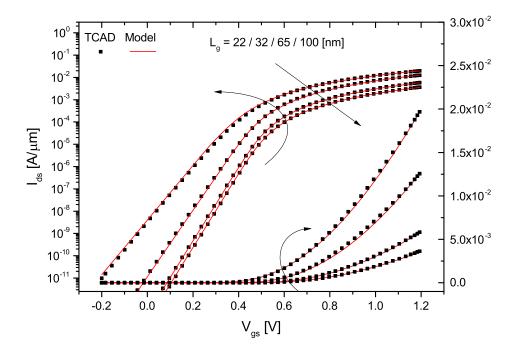

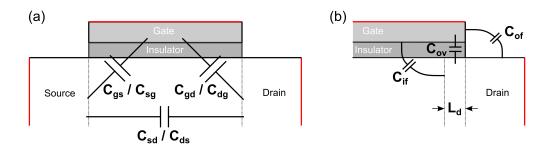

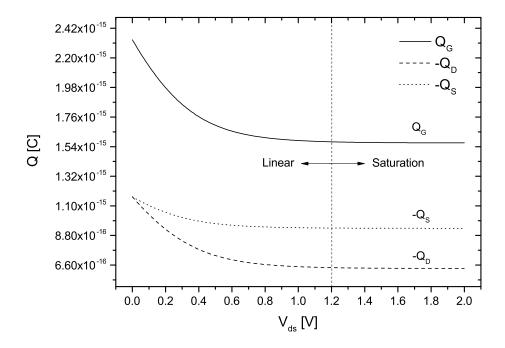

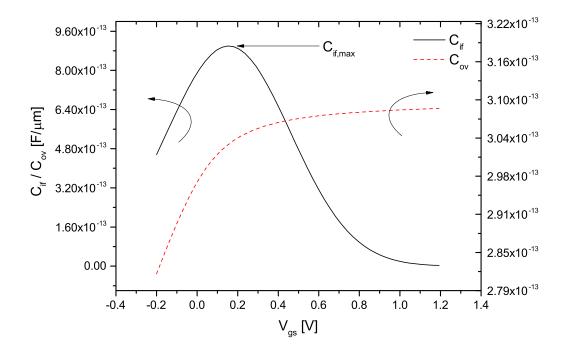

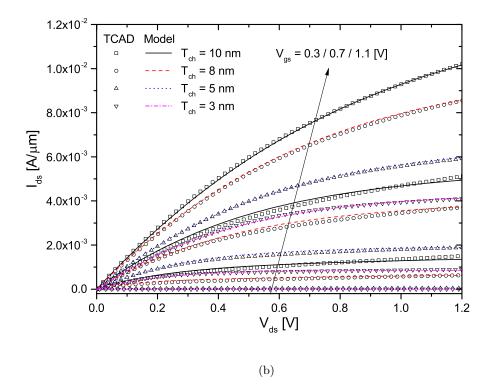

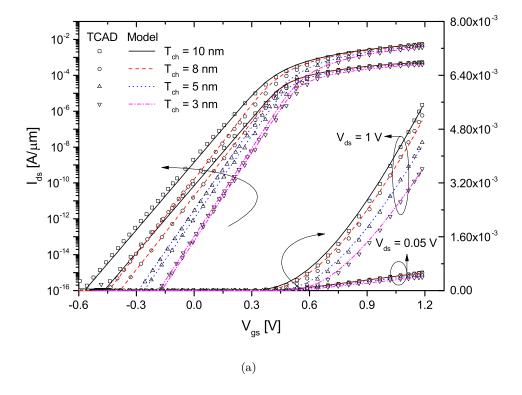

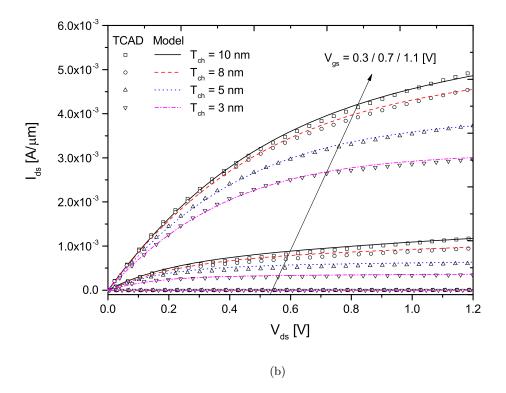

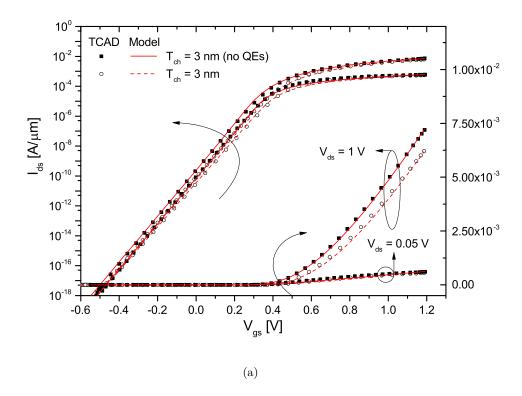

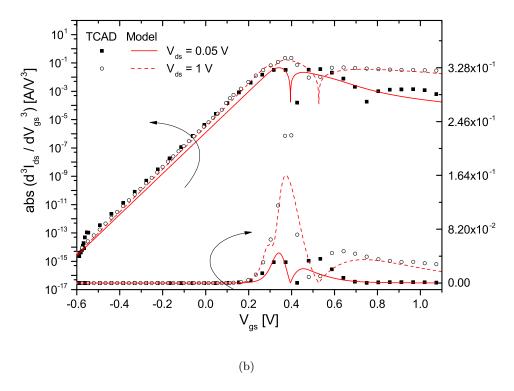

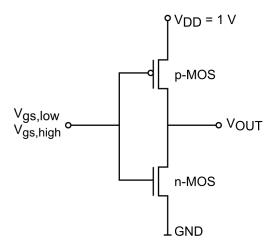

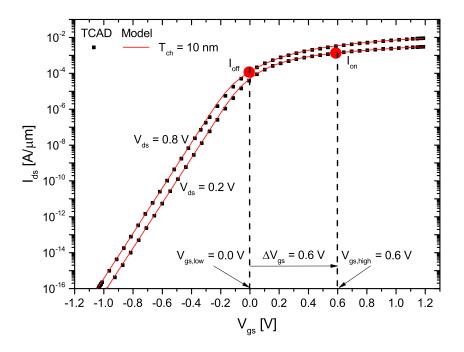

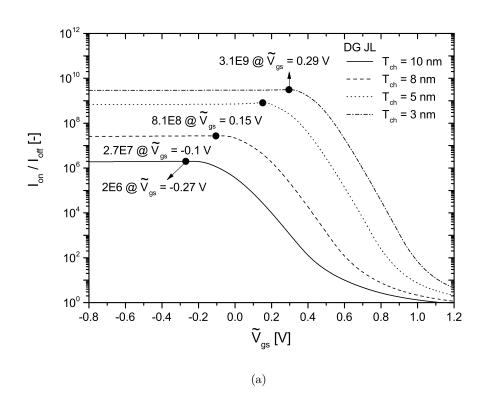

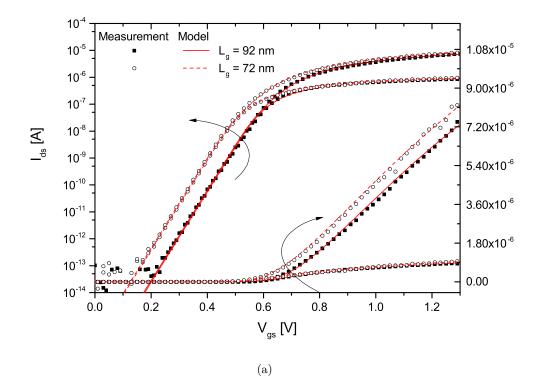

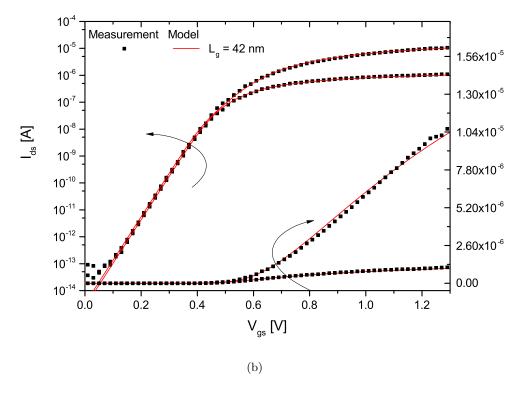

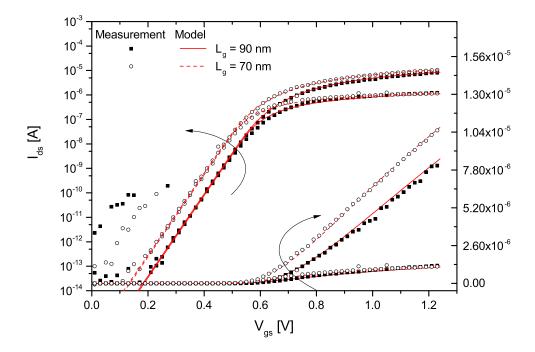

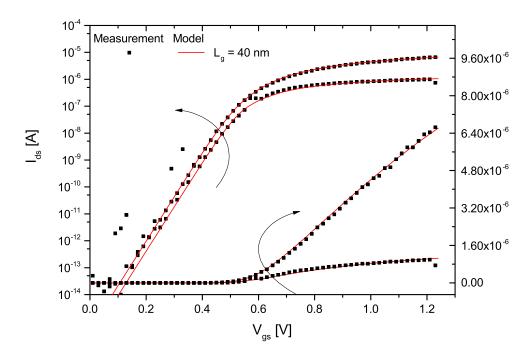

In chapter 2 the basics of the inversion mode and the junctionless MOSFET are detailed, as well as their operation principles. A complete overview of the state-of-the-art technologies and models is presented to the reader.