## PROPOSAL AND DEVELOPMENT OF A HIGHLY MODULAR AND SCALABLE SELF-ADAPTIVE HARDWARE ARCHITECTURE WITH PARALLEL PROCESSING CAPABILITY.

THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENT FOR THE PHD DEGREE ISSUED BY THE UNIVERSITAT POLITÈCNICA DE CATALUNYA, IN ITS ELECTRONIC ENGINEERING PROGRAM.

JAVIER E. SOTO VARGAS

DIRECTOR: JUAN MANUEL MORENO AROSTEGUI

Barcelona, España

July , 2014

This document is prepared to be printed double-sided.

To my wife Carol, for her immense love and unconditional support, thanks for always being there for me.

To my two little dinosaurs: Gabriela and Daniel, for the games that we will play, and for the life that you will teach me to discover.

This thesis is for you, my beautiful family.

Con mucho cariño para mis padres: Evandro 🜩 y Nair. Gracias por el gran ezfuerzo y sacrificio que le han brindado a todos sus hijos.

Para toda mi famila, a la que siempre tengo presente. A mis hermanos: Lina, Diana y Raúl, a mi sobrino Nicolás. y a la memoria de mi tio Enrique .

Para Amira, Dalila y Sarah. Gracias por el apoyo y cariño que le han brindado a la familia durante esta etapa de nuestras vidas, lejos de casa.

# Acknowledgements / Agradecimientos

I consider myself the best friend of my friends, and I think any of them love me as much as I love the friend I love less. Me considero el mejor amigo de mis amigos, y creo que ninguno de ellos me quiere tanto como yo quiero al amigo que quiero menos.

Gabriel García Márquez (1927 – 2014)

First, I would like to thank my thesis supervisor, Professor Juan Manuel Moreno Arostegui, for their guidance during my studies in the Universitat Politècnica de Catalunya. Thank you for your professional and appropriate corrections in the preparation of this work. I would also like to thank the professors Joan Cabestany and Jordi Madrenas for kindly receiving me in the AHA research group. Thank you all for opening the doors of this university, and give me the opportunity of professional growth during the development of my doctoral studies.

Quiero agradecer a todos los que me han brindado su apoyo directo e indirecto durante el desarrollo de mis estudios de doctorado. Escribiendo estas líneas siento deseos de mencionar a muchas personas que he conocido y con quien he compartido algún momento de mi vida, tanto de carácter personal como profesional, con aquellos que han sido parte mi formación como persona y como ingeniero. Con ellos seguramente podremos recordar alguna anécdota o algún momento especial que se mantenga presente en la memoria, uno de esos que siempre se recuerdan con una sonrisa. Para todos los que aparecen en estas líneas y los que no, muchas gracias.

Gracias a la Escuela Colombiana de Ingeniería por formarme como Ingeniero y permitirme ser parte de su comunidad. Gracias a mis compañeros de universidad: Angela, Gustavo, Jaime, Angel y Andrés, con quienes compartí y espero seguir compartiendo, la profesión que ha marcado el futuro de nuestras vidas. Gracias a mis profesores, algunos de los cuales tengo el privilegio de tener como compañeros y amigos. Gracias a Henry por su amistad y apoyo en este proceso. Gracias a Alex y Gina, con quien compartí (sufrí) en paralelo este proceso de formación científica y de crecimiento familiar.

Gracias a mis grandes amigos del colegio, los fetzes: Luis Guillermo, José Alberto, Mauricio, Gustavo, Carlos, Julio y Luis Alfonso. Con quienes viví las aventuras más emocionantes de mi vida antes de salir de Colombia. Gracias a todos ellos, a los que que considero grandes amigos, con los que he compartido muchas fiestas, innumerables carcajadas y alguna copa de aguardiente, estoy seguro vendrán nuevas aventuras y seguiremos viviendo grandes momentos que serán inolvidables, ahora en su gran mayoría con familia incluida. Gracias a Mauricio (Mao), que me brindó su generosa e incondicional amistad durante estos casi siete años en Barcelona. Agradezco también a los demás amigos en España: el siempre amable Rodrigo, los compañeros doctorandos en la UPC, los compañeros de trabajo en Delphi y Wonesys. Todos ellos, *culés* o *merengues* en su mayoría, con quienes compartí muchos momentos de carácter académico, laboral y de ocio, que sin duda recordaré tanto como este periodo en la universidad. Podría asegurar que con la gran mayoría compartí charlas personales, académicas, profesionales y sobre todo deportivas, incluyendo especulaciones pre y post partidos de liga, felicidad en las victorias y tristeza en las derrotas, pero siempre con respeto y amabilidad. También he tenido la oportunidad de compartir con todos ellos claritas, medianas, mojitos, cortados, cafés, biquinis, bocadillos, combinados, menús, días de marcha, partidos de fútbol, ping-pong, futbolín y muchos otros, pero sobre todo siempre brindándome buenos momentos que nunca olvidaré en mi paso por Barcelona.

Agradecimientos muy especiales para mi suegra Amira (Aguila 3), mi cuñada Dalila y mi sobrina Sarah, quienes me han brindado un valioso apoyo durante el tiempo que llevamos en Barcelona, principalmente estando muy pendientes de la familia, situación que me permitía trabajar en el desarrollo de este proyecto de tesis. Su cercanía a pesar de la distancia, nos ayudo a consolidar una unión familiar que fue y es aún un importante soporte para mí y sobretodo para mí familia, y que por lo tanto me ayudó a mantener la esperanza y tranquilidad de que este trabajo finalmente se lograría. Gracias también a todos los demás miembros de la familia Sánchez, que siempre nos han acompañado en este proceso.

Quiero agradecer a mi familia en Colombia, a quienes siempre tengo presentes a pesar de la distancia y del poco contacto que he podido brindarles en este tiempo. Gracias a mi Padre, luchador incansable y gran formador de mi carácter, al que recuerdo con profundo sentimiento y al que pido disculpas por no estar junto a él en los momentos más duros. Gracias a mi madre, el pilar de la familia, que con sus sonrisas y lágrimas ha llenado siempre a su hogar de amor y alegría. Gracias a cada uno de mis hermanos: Lina, Diana y Raúl, y a mi sobrino Nicolás; recordarlos y saber que siempre estarán allí, me llenó de buena energía para seguir adelante en el que fue un largo, intermitente y duro proceso. Gracias a mi tío Enrique por su eterna bondad y su su sonrisa siempre amigable. Gracias también a quienes rodearon constantemente a mi madre y hermanos: familiares, amigos, las tías (y tíos) Vargas, sobrinos y primos. El solo hecho de saber que mi madre estaba o estuvo con alguno de ellos cada vez que me contaba algo de lo que hacia, me tranquilizaba y me hacia olvidar por un momento de lo triste que es no estar a su lado para compartir tantos momentos importantes que me perdí por estar lejos de ellos, intentando conseguir un título que no me pertenece solo a mí.

Por último y sin duda, los agradecimientos mas importantes son para mi esposa e hijos: Gabriela y Daniel. Gracias Carol por compartir conmigo este largo proceso, tu presencia y compañía ha sido fundamental en todos los aspectos, agradezco profundamente tu apoyo y paciencia en el desarrollo de este trabajo. Son ellos por los que era impensable rendirse o dejar atrás algo que durante mucho tiempo pareció una meta lejana e incierta. También aprovecho para pedirles disculpas por gastar gran parte de mi tiempo libre, parte de mi atención y concentración en el desarrollo de algoritmos, lineas de código, solución de innumerables inconvenientes o cualquier otro aspecto relacionado con el doctorado, el cual nunca supe con certeza como compartir con ustedes. Gracias hijos por recordarme lo divertido que es jugar a cualquier cosa, desordenar todo sin importar las consecuencias y sobre todo no hacerle caso a la mamá. Gracias por los grandes e inolvidables momentos que hemos compartido en Barcelona, los dos más importantes cuando Millonarios y el Real Madrid ..., mentiras, el nacimiento de nuestros dos pequeños, a quienes pondré a leer algunas lineas de este trabajo cuando se porten mal y quiera castigarles, y en el supuesto que esto continuara, tendrían que explicarme alguno de los algoritmos propuestos de la Arquitectura de Hardware Auto-adaptable con Capacidad de Procesamiento en Paralelo que propuse en esta tesis doctoral. Este trabajo es para todos ustedes.

Agradezco a la persona que de manera anónima recuperó el morral que contenía el portátil con toda la información referente al trabajo de doctorado mientras inexplicablemente lo descuidé haciendo un trámite. Gracias a él o ella puedo escribir estas líneas y por lo tanto evitar una situación que recordaré como una anécdota y una lección más en la vida: "el gran susto del último día de tesis".

Moltes Gràcies Barcelona, Ciutat Comtal.

# Abstract

Education is what remains after one has forgotten what one has learned in school. La educación es lo que queda después de que uno ha olvidado lo que se ha aprendido en la escuela.

Albert Einstein (1879 - 1955)

This dissertation describes a novel unconventional self-adaptive hardware architecture with capacity for parallel processing. For scalability issues, this bioinspired architecture is based on a regular array of homogeneous cells. The proposed programmable architecture implements in a distributed way self-adaptive capabilities including self-placement and self-routing which, due to its intrinsic design, enable the development of systems with runtime reconfiguration, self-repair and/or fault tolerance capabilities. Additionally, this work defines the *configuration* and the *functional* units of the elementary cell, which implements the self-adaptive and parallel processing capabilities respectively.

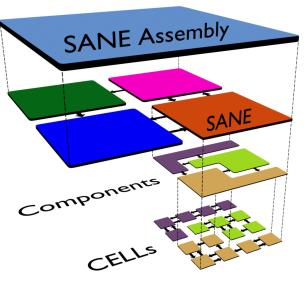

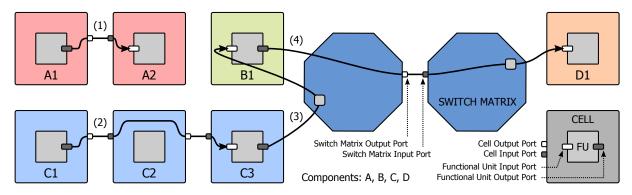

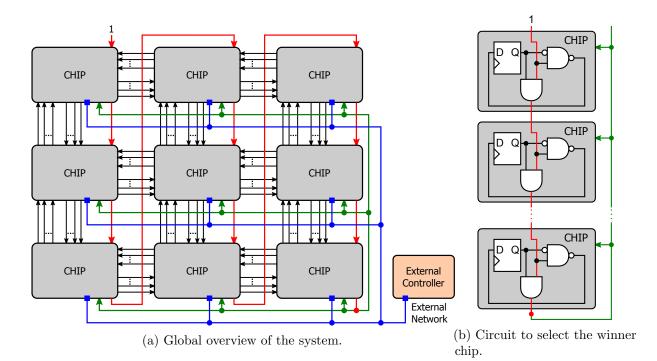

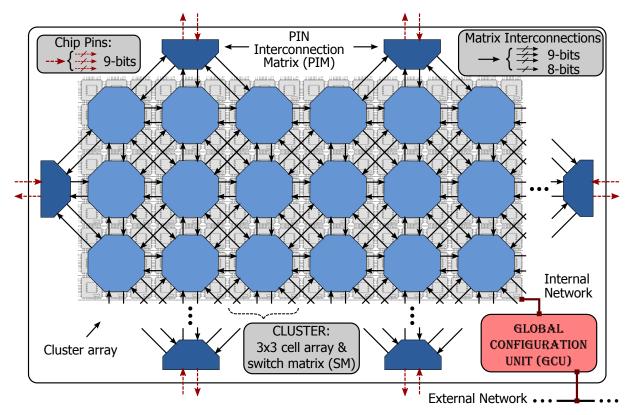

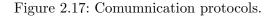

The physical implementation of this architecture is composed of two-layers, interconnected cells in the first level and interconnected switch and pin matrices in the second level. Several chips can be interconnected for enlarging the cell array. Any application scheduled to the system has to be organized in components, where each component is composed by one or more interconnected cells. The interconnection of cells inside a component is made at cell level (first layer), while the physical interconnections of components are made in the second layer. Additionally, two layers are defined as conceptual organization for the implementation of general purpose applications: the SANE and the SANE assembly. The SANE (Self-Adaptive Networked Entity) is composed by a group of components. This is the basic self-adaptive computing system. It has the ability to monitor its local environment and its internal computation process. The SANE ASSEMBLY (SANE-ASM) is composed by a group of interconnected SANEs.

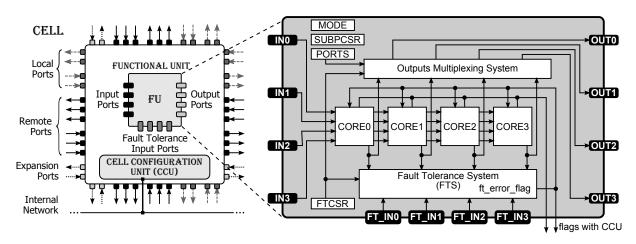

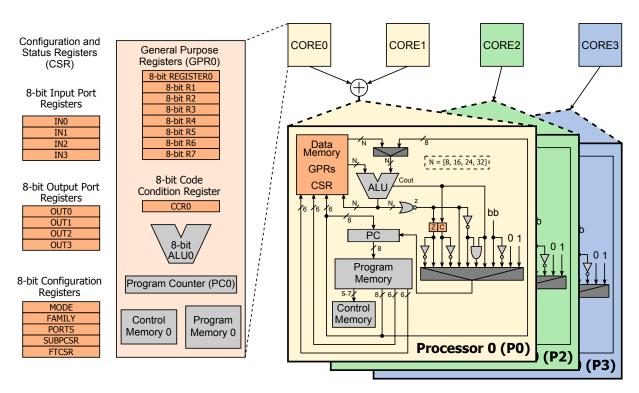

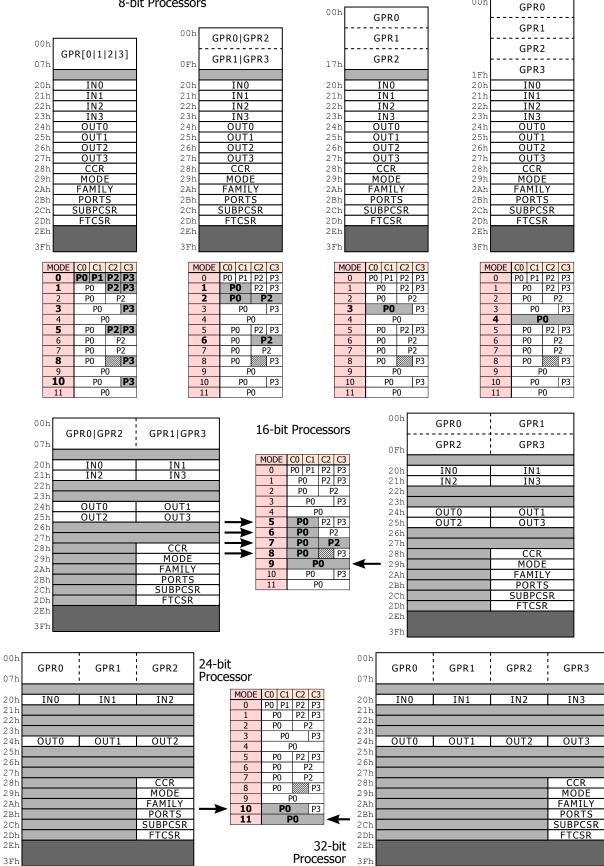

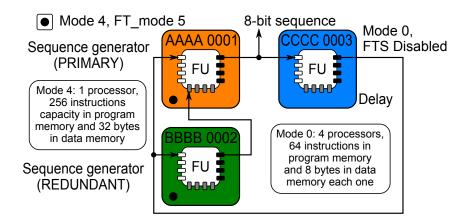

The processing capabilities of the cell are included in its Functional Unit (FU), which can be described as a four-core configurable multicomputer. The FU includes twelve programmable configuration modes , i.e., each cell permits to select from one to four processors working in parallel, with different size of program and data memories. The cores are grouped or not depending of the configuration mode, allowing program memory sizes of 64, 128, 192 or 256 instructions. Similarly, the data memory can be combined in width and length, achieving combinations for data processing of 8, 16, 24 and 32 bits.

The self-adaptive capabilities of the cell are executed mainly by the Cell Configuration Unit (CCU). The self-placement algorithm is responsible for finding out the most suitable position in the cell array to insert the new cell of a component. The self-routing algorithm is executed since the insertion of the second cell of a component, each time that the self-placement process ends. This algorithm allows interconnecting the ports of the FU of two cells through the cell ports. The self-placement and self-routing processes allow for performing complex functionality changes in real time, these processes endow the system with enhanced functionality, enabling the system

to change itself, this allows for the implementation of run-time self-configuration, without the need for any configuration manager. The absence of a centralized supervision system permits cells to perform some of the tasks in a distributed way.

The architecture proposed includes two mechanisms of fault tolerance. One of these is the Dynamic Fault Tolerance Scaling Technique, that has the ability to create and eliminate the redundant copies of the functional section of a specific application. This is possible due to the ability of runt-time self-configuration included in the architecture. The other mechanism of fault tolerance is a dedicated or static Fault Tolerance System. It provides redundant processing capabilities that are working continuously. When a failure in the execution of a program is detected, the processors of the cell are stopped and the self-elimination and self-replication processes start for the cell (or cells) involved in the failure. This cell(s) will be self-discarded for future self-placement processes.

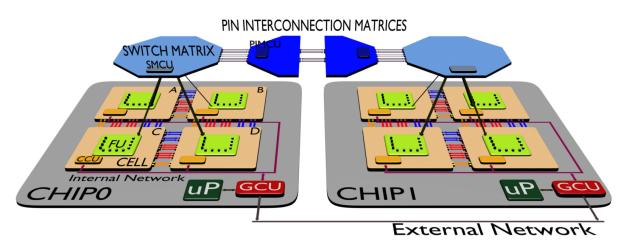

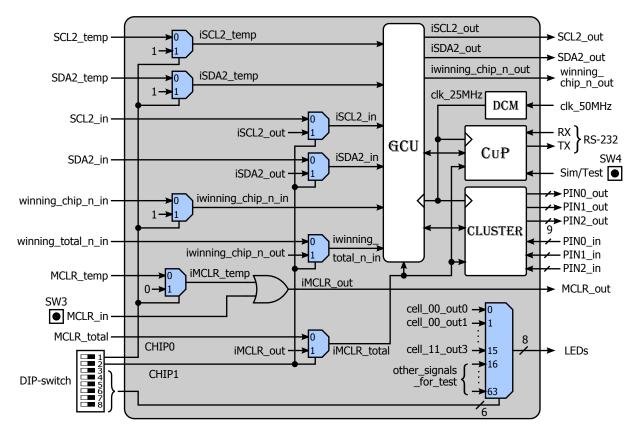

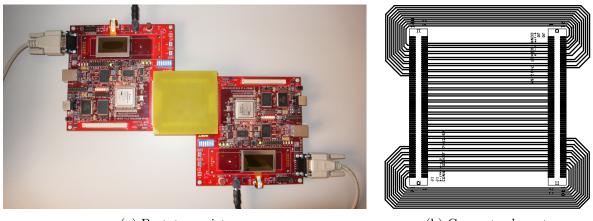

An FPGA-based prototype and a software tool have been built for demonstration purposes. The prototype includes all the self-adaptive capabilities described in this document. The prototype has been developed in two chips, each one is a Virtex4 Xilinx FPGA (XC4VLX60). The physical design includes the cell array together with a component-level routing system. Additionally a Control Microprocessor (C $\mu$ P) and other peripherals provide support for the implementation of general purpose applications in the prototype.

With the purpose of having a complete development system, the software tool SANE Project Developer (SPD) has been implemented. The SPD is an Integrated Development Environment (IDE) that allows generating the memory initialization data for the control microprocessor inside the prototype. The SPD allows the creation and edition of various files that describe the configuration of a SANE-ASM. The main (or top) file includes special SANE-ASM instructions (SASM files), which are equivalent to the assembler language for classic processors. The SPD allows the creation and edition of the SANE-ASM. In addition, the SPD automatically builds the final hexadecimal file with the configuration of the SANE-ASM that will be downloaded in the FPGA-based prototype.

# Resumen

No man should escape our universities without knowing how little he knows. Ningún hombre debe escapar de nuestras universidades sin saber lo poco que sabe. Julius Robert Oppenheimer (1904 – 1967)

Esta tesis doctoral describe una arquitectura de hardware auto-adaptable novedosa y no convencional con capacidad de procesamiento en paralelo. Por razones de escalabilidad, esta arquitectura bioinspirada está basada en una matriz regular de células homogéneas. La arquitectura propuesta es programable, e implementa de manera distribuida diversas capacidades auto-adaptables incluyendo el auto-emplazamiento y auto-enrutamiento, los cuales debido a su diseño intrínseco, permiten el desarrollo de sistemas reconfigurables en tiempo de ejecución, así como de sistemas auto-reparables y/o con capacidades de tolerancia a fallos. Adicionalmente este trabajo define las unidades de *configuración* y *funcional* de la célula, las cuales implementan las capacidades auto-adaptables y de procesamiento en paralelo respectivamente.

La implementación física de esta arquitectura esta compuesta de dos capas, que incluyen células interconectadas en el primer nivel y matrices de conmutación y pines en el segundo nivel. Las células ejecutan la funcionalidad básica del sistema. Diversos chips pueden ser interconectados para aumentar la matriz de células en el sistema. Cualquier aplicación que se quiera programar en el sistema debe estar organizada en componentes, donde cada componente está compuesto por una o más células interconectadas. La interconexión de células dentro de un componente es realizado en el mismo nivel de la matriz de células (primera capa), mientras que la interconexión de componentes es realizada en la segunda capa. Adicionalmente, se definen dos capas conceptuales que son usadas con propósitos organizativos en aplicaciones de propósito general, estas son: el SANE y el SANE-assembly. La *entidad auto-adaptable interconectada* o SANE (Self-Adaptive Networked Entity) está compuesta por un grupo de componentes. Este es el sistema de computación auto-adaptable básico, el cual tiene la habilidad de monitorizar su entorno local y su proceso de computación interno. El *Conjunto de SANEs* o SANE ASSEMBLY (SANE-ASM) esta compuesto por un grupo de SANEs interconectados.

Las capacidades de procesamiento de la célula están incluidas en su unidad funcional o Functional Unit (FU). Esta puede ser definida como un multicomputador configurable con cuatro núcleos. La FU tiene doce modos de configuración programables, por lo que cada célula permite seleccionar entre uno y cuatro procesadores trabajando en paralelo con diversas capacidades en las memorias de programa y datos. Los núcleos son agrupados o no dependiendo del modo de configuración, permitiendo que la memoria de programa pueda implementar 64, 128, 192 o 256 instrucciones. De manera similar, la memoria de datos puede ser expandida a lo largo y/o ancho, permitiendo procesamiento de datos para 8, 16, 24 y 32 bits.

Las capacidades auto-adaptables de la célula son ejecutadas principalmente por la unidad de configuración de la célula o Cell Configuration Unit (CCU). El algoritmo de auto-emplazamiento

es el encargado de encontrar la posición mas adecuada dentro de la matriz de células para insertar la nueva célula de un componente. El algoritmo de auto-enrutamiento es ejecutado a partir de la inserción de la segunda célula de un componente, cada vez que el algoritmo de auto-emplazamiento termina. Este algoritmo permite interconectar los puertos de las FU de dos células a través de los puertos de la célula. Los procesos de auto-emplazamiento y autoenrutamiento permiten realizar en tiempo real cambios funcionales complejos; estos procesos dotan al sistema de una mayor funcionalidad, permitiendo que el sistema cambie por si mismo, lo que permite la implementación de la auto-configuración en tiempo real, sin la necesidad de ningún gestor de configuración. La ausencia de un sistema de supervisión centralizado permite a las células realizar algunas de sus funciones de manera distribuida.

La arquitectura propuesta incluye dos mecanismos de tolerancia a fallos. Uno de estos es una técnica escalonada y dinámica de tolerancia a fallos, que tiene la habilidad de crear y eliminar copias redundantes de la unidad funcional (o de cómputo) de una aplicación específica. Esto es posible gracias a la capacidad de auto-configuración en tiempo real incluida en la arquitectura. El otro mecanismo de tolerancia a fallos es el Sistema de Tolerancia a Fallos dedicado o estático. Este provee capacidades de procesamiento redundante que están en funcionamiento continuamente. Cuando un fallo en la ejecución de un programa es detectado, los procesadores de la célula son detenidos y los procesos de auto-eliminación y auto-replicación se inician para la célula (o células) implicada en el fallo. Esta(s) célula(s) serán auto-descartadas para futuros procesos de auto-emplazamiento.

Se desarrolló un prototipo basado en FPGAs y una herramienta de software para comprobar la funcionalidad del sistema. El prototipo incluye todas las características de los sistemas autoadaptable descritas en este documento. El prototipo ha sido desarrollado en dos chips, cada uno es una FPGA Virtex4 de Xilinx (XC4VLX60). El diseño físico incluye el arreglo de células junto a un sistema de enrutamiento a nivel de componentes. Adicionalmente incluye un microprocesador de control o CµP (Control Microprocessor) y otros periféricos, que dan soporte a la implementación de aplicaciones de propósito general en el prototipo.

Con el propósito de tener un sistema de desarrollo completo, la herramienta de software SPD (SANE Project Developer) ha sido desarrollada. El SPD es un ambiente integrado de desarrollo (Integrated Development Environment o IDE) que permite generar y descargar la memoria de inicialización de datos para el CµP dentro del prototipo. El SPD permite la creación y edición de archivos que describen la configuración de un SANE-ASM. El archivo principal incluye instrucciones especiales para el SANE-ASM (archivos SASM), el cual es equivalente al lenguaje de ensamblador de un procesador clásico. El SPD permite la creación y edición de toda la información relacionada con el SANE-ASM, así mismo construye de manera automática el archivo hexadecimal de configuración que será descargado a la FPGA del prototipo.

# Contents

| Ackno                                                                                    | vledgements / Agradecimientos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | vii                                                                                                                                  |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{Abstr}$                                                                         | ct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | xi                                                                                                                                   |

| Resu                                                                                     | en x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | iii                                                                                                                                  |

| Conte                                                                                    | ts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\mathbf{x}\mathbf{v}$                                                                                                               |

| List o                                                                                   | Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xi                                                                                                                                   |

| List o                                                                                   | Figures xx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | iii                                                                                                                                  |

| Listin                                                                                   | s x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | xv                                                                                                                                   |

| <ol> <li>Int</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>1.5</li> </ol> | Adaptive and Bioinspired Systems         Self-Adaptive capabilities in the proposed architecture         Architectures for parallel computing         Preliminary work         1.4.1         POEtic         1.4.2         PERPLEXUS         State of the art         1.5.1         Confetti         1.5.2         eDNA         1.5.3         Self-routing reconfigurable fault-tolerant cell array         1.5.4         CEDAR         1.5.5         Amorphous         1.5.6         Cell Processors - Sony-Toshiba-IBM team         1.5.7         ADRES         1.5.8         MorphoSys         1.5.9         REMARC         1.5.10         XPP (eXtreme Processing Platform)         1.5.11         The SANE Virtual Processor (SVP)         1.5.12         HTHREADS         Architecture Overview and Contributions         1.6.1         Scalability | $\begin{array}{c} 1 \\ 1 \\ 2 \\ 2 \\ 3 \\ 3 \\ 4 \\ 4 \\ 4 \\ 4 \\ 4 \\ 5 \\ 5 \\ 5 \\ 5 \\ 6 \\ 6 \\ 7 \\ 7 \\ 8 \\ 8 \end{array}$ |

| $1.7 \\ 1.8$                                                                             | Document Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9<br>9                                                                                                                               |

| <b>2</b> | Syst       | em Architecture 11                                              |

|----------|------------|-----------------------------------------------------------------|

|          | 2.1        | Conceptual organization                                         |

|          | 2.2        | Overview for the configuration of an application                |

|          |            | 2.2.1 Connection of cells                                       |

|          | 2.3        | Overview of System Architecture                                 |

|          | 2.4        | Chip Architecture                                               |

|          | 2.5        | Global Configuration Unit                                       |

|          | 2.6        | Cluster                                                         |

|          | 2.7        | Cell Architecture                                               |

|          | 2.1        | 2.7.1 Functional Unit (FU)                                      |

|          |            | 2.7.2 Cell Configuration Unit (CCU)                             |

|          | 2.8        | Switch Matrix         17                                        |

|          | 2.0<br>2.9 | Pin Interconnection Matrix                                      |

|          |            | Expansion Signals                                               |

|          | 2.10       | 2.10.1 Global Signals for Self-routing Process                  |

|          | 0.11       |                                                                 |

|          | 2.11       | Internal and External Networks                                  |

|          |            | 2.11.1 Communication Interface                                  |

|          |            | 2.11.2 Data Transmission   23                                   |

|          |            | 2.11.3 Comparison Process    23                                 |

|          |            | Communication Protocol for Internal Network                     |

|          |            | Communication Protocol for External Network                     |

|          |            | Prototype architecture                                          |

|          | 2.15       | Conclusions                                                     |

| 3        | Fun        | ctional Unit Architecture 31                                    |

| Ŭ        | 3.1        | General Description                                             |

|          | 3.2        | FU Ports                                                        |

|          | 3.3        | Architecture of Processors       33                             |

|          | 0.0        | 3.3.1 Cores                                                     |

|          |            | 3.3.2 Processor                                                 |

|          |            | 3.3.3 Configuration modes                                       |

|          | 3.4        | Data Memory   36                                                |

|          | 0.4        | 3.4.1 General Purpose Registers (GPRs)                          |

|          |            |                                                                 |

|          |            | 3.4.2 Configuration and Status Registers (CSRs) 36              |

|          | 0 5        | 3.4.3 Data Memory Map                                           |

|          | 3.5        | Program Memory and Instructions Set                             |

|          | 3.6        | Output Multiplexing System       37         Data (DTR)       37 |

|          | 3.7        | Fault Tolerance System (FTS)    37                              |

|          |            | 3.7.1 Fault Tolerance Input Ports                               |

|          |            | 3.7.2 Fault Tolerance Modes                                     |

|          |            | 3.7.3 Configuration of FTS 41                                   |

|          | 3.8        | Conclusions                                                     |

| 4        | Self-      | Adaptive Processes 43                                           |

| -        | 4.1        | Summary                                                         |

|          | 4.2        | Previous Considerations                                         |

|          | 4.3        | Initial State, Cell Address and Connection Tables               |

|          | 4.4        | Creation of Components in a Chip                                |

|          | 4.5        | Self-Placement Process                                          |

|   |                                            | 4.5.1 Self-Placement of the First Cell of a Component                                                          | 47 |  |

|---|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|----|--|

|   |                                            | 4.5.2 Self-Placement of Other Cells of a Component                                                             | 47 |  |

|   | 4.6                                        | Self-Routing Process                                                                                           | 49 |  |

|   | 4.7 Self-Routing at Cell Level             |                                                                                                                |    |  |

|   |                                            | 4.7.1 Configuration of source and target cells for cell connections                                            | 49 |  |

|   |                                            | 4.7.2 Expansion Process at Cell Level                                                                          | 50 |  |

|   | 4.8                                        | Self-Routing at Component Level                                                                                | 53 |  |

|   |                                            | 4.8.1 Configuration of Source and Target Cells for Components Connections                                      | 54 |  |

|   | 4.8.2 Expansion Process at Component Level | 54                                                                                                             |    |  |

|   | 4.9                                        | Self-Elimination and Self-Replication                                                                          | 58 |  |

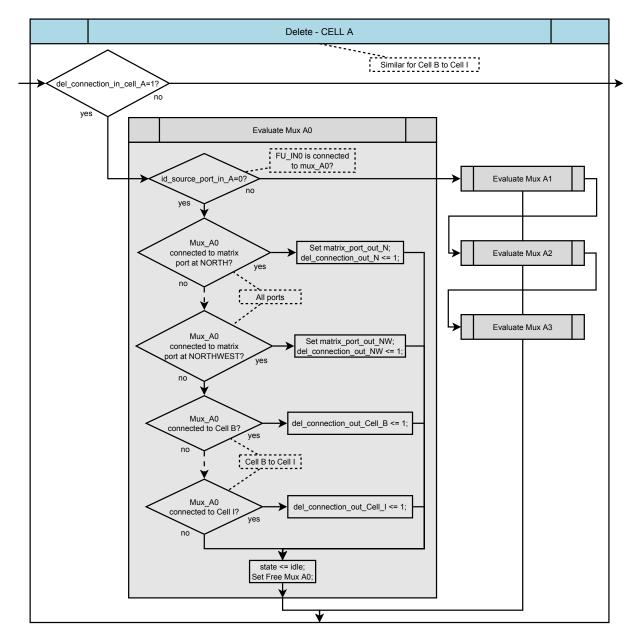

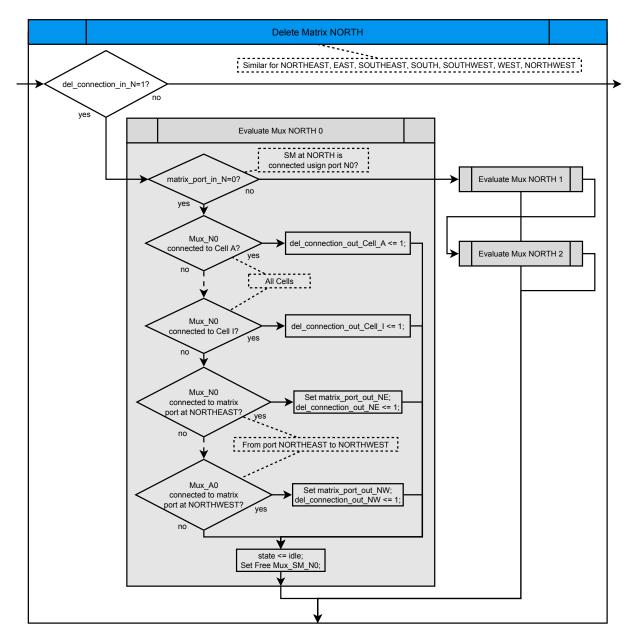

|   |                                            | 4.9.1 Elimination of a Cell inside a Chip                                                                      | 58 |  |

|   | 4.10                                       | Self-Configuration by means of Subprocesses                                                                    | 59 |  |

|   |                                            | 4.10.1 Delete a Component inside a Chip                                                                        | 59 |  |

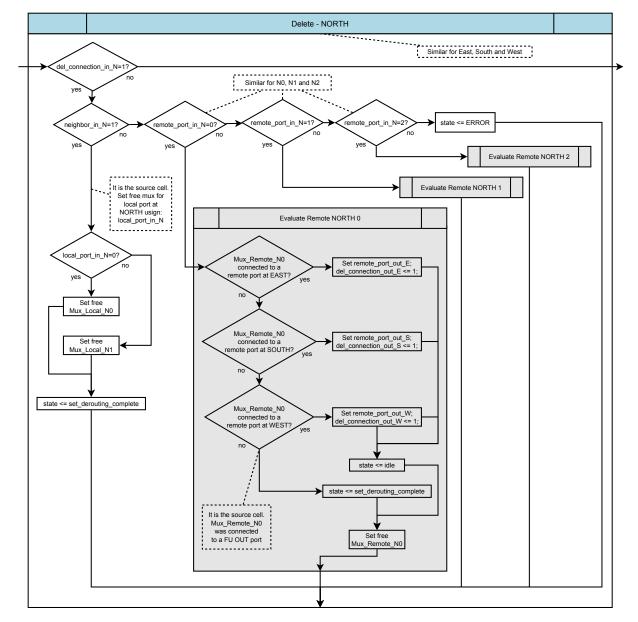

|   | 4.11                                       | Self-Derouting Process                                                                                         | 59 |  |

|   |                                            |                                                                                                                | 60 |  |

|   |                                            |                                                                                                                | 60 |  |

|   |                                            | • • • • • • • • • • • • • • • • • • •                                                                          | 61 |  |

|   | 4.12                                       |                                                                                                                | 63 |  |

|   |                                            |                                                                                                                |    |  |

| 5 |                                            | elopment and Implementation of Self-adaptive Applications with Parallel                                        |    |  |

|   | Pro                                        |                                                                                                                | 35 |  |

|   | 5.1                                        | 1 0                                                                                                            | 65 |  |

|   | 5.2                                        | <b>0 11</b>                                                                                                    | 66 |  |

|   | 5.3                                        | *                                                                                                              | 68 |  |

|   |                                            |                                                                                                                | 68 |  |

|   |                                            | 5.3.2 Connection of Components                                                                                 | 69 |  |

|   |                                            | 5.3.3 Delete Components                                                                                        | 70 |  |

|   |                                            | 5.3.4 Write Functional Unit Program Memories and Configuration Registers                                       | 71 |  |

|   |                                            | 5.3.5 Restart, Enable and Disable Processors                                                                   | 73 |  |

|   |                                            | 5.3.6 System in "Wait" State for Runtime Self-configuration                                                    | 74 |  |

|   |                                            | 5.3.7 Runtime Self-configuration by means of Subprocesses                                                      | 75 |  |

|   |                                            | 5.3.8 Static Fault Tolerance Configuration                                                                     | 76 |  |

|   | 5.4                                        | Development of Applications                                                                                    | 78 |  |

|   | 5.5                                        |                                                                                                                | 81 |  |

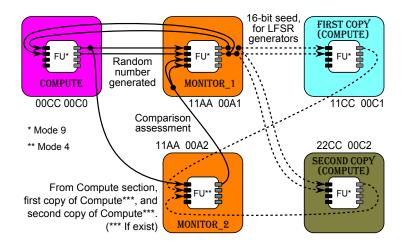

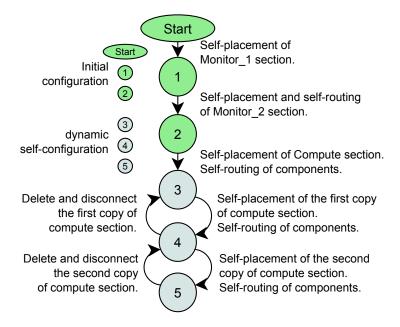

|   |                                            | 5.5.1 Dynamic Fault-Tolerance Structure                                                                        | 81 |  |

|   |                                            | 5.5.2 Description of the application                                                                           | 82 |  |

|   | 5.6                                        | Application Example: Static Fault-Tolerance                                                                    | 84 |  |

|   | 5.7                                        | Conclusions                                                                                                    | 85 |  |

| _ |                                            |                                                                                                                |    |  |

| 6 |                                            |                                                                                                                | 87 |  |

|   | 6.1                                        |                                                                                                                | 87 |  |

|   |                                            | · · ·                                                                                                          | 87 |  |

|   |                                            | • •                                                                                                            | 88 |  |

|   |                                            | e de la construcción de la constru | 88 |  |

|   |                                            |                                                                                                                | 89 |  |

|   |                                            |                                                                                                                | 89 |  |

|   |                                            |                                                                                                                | 90 |  |

|   | 6.2                                        |                                                                                                                | 90 |  |

|   |                                            | 6.2.1 Hardware                                                                                                 | 90 |  |

|   | 6.3                                 | Firmware                                                                      | 92         |  |

|---|-------------------------------------|-------------------------------------------------------------------------------|------------|--|

|   | 6.4                                 | Software                                                                      | 92         |  |

|   | 6.5 Synthesis Process for Prototype |                                                                               |            |  |

|   | 6.6                                 | Conclusions                                                                   | 94         |  |

| 7 | Con                                 | clusions and Future Work                                                      | 97         |  |

|   | 7.1                                 | Conclusions                                                                   | 97         |  |

|   |                                     | 7.1.1 About System Architecture                                               | 98         |  |

|   |                                     | 7.1.2 About the Self-Adaptive Processes                                       | 99         |  |

|   |                                     | 7.1.3 About Integrated Development System                                     | 100        |  |

|   | 7.2                                 | Future Work                                                                   | 100        |  |

| Δ | Inst                                | ructions Set for Functional Unit Processors                                   | 103        |  |

|   |                                     | Instructions Format                                                           | 103        |  |

|   |                                     | Instructions Set                                                              |            |  |

| ъ |                                     |                                                                               | 118        |  |

| В |                                     | a Memory Registers of Functional Unit Processors<br>Abbreviations             | <b>115</b> |  |

|   | B.2                                 | Input Ports Registers                                                         |            |  |

|   | B.3                                 | Output Ports Registers                                                        |            |  |

|   | B.4                                 | Code Condition Register                                                       |            |  |

|   | B.5                                 | Mode Register                                                                 |            |  |

|   | B.6                                 | Family Register                                                               |            |  |

|   | B.7                                 | Output Ports Configuration Register (PORTS)                                   |            |  |

|   | B.8                                 | Subprocess Configuration and Status Register (SUBPCSR)                        |            |  |

|   | B.9                                 | Fault Tolerance Configuration and Status Register (FTCSR)                     |            |  |

| С | Floy                                | w Diagrams for Self-adaptive Processes in System                              | 127        |  |

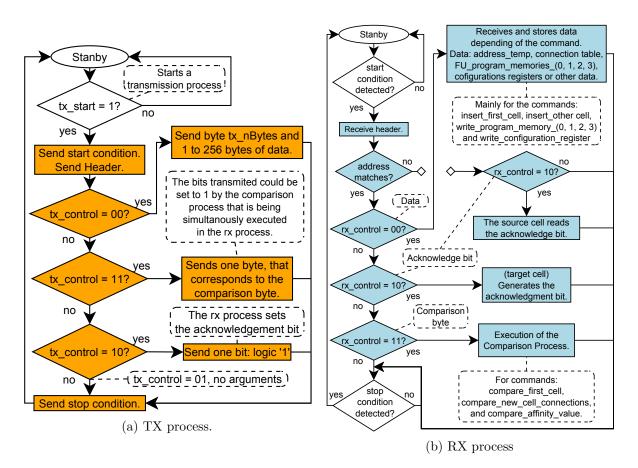

| - |                                     | Transmission and Reception in Cell                                            |            |  |

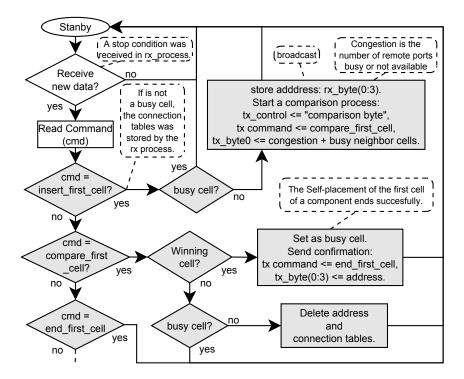

|   | C.2                                 | Self-Placement Processes in CCU                                               |            |  |

|   |                                     | C.2.1 Flow Diagram for Insertion of First Cell of a Component                 |            |  |

|   |                                     | C.2.2 Flow Diagram for Insertion of Other Cells of a Component                | 128        |  |

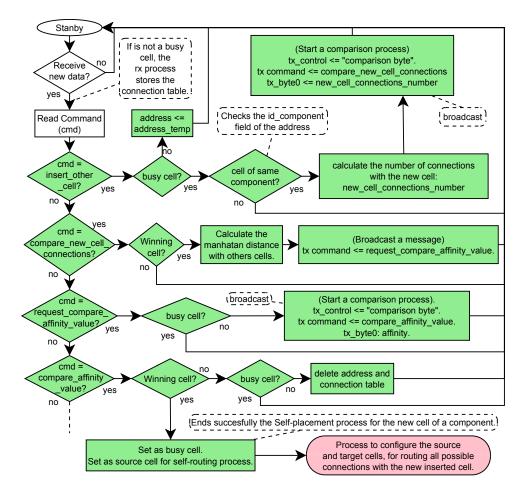

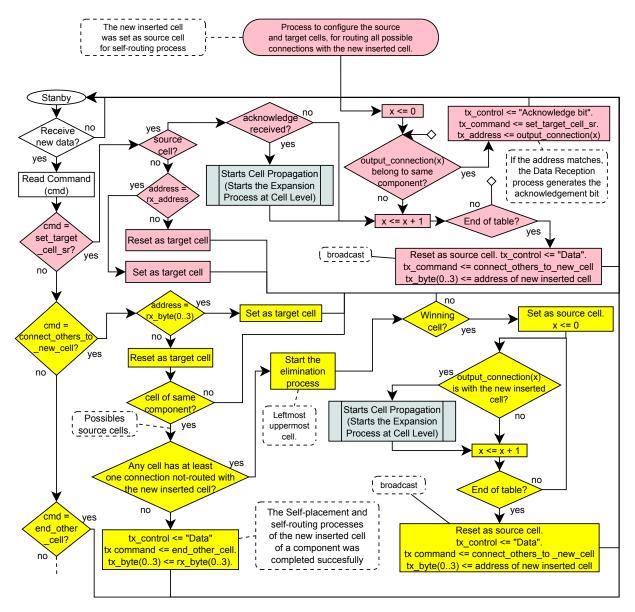

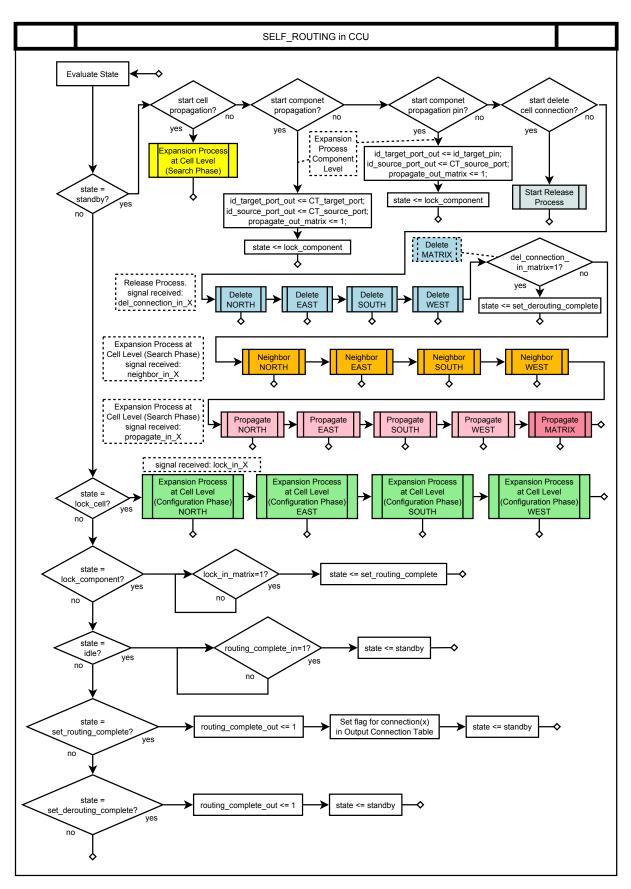

|   | C.3                                 | Self-Routing Processes in CCU                                                 | 130        |  |

|   |                                     | C.3.1 Flow Diagram to select the Source and Target cells before the Expansion |            |  |

|   |                                     | Process at Cell Level                                                         | 130        |  |

|   |                                     | C.3.2 Main Flow Diagram in CCU                                                | 131        |  |

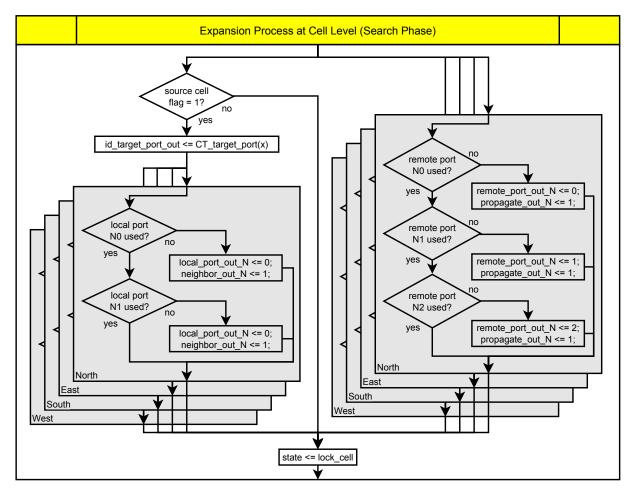

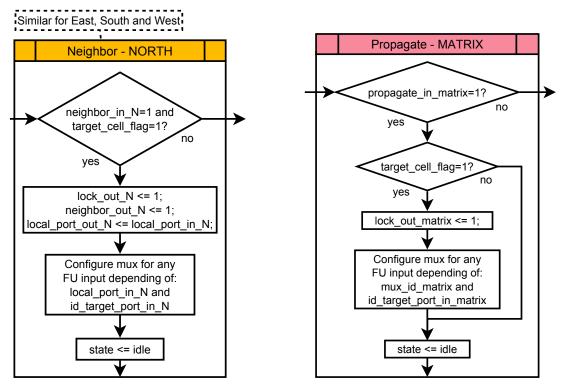

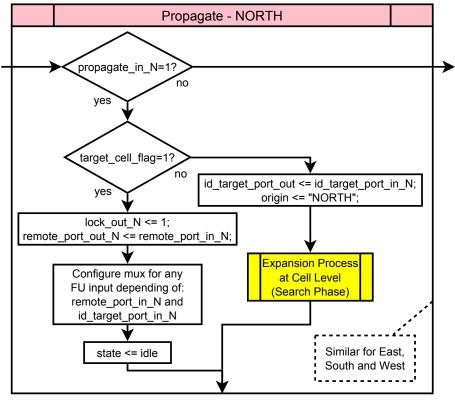

|   |                                     | C.3.3 Expansion Process at Cell Level - Search Phase                          |            |  |

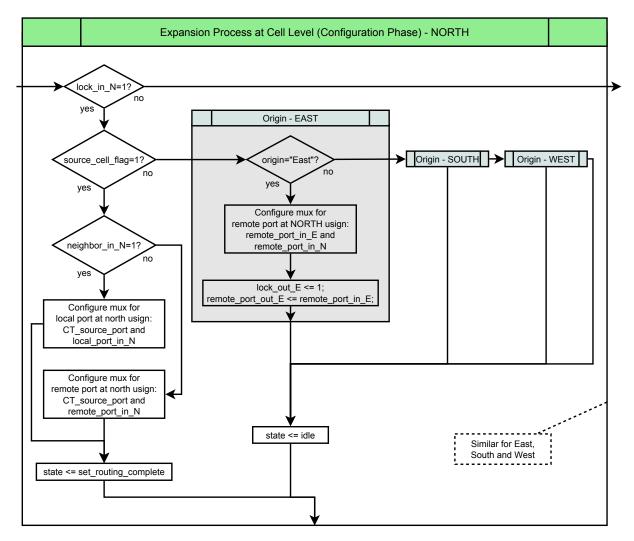

|   |                                     | C.3.4 Expansion Process at Cell Level - Configuration Phase                   |            |  |

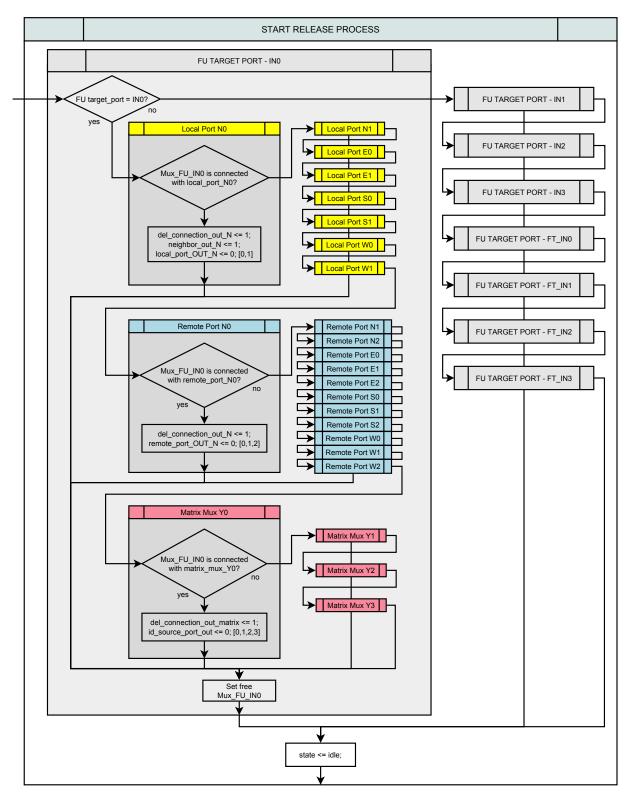

|   |                                     | C.3.5 Release Process at Cell Level                                           |            |  |

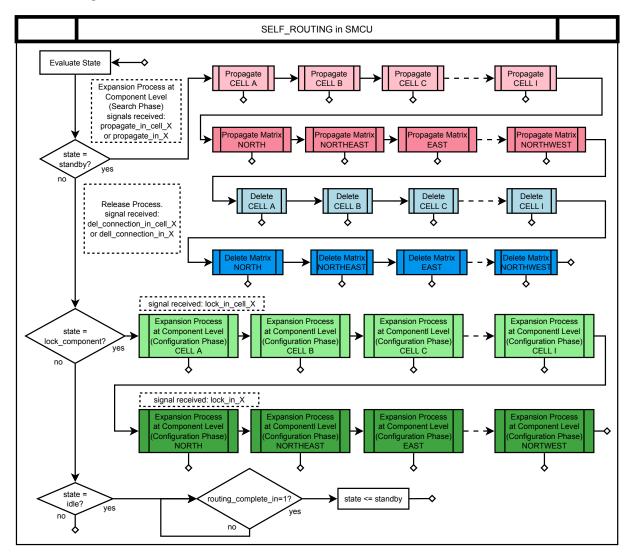

|   | C.4                                 | Self-Routing Processes in SMCU                                                |            |  |

|   |                                     | C.4.1 Expansion Process at Component Level - Search Phase                     |            |  |

|   |                                     | C.4.2 Expansion Process at Component Level - Configuration Phase              |            |  |

|   |                                     | C.4.3 Release Process at Component Level                                      |            |  |

|   | C.5                                 | Conclusions                                                                   | 145        |  |

| D |                                     | NE Project Developer (SPD)                                                    | 147        |  |

|   |                                     | Description                                                                   | 147        |  |

|   | D.2                                 | Files Edition                                                                 | 149        |  |

|   |                                     | D.2.1 Assembler Files                                                         | 150        |  |

|   |                                     | D.2.2 SANE Assembler Files                                                    | 151        |  |

|              | D.3    | Functions                                                          | 52  |

|--------------|--------|--------------------------------------------------------------------|-----|

|              |        | D.3.1 File Menu                                                    | 52  |

|              |        | D.3.2 Edit Menu                                                    | .52 |

|              |        | D.3.3 Project Menu                                                 | .53 |

|              |        | D.3.4 Tool Menu                                                    |     |

|              |        | D.3.5 View Menu                                                    | .56 |

|              |        | D.3.6 Communication Menu                                           | .56 |

|              |        | D.3.7 Help and Admin Menus                                         | .56 |

|              | D.4    | Downloading Project to Prototype                                   |     |

|              |        | D.4.1 Communication Test                                           |     |

|              |        | D.4.2 Clear Memory                                                 | .58 |

|              |        | D.4.3 Write Memory                                                 |     |

|              |        | D.4.4 Read Memory                                                  | .59 |

|              | D.5    | Conclusions                                                        | .60 |

| _            |        |                                                                    |     |

| $\mathbf{E}$ | List   |                                                                    | .61 |

|              | E.1    | Listings for Dynamic Fault Tolerance Scaling Application Example 1 | 63  |

|              | E.2    | Listings for Static Fault Tolerance Application Example            | .79 |

|              | E.3    | Conclusions                                                        | 84  |

| G            | lossai | y 1                                                                | .87 |

| Re           | efere  | lces 1                                                             | 94  |

# List of Tables

| 1.1                             | Flynn's taxonomy: classification of computer architectures with respect to its parallelism.                                                                                                                    | 3                          |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| $2.1 \\ 2.3$                    | Commands list for Internal Network                                                                                                                                                                             | 26<br>28                   |

| 3.1<br>3.2<br>3.3<br>3.4        | Configuration modes: active components for processors and memory distribution<br>Output Multiplexing System operating table                                                                                    | 35<br>39<br>40<br>42       |

| $4.1 \\ 4.2$                    | Description of expansion port signals used by the Expansion Process at Cell Level.<br>Description of expansion port signals used by the Expansion Process at component                                         | 50                         |

| 4.3                             | level                                                                                                                                                                                                          | $\frac{55}{62}$            |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | List of SASM or high-level instructions for initial and run-time configuration Syntax and format for create_component instruction                                                                              | 67<br>68<br>69<br>70       |

| 5.6                             | Memories and Configuration Register                                                                                                                                                                            | 72                         |

| 5.7<br>5.8<br>5.9<br>5.10       | SASM file                                                                                                                                                                                                      | 73<br>74<br>75<br>76<br>84 |

| $6.1 \\ 6.2 \\ 6.3 \\ 6.4$      | List of VHDL files for hardware implementation of prototype List of C files for firmware section of prototype (Control Microprocessor) List of C# files developed for implementation of SANE Project Developer | 92<br>92<br>94<br>95       |

| A.1<br>A.2<br>A.3               | Nomenclature for processor operations                                                                                                                                                                          | 105<br>105<br>106          |

| B.1                             | Abbreviations for bits of Data Memory registers                                                                                                                                                                | 115                        |

| D.1 | Relation of files for SANE Project Developer.                     | 150 |

|-----|-------------------------------------------------------------------|-----|

| D.2 | Description of fields for XMODEM based protocol                   | 157 |

| D.3 | Example of data flow for Communication Test with prototype        | 158 |

| D.4 | Example of data flow for Clear Memory in prototype.               | 158 |

| D.5 | Example of data flow for Write Memory in prototype.               | 159 |

| D.6 | Example of data flow for Read Memory from prototype               | 160 |

| E.1 | Listings for Dynamic Fault Tolerance Scaling application example. | 162 |

|     | Listings for Static Fault Tolerance application example.          |     |

# List of Figures

| 2.1  | Conceptual layers of the self-adaptive hardware architecture                                                                                                                                           | 2 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.2  | Possible connection between Functional Unit ports of two cells                                                                                                                                         | 2 |

| 2.3  | System architecture                                                                                                                                                                                    | 3 |

| 2.4  | Organization of the proposed architecture inside a chip                                                                                                                                                | 5 |

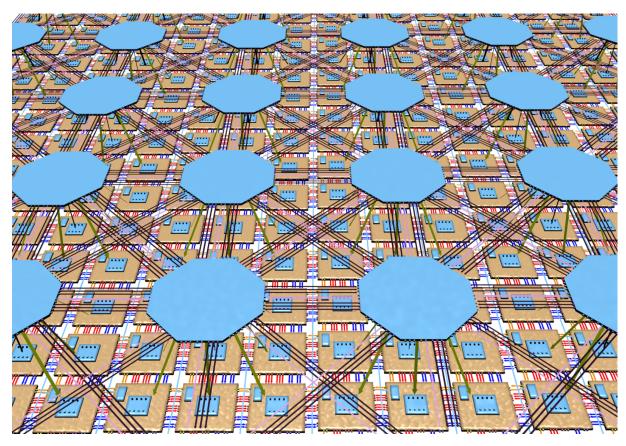

| 2.5  | System architecture: 3D representation of an array of clusters                                                                                                                                         | 5 |

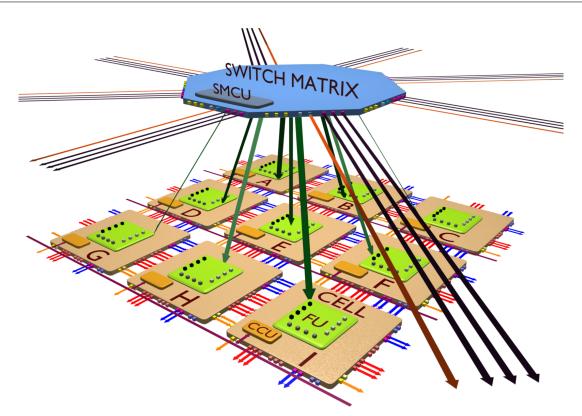

| 2.6  | Cluster: 3x3 cell array and switch matrix                                                                                                                                                              | 3 |

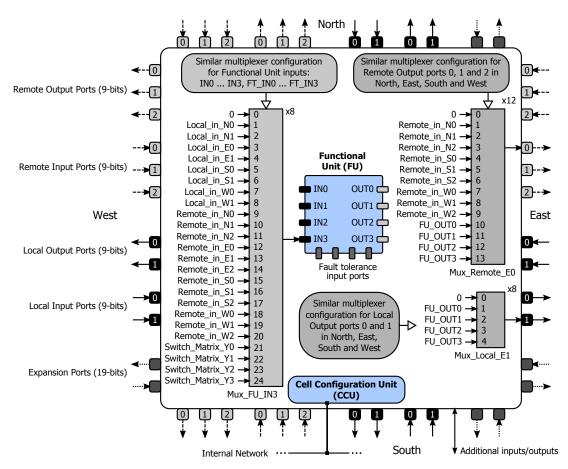

| 2.7  | Cell architecture: internal hardware and ports                                                                                                                                                         | 3 |

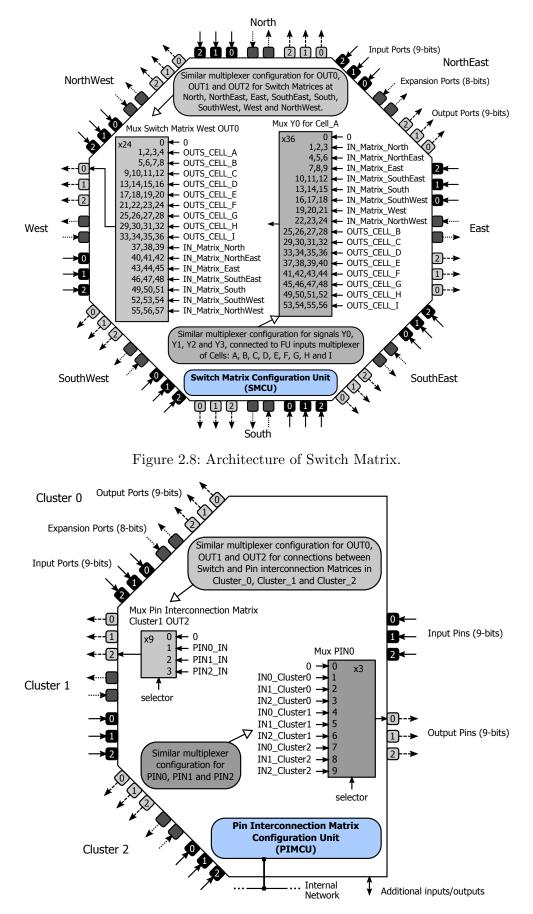

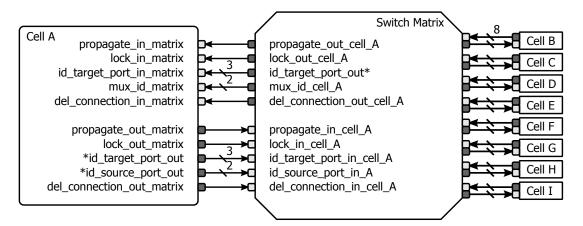

| 2.8  | Architecture of Switch Matrix                                                                                                                                                                          | ) |

| 2.9  | Architecture of Pin Interconnection Matrix                                                                                                                                                             | ) |

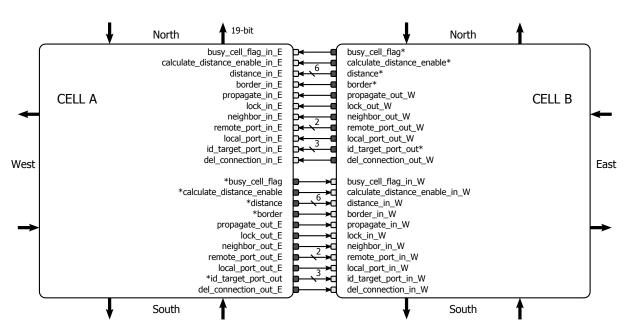

|      | Expansion signals between $cells^1$                                                                                                                                                                    | 1 |

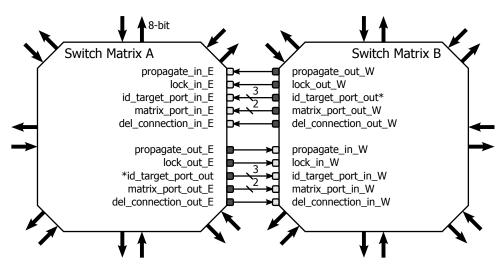

| 2.11 | Expansion signals between cell and Switch Matrix <sup>1</sup> . $\ldots \ldots \ldots$ |   |

|      | Expansion signals between Switch Matrices (including Pin Interconnection Matrix) <sup><math>1</math></sup> . 2.                                                                                        |   |

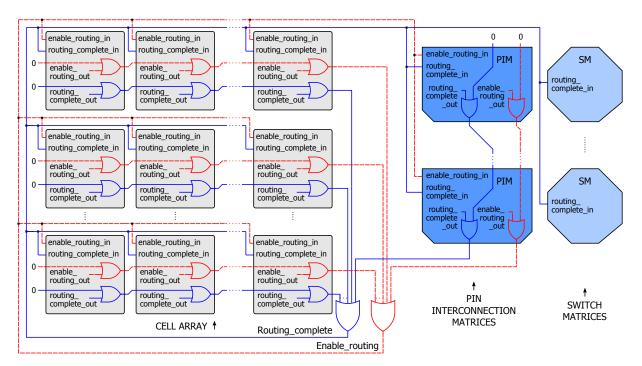

|      | Routing signals implementation. 22                                                                                                                                                                     |   |

|      | Internal Network implementation                                                                                                                                                                        |   |

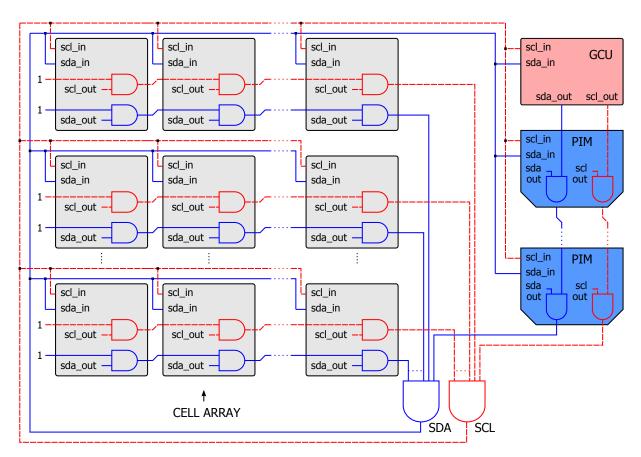

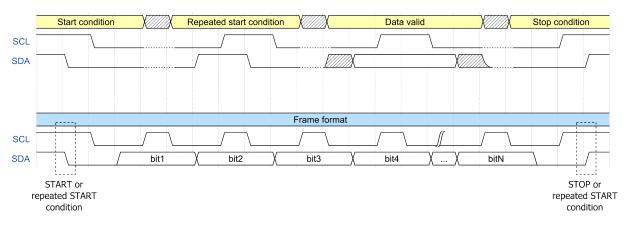

|      | Considerations for Internal and External Networks                                                                                                                                                      |   |

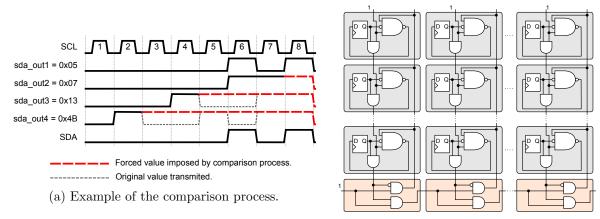

|      | Comparison process                                                                                                                                                                                     |   |

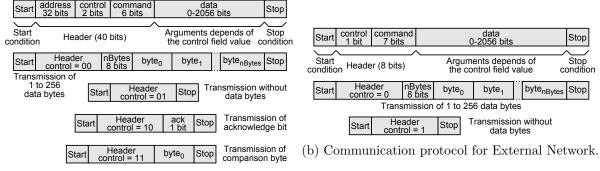

|      | Comumication protocols                                                                                                                                                                                 |   |

|      | 3D representation of the prototype architecture                                                                                                                                                        |   |

|      | Block diagram of a chip in prototype                                                                                                                                                                   |   |

| 2.20 | Prototype implementation                                                                                                                                                                               | ) |

| 3.1  | Functional Unit architecture.    32                                                                                                                                                                    | 2 |

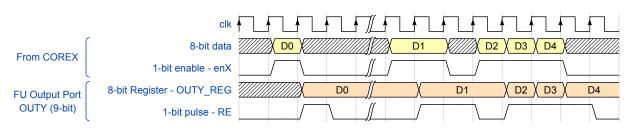

| 3.2  | Read Enable pulse example.    33                                                                                                                                                                       | 3 |

| 3.3  | Construction of processors based on cores                                                                                                                                                              | 1 |

| 3.4  | Data memory map for 8, 16, 24 and 32 bit processors                                                                                                                                                    | 3 |

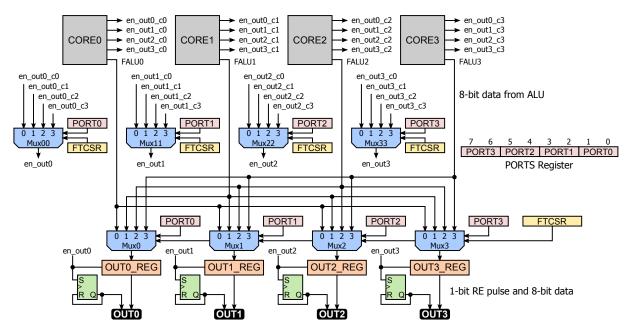

| 3.5  | Block diagram of Output Multiplexing System                                                                                                                                                            | ) |

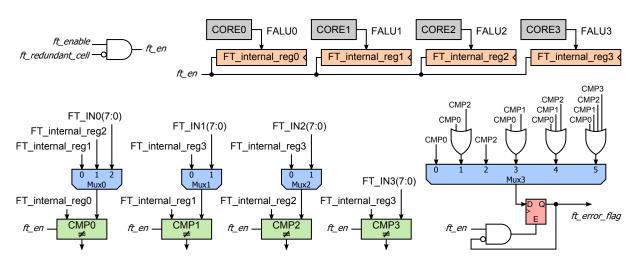

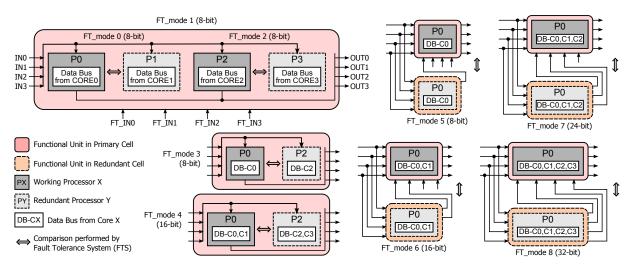

| 3.6  | Fault Tolerance System.    40                                                                                                                                                                          | ) |

| 3.7  | FT_modes for processors in Functional Unit                                                                                                                                                             | 1 |

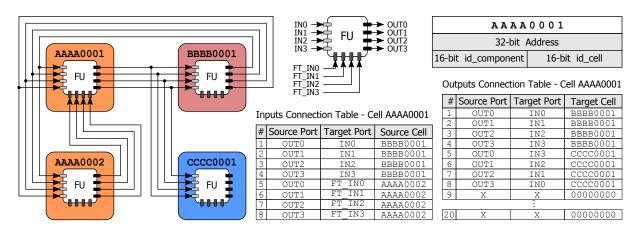

| 4.1  | Address and Connection Tables example for cell AAAA0001                                                                                                                                                | 5 |

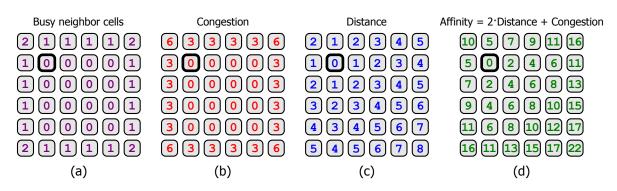

| 4.2  | Example of <i>busy_neighbor_cells</i> , <i>congestion</i> , <i>distance</i> and <i>affinity</i>                                                                                                        | 3 |

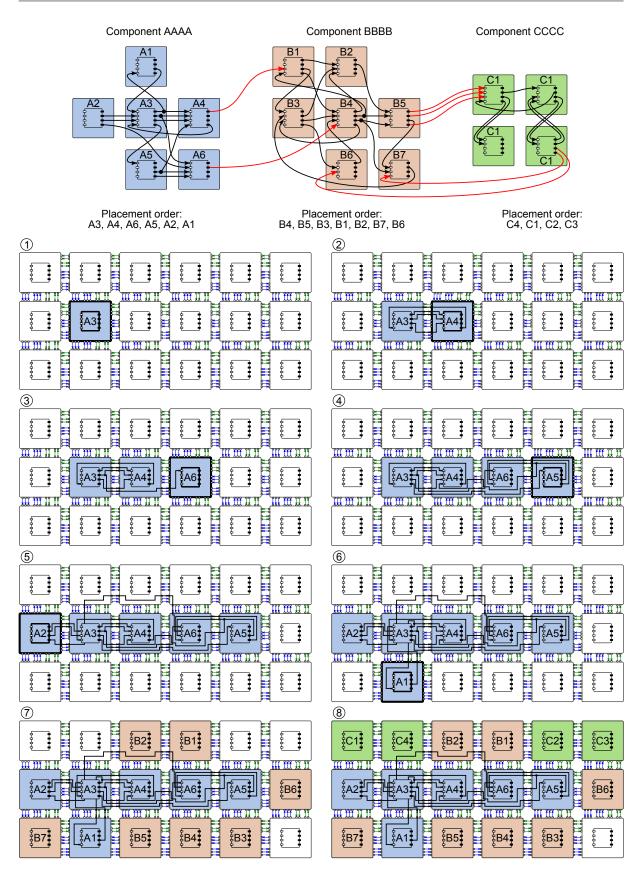

| 4.3  | Example of the self-placement algorithm implementation for three components                                                                                                                            |   |

|      | in an array of two clusters (6x3 cell array). The resources used by self-routing                                                                                                                       |   |

|      | algorithm are shown only for component AAAA                                                                                                                                                            | 3 |

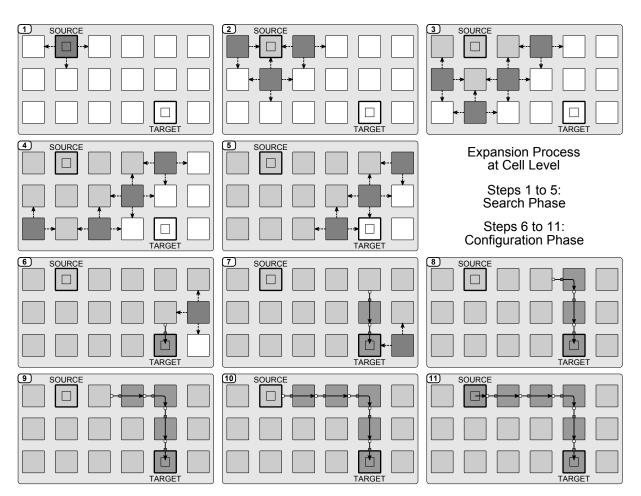

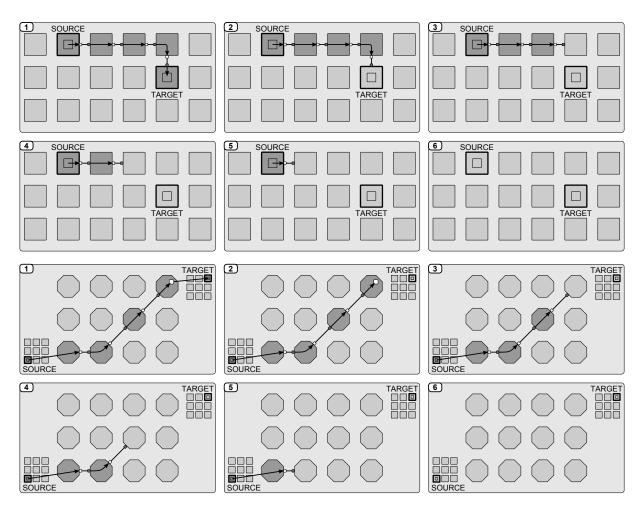

| 4.4  | Example of Expansion Process at Cell Level                                                                                                                                                             | 2 |

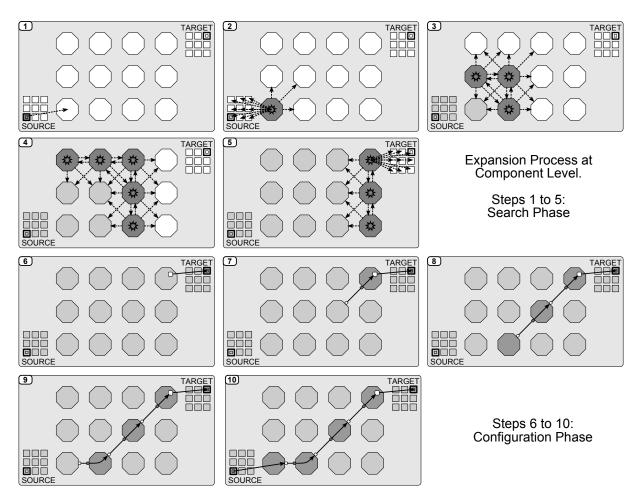

| 4.5  | Example of Expansion Process at component level                                                                                                                                                        | 7 |

| 4.6  | Example of Release Process at Cell and Component Level 6                                                                                                                                               | 1 |

| 5.1  | Component interconnection for the dynamic fault tolerance application 85                                                                                                                               | 3 |

| 5.2<br>5.3                                                  | Sequence of activities. The processes executed by the system are represented by the text over the arrows. All cells are free in the "start" state                                                                                                  | 83<br>85                 |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A.1                                                         | Instructions format.                                                                                                                                                                                                                               | 104                      |

| C.1<br>C.2<br>C.3<br>C.4                                    | Self-placement algorithm for the insertion of the first cell of a component I<br>Self-placement algorithm for other cells of a component (from the second) I<br>Configuration of source and target cell for execution of Expansion Process at Cell | 128<br>129<br>129<br>130 |

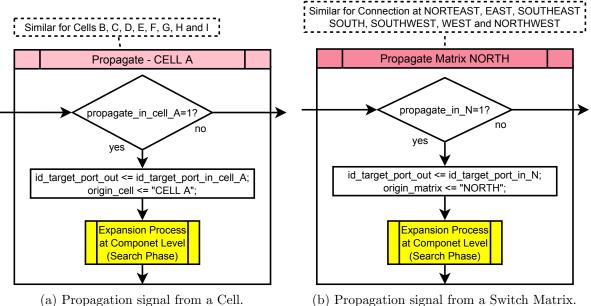

| $\begin{array}{c} \mathrm{C.5} \\ \mathrm{C.6} \end{array}$ | Main flow diagram for Expansion and Release processes in Cell Configuration Unit.<br>Flow diagram for the propagation of Signals in the Search Phase of the Expansion                                                                              |                          |

| C.7                                                         | Process at Cell Level. 1<br>Flow diagrams for Expansion Process when propagation input signals is received                                                                                                                                         | 133                      |

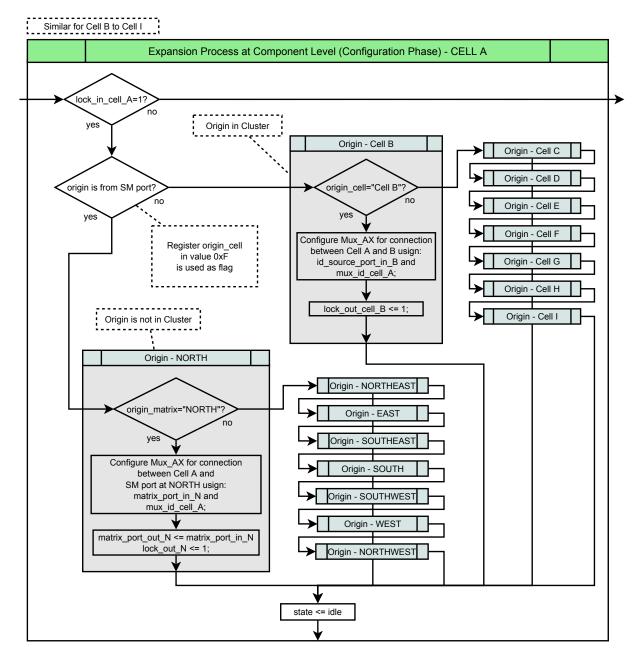

| C.8<br>C.9                                                  | Flow diagram for Configuration Phase of the Expansion Process at Cell Level 1                                                                                                                                                                      | 134<br>135<br>136        |

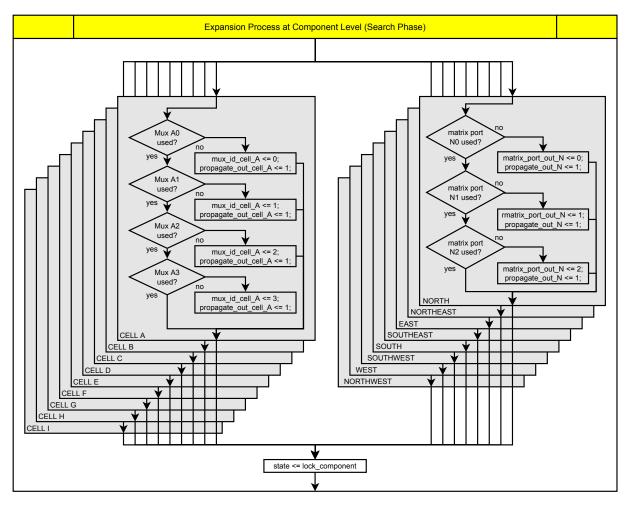

|                                                             | Main flow diagram for Expansion and Release processes in Switch Matrix Config-                                                                                                                                                                     | 137 $138$                |

| C.12                                                        | Flow diagrams for propagation input signals at component level in Switch Matrix                                                                                                                                                                    | 140                      |

|                                                             | Flow diagram for the propagation of Signals in the Search Phase of the Expansion<br>Process at Component Level.                                                                                                                                    | 140                      |

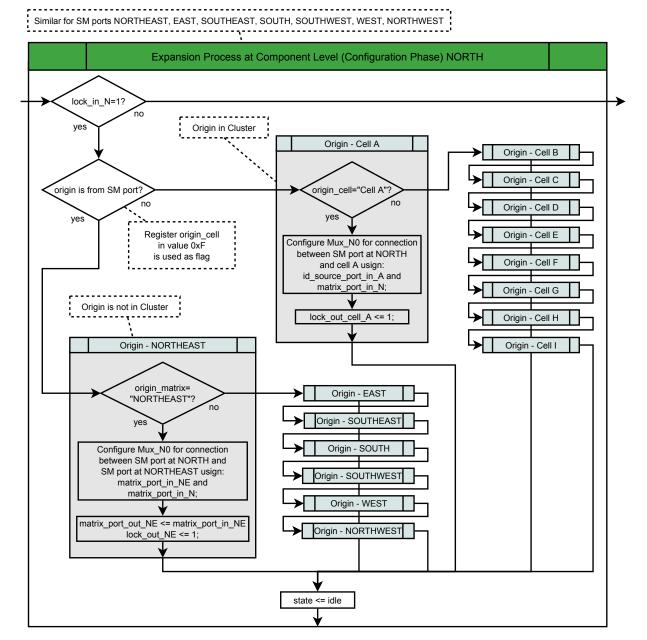

|                                                             | Flow diagram for Configuration Phase of the Expansion Process at Component<br>Level when the <i>lock_in</i> signal comes from a Cell.                                                                                                              | 141                      |

|                                                             | Level when the <i>lock_in</i> signal comes from a Switch Matrix                                                                                                                                                                                    | 142                      |

| C.17                                                        | Flow digram of Release Process at Component Level when <i>del_connection</i> signal                                                                                                                                                                | 143 $144$                |

|                                                             | Screen capture of SANE Project Developer.       1         Component editor tool.       1                                                                                                                                                           | 148<br>154<br>155        |

# Listings

| 5.1  | Example of a SANE-ASM with Subprocesses for dynamic reconfiguration 8               | 0  |

|------|-------------------------------------------------------------------------------------|----|

| 5.2  | Example of a SANE-ASM with Subprocesses for dynamic reconfiguration 8               | 31 |

| E.1  | SASM file for configuration of Dynamic Fault Tolerance Scaling application 16       | 3  |

| E.2  | ASM code for Monitor_1 section                                                      | 4  |

| E.3  | ASM code for Monitor_2 section                                                      | 8  |

| E.4  | ASM code for Compute sections (original, first and second copy)                     | 9  |

| E.5  | SHEX file generated by SANE Project developer after execute Build Project option.17 | 0  |

| E.6  | SXM file generated by SANE Project developer after execute Build Project option.17  | 7  |

| E.7  | SASM file for Static Fault Tolerace example application                             | 9  |

| E.8  | ASM code for Working and Redundant Processors in Primary and Redundant Cells.18     | 0  |

| E.9  | ASM code for delay of binary sequence                                               | 31 |

| E.10 | SHEX file generated by SANE Project developer after execute Build Project option.18 | 31 |

| E.11 | SXM file generated by SANE Project developer after execute Build Project option.18  | 54 |

# Chapter 1 Introduction

Fall Down Seven Times, Get Up Eight. Cae siete veces, levántate ocho. Japanese Proverb – Proverbio Japonés

**Abstract:** This chapter is an introduction to adaptive and parallel processing systems. It includes mainly a theoretical framework, architecture overview and contributions, preliminary and related works.

Self-adaptation is defined as the ability of a system to react to its environment in order to optimize its performance. The AETHER project (Self-Adaptive Embedded Technologies for Pervasive Computing Architectures) [1] was a notable initiative in the study of novel self-adaptive computing technologies for future embedded and pervasive applications.

This work started as a contribution of the hardware platform for the AETHER project. After finalization of this project, I continue with the investigation introducing additional contributions to the initial platform developed.

One of the purposes of the AETHER project (including this work) is to show that self-adaptive computing architectures can be a powerful approach to simultaneously addressing the major problems raised by pervasive computing. In particular, it aims to tackle the issues related to parallel processing, self-adaptive capabilities and technological scalability, increased complexity and programmability of future embedded computing architectures by introducing self-adaptive technologies in computing resources.

### 1.1 Adaptive and Bioinspired Systems

An adaptive system consists of a set of interacting entities, which form an integrated whole that is able to respond to environmental changes or changes in the interacting parts. Adaptive systems are closely tied with the concept of bioinspired systems, that are systems built using configurable hardware and electronic instruments, that emulates the capabilities of the biological systems to process information and solve problems.

These features are relevant in research areas such as embedded systems and pervasive computing among others [2]. Some important features like self-organization and self-configuration are linked to higher computational requirements, where adaptive system architectures are formed as a promise in the evolution of classical computing systems. Self-adaptive computing architectures can be a powerful approach to simultaneously address the major problems raised by pervasive computing. In coming years virtually every object will have a processing power, where the processing resources will require greater flexibility and scalability to meet the various needs of users. Adaptive computing systems offer the ability to adequate all or part of its architecture with applications that include changing needs or changing environments.

Adaptable architectures are closely linked to the concept of parallelism and reconfigurability, theoretically allowing greater efficiency for development of general purpose applications. According to [2] adaptive systems should have the following characteristics of bioinspired systems: self-configuration, adaptivity, self-distribution, self-organization, self-healing, automatic parallelization, accounting, self-protection and protection of others.

Self-healing is a special feature of an adaptive system, where hardware failures should be detected, handled and corrected by the system automatically. A fault tolerance system in an adaptive system together with other self-adaptive capabilities could provide this functionality.

### 1.2 Self-Adaptive capabilities in the proposed architecture

Self-configuration is a basic principle that permits a programmable or configurable system to modify autonomously its functionality at a given time [3]. This modification is usually driven by an optimization process that tries to match the behavior of the system with the constraints posed to the application it is intended to solve. The main characteristic to be present in the actual self-adaptive system is the capability of determining its configuration at a given time in an autonomous and distributed way by the system members (cells). This implies that the following properties should be supported at the hardware level by any architecture intended to be used as an efficient platform for self-adaptive principles: dynamic and distributed self-routing [4] [5] [6], dynamic and distributed self-placement, scalability and distributed control.

The self-placement and self-routing processes, due to its nature, enable the systems with runtime reconfiguration, self-repair and/or fault tolerance capabilities. This processes allow for performing complex functionality changes in real time, beyond the programmed context changes, currently common in the FPGA domain. The proposed self-placement and self-routing processes endow the system with enhanced functionality, making it possible for the system to change by itself, without the need for any configuration manager, as needed in current FPGAs. The absence of a centralized supervision system allows performing some of the tasks in a distributed way.

### **1.3** Architectures for parallel computing

Flynn's taxonomy [7] is probably the most common way to classify computer architectures with respect to their parallelism, based on the instruction and data flows. These streams are independent, so there are four possible combinations in parallel computing (see Table 1.1).

The model SISD (Single Instruction Single Data) based on the Von Neumann machine is the classic computing architecture; it uses a processor that is capable of performing actions sequentially, making different types of operations (arithmetic, logical, shifts, etc.) between data memory and processor registers. Although significant improvements have been implemented, like pipelining, prefetching, RISC architectures, code optimizers and others, it is expected to slow the pace of improvement, mainly due to physical implementation constraints. On the other hand, the need to solve new problems has increased, which demands high computational loads, so that the development of new parallel processing system acquires significant importance.

In a SIMD (Single Instruction Multiple Data) model a single program controls the processors using multiple data streams to perform operations that can be parallelized in a natural way. This type of architecture is useful in uniform applications, as in image processing, where it is necessary to apply the same function to many pixels simultaneously.

| Name    | Instructions     | Data     | Example, application                                                              |

|---------|------------------|----------|-----------------------------------------------------------------------------------|

| Ivaille | Flow             | Flow     | Example, application                                                              |

| SISD    | 1                | 1        | Classic computing architectures: Von Neumann, Harvard, PCs.                       |

| SIMD    | 1                | Multiple | Vector processors, graphics cards.                                                |