# Techniques for Improving the Performance of Software Transactional Memory

Srđan Stipić

Department of Computer Architecture

Universitat Politècnica de Catalunya

A thesis submitted for the degree of  $Doctor\ of\ Philosophy\ in\ Computer\ Architecture$   $July,\ 2014$

Advisor: Adrián Cristal

Co-Advisor: Osman S. Unsal

**Tutor:** Mateo Valero

| Acta de calificación de te                   | sis doctoral                |                            | Curso académico:                          |

|----------------------------------------------|-----------------------------|----------------------------|-------------------------------------------|

| Nombre y apellidos                           |                             |                            |                                           |

| Programa de doctorado                        |                             |                            |                                           |

| Unidad estructural responsable del programa  |                             |                            |                                           |

|                                              |                             |                            |                                           |

| Resolución del Tribunal                      |                             |                            |                                           |

| TROOTIGOTI GOT TITIOGITAL                    |                             |                            |                                           |

| _                                            |                             |                            | a expone el tema de la su tesis doctoral  |

| titulada                                     |                             |                            |                                           |

| Acahada la lectura y desnués de              | dar resnuesta a las         | cuestiones form            | nuladas por los miembros titulares del    |

| tribunal, éste otorga la calificación:       | dai respuesta a las         | cuestiones form            | idiadas por los miembros titulares der    |

|                                              | APROBADO                    | NOTABLE                    | SOBRESALIENTE                             |

| NO AFTO                                      | AFROBADO                    | NOTABLE                    | SOBRESALIENTE                             |

|                                              |                             | I                          |                                           |

| (Nombre, apellidos y firma)                  |                             | (Nombre, apellidos y firm  | na)                                       |

| <b>-</b>                                     |                             |                            |                                           |

| Presidente/a (Nombre, apellidos y firma)     | (Nombre, apellidos y firma) | Secretario/a               | (Nombre, apellidos y firma)               |

| (remains, apparation y mina)                 | (Nomero, apomaco y mina)    |                            | (voils) of apollage y limite)             |

| Vocal                                        | Vocal                       |                            | Vocal                                     |

|                                              | Vocai                       |                            | 10000                                     |

|                                              | de                          | de                         |                                           |

| ·                                            |                             | uc                         |                                           |

|                                              |                             |                            |                                           |

|                                              |                             |                            |                                           |

| El resultado del escrutinio de los vo        | tos emitidos por los        | miembros titulare          | es del tribunal, efectuado por la Escuela |

| de Doctorado, a instancia de la Com          | nisión de Doctorado         | de la UPC, otorga          | la MENCIÓN CUM LAUDE:                     |

| ☐ sí ☐ NO                                    |                             |                            |                                           |

|                                              |                             |                            |                                           |

| (Nombre, apellidos y firma)                  |                             | (Nombre, apellidos y firm  | na)                                       |

| ( · · · · · · · · · · · · · · · · · · ·      |                             | ,                          | ,                                         |

|                                              |                             |                            |                                           |

| Presidente de la Comisión Permanen Doctorado | te de la Escuela de         | Secretaria de la Doctorado | Comisión Permanente de la Escuela de      |

|                                              |                             | 1                          |                                           |

|                                              |                             |                            |                                           |

| Barcelona a de                               | de                          |                            |                                           |

# Acknowledgements

I am thankful to a lot of people without whom I would not have been able to complete my PhD studies. While it is not possible to make an exhaustive list of names, I would like to mention a few. Apologies if I forget to mention any name below.

I would like to thank my advisors Adrián Cristal and Osman Unsal for all the help and guidance they provided during my PhD studies. I would also like to acknowledge Ibrahim Hur for his help while he was part of Barcelona Supercomputing Center. I also thank Mateo Valero for his dedication and continuous effort in making the Barcelona Supercomputing Center such a great platform for research.

I would like to thank Tim Harris, who kindly mentored me during my three-month stay in Microsoft Research Cambridge. I had a great and productive time in Microsoft thanks to Tim's always positive attitude and enthusiasm.

I would like to thank Lukasz Skital, Rory Ward, and Tom Limoncelli from Google where I did internship in Google-Dublin/Ireland for three months in 2011. Internship in Google gave me the opportunity to work in industrial environment where I was working on their internal tool for managing network connections in Google's data-centers.

I would also like to acknowledge all my friends and colleagues from the office that helped me throughout my PhD; for their insights and expertise in technical matters, and for their unconditional support that has been crucial to keep me sane. Many thanks go to Adrià Armejach, Ana Jokanović, Azam Seyedi, Bojan Marić, Branimir Dickov, Chinmay Kulkarni, Cristian Perfumo, Daniel Nemirovsky, Ege Akpinar, Ferad

Zyulkyarov, Gokcen Kestor, Gülay Yalçın, Ivan Ratković, Javier Arias, Jelena Koldan, Maja Etinski, Milan Pavlović, Milan Stanić, Milovan Đurić, Miloš Milovanović, Nehir Sonmez, Nikola Marković, Nikola Vujić, Oriol Arcas, Paul Carpenter, Saša Tomić, Timothy Hayes, Vasilis Karakostas, Vesna Smiljković, Vladimir Subotić, Vladimir Gajinov, Vladimir Marjanović, and many others. I sincerely thank you all for your help and all the great moments we have had together.

I would like to thank my friends and family for supporting me during this endeavour. My deepest thanks to my wife Claudia for her love and for being there for me all the time. This dissertation would have not been possible without her.

# Abstract

Transactional Memory (TM) provides software developers the opportunity to write concurrent programs more easily compared to any previous programming paradigms and promisses to give a performance comparable to lock-based synchronizations.

Current Software TM (STM) implementations have performance overheads that can be reduced by introducing new abstractions in Transactional Memory programming model.

In this thesis we present four new techniques for improving the performance of Software TM: (i) Abstract Nested Transactions (ANT), (ii) TagTM, (iii) profile-guided transaction coalescing, and (iv) dynamic transaction coalescing. ANT improves performance of transactional applications without breaking the semantics of the transactional paradigm, TagTM speeds up accesses to transactional metadata, profile-guided transaction coalescing lowers transactional overheads at compile time, and dynamic transaction coalescing lowers transactional overheads at runtime.

Our analysis shows that Abstract Nested Transactions, TagTM, profile-guided transaction coalescing, and dynamic transaction coalescing improve the performance of the original programs that use Software Transactional Memory.

# Contents

| 1 | Inti | roduct   | ion                                                        | 1  |

|---|------|----------|------------------------------------------------------------|----|

|   | 1.1  | Introd   | luction to Transactional Memory                            | 1  |

|   |      | 1.1.1    | Transactions in databases                                  | 2  |

|   |      | 1.1.2    | Transactional memory                                       | 3  |

|   |      | 1.1.3    | Nested Transactions                                        | 6  |

|   |      | 1.1.4    | Software Transactional Memory (STM)                        | 8  |

|   |      | 1.1.5    | Hardware Transactional Memory (HTM)                        | 8  |

|   |      | 1.1.6    | Hybrid Transactional Memory                                | 9  |

|   | 1.2  | STAN     | IP Benchmark Suite                                         | 9  |

|   | 1.3  | Proble   | em Statement                                               | 13 |

|   |      | 1.3.1    | Unintended Transaction Aborts                              | 13 |

|   |      | 1.3.2    | Transactional Meta-data Accesses                           | 13 |

|   |      | 1.3.3    | Transaction starting and committing overheads              | 14 |

|   | 1.4  | Previo   | ous Techniques for Improving the Performance of STMs       | 14 |

|   | 1.5  | Thesis   | s Contributions and Organization                           | 15 |

| 2 | Abs  | stract 1 | Nested Transactions                                        | 17 |

|   | 2.1  | Introd   | luction to Abstract nested transactions                    | 17 |

|   | 2.2  | Motiv    | ation for Abstract nested transactions                     | 18 |

|   | 2.3  | Benig    | n conflicts                                                | 22 |

|   |      | 2.3.1    | Shared temporary variables                                 | 22 |

|   |      | 2.3.2    | False sharing                                              | 23 |

|   |      | 2.3.3    | Tx using commutative operations with low-level conflicts . | 24 |

|   |      | 2.3.4    | Defining commutative operations with low-level conflicts . | 25 |

|   |      | 2.3.5    | Making arbitrary choices deterministically                 | 27 |

|   |     | 2.3.6         | Discussion                                        | 28 |

|---|-----|---------------|---------------------------------------------------|----|

|   | 2.4 | Abstra        | act nested transactions                           | 29 |

|   |     | 2.4.1         | Syntax                                            | 30 |

|   |     | 2.4.2         | Semantics                                         | 30 |

|   |     | 2.4.3         | Performance                                       | 31 |

|   | 2.5 | Protot        | type implementation                               | 32 |

|   |     | 2.5.1         | Changes when executing an atomic block            | 32 |

|   |     | 2.5.2         | Changes when committing an atomic block           | 35 |

|   |     | 2.5.3         | Implementing equality in RTS                      | 37 |

|   | 2.6 | Result        | s                                                 | 39 |

|   | 2.7 | Summ          | ary                                               | 41 |

| 3 | Tag | $\mathbf{TM}$ |                                                   | 45 |

|   | 3.1 | Introd        | uction to TagTM                                   | 45 |

|   | 3.2 | Global        | l Tags (GTags)                                    | 46 |

|   | 3.3 | TagTN         | М                                                 | 47 |

|   |     | 3.3.1         | TinySTM                                           | 47 |

|   |     | 3.3.2         | Bottlenecks in TinySTM                            | 48 |

|   |     | 3.3.3         | Using GTags in TinySTM                            | 48 |

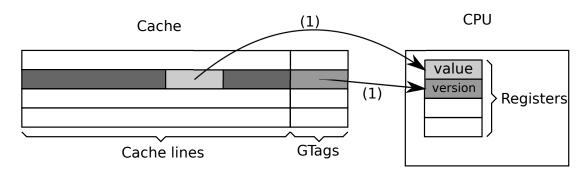

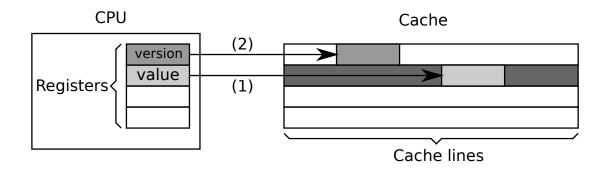

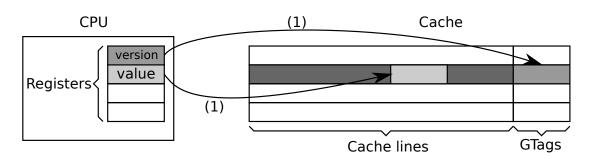

|   |     | 3.3.4         | Improving the tx_read operation                   | 49 |

|   |     | 3.3.5         | Improving the tx_commit operation                 | 51 |

|   |     | 3.3.6         | Modifying remaining transactional operations      | 53 |

|   | 3.4 | Evalua        | ation                                             | 53 |

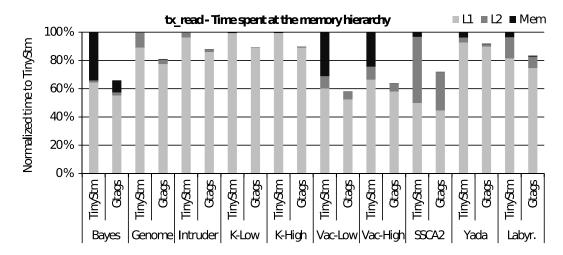

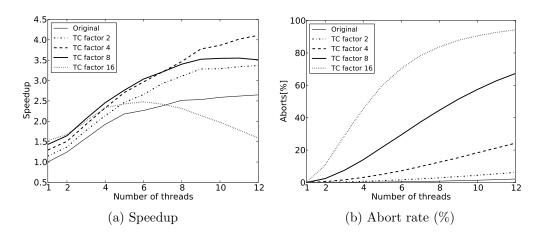

|   |     | 3.4.1         | Transactional operations performance improvements | 54 |

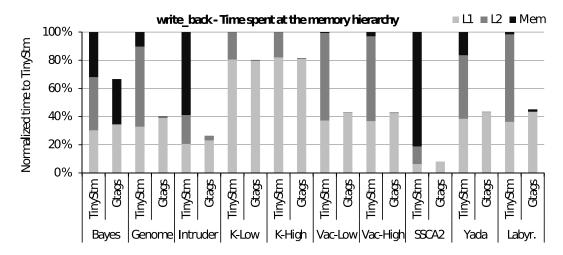

|   |     | 3.4.2         | Transaction execution performance improvements    | 55 |

|   |     | 3.4.3         | GTags - L1 cache overhead                         | 57 |

|   | 3.5 | Relate        | d Work                                            | 58 |

|   | 3.6 | Summ          | ary                                               | 59 |

| 4 | Pro | file-Gu       | ided Transaction Coalescing                       | 61 |

|   | 4.1 | Introd        | uction to Profile-Guided Transaction Coalescing   | 61 |

|   | 4.2 | Motiva        | ation for Profile-Guided Transaction Coalescing   | 62 |

|   | 4.3 | Transa        | actional overheads                                | 63 |

|   | 4.4 | Transa        | action coalescing                                 | 66 |

### CONTENTS

|   | 4.5 | Apply  | ing TC                                   | 69         |

|---|-----|--------|------------------------------------------|------------|

|   |     | 4.5.1  | Profiling tool                           | 69         |

|   |     | 4.5.2  | Transaction Coalescing Heuristic         | 70         |

|   |     | 4.5.3  | Compiler Pass                            | 73         |

|   |     | 4.5.4  | Transaction Coalescing - Correctness     | 75         |

|   |     | 4.5.5  | Executing non-undoable code              | 77         |

|   | 4.6 | Evalua | ation                                    | 78         |

|   |     | 4.6.1  | Benchmarks                               | 79         |

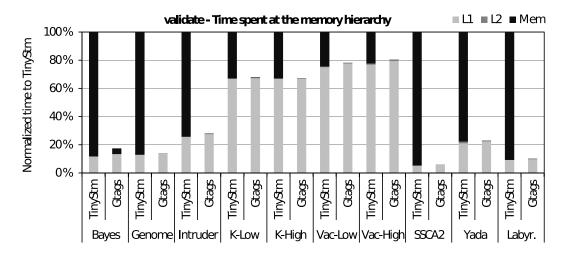

|   |     | 4.6.2  | Results                                  | <b>7</b> 9 |

|   | 4.7 | Summ   | nary                                     | 83         |

| 5 | Dyr | namic  | Transaction Coalescing                   | 85         |

|   | 5.1 | Introd | luction to Dynamic Transactional Memory  | 85         |

|   | 5.2 | Motiv  | ation for Dynamic Transaction Coalescing | 86         |

|   | 5.3 | Backg  | round                                    | 87         |

|   | 5.4 | Dynar  | mic Transaction Coalescing               | 90         |

|   |     | 5.4.1  | Loop Replacement and Unrolling (LU)      | 92         |

|   |     | 5.4.2  | Transaction Coalescing Algorithm (TCA)   | 92         |

|   |     | 5.4.3  | Run-time Transaction Profiling (RTP)     | 93         |

|   |     | 5.4.4  | Discussion                               | 94         |

|   | 5.5 | Evalua | ation Methodology                        | 95         |

|   |     | 5.5.1  | Benchmarks                               | 95         |

|   |     | 5.5.2  | Metrics                                  | 97         |

|   | 5.6 | Result | ts                                       | 97         |

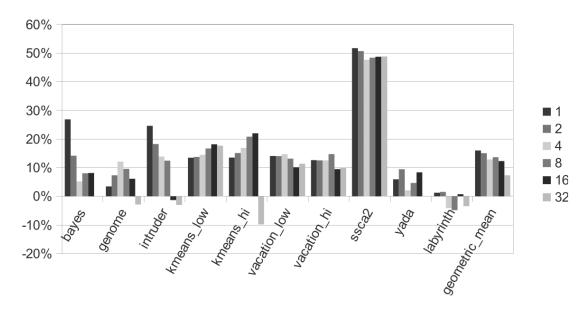

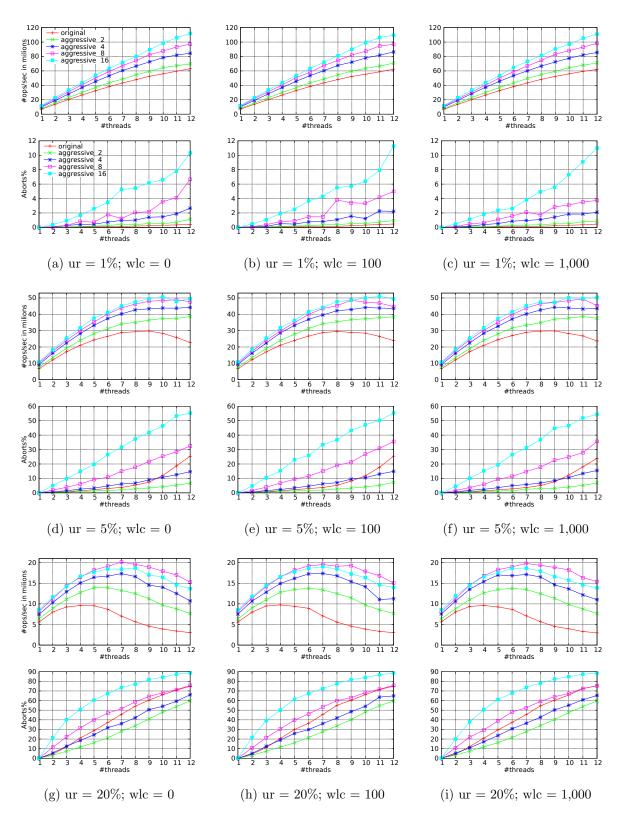

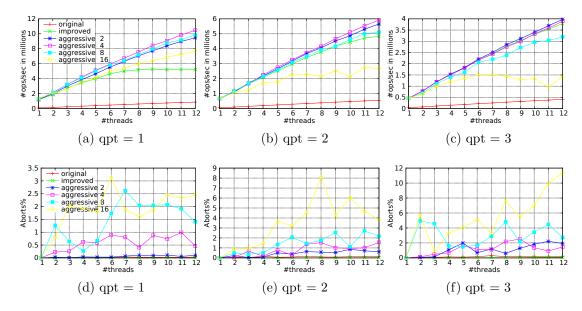

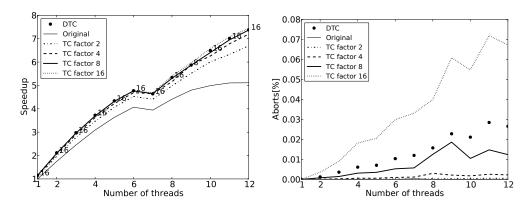

|   |     | 5.6.1  | Hash-table                               | 97         |

|   |     | 5.6.2  | Red-black tree                           | 99         |

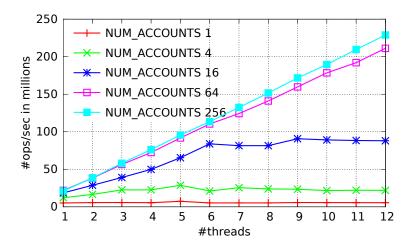

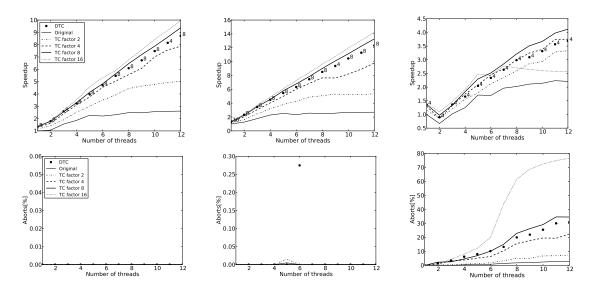

|   |     | 5.6.3  | Vacation & SSCA2                         | 100        |

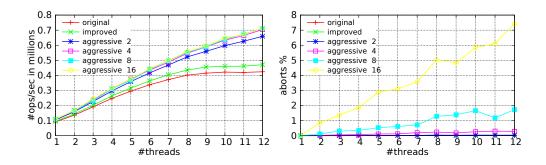

|   |     | 5.6.4  | CLOMP-TM                                 | 101        |

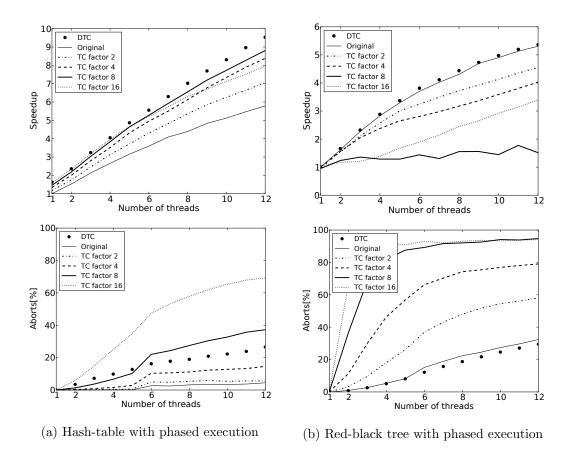

|   |     | 5.6.5  | Phased execution                         | 101        |

|   |     | 5.6.6  | Overview                                 | 103        |

|   | 5 7 | Summ   | 10ry                                     | 104        |

### CONTENTS

| 6                         | Conclusions |                                                 |     |  |  |  |

|---------------------------|-------------|-------------------------------------------------|-----|--|--|--|

|                           | 6.1         | Thesis Contributions                            | 105 |  |  |  |

|                           | 6.2         | Future Work                                     | 107 |  |  |  |

| 7                         | Pul         | olications on the topic                         | 109 |  |  |  |

|                           | 7.1         | Publications from the thesis:                   | 109 |  |  |  |

|                           | 7.2         | Related publication not included in the thesis: | 110 |  |  |  |

| $\mathbf{R}_{\mathbf{c}}$ | efere       | nces                                            | 120 |  |  |  |

# Chapter 1

# Introduction

# 1.1 Introduction to Transactional Memory

The multi-core era has already arrived. Currently, most of the new desktop or laptop computers have two or more cores. Intel and AMD are promising that in coming years we will have 32, 64 or more cores integrated in to a single chip. The new game consoles like XBOX ONE from Microsoft and PlayStation 4 from Sony have multi core CPUs (8 CPU cores with multi-core GPU). Still, the developers of new applications have hard time writing concurrent programs that utilize all of the available CPU cores. The reason for this is that the programmers are still using locks as their main building blocks for writing concurrent programs. The use of locks introduces problems like: dead lock and live lock, that are hard to detect, debug and reproduce. The transactional memory raises the level of abstraction for the programmers and elegantly eliminates the problems stated above.

The transactional memory (TM) technology borrows proven concurrency-control concepts from work done over the decades in the database field, and try to apply them in everyday programming languages (C, C++, Java, C#).

Transactional Memory (TM) systems can be subdivided into three flavors: Hardware TM (HTM), Software TM (STM) and Hybrid TM (HyTM) (the mix of hardware and software transactional memory).

#### 1.1.1 Transactions in databases

In the context of databases, a single logical operation on the data is called a transaction. A set of properties that database transactions guarantee are: atomicity, consistency, isolation, and durability (ACID).

An example of a transaction is a transfer of funds from one account to another, even though it might consist of multiple individual operations, such as debiting one account and crediting another.

#### Atomicity

Atomicity refers to the ability of the database to guarantee that either all of the tasks of a transaction are performed or none of them are. For example, the transfer of funds can be completed or it can fail for a multitude of reasons, but atomicity guarantees that one account will not be debited if the other is not credited. Atomicity states that database modifications must follow an "all or nothing" rule. Each transaction is said to be "atomic." If one part of the transaction fails, the entire transaction fails. It is critical that the database management system maintains the atomic nature of transactions in spite of any operating system or hardware failure.

#### Consistency

Consistency property ensures that the database remains in a valid state before the start of the transaction and after the transaction is over, whether successful or not.

Consistency states that only valid data will be written to the database. If, for some reason, a transaction is executed that violates the database's consistency rules, the entire transaction will be rolled back and the database will be restored to a state consistent with those rules. On the other hand, if a transaction successfully executes, it will take the database from one state that is consistent with the rules to another state that is also consistent with the rules

#### **Isolation**

Isolation refers to the constraint that prevent other operations to access or see the data in the intermediate state during transaction. This constraint is required to maintain the consistency between transactions in a DBMS system.

#### Durability

Durability refers to the guarantee that once the user has been notified of success, the transaction will persist, and not be undone. This means it will survive system failure, and that the database system has checked the integrity constraints and won't need to abort the transaction. Many databases implement durability by writing all transactions into a log that can be played back to recreate the system state right before the failure. A transaction can only be deemed after it is safely stored in the log.

## 1.1.2 Transactional memory

In computer science, transactional memory (TM) is a concurrency control mechanism analogous to database transactions for controlling access to shared memory in concurrent computing. It functions as an alternative to lock-based synchronization. A transaction in this context is a piece of code that executes a series of reads and writes to a shared memory. These reads and writes logically occur at a single instant in time (atomicity); intermediate states are not visible to other (successful) transactions (isolation). The idea of providing hardware support for transactions originated in paper by Tom Knight [Knight (1986)]. The idea was popularized by Maurice Herlihy and J. Eliot B. Moss [Herlihy & Moss (1993)] for hardware TM. In 1995 Nir Shavit and Dan Touitou extended this idea to software-only transactional memory (STM) [Shavit & Touitou (1995)].

Transactions in TM do not try to provide all ACID properties of database transactions. From the programming point of view only atomicity and isolation properties are required because TM as a concept tries to eliminate explicit use of locks (TM systems can use locks in their implementations but those locks are not exposed to the programmers).

Figure 1.1: Decrementing a counter

Consistency property (as it is defined in databases) does not exist in TM, but most of TM systems provide a 'retry' operation that automatically restarts the transaction. The retry operation can be used to implement consistency rules that are specified in the program.

The example in Figure 1.1 shows how the consistency rules are programmed by using locks and by using transactions with retry operation. For example, assume that we want to decrement a shared counter only if it is greater than zero (consistency rule). In the version of the program that uses locks we have have to take special care (to release the lock) in order not to create a deadlock. We can see that the transactional version is much simpler and it does not suffer from the deadlock problem because the TM system guaranties correct execution.

Durability is not provided in TM because the programs which use TM are not durable by definition.

#### Version control

Depending on the moment when we update the shared memory locations we can identify two types of version control:

• Eager versioning: a write access within a transaction immediately writes to memory the new data version. The old version is buffered in an undo log.

• Lazy versioning: stores all new data versions in a write buffer until the transaction completes.

#### Conflict detection

Depending on the moment when we detect conflicts between transactions we can identify two types of version control:

- Eager conflict detection: TM detects a conflict when a transaction tries to access a memory reference.

- Lazy conflict detection: TM detects conflicts when the first of two or more conflicting transactions commits.

#### Read and Write set

During the execution of a transaction, the transaction speculatively reads and writes shared memory locations. In order to keep the track of read and write accesses to shared memory location, each transaction keeps the access information in its read and write sets. We define read and write set of a transaction in the following way:

- Read set is the set of shared memory locations that are read speculatively during the execution of the transaction.

- Write set is the set of shared memory locations that are written speculatively during the execution of the transaction.

Read and write set can overlap or they can be disjunctive. At the commit time, the transaction validates its read and write set and commits its write set (the transaction updates the shared memory locations with the speculative values from the write set).

#### Conceptual advantages and disadvantages of TM

TM greatly simplifies conceptual understanding of multithreaded programs and helps make programs more maintainable by working in harmony with existing high-level abstractions such as objects and modules. Lock-based programming has a number of well-known problems that frequently arise in practice:

- Locks require thinking about overlapping operations and partial operations in distantly separated and seemingly unrelated sections of code, a task which is very difficult and error-prone for programmers.

- The fine grained locking require programmers to adopt a locking policy to prevent deadlock, livelock, and other failures to make progress. Such policies are often informally enforced and fallible, and when these issues arise they are difficult to reproduce and debug.

- Locks can lead to priority inversion, a phenomenon where a high-priority thread is forced to wait on a low-priority thread holding exclusive access to a resource that it needs.

In contrast, the concept of a memory transaction is much simpler, because each transaction can be viewed in isolation as a single-threaded computation. Deadlock and livelock are either prevented entirely or handled by an external transaction manager. Priority inversion can still be an issue, but high-priority transactions can abort conflicting lower-priority transactions that have not already committed.

On the other hand, the need to abort failed transactions also places limitations on the behavior of transactions: they cannot perform any operation that cannot be undone, including most I/O.

#### 1.1.3 Nested Transactions

Figure 1.2 shows an example of two functions f() and g() where each function contains one transaction. The function g() executes transaction that contains the call to function f(). Because function f() is marked as inline, the compiler inlines the body of function f() in the function g(). After inlining, the function

```

void g() {

inline void f() {

atomic {

atomic { a++; }

b++;

}

f();

}

}

// after inlining

void g() {

// outer transaction

atomic {

b++;

// inner transaction

atomic { a++; }

}

}

```

Figure 1.2: Nested transactions

g() contains two transactions (outer and inner). TM system define 3 modes how these two transactions execute with respect to other transactions in the system: (i) flat nesting, (ii) closed nesting, and (iii) open nesting.

Flat nesting mode executes outer transaction as one big transaction. Flat nesting ignores the presence of the nested atomic block but executes the body of nested transaction as part of the outer transaction. If a conflict happens on a or b, the outer transaction is restarted. When the outer transaction finishes executing, the speculative values of a and b are committed to the memory.

Closed nesting mode executes outer transaction as one big transaction. If a conflict happens on a, the inner transaction is restarted; and if the conflict happens on b, the outer transaction is restarted. When the outer transaction finishes executing, the speculative values of a and b are committed to the memory.

Open nesting mode executes outer transaction as two separate transactions. If a conflict happens on a inner transaction is restarted and if conflict happens on b the outer transaction is restarted. When the inner transaction finishes executing, the speculative value of a is committed to the memory (even though the outer

transaction did not finish). When the outer transaction finishes executing, the speculative value of b is committed to the memory.

## 1.1.4 Software Transactional Memory (STM)

Unlike the locking techniques used in most modern multithreaded applications, a thread speculatively access the shared memory without regard for what other threads might be doing, recording every read and write that it is performing in a log. Instead of placing the burden on the writer thread to make sure it does not adversely affect other operations in progress, it is placed on the reader thread, who after completing an entire transaction verifies that other threads have not concurrently made changes to memory that it accessed in the past. This final operation, in which the changes of a transaction are validated and, if validation is successful, made permanent, is called commit. A transaction may also abort at any time, causing all of its prior changes to be rolled back and undone. If a transaction cannot be committed due to conflicting changes, it is typically aborted and re-executed from the beginning until it succeeds.

However, in practice STM systems also experience a performance hit relative to fine-grained lock-based systems on small numbers of processors (1 to 4 depending on the application). This is primarily due to the overhead associated with maintaining the log and the time spent committing transactions.

# 1.1.5 Hardware Transactional Memory (HTM)

In HTM systems, the hardware ensures correct transaction execution. HTM – compared with STM – does not experience the performance penalties. Hardware implements all necessary transactional mechanisms in caches [Hammond *et al.* (2004a), Ananian *et al.* (2005)] or memory directory [Moore *et al.* (2006b)].

Currently proposed HTM systems fall into three regions of the design space:

- LL: lazy conflict detection, lazy version management [Hammond *et al.* (2004a)]

- EL: eager conflict detection, lazy version management [Ananian et al. (2005)]

• EE: eager conflict detection, eager version management [Moore et al. (2006b)]

In the paper [Bobba et al. (2007)], the authors show that lazy/lazy TM perform better than eager/eager TMs in general case.

The downsides of HTM is that none of the CPU manufactures (Intel, AMD, IBM) are planing to implement full HTM in their CPUs, because of its complexity. Sun Microsystems planed to release the Rock CPU that provide limited support for executing small transactions in hardware [Moir et al. (2008)] but in the end the project was canceled. Intel released Haswell CPU with best effort HTM system [Yoo et al. (2013)] that executes transaction as long as the transactional data fit in L1 cache. When the transactional data overflows the cache, the transaction use software fallback mechanism.

## 1.1.6 Hybrid Transactional Memory

Hybrid transactional memory promises best of the two worlds. Small transitions can be executed in hardware and larger ones in software. Most transactions have small size [Ananian et al. (2005)] and HTM system can execute them in hardware which as a consequence gives us the maximum performance for the majority of the transactions. The transactions that exceed hardware resources will fall back to software mode.

University of Rochester proposed an extension to the MESI protocol [Shriraman et al. (2006)] that provides acceleration of STM. In 2006. Intel proposed adding few additional bits to the cache lines of the CPU in order to follow the validity of the memory locations that are referenced by STM [Saha et al. (2006a)]. Sun Microsystems [Moir et al. (2008)] proposed a hybrid TM approach in which transactions execute in hardware and if they overflow, they are rolled back and restarted in software.

#### 1.2 STAMP Benchmark Suite

STAMP benchmark suite [Minh et al. (2008)] is de facto standard in TM community for the evaluation of TM systems, thus, we use it for the evaluation of hardware and software techniques presented in this thesis [Chapters 3, 4,

| Application | Domain                        | Description                            |

|-------------|-------------------------------|----------------------------------------|

| bayes       | machine learning              | Learns structure of a Bayesian network |

| genome      | bioinformatics                | Performs gene sequencing               |

| intruder    | security                      | Detects network intrusions             |

| kmeans      | data mining                   | Implements K-means clustering          |

| labyrinth   | engineering                   | Routes paths in maze                   |

| ssca2       | scientific                    | Creates efficient graph representation |

| vacation    | online transaction processing | Emulates travel reservation system     |

| yada        | scientific                    | Refines a Delaunay mesh                |

Table 1.1: STAMP benchmark suite applications

and 5]. STAMP consist of eight different benchmarks (Table 1.1) that cover a wide range of transactional execution cases (e.g., small/large transactions, small/large conflict rate). The benchmarks are: **bayes**, **genome**, **intruder**, **kmeans**, **labyrinth**, **ssca2**, **vacation**, **yada**.

Bayes application implements algorithm for learning the structure of Bayesian networks from observed data. The Bayesian network itself is represented as a directed acyclic graph, with a node for each variable and an edge for each conditional between variables. Initially, the network hash no dependencies among variables, and the algorithm incrementally learns dependencies by analysing the observed data. On each iteration, each thread is given a variable to analyze, and as more dependencies are added to the network, connected subgraphs of dependent variables are formed.

A transaction is used to protect the calculation and addition of a new dependency, as the result depends on the extent of the subgraph that contains the variable being analyzed. Using transaction is much simpler than a lock-base approach as using locks would require manually orchestrating a two-phase locking scheme with deadlock detection and recovery to allow concurrent modification of the graph. Calculations of new dependencies take up most of the execution time, causing **bayes** to spend almost all its execution time in long transactions that have large a read and write set. Overall, this benchmark has high amount of contention as the subgraph changes frequently.

Genome application takes large number of DNA segments and tries to match them to reconstruct the original source genome. The application operates in two phases. In the first phase, **genome** uses hash set to remove the duplicate DNA segments, and in the second phase, tries to remove a segment from a global pool of unmatched segments and add it to its partition of currently matched segments.

Transaction are used in each phase of the benchmark. Additions to the set of unique segments are enclosed by transactions to allow concurrent accesses, and accesses to the global pool of unmatched segments are also enclosed by transactions since threads may try to remove the same segment. Overall, the transaction in **genome** are of moderate length and have moderate read write set size. Additionally, almost all of the execution time is transactional, and there is little contention.

Intruder application uses signature-based network intrusion detection system to scan network packets for matches against a known set of intrusion signatures. Network packets are processed in parallel and go through three phases: capture, reassembly, and detection. The main data structure in the capture phase in simple FIFO queue, and the reassembly phase uses a self-balancing tree that contains lists of packets that belong to the same session and uses coarse-grain synchronization. The capture and reassembly phase are each enclosed by transactions. So, the code for each phase is equivalent to the lock version and has short transactions with moderate levels of contention.

Kmeans application implements K-means algorithm that groups objects in and N-dimensional space into K clusters. The algorithm is commonly used to partition data items into related subsets. The application uses transactions to protect the update of the cluster center that occurs during each iteration. The amount of contention among threads depends on the value of K, with larger values resulting in less frequent conflicts as it is less likely that two threads are concurrently operation on the same cluster center. When updating the cluster centers, the size of transaction is proportional to the dimensionality of the space. Thus, the size of the transactions are relatively small.

Labyrinth application uses three-dimensional uniform grid that represents maze. The application uses threads, where each thread grabs a start and end point and tries to connect it with adjacent maze grid points. The calculation of the path is executed in a single transaction. A conflict occurs when two threads pick paths that overlap. Almost all of the application execution time is taken by the patch calculation, and this operation reads and writes an amount of data proportional to the number of total maze grid points, thus, **labyrinth** has very long transactional with very large read and write sets. Almost all the code is executed transactionally, and the amount of contention is very high.

Vacation application implements a travel reservation system powered by an in-memory database. Several client threads interact with the database through transactional requests. The performance is measured as the number of served client requests per second. The paper [Zyulkyarov et al. (2010a)] shows that the performance bottleneck in vacation is the red-black tree that is used as database storage, and they suggest replacing it with a hash table. We follow the same approach. Moreover, we identified another performance bottleneck: a function for generating random numbers was on the critical path limiting the throughput. We moved the generation of random numbers to the initialization part of the benchmark, where we populate per thread arrays with random numbers. We replaced the original random number function with an array indexing function that reads the random numbers from the arrays. In this way, we improved the throughput of the original benchmark without modifying its semantics.

Ssca2 [Bader & Madduri (2005)] application is a synthetic benchmark that operates on a large, directed, weighted multi-graph. The main loop of ssca2 traverses all the edges of the graph. The graph can be traversed in any order and the final execution of the benchmark is the same. Thus, transactions in the main loop execute in arbitrary order. We modified the main loop and instead of executing the transactions immediately, we buffer the values of the variables used in the transactions. When the buffer gets full, we execute all the transactions in a tight loop.

Yada application implements Ruppert's algorithm for Delaunay mesh refinement [Ruppert (1995)]. Yada uses graph data-structure to store all mesh triangles. In each iteration of the algorithm, one triangle is removed from the work queue, its retriangualtion is performed on the mesh, and any new triangles that result from the retriangualation are added to the work queue. Accesses to the

work queue are enclosed by transaction and almost all execution time is spend calculation the retriangualtion.

#### 1.3 Problem Statement

This thesis addresses several issues present in STM systems. These can be categorised under three heads: unintended transaction aborts, transactional metadata accesses, and transaction starting and committing overheads.

#### 1.3.1 Unintended Transaction Aborts

STM implementations use conflict detection based on the memory location that a transaction accesses. When two transactions update or write and read the same memory location, STM system detects the conflict and aborts one of the two transactions. For example, if two transactions insert items into the same hash-table under different keys witch happen to hash to the same bucket, the insertions update the same memory locations. This creates conflict between transactions because the implementation of the hash table updates the same memory locations even though the higher-level operations they are performing are commutative. Even though the transactions that update the hash table do not have conflict at semantic level (because the final content of the hash table is always and in independent of the order of the transaction commit order), they experience unintended transactional aborts because they update the same memory location.

#### 1.3.2 Transactional Meta-data Accesses

For every transaction in a program, the STM system keeps additional meta-data that is used for storing information about currently executing transactions. This meta-data is accessed and updated during every transactional operation (e.g, transaction read, write, commit). Most of the transactional overheads appear due to meta-data accesses and it is critical to reduce these overheads in order to make STM applications competitive with lock based application.

#### 1.3.3 Transaction starting and committing overheads

For most of the transactions executing in a program, STM system usually initializes transactional meta-data before the execution of a transaction and has to commit the data and meta-data at the end of a transaction. In the case of short transactions, the initialization and commit overheads can dominate the transaction execution time. If transactions are numerous and small, STM overheads accumulate rapidly.

# 1.4 Previous Techniques for Improving the Performance of STMs

The paper [Chung et al. (2008)] uses STM to provide thread-safe dynamic binary translation. They translate all the code transactionally and create transactions at the basic block level. They reduce the overhead of transactional execution by merging consecutive basic blocks into a large transaction.

To address the overhead of STM, researchers have proposed hybrid TM systems that provide some hardware support for conflict detection in STM code [Minh et al. (2007a); Saha et al. (2006b); Shriraman et al. (2007)]. For example, the paper [Saha et al. (2006b)] introduces hardware accelerated software transactional memory (HASTM) as ISA extensions and novel hardware mechanisms that improve STM performance by using additional bits per cache line. In addition, minor hardware changes can improve performance of transactional applications significantly.

The paper [Wang et al. (2012)] describes a BlueGene/Q machine with best effort HTM. BlueGene/Q maintains speculative states in the L2 cache and uses software register checkpointing with the setjmp() function. Even though Blue-Gene/Q has support for best effort hardware TM, this HTM implementation has issues with small transactions. The authors of the paper admit that the software register checkpointing has significant overhead for small transactions.

Many optimizations have been proposed for compilers and runtime systems to reduce the overheads of STM read and write operations [Afek et al. (2011); Dragojevic et al. (2009); Wang et al. (2007); Wu et al. (2009)]. The paper [Wang et al.

(2007)] provides compiler optimizations for eliminating unnecessary read/write barriers (read after write barrier, barriers on local variables, etc.) and register checkpointing. The paper [Afek et al. (2011)] proposes static analysis and code motion to decrease the number of memory accesses. For eliminating redundant barriers and checkpointing, the paper [Wu et al. (2009)] uses compiler optimizations on statistics collected at runtime. The paper [Dragojevic et al. (2009)] presents runtime and compiler optimizations to identify transaction-local stack and heap allocation, and an API for annotating thread-local and read-only memory regions.

The paper [Adl-Tabatabai *et al.* (2006a)] uses compiler and runtime optimizations for transactional memory language constructs. They use a JIT compiler to reduce the overheads of STM.

Yoo et al. [Yoo et al. (2013)] evaluate the performance of Intel Transaction Synchronization Extensions (TSX) that implement best effort hardware transactional memory. To quantify the transactional overheads, the authors analyze the performance benefits of static and dynamic transaction coalescing<sup>1</sup> and show that transaction coalescing improves performance. However, their implementation of transaction coalescing lacks the profiling mechanism that identifies the optimal transaction granularity at run-time. Their dynamic coalescing combines multiple dynamic instances of the same transactional region.

# 1.5 Thesis Contributions and Organization

This thesis provides an extensive study of optimization techniques for improving the performance of software transactional memory systems. The main contribution of this thesis are:

- Four new techniques for improving the performance of STM systems: (i) Abstract Nested Transactions (ANT), (ii) TagTM, (iii) Profile-Guided Transaction Coalescing, and (iv) Dynamic Transaction Coalescing (DTC).

- We explain, in detail the hardware and software implementation of our techniques.

<sup>&</sup>lt;sup>1</sup>Transaction coalescing is called coarsening in Intel's terminology.

• We show that our techniques improve the performance of STM systems.

The rest of the thesis is organized as follows: Chapter 2 explains Abstract Nested Transaction, a runtime technique that reduces the overheads of repeated restarts of transactions; Chapter 3 explains TagTM, a hardware and software technique that reduces the overheads of transactional read, commit, and validate operations; Chapter 4 explains Profile-Guided Transaction Coalescing, a profile-guided compile-time technique that reduces transactional overheads by coalescing transactions; Chapter 5 explains Dynamic Transaction Coalescing, a compile-time and run-time profiling technique that dynamically adjusts the transaction granularity to improve the transactional throughput; Chapter 6 concludes the thesis; and Chapter 7 lists the publications during my PhD.

# Chapter 2

# Abstract Nested Transactions

The content of this chapter was presented in the paper "Abstract Nested Transactions" at TRANSACT'07 (The Second ACM SIGPLAN Workshop on Transactional Computing).

#### 2.1 Introduction to Abstract nested transactions

TM implementations typically use conflict detection based on the memory locations that a transaction accesses. This can cause transactions to be re-executed because of *benign conflicts*, for example if two transactions insert items into the same hashtable under different keys which happen to hash to the same bucket: the insertions update the same memory locations, even though the higher-level operations they are performing are commutative.

In this chapter we introduce abstract nested transactions (ANTs) as a way of improving the scalability of atomic blocks that experience benign conflict. The main idea is that ANTs should contain operations that are likely to be the victims of benign conflicts. The run-time system then performs extra book-keeping so that, if an ANT does experience a conflict, the ANT can be re-executed without needing to re-run the larger transaction that contains it. Unlike closed nested transactions (CNTs) this re-execution can happen after the ANT has finished running – in our implementation we only re-execute ANTs at the point that we try to commit a top-level atomic block.

Moving code into or out of an ANT is *semantics preserving*: ANTs affect only the program's performance, not its possible results. This opens the door for future research in automatic ways to place ANTs in programs in order to deal with contention 'hot spots' that they experience.

## 2.2 Motivation for Abstract nested transactions

Atomic blocks provide a promising simplification to the problem of writing concurrent programs. A code block is marked atomic and the compiler and run-time system are responsible for ensuring atomicity during its execution. The programmer no longer needs to worry about manual locking, low-level race conditions or deadlocks.

Atomic blocks are typically implemented over *transactional memory* which provides the abstraction of memory read and write operations which can be grouped together to form a transaction and then committed to the memory as a single atomic step. The book [Larus & Rajwar (2007)] summarizes many of the hardware, software, and hybrid implementation techniques being explored.

In this chapter we highlight a number of ways that the performance of programs can degrade when based on TM. This happens due to *benign conflicts* (Section 2.3) that can occur between transactions. In each of these cases the TM implementation can force one or more transactions to abort because it detects a conflict which does not affect the application logic.

Figure 2.1 (a) shows a running example that we will use. We use a 'g\_' prefix on variable names to indicate that they are shared between threads. Other variables are threadprivate. The example involves two transactions, Tx-1 and Tx-2, which call 'performWork' on different objects. The function increments a count of the number of times that it has been called and then performs some work on the object that it has been passed. The updates to the shared counter will cause Tx-1 and Tx-2 to conflict with one another, leading to the re-execution of a whole atomic block even if the bulk of performWork is non-conflicting.

We introduce a taxonomy for different variants of this problem in Section 2.3. As we discuss with the taxonomy, there are several ways that programmers can try to avoid problems from benign conflicts. In some cases it is possible to restructure

```

atomic { // Tx-1 atomic { // Tx-2 performWork(g_o1); performWork(g_o2); }

void performWork(Object o) {

g_invocation_count ++;

// Work on 'o'

work(o);

}

```

(a) An ordinary implementation of performWork introduces conflicts via the global invocation counter.

```

void performWork(Object o) {

ant {

g_invocation_count ++;

}

// Work on 'o'

work(o);

}

```

(b) Rewriting performWork to use an ANT causes the higher-level update operation to be logged, rather than the low level reads and writes it performs.

Figure 2.1: A benign conflict between Tx-1 and Tx-2.

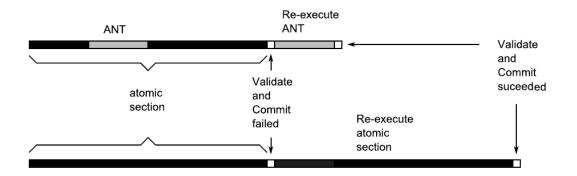

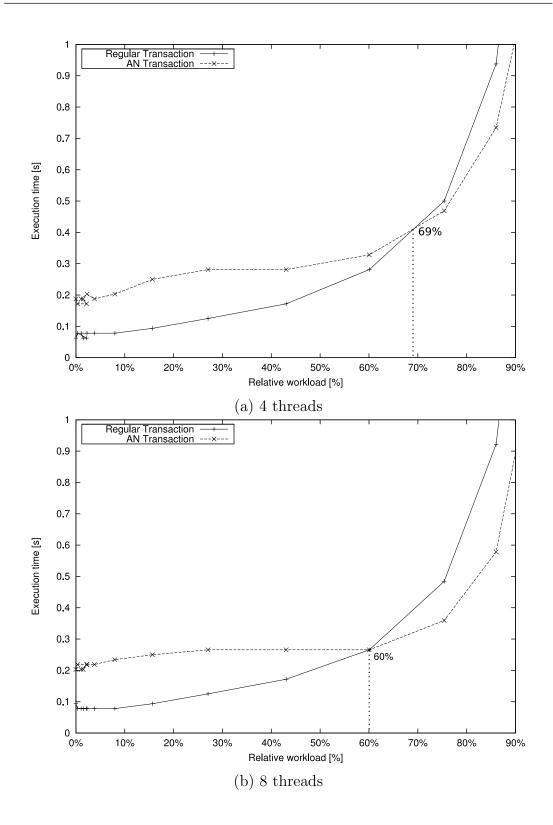

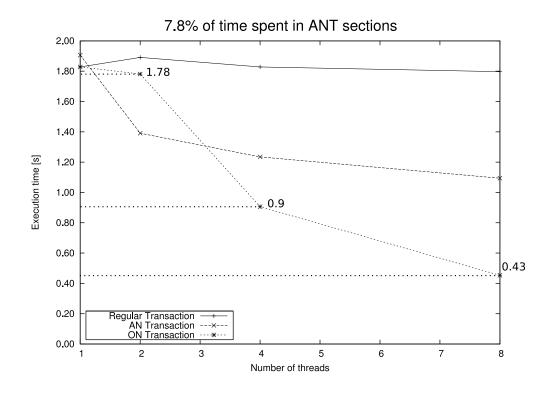

Figure 2.2: Execution time of an atomic section with ANT (top) and same atomic section without ANT (bottom).

code, to use open nested transactions [Ni et al. (2007)], or to use TM-specific optimization interfaces to avoid benign conflicts. All of these approaches have their problems: manually restructuring code can harm the composability benefits of atomic blocks, open nested transactions provide a powerful general purpose abstraction but one which relies on programmer care for correct usage, and TM-specific optimization interfaces are hard to use correctly.

In this chapter we introduce a new approach to avoid reexecuting whole atomic blocks that contain benign conflict. The idea, which we call abstract nested transactions (ANTs), is to identify operations that are likely to be the 'victims' of benign conflicts. This lets the TM implementation keep a separate log of the operations being performed by ANTs and, in the event of a low-level conflict, just re-execute the ANTs rather than re-executing the larger transaction containing them. Figure 2.1 (b) shows our example using an ANT to increment the counter.

Figure 2.2 shows why this can be faster: assuming that the ANT forms a small part of the overall execution time of an atomic block, it reduces the amount of work on a conflict.

We discuss the syntax and semantics of ANTs in Section 2.4. A fundamental design principle we took is that they are *semantically transparent*: marking a block of code as an ANT does not affect the possible results of a program. Our motivation in doing this is that it makes ANTs easier to use and, although we

show them being used manually in this chapter, in future work they could be placed automatically based on run-time feedback.

This principle guides many aspects of the design and implementation of ANTs: what happens if an ANT conflicts with a transaction that encloses it? What happens if an ANT raises an exception or tries to block using retry [Harris et al. (2005b)]? What happens if an ANT behaves one way on its first execution and then behaves differently if it is re-executed? We discuss these questions in Section 2.4.

We have prototyped our implementation of ANTs using STM Haskell [Harris et al. (2005b)]. In Section 2.5 - 2.6 we describe the details of this implementation and evaluate the performance impact of using ANTs.

In this chapter we make the following contributions:

- An initial taxonomy of *benign conflicts* that can occur between atomic blocks.

- The idea of abstract nested transactions as a way of making the performance of atomic blocks more robust to the presence of benign conflict.

- An implementation of ANTs in which they are semantically transparent, being able to be placed around any transactional code and affecting only its performance.

- Specific to our Haskell-based prototype, we describe a new mechanism for comparing possibly-non-terminating computations using lazy evaluation.

Throughout the chapter we assume an implementation over an STM using lazy conflict detection [Moore et al. (2006a)] that is, detecting conflicts at committime in short-running transactions, and periodically in long-running transactions and lazy versioning [Moore et al. (2006a)] that is, recording tentative updates privately for each transaction, and writing them to the heap upon successful commit.

The reminder of this chapter is organized as follows: in Section 2.3 we define benign conflicts; in Section 2.4 we explain the key ideas behind abstract nested transactions; in Section 2.5 we explain the prototype implementation of ATN; in Section 2.6 we show the experimental results; finally, we conclude in Section 2.7;

Figure 2.3: Shared temporary variables. Transactions Tx-1 and Tx-2 will conflict because they both write to g\_temp, even though neither depends on the values written by the other.

# 2.3 Benign conflicts

In this section we identify a number of different kinds of benign conflict that can cause a transaction to abort because of the low-level at which conflicts are typically detected in TM implementations. This is an intentionally imprecise definition; as we illustrate, whether or not a given conflict is benign depends on the context in which the transaction experiencing it occurs. However, distinguishing different kinds of benign conflict helps us identify the cases where ANTs are useful and the cases where they are not.

We focus solely on serializable atomic blocks. As the database community has explored, weaker isolation levels can reduce conflicts [Berenson et al. (1995)]. However weaker isolation also means that it is no longer possible to reason about atomic blocks as executing in isolation from one another; it is unclear whether this would be acceptable as part of a mainstream programming model.

# 2.3.1 Shared temporary variables

The first kind of benign conflict occurs when global variables are used for transaction local storage. Figure 2.3 shows an example: each transaction starts by writing to g\_temp and then using it for its own temporary storage. We have seen

Figure 2.4: **False sharing.** Transactions Tx-1 and Tx-2 will conflict using the Bartok-STM implementation which detects conflicts on a per-object basis.

this in practice when using the xlisp interpreter on Bartok-STM [Harris et al. (2006)] and also in the red-black tree implementation that Fraser used in his PhD work [Fraser & Harris (2004)] in which transactions working near the leaves of the tree will write and then read values in a sentinel node [Cormen (2001)] whose contents do not need to be retained between operations on the tree.

Fraser provides a mechanism for disabling conflict detection on such data [Fraser & Harris (2004)]; if this is mis-used then transactions may no longer be serializable.

Haskell-STM identifies the special case of *transactionally silent* stores in which a transaction makes a series of updates to a shared field, but the value at the end of the transaction is the same as at the start: the overall access can then be treated as a read rather than a write. This can increase scalability in some cases. However, not all shared temporaries are used in this way.

# 2.3.2 False sharing

False sharing occurs when the granularity at which TM detects conflicts is coarser than the granularity at which atomic blocks access data.

Figure 2.4 illustrates this with an example of a pair of transactions that conflict when run over the Bartok-STM implementation [Harris et al. (2006)]: the two transactions conflict because they both write to fields in the same object. False sharing can also occur in HTMs - for example if conflicts are detected on a per cache-line basis and two transactions update different words on the same cacheline. The paper [Zilles & Rajwar (2007)] analyze the problem of false sharing in TM implementations that use tagless ownership tables, showing that it may happen more frequently than intuition suggests.

Figure 2.5: Using commutative operations with low-level conflicts. Transactions Tx-1 and TX-2 work on objects that they look up from hashtable g\_ht under different keys. The hashtable operations may introduce conflicts if the keys hash to the same bucket in the table.

In software, false sharing can be avoided by splitting objects into portions that are likely to be accessed separately - the ability to do this is one motivation for detecting conflicts at an object-granularity because it allows the programmer to control conflicts when deciding which fields to place in the same object.

# 2.3.3 Tx using commutative operations with low-level conflicts

A further source of benign conflicts occurs when transactions use commutative operations that introduce low-level conflicts. When we say that operations A and B on a shared object are commutative, we mean that there is no difference, in executing A-before-B or B-before-A in terms of the operations' results or the subsequent behavior of the shared object. One example is the shared counter from Figure 1(a): the increment operations are commutative, but the read and writes that they perform are not.

Another example of this kind of benign conflict is lazy initialization: a data item may have its value computed on demand by the first transaction to access it. In many cases the computation can safely be performed more than once, although in other cases this is not true, e.g. in implementations of the singleton design pattern, where a common shared object is being instantiated.

Figure 2.5 shows a more complicated example: two transactions access a shared hashtable (g\_ht) and perform operations on different keys. These are

likely to conflict in the memory locations that they access if the keys happen to hash to the same bucket in the table.

Ni et al. use an example like this to motivate the use of open-nested transactions (ONTs) [Ni et al. (2007)]. Using ONTs it is possible to prevent Tx-1 and Tx-2 from conflicting by (i) running the remove and insert operations in ONTs so that they are performed directly to the hashtable when they are invoked inside transactions, (ii) defining compensating operations to roll-back any tentative operations that are made by transactions that subsequently abort, (iii) using abstract-locks to prevent concurrent transactions performing non-commutative operations on the hashtable - for example insertions under the same key.

Versioned boxes [Cachopo & Rito-Silva (2006)] provide mechanisms for dealing with some kinds of low-level conflict between commutative operations: delayed computations that execute at commit time, and restartable transactions that perform read-only operations that can be re-executed at commit time to check for benign conflicts. ONTs provide a more general-purpose mechanism to tackle many problems, including this one, but they rely on programmer care in defining the compensating actions and abstract locking discipline in order to ensure that atomic blocks using them remain serializable.

# 2.3.4 Defining commutative operations with low-level conflicts

A further source of benign conflicts occurs within the definition of commutative operations. Figure 2.6 shows an example: two transactions access a sorted linked list of integers, with Tx-1 searching the list for item 1000 and Tx-2 inserting item 10. If we assume that the list contains many elements then Tx-1 will build up a large read-set and conflict with Tx-2 and any other transactions making updates to the list in the range 1..1000.

ONTs do not provide an obvious solution to this problem: the atomic blocks consist of a single operation on a list, which must be performed atomically whether it is in an ordinary transaction, or in an open one. However, many STM implementations have included 'back doors' by which expert programmers can remove accesses from a transaction's read-set that they believe are unnecessary [Herlihy

```

atomic \{ // Tx-1 \}

atomic \{ // Tx-2 \}

f = listFind(g_1, 1000);

listInsert(g_l, 10);

}

}

List listFind(List 1, int key) {

while (1.Next.Key <= key) {</pre>

1 = 1.Next;

}

return 1;

}

bool listContains(List 1, int key) {

1 = listFind(1, key);

return (1.Key == key);

}

void listInsert(List 1, int key) {

1 = listFind(1, key);

if (1.Key != key) {

1.Next = new List(key, 1.Next);

}

```

Figure 2.6: Defining commutative operations with lowlevel conflicts. Transactions Tx-1 and Tx-2 will conflict in their accesses to the shared list g\_l holding sorted integers: Tx-1 will traverse the list up to the node holding 1000, and Tx-2 will conflict with these reads when it inserts a node holding 10.

```

while (true) {

while (true) {

atomic { // Tx-1

atomic { // Tx-2

t = getAny(g_in);

t = getAny(g_in);

if (t == null) break;

if (t == null) break;

// Work on t

// Work on t

put(g_out, t);

put(g_out, t);

}

}

}

}

```

Figure 2.7: Making arbitrary choices deterministically. Transactions Tx-1 and Tx-2 both take work items from an input input pool (g\_in), work on them, and place the results in an output pool (g\_out). A deterministic implementation of getAny will lead them both to pick the same item.

et al. (2003)]. In this case listFind could be rewritten to retain only its accesses to nodes in the vicinity of the key: earlier nodes would be removed from the read-set and concurrent updates to these nodes would not be treated as conflicts.

Using these operations correctly requires great care from the programmer. For example, using them here leads to similar search and insert functions to the non-blocking linked list algorithms by Harris [Harris (2001)] and Michael [Michael (2002)]. Furthermore, adding an additional operation to a data structure can make the implementation of existing operations incorrect. For example, if we added listDeleteFrom implemented by cutting off the tail of a list at a specified element, then it would no longer be correct to remove elements from the read-set during a call to listContains.

# 2.3.5 Making arbitrary choices deterministically

A final example of benign conflict is caused by making arbitrary choices deterministically. Figure 2.7 shows an example. Two threads repeatedly take items from a pool of input items g\_in, work on them, and place them into an output pool g\_out. All of the items must be processed, but it does not matter what order this happens in.

If we assume that the input pool is implemented by a shared queue then the two threads' transactions will conflict because they will deterministically select the first item from the queue even though, in this context, any item is acceptable.

ONTs can be used in this case: each thread executes getAny in an ONT and uses a compensating action to replace the item. There is one subtlety to beware of in this example - a transaction observing the queue to be empty can only be allowed to commit once there is no possibility of a concurrent call to getAny being compensated.

#### 2.3.6 Discussion

In this section we have introduced a number of ways in which programs can experience benign conflicts. There is a wide range of existing techniques addressing parts of this problem space:

- Converting shared temporaries into transactionally-silent stores reduces conflicts using some STM implementations (Section 2.3.1) and restructuring how data is partitioned between objects can reduce false sharing (Section 2.3.2).

- Open nested transactions can be used to avoid serializing commutative operations (Section 2.3.3) and avoid making arbitrary choices deterministically (Section 2.3.5).

- Manual optimization interfaces can be used to trim unnecessary reads from transactions read-sets (Section 2.3.4).

Common to all of these is the use of manual techniques that introduce a risk of changing the behavior of the atomic blocks as well as their performance: if they are mis-used then ONTs and read-set reduction interfaces can lead to nonserializable executions of atomic blocks.

Our goal is to explore how far we can go with techniques without that risk. The 'abstract nested transactions' in this chapter are the first step in that direction. In particular, we aim to tackle the problems of false conflicts (Section 2.3.2)

and atomic blocks using commutative operations with low-level conflicts (Section 2.3.3).

Why do we not tackle the other problems? Essentially because we believe they are best tackled elsewhere. First, it is likely that shared temporary variables can be identified automatically by modifications to the TM implementation. Second, we believe that scalable implementations of data structures involving arbitrary choices can be built over atomic blocks and ANTs using randomization techniques similar to those in Scherer's exchanger [Scherer III (2006)] – in effect, making the operations non-deterministic where possible. Third, we believe that some cases of read-set reduction are possible by compile-time analyses. Whether or not these techniques are effective is the subject of future work.

### 2.4 Abstract nested transactions

The key idea with ANTs is to identify operations like false sharing (Section 2.3.2) and commutative operations (Section 2.3.3), which are likely to be the victims of benign conflicts when executed over TM. For example, the hashtable operations in Figure 2.5 could be executed inside ANTs, as could the accesses to g\_obj.x and g\_obj.y in Figure 2.6.

We chose the name ANTs because the programmer can think of them as being handled at a different level of abstraction from the ordinary reads and writes that a transaction performs. For example, an atomic block that inserts data into a hashtable within an ANT will only be forced to re-execute if a concurrent transaction inserts a conflicting item into the table, rather than (with a typical hashtable implementation) if a concurrent transaction inserts a value that happens to hash to the same bucket.

We detect benign conflicts without programmer annotations about which operations conflict with one another. Instead, we perform extra book-keeping at run-time which lets us (i) identify benign conflicts involving ANTs, (ii) recover from benign conflicts by just re-executing the ANTs, rather than re-executing the atomic block that contains them.

The main difficulty, of course, is ensuring that it is correct to just re-execute the ANTs. We discuss the mechanisms we use to do this in Section 2.5 after first discussing the syntax (Section 2.4.1) and semantics (Section 2.4.2) of ANTs, and programmer guidelines for how to use them to improve performance (Section 2.4.3).

### 2.4.1 Syntax

The exact way that ANTs are exposed to programmers will depend on the language. In the example in Figure 2.1 (b) we suggested using ant blocks. We will use this concise form for examples in the remainder of the chapter, both as stand-alone ANT blocks (ant $\{X\}$ ) and as ANT blocks that return a result  $(Y = ant\{X\})$ .

In practice, in a language like C# or Java, it would be more natural to express ANTs using an attribute on individual method signatures, or on a class in which case all methods on the class would execute in ANTs. That would be consistent with the expectation that all operations on a given shared object would be performed through ANTs. Of course, many other possibilities can be imagined, such as creating an ANT-wrapper around an existing object, or designating an object as ANT-wrapped at the point that it is instantiated.

### 2.4.2 Semantics

ANTs are semantically transparent. In our pseudo-code, running ant{X} is always equivalent to X, no matter what operations are performed in X and what context the ANT occurs in. The same is true for ANTs returning a result.

This is an important decision: it means that the addition or removal of ANTs is based purely on performance considerations, making it easier to use feedback-directed tools to identify contention. We did consider whether we could use a different implementation of *closed nested transactions* (CNTs) instead of introducing new notation for ANTs. However, most languages that expose CNTs via nested atomic blocks choose to allow exceptions raised inside a CNT to roll-back the nested transaction. This means it is not possible to add or remove CNTs without considering semantic changes to the program.

Another important consequence of our design decision is that an atomic block containing ANTs can always be executed in *fallback-mode* in which the ANTs are

executed without any special run-time support. We use this idea to simplify our prototype implementation.

#### 2.4.3 Performance

Our implementation of ANTs is based on re-executing ANTs that experience conflicts without needing to re-execute the whole atomic block that contains them.

For instance, using the hashtable example from Figure 2.5, if the two keys hash to the same bucket then the second transaction to commit can experience conflicts from the first. However, if the remove and insert operations are implemented using ANTs then the second transaction will abort its initial execution of remove and insert and re-execute just these operations rather than needing to reexecute the entire atomic block. If the re-execution succeeds without conflict, if the result returned by remove is the same upon re-execution, and if this result is the only way that the ANTs interacted with the outer block, then the atomic block and the re-executed ANTs can be committed. Otherwise, the outer transaction is reececuted with flat nesting.

The programmer should use the following rules in order to achieve good performance:

• A given piece of data should be consistently accessed inside ANTs, or consistently accessed outside ANTs. Consider the following example:

```

atomic {

ant { g_temp = remove(g_ht, 39); }

// Work on 'g_temp'

work(g_temp);

}

```

In this example, the ANT interacts with the rest of the atomic block through g\_temp. We detect that ANT is not commutative with the outer transaction, and we restart the outer transaction and execute it in flatten mode (by flattening ANT in outer transaction).

- ANTs should constitute a small portion of the execution time of the atomic block that contains them. Otherwise, there is no practical gain by reexecuting just the ANTs.

- The programmer should mark the commutative sections of the code with ANT transactions.

# 2.5 Prototype implementation

We have implemented support for ANTs in the run time system (RTS) of the Glasgow Haskell Compiler (GHC). Aside from the subtlety discussed in Section 2.5.3 about detecting equality between Haskell values, the implementation should be applicable to other languages using similar STM algorithms. Although STM-Haskell does not expose nested atomic blocks to the programmer, our implementation of ANTs does support closed nested transactions which are used internally by the GHC RTS in its implementation of exception handling and the orElse and retry constructs for composable blocking [Harris et al. (2005b)].

GHC's existing support for STM uses lazy conflict detection and lazy versioning using transaction logs that keep track of shared memory accesses. Each transaction's log is a list of log entries containing the following fields: the *memory address* being accessed, the *old value* that the transaction expects to be stored there and the *new value* that it wants to write there. Every read or write to a shared memory location is performed first by scanning through the transaction log and, if the location is not found in the log, the memory access is performed and a new log entry is created in the log.

# 2.5.1 Changes when executing an atomic block

While executing an atomic block we differentiate between memory accesses made from within ANTs and those made from the enclosing transaction. To achieve this, the transaction log keeps entries in two separate lists: one list records the accesses in the ANTs, and the other list records all the normal transactional accesses.

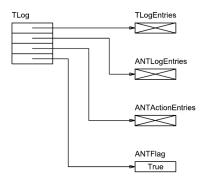

(a) A transaction starts with an empty transaction log.

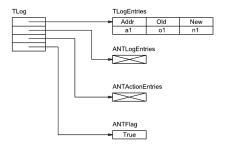

(b) The transaction writes address a1.

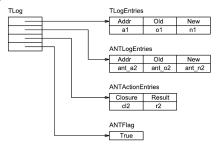

(c) The first ANT finishes, having made updates to address ant  ${\tt a2}$  and returned

(d) The second ANT finishes.

Figure 2.8: Transaction execution with ANTs enabled.

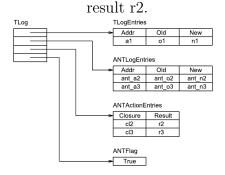

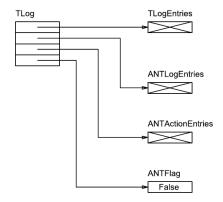

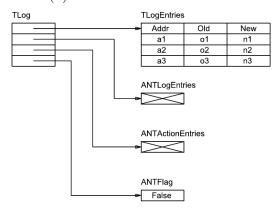

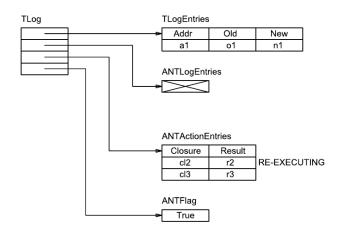

The structure of the transaction log (TLog) can be seen on the Figure 2.8 (a). The TLog has four fields. TLogEntries holds the normal transactional accesses. ANTLogEntries holds the accesses made within ANTs. ANTActionEntries records the high-level operations being performed by ANTs. Each is represented by a pair of pointers. The first points to the block of code (closure) that executes the ANT. The second points to the result that was returned by the closure when the ANT was first executed. ANTFlag is used to implement fallbackmode: if the flag is set to True, then ANTs are enabled and logging is done using the ANTLogEntries list. If the flag is set to False, then ANTs are disabled and all logging is done to the TLogEntries list.

We will show, on a small example, how these logs are used. The following example is written in Java-like pseudocode:

```

1. atomic {

2. a1 = <LARGE COMPUTATION>;

3. r2 = ant { <SMALL COMPUTATION>; }

4. <LARGE COMPUTATION>;

5. r3 = ant { <SMALL COMPUTATION>; }

6. <LARGE COMPUTATION>;

7. }

```

In Figure 2.8, we can see the structure of the TLog at different stages during the execution of the atomic block. The atomic block starts a transaction by creating an empty TLog (after executing line 1). TLogEntries, ANTLogEntries and ANTActionEntries are empty in the beginning (Figure 2.8 (a)). Line 2 modifies variable a1 with a tentative change to the TLogEntries (Figure 2.8 (b)). In line 3, the ANT uses the ANTLogEntries for its tentative update: the ANT modifies variable a2 and the change is logged in the ANTLogEntries. After the execution of the ANT, the pointer to the ANT's code and its result are saved in the ANTActionEntries (Figure 2.8 (c)). Line 4 reverts to using TLogEntries for logging. In the example case, no access to the other transaction variables occured. The ANT in the line 5 changes the variable a3 and uses the same the ANTLogEntries slot that was used by the ANT in line 3. The return value and the closure are once again saved in ANTActionEntries.

### 2.5.2 Changes when committing an atomic block

Ordinarily, at the end of an atomic block, the GHC RTS implementation of STM validates the transaction log and commits the updates to memory. The following algorithm explains how we modify the commit phase of a transaction:

```

start:

case validate(TLog):

OK : commit TLog

ANTLogEntries and TLogEntries intersect:

set ANTFlag = False

restart transaction

ANTLogEntries invalid, TLogEntries valid:

re-execute ANTActionEntries

goto start

TLogEntries invalid:

restart transaction

```

This algorithm starts by validating the entire TLog, comprising the entries in TLogEntries and ANTLogEntries. There are four cases to consider:

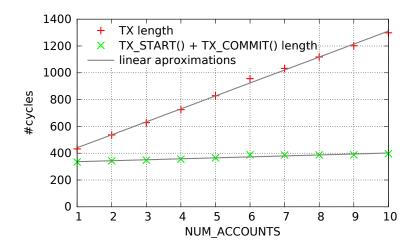

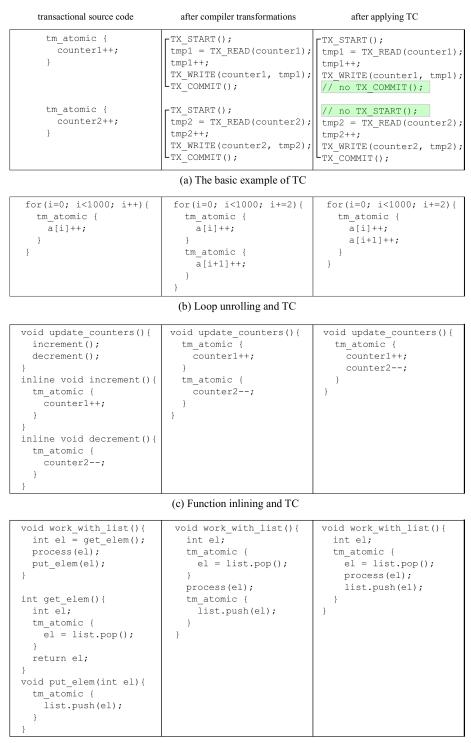

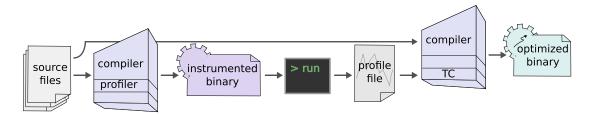

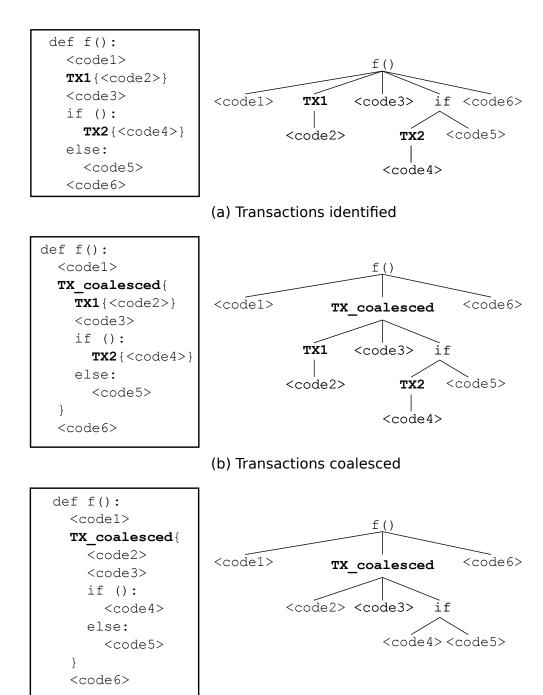

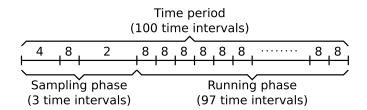

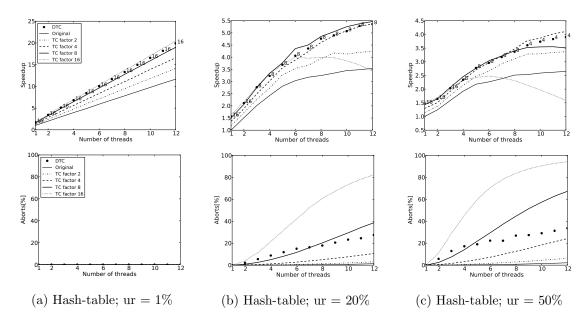

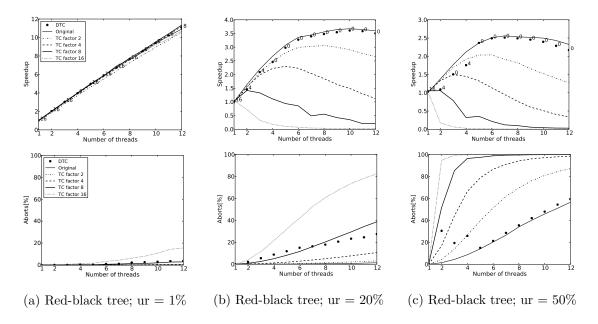

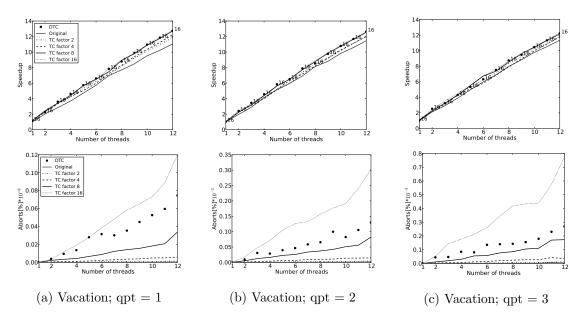

- 1. TLogEntries and ANTLogEntries are all valid. This means that there have been no conflicts at all: not with the ANTs or with the remainder of the atomic block. In this case we commit all the log entries to memory.