# Study of the theoretical bounds and practical limits of time synchronization protocols using an Ethernet FPGA platform

Carles Nicolau Jené

Tesi Doctoral UPF / 2010

Dirigida per

Dra. Dolors Sala i Batlle

Departament de Tecnologíes de la Informació i les Comunicacions

Make everything as simple as possible, but not simpler.

Albert Einstein

#### ACKNOWLEDGEMENTS

I express my gratitude to my thesis advisor, Prof. Dolors Sala, for giving me the opportunity to be part of her networking research group and for joining different projects and research events along these years.

This work would also not exist without the financial support of the Department of Information and Communication Technologies of Universitat Pompeu Fabra. Thanks

My gratitude to Prof. Enrique Cantó for his help on the daily problems with the FPGAs, and to all the tribunal for accepting the attendance to this thesis defense: Dr. Carlos Macián, Prof. Enrique Cantó, Prof. José Luís Marzo, Prof. Josep  $M^a$ . Fuertes and Prof. Boris Bellalta.

I am grateful to my research group colleagues for their time dedicated on me: Eduard, Khan, Javier, Ali and Darko.

I will be lifetime indebted to my parents for their love and faith on me, for listening to, for advising and for supporting me day after day along the years. I also wish to thank my brother, for his optimism and everlasting self-worth injections on me. Thanks.

Lastly, I want to dedicate this Thesis to my Dear Олеся. Без тбоей любви и веры в меня, я не смог бы закончит последнюю часть этого длинного и трудного пути. Спасибо тебе. Я тебя очень люблю.

#### Abstract

The goal of synchronization is to align/synchronize the time and frequency scales of all nodes within a network. In industrial applications, synchronization enables simultaneous triggering of distributed events and synchronous data acquisition at different nodes. For wide distributed systems, such as Internet, clock synchronization is advantageous for maintaining end-to-end Quality of Service (QoS).

Ethernet is the technology of choice for the future networks. Its low cost, the ever increasing data rates and low complexity and maintenance are key enablers for adopting it at all geographical scales and applications, ranging from the Network Provider to the industrial level. However, low cost and simplicity that characterizes the legacy Ethernet are only part of its attraction. The challenge is that it was initially conceived as a 'best-effort' and asynchronous oriented technology, limitations that difficult its adoption to handle, for example, time-sensitive applications in the industrial field, or carrier-class transport of services, from the Network Provider perspective. To better support new applications with tight synchronization requirements, standardization bodies and equipment manufacturers are making considerable efforts to extend its functionalities and release solutions to meet the synchronization requirements of new applications.

High accuracy time synchronization is a key enabler for offering such carrierclass QoS and handling distributed applications with stringent synchronization needs. Today's Ethernet-based approaches that deliver time synchronization rely on timestamped packets that distribute to the network. The acts of timestamping and sending the packet are crucial for achieving high accuracy synchronization, as they are exposed to a number of delay variabilities from the source to the destination node that impair the synchronization accuracy between nodes.

As the timestamping is a key component for actual synchronization protocols, the main goal in this work is to evaluate the impact of these sources of inaccuracies of Ethernet layers on the synchronization accuracy between nodes. The followed evaluation method is based on a real prototype utilizing low-cost platform Field Programmable Gate Arrays (FPGAs). The inherent complexity of these devices poses an additional challenge to the evaluation process, especially if the addressed synchronization accuracies are at the level of few nanoseconds. Therefore, this work also discusses and proposes methods to overcome platform-dependent limitations.

Additionally, this work proposes a different perspective for Ethernet technology which consists on envisioning the legacy Ethernet with a time synchronization functionality. We believe that such a new capability would allow Ethernet to better handle time sensitive applications and to be independent/compatible from/with the higher layers while keeping its initial philosophy: low-cost, simplicity and asynchronous technology.

#### Resum

L'objectiu de la sincronització és alinear/sincronitzar les escales de temps de tots els nodes d'una xarxa. En aplicacions industrials, la sincronització permet l'inici simultani d'esdeveniments distribuïts o l'adquisició de dades de forma síncrona als diferents nodes. En grans sistemes distribuïts, com per exemple l'Internet, la sincronització és beneficiosa per mantenir Qualitat de Servei (QdS) entre dos nodes distants entre si.

Ethernet és la tecnologia d'el·lecció per les xarxes del futur. El seu baix cost, les contínues actualitzacions de velocitat i la baixa complexitat i manteniment són els activadors per adoptar-la a tots els nivells geogràfics i aplicacions, des de Proveïdors de Xarxa en xarxes metropolitanes, fins a aplicacions industrials en xarxes locals. No obstant, el baix cost i simplicitat que caracteritzen a Ethernet constitueixen només una part del seu interés. El problema és que aquesta va ser originalment concebuda com una tecnologia de serveis mínims i asíncrona, dues limitacions que dificulten la seva adopció en aplicacions amb fortes restriccions de temps, tant en el camp industrial com en el transport de serveis de qualitat d'operadora. Per tal de suportar noves aplicacions amb fortes restriccions de temps, diversos organismes d'estandardització i fabricants d'equipament estan treballant activament per extendre les seves funcionalitats i llançar solucions per tal de complir amb nous requeriments de sincronització.

La sincronització de temps d'alta exactitud és clau per oferir serveis d'alt QdS i suportar aplicacions distribuïdes que necessitin fortes restriccions de temps. Les solucions d'avui dia basades en Ethernet que entreguen sincronització de temps es basen en distribuïr paquets amb una marca de temps a la xarxa. Les accions d'inserir la marca de temps i enviar el paquet són decisives per aconseguir sincronització d'alta exactitud ja que estan exposades a un nombre de variabilitats de retard des de l'origen fins el destí que empitjoren l'exactitud de la sincronització entre nodes.

Degut a que l'acció d'inserir la marca de temps és un component clau pels protocols de sincronització actuals, l'objectiu principal en aquesta Tesi és avaluar l'impacte d'aquestes fonts d'inexactitud de les capes d'Ethernet en la sincronització entre nodes. El mètode d'avaluació està basat en un prototipus real utilitzant plataformes basades en matrius de portes lògiques programables per camp (de l'anglès, Field Programmable Gate Arrays (FPGA)) de baix cost. La inherent complexitat d'aquests dispositius suposa un repte addicional al procés d'avaluació, especialment si s'adreçen exactituds de sincronització de nivells de pocs nanosegons. Aleshores, aquesta Tesi també debat i proposa mètodes per vèncer les limitacions dependents de la plataforma.

A més, aquesta Tesi proposa una perspectiva diferent per a la tecnologia Ethernet, la qual consisteix en extendre l'Ethernet inicial amb una funcionalitat de sincronització. Creiem que una funcionalitat com aquesta permetria a Ethernet suportar aplicacions amb fortes restriccions de temps amb independència de, i compatibilitat amb capes més altes tot mantenint la seva filosofia inicial: baix cost, simplicitat i tecnologia asíncrona.

#### Publications derived from this work

The results obtained from this Thesis derived on the following publications:

- ⇒ C. Nicolau, A Zero-Nanosecond Time Synchronization Platform for Gigabit Ethernet Links. In Proceedings of the 6th International Conference on Testbeds and Research Infrastructures for the Development of Networks & Communities (Trident Com), Berlin, Germany, May 2010.

- ⇒ C. Nicolau, D. Sala, E. Cantó, Clock Duplicity for High-Precision Timestamping in Gigabit Ethernet. In Proceedings of the 19th International Conference on Field Programmable Logic and Applications (FPL), Prague, Czech Republic, August-September 2009.

- ⇒ C. Nicolau, D. Sala, Flat-Soft Synchronization for Gigabit Ethernet. In Proceedings of the 28th International Conference on Computer Communications, IEEE Infocom 2009 Student Workshop, Rio de Janeiro, Brazil, April 2009.

# Contents

| Co | Contents ix |          |                                                   |     |     |

|----|-------------|----------|---------------------------------------------------|-----|-----|

| Li | st of       | Figur    | es                                                |     | xii |

| Li | st of       | Table    | $\mathbf{s}$                                      |     | xiv |

| 1  | Intr        | oducti   | ion                                               |     | 1   |

|    | 1.1         | The N    | Need for Synchronization in Ethernet              |     | 1   |

|    | 1.2         | Synch    | ronization Provisioning for IEEE 802.3 Ethernet   |     | 2   |

|    | 1.3         |          | ical Approach                                     |     | 7   |

|    | 1.4         | Summ     | nary of Contributions                             |     | 7   |

|    | 1.5         | Outlin   | ne of the Thesis                                  |     | 9   |

| 2  | Tim         | ning an  | nd Synchronization in Networks                    |     | 11  |

|    | 2.1         | _        | is Synchronization?                               |     | 11  |

|    |             | 2.1.1    | Different Meanings, Different Abstractions        |     | 11  |

|    |             | 2.1.2    | What Is A Clock?                                  |     | 12  |

|    |             | 2.1.3    | Why Do We Need Synchronization?                   |     | 12  |

|    |             | 2.1.4    | Time, Phase and Frequency Synchronization         |     | 13  |

|    |             | 2.1.5    | Timing Between Signals and Systems                |     | 14  |

|    | 2.2         | Synch    | ronization in Networks                            |     | 15  |

|    |             | 2.2.1    | Synchronous and Asynchronous Networks             |     | 15  |

|    |             | 2.2.2    | Actual Synchronization in IEEE 802.3              |     | 16  |

|    |             | 2.2.3    | Time Synchronization Protocols                    |     | 17  |

|    |             | 2.2.4    | Delay, Jitter and Timestamping                    |     | 18  |

|    |             | 2.2.5    | Synchronization Algorithms                        |     | 18  |

|    | 2.3         | High-l   | Performance Computing Platforms                   |     | 20  |

|    |             | 2.3.1    | Platform Technologies                             |     | 20  |

|    |             | 2.3.2    | FPGA-based Embedded Platforms                     |     | 21  |

|    |             | 2.3.3    | Hardware/Software Co-design                       |     | 23  |

|    |             | 2.3.4    | The Cost of Hardware Design                       |     | 23  |

| 3  | Stat        | te of tl | he Art of Synchronization in Ethernet-based Netwo | rks | 27  |

|    | 3.1         |          | luction                                           |     | 27  |

|    | 3.2         | Proto    |                                                   |     | 28  |

|    |             | 3.2.1    | Pure Hardware Approaches                          |     | 28  |

x CONTENTS

| 6        | Eva               | luatior       | 1                                                                       | 99 |

|----------|-------------------|---------------|-------------------------------------------------------------------------|----|

|          | 0.0               | Concr         | MODICIALO                                                               | 91 |

|          | 5.6               |               | usions                                                                  |    |

|          |                   | 5.5.4 $5.5.5$ | Memory Allocation                                                       |    |

|          |                   | 5.5.4         | Application Functionality                                               |    |

|          |                   | 5.5.2 $5.5.3$ | Basic Application Interface                                             |    |

|          |                   | 5.5.1 $5.5.2$ | TSU drivers                                                             |    |

|          | J.J               | 5.5.1         | Requirements                                                            |    |

|          | 5.5               |               | are Design                                                              |    |

|          |                   | 5.4.4 $5.4.5$ | Used resources                                                          |    |

|          |                   | 5.4.4         | Hardware Design Challenges                                              |    |

|          |                   | 5.4.2 $5.4.3$ | TSU Architecture Description                                            |    |

|          |                   | 5.4.1 $5.4.2$ | Distributed Timestamping                                                |    |

|          | 0.4               | 5.4.1         | Requirements and Functionalities                                        |    |

|          | 5.4               |               | tamping Unit                                                            |    |

|          |                   | 5.3.4         | Platform Functionality                                                  |    |

|          |                   | 5.3.2         | Message Handling                                                        |    |

|          |                   | 5.3.1         | Synchronization Platform                                                |    |

|          | 0.0               | 5.3.1         | Architectural Adaptations                                               |    |

|          | 5.3               | -             | vare Design                                                             |    |

|          |                   | 5.2.2         | Limitations and Challenges                                              |    |

|          |                   | 5.2.1 $5.2.2$ | FPGA Overview                                                           |    |

|          | ⊍.∠               | 5.2.1         | Platform Overview                                                       |    |

|          | $\frac{5.1}{5.2}$ |               | r-Cost Platform FPGA                                                    |    |

| 5        | 5.1               | _             | chronization Implementation for Gigabit Ethernet tives and Requirements |    |

| <b>5</b> | T:                | . C           | chronization Implementation for Circhit Eth                             | 61 |

|          | 4.4               | Conclu        | usions                                                                  | 58 |

|          |                   | 4.3.5         | Operation of the prototype                                              |    |

|          |                   | 4.3.4         | Protocol Data Units                                                     |    |

|          |                   | 4.3.3         | Synchronization Mechanism                                               |    |

|          |                   | 4.3.2         | Point to Point Layer 2 Architecture                                     |    |

|          |                   | 4.3.1         | The Control Plane                                                       |    |

|          | 4.3               | Layer         | 2 Network Model                                                         |    |

|          | 4.2               | Goals         | and Approach                                                            | 51 |

|          | 4.1               | _             | Components in Timing Message Delivery                                   | 49 |

| 4        | $\mathbf{Des}$    | ign of        | an Evaluation Platform                                                  | 49 |

|          | J. 4              | Concr         |                                                                         | 40 |

|          | 3.4               | Conclu        | Prevention                                                              |    |

|          |                   | 3.3.2         | Methods for Timestamp Accuracy Measurement and Error                    |    |

|          |                   | 3.3.1         | Error Sources                                                           | 42 |

|          | 3.3               | Times         | tamping in Ethernet-based Networks                                      |    |

|          |                   | 3.2.4         | Specific Needs, Specific Applications                                   |    |

|          |                   | 3.2.3         | Hybrid Hardware/Software Approaches                                     | 34 |

|          |                   | 3.2.2         | Pure Software Approaches                                                | 32 |

|          |                   |               |                                                                         |    |

| CONTENTS   | xi |

|------------|----|

| 0011121110 |    |

|     | 6.4.2 | Synchronization Components              | 118 |

|-----|-------|-----------------------------------------|-----|

| 0.4 | 6.4.1 | Proposed Methods                        |     |

| 6.4 | 6.3.5 | Clock Duplicity                         |     |

|     | 6.3.4 | Phase and Time Synchronization Accuracy |     |

|     | 6.3.3 | Internode Jitter                        | 105 |

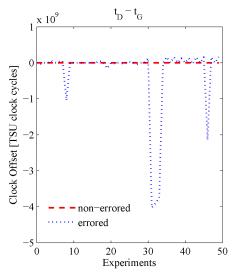

|     | 6.3.2 | Timestamping Reliability                | 104 |

|     | 6.3.1 | Clock Frequency and Drift               | 102 |

| 6.3 | Synch | ronization Evaluation Components        |     |

|     | 6.2.2 | Software System                         |     |

| 0   | 6.2.1 | Hardware System                         |     |

| 6.2 |       | ias, Methods and Goals                  |     |

# LIST OF FIGURES

| 2.1<br>2.2 | Physical quantities to represent synchronization                                                                                                                                                        | 14  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | nals, systems or networks                                                                                                                                                                               | 15  |

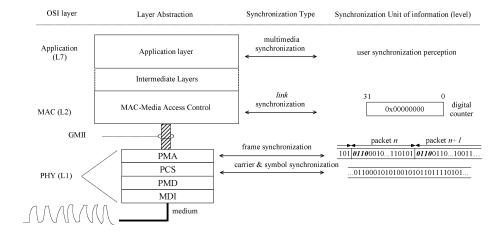

| 2.3        | Actual synchronization functionalities in the OSI model                                                                                                                                                 | 16  |

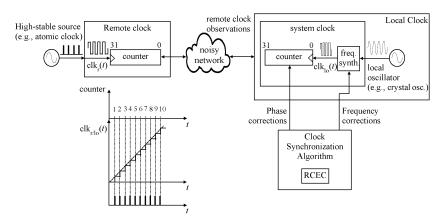

| 2.4        | Clock synchronization algorithm scheme                                                                                                                                                                  | 19  |

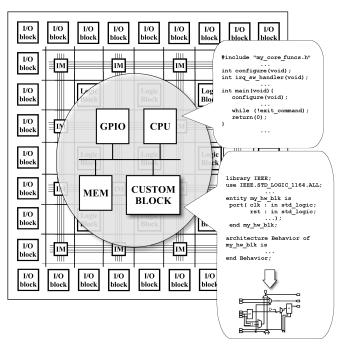

| 2.5        | Generic FPGA internal architecture. Programmable hardware ( $custom\ block$ ) is described with HDL languages. The application software executed by the CPU can be described using standard programming |     |

|            | languages, such as C                                                                                                                                                                                    | 22  |

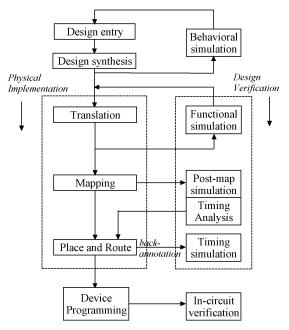

| 2.6        | Generic FPGA design flow                                                                                                                                                                                | 24  |

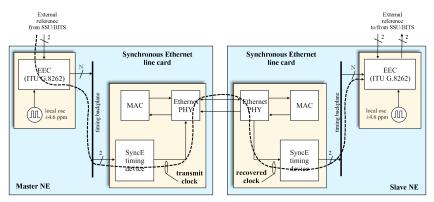

| 3.1<br>3.2 | Synchronous Ethernet cards architecture                                                                                                                                                                 | 29  |

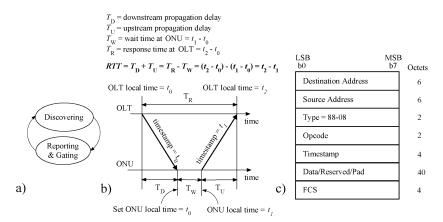

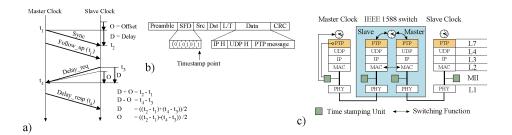

| 3.3        | (b)). Multipoint control protocols data units (MPCPDU) (c)) Synchronization procedure (a)). PTP header format (b)). PTP node                                                                            | 31  |

| ა. ა       | architecture (c))                                                                                                                                                                                       | 35  |

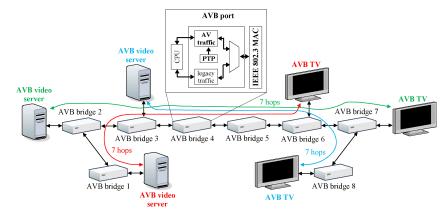

| 3.4        | Audio-Video Bridged network.                                                                                                                                                                            | 39  |

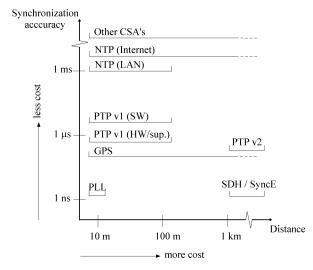

| 3.5        | Synchronization classification according to synchronization the accu-                                                                                                                                   |     |

| 3.6        | racy, geographical dispersion and cost.                                                                                                                                                                 | 41  |

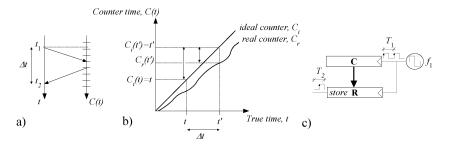

| 5.0        | Delay in a timestamp reading (a)). Clock and timestamping errors (b)). Clock reading errors (c))                                                                                                        | 43  |

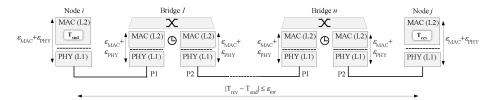

| 4.1        | Delay and delay uncertainty components of a time message delivery                                                                                                                                       | 50  |

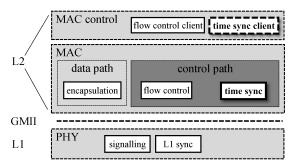

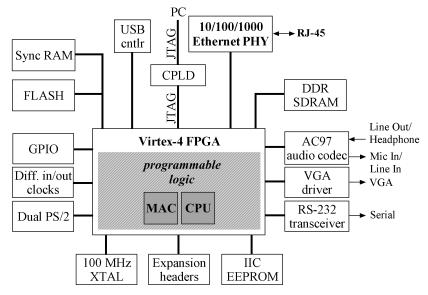

| 4.2        | Proposed time synchronization extension in the Ethernet architecture.                                                                                                                                   | 53  |

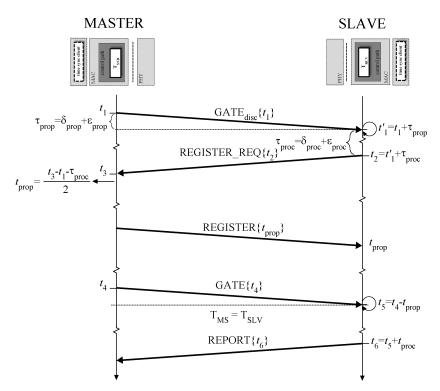

| 4.3        | Synchronization message exchange pattern                                                                                                                                                                | 54  |

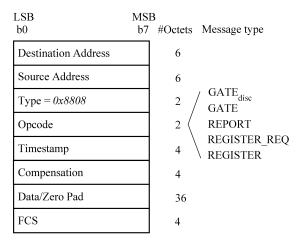

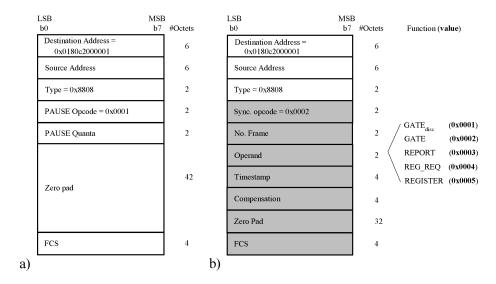

| 4.4        | Ethernet MAC control frame transporting synchronization information.                                                                                                                                    | 56  |

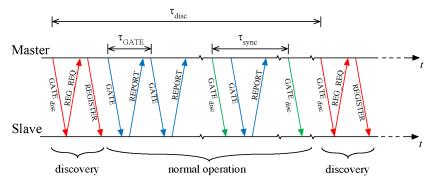

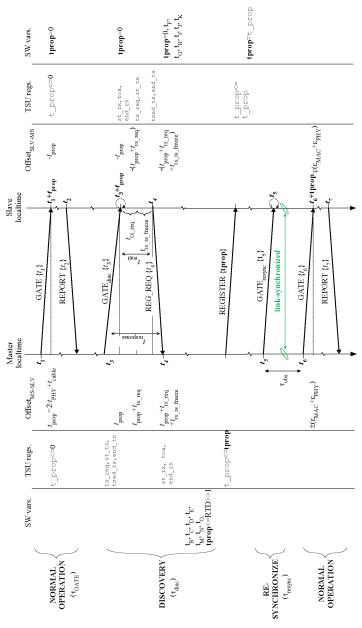

| 4.5        | Timeline of synchronization messages exchange pattern                                                                                                                                                   | 58  |

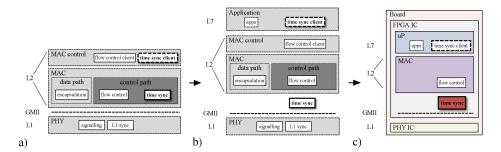

| 5.1        | Block diagram of the ML403 evaluation board                                                                                                                                                             | 62  |

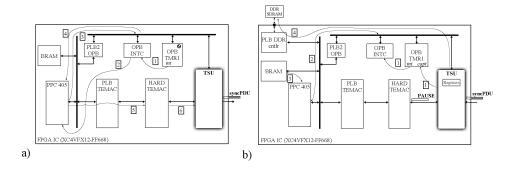

| 5.2        | Proposed time synchronization extension in the Ethernet architecture                                                                                                                                    |     |

|            | (a)). Reallocation of the synchronization functionality considering the                                                                                                                                 |     |

|            | MAC inaccessibility (b)). Mapping of the synchronization functional-                                                                                                                                    | C = |

| ۲.۵        | ity into the physical components of the platform FPGA (c))                                                                                                                                              | 65  |

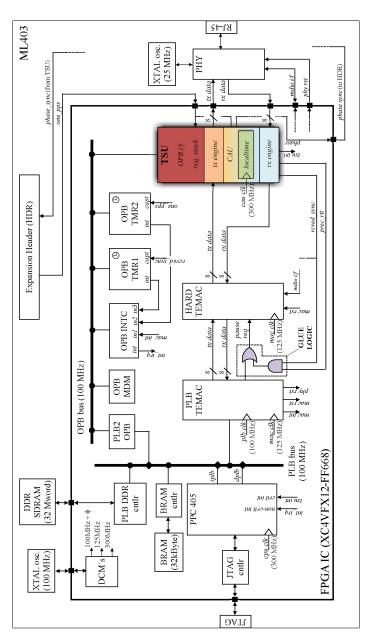

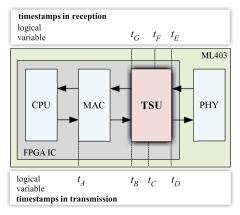

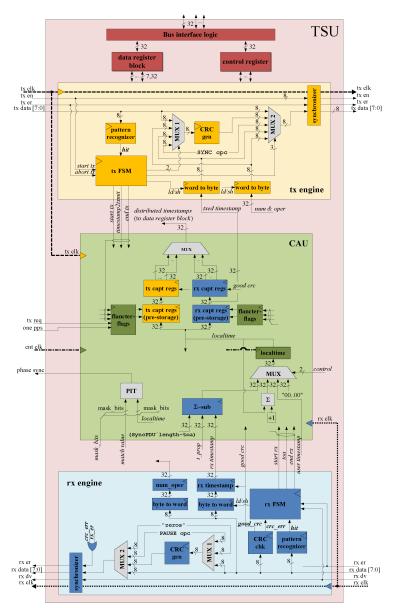

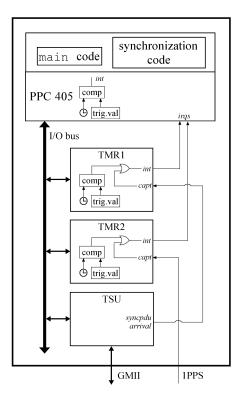

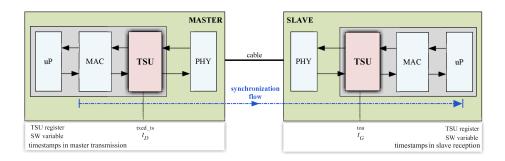

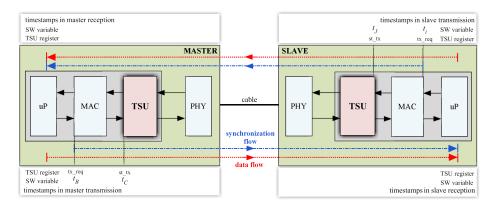

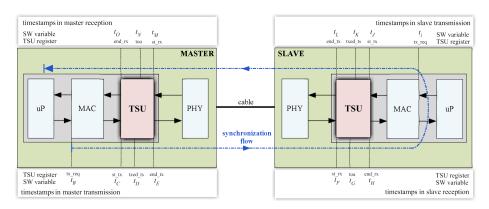

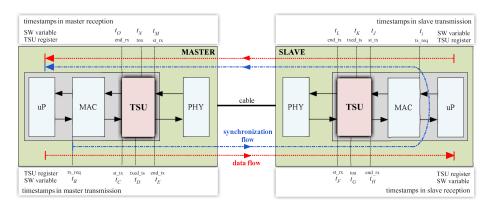

| 5.3        | Embedded platform architecture and TSU allocation                                                                                                                                                       | 67  |

| 5.4        | Pause control frame (a)). Synchronization protocol data unit (syncPDU)                                                                                                                                  |     |

|            | (b))                                                                                                                                                                                                    | 70  |

| LIST OF FIGURES | xiii |

|-----------------|------|

|-----------------|------|

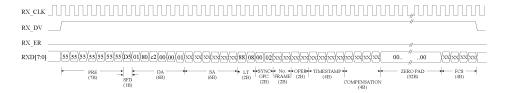

| 5.5  | Steps involved in sending (a)) and receiving (b)) a sync<br>PDU                                                                         | 71  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

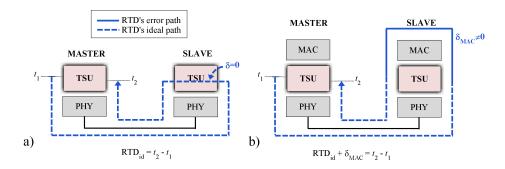

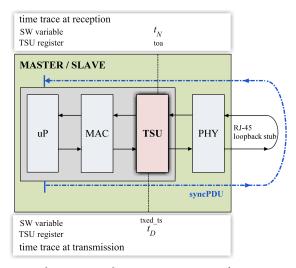

| 5.6  | syncPDU journey with no inter-layer delay (a)). Platform's syncPDU journey, with additional delay to regenerate the syncPDU reply (b)). | 74  |

| 5.7  | Distributed timestamping architecture                                                                                                   | 75  |

| 5.8  | PAUSE frame transmission waveform across MAC interface (adopted                                                                         | 10  |

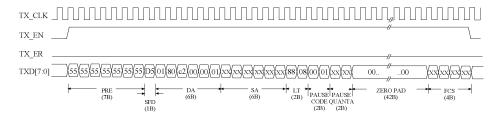

| 0.0  | from [Xilinx, Inc. (2007b)])                                                                                                            | 76  |

| 5.9  | Internal architecture of the Timestamp Unit                                                                                             | 78  |

| 5.10 | SyncPDU frame reception waveform across PHY interface (adopted                                                                          |     |

| 0.10 | from [Xilinx, Inc. (2007b)])                                                                                                            | 79  |

| 5.11 | TSU without timestamping reliability mechanism (a)). TSU with                                                                           |     |

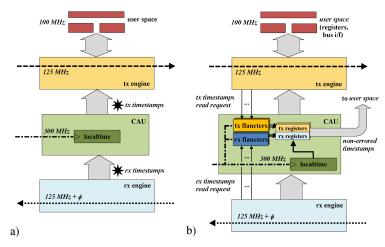

| _    | timestamping reliability mechanism, with flancter-flags. (b))                                                                           | 83  |

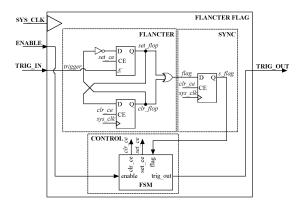

| 5.12 | Flancter-flag circuit.                                                                                                                  | 83  |

|      | Software layered architecture                                                                                                           | 85  |

|      | Basic application interface (BAI)                                                                                                       | 89  |

|      | Message exchange pattern.                                                                                                               | 92  |

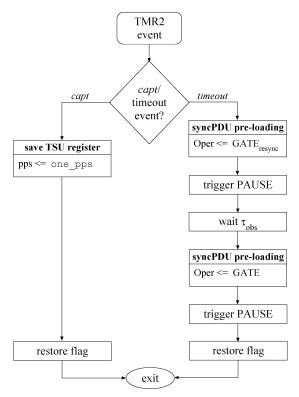

|      | TMR1 event handling (Master). GATE message transmission (at in-                                                                         |     |

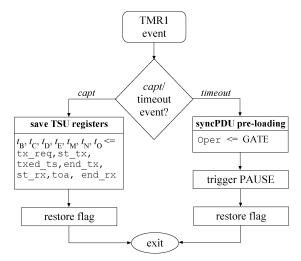

|      | tervals of $\tau_{GATE}$ ), and syncPDU arrival                                                                                         | 93  |

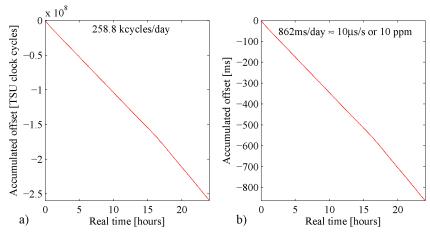

| 5.17 | TMR2 event handling (Master). $GATE_{sync}$ message transmission (at                                                                    |     |

|      | intervals of $\tau_{resync}$ ), and 1PPS events                                                                                         | 94  |

| 5.18 | TMR3 event handling (Master). Start of the discovery process (at                                                                        |     |

|      | intervals of $\tau_{disc}$ )                                                                                                            | 95  |

|      | TMR1 event handling (Slave)                                                                                                             | 96  |

| 5.20 | TMR2 event handling (Slave). Subroutine for storing 1PPS events                                                                         | 96  |

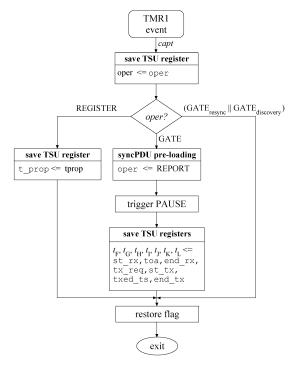

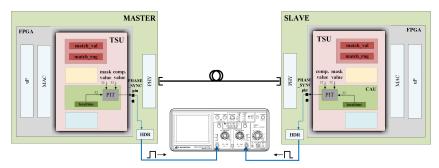

| 6.1  | Synchronization platform setup                                                                                                          | 101 |

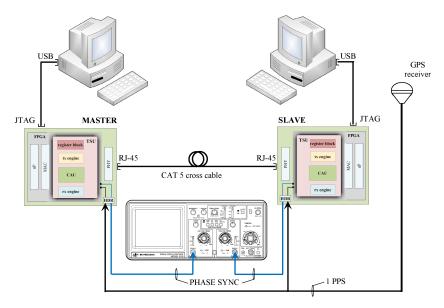

| 6.2  | Relative clock drift, expressed in TSU clock cycles (a)) and in ms (b)).                                                                |     |

| 6.3  | Platform setup for testing the timestamping reliability                                                                                 |     |

| 6.4  | Effect on timestamping reliability with and without flancter-flags                                                                      |     |

| 6.5  | MAC latency measurement setup                                                                                                           |     |

| 6.6  | Platform setup for PHY latency and jitter measurement                                                                                   |     |

| 6.7  | Platform setup for RTD evaluation.                                                                                                      |     |

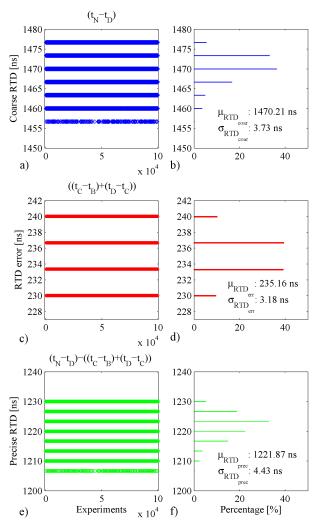

| 6.8  | RTD calculation. RTD with no internal processing compensation                                                                           |     |

|      | (a,b)). Internal processing time (RTD error) (c,d)). RTD with in-                                                                       |     |

|      | ternal processing compensation (e,f))                                                                                                   | 110 |

| 6.9  | Setup used for the evaluation of time synchronization                                                                                   | 111 |

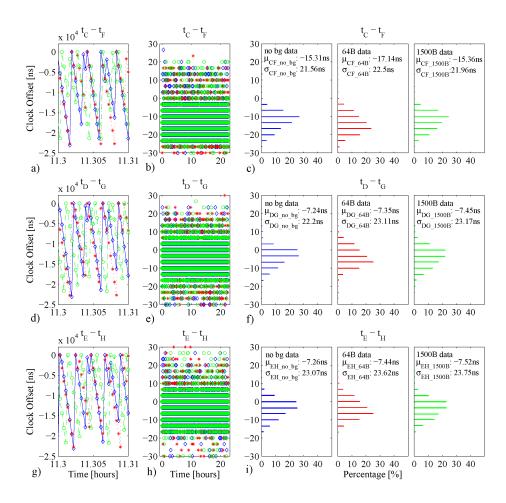

| 6.10 | Evaluation of the synchronization accuracy (24 hour experiments). a,                                                                    |     |

|      | d, g) Running clock offset (in $\sim 36~s$ . window). b, e, h) Clock offset                                                             |     |

|      | series after the re-synchronization. c, f, i) Distribution of plots b, e,                                                               |     |

|      | h, for a each load scenario.                                                                                                            |     |

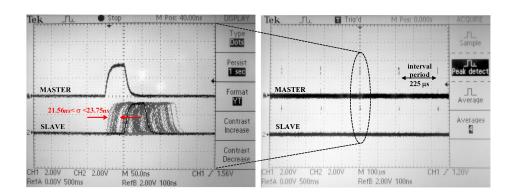

| 6.11 | Setup the evaluation of time and phase accuracy                                                                                         |     |

| 6.12 | Phase error of the synchronized timing signal (right). Re-synchronization                                                               |     |

|      | variability (left)                                                                                                                      | 115 |

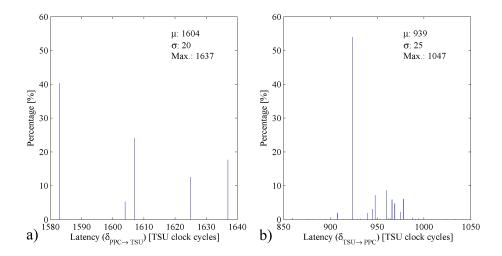

| 6 I3 | Division Call to the Call DDC: DCT / \\ 1 mcTT                                                                                          |     |

| 0.10 | Distribution of the register transfer delays: PPC to TSU (a)) and TSU                                                                   |     |

| 0.10 | Distribution of the register transfer delays: PPC to TSU (a)) and TSU to PPC (b))                                                       | 117 |

| 7.1  | • • • • • • • • • • • • • • • • • • • •                                                                                                 |     |

# LIST OF TABLES

| 3.1 | Timing requirements of the main wireless technologies 40                                                   |

|-----|------------------------------------------------------------------------------------------------------------|

| 5.1 | Summary of the hard-IP blocks and programmable resources of the Virtex-4 (XC4VFX12-FF668)                  |

| 5.2 | Summary of the programmable resources utilized for TSU implementation and percentage of the overall amount |

| 5.3 | Description of the distributed timestamps (logical variables) collected                                    |

|     | during a syncPDU transmission and reception                                                                |

| 5.4 | Data register definition within TSU's register block 81                                                    |

| 5.5 | Control register definition within TSU's register block 81                                                 |

| 5.6 | Summary of the programmable resource utilization of the TSU (ex-                                           |

|     | pressed as used amount and percentage)                                                                     |

| 5.7 | Low-level C drivers for read/write access from/to the TSU 88                                               |

| 5.8 | Association of the software interruption handlers with BAI's hardware                                      |

|     | blocks                                                                                                     |

| 6.1 | Absolute error at different error rates and intervals                                                      |

| 6.2 | Number of clock cycles spanned by one_pps event registers at every                                         |

|     | second, and percentage over one day                                                                        |

| 6.3 | Accumulated clock offset at the rate of 10 ppm                                                             |

| 6.4 | Latency and jitter measurements of the Xilinx MAC core (expressed                                          |

|     | in number of TSU clock cycles, nanoseconds and percentage over 200k                                        |

|     | samples)                                                                                                   |

| 6.5 | Round trip delay (RTD) and jitter (RTJ) measurements of 88E1111                                            |

|     | Marvell's PHY (expressed in number of TSU clock cycles, nanoseconds                                        |

|     | and percentage over 200k samples)                                                                          |

| 6.6 | Number of TSU clock cycles to perform the transfer from CPU's                                              |

|     | counter to TSU's counter, and vice versa (percentage over 100k samples). 116                               |

# 1.1 The Need for Synchronization in Ethernet

In the context of packet-based computer networks, synchronization is becoming a critical factor since the advent of the World Wide Web. Whereas in the early days it was only the exchange of 'best-effort' data, it now encompasses time-sensitive data, such as high-quality voice and video communication and a myriad of services that need exact knowledge of global time to render consistent results. Traditionally, time-sensitive data was transported by digital networks, such as Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH). Digital networks are costly infrastructures in which the data transportation relies on providing precise and controlled timing to the overall equipment. The principle of digital networks consists on providing a high-stable timing signal coming from an expensive clock (e.g., a Primary Reference Clock (PRC)) to the physical layer of each node of network, thus making the network fully synchronous. Nowadays, access transport networks are evolving from dedicated-service, narrowband and highly bit-optimized PDH/SDH-based networks to multiservice, wideband and over-provisioned packet-based networks. This turn has been driven by an increasing demand of new broadband services, such as carrier-class voice, video over IP, IPTV, new applications, such as mobile wireless broadband services, and packet-switched concepts. All these applications demand synchronization accuracies that range from sub-microsecond down to nanosecond levels.

For high-capacity low-cost services to be commercially viable, telecommunication operators must decrease their per-bit production costs. Indeed, the technology that is on the spotlight since many years is Ethernet. It is becoming the technology of choice at local, metropolitan and wide area networks (WAN), as it offers simplicity, high data rates, plug'n'play network connection and more bandwidth at a lower cost than traditional WAN services. Ethernet was designed as a two-layer technology. In the Layer 2, or the data link layer, there was specified how the data is organized and sent over the network. In the Layer 1, or the physical layer, there was described the network medium and the signalling specifications. Currently, it operates from 1Mbps to 100Gbps, in different Layer 1 technologies (optical and electrical), and over large distances and different topologies (point-to-point and shared). The line capacity upgrades of Ethernet over the past years aimed at accommodating the increasing bandwidth needs many times. Modifications on the capacity do not involve any protocol functionality exten-

sion, but on over-provisioning the architecture to be able to provide quality of service<sup>1</sup>(QoS).

The work in this Thesis commits the adoption of Ethernet to Provider Networks and industrial field through a small extension of the existing architecture. The introduction of provider capabilities was initiated with the Ethernet in the First Mile (EFM) specification [IEEE Std. 802.3 (1998)] covering all type of broadband residential deployments (copper, point-to-point fiber and passive optical networks (EPONs)), together with the management capabilities. As far as the synchronization is concerned, EPON specification introduced a time synchronization capability based on timestamping for the purpose of coordinating the slotted access of point-to-multipoint networks. The synchronization capabilities in EPON were entirely defined at Layer 2. As far as the industrial field is concerned, Ethernet has attracted interest only recently. Actually, a number of vendors are offering industrial communication products based on Ethernet and TCP/IP as a means to interconnect field devices to the first level of automation. Others restrict their offer to communication between automation devices such as programmable logic controllers and provide integration means to existing fieldbuses [Decotignie (2005)]. In the area of industrial communications, synchronization is also delivered by means of timestamps within specific messages.

Kopetz was the first author who pointed that the synchronization accuracy among networked nodes using timestamping techniques is mainly affected by the sum of time variabilities during the insertion of the time information in the message, the transmission and propagation of the time message, and during the reception at the receiver side [Kopetz & Ochsenreiter (1987)]. Proper tuning of these main parameters will lead to a better synchronization. In order to know which are the synchronization limitations of Ethernet in shared topologies, the EPON timestamp and synchronization functionality should be refined in terms of jitter and resolution. Thus, this Thesis aims at characterizing accurately a Layer 2 synchronization mechanism for native Ethernet. A proper optimization would allow Ethernet to better support time sensitive applications with optimal QoS. Our objective is to improve Ethernet capabilities within an acceptable range while respecting its architecture simplicity principle.

#### 1.2 Synchronization Provisioning for IEEE 802.3 Ethernet

Ethernet-based networks are asynchronous networks, i.e., they do not share a common timing signal as in e.g., SDH, but each node's physical layer is provided with a low-cost timing source for pacing the transmission and reception of the information. This principle decreases Ethernet's cost dramatically and allows to embrace a wide set of technologies built on top of it. The timing source is generally a low-cost quartz crystal oscillator from which a square clock signal is obtained and used to pace other circuitry within the node. Ethernet's Layer 1 are provided with hardware synchronization blocks that reconcile/synchronize

<sup>&</sup>lt;sup>1</sup>In this Thesis term quality of service (QoS) refers to achieved service quality rather than the resource reservation control mechanisms.

the local timing from the neighbor node, thus creating a network of *free-running* nodes capable to communicate at any time and relegating services running on upper layers from synchronization.

Accordingly, synchronization transfer methods in Ethernet networks rely on synchronization protocols that distribute the timing using time marks (timestamps) inside the messages. Synchronization protocols define the message semantics, the rules for exchanging messages and the state information to be kept by the node. In a synchronization network there is usually a main node, commonly known as best clock, to which all the other nodes of the network synchronize to. Although there are different communication schemes (i.e., unicast, multicast or broadcast), the essence of synchronization protocols is similar: there is a periodic exchange of time messages from which the propagation delays are inferred and used to improve the synchronization. The nodes that need to be synchronized adjust their respective clocks accounting for the propagation delay. The more accurate, precise and deterministic the delay is, the more accurate the synchronization between nodes will be. It is precisely on the calculation of this parameter where synchronization fails; to calculate the delay, a node utilizes the remote timestamps which arrive indeterministically due to jitter sources present along the path of the message and within the same node.

To provide synchronization capabilities to Ethernet, several approaches have been proposed. Two distinguishable aspects exist between them: whether they provide synchronization in the form of frequency or time/phase, and whether they use dedicated hardware to carry out critical functions or not. The combination of choice depends on the synchronization needs of the application. For instance, backhaul cellular technologies require precise frequency and phase synchronization to the level of few parts-per-billion (ppb) and microseconds ( $\mu s$ ) to efficiently share the radio access; time division multiplexed (TDM) networks have also the strong requirement of few ppb's frequency synchronization across the entire network, as accurate multiplexing and demultiplexing of data depends on that capability; a distributed measurement network running at ten gigabit speed requires time synchronization accuracies below few tenths of nanoseconds (ns) to distributedly log the interarrival times of the packets.

A technology that is gaining momentum among Tier 1 telecommunication operators to distribute frequency through Ethernet is Synchronous Ethernet (SyncE) [ITU-T G.8262 (2007)]. SyncE distributes frequency directly to the Ethernet physical layer. SyncE transceivers are provided with PLL-based mechanisms that pass timing from node to node in the same way timing is transported in, e.g., SDH. In IEEE 802.3 Ethernet networks, frequency synchronization is not mandatory as they do not need timing synchronization to work and, most important, they have been optimized for cost efficiency. Considering these requirements, other technologies built over Ethernet, such as the Network Time Protocol (NTP) [Mills (1992b)], or the more recent Precision Time Protocol (PTP)/IEEE Std. 1588 [IEEE Std. 1588 (2008)] are being developed and enhanced for high-quality time distribution.

Key to understanding synchronization in Ethernet networks is that each node suffers from an unsurmountable physical limitation: the local oscillator's fre-

quency drifts at a nominal rate of  $\pm 50\mu s/s$  (100 ppm), thus making nodes to drift apart few seconds per day from the ideal rate. Moreover, the drift rate can change due to temperature variations or aging, thus further impairing the synchronization. Oscillators' drift is the cornerstone problem of all synchronization mechanisms that drive synchronization protocols to re-synchronize periodically using messages. It is precisely in the process of the time message exchange where the synchronization accuracy between nodes is more impaired because the messages suffer from two error sources: fixed propagation delay and propagation delay variability (or jitter). Synchronization protocols face the complex task of estimating and cancelling the fixed propagation delay piggybacked on each timestamp. In the case of symmetric paths, the propagation delay can be inferred optimally (from the round trip delay (RTD)). On the other hand, jitter cannot be eliminated, but it has to be accommodated by the applications running at upper layers. The jitter is critical in synchronization and it raises from different sources in the path of the message:

- ⇒ Internode jitter. Corresponds to the time variability of an inbound/outbound synchronization message to cross the layered-stack. In IP-based synchronization schemes like PTP and NTP, this time penalty stems from the priority-based behavior of the operating system which queues the time message for a variable amount of time before sending. The most accurate solution to eliminate the gross part of the internode jitter is to generate and introduce the timestamp after the message has been queued. To carry out this approach, it is necessary to use specialized hardware capable to recognize the time packet while it is being sent/received. A common practice in Ethernet architecture consists on triggering the timestamp between the Media Access Controller (MAC) and the Ethernet transceiver (PHY). The paradigm of generating and inserting the time in a message by means of dedicated hardware is known as hardware timestamping. Software timestamping alludes to the same concept except that the timestamping process run on top of the jittery schedulling tasks of the operating system. Both timestamping paradigms establish the division line of performance and cost among the time synchronization protocols. Software-based protocols can be implemented in low-cost commodity hardware at expenses of poor synchronization accuracy, while hardware-based synchronization protocols leverage specialized hardware to generate timestamps with very low jitter. The use of hardware reports improvements of three or four orders of magnitude on the synchronization accuracy in many implementations.

- ⇒ Network jitter. Corresponds to the time variability of a synchronization message go across the layered-stack of the intermediate elements from a source node to a destination node. The network jitter is aggravated by the residence time variability that the packets experiment in the internal queues of the network elements (NE) like switches and routers. As switches are store-and-forward devices, the packets received on one port are stored temporarily while the device figures out which forwarding port(s) to send them

to. The time the packet is delayed is called the residence time. In scenarios with dense and variable network traffic, the residence time is variable and unpredictable. Moreover, topologies with several NEs suffer from the jitter introduced by each element, thus further aggravating the end-to-end synchronization. Although switch and router technologies and architectures have greatly improved over the years, packet delay variability (PDV) is still the more relevant limiting point to achieve accurate synchronization. Synchronization protocols, like PTP, tackle this problem in two ways. First, by defining profiles, i.e., specific network topologies with a maximum number of NEs to accommodate a permissible level of jitter. And second, by leveraging hardware assistance. To achieve ns-level synchronization, hardware assistance is a must. Hardware-assisted switches subtract, in the same NE, the time that a message is retained in the queue and modify the time information when the message is being transmitted. This technique is not widely available yet in commercial off-the-shelf products because there can be diminishing returns where more is not always better nor necessary. In the context of PTP these switches are called boundary and transparent clocks.

The actual technological trend in communication nodes points toward an increase in the use of specific hardware for the support of communication tasks. Although pure software systems have greatly increased their performance, hardware domains still achieve orders of magnitude better results. Known truth is that software systems feature more flexibility and short time-to-market than hardware systems, but the actual rapid evolution and creation of new standards and protocols has pointed hardware manufacturers towards more flexible and programmable hardware platforms to their products. This fact, taken in conjuction with the integrated circuit (IC) technological evolution (chip size reduction, power reduction and speed increase) and the integration of multiple systems in a single chip (SoC), is facilitating the integration of new functions into the hardware domain. A technology that is gaining force in the market is Field Programmable Gate Array (FPGA). FPGAs are programmable devices that have been developed as a form of intermediate approach: hardware design on a high-performance platform, optimal resources and programmability as the devices/systems within can be reprogrammed. In broad stokes, state-of-the-art FPGAs integrate thousands of programmable devices, hundreds of third part Intellectual Property (IP) blocks and microprocessor cores into one single part.

Over the last decades, the world of computing platforms has been progressing towards very complex systems for the sake of better efficiency. Actually, computing platforms are provisioned with extra resources capable to communicate at dizzying speeds. Architecture complexity has lead to the need to consider platforms as "black boxes" in order to simplify the design process. On the one hand, abstractions simplify the programmability as the designer 'only' needs to fouce on the application functionality. On the other hand, the fact of considering systems as black boxes lead to omit the hardware's behavior. Computation relies on hardware, and hence it cannot be ignored. Hardware systems are an integral part of the design, and thus the software must be designed to operate with it

accordingly. High-level programming languages and traditional programming is time-agnostic and provide functionality through ordering. Computer systems are provided with operating systems, with a rich suite of services that lack of a notion of time. To put an example, higher-level modern programming languages do not support the use of periodic interruptions in their semantics or counting the number of microprocessor clock cycles of a piece of code in a critical inner loop. Physical systems are intrinsically concurrent and temporal. Actions and reactions happen simultaneously and over time, consequently time plays an essential part in the system's behavior.

Embedded systems are on the other side of computing platforms. are small computers that adhere to the world of embedded computing, characterized for having a limitation in the number of hardware resources and a direct interaction with them. In the embedded system world, time matters, and thus embedded-system applications are designed with low-level programming languages, more capable to provide notion of time and direct mapping to the hardware resources. For these reasons, embedded programming challenges to manage common hardware resources efficiently, reliably and, most important, in a predictable amount of time. In this view, the evaluation of synchronization protocols in embedded platforms entails an added problem that is predictability, or the lack of deterministic response and execution times in the interaction between software and hardware. Although FPGAs with processor cores provide an alternative architectural division between hardware and software, when time synchronization is needed at the level of ns, their interaction becomes more stringent. The software part, the "intelligent" side, hosts protocol management functions and rather complex arithmetic operations, while hardware is consigned to repetitive, noncomplex but time-restrictive tasks. Hardware is put at the service of executing the requests of the software.

To summarize, the level of synchronization in Ethernet-based packet networks depends on the amount of jitter that exists between nodes. Jitter becomes more gross as more high in the protocol stack the timestamps are obtained. In IP-based networks the major part of the *internode jitter* is introduced by the stochastic behavior of the operating system. In pure Layer 2 Ethernet-based networks, the jitter sources arise from the time variabilities committed by the hardware mechanisms in the MAC and the PHY of the end nodes to transmit, propagate and receive the messages. This work focuses on accurately and precisely deriving the jitter at and below the MAC.

To tackle the problems stated above, this Thesis introduces a time synchronization functionality at Layer 2 for IEEE 802.3 Ethernet based on a readaptation of the EPON synchronization protocol. The synchronization functionality resides at the control path of the MAC, while the protocol is part of the MAC control sublayer. The protocol defines a set of control headers for delivering the synchronization and a message exchange pattern. The proposed model is implemented and evaluated in a low-cost FPGA-based embedded platform. The core of the time functionality falls in the hardware part, in the form of a timestamping block that permits to timestamp on-the-fly the time messages. The timestamping block characterizes for having a high-resolution time counter that

permits to timestamp very precisely the time messages. The timestamping block also records the time of flight of the time messages for deriving the jitter of the MAC and the PHY.

# 1.3 Technical Approach

This Thesis aims at evaluating what is the potential of Ethernet as a technology for delivering high-precision time synchronization. To that end, this work follows a methodology based on analysis, design and implementation:

- ⇒ Analysis & study. First, the existing technologies for delivering synchronization in Ethernet networks need to be explored and carefully studied to know their shortcomings and limitations. At the same time, a study of the actual synchronization needs of specific applications and services will give a set of specifications for the design phase.

- ⇒ Design. This phase comes up with a new model for IEEE 802.3 Ethernet to provide a time synchronization service. The design extension is fully prospected at Layer 2 and re-adopts the synchronization mechanism introduced in EPON.

- ⇒ Implementation and Evaluation. Ethernet functions are defined in the hardware domain, thus our conceptual design will be implemented in a hardware platform, a low-cost generic platform FPGA. As hardware design is an inherently complex task due to the number of physical limitations incurred in the design process, some parameters are very difficult to verify correctly. This Thesis will introduce a set of methods that will allow a correct verification of the proposed synchronization functions with independence of the platform limitations. Hence, this work will emphasize the implementation and evaluation aspects of the proposed mechanism.

#### 1.4 Summary of Contributions

The contributions of this Thesis are:

- ⇒ An architectural extension proposal for IEEE 802.3 Gigabit Ethernet consisting on the introduction of a time synchronization functionality at Layer 2 (see Chapter 4). The synchronization function re-adopts the ranging procedure of the Ethernet Passive Optical Network (EPON) synchronization protocol. The function is fully prospected in the control plane of the MAC and introduces new control messages.

- ⇒ An optimal implementation of the time synchronization mechanism on a low-cost platform FPGA (see Chapter 5). The core of the mechanism is a hardware timestamping unit (TSU) that allows to timestamp on-the-fly the ingress/egress control frames. The TSU contains a high-speed time counter

that allows to timestamp the frames and synchronize with the maximum allowed precision given by the platform,  $3.\widehat{33}$  ns.

The implementation of the synchronization function on a generic platform, the use of a high-resolution counter and the oscillator clock drift entail several challenging problems. The first one and most critical is that the clock frequency of the counter is asynchronous to the rest of the clock signals within the TSU. This can lead to unpredictable errors [J. Stephenson (Altera, Corp.) (2009)] in the captured timestamps that can totally invalidate the evaluation results (see Section 6.3.2). Second, the propagation time derived in the ranging procedure is not accurate, as it suffers from the processing delays within the node (see Sections 5.5.4 and 6.3.4). Third, the accumulated clock offset due to the clock drift when targeting synchronization accuracies at the level of nanoseconds impairs seriously the synchronization accuracy, therefore the real offset cannot be correctly verified (see Section 6.3.1).

The need to address these three limitations have lead to the following relevant contributions:

- ⇒ A hardware mechanism based on a digital circuit called *flancter* that totally prevents from timestamping errors in presence of multiple asynchronous clock sources (see Section 5.4.4). Our *flancter-flag* blocks accommodate the counter frequency of the TSU with the transmission and reception frequencies of the MAC and PHY interfaces. This block can be re-used in other designs with disparity of frequencies.

- ⇒ A method to calculate with high accuracy the propagation time in the ranging process, and thus to synchronize optimally. The method consists on capturing several distributed timestamps along the MAC layer during the synchronization message journey and re-use them to subtract the node processing delays. To be able to obtain these timestamps, the TSU architecture has carefully been designed (see Sections 5.4.2 and 5.4.3).

- ⇒ Two methods to evaluate the time synchronization accuracy with independence from the oscillator drift. The first one is based on the capture and comparison of the distributed timestamps between two nodes. The second one is based on the comparison of the instantaneous time of two remote nodes using programmable interval timers (PIT) (see Section 6.3.4).

The combination of the synchronization protocol, the hardware timestamping and a careful analysis of the platform architecture has rendered synchronization accuracies of zero nanoseconds in a point-to-point configuration (see Section 6.3.4).

#### 1.5 Outline of the Thesis

After introducing the problem and the objectives in this chapter, the remainder of the thesis is organized in six chapters as follows:

Chapter 2 provides a summary of terms and concepts most used and relevant to this Thesis.

Chapter 3 reviews the state of the art work most related to this Thesis and summarizes the actual needs for synchronization of end-users and applications. It also reviews the problems that timestamping mechanisms usually suffer from.

Chapter 4 presents the first contribution of this Thesis, which is a time synchronization model for Gigabit Ethernet. It describes the followed conceptual approach while leaving aside implementation details.

In Chapter 5, we cover an important part of this Thesis which is the implementation of our conceptual model in a platform FPGA. Here, we present almost the rest of the contributions and explain in detail the main design components of our synchronization platform: the main hardware subblocks of our timestamping unit, the concept of distributed timestamping to re-synchronize and calculate the RTDs optimally and the *flancter-flag* blocks to prevent from timestamping errors.

Chapter 6 presents the experimental results for characterizing the timestamping mechanism, the internode jitter and the synchronization accuracy achieved in a point-to-point configuration. The last contribution of this Thesis is presented here: a method to evaluate the synchronization accuracy at nanosecond level with independence of the clock drift.

In Chapter 7, we draw conclusions and identify directions for future work.

#### § 2. Timing and Synchronization in Networks

This chapter presents most relevant terms and concepts used in this thesis. Especially it aims at differentiating the different ways that the term synchronization can be understood, along with its metrics and the methods to disseminate synchronization in a network of geographically dispersed nodes. Last, this chapter gives a tradeoff of actual computing platforms and why this thesis uses a platform FPGA as a validation tool.

# 2.1 What is Synchronization?

Synchronization is the act or result of synchronizing, namely, to represent or arrange events to indicate coincidence or coexistence [Merriam-Webster, Inc. (2010)]. In the context of networks, synchronization can be understood as the process that deals with the distribution of time and frequency across all the nodes of the network [Bregni (2002)]. Thus, the goal of a synchronization process is to align (i.e. synchronize) the time and frequency scales of all clocks of a network by using the communication capacity of their interconnecting links.

#### 2.1.1 Different Meanings, Different Abstractions

The term synchronization has different meanings and challenges depending on the area of work, the level of abstraction and the context. For a software specialist, synchronization deals with the consistency between two files, i.e. which of the two files were lastly modified. For an expert on digital communications, the term is familiar on the acquisition and tracking of a clock in a receiver, with reference to the periodic timing information contained in the received signal. And for a digital circuit designer, synchronization deals with the circuit mechanisms to ensure reliable data passing among different groups of logic paced at different clock frequencies. Regardless of the abstraction level and area of expertisement is referring to, synchronization in digital systems is crucial as it ensures correct information flow and that operations follow in the correct order to obey a precedence and timing to obey deadlines. Each level of abstraction relies on the features of the abstraction level below and hides unnecessary details to the level above. Whichever is the abstraction criterion in describing hardware and software systems, the entities (networks, nodes, systems, blocks) are mutually correlated at any level, and the correct interoperation relies on a correct temporal coordination [Messerschmitt (1990)].

#### 2.1.2 What Is A Clock?

The term *clock* has also different meanings depending on the level of abstraction and the context too. In the world of electronics, a clock is a digital signal consisting on periodic pulses. The pulses are generated by an oscillator, which relies on the performance of a resonator as a stabilizing element. Digital systems are entities that at register level exchange binary information at periodic intervals paced by the clock signal. As telecommunications equipment rely on smaller digital subsystems, their synchronization performance is at expenses of the subsystems below. Furthermore, in order to have an optimal coordination and a reliable information transfer among digital subsystems, the equipment has to share the same clock signal. In the real world there are no two or more clock signals that oscillate at the same frequency, as the resonator output frequency is affected by manufacturing deficiencies and environmental conditions (humidity, temperature, aging).

In personal computers, the clock is known as system clock and it is rendered to the user in the format of year, day, hour:minute:second [ISO 8601:2004 (2004)]. The formatting task is accomplished by a high-priority routine within the operating system after reading one of the several existing timing sources, either within the motherboard or the microprocessor, i.e., from the Real Time Clock (RTC) or the Timestamp Counter (TSC). Both counters are hardware registers that sum up ticks at a multiple<sup>1</sup> of the on-board resonator's frequency to keep track of real time.

In the context of synchronization of networks, every node of a network that has to synchronize to a reference node is a *clock*. The reference nodes have a better quality in terms of frequency stability, as they are generally locked to a high stable frequency signal coming from an atomic resonator. Atomic clocks are a kind of devices based on an atomic material and deliver a high stable frequency signal, generally in the flavours of 1, 5, and 10 MHz. Reference clocks in networks are dedicated high-performance computers that are locked to an atomic resonator in order to offer a high stable time to those client nodes with less stability.

### 2.1.3 Why Do We Need Synchronization?

The need for synchronization is global, in daily life, in electronic systems and in networks. Networks are built of electronic devices that are paced by drifty clocks that run at different frequencies. Consider for example the disparity of frequencies of the components in an electronic system. A processor of a personal computer may operate at 3 gigahertz and the data information travelling through the busses of a printed circuit board may run at hundreds of megahertz. In this case, the provision of synchronization mechanisms to adapt the information transfer speeds between the CPU and the bus is a must, otherwise the information would be lost. All the electronic digital systems are subjected to this ultimate level, thus

<sup>&</sup>lt;sup>1</sup>It is common to fold the resonator's frequency by specialized frequency synthesis circuits inside the digital chips as actual quartz resonators can only resonate in the range of tens of kilohertz to tens of megahertz.

different re-synchronization mechanisms are provided along the information path, i.e., from the physical to the user level.

The lack or loss of synchronization has a different effect depending on where it takes place. For example, a loss of synchronization in the transfer of information from one register to another may raise to a misinterpretation of one or more bits. The type and mechanisms to provide synchronization depend on the synchronization abstraction level, while the specific requirements depend on the application needs. Consider another example, a voice communication over IP network (VoIP). The time delays and variabilities (jitter) are splitted along the path from the source to the destination nodes. Every node contains electronic circuitry that run at a different frequency and low-level synchronization mechanisms that add latency and jitter on the time needed for the packet to reach the destination. Besides, the intermediate elements (i.e., the switches and routers) store the packets for a variable amount of time that depends on the traffic load in the other ports. As in the case of VoIP, the packets need to be delivered to the user within a specific time interval to be sequentially and orderly processed on-time in the destination node for proper playout. However, if one or several packets containing the encoded voice data of the user is excessively delayed, the destination node will notice gaps of time with no voice.

All the waiting time counts, either coming from the latency and jitter added by digital circuits or the intermediate software processes that handle the packet before delivering it to the user. The crux of the matter is what are the synchronization requirements at a specific level of abstraction, and if that level can accommodate the delay and jitter introduced by lower layers.

# 2.1.4 Time, Phase and Frequency Synchronization

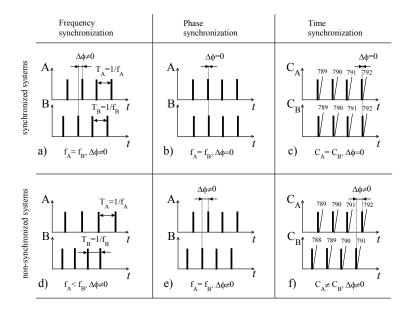

Synchronization is a generic concept that depicts the act of aligning the timing references of two or more entities. The timing references can be treated in different physical quantities, i.e. either in frequency, phase and time. Figure 2.1 shows an elementary view of two signals, A and B, being synchronized (subplots a, b, c) and unsynchronized (subplots d, e, f). Columns show the type of synchronization, i.e., frequency, phase and time:

- Frequency synchronization: As shown in Figs. 2.1a and 2.1d, frequency synchronization consists on matching the frequencies  $(f_a = f_b)$  of both signals, regardless of the phase difference  $(\Delta \phi \neq 0)$  between them. Conversely, the two signals are unsynchronized if the frequencies differ  $(f_a \neq f_b)$ . In the context of networks, the term frequency synchronization is also know as syntonization.

- Phase synchronization: As shown in Figs. 2.1b and 2.1e, phase synchronization implies that the rising edges of the reference signal occur at the same instant  $(f_a = f_b, \Delta \phi = 0)$ . Phase synchronization is more restrictive than frequency synchronization as it requires frequency and phase matching at the same time. In the context of networks, this term might include

the notion of frame timing, i.e., the point in time when the time slot of an outgoing frame has to be generated.

• Time synchronization: As shown in Figs. 2.1c and 2.1f, in the context of networks, time synchronization refers to the alignment the timescales of two geographically dispersed real-time clocks. Two nodes are time-synchronized if their timescales match  $(C_A = C_B)$ . Notice from the figure that time synchronization is one way of achieving phase synchronization.

Figure 2.1: Physical quantities to represent synchronization.

#### 2.1.5Timing Between Signals and Systems

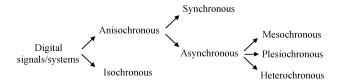

By definition, two digital signals or systems or networks are synchronous to each other if they share the same clock signal for transmitting and receiving the information. Synchronization of data passing between two nodes/networks is only necessary if the timing of the systems is different. If both systems work with the same clock, then they are synchronous and changes in the data from one system are always made at the same time in its clock cycle. The receiving system knows when the data is stable relative to its own clock and can sample it at that time, thus no synchronization is necessary. Figure 2.2 is inherited from [Messerschmitt (1990)] and illustrates a taxonomy of the timing relationship between two digital signals or systems. Mesochronous relationship is given to the systems that

do not share the same clock signal but they are tightly coupled, e.g., with the help of a phase locked loop (PLL), with small phase difference. Two systems are plesiochronous when both clock frequencies may be nominally the same, but the phase difference can drift over a period of time in an unbounded manner. Synchronization of two plesiochronous systems can be achieved by predicting when conflicts might occur, and avoiding data transfers when the two clocks conflict. If the time frame of one system is completely unknown to the other, there is no way that a conflict can be avoided and it is essential that data transfers are synchronized every time. In such a case the path is heterochronous.

Figure 2.2: Synchronous and Asynchronous relationship between two digital signals, systems or networks.

# 2.2 Synchronization in Networks

#### 2.2.1 Synchronous and Asynchronous Networks

Ethernet is well-known to be an "asynchronous technology". Each node of an Ethernet network has a free-run clock for sending and receiving information. As each Ethernet node runs at a different speed, synchronization mechanisms at the receiver node are required to adapt the sender datarate to its local clock. This first stage synchronization is entirely performed in the physical layer by hardware mechanisms. In Ethernet technology, the Ethernet transceiver (PHY) carries out this task [IEEE Std. 802.3 (2005)]. Once the information is synchronized and within the node, other types of synchronization are performed. For the specific case of Ethernet, each frame contains a special and fixed header (i.e., the preamble) to differentiate the frames.

Asynchronous networks are a type of networks with independent timed processors and hardware mechanisms to adapt the different datarates. This free-running characteristic is what differentiates asynchronous and synchronous networks. Asynchronous networks are architecturally simpler compared to synchronous counterparts, but the overhead of establishing the local synchronization is significant. On the other hand, in synchronous networks, all clocks are completely bound together through hardware mechanisms and equipment geographically dispersed. Many Network Operators are actually replacing synchronous technologies, such as SDH, to reduce cost in equipment technology, network setup and maintenance. Digital networks, such as SDH, where initially deployed in the 70s for the transmission of voice in digital telephone networks. Nowadays, with the advent of Internet and cellular mobile technologies, data traffic points

towards an ever increasing bandwidth demand, a parameter that traditionally synchronous technologies or circuit-switched networks cannot accommodate.

#### 2.2.2 Actual Synchronization in IEEE 802.3

According to the definitions stated in Section 2.1.5, native Ethernet is a heterochronous technology, i.e., Each node of an Ethernet network has a free-running clock that paces the transmission of the data to the media. Ethernet was defined as a two-layer technology that addressed, in the Layer 2, how the data was organized and sent over the network medium, and in the Layer 1, how were the signalling and synchronization mechanisms. The actual synchronization provisioning in Ethernet is performed in the physical layer (PHY) to recover the analog signals from the cable to the digital data delivered to the MAC (L2). In the context of networks, an "asynchronous technology" is a technology that

Figure 2.3: Actual synchronization functionalities in the OSI model.

do not share with other nodes a common timing from a high quality frequency standard source, but it uses a free-running crystal oscillator (XO) on-board to communicate with its adjacent node. In the case of Ethernet, this task is carried out by the PHY. During the link setup between two nodes, the autonegotiation function of the PHY decides which node acts as a master and which one as a slave. Hereafter, the master generates the transmit clock locally from the XO and the slave recovers the master clock from the received data and uses this recovered clock to receive data properly. After each packet transmission, the MAC enters in the interframe gap period (IGP), where the underlying PHY injects *idle* control codes to keep synchronized with the adjacent node until the next packet transmission. Without this Layer 1 (carrier, symbol and frame) synchronization it would not be possible for the PHY of the receiving node to receive incoming packets. This fact poses several pros and cons. On the one hand, the systems and the overall network is simpler and much cheaper than other technologies, such

as SONET/SDH or PDH. On the other hand, the overhead of establishing local synchronization is be significant for certain applications in terms of latency and jitter. Figure 2.3 illustrates different representations and synchronization techniques in the path of a message through the layered stack of an Ethernet node. The information in the medium is transported by means of analog pulses that are degraded by different sources of noise along the path. The PHY transceiver on Ethernet boards have the task to convert the incoming information from analog to binary format (carrier & symbol synchronization). This conversion is performed in the PCS sublayer, which contains complex hardware mechanisms such as noise filters, carrier recovery circuits, de-scramblers, decoders and so on. All Ethernet frames have a fixed header at the beginning of the frames that is used by the PHY to partition the string of decoded bits into frames (frame synchronization). The splitting of each frame into bytes is performed in the PMA sublayer and then it is passed to the MAC. Thus, time synchronization at Layer 2 (link)synchronization) can be represented as a string readable format coming from a digital counter. Synchronization within the MAC is represented in multiples of byte (8, 16, 32 bits, and so on). It must be noted that frame synchronization does not result in link synchronization, but it is a method to obtain the frames from a bitstream of logical '0' and '1'. To provide time synchronization at Layer 2, there must be hard hardwared mechanisms within the MAC to update the digital counter and note the ingress and egress times of a frame.

#### 2.2.3 Time Synchronization Protocols

A protocol specifies a collection of rules that describe message formats and the patterns for exchanging those messages. The same applies to time synchronization protocols which aim at aligning the timescales of geographically dispersed real-time clocks. They distribute time as a machine-readable string in specific messages and exchange them between nodes. Remote nodes collect the time inside the packets to find an agreement of global time. The strings with the time information come, either from a digital counter located in the hardware resources of the node, or from a software variable as a wasy to represent real time by means of a "synthetic" counter.