**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# EFFICIENT HARDWARE/SOFTWARE CO-DESIGNED SCHEMES FOR LOW-POWER PROCESSORS

Dissertation submitted for the degree of Doctor of Philosophy in Computer Architecture

PhD Student: Pedro López Muñoz

PhD Supervisor: Fernando Latorre Salinas

PhD Co-supervisors: Enric Gibert Codina, Antonio González Colás

Universitat Politècnica de Catalunya

Programa de Doctorat en Arquitectura de Computadors

Barcelona, 2014

## Contents

| Contents                                                        | i        |

|-----------------------------------------------------------------|----------|

| List of Figures                                                 | v        |

| List of Tables                                                  | ix       |

| Abstract                                                        | xi       |

| Acknowledgments                                                 | xii      |

| 1 Thesis Introduction                                           | 1        |

| 1.1 Thesis Objectives                                           | 2        |

| 1.1.1 Code Profiler Design Objectives                           | 4        |

| 1.1.2 Register CheckPointing Design Objectives                  | 5        |

| 1.1.3 Loop Parallelization Scheme Design Objectives             | 6        |

| 1.2 Outline                                                     | 7        |

| 2 Background                                                    | 8        |

| 2.1 General Introduction to Virtual Machines                    | 8        |

| 2.2 Hardware/Software Co-Designed Virtual Machines              | 11       |

| 2.3 Operation of a Co-Designed VM at System Level               | 13       |

| 2.4 Operation of a Hardware/Software Co-Designed VM at Internal | Level 14 |

| 2.4.1 Detecting Regions to be Optimized                         | 17       |

| 2.4.2 Storing Optimized Regions                                 | 18       |

| 2.4.3 Using the Optimized Regions                               | 20       |

| 2.5 Improving Program Execution via a Co-Designed Virtual Machi | ne21     |

| 2.5.1 Code Optimizations                                        | 21       |

| 2.5.2 | Mechanisms to allow speculative code execution   | 25 |

|-------|--------------------------------------------------|----|

| 2.5.3 | Trade-Offs                                       | 26 |

| 2.6 H | Baseline Hardware/Software Co-designed Processor | 26 |

| 3 De  | tecting Hot Code                                 | 29 |

| 3.1 F | Profiling                                        | 30 |

| 3.1.1 | Description                                      | 30 |

| 3.1.2 | Online versus Offline Profiling                  | 30 |

| 3.1.3 | Gathering Information                            | 31 |

| 3.1.  | .3.1 Program Events                              | 31 |

| 3.1.  | .3.2 Hardware and Software Approaches            | 32 |

| 3.2 F | Profiling for Hot Code Detection                 |    |

| 3.2.1 | Objectives                                       |    |

| 3.2.2 | Related Work                                     | 38 |

| 3.2.3 | Application Characterization                     | 36 |

| 3.2   | 3.1 Static and Dynamic Instructions              | 36 |

| 3.2   | .3.2 Counting instructions                       | 41 |

| 3.2.4 | Basic Block Cycle of Life                        | 44 |

| 3.2.5 | Context Switch                                   | 49 |

| 3.2.6 | Reset Counters Coverage Cost                     | 50 |

| 3.2.7 | Basic Block Classification                       | 54 |

| 3.3 F | Proposed Solution (LIU)                          | 56 |

| 3.3.1 | Hardware Structure                               | 56 |

| 3.3.2 | Software Support                                 | 58 |

| 3.3.3 | Replacement Policy Motivation                    | 59 |

| 3.3.4 | LIU Definition                                   | 60 |

| 3.3.5 | pLIU: A Realistic LIU Implementation             | 62 |

| 3.4 H | Evaluation                                       | 65 |

| 3.4.1 | Simulation Framework                             | 65 |

| 3.4.2 | Results                                          | 65 |

| 3.4   | .2.1 Indexing Bits                               | 66 |

| 3 4   | 2.2 Replacement Policies Evaluation              | 67 |

| 3.4.2            | .3 Basic Block Characterization Evaluation      | 69  |

|------------------|-------------------------------------------------|-----|

| 3.4.2            | .4 pLIU Evaluation                              | 71  |

| 3.4.2            | .5 Performance & Overheads                      | 72  |

| 3.4.2            | .6 Power Requirements                           | 76  |

| 3.5 Co           | onclusions and Future Work                      | 76  |

| $4  \mathrm{HW}$ | /SW Register Checkpointing                      | 79  |

| 4.1 H            | RC Overview                                     | 81  |

| 4.2 St           | ate of the Art                                  | 83  |

| 4.3 Ba           | aseline Core Characteristics and Pipeline       | 84  |

| 4.4 De           | etailed HRC Implementation                      | 86  |

| 4.4.1            | Checkpointing Mechanism                         | 87  |

| 4.4.2            | Recovery Mechanism                              | 90  |

| 4.4.3            | Hardware Implementation Details                 | 92  |

| 4.5 Ev           | valuation                                       | 94  |

| 4.5.1            | Simulation Framework                            | 94  |

| 4.5.2            | Results                                         | 95  |

| 4.5.2            | .1 Performance Impact                           | 95  |

| 4.5.2            | .2 Register Pressure                            | 97  |

| 4.5.2            | .3 Area and Power Estimations                   | 99  |

| 4.6 Co           | onclusions and Future Work                      | 101 |

| 5 Loop           | p Parallelization                               | 103 |

| 5.1 St           | ate of the Art                                  | 105 |

| <b>5.2</b> Lo    | oop Parallelization                             | 108 |

| 5.2.1            | Code Regions to Parallelize                     | 109 |

| 5.2.2            | Potential Numbers of the Regions to Parallelize | 112 |

| 5.3 Lo           | oop Parallelization Scheme Implementation       | 115 |

| 5.3.1            | Baseline Core Characteristics                   | 115 |

| 5.3.2   | Thread Spawning                                            | 115 |

|---------|------------------------------------------------------------|-----|

| 5.3.3   | Iteration Ordering                                         | 118 |

| 5.3.4   | Communications                                             | 120 |

| 5.3.    | 4.1 Register Communications                                | 122 |

| 5.3.4   | 4.2 Memory Communications                                  | 126 |

| 5.3.5   | Iteration Finalization                                     | 128 |

| 5.3.6   | Loop Finalization                                          | 130 |

| 5.3.7   | Exception Handling                                         | 134 |

| 5.3.8   | Loop parallelization mechanisms summary                    | 136 |

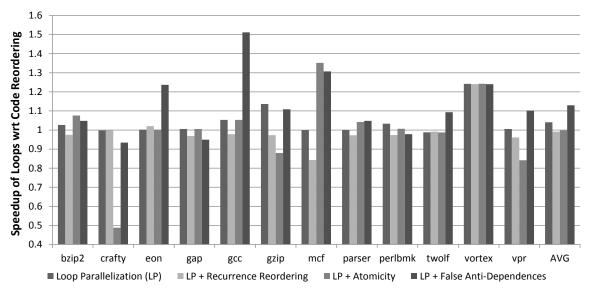

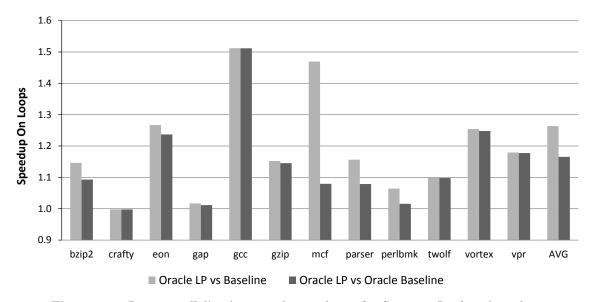

| 5.4 O   | optimizing the Regions to Parallelize                      | 137 |

| 5.4.1   | Recurrence Reordering.                                     | 139 |

| 5.4.2   | Atomic Execution of Regions                                | 139 |

| 5.4.3   | Breaking Anti-Dependences by Using Temporal Registers      | 140 |

| 5.4.4   | Combining the Optimizations                                | 142 |

| 5.5 E   | valuation                                                  | 142 |

| 5.5.1   | Simulation Framework                                       | 142 |

| 5.5.2   | Results                                                    | 143 |

| 5.5.    | 2.1 Removing Thread Spawning Bubbles                       | 145 |

| 5.5.    | 2.2 Loop Parallelization Performance without Optimizations | 145 |

| 5.5.    | 2.3 Loop Parallelization Performance with Optimizations    | 146 |

| 5.6 C   | Conclusions & Future Work                                  | 150 |

| 6 Coı   | nclusions                                                  | 153 |

| 6.1 O   | Priginal Contributions                                     | 154 |

| 6.2 F   | uture Work                                                 | 156 |

| Ribliog | ranhy                                                      | 150 |

## List of Figures

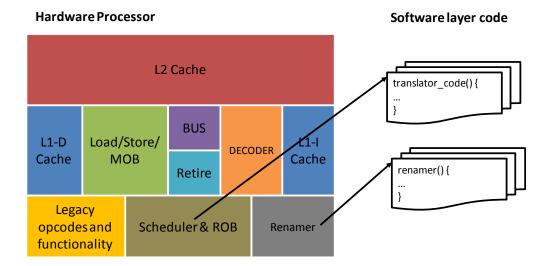

| Figure 1.1: Example of possible hardware components to be implemented in software in      | a  |

|-------------------------------------------------------------------------------------------|----|

| Co-designed Hardware/Software processor                                                   | 4  |

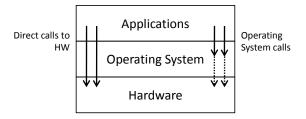

| Figure 2.1: Today's computer components                                                   | 8  |

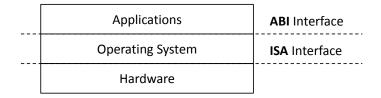

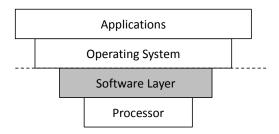

| Figure 2.2: One possible VM software layer integration in the three component compute     | er |

| design                                                                                    | 10 |

| Figure 2.3: J. Smith's Virtual Machines classification                                    | 11 |

| Figure 2.4: Co-designed Virtual Machine approach                                          | 12 |

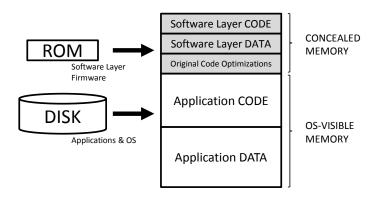

| Figure 2.5: Memory distribution of a hardware/software co-designed system                 | 15 |

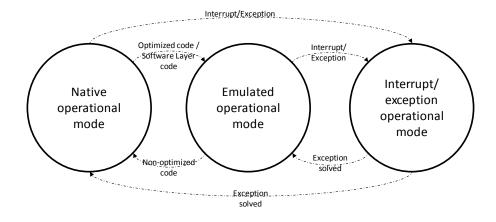

| Figure 2.6: Hardware/Software co-designed virtual machine internal operational modes.     | 15 |

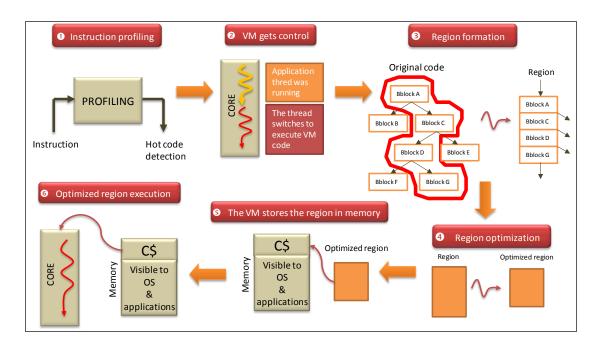

| Figure 2.7: Execution Life Cycle of a Co-designed VM                                      | 16 |

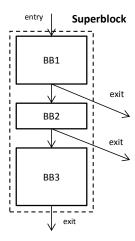

| Figure 2.8: Example of a superblock code region                                           | 17 |

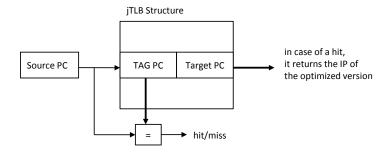

| Figure 2.9: jTLB implementation                                                           | 20 |

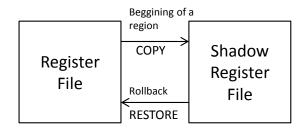

| Figure 2.10: Shadow Register File                                                         | 24 |

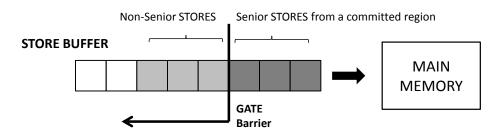

| Figure 2.11: Gated Store Buffer implementation                                            | 25 |

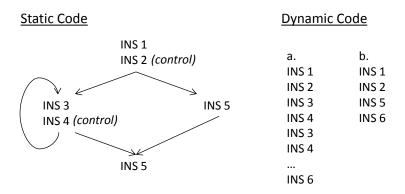

| Figure 3.1: Static vs dynamic instruction code                                            | 37 |

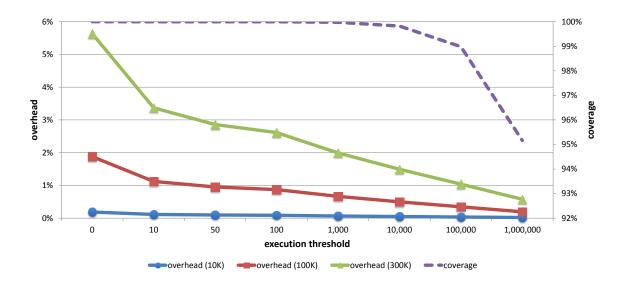

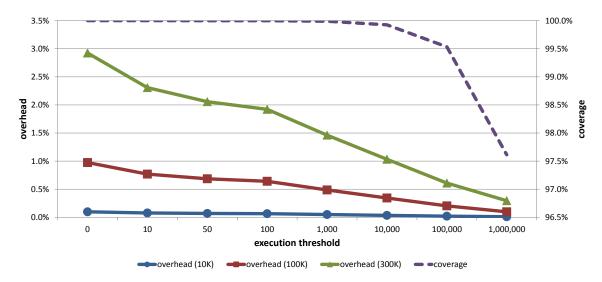

| Figure 3.2: Coverage & overheads of optimizing different subsets of static instructions   |    |

| considering Spec2K Integer benchmarks                                                     | 40 |

| Figure 3.3: Coverage & overheads of optimizing different subsets of static instructions   |    |

| considering Spec2K6 benchmarks                                                            | 40 |

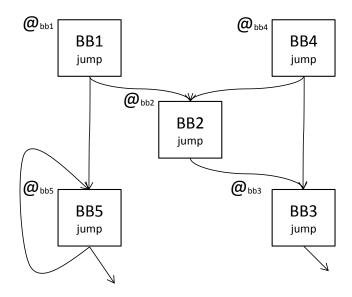

| Figure 3.4: Basic Blocks execution example                                                | 42 |

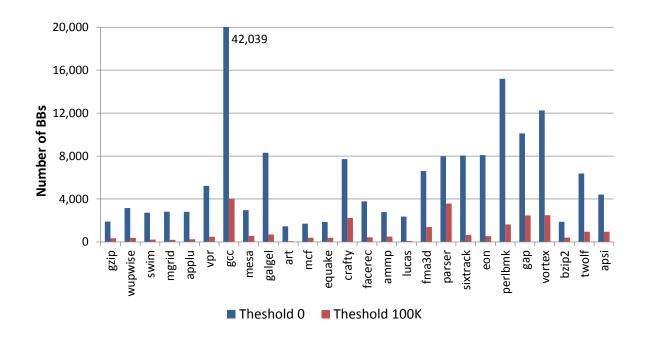

| Figure 3.5: Number of basic blocks in Spec2000 benchmarks that are executed above a       |    |

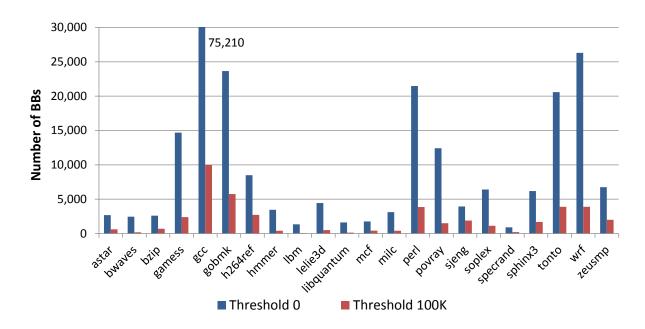

| specific threshold                                                                        | 43 |

| Figure 3.6: Number of basic blocks in Spec2006 benchmarksthat are executed above a        |    |

| specific threshold value                                                                  | 43 |

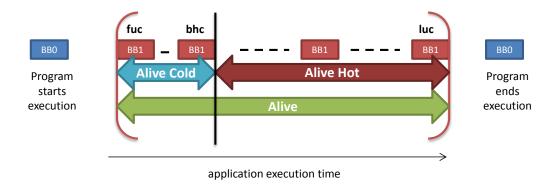

| Figure 3.7: Basic Block Life Cycle during application execution                           | 44 |

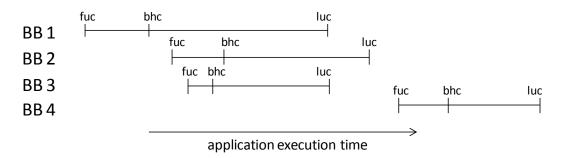

| Figure 3.8: Basic block life cycles during a program execution example                    | 45 |

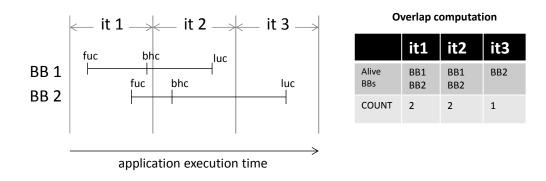

| Figure 3.9: Life Cycle overlap computation example                                        | 46 |

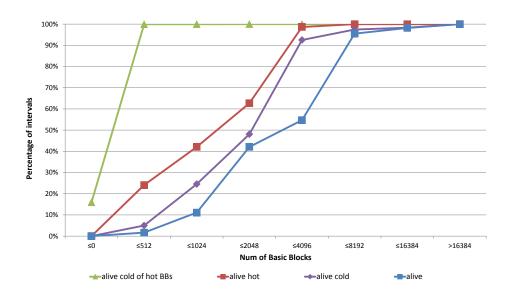

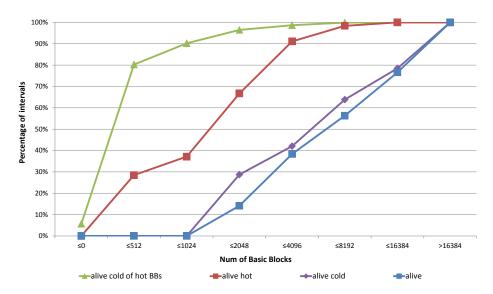

| Figure 3.10: Percentage of intervals with the same number of basic block life cycle perio | ds |

| overlapping for Spec2000Int benchmarks                                                    | 48 |

| Figure 3.11: Percentage of intervals with the same number of basic block life cycle perio | ds |

| overlapping for Spec2006 benchmarks                                                       | 48 |

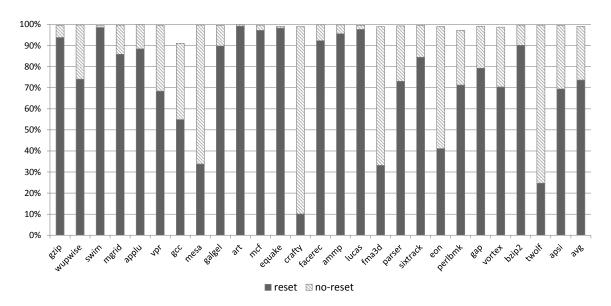

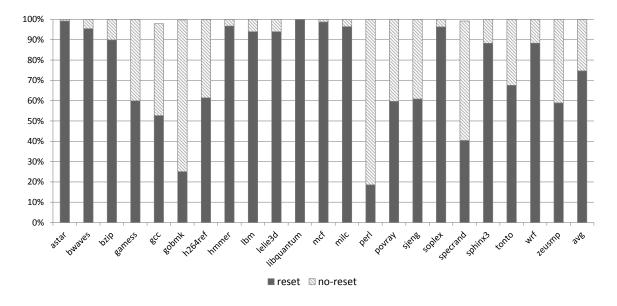

| Figure 3.12: Basic block coverage for SPEC2000 benchmarks when applying counters          |    |

| reset                                                                                     | 50 |

| Figure 3.13: Basic block coverage for SPEC2006 benchmarks when applying counters           |       |

|--------------------------------------------------------------------------------------------|-------|

| reset                                                                                      | 50    |

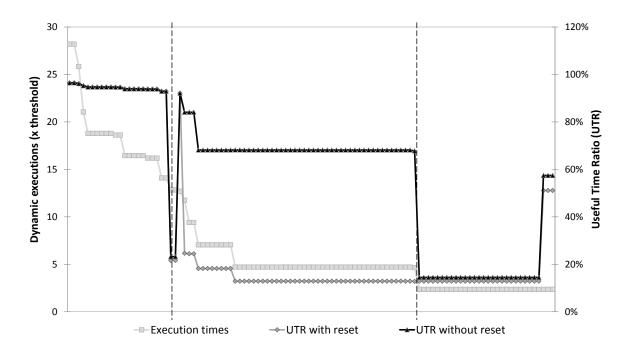

| Figure 3.14: Coverage and useful time ratio for detected hot basic blocks in Spec2006      |       |

| Specrand benchmark when profiler reset technique is applied                                | 53    |

| Figure 3.15: Coverage and useful_time_ratio for non-detected hot basic blocks in           |       |

| Spec2006 Specrand benchmark when profiling reset technique is applied                      | 53    |

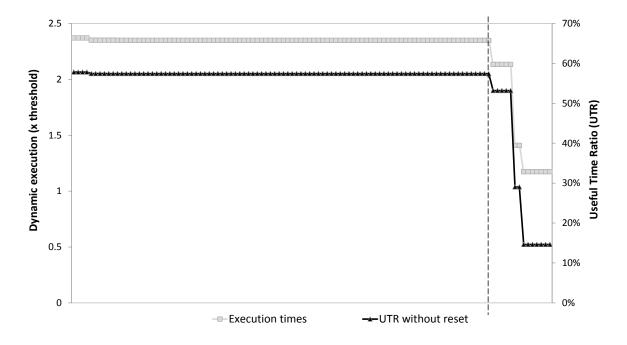

| Figure 3.16: Basic Block execution Classification by using animal speeds                   | 55    |

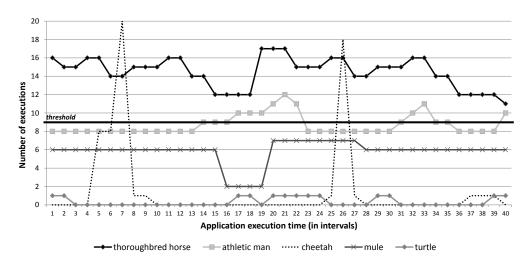

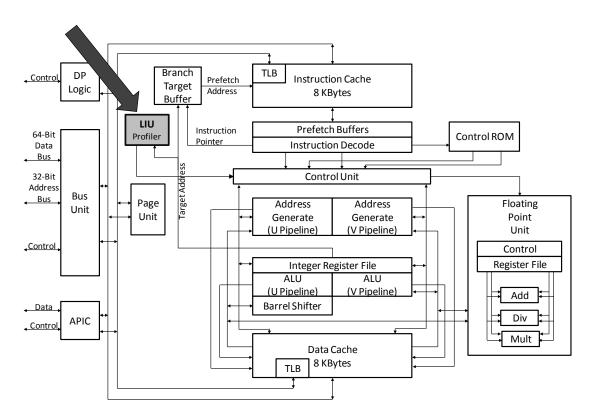

| Figure 3.17: LIU Profiler hardware design.                                                 | 57    |

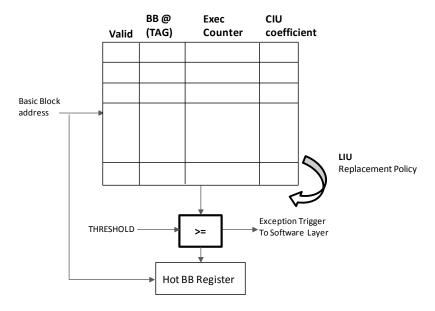

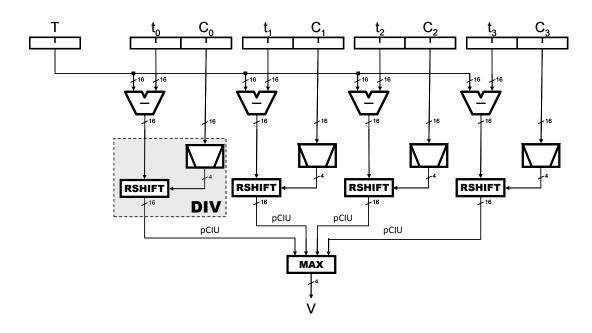

| Figure 3.18: Hardware implementation of the LIU. V is the victim                           | 64    |

| Figure 3.19: High-level block diagram of the P54C core with the pLIU profiler (highligh    | hted  |

| with the arrow). Figure from P54C Datasheet [105]                                          | 64    |

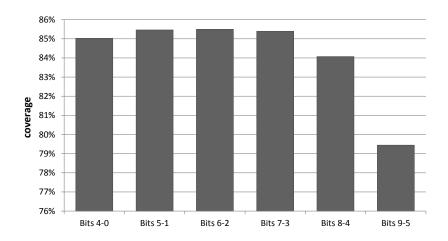

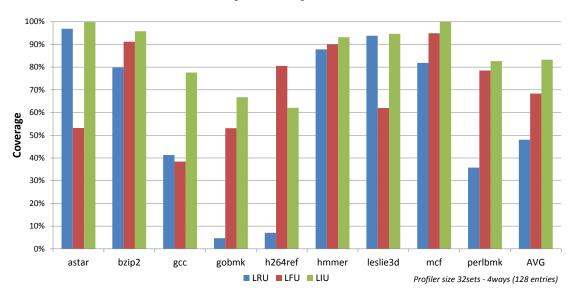

| Figure 3.20: Hot code coverage evaluated in a 32sets-4way cache profiler by using diffe    | erent |

| cache indexing bits from instruction address                                               | 66    |

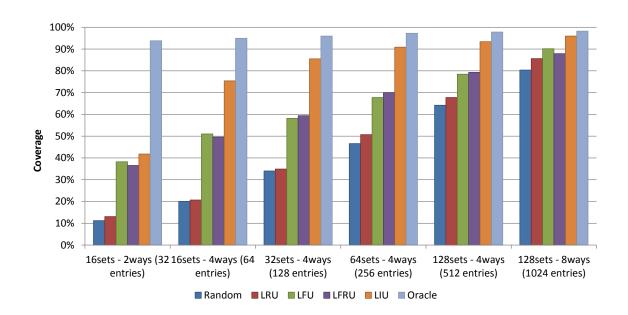

| Figure 3.21: Hot code coverage evaluated by using different cache configurations and       |       |

| replacement policies                                                                       | 69    |

| Figure 3.22: Hot code coverage evaluated by using LIU, LRU and LFU replacement             |       |

| policies and Spec2006 benchmarks                                                           | 69    |

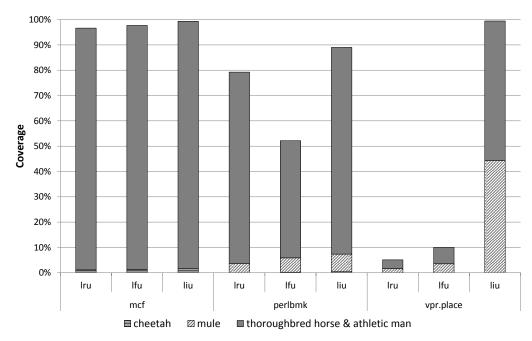

| Figure 3.23: Coverage of the different types of basic blocks in mcf, perlbmk and vpr wi    | ith   |

| place input set benchmarks                                                                 | 70    |

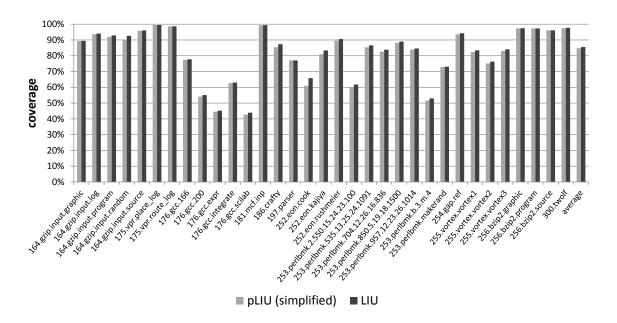

| Figure 3.24: Dynamic code coverage evaluation for SPEC2000Int benchmarks                   | 71    |

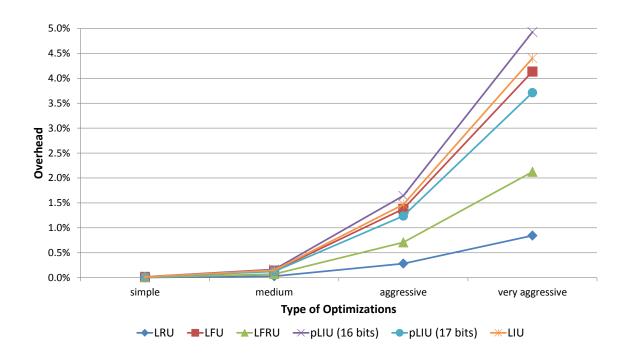

| Figure 3.25: Potential optimization overheads in Spec2000Int for different replacement     | ;     |

| policies using a simple analytical model                                                   | 75    |

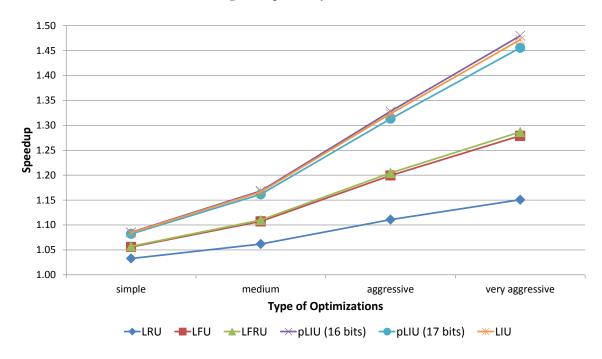

| Figure 3.26: Potential speedup for Spec2000Int benchmarks of a dynamic binary optim        | nizer |

| system using different profiling techniques compared to a system that does not implem      | nent  |

| a binary optimizer using a simple analytical model                                         | 75    |

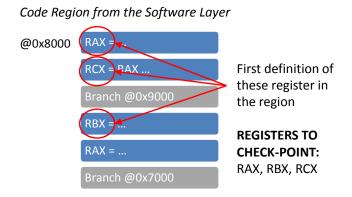

| Figure 4.1: Example of first usage of registers in a code region                           | 81    |

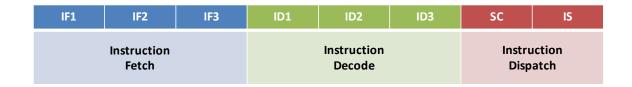

| Figure 4.2: Processor front-end pipeline                                                   | 86    |

| Figure 4.3: Processor back-end pipeline.                                                   | 86    |

| Figure 4.4: Software layer algorithm to indentify the registers that require checkpointing | ng    |

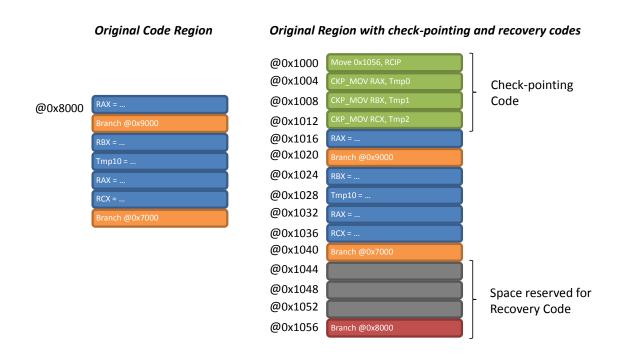

| within a region                                                                            | 88    |

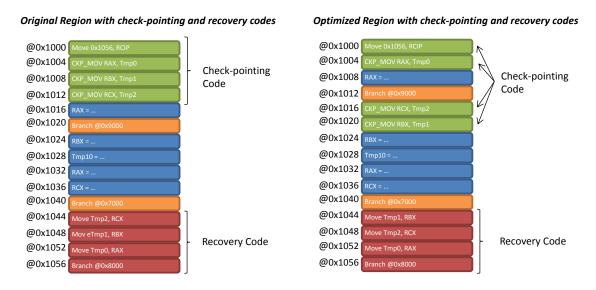

| Figure 4.5: Example of code generated when using the checkpointing and recovery            |       |

| mechanism                                                                                  | 89    |

| Figure 4.6: Example of code reordering applied on top of a region that already includes    | s     |

| the checkpointing and recovery codes                                                       | 89    |

| Figure 4.7: Recovery mechanism functionality example                                       | 93    |

| Figure 4.8: Processor pipeline execution examples of the CKP_MOV instruction               | . In case  |

|--------------------------------------------------------------------------------------------|------------|

| a), the instruction is executed with its corresponding instruction that overwrites         | the        |

| checkpointed register. In case b), the two instructions are executed back to back          | 93         |

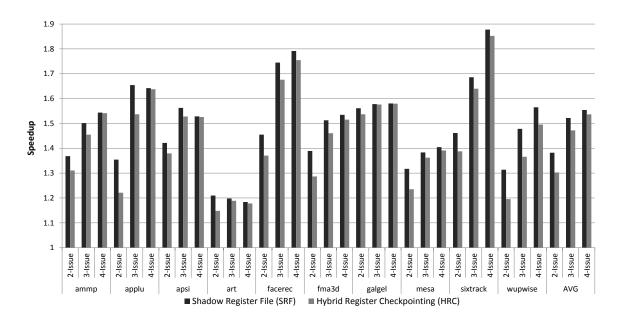

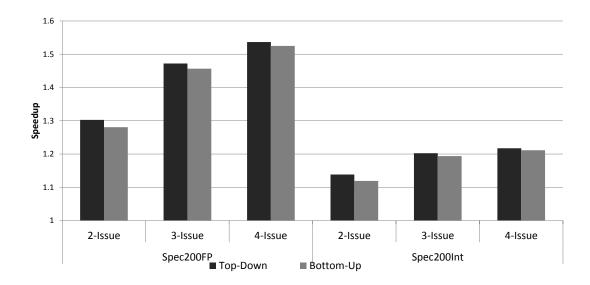

| Figure 4.9: Performance impact of the HRC scheme when compared to a tradition              | onal SRF   |

| scheme. Results for Spec2000FP benchmark suite and top-down instruction list               |            |

| scheduling                                                                                 | 96         |

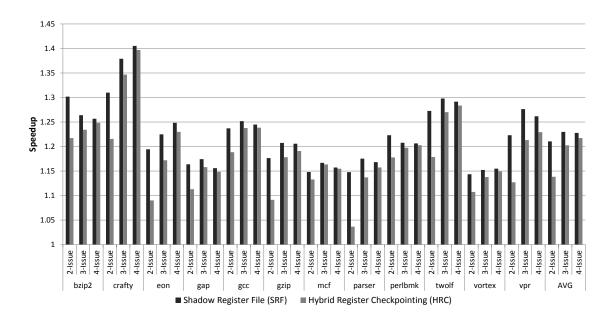

| Figure 4.10: Performance impact of the HRC scheme when compared to a tradit                | ional SRF  |

| scheme. Results for Spec2000Int benchmark suite and top-down instruction list s            | _          |

| Figure 4.11: Performance of the software checkpointing with TD and BU list-sch             | eduling.97 |

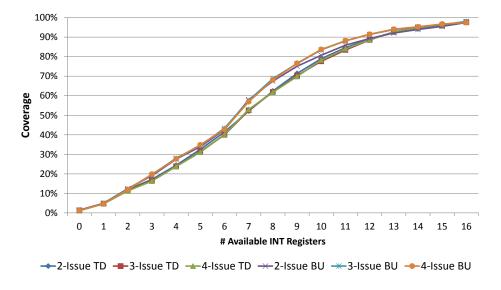

| Figure 4.12: Integer Register pressure impact of the software checkpointing prop           | osal 98    |

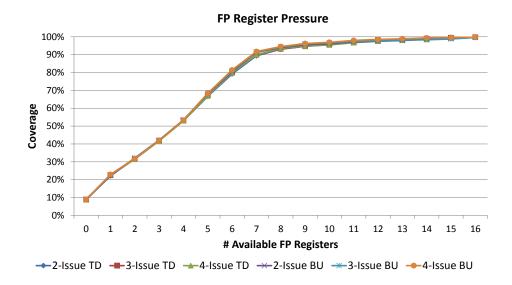

| Figure 4.13: Floating-Point Register pressure impact of the software checkpointi proposal. | _          |

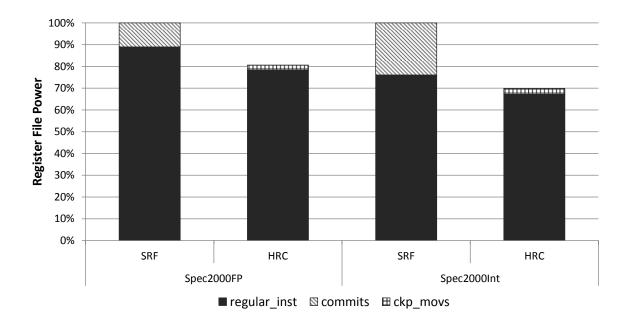

| Figure 4.14: Register file dynamic power consumption evaluated with CACTI                  |            |

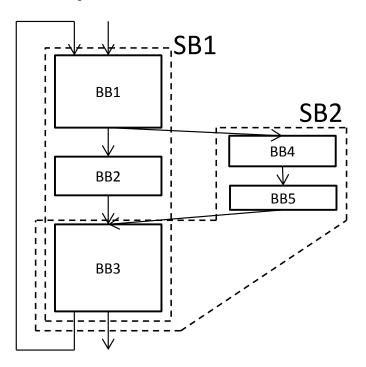

| Figure 5.1: Example of a loop region respresented by using super-blocks                    |            |

| Figure 5.1: Example of a loop region respresented by using super-blocks                    |            |

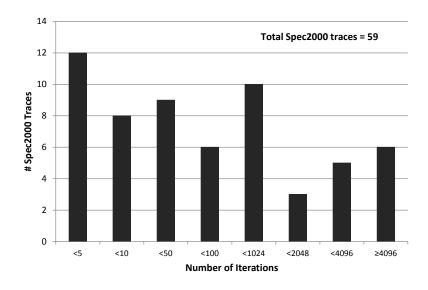

| Figure 5.2: Average number of inner-most loop iterations in Spec2000 benchmark             |            |

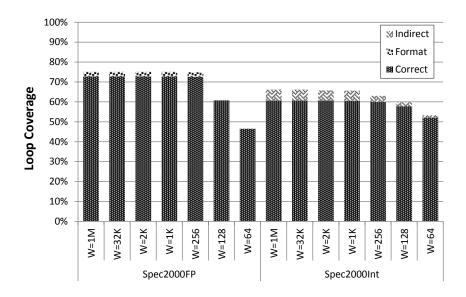

|                                                                                            |            |

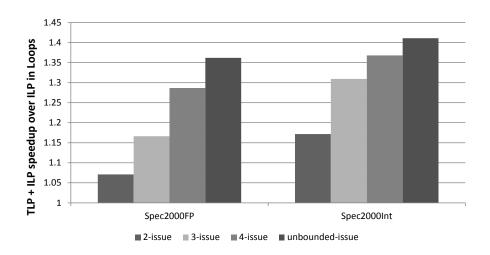

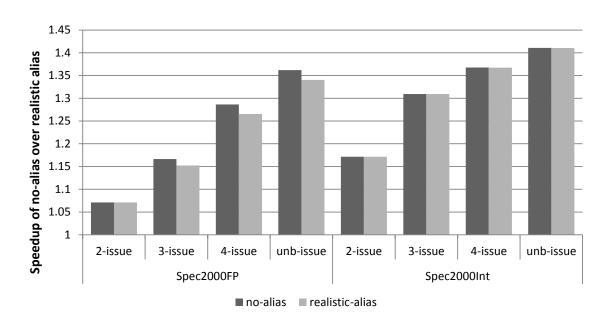

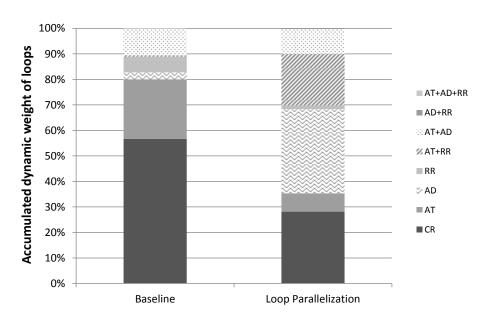

| Figure 5.4: Estimated performance for loop parallelization in loops                        |            |

| consecutive iterations                                                                     |            |

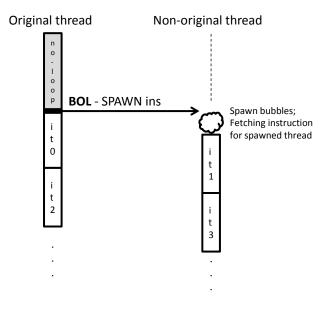

| Figure 5.6: Loop parallelization thread spawning                                           |            |

|                                                                                            |            |

| Figure 5.7: Spawn signal bubbles example by using an Atom®-like processor pip              |            |

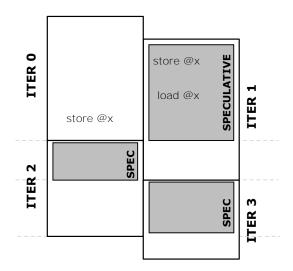

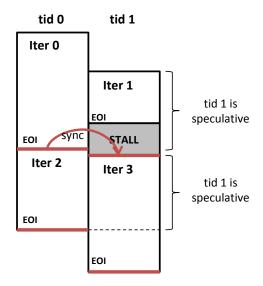

| Figure 5.8: Speculative thread concept in loop paralellization                             |            |

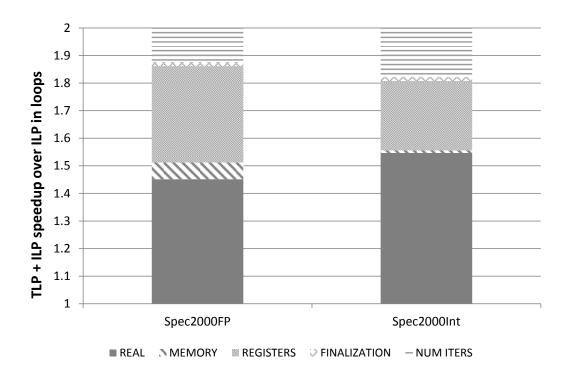

| Figure 5.9: Reasons why a 2x speedup is not achieved with speculative loop para            |            |

| using Spec2000 benchmarks.                                                                 |            |

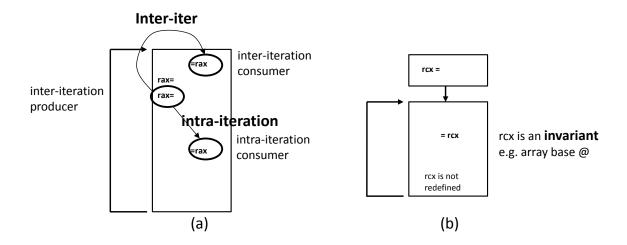

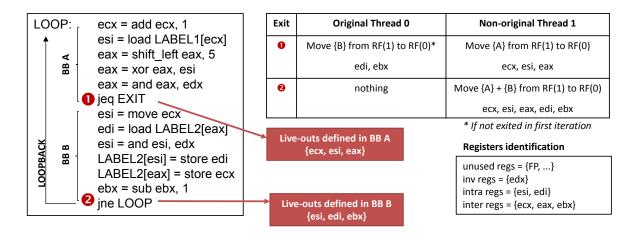

| Figure 5.10: Register dependences in loop parallelization                                  |            |

| Figure 5.11: Algorithm used by the software layer to mark producers/consumers              |            |

| D: 7 10 I 11.1:                                                                            |            |

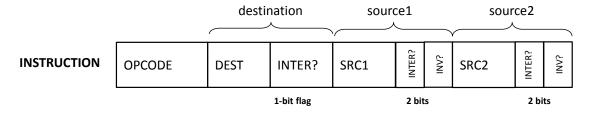

| Figure 5.12: Loop parallelization instruction encoding for register dependences            |            |

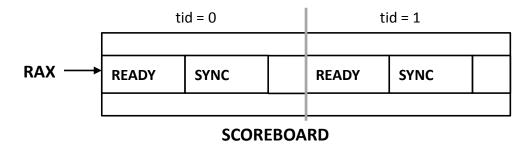

| Figure 5.13: Scoreboard for register communication in loop parallelization                 |            |

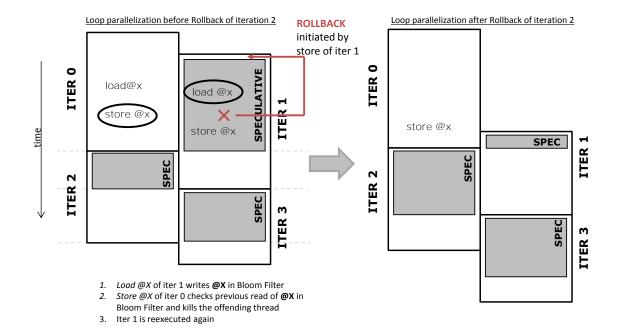

| Figure 5.14: Loop parallelization iteration rollback example                               |            |

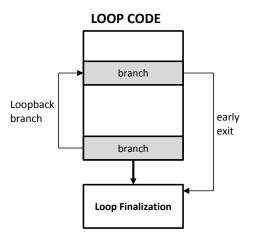

| Figure 5.15: Loop finalization branches                                                    |            |

| Figure 5.16: Loop parallelization iteration finalization example                           |            |

| Figure 5.17: Loop finalization example.                                                    |            |

| Figure 5.18: The traditional static binding between registers and threads is show          |            |

| left. On the right, a dynamic binding is achieved by using a Where bit mask W.             | For each   |

| register R <sub>i</sub> , W <sub>i</sub> identifies whether the local (0) or remote (1) register is used. Note how in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| this case we refer to contexts A and B and not contexts 0 and 1. For example, when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| thread 0 uses register R2 it will access the copy in context B, while thread 1 will access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| the copy in context A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

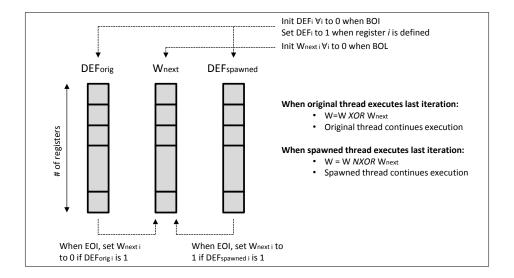

| Figure 5.19: Structures used to compute mask W. Dotted lines describe how and when                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| these structures are initialized and updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

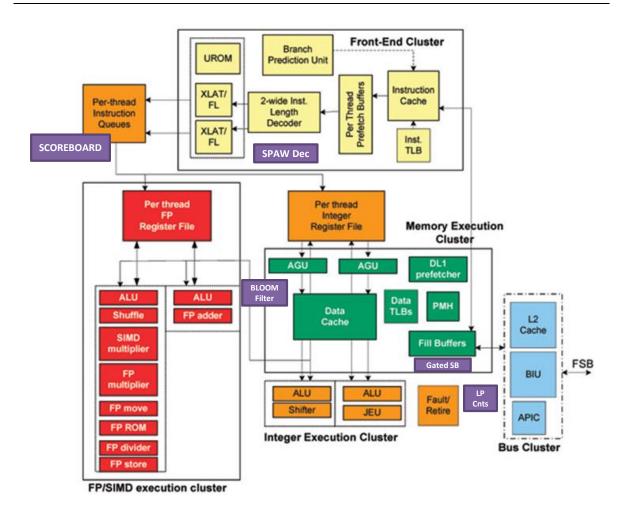

| Figure 5.20: Atom-like architecture with the Loop Parallelization mechanism additions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (original block diagram from [143])136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

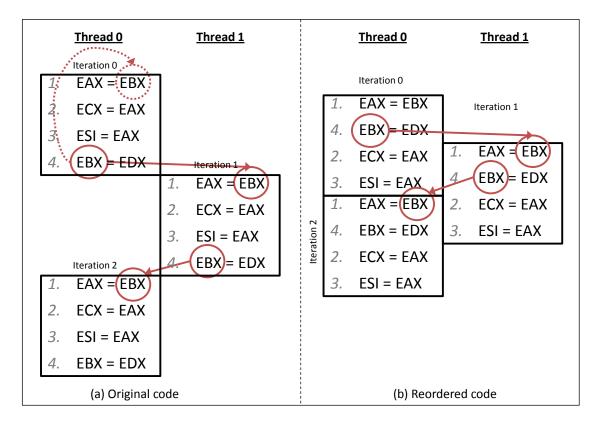

| Figure 5.21: Example of inter-iteration dependence based on instruction scheduling for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| loop parallelization. Figure (a) shows the original code and how it is executed in loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| parallelization mode given the inter-iteration dependences. Figure (b) shows the optimized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| code and how it is executed in loop parallelization mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

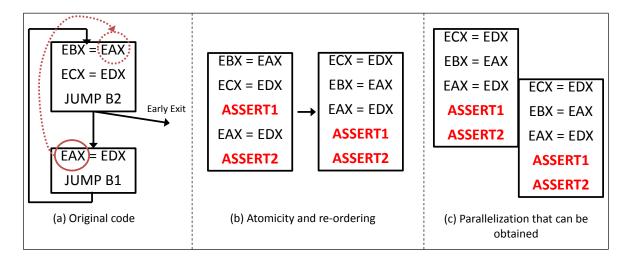

| Figure 5.22: Example of atomicity optimization for loop parallelization. Figure (a) shows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| the original code and the inter-iteration recurrence dependence. Figure (b) shows the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| resultant code after applying the atomicity optimization. Figure (c) shows how the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| resultant optimized code is executed when loop parallelization execution mode is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

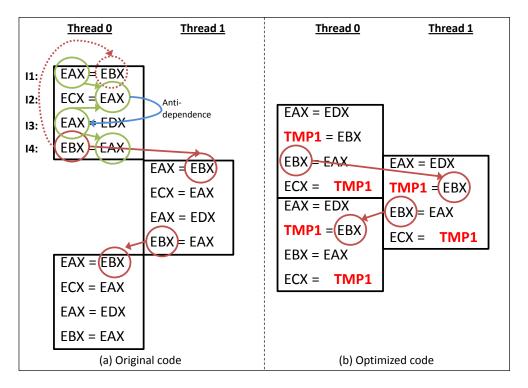

| Figure 5.23: Example of register temporal usage for breaking anti-dependences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| optimizations. Figure (a) shows the original code execution in loop parallelization mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figure (b) shows the execution in loop parallelization mode of the resultant optimized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| code after breaking the anti-dependences for the data inter-iteration recurrence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

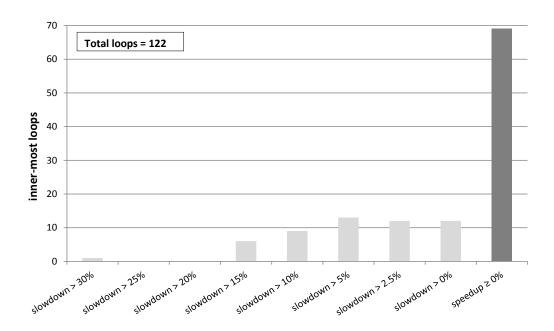

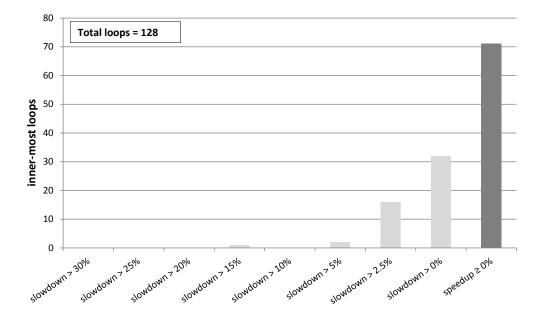

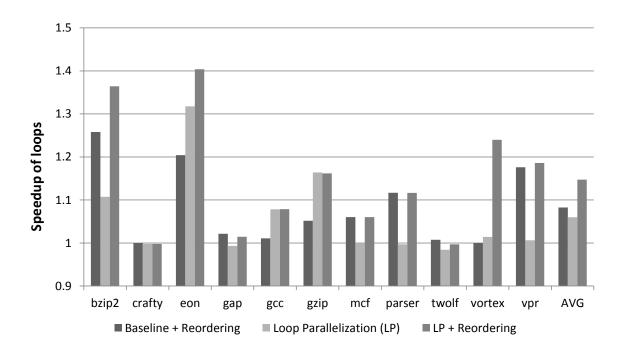

| $ Figure \ 5.24: \ Spec 2000 Int \ inner-most \ loops \ speedups \ for \ loop-parallelization \ with \ respect \ to \ loop \ speedup \ for \ loop \ $ |

| sequential execution using $Spawn-at$ -execute. Efficient SPAWN mechanism is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| implemented. The y-axis represents the number of loops bucketed based on their                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| performance (x-axis)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $ Figure \ 5.25: Spec 2000 Int \ inner-most \ loops \ speedups \ for \ loop-parallelization \ with \ respect \ to \ constraints \ declared to \ declared to$ |

| sequential execution using $Spawn-at$ -fetch. Efficient SPAWN mechanism is implemented.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| The y-axis represents the number of loops bucketed based on their performance (x-axis).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |