**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# Reliability In The Face of Variability in Nanometer Embedded Memories

### Shrikanth Ganapathy

Department d'Arquitectura de Computadors

Universitat Politècnica de Catalunya

# A THESIS SUBMITTED IN FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

Doctor of Philosophy

March, 2014

# Reliability In The Face of Variability in Nanometer Embedded Memories

## Shrikanth Ganapathy

#### **Advisors:**

Ramon Canal Corretger

Universitat Politećnica de Catalunya

Antonio González Colás

Universitat Politećnica de Catalunya & Intel Barcelona Research Center

Antonio Rubio Solá

Universitat Politećnica de Catalunya

#### Abstract

Constant feature miniaturization has been a principal component in the advancement of CMOS technology. As we continue to scale device dimensions further, the advantages are slowly diminishing as stringent constraints are being set on processor power and performance. In light of this, device characteristics such as supply and threshold voltage are scaled aggressively to achieve significant power reduction across successive process generations. However, as we continue to scale, manufacturing processes are becoming less deterministic inducing variations severely inhibited by process control limitations. Such variations have a strong negative impact on the operational margin of the processor affecting key metrics across the lifetime of the chip. This is worsened by lowering of reliability margins where regular operation of the system is characterised by frequent failures and errors. Therefore, it has become a serious challenge to design for high-performance and low-power in the presence of parametric variability.

In this thesis, we have investigated the impact of parametric variations on the behaviour of one performance-critical processor structure - embedded memories. As variations manifest as a spread in power and performance, as a first step, we propose a novel modeling methodology that helps evaluate the impact of circuit-level optimizations on architecture-level design choices. Choices made at the design-stage ensure conflicting requirements from higher-level are decoupled. We then complement such design-time optimizations with a runtime mechanism that takes advantage of adaptive body-biasing to lower power whilst improving performance in the presence of variability. Our proposal uses a novel fully-digital variation tracking hardware using embedded DRAM (eDRAM) cells to monitor run-time changes in cache latency and leakage. A special fine-grain body-bias generator uses the measurements to generate an optimal body-bias that is needed to meet the required yield targets. A novel variation-tolerant and soft-error hardened eDRAM cell is also proposed as

an alternate candidate for replacing existing SRAM-based designs in latency critical memory structures. In the ultra low-power domain where reliable operation is limited by the minimum voltage of operation ( $V_{dd_{min}}$ ), we analyse the impact of failures on cache functional margin and functional yield. Towards this end, we have developed a fully automated tool (INFORMER) capable of estimating memory-wide metrics such as power, performance and yield accurately and rapidly. Using the developed tool, we then evaluate the effectiveness of a new class of hybrid techniques in improving cache yield through failure prevention and correction. Having a holistic perspective of memory-wide metrics helps us arrive at design-choices optimized simultaneously for multiple metrics needed for maintaining lifetime requirements.

## Contents

| $\mathbf{C}$ | onter            | nts   |                                                      | iii  |

|--------------|------------------|-------|------------------------------------------------------|------|

| Li           | $\mathbf{st}$ of | Figur | es                                                   | viii |

| Li           | st of            | Table | ${f s}$                                              | xii  |

| 1            | Intr             | oduct | ion                                                  | 1    |

|              | 1.1              | Impac | et of Spatio - Temporal Variations                   | 2    |

|              |                  | 1.1.1 | Power/Performance Variability                        | 2    |

|              |                  | 1.1.2 | Soft Failures and Errors                             | 3    |

|              |                  | 1.1.3 | Lifetime Reliability                                 | 4    |

|              | 1.2              | Nanor | meter Embedded Memory Design                         | 5    |

|              | 1.3              | Main  | Contributions                                        | 8    |

|              |                  | 1.3.1 | Model-based Energy-Delay Variation Prediction        | 8    |

|              |                  | 1.3.2 | Post-Silicon Adaptivity Using Hardware Monitoring    | 9    |

|              |                  | 1.3.3 | Soft-Error Hardened Embedded 4T-DRAM Cell            | 9    |

|              |                  | 1.3.4 | Parametric Yield Enhancement Using Hybrid Techniques | 10   |

|              |                  | 1.3.5 | INFORMER: A Tool for Memory Robustness Analysis      | 10   |

| 2            | Bac              | kgrou | nd and Related Work                                  | 12   |

|              | 2.1              | Overv | iow                                                  | 19   |

|   | 2.2 | Proces  | ss Variations                                | 13 |

|---|-----|---------|----------------------------------------------|----|

|   | 2.3 | Source  | es of Variations                             | 13 |

|   |     | 2.3.1   | Random Dopant Fluctuations (RDF)             | 14 |

|   |     | 2.3.2   | Line-Edge Roughness                          | 16 |

|   |     | 2.3.3   | Channel Length Variation                     | 17 |

|   |     | 2.3.4   | Environmental Variations                     | 17 |

|   |     |         | 2.3.4.1 Thermal variations                   | 17 |

|   |     |         | 2.3.4.2 Supply voltage variations            | 18 |

|   |     |         | 2.3.4.3 Bias Temperature Instability (BTI)   | 19 |

|   | 2.4 | Copin   | g with Variability                           | 21 |

|   |     | 2.4.1   | Modelling and Optimization using CAD         | 21 |

|   |     |         | 2.4.1.1 Propagation Delay Calculation        | 21 |

|   |     |         | 2.4.1.2 Energy and Power Estimation          | 22 |

|   |     |         | 2.4.1.3 Statistical Optimization             | 23 |

|   |     | 2.4.2   | Circuit Techniques                           | 24 |

|   |     | 2.4.3   | Architecture Adaptation                      | 25 |

|   | 2.5 | Variat  | ion-Tolerant Embedded Memory Design          | 25 |

|   |     | 2.5.1   | Novel Cell Topologies                        | 25 |

|   |     | 2.5.2   | Device and Circuit                           | 26 |

|   |     | 2.5.3   | Architecture reconfiguration                 | 27 |

| 3 | Ene | ergy-De | elay Modeling and Optimization: CAD Approach | 29 |

|   | 3.1 | Overv   | iew                                          | 29 |

|   | 3.2 | Introd  | uction                                       | 30 |

|   | 3.3 | Captu   | ring Spatial Correlations                    | 30 |

|   | 3.4 | Path-A  | Aware Delay Modeling                         | 33 |

|   |     | 3.4.1   | Transistor Specific Delay Modeling           | 33 |

|   | 3.5 | Memo    | ry Array Model                               | 36 |

|   | 3.6  | Experimental Results                                                                 | 37 |

|---|------|--------------------------------------------------------------------------------------|----|

|   |      | 3.6.1 Simulation Results                                                             | 38 |

|   | 3.7  | Use Cases of Proposed Model                                                          | 40 |

|   |      | 3.7.1 Simultaneous Impact of Temperature and D2D Variation                           | 40 |

|   |      | 3.7.2 Memory Critical Path Dual- $V_{th}$ Assignment                                 | 41 |

|   | 3.8  | Energy Estimation in Memories                                                        | 42 |

|   |      | 3.8.1 General Characteristics of a Suitable Model                                    | 42 |

|   | 3.9  | MODEST: Model for Energy-Estimation under Spatio-Temporal Variations                 | 44 |

|   | 3.10 | Experimental Results                                                                 | 49 |

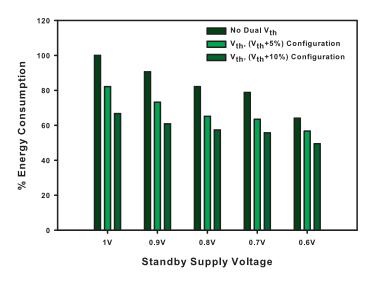

|   |      | 3.10.1 Supply Voltage Reduction Analysis                                             | 50 |

|   |      | 3.10.2 Energy-Delay Analysis                                                         | 50 |

|   | 3.11 | Use Case: Fast Per-Chip Energy Optimization through selective Dual $\mathbf{V}_{th}$ |    |

|   |      | assignment                                                                           | 53 |

|   | 3.12 | Summary                                                                              | 55 |

| 4 | Dyn  | amic Fine-Grain Body-Biasing (DFGBB)                                                 | 56 |

|   | 4.1  | Overview                                                                             | 56 |

|   | 4.2  | Motivation and Background                                                            | 57 |

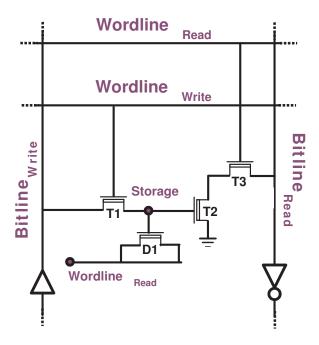

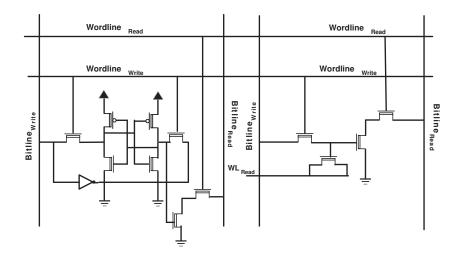

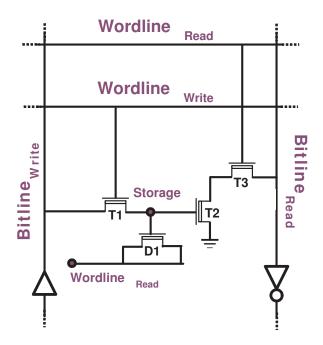

|   | 4.3  | Three Transistor One-Diode (3T1D) eDRAM                                              | 59 |

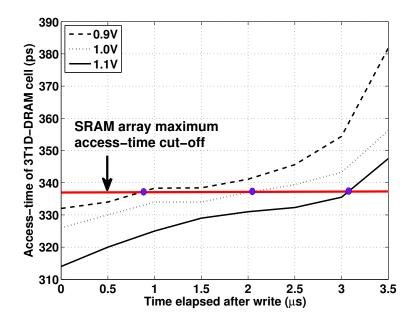

|   |      | 4.3.1 Retention and access time                                                      | 60 |

|   |      | 4.3.2 Simulation Parameters                                                          | 61 |

|   | 4.4  | Latency/Leakage Measurement                                                          | 63 |

|   |      | 4.4.1 Run-Time Classification of Memory Arrays                                       | 63 |

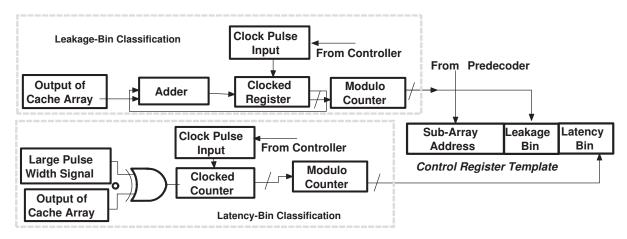

|   |      | 4.4.2 Discretization Architecture                                                    | 64 |

|   | 4.5  |                                                                                      | CO |

|   |      | Applying Fine Grain Body Biasing                                                     | 68 |

|   | 4.6  | Applying Fine Grain Body Biasing                                                     | 70 |

|   | 4.6  | Experimental Results                                                                 |    |

|   | 4.7 | Summary                                                          | 73         |

|---|-----|------------------------------------------------------------------|------------|

| 5 |     | ention Enhancement and Improved Radiation Tolerance In Embed-    | <b>7</b> 5 |

|   | 5.1 | Overview                                                         | 75         |

|   | 5.2 | Motivation and Background                                        | 76         |

|   | 5.3 | Revisiting 3T1D Operation: Retention Time Perspective            | 77         |

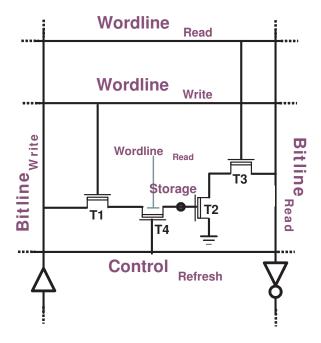

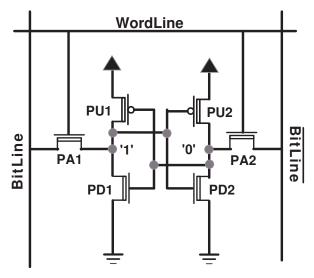

|   | 5.4 | 4T-DRAM Cell                                                     | 80         |

|   | 5.5 | Impact of Process Variations                                     | 83         |

|   |     | 5.5.1 Simulation Parameters                                      | 83         |

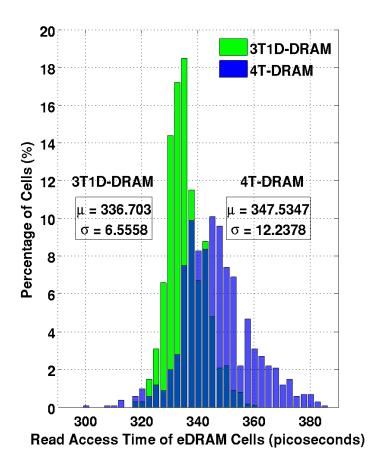

|   |     | 5.5.2 Variation in Access and Retention Times                    | 84         |

|   |     | 5.5.3 Power consumption comparison                               | 87         |

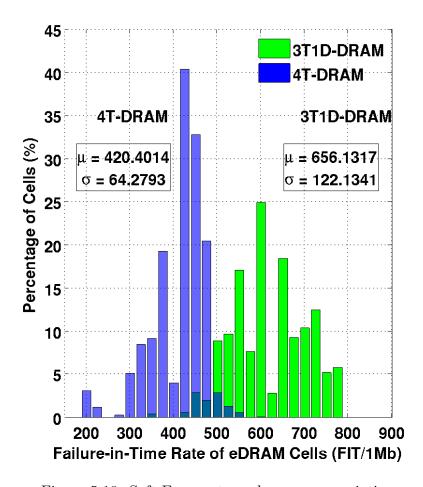

|   | 5.6 | Soft-Error Tolerance                                             | 87         |

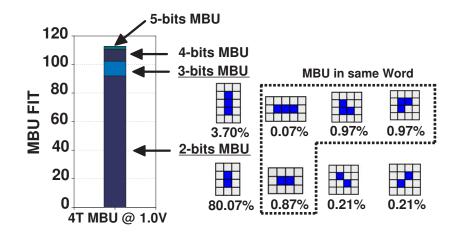

|   |     | 5.6.1 Multiple Bit Upsets (MBU)                                  | 89         |

|   | 5.7 | Summary                                                          | 91         |

| 6 | Hyl | orid Techniques to Enhance Parametric Yield                      | 92         |

|   | 6.1 | Overview                                                         | 92         |

|   | 6.2 | Motivation and Background                                        | 93         |

|   | 6.3 | Parametric Failures in 6T-SRAM Cells                             | 95         |

|   |     | 6.3.1 Rapid Failure Probability Estimation                       | 98         |

|   | 6.4 | INFORMER: An Integrated Framework for Early-Stage Memory Robust- |            |

|   |     | ness Analysis                                                    | 01         |

|   | 6.5 | Use Cases of INFORMER                                            | 04         |

|   |     | 6.5.1 Constraint based optimization                              | 04         |

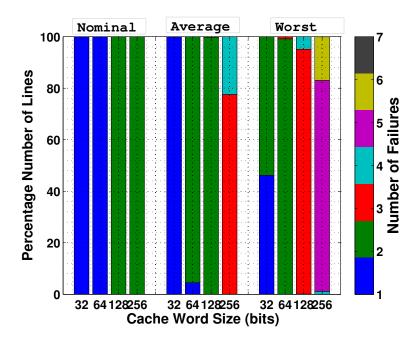

|   |     | 6.5.2 Column redundancy limits on yield                          | 04         |

|   |     | 6.5.3 Variability aware soft-error rate estimation               | 05         |

|   | 6.6 | Proactive R/W Assist Techniques                                  | 07         |

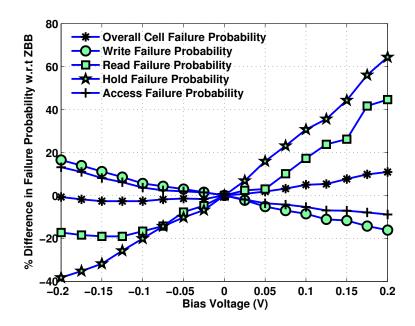

|   |     | 6.6.1 Adaptive Body Biasing                                      | 07         |

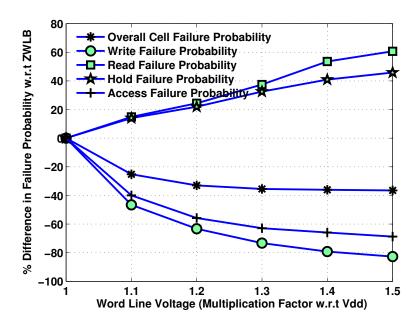

|    |              | 6.6.2  | Wordline Boosting                            | 109 |

|----|--------------|--------|----------------------------------------------|-----|

|    | 6.7          | Reacti | ve Techniques                                | 110 |

|    |              | 6.7.1  | Error-Correcting Codes (ECC)                 | 110 |

|    |              | 6.7.2  | Redundancy                                   | 111 |

|    | 6.8          | Hybrid | d Yield Enhancement Techniques               | 113 |

|    | 6.9          | Summ   | ary                                          | 116 |

| 7  | Con          | clusio | ns and Future Work                           | 117 |

|    | 7.1          | Summ   | ary of Contributions                         | 117 |

|    | 7.2          | Future | e Work                                       | 119 |

|    |              | 7.2.1  | NBTI Tolerance in Caches (On-going research) | 119 |

|    |              | 7.2.2  | Ultra Low Power Operation                    | 120 |

|    |              | 7.2.3  | Emerging Memory Technologies                 | 120 |

|    | 7.3          | Public | ations                                       | 121 |

| Li | st of        | Abbre  | eviations                                    | 121 |

| Re | References 1 |        |                                              | 125 |

# List of Figures

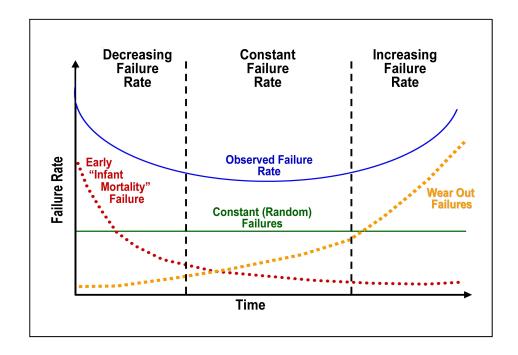

| 1.1 | Bathtub Curve: Failure rate across operational lifetime                                                                                                                                                                                                                                     | 4   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

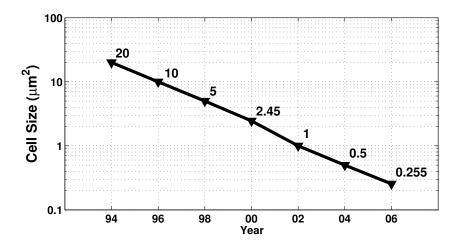

| 1.2 | SRAM cell area scaling from 350nm to 45nm across 7 process generations [3, 113]                                                                                                                                                                                                             | 6   |

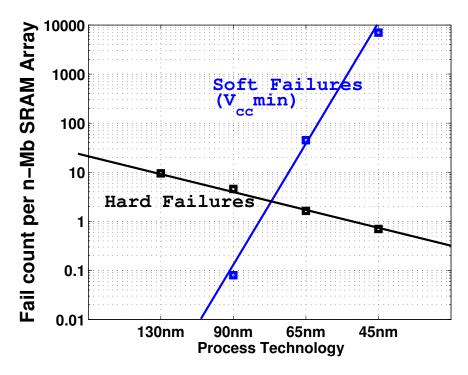

| 1.3 | Hard and soft failure trends with SRAM scaling [86]                                                                                                                                                                                                                                         | 7   |

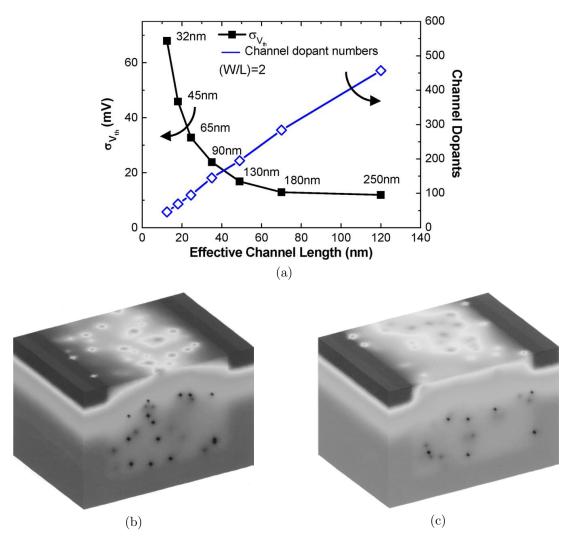

| 2.1 | (a) Scaling trend of $V_{th}$ variance due to random dopant fluctuations (RDF) [114] (b) MOSFET with $V_{th} = 0.78V$ (170 dopant atoms) (c) MOSFET with $V_{th} = 0.56V$ (170 dopant atoms) [9]                                                                                            | 15  |

| 2.2 | Impact of Line-Edge Roughness on $V_{th}$ as a function of transistor width [114]                                                                                                                                                                                                           | 16  |

| 2.3 | Within die temperature variations [15]                                                                                                                                                                                                                                                      | 18  |

| 2.4 | Voltage droop in chip multiprocessors where physical cores share the same power grid (a) Voltage droop in a core as it turns on increasing the load (b) coupled voltage droop in another block as it is switched on after a few ns delay [40]                                               | 19  |

| 2.5 | $\Delta V_{th}$ shift (under NBTI) in 32nm PMOS device operating at 85°C                                                                                                                                                                                                                    | 21  |

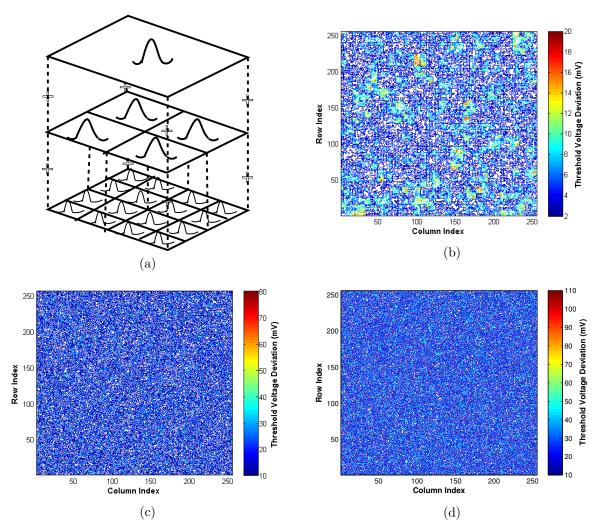

| 3.1 | (a) Multi-level spatial grid model to capture correlated variations dependent on proximity (b) Sample variation map for 256x256 memory array only with correlated variations (c) Sample variation map for 256x256 array only with random variation (d) Overall variation map with summation | 9.0 |

|     | of D2D, WID-Systematic and WID-random variations                                                                                                                                                                                                                                            | 32  |

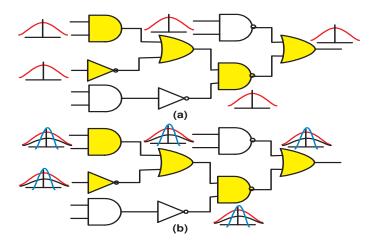

| 3.2        | example schematic implementing a path-based delay estimation method-<br>ology                                                                                                                                                                         | 33 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

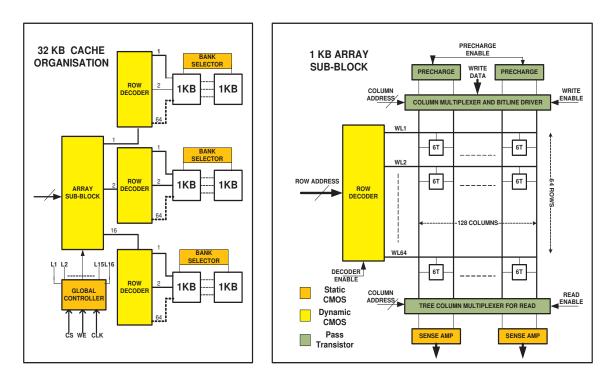

| 3.3        | 32KB memory array design using sub-blocking for energy minimization .                                                                                                                                                                                 | 35 |

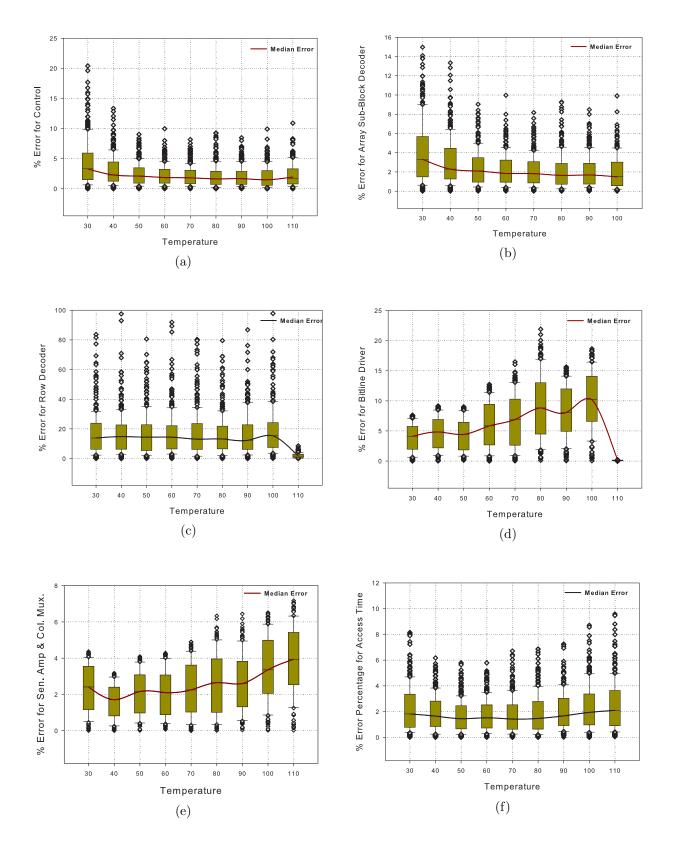

| 3.4        | Error in Calculation of Propagation Delay between Proposed Scheme and HSPICE for (a) Control Circuitry (b) Array Sub-Block Decoder (c) Row Decoder (d) Bitline Driver (e) Sense Amplifier and Column Multiplexer (f) Overall access time              | 39 |

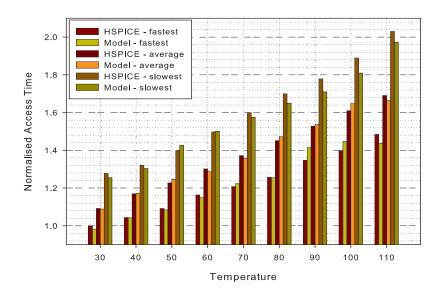

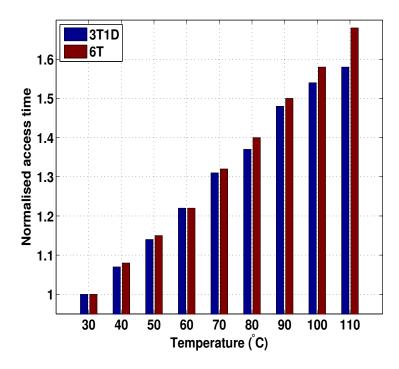

| 3.5        | Variation of normalized access time across multiple dies and temperatures.                                                                                                                                                                            | 41 |

| 3.6        | Impact of Dual $V_{th}$ Assignment on Cache Access Time                                                                                                                                                                                               | 42 |

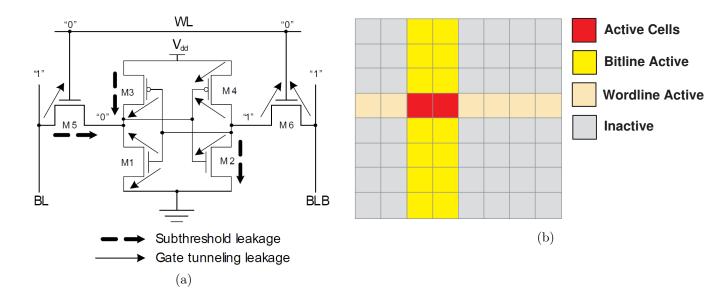

| 3.7        | Leakage power dissipation in SRAM cells (a) Subthreshold and gate tunnelling leakage in 6T-SRAM (b) Sub-array power dissipation layout                                                                                                                | 43 |

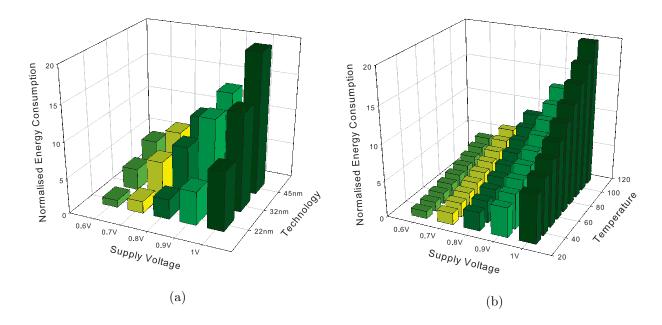

| 3.8        | Normalised memory array energy consumption across a range of supply voltages (a) Comparison across three process generations (45nm, 32nm and 22nm) at 30°C(b) Comparison across a range of temperatures from 20°C-110°C in steps of 20°C in 22nm node | 44 |

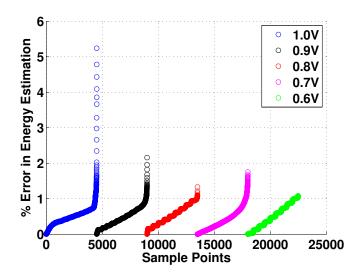

| 3.9        | Percentage error in estimation of memory array energy between HSPICE simulations and MODEST calculations. For the sake of clarity, the data points (estimation error) have been arranged in increasing order for each voltage level.                  | 49 |

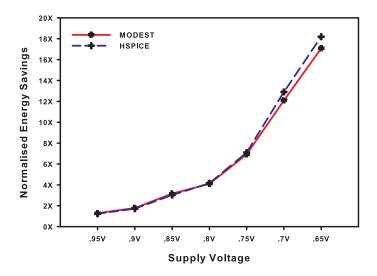

| 3.10       | Comparison between HSPICE and MODEST for estimates of energy savings in a 32KB memory block with supply voltage scaling                                                                                                                               | 50 |

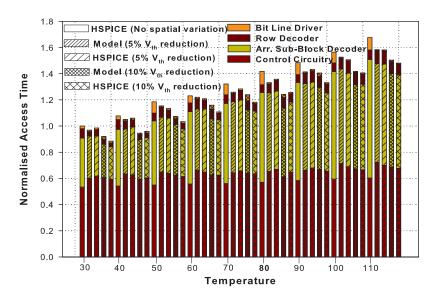

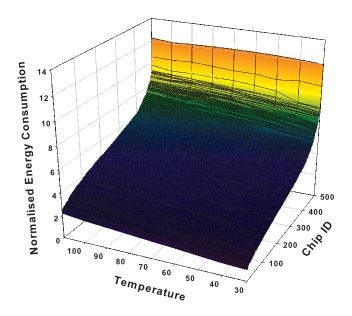

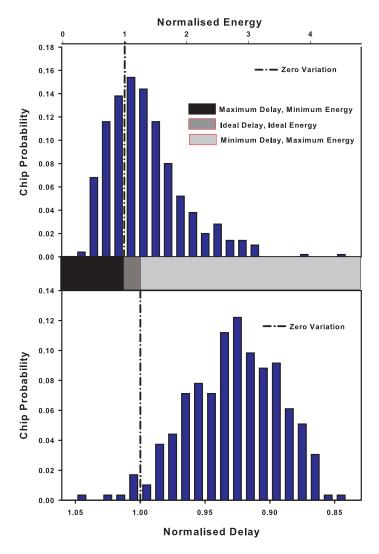

| 3.11       | Energy variations of a 32KB memory block under the impact of spatial and temperature variations                                                                                                                                                       | 51 |

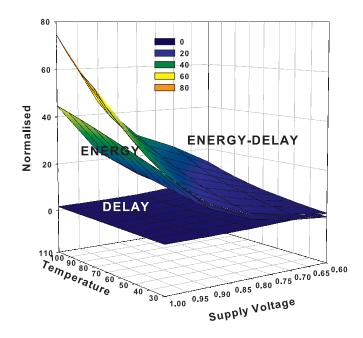

| 3.12       | Energy-delay variation of a 32KB memory block under the impact of temperature and supply voltage variations                                                                                                                                           | 52 |

| 3.13       | Distribution of energy-delay variations of a 32KB memory block under the impact of spatial variations                                                                                                                                                 | 53 |

| 3.14       | Studying the impact of simultaneous dual- $V_{th}$ & standby supply voltage minimization optimization by using MODEST                                                                                                                                 | 54 |

| <i>4</i> 1 | Schematic of the 3T1D eDRAM memory cell                                                                                                                                                                                                               | 60 |

| 4.2  | 3T1D-DRAM embedded with a 8T-SRAM                                                                                                                                                                   | 61                |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.3  | Comparison of the normalized access times of 3T1D eDRAM and 6T SRAM cell across a range of temperatures                                                                                             | 62                |

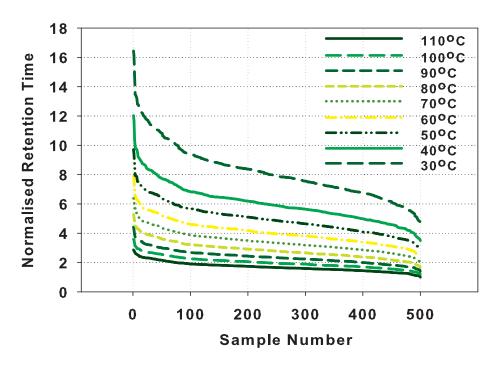

| 4.4  | Comparison of the retention times of a 3T1D cell across a range of temperatures under the impact of spatial variations of process parameters                                                        | 63                |

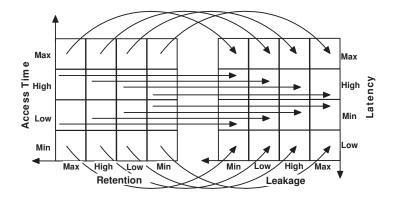

| 4.5  | Discrete Classification based on Latency/Leakage                                                                                                                                                    | 64                |

| 4.6  | Hardware Based Leakage/Latency Bin Classification based on Retention/According                                                                                                                      | ess<br>65         |

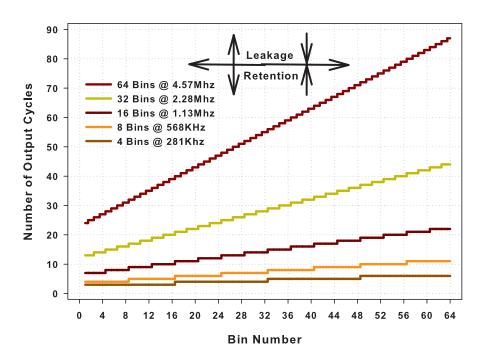

| 4.7  | Number of Output Cycles Vs Power Bin Number. (The number of output cycles (modulo) target number of bins) is the value that is written into the control register                                    | 66                |

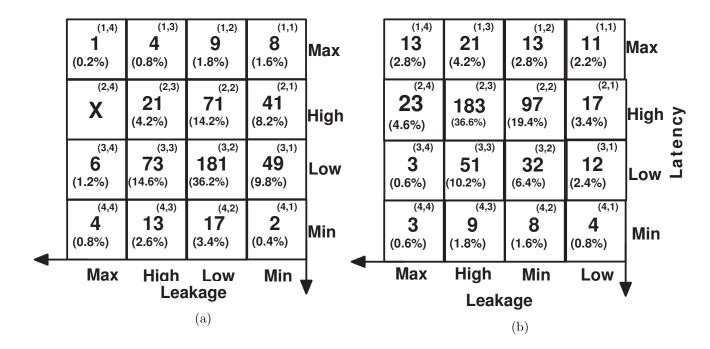

| 4.8  | (a) Power/Performance Binning using Shadow Cells at ambient temperature (b) Power/Performance Binning using Shadow Cells at 110°C temperature                                                       | 67                |

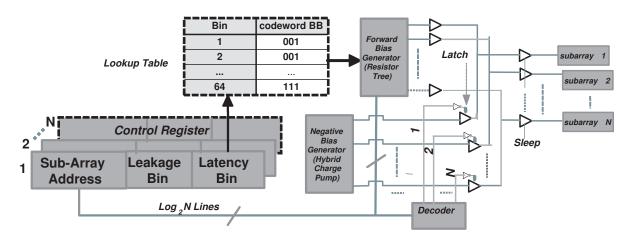

| 4.9  | Fine-Grain Body Bias Generator for Caches                                                                                                                                                           | 69                |

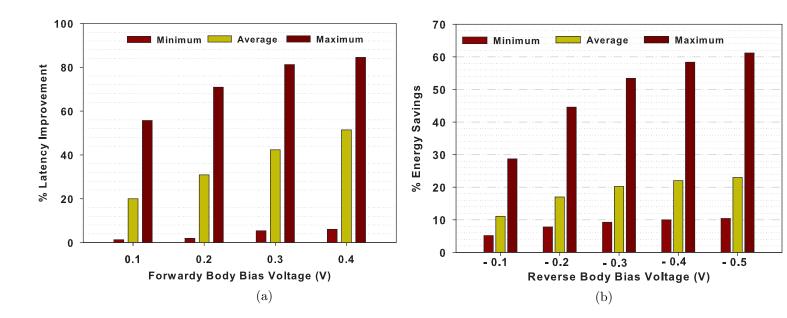

| 4.10 | (a) Percentage Energy Savings as a function of the reverse body voltage & (b) Percentage Latency Improvement as a function of forward body voltage. The bars represent savings when compared to ZBB | 71                |

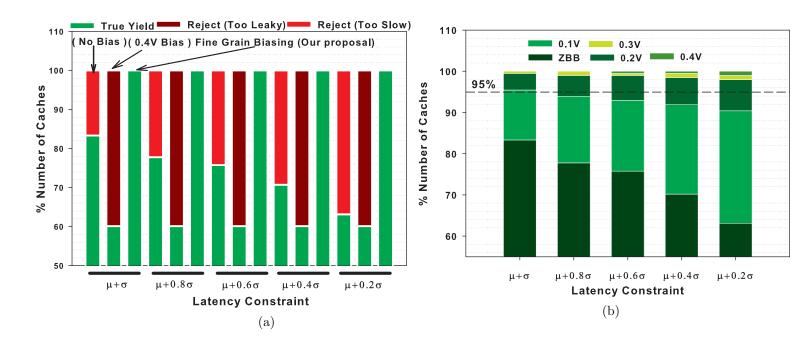

| 4.11 | (a) Yield estimated for ZBB, constant FBB and DFGBB as a function of latency constraints & (b) Number and amount of FB Voltages required for 100% yield                                             | 72                |

| F 1  |                                                                                                                                                                                                     |                   |

| 5.1  | 3T1D-DRAM cell schematic                                                                                                                                                                            | 78<br><b>-</b> 20 |

| 5.2  | Increasing 3T1D read access latency with time after a write access                                                                                                                                  | 79                |

| 5.3  | 4T-DRAM Cell Schematic                                                                                                                                                                              | 80                |

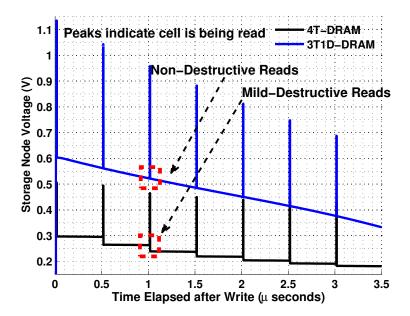

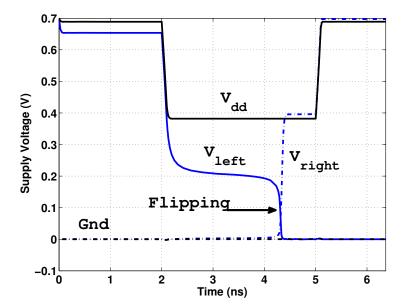

| 5.4  | Storage node voltage of 3T1D-DRAM and 4T-DRAM during read and hold mode                                                                                                                             | 81                |

| 5.5  | Storage node Voltage of 4T-DRAM with body-biasing                                                                                                                                                   | 82                |

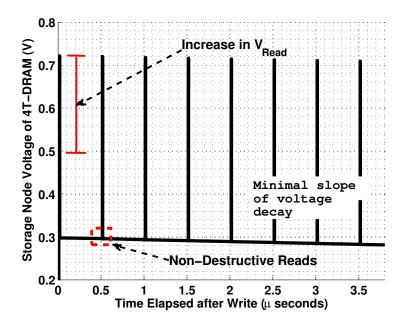

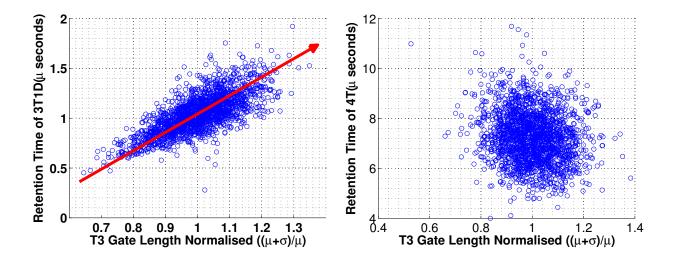

| 5.6  | (a) Retention time-variation of 4T and 3T1D under process variability (b) Cumulative distribution function of the retention times of 4T and 3T1D under process variability                          | 84                |

|      | under process variability                                                                                                                                                                           | 04                |

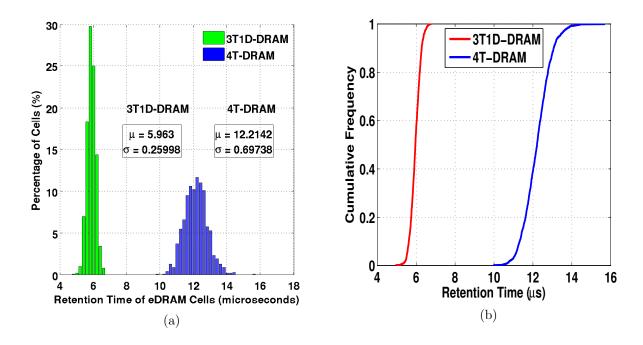

| 5.7  | Influence of gate-length variation of T3 on retention time. (left) 3T1D (right) 4T                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.8  | Read access time-variation of 4T and 3T1D under process variability 86                                                                              |

| 5.9  | Soft-Error rate under varying supply                                                                                                                |

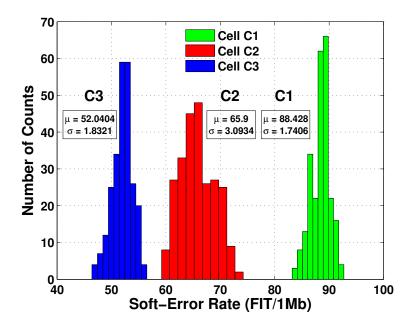

| 5.10 | Soft-Error rate under process variations                                                                                                            |

| 5.11 | Multiple Bit Upsets in 4T                                                                                                                           |

| 6.1  | 6T-SRAM Cell Schematic                                                                                                                              |

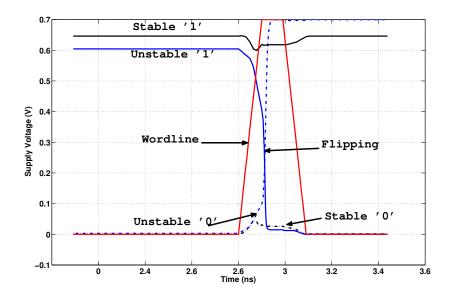

| 6.2  | Mechanism of unstable and stable read operations leading to a failed/successful read accesses                                                       |

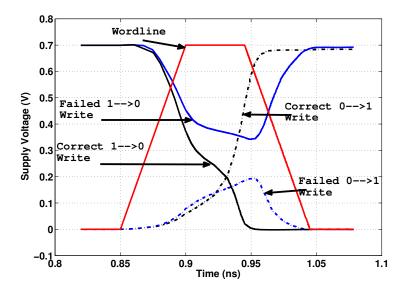

| 6.3  | Mechanism of unstable and stable write operations leading to a failed/successful write accesses                                                     |

| 6.4  | Mechanism of unstable and stable standby mode leading to a failed/successful retention of value                                                     |

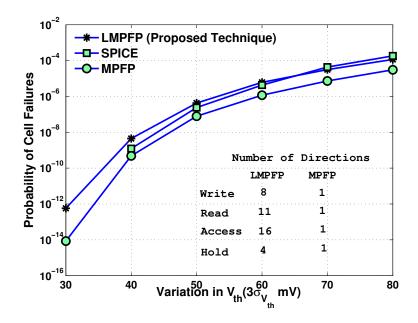

| 6.5  | Failure probabilities under varying threshold voltage deviation                                                                                     |

| 6.6  | INFORMER design flow                                                                                                                                |

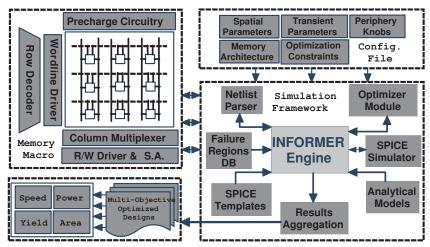

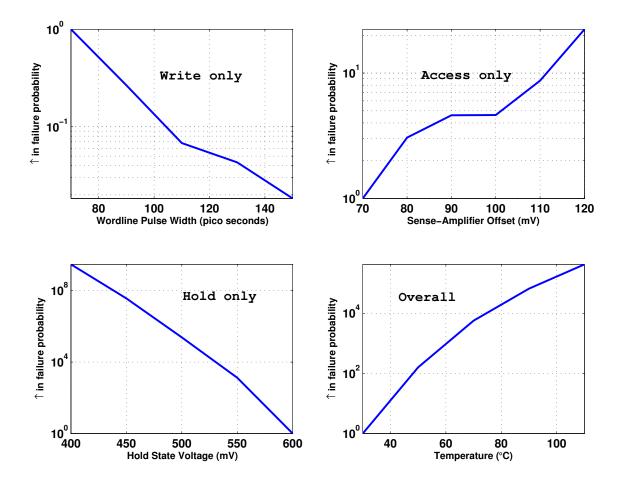

| 6.7  | Estimated increase in failure probabilities as a function of varying control knobs. The values are normalized to the lowest failure probability 103 |

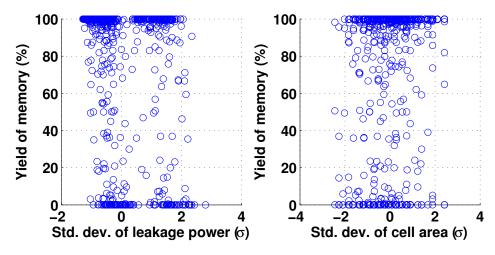

| 6.8  | Impact of cell area and power on yield                                                                                                              |

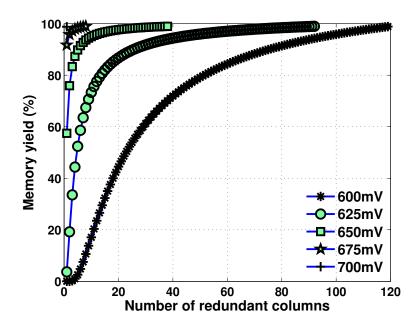

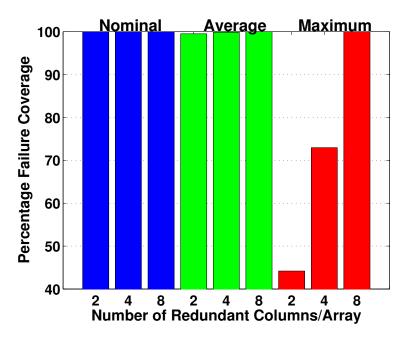

| 6.9  | Yield w.r.t. the number of redundant columns in a 256x128 Array 106                                                                                 |

| 6.10 | Soft-error rate (FIT/1Mb) of memory designed using differently sized SRAM cells under the impact of process variability                             |

| 6.11 | Impact of body biasing on cell failure probability                                                                                                  |

| 6.12 | Impact of wordline boosting on cell failure probability                                                                                             |

| 6.13 | Number of Failures observed for varying word size                                                                                                   |

| 6.14 | Impact of redundancy on fault coverage                                                                                                              |

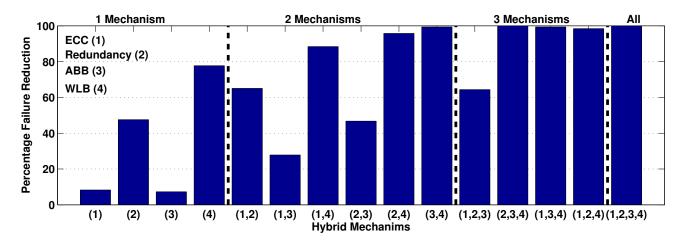

| 6.15 | Hybrid yield enhancement techniques                                                                                                                 |

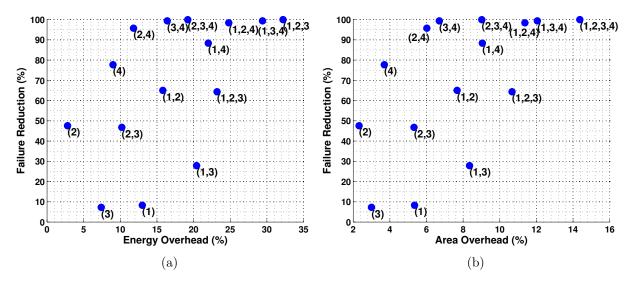

| 6.16 | Improvement in parametric yield at the cost of increasing area and energy overheads when using hybrid techniques                                    |

# List of Tables

| 2.1 | Reactive-Diffusion model based threshold voltage shift                 | 20  |

|-----|------------------------------------------------------------------------|-----|

| 3.1 | Parameter Deviation                                                    | 38  |

| 3.2 | Simulation time speedup of the model compared to HSPICE simulations    | 40  |

| 3.3 | Energy breakdown of each component in the memory block                 | 47  |

|     |                                                                        |     |

| 5.1 | Parameter Deviation                                                    | 84  |

| 5.2 | MBU Comparison between 3T1D and 4T                                     | 90  |

|     |                                                                        |     |

| 6.1 | Percentage reduction in failures for a combination of WLB and reactive |     |

|     | mechanisms (C - Column Redundancy)                                     | 113 |

#### Acknowledgements

I would like to thank my advisors Prof.Ramon Canal, Prof.Antonio González and Prof. Antonio Rubio for providing me this wonderful opportunity to do a PhD under their tutelage. Ramon over these last six years has been a great mentor and an even better friend who has helped me successfully navigate through the rough seas of a PhD. Ramon has always insisted on keeping things simple and focused. I hope someday I can emulate the great qualities as an advisor he has to offer. Antonio González has been very supportive of my research endeavors and provided me the much needed freedom to work on a problem of my choice. One of the most valuable lessons Antonio taught me was that communicating research ideas in a lucid manner is of paramount importance to a good researcher. Antonio Rubio has been one of the most affable teachers I have studied under. I could approach him for scientific advise at all times and he would readily spend hours together working on the problem. For all the motivation, encouragement and enlightenment, I cannot thank my advisors enough. I would also like to thank Jaume Abella (Barcelona Super Computing Center), Serkan Ozdemir (Intel Barcelona Research Center) and Francesc Moll (UPC) for their valuable comments and suggestions through the course of preparing this thesis.

My time here at UPC was made all the more pleasant in part due to the many friends and colleagues who in one way or the other have contributed to the betterment of my life here. I would like to thank all the students who have worked at D6-113 over the course of last six years. I particularly enjoyed the numerous coffee breaks where we indulged in conversations ranging from fifth century Indian ideologies to twenty first century internet of things. I would like to thank all members of the ARCO group for instilling in me the importance of teamwork and providing important feedback after the group's seminar sessions. I would like to thank Dr.Dan Alexandrescu and Enrico Costenaro from iRoC technologies for having me as an intern in their organization. Dan

and Enrico have been very positive about my research and were instrumental in helping me receive the 2012 Intel Doctoral Student Honor Programme fellowship. They were also kind enough to let me access their servers and other resources for a sufficient period after my internship. I would also like to thank all personnel from LCAC and ADMAC who have offloaded from me all issues pertaining to non-technical aspects of my PhD.

Outside life at UPC, I've had the privilege of making friends with a number of people who have made my life all the more enjoyable. I thank Vinoth, Karthi, Aswin, Karishma, Rahul, Adi, Vinay, Martha, Sudhanshu, Prithvi, Rammy, CK and Maddy who through the years have managed to put up with all my tantrums and still enjoy my company. Back in India, Venkat, Varun, Yogi, Sats, Vrusha and Sujatha who I now know for more than a decade have always supported me in all my endeavors and have made my vacations back home extremely enjoyable. Thank you!

I would like to thank my undergraduate mentor Prof. Venkateswaran for having faith in me and providing me an opportunity to study at WARFT. Not only a great mentor, he has been a cornerstone in my professional development.

I would not have dared to begin this journey if not for my family. I am forever indebted to my parents for showering me with all the unconditional love and affection and quite literally standing by my side in times of crisis. My father has always valued the importance of hard work and perseverance while my mother often reminds me of how important it is to think and stay positive. Today, I think their combined efforts have brought to fruition a better researcher in me. I know I can always count on my brother and sisterin-law during rough times and I am grateful to them for that. My adorable niece has been a bundle of joy always re-energizing me after a hard day's work. Thank you amma, appa, anna & manni!

Finally, I would like express my gratitude to the almighty for providing me the strength and blessings to complete this journey. Dedicated to Akriti, Anna, Manni, Amma & Appa

#### Introduction

In the last 40 years, computer architects have obediently followed Moore's law by designing microprocessors that scale performance at a rate equal to the growth of number of devices on a chip. This phenomena, made possible by the tremendous advancements in manufacturing technology, has today enabled billion transistor integration, paving the way for even faster processors with lower power consumption. Technology scaling has thus provided a stable platform for constant innovation that allows us to design complex processors requiring integration of increased amount of functionality. We, as consumers of such innovations are already enjoying the benefits as evinced by our heavy reliance on one or more number of modern day electronic gadgets.

To be able to sustain this pace of innovation, it is imperative that Moore's law needs to continue being a major driver for semiconductor companies. Moore's law mainly deals with scaling of resources quantitatively and does not delve into the attributes of changing device characteristics. In the present day context, this observation is of extreme importance as we scale to deep sub-micron technologies where semiconductor manufacturing is the biggest bottleneck that is mitigating the advantages of continuous device scaling. This is because, the ability to exert complete control and maintain uniformity over the

manufacturing process is reducing with every subsequent technology node. As a result, imperfect fabrication conditions introduce variations in process parameters that make the chip behave differently from their design specifications. These variations in parameter values between intended design and obtained chip manifest as a reduction in yield, increase in idle power and/or considerable reduction in performance. Overcoming such pitfalls by adopting a variation-aware design paradigm requires developing holistic design principles that involve leveraging information obtained from pre-silicon characterization through extensive design-space exploration and employing it to develop run-time response techniques using on-chip mechanisms for variability compensation.

#### 1.1 Impact of Spatio - Temporal Variations

#### 1.1.1 Power/Performance Variability

Variation in key transistor parameters like threshold voltage, channel length and width manifest as a wide spread in circuit characteristics such as delay and leakage. While certain chips run faster than the desired specifications, there are others that fail to meet the expected operating frequencies. The slower chips have to be discarded resulting in a yield loss or rely on post-manufacturing binning to be sold at a lower cost. It was shown in [16], the highest impact on maximum operating frequency  $F_{max}$  is due to within-die systematic variations. Assuming a  $3\sigma$  variation of 20% in channel length in 50nm technology node, a generation of performance gain can be lost. However, further results have also indicated that the spread in  $F_{max}$  tends to average out with increasing logic depth. Dynamic power (switching power) is quadratically proportional to the supply voltage and supply voltage scaling is an effective method for power savings. However, with technology scaling, the rate of voltage scaling has diminished due to the stringent requirements set on performance (directly proportional to voltage). Designers have rather relied on aggressive generational (process generation) reduction in threshold voltage for improving performance with every subsequent technology node. One of the main challenges of such an approach is coping with static power (leakage) which increases exponentially with reducing threshold voltage. In the era of dark silicon where it is understood that large amounts of on-chip components will be under-utilised and remain in their idle-state, leakage power can become quite significant in the context of overall system power. As evinced by previous researchers in [32], either under- or over-designing processors will

never suffice as it can result in reduced performance or rejection of good-dies in lieu of not meeting power budgets. In such cases, it is important to develop accurate models that can capture the non-trivial impact of variations on parameters such as delay and power. This can ensure designers prevent either under- or over-estimation of system parameters and help them make important design decisions in the early-stages of the design life-cycle.

#### 1.1.2 Soft Failures and Errors

Dynamic voltage scaling (DVS) techniques can help the system toggle between high-performance and low-power modes by frequently modulating the supply voltage. Lower supply voltage modes resulting in lower power consumption are generally exercised during periods of minimum activity or when parts of the processor are in the standby mode. As the voltage is lowered further, the analog distance between logic '0' and logic '1' is reduced tremendously. In other words, the margin differentiating a logic '0' and logic '1' is very minimum. This margin can be very easily disturbed by providing a small amount of noise. Process variations and external factors are very much capable of inducing such a noise during regular operation of the processor. The stability is disturbed causing intermittent failures (or errors) killing the functionality of the underlying logic. Such disturbances result in unintentional flipping of logic values and frequent flipping can stall the system in certain scenarios. Voltage-noise dependent stability concerns can result in two types of reliability problems

- Parametric Failures: Random variations in device parameters can lower the noise margin of the transistor by making them weak (high threshold voltage) reducing the overall drive current. The amount of current needed for a transition is dependent on threshold voltage value and for transistors with  $-\sigma_{V_{th}}$ , increase in current flow can upset the state of the transistor causing a failure. These types of intermittent failures are known as parametric failures that are largely dependent on parameter values affecting key electrical characteristics of the transistor.

- Soft Errors: Radio-active particles generated either by cosmic rays or impurities (secondary particles) in the package can interact with the substrate and generate electron-hole pairs. This process creates sufficient energy (noise) that can disturb the stability of the component leading to an error. Such errors are intermittent and dependent heavily on operating environment. The term soft indicates they are transient in nature as opposed to hard faults.

#### 1.1.3 Lifetime Reliability

The previous two challenges highlighted concerns mostly arising from imperfect fabrication conditions resulting in static variations of process parameters. It is assumed that any system without mechanical moving parts will never degrade temporally and can guarantee consistent functionality across its lifetime. However, under heavy workloads and continuous stress, the underlying silicon material is subjected to physical changes that can alter the fundamental behaviour of transistor. This stress can be attributed to con-

Figure 1.1: Bathtub Curve: Failure rate across operational lifetime

stant scaling of device dimensions that has resulted in reduction of gate oxide thickness leading to increased electric field densities across the device. Negative bias temperature instability (NBTI) is one such reliability mechanism that manifests as an increase in the threshold voltage of PMOS transistors across the lifetime. Such temporal variations in the threshold voltage translate directly to a spread in power and performance temporally. Increase in delay (reduced performance) can cause timing violations exacerbating NBTI-dependent parametric failures. Figure 1.1 shows the failure rate of any product across its lifetime. The trend in failure rate can be figuratively described by the bathtub curve. During the initial period of operation, also called 'infant mortality period', the rate of failure is high and reduces gradually with time. The high failure rate is due do

failures arising from imperfect manufacturing, defects in the material, bugs introduced during design-stages and some other failures that are accelerated by post-manufacturing testing processes such as burn-in. With reduction in failure rate, a plateaued behaviour is observed during which the failure rate is constant. Random errors and failures caused by external sources such as cosmic-rays and cross-talk induced noise maintain this constant failure rate. Aggressive degradation and ageing increase the failure rate towards the end of the product life-cycle. Such failures are called wear-out failures and drastically reduce product reliability.

#### 1.2 Nanometer Embedded Memory Design

As postulated by the  $F_{max}$  theory, structures with the most number of parallel and shallow critical paths are the most affected by parametric variations. Embedded memories such as register files, shared and private caches are example structures that exhibit the above characteristics. Due to lower area overhead compared to the performance they offer, on-chip memories are growing in size with every new process generation. It is strongly expected that in the following generations, more than 90% of silicon real-estate will be covered with embedded memories. This is primarily driven by factors such as need for higher performance, lower power and most importantly higher density (tighter integration).

As memories are a very important component from an area point of view, it thus becomes extremely challenging to optimize chip yield keeping in mind the effects of spatial variations of process parameters and temporal variations of temperature and voltage. Modern day caches rely on high-performance, low-power six transistor static random access memory(6T-SRAM) cells for storing data. As shown in figure 1.2, as we move from one process generation to next, while there is moderate reduction of approximately 30% in feature sizes (gate-pitch), SRAM bitcells are subjected to restrictive design rules that necessitate atleast 50% reduction in area as we move from one technology to another. This enables integration of as much as  $152\text{Mbit}/cm^2$  in state of the art 45nm technology. Given these area constraints, memory cells are typically designed using minimum geometry transistors that are highly susceptible to intrinsic device level variations. This can be attributed to device dimensions (using minimum geometry transistors) where the effects of random dopant fluctuations (RDF) and line-edge roughness (LER) are more pronounced [107]. With aggressive scaling, due to atomic level fluctuations (intrinsic

Figure 1.2: SRAM cell area scaling from 350nm to 45nm across 7 process generations [3, 113]

fluctuations), even adjacent SRAM cells do not exhibit uniform characteristics resulting in erratic runtime behaviour of similarly designed structures. In addition to influencing the power and performance characteristics of the memory negatively, variations can affect strongly the functionality of the memory cell making them especially susceptible to large number of failure mechanisms (see previous section).

As shown in figure 1.3, the amount of  $V_{cc_{min}}$  (defined as the minimum voltage of operation that guarantees reliable functioning of the system) influenced failures increases by orders of magnitude with every subsequent process generation. Hard failures due to manufacturing defects or mechanisms like NBTI are shown to have reduced with scaling. This can be attributed to the improvements in the underlying manufacturing processes. The failures induced in memories concern chip designers the most as they can influence a large number of design choices at different levels of abstraction [18]. For example, the  $V_{cc_{min}}$  of the cache which decides the  $V_{cc_{min}}$  of the whole processor is dependent on the highest  $V_{cc_{min}}$  among all cells in all arrays. This would mean that, under the effects of random variations where failures are distributed, a single SRAM cell could potentially affect the functional yield of the whole processor if no repair mechanisms are in place. Reduction in functional yield translates directly to a reduction in total cache addressable space. Such a phenomenon can have a serious detrimental effect on system-wide metrics such IPC and performance/watt.

Moving away from SRAM technology in light of such scalability challenges, semiconductor companies have recently started embracing embedded-DRAM (eDRAM) technology

Figure 1.3: Hard and soft failure trends with SRAM scaling [86].

nology for on-chip memories that has recently led to their adoption in many commercial products. 1T1C eDRAM cells are the most widely used but because of their high latency and reads being destructive, they cannot be used in latency-sensitive components like L1 caches. On the contrary, basic three-transistor (3T)-eDRAM and its derivatives in addition to offering access speeds on par with regular SRAM, provide non-destructive reads and are capable of driving large-loaded bitlines suitable for operation in low-voltage caches. One of the major advantages of replacing regular SRAMs with eDRAM is the ability to seamless integrate eDRAM designs by virtue of their logic compatibility. As such, no additional process steps are required and eDRAM cells can be easily realised using standard-cell libraries. However, a major cause of concern with all DRAM technology is the data retention capability which diminishes over time. This particular characteristic makes eDRAM technology extremely unsuitable for L1 caches where the data needs to be held for a sufficiently large period without being destroyed. Also, unlike regular capacitor-based DRAMS, a refresh operation (write-back) in eDRAM-based memories is quite expensive from a performance and power perspective. For high-activity factor component like L1 caches, frequent refresh operations in addition to increasing the dynamic power overhead, can reduce the total available bandwidth as the read ports are blocked

during a write-data-back (refresh) operation. Further, as retention time can be in the order of seconds, for a pulse generated by a particle strike (cosmic rays), the window where it can manifest as a bit-flip is very wide, making the cell highly susceptible to soft-errors during hold mode. Therefore, by enhancing the retention time, not only can the cell guarantee fast reads for a larger number of accesses, the time period during which the total charge held by the storage node is much higher than the critical charge ( $Q_{crit}$ ) improving temporal soft-error tolerance.

#### 1.3 Main Contributions

This thesis focuses on addressing the problem of parametric variability in embedded SRAM- and eDRAM-based memories. The techniques proposed to combat variations include a combination of design-specific and run-time optimizations to trade-off reliability for other system-wide metrics.

#### 1.3.1 Model-based Energy-Delay Variation Prediction

In order to optimize memory design under the effects of variability, it is important to model global figures of merit such as performance and power for early-stage estimation. Choices made at the design-stage ensure conflicting requirements from higher-levels are decoupled. A multivariate regression based modelling technique for estimating energy/delay has been proposed. The models rely extensively on circuit-level simulations for gathering empirical data. The multi-dimensional regression problem is then simplified into lesser dimensions by a combination of regression and clustering. By generating a polynomial best-fit for the output data, the slope is optimized till the error between simulated data and model generated data is minimum. The median error between generated and simulated data for delay and energy was 1.75% & 0.8% respectively. When combined with architecture-level specifics, the models can then guide large-scale design space exploration.

In relation to this topic, two papers have been published.

- MODEST: A Model For Energy Estimation under Spatio Temporal Variability [42]

S.Ganapathy, R.Canal, A.Gonzalez & A.Rubio

International Symposium on Low Power Electronic Design (ISLPED'10)

- Circuit Propagation Delay Estimation through Multivariate Regression-Based Modeling

under Spatio-Temporal Variability [41]

S.Ganapathy, R.Canal, A.Gonzalez & A.Rubio

Design, Automation & Test in Europe Conference (DATE'10)

#### 1.3.2 Post-Silicon Adaptivity Using Hardware Monitoring

In order to take full-advantage of constant feature minimization, it is important to provide runtime support to complement design-level optimizations. Post-silicon adaptivity involves detecting changes in low-level circuit parameters (delay & leakage currents) post-manufacturing using on-chip canary structures and providing recovery circuits for effective repair. We have proposed a novel three-transistor one-diode (3T1D)DRAM based on-chip sensor for obtaining run-time latency/leakage profiles of memories. The profiles are stored in a lookup table that is referenced by dynamic fine-grain body-bias generator to generate an optimal body-bias that trades-off leakage power for cache latency. Our technique reduces leakage energy consumption and improves access latency of the cache on an average by 20% & 18% respectively.

In relation to this topic, one paper has been published.

• Dynamic Fine-Grain Body Biasing of Caches with Latency and Leakage 3T1D-based Monitors [43]

S.Ganapathy, R.Canal, A.Gonzalez & A.Rubio International Conference on Computer Design (ICCD'11)

#### 1.3.3 Soft-Error Hardened Embedded 4T-DRAM Cell

We propose a a novel 4T-based eDRAM cell that when compared to a similar sized eDRAM cell has higher tolerance to process variations and soft-errors. We replace the gated-diode in a 3T1D (3-Transistor 1-Diode) cell with a NMOS pass transistor to suppress sub-threshold leakage which in turn improves the retention time. This is shown to improve the retention by 2.04X on average. The only downside though is that the absence of gated diode reduces gate-overdrive making the cell slower. The resulting increase in write access time is 3% is small enough to not have a system-wide performance degradation. Another function of the pass transistor is to reduce the total sensitive-area exposed to neutron strikes. With a long-channel length pass-transistor, the amount of time needed by the generated pulse to traverse through is long enough to generate only a

small glitch and not cause a bit-flip due to neutron-induced energization. The soft-error rate which is measured in terms of failures-in-time (FIT) is reduced by 36% on average.

In relation to this topic, one paper has been published.

• A Novel Variation-Tolerant 4T-DRAM with Enhanced Soft-Error Tolerance [44] S.Ganapathy, R.Canal, D.Alexandrescu, E.Costenaro, A.Gonzalez & A.Rubio International Conference on Computer Design (ICCD'12)

#### 1.3.4 Parametric Yield Enhancement Using Hybrid Techniques

The effectiveness of combining failure-prevention and failure-reduction techniques is thoroughly investigated in this study. Proactive read/write assist mechanisms that operate at the sub-array level reduce the failure probability of the SRAM-cell by modifying the electrical characteristics of a transistor at run-time. This is effected using techniques such as body-biasing or wordline boosting that either improve read or write noise margins. Assist techniques can help lower  $V_{cc_{min}}$  whilst maintaining a failure rate observable at nominal voltages. This can enable large-scale power reduction. Reactive mechanisms such as error-correcting codes (ECC) and redundancy can then be used to recover from any persistent failures due to lowering of  $V_{cc_{min}}$ . While proactive techniques can help improve functional margin (lowering power), reactive techniques improve functional yield (total addressable space). Contrary to the notion that the two class of techniques are mutually exclusive, we show that the hybrid schemes offer better quality-energy-area trade-offs when compared to their standalone configurations.

In relation to this topic, one paper has been published.

• Effectiveness of Hybrid Recovery Techniques on Parametric Failures [45] S.Ganapathy, R.Canal, A.Gonzalez & A.Rubio International Symposium on Quality Electronic Design (ISQED'13)

#### 1.3.5 INFORMER: A Tool for Memory Robustness Analysis

Adopting a variation-aware design paradigm requires a holistic perspective of memory-wide metrics such as yield, power and performance. However, accurate estimation of such metrics is largely dependent on circuit implementation styles, technology parameters and architecture-level specifics. In line with the requirements, we designed a prototype tool (INFORMER) that helps high-level designers estimate memory reliability metrics rapidly

and accurately for a given SRAM cell design, technology, topology, working environment and memory architecture. The tool relies on accurate circuit-level simulations to capture multiple failure mechanisms (ageing, soft-errors and parametric failures) and helps couple low-level statistics with higher-level design choices. Additionally, to estimate the failure probability of rare events (low probability) where traditional Monte-Carlo based sampling techniques suffer, we propose a novel algorithm that leverages SRAM transistor dimensions to determine regions of higher failure probability. In these regions, we then determine the *most probable failure point* around which norm-minimization based importance sampling is exercised. The technique achieves near-SPICE like accuracy while improving simulation time by orders of magnitude.

In relation to this topic, a paper has been published.

• INFORMER: An Integrated Framework for Early-Stage Memory Robustness Analysis S.Ganapathy, R.Canal, D.Alexandrescu, E.Costenaro, A.Gonzalez & A.Rubio Design, Automation & Test in Europe Conference (DATE'14)

# 2

## Background and Related Work

#### 2.1 Overview

In this chapter, we present an overview of several topics needed to better understand the fundamentals of variation-tolerant design. Section 2.3 broadly discusses different sources of variation and how they are characterized. This section covers variations arising from manufacturing processes, fluctuations in environmental parameters (supply voltage and temperature) and finally temporal variations due to degradation. In section 2.4, techniques to cope with variability ranging from design-level optimizations to run-time adaptation using circuit and architecture mechanisms are discussed. Section 2.5 discusses the impact of variations on embedded memories specifically. Techniques to lower power/performance/yield variation using novel cell topologies, post-silicon adaptivity and cache reconfiguration are discussed here.

#### 2.2 Process Variations

Process variations are statistically defined by the difference in parameter values between intended design and the obtained product. They are primarily caused by imperfect manufacturing conditions due to challenges imposed by the lack of complete control over the process.

#### 2.3 Sources of Variations

Spatial variations of process parameters affect the electrical characteristics of both transistors and the underlying interconnect fabric. They are broadly classified into statistical and systematic variations. Statistical variations arising from unfavourable conditions either during wafer processing steps such as oxidation, diffusion, etching, ion implantation, chemical- mechanical polishing (CMP), electroplating or annealing can cause variation in parameters such as impurity concentrations and oxide thickness. Further, limitations imposed by photo-lithography in advanced process nodes, makes it extremely cumbersome to draw smaller lines. In such scenarios, issues such as lens abberations cause a further deviation in the  $\frac{W}{L}$  ratio of transistor and interconnect dimensions. Broadly speaking, spatial variations of process parameters can be divided into two classes:

- Die-to-Die (D2D): Mainly caused due to discrepancies in lithography, CMP and RTA, die-level variations are global inter-die variations that cause a difference across die(s) without affecting devices within a die.

- Within-Die (WID): Characterised by both systematic and random WID variations. Systematic variations are proximity and layout geometry dependent wherein variations in certain components cause a variation in a nearby similarly designed component. As the distance increases, the correlation in variation reduces subjecting on-chip components to accidental heterogeneity with differing power and performance profiles. Intrinsic device level fluctuations caused due to effects such as random dopant fluctuations and line edge roughness induce discrepancy in electrical characteristics even across adjacent transistors.

#### 2.3.1 Random Dopant Fluctuations (RDF)

This type of variations are primarily caused due to the random placement of dopant atoms in the channel. The effect is more pronounced with scaling of technology where the total number of dopant atoms needed for implantation reduces with subsequent technology nodes. This problem of RDF has been well documented over the last three decades and has been predicted to be a major challenge for controlling device performance. Due to the random nature of this phenomena, the threshold voltage  $(V_{th})$  of the transistor undergoes significant variation. This is because the intrinsic value of  $V_{th}$  is dependent on the charge of the ionized dopants in the depletion region. The standard deviation of  $V_{th}$  follows the inverse square law of the device area. In other words, with scaling of technology,  $\sigma V_{th}$  dependent on RDF increases for transistors with smaller area. The variation in  $V_{th}$  due to RDF has been demonstrated to follow a Gaussian distribution with its standard deviation derived as,

$$\sigma V_{th} = (\sqrt[4]{2q^3 \epsilon_{Si} N_a \phi_B}) \cdot \frac{T_{ox}}{\epsilon_{ox}} \cdot \frac{1}{\sqrt{3WL}}$$

(2.1)

where q represents electron charge,  $\epsilon_{Si}$  and  $\epsilon_{ox}$  are permittivity of silicon and gate oxide,  $N_a$  is the channel dopant concentration,  $\phi_B$  is the difference between Fermi level and intrinsic level,  $T_{ox}$  is the gate oxide thickness, W and L are the channel width and length of the transistor, respectively [3, 84].

The trend in reduction in the total number of dopant atoms when reducing device dimensions is shown in figure 2.1a. It is evident that with reduction in total number of dopant atoms with subsequent process nodes, the increase in  $\sigma V_{th}$  is significant. Figures 2.1b & 2.1c show the cross-section of two-identical MOSFETs each with 170 dopant atoms. However, because of the difference in placement of the dopant atoms along the channel, the device in figure 2.1b has a  $V_{th}$  of 0.78V when compared to the device in figure 2.1c that has a threshold of 0.56V. This is primarily because of the fact that a minimum number of dopants in device (b) in the middle of the channel spaced equally along the channel width block the free flow of current increasing the threshold voltage [9]. As RDF is inversely proportional to the device area, SRAM cells constructed with minimum geometry transistors are intrinsically the most susceptible to this type of variation.

Figure 2.1: (a) Scaling trend of  $V_{th}$  variance due to random dopant fluctuations (RDF) [114] (b) MOSFET with  $V_{th} = 0.78V$  (170 dopant atoms) (c) MOSFET with  $V_{th} = 0.56V$  (170 dopant atoms) [9]

#### 2.3.2 Line-Edge Roughness

Line-edge roughness is mainly caused by the change in the shape of the gate along the channel width direction [114]. This roughness in the edge of the gate is caused by the inherent characteristics of the materials forming the gate and additional process steps such as etching and imperfection in lithography. The impact of this phenomenon is more pronounced at technologies below 50nm where stringent constraints set on the device performance require much higher level of control over the gate-length. The impact of LER induced variation on  $V_{th}$  follows Gaussian distribution and is inversely proportional to the gate width of the transistor [13]. The impact of LER when changing the device dimension from  $W_1$  to  $W_2$  on  $\sigma V_{th}$  is given by the following equation,

$$\sigma_{V_{th}|W_2} = \sqrt{W_1/W_2} \ \sigma_{V_{th}|W_1} \tag{2.2}$$

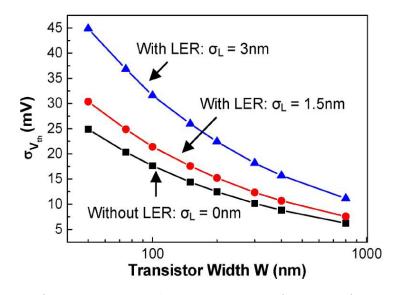

Figure 2.2: Impact of Line-Edge Roughness on  $V_{th}$  as a function of transistor width [114]

Figure 2.2 shows the impact of LER on  $V_{th}$  fluctuation with scaling of transistor widths. As explained in [114], the variance of this phenomena does not reduce with technology scaling despite improvements to the underlying manufacturing technology. As a result, the problem can become quite critical for devices such as memory cells that are extremely susceptible to device-level  $V_{th}$  mismatch.

#### 2.3.3 Channel Length Variation

Variations or perturbations during the lithography phase are known to affect a large number of electrical characteristics. Variation in transistor channel length or critical dimension (CD) is the most critical from a performance perspective [87] This is primarily because of the fact that effective channel length being the smallest implemented on-die feature, it is the most susceptible to intra-die variation resulting from Optical Proximity Errors (OPE). For short-channel devices with +ve standard deviation, the resulting reduction in drive current increases propagation delay tremendously ( $\approx C_L V_{DD}/2I_D$ ). This effect can be better explained by the phenomena better known as *Drain induced barrier lowering* (DIBL) where in technologies below 45nm, in short-channel devices, the threshold voltage is strongly dependent on the channel length. Using techniques such as forward body-biasing, the  $V_{th}$  roll-off can be reduced lowering the influence of channel length variation on  $V_{th}$ . However, this incurs significant overhead in leakage power.

#### 2.3.4 Environmental Variations

#### 2.3.4.1 Thermal variations

In-line with the consequences of Moore's law, on-chip power density has been observed to double approximately every three years. It is expected that this phenomenon will exacerbate with the introduction of new materials and constant feature minimization. As the dissipated energy is converted into waste heat, the corresponding increase in thermal density is creating new challenges in reliability and manufacturing costs [100]. While techniques like supply voltage scaling can help reduce the overall on-die temperature, it impacts speed negatively lowering processor wide performance. As enumerated in [13], spatial variation of temperature on-die is dependent on the following factors

- Correlation with temperature profile of adjacent blocks: Depending upon the switching activity and power demands of a particular block, the thermal characteristics of adjacent areas are influenced significantly. Frequent temperature shoot-ups can cause functionality problems resulting in failures that can permanently damage the underlying silicon.

- Material dependence: The rate at which the heat spreads is dependent on the thermal conductivity of the material used. Bulk-CMOS technology in comparison to silicon-on-insulator (SOI) helps lower temperature levels as the heat generated is spread into

the substrate and the interconnects. SOI technology, in contrast has lower levels of thermal conductivity of the oxide material making the interconnects better conductors of heat. By making the wafers thinner, resistance of the material is reduced moving the areas of heat generation closer to the heat spreading packaging.

- Cooling and packaging: Traditional designs incorporate either heat pipes or water-cooling to absorb most of the heat that is dissipated from the package. Heat pipes with their increased surface area help remove or move heat to an area with sufficient air-flow. To reduce cost and lower area foot-print in mobile devices such as laptops, packaging decisions often involve omitting the heat spreader plate and heat sink and instead use heat pipes and other mechanisms that reduce the weight and size of the sink.

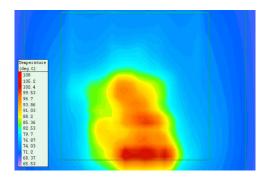

- Activity factor: Run-time variations in the workload of the processor temporally influence both thermal as well as supply voltage variations. Dynamic thermal management (DTM) techniques often rely on on-die hardware sensors to build real-time thermal profiles and enforce cross-layer optimizations to reduce temperature in a staggering manner. Figure 2.3 shows the thermal image of microprocessor with hotspots of temperature as high as 120°C. As the power densities continue to increase with every subsequent process generation, the disparity in performance of blocks across a die will continue to widen.

Figure 2.3: Within die temperature variations [15]

#### 2.3.4.2 Supply voltage variations

This type of variation occur when there is a rapid change in the load (demand) within a short time interval. Due to the parasitic inductance in the power-delivery subsystem, voltage ripples are generated along the supply lines. This is fundamentally defined as the Ldi/dt effect. Due to the stringent constraints set on power consumption, mechanisms

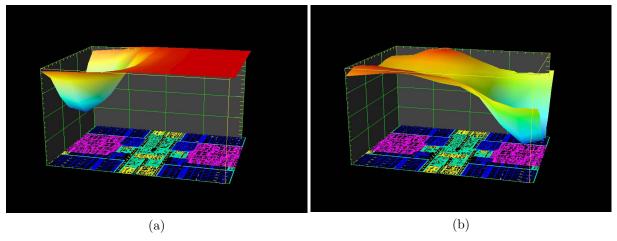

Figure 2.4: Voltage droop in chip multiprocessors where physical cores share the same power grid (a) Voltage droop in a core as it turns on increasing the load (b) coupled voltage droop in another block as it is switched on after a few ns delay [40].

like clock-gating, power-gating and idle/sleep modes that require fine-grained control of the run-time supply voltage make it difficult to prevent these types of variations. In chip multiprocessor architecture (CMP), depending upon the core utilization patterns and activity interaction between cores, the inter-core voltage fluctuation can be quite significant [48]. Figures 2.4a and 2.4b depict the phenomena of voltage droop in one block generating a new voltage droop in another block at a different instant of time. Initially, as shown in figure 2.4a a voltage droop is observed at a block, say Core 1. During this period, another block at the far right corner (say Core 2) is still in the idle mode. A few nano seconds later (4ns for the instruction stream to start on Core 2), as depicted in figure 2.4b, core 2 is switched on after a delay and experiences worse voltage droop compared to Core 1. This is primarily because of the coupling effect where the droop generated in core 1 is coupled to core 2 increasing the supply voltage noise. While it is very cumbersome to predict such run-time behaviour early in the design stage, sufficient guard-banding can mitigate the negative impact to a certain extent. The impact in such scenarios can be minimized by using on-chip regulators and decoupling capacitors [13].

#### 2.3.4.3 Bias Temperature Instability (BTI)

Negative BTI (NBTI) occurs when a negative gate voltage ( $V_{gs} = -V_{dd}$ ) is applied for a sufficient long period at high temperatures. It results in increased  $V_{th}$  with time degrading PMOS performance across the lifetime of the processor. NBTI experienced by PMOS

transistors results from the generation of interface traps along the channel and gate dielectric interface. Due to lower number of holes along the channel in NMOS devices, they do not suffer from NBTI.

NBTI occurs in two phases, namely stress and recovery. Periods of stress are caused due to the generation of interface traps as and when Si-H bonds are broken under the influence of high electric fields and elevated temperatures. The dangling bonds created by the separation of hydrogen-terminated trivalent silicon bonds (Si<sub>3</sub>-Si-H) create traps at the interface causing hydrogen to diffuse into the gate-oxide. This results in a degradation of the  $V_{th}$  of PMOS devices. The annealing process of recovery is made possible by the application of  $V_{dd}$  to the gate that temporarily inhibits further generation of interface traps. As a result, the dissociated hydrogen bonds return to the interface to join with the broken silicon bonds to partially recover degraded threshold voltage.

Table 2.1: Reactive-Diffusion model based threshold voltage shift

|                | $\Delta  V_{th} $ under NBTI                                                   |

|----------------|--------------------------------------------------------------------------------|

| Stress         | $\sqrt{K_v^2 \cdot (t - t_0)^{0.5} + \Delta V_{TH0}} + \delta_v$               |

| Recovery       | $(\Delta V_{TH0} - \delta_v) \cdot \lfloor 1 - \sqrt{\eta(t - t_0)/t} \rfloor$ |

|                | $A.t_{ox}.\sqrt{C_{OX}(V_{GS}-V_{TH})}.$                                       |

| $\mathrm{K}_v$ | $[1 - V_{DS}/\alpha(V_{GS} - V_{TH})].$                                        |

|                | $exp(E_{OX}/E_0).exp(E_a/kT)$                                                  |

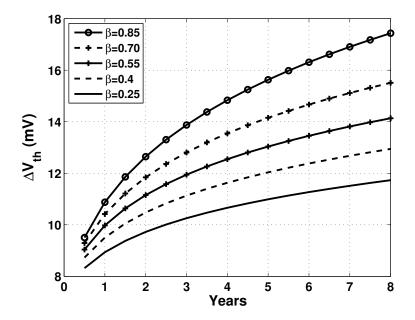

Traditionally, the process of stress and recovery is modelled through the well established Reaction-Diffusion (R-D) theory [7, 73, 108]. Table 2.1 shows the different parameters influencing the amount threshold voltage shift during stress and recovery phases. It should be observable that the change in the threshold voltage  $(\Delta V_{th})$  is directly dependent on the total time under stress ( $\sim t^{0.25}$ ) for a given supply voltage and temperature. By modulating the supply voltage, the overall power-density of the chip can be controlled which in-turn regulates temperature. Temperature has an exponential influence on NBTI stress thereby escalating the degradation at high temperatures (heavy-workload or high supply voltage). The degradation exhibited by NBTI is "frontloaded" in nature wherein the rate of degradation reduces with time [20]. By accounting for the supply voltage-speed dependence, the total time under stress can be considerably manipulated lowering the rate of ageing at nominal voltages. However, as demonstrated in [20], the returns on dynamic voltage scaling diminish due to the "front-loaded" nature of degradation and it cannot be used to extend the lifetime of the processor. Since the device is only under stress when a negative-bias  $(V_{GS} = -V_{dd}|'0')$  is applied, the duty cycle ( $\beta$ ) is an important parameter that can influence  $\Delta V_{th}$  significantly [89]. Figure

Figure 2.5:  $\Delta V_{th}$  shift (under NBTI) in 32nm PMOS device operating at 85°C

2.5 shows the impact of duty cycle ( $\beta$ ) variation on the  $\Delta V_{th}$  for a 32nm PTM PMOS device operating at 85°C [1]. Duty cycle is defined as the ratio of time period between the time the device is under stress ( $logic\ \theta$ ) and recovery ( $logic\ 1$ ). It can be observed that the rate of degradation (slope of  $\Delta V_{th}$ ) is higher for a device with larger duty cycle. Higher shifts in  $\Delta V_{th}$  require higher margin of  $V_{dd}$  or temperature tuning to ensure sufficient recovery. Unlike other design specifications, duty cycle cannot be tuned arbitrarily and the effectiveness of duty-cycle modulation needs to be studied together with other metrics such as component utilization factor and input vector probability.

# 2.4 Coping with Variability

# 2.4.1 Modelling and Optimization using CAD

#### 2.4.1.1 Propagation Delay Calculation

In order to provide a way to optimize performance parameters such as circuit propagation delay across a wide range of process parameters (random variations), statistical design is used extensively. While they can help cope with static variations arising from manufacturing processes, to cope with run-time variations of environmental factors needs on-chip mechanism that can provide necessary support. The first step towards designing fast

and reliable circuits is development of accurate timing models than capture performance variability under the impact of variations. This helps better understand the trade-offs between performance and functional correctness. Timing verification is used to determine the range the operational frequencies that can guarantee a certain yield. In this context, it is important to define two types of violations that are needed to verify the design from a timing perspective.

- Hold-time violation: This type of error is more prevalent in edge-triggered latches where the input is not held (or stable) for a sufficient period after the clock transitions. As a result, if the inputs to the latch change when the edge is triggered, there is certain probability the output is in-deterministic for a short period of time.

- Setup-time violation: If the input signal arrives at a time before the clock has transitioned, then it results in a setup-time violation.