### Development of a multichannel integrated circuit for Silicon Photo-Multiplier arrays readout

Albert Comerma i Montells

**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (**www.tdx.cat**) i a través del Dipòsit Digital de la UB (**diposit.ub.edu**) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX ni al Dipòsit Digital de la UB. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX o al Dipòsit Digital de la UB (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (www.tdx.cat) y a través del Repositorio Digital de la UB (diposit.ub.edu) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR o al Repositorio Digital de la UB. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR o al Repositorio Digital de la UB (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (**www.tdx.cat**) service and by the UB Digital Repository (**diposit.ub.edu**) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized nor its spreading and availability from a site foreign to the TDX service or to the UB Digital Repository. Introducing its content in a window or frame foreign to the TDX service or to the UB Digital Repository is not authorized (framing). Those rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

## Development of a multichannel integrated circuit for Silicon Photo-Multiplier arrays readout

Albert Comerma i Montells

# UNIVERSITAT DE BARCELONA INSITUT DE CIÈNCIES DEL COSMOS DEPARTAMENT D'ELECTRÒNICA PROGRAMA DE DOCTORAT EN ENGINYERIA I TECNOLOGIES AVANCADES

### Development of a multichannel integrated circuit for Silicon Photo-Multiplier arrays readout

### Albert Comerma i Montells

DIRECTOR.

Dr. David Gascón i Fora

TUTOR.

Dr. Atilà Herms i Berenguer

Memòria presentada per  $Albert\ Comerma\ i\ Montells$  per optar al grau de Doctor

Barcelona, 2013

### **Agra**iments

Abans d'agrair res a ningú em voldria disculpar per a totes les persones que m'han ajudat a arribar fins aquí i que no mencionaré en els agraïments. Per començar tots els estudiants de doctorat i postdocs que he tingut la sort de conèixer durant tots aquests anys al departament i que seria llarg d'enumerar i molt probablement impossible de no deixar-me algú.

Moltes gràcies en primer lloc a en David Gascón, per ser el meu director, però sobretot per la seva feina en el disseny de molts dels circuits descrits en aquesta tesi i la seva visió i experiència per entendre com funcionen (o perquè no funcionen) d'una sola ullada. Sense ell hagués estat impossible realitzar aquesta feina (almenys en el temps que s'ha fet).

Gràcies també a en Lluís Freixas per totes les hores de disseny i layout dedicades a molts blocs comentats en aquesta tesi. Sobretot per les nits sense dormir just abans d'enviar a fabricar alguns dels prototips. Sense la seva feina segur que tampoc haguéssim arribat a bon port tant ràpidament.

Muchísimas gracias a José Manuel-Pérez y Jesús Marín del CIEMAT por tener una idea tan clara de como funciona un sistema PET y como debería ser la electrónica de lectura, y a Juan José Vaquero de la UC3M por comentar los problemas que se han encontrado y como mejorar los sistemas actuales. Muchas gracias también a todo el equipo del CIEMAT y en especial a Pedro Rato e Icíar Sarasola por la validación de la electrónica en un sistema PET.

Thanks to EPFL people for their collaboration in the SciFi tracker design, specially to Fred Blanch for all the meetings and Guido Haefeli for the SiPM knowledge and testing.

Thanks also to Hervé Chanal from Clermont Ferrand for all the brainstorming around PACIFIC ASIC.

Merci beaucoup Laurent Royer pour l'intégration du design PACIFICr1 dans TROPIC ASIC.

Moltes gràcies a en Ricardo Graciani per la seva ajuda a entendre què ha de sortir de la mesura d'una font radioactiva i com ha de ser l'espectre resultant d'un cristall. També per proporcionar les fonts del laboratori de docència per a realitzar les mesures. I a en Lluís Garrido i l'Eugeni Graugés per confiar en mi per aquesta tasca i crear i mantenir el grup durant tant de temps.

També haig de donar les gràcies a en Juan Trenado, pels seus processats i gràfics en python, per comentar els seus extensos coneixements sobre el comportament de semiconductors amb mi i totes les hores de testbeam passades (encara que no incloses en aquesta tesi). Moltes gràcies als companys de despatx; Adrià Casajús (per als vale por un Adri), Andreu Sanuy (el rei del layout) i l'Edu Picatoste sempre disposat a donar un cop de mà en qualsevol bloc.

Moltíssimes gràcies als meus pares que em van fer tal com sóc i sempre m'han ajudat i donat suport per a dedicar-me a el que més m'agradés. Inculcar-me la curiositat pel que ens envolta i arribar a entendre com funcionen les coses ha fet que hagi arribat fins aquí. Moltes gràcies als meus germans també, Dani i Núria, dels quals he après moltes més coses de les que es poden imaginar.

Moltes gràcies a en Joan i la Mercè, tu si que vales. I moltíssimes gràcies a la Pat per estar al meu costat, fins i tot mentre intento escriure aquestes línies i la resta de la tesi tancats a casa. Moltes gràcies per compartir la muntanya amb mi. Endavant!

La feina descrita en aquesta tesi ha estat realitzada entre els centres:

Universitat de Barcelona

Institut de Ciències del cosmos

Centro de Investigaciones Energéticas Medioambientales y Tecnológicas (CIEMAT)

### Amb la col.laboració de:

CERN

LHCb

I finançada parcialment pels projectes del Ministerio de Ciencia e Innovacion: FPA2008-06271-c02-01 PTA2009-2077-P

The aim of this thesis is to present a solution for the readout of Silicon Photo-Multipliers (SiPMs) arrays improving currently implemented systems. Using as a starting point previous designs with similar objectives a novel current mode input stage has been designed and tested. To start with the design a valid model has been used to generate realistic output from the SiPMs depending on light input. Design has been performed in first place focusing in general applications for medical imaging Positron Emission Tomography (PET) and then using the same topology for a more constrained design in particle detectors (upgrade of Tracker detector at LHCb experiment).

A 16 channel ASIC for PET applications including the novel input stage has demonstrated an excellent timing measurement with good energy resolution measurement and pile-up detection. This document starts with the analysis of the requirements needed to fit such a system. Followed by a detailed description of the input stage and analog processing. Signal is divided in the input stage into three different signal paths: timing, energy and pile-up. Every channel performs different signal analysis to deliver; a fast time signal output (digital edge), energy output (a linear time over threshold digital output) and a digital bit to signal pile-up. The time information is then ORed between all channels to generate a single timing output. All the pile-up bits are combined in a digital word ready to be readout for the 16 channels. Design has been optimized for reduced power consumption and no components needed to interface inputs and outputs. Digital slow control to tune the circuit behaviour is also included. The prototype measurements have proved to be a valid option for integration in a full system scanner.

An adapted prototype of the input stage using different technology and adapted to the different constraints from a particle detector is also presented. Only simulation results are available since device is still under production. An analysis of the different requirements needed by the SciFi tracker design is summarized. Current specifications are still evolving since final sensor is still not defined, but other requirements and some tunable elements permits to design such prototypes.

### **Contents**

| Λ | D | CT       | ΓR  | Λ | $\mathbf{c}$ | г |

|---|---|----------|-----|---|--------------|---|

| м | u | <b>.</b> | 11/ | м | _            |   |

| RI | ESUN | /       |           |                                        | v     |

|----|------|---------|-----------|----------------------------------------|-------|

| SI | JMM  | ARY     |           |                                        | xxxix |

| P  | ATEN | т пот   | TICE      |                                        | lxxv  |

| 1  | INT  | RODU    | CTION     |                                        | 1     |

|    | 1.1  | Detect  | or System | ms Overview                            | 4     |

|    | 1.2  | Light   | sensors   |                                        | 6     |

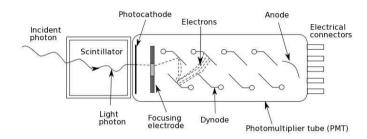

|    |      | 1.2.1   | Photo-N   | Multiplier Tube, PMT                   | 6     |

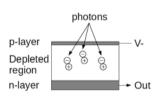

|    |      | 1.2.2   | Avalanc   | che Photo-Diode, APD                   | 9     |

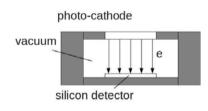

|    |      |         | 1.2.2.1   | Hybrid devices                         | 11    |

|    |      | 1.2.3   | Silicon 1 | photo-multipliers, SiPM                | 12    |

|    |      |         | 1.2.3.1   | Dynamic range                          | 14    |

|    |      |         |           | Gain Variation with Temperature        | 15    |

|    |      |         | 1.2.3.3   | · ·                                    | 16    |

|    |      |         |           | Typical Signal                         | 17    |

|    |      |         |           | After Pulsing                          | 18    |

|    |      |         |           | Dark Count                             | 18    |

|    |      |         |           | Crosstalk                              | 19    |

|    |      | 1.2.4   |           | construction                           | 19    |

|    | 1.3  | Scintil |           |                                        | 22    |

|    |      |         | Phoswic   |                                        | 24    |

|    | 1.4  |         | Applica   |                                        | 26    |

|    |      | 1.4.1   |           | Imaging                                | 26    |

|    |      |         |           | Positron Emission Tomography           | 26    |

|    |      |         | 1.4.1.2   | 0                                      | 29    |

|    |      |         | 1.4.1.3   | Single-Photon Emission Computed Tomog- |       |

|    |      |         |           | raphy                                  | 29    |

|    |      | 1.4.2   |           | Detectors                              | 31    |

|    |      |         |           | CERN and LHC                           | 32    |

|    |      |         | 1.4.2.2   | LHCb                                   | 34    |

|    |      |         | 1.4.2.3   | Scintillator Fibre Tracker             | 36    |

|   |      | 1.4.3  | Other Applications                             | 38 |

|---|------|--------|------------------------------------------------|----|

| 2 | SIP  | м мо   | DELLING                                        | 39 |

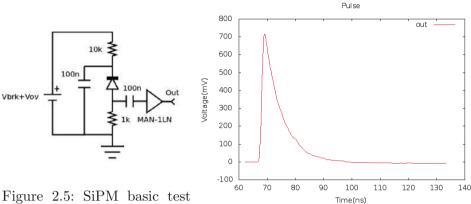

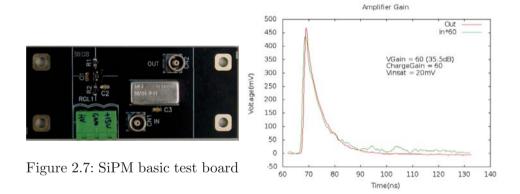

|   | 2.1  | PSpic  | e model                                        | 39 |

|   |      | 2.1.1  | Parameters extraction                          | 41 |

|   |      | 2.1.2  | Measurement setup                              | 42 |

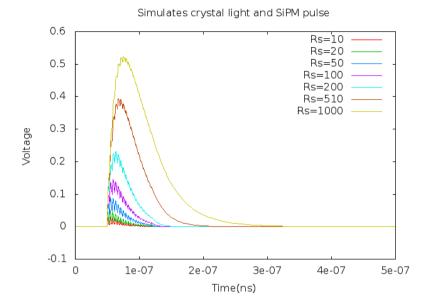

|   |      | 2.1.3  | Simulation results                             | 43 |

|   | 2.2  | Verilo | gA model                                       | 47 |

| 3 | SIP  | M REA  | ADOUT ASICS                                    | 49 |

|   | 3.1  | FLC_S  | SiPM                                           | 50 |

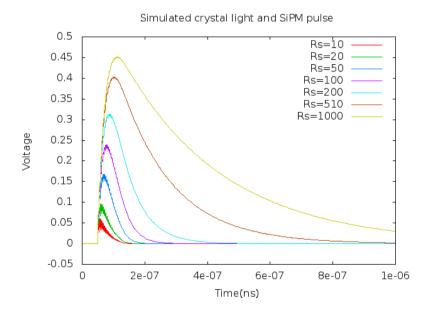

|   | 3.2  | MAR    | OC                                             | 52 |

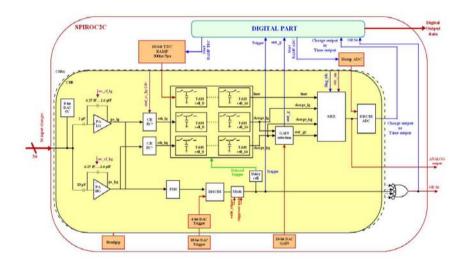

|   | 3.3  | SPIRO  | OC                                             | 54 |

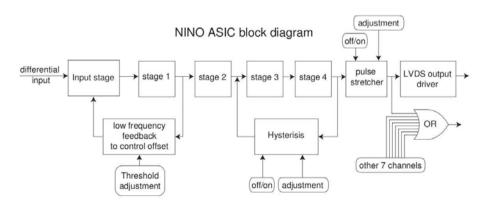

|   | 3.4  | NINO   |                                                | 56 |

|   | 3.5  | PETA   | L                                              | 57 |

|   | 3.6  | BASI   | C                                              | 59 |

|   | 3.7  | VATA   | .64                                            | 60 |

|   | 3.8  | RAPS   | SODI                                           | 62 |

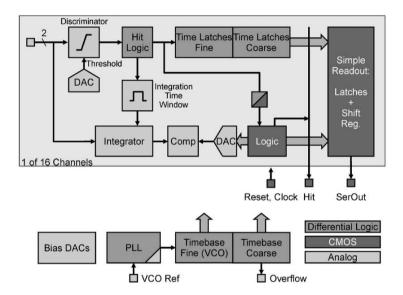

|   | 3.9  | TOFF   | PET                                            | 63 |

|   | 3.10 | Comp   | arison tables                                  | 65 |

| 4 | INP  | UT ST  | AGE                                            | 69 |

|   | 4.1  | Archit | tecture                                        | 70 |

|   | 4.2  | Circui | it analysis                                    | 71 |

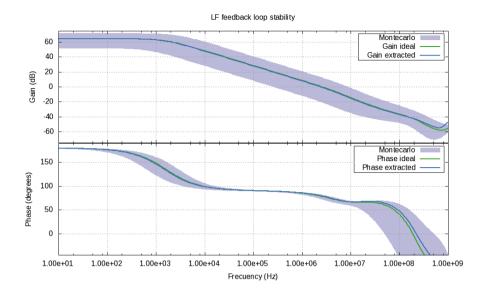

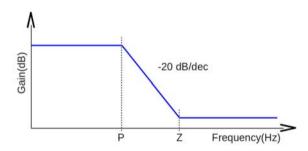

|   |      | 4.2.1  | Low Frequency feedback loop                    | 72 |

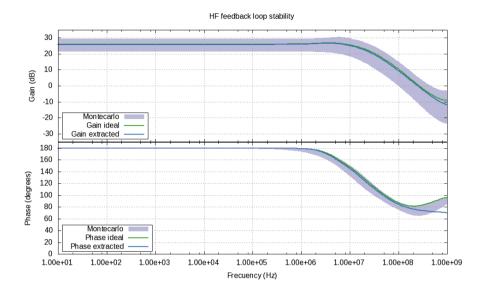

|   |      | 4.2.2  | High Frequency feedback loop                   | 73 |

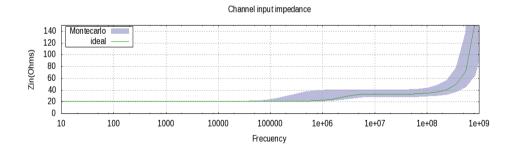

|   |      |        | 4.2.2.1 Input impedance                        | 76 |

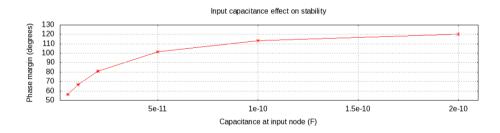

|   |      |        | 4.2.2.2 Input capacitance                      | 77 |

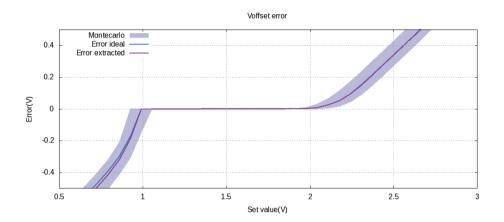

|   |      | 4.2.3  | Input voltage variation                        | 78 |

|   |      | 4.2.4  | Noise                                          | 79 |

| 5 | DES  | SIGN F | OR PET APPLICATIONS                            | 81 |

|   | 5.1  | Requi  | rements                                        | 84 |

|   |      | 5.1.1  | Number of channels                             | 84 |

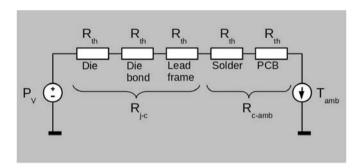

|   |      |        | 5.1.1.1 Packaged electronics power consumption | 85 |

|   |      | 5.1.2  | Rate constraints                               | 86 |

|   |      | 5.1.3  | Bandwidth                                      | 86 |

|   |      | 5.1.4  | Linearity                                      | 87 |

|   |      | 5.1.5  | Specifications summary                         | 87 |

|   | 5.2  | Imple  | mentation                                      | 88 |

|     | 5.2.1  | Architec | ture                                     | 88  |

|-----|--------|----------|------------------------------------------|-----|

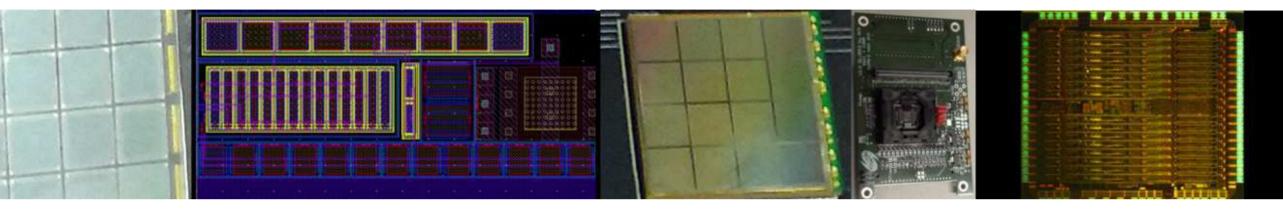

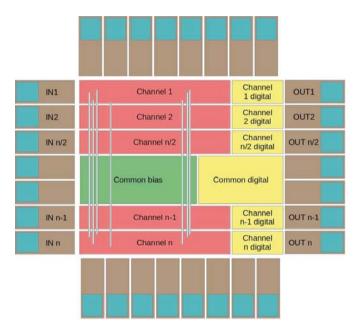

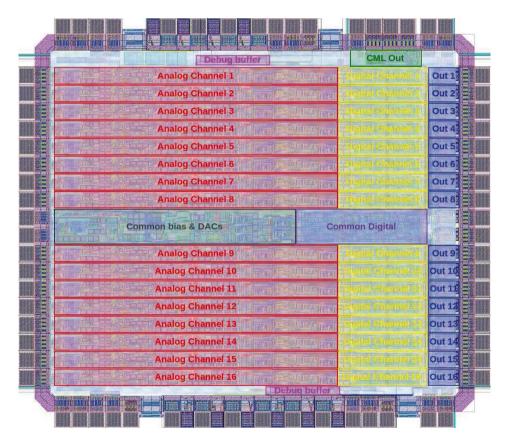

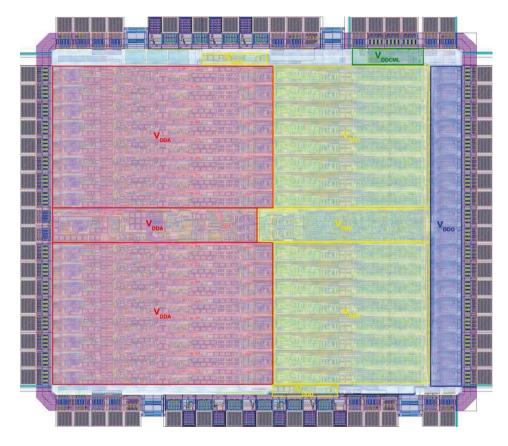

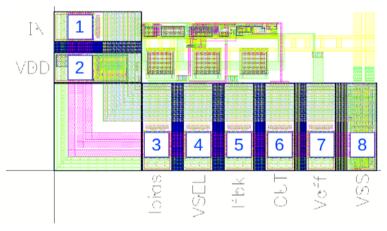

|     |        | 5.2.1.1  | Floorplan                                | 90  |

|     | 5.2.2  | Power    |                                          | 91  |

|     | 5.2.3  | Energy 1 | measurement Blocs                        | 91  |

|     |        | 5.2.3.1  | Linear Time Over Threshold               | 91  |

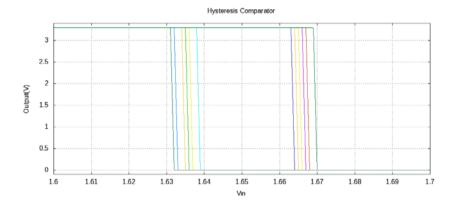

|     |        | 5.2.3.2  | Hysteresis comparator                    | 95  |

|     | 5.2.4  | Time me  | easurement Blocs                         | 97  |

|     |        | 5.2.4.1  | Current discriminator                    | 97  |

|     | 5.2.5  | Pile-up  | detection blocs                          | 98  |

|     | 5.2.6  | Common   | a Blocs and Biasing                      | 99  |

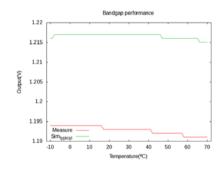

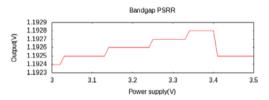

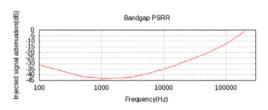

|     |        | 5.2.6.1  | Bandgap references                       | 99  |

|     |        | 5.2.6.2  | DACs                                     | 99  |

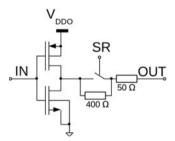

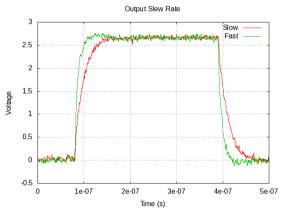

|     |        | 5.2.6.3  | Single Ended CMOS Pad                    | 101 |

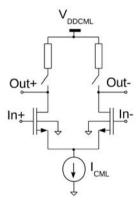

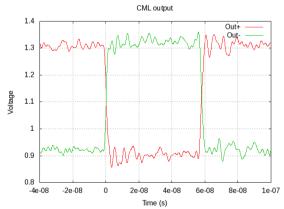

|     |        | 5.2.6.4  | Differential Current Mode Logic Pad      | 102 |

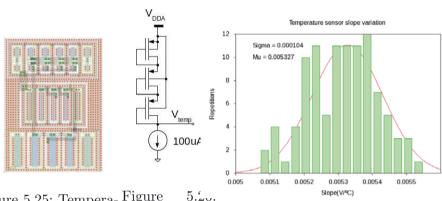

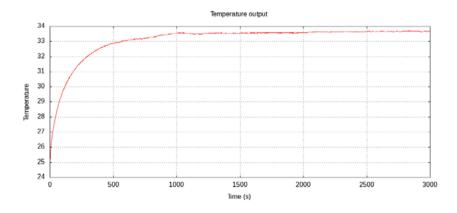

|     |        | 5.2.6.5  | Temperature sensor                       | 103 |

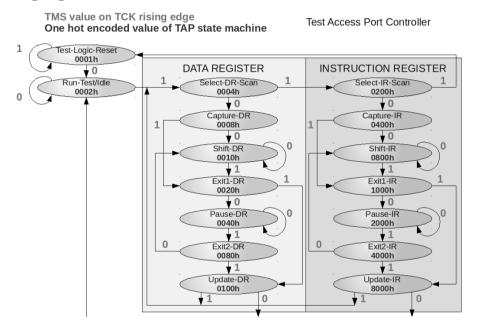

|     |        | 5.2.6.6  | Slow Control                             | 104 |

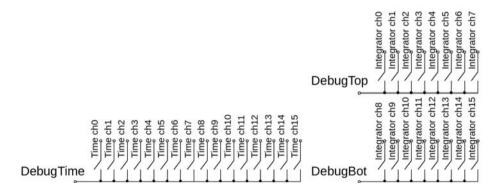

|     |        | 5.2.6.7  | Debug signals                            | 105 |

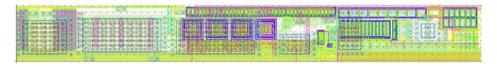

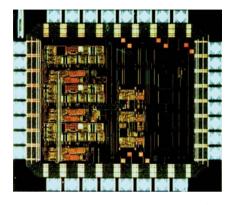

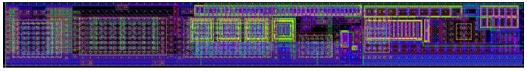

|     | 5.2.7  | Layout   |                                          | 106 |

| 5.3 | Result | S        |                                          | 108 |

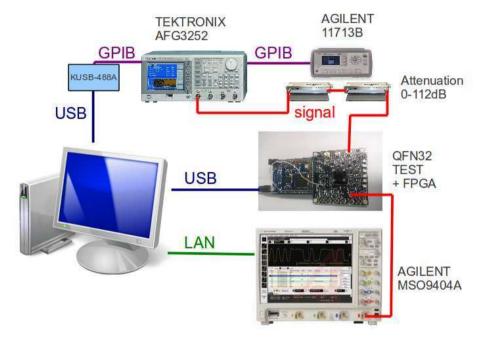

|     | 5.3.1  | Test sys | tem                                      | 108 |

|     | 5.3.2  | Power co | onsumption                               | 109 |

|     | 5.3.3  | Input st | age Bloc                                 | 110 |

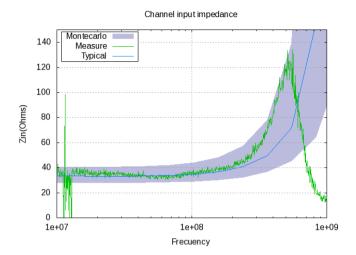

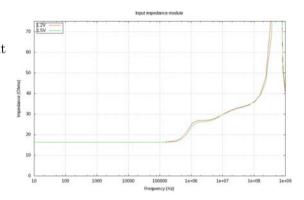

|     |        | 5.3.3.1  | Input Impedance                          | 110 |

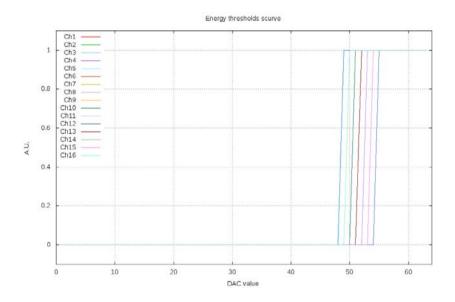

|     | 5.3.4  | Energy 1 | measurement Blocs                        | 112 |

|     |        | 5.3.4.1  | Hysteresis comparator                    | 112 |

|     |        | 5.3.4.2  | Electrical signal injection measurements | 113 |

|     | 5.3.5  | Time me  | easurement Blocs                         | 118 |

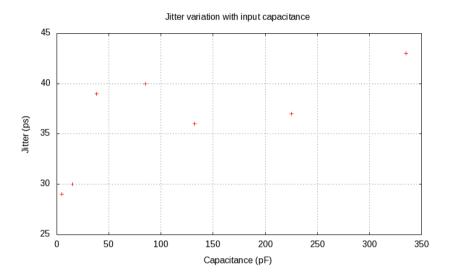

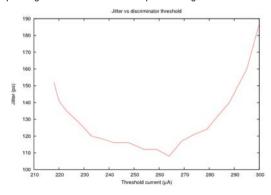

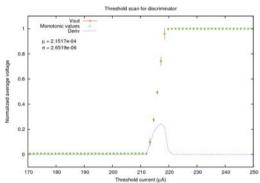

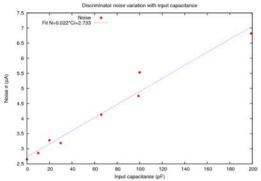

|     |        | 5.3.5.1  | Jitter                                   | 118 |

|     | 5.3.6  | Pile-up  | measurement Blocs                        | 120 |

|     | 5.3.7  | Common   | a Blocs and Biasing                      | 120 |

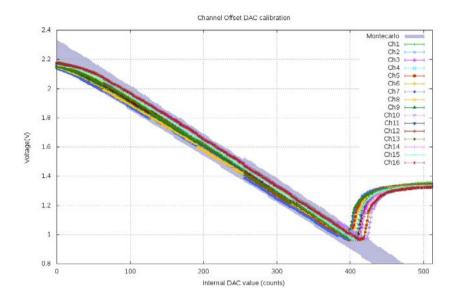

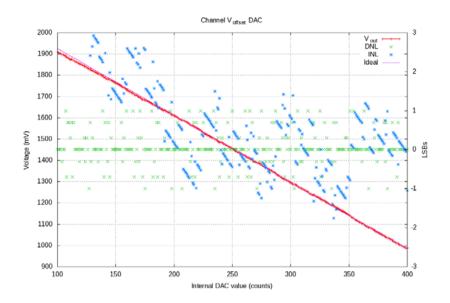

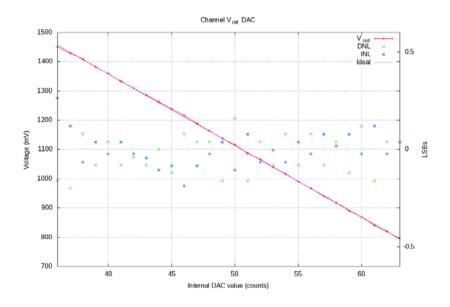

|     |        | 5.3.7.1  | DACs                                     | 120 |

|     |        | 5.3.7.2  | Single Ended CMOS Pad                    | 123 |

|     |        | 5.3.7.3  | Differential Current Mode Logic Pad      | 123 |

|     |        | 5.3.7.4  | Temperature sensor                       | 124 |

|     | 5.3.8  | SiPM m   | easurements                              | 125 |

|     | 5.3.9  | Radioac  | tive sources                             | 125 |

|     | 5.3.10 | Coincide | ence Resolving Time                      | 128 |

|     | 5.3.11 | PET sys  | etem measurements                        | 131 |

| DES | SIGN F | OR SCIE  | TRACKER                                  | 135 |

|   | 6.1  | Front  | End Elec | etronics                    | 138 |

|---|------|--------|----------|-----------------------------|-----|

|   |      | 6.1.1  | Number   | of channels                 | 138 |

|   |      | 6.1.2  | Power of | consumption                 | 139 |

|   |      | 6.1.3  | Timing   | constraints                 | 139 |

|   |      |        | 6.1.3.1  | Double peak resolution      | 139 |

|   |      |        | 6.1.3.2  | Spill over                  | 139 |

|   |      | 6.1.4  | Noise    |                             | 140 |

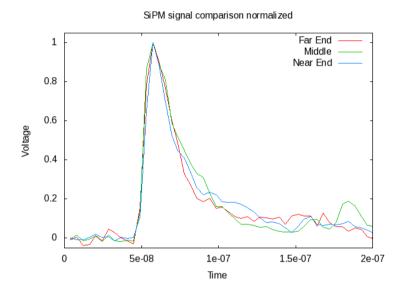

|   |      | 6.1.5  | Signal f | rom SiPM                    | 140 |

|   |      |        | 6.1.5.1  | Dynamic range               | 142 |

|   |      |        | 6.1.5.2  | Propagation delay           | 143 |

|   |      |        | 6.1.5.3  | Mirror                      | 144 |

|   |      | 6.1.6  | Slow co  | ntrol                       | 145 |

|   |      | 6.1.7  | Data lin | nk                          | 145 |

|   |      | 6.1.8  | Specific | ations summary              | 146 |

|   | 6.2  | Imple  | mentatio | n                           | 147 |

|   |      | 6.2.1  | Archite  | cture                       | 147 |

|   |      | 6.2.2  | Preamp   | lifier                      | 148 |

|   |      |        | 6.2.2.1  | Multiple voltages operation | 149 |

|   |      | 6.2.3  | Simulat  | ion results                 | 149 |

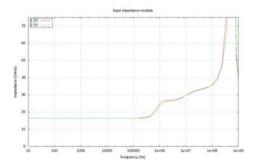

|   |      |        | 6.2.3.1  | Input impedance             | 150 |

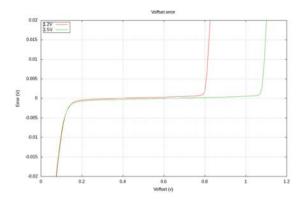

|   |      |        |          | Input voltage variation     | 150 |

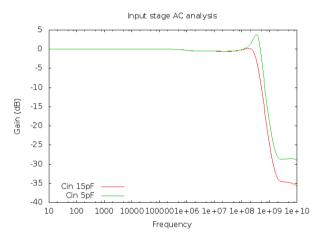

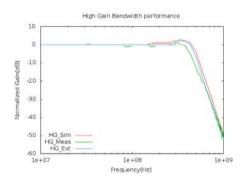

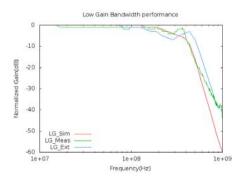

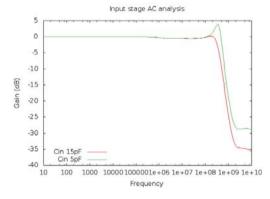

|   |      |        |          | Bandwidth                   | 151 |

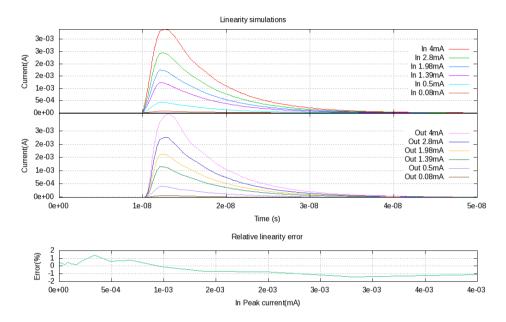

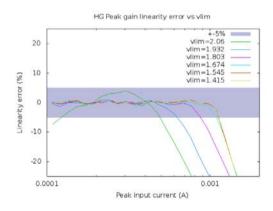

|   |      |        | 6.2.3.4  | Linearity                   | 152 |

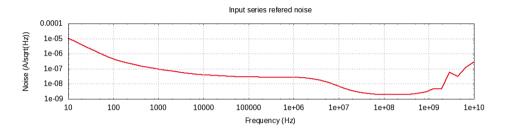

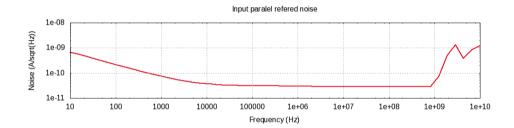

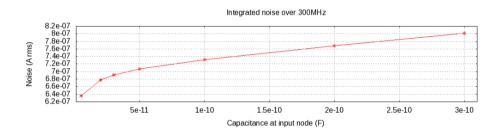

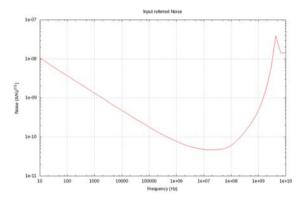

|   |      |        | 6.2.3.5  | Noise                       | 153 |

|   |      | 6.2.4  | Layout   |                             | 153 |

| 7 | COI  | NCLUS  | IONS     |                             | 155 |

|   | 7.1  | Achie  | vements  |                             | 155 |

|   | 7.2  | Outlo  | ok       |                             | 156 |

|   | REF  | EREN   | CES      |                             | 159 |

|   | LIS  | T OF A | CRONY    | MS                          | 165 |

|   | LIST | T OF F | IGURES   |                             | 173 |

|   |      | _      | TABLES   |                             | 175 |

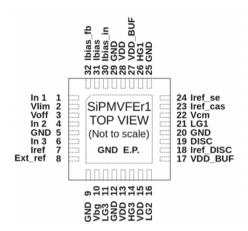

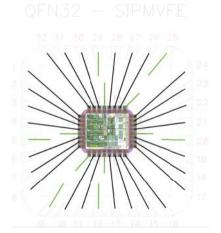

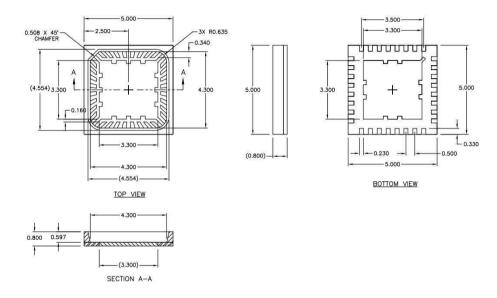

| A | SIP  | MVFEI  | R1 DATA  | SHEET                       | 177 |

| В | PAC  | IFICR: | 1 DATAS  | HEET                        | 191 |

L'objectiu d'aquesta tesi és presentar una solució per a la lectura de matrius de fotomultiplicadors de silici (SiPM) millorant les característiques de sistemes actuals. Amb aquesta finalitat s'ha dissenyat i provat el circuit d'una nova etapa d'entrada. En primer lloc s'ha dissenyat pensant en aplicacions genèriques i per a imatge mèdica, concretament per a escàners PET (Positron Emission Tomography). Però més endavant s'aplica la mateixa topologia per a una aplicació més concreta i específica com és un detector de partícules (l'actualització del Tracker a l'experiment LHCb).

Els SiPM són uns dispositius electrònics relativament nous<sup>[1]</sup> amb la possibilitat de comptar fotons i millorant algunes característiques dels sensors actuals, com serien la tensió d'operació més baixa, més guany o immunitat a camps magnètics, mentre manté unes prestacions excel·lents respecte el guany, resolució temporal i rang dinàmic. Aquest tipus de dispositius es troben en constant evolució encara i una gran varietat de fabricants intenten millorar les prestacions, sobretot respecte la eficiència en la detecció de llum, reduir el corrent d'obscuritat, construir matrius més grans i augmentar l'espectre al qual són sensibles.

En aquest document es presenta el disseny d'un circuit integrat específic amb les següents característiques: gran rang dinàmic, alta velocitat, multicanal, amb entrada en corrent i baixa impedància d'entrada, baix consum, control de la tensió de polarització del SiPM i amb les sortides de; temps, càrrega i apilament.

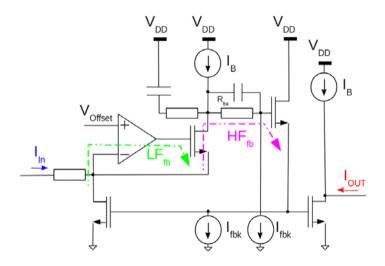

El preamplificador utilitza un circuit nou amb doble realimentació que redueix la impedància d'entrada al mateix temps que manté una polarització fixa en el node d'entrada.

### Fotomultiplicador de Silici (SiPM)

Els fotomultiplicadors de silici són uns dispositius formats per centenars de micro-cel·les en paral·lel. Cada cel·la és un díode d'allau (APD) treballant en mode Geiger, amb una resistència que evita la destrucció del dispositiu. El comportament dels APDs és conegut i estudiat des de principis dels anys  $60^{[7]}$ . Totes les cel·les es combinen en una sola sortida (connectades en paral·lel). El resultat és una sortida molt similar a la produïda

per un Tub Fotomultiplicador convencional (PMT), però amb una senyal discreta (cada cel·la deixa anar una quantitat fixa de càrrega).

De la mateixa manera que els APDs els primers parells de portadors dins el silici es generen mitjançant efecte fotoelèctric i es multipliquen dins del silici. En aquest cas, però la multiplicació és una allau produïda pel fet d'estar per sobre la tensió de trencament del dispositiu. Per evitar un efecte destructiu de l'allau s'incorpora una resistència en serie al dispositiu per baixar la tensió per sota el trencament en el cas d'una allau. El guany resultant és semblant al d'un PMT de l'ordre de  $10^5$  a  $10^7$ .

La probabilitat de detecció de llum d'un SiPM es defineix per la Eficiència de Detecció de Fotons (PDE). Aquesta eficiència es calcula mitjançant els efectes produïts per la zona no utilitzada entre les micro-cel·les (FF) i la eficiència quàntica del dispositiu (QE). El PDE es calcula fàcilment multiplicant els elements anteriors per la probabilitat que un parell electró-forat comenci una allau.

Moltes mesures sobre diferents propietats de diferents fabricants es poden consultar en la literatura<sup>[8]</sup> igual que la descripció de diferents efectes no desitjats dels dispositius<sup>[9]</sup>.

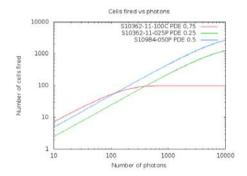

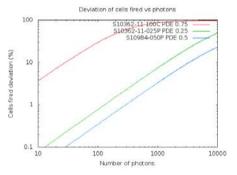

Els SiPM ofereixen una sortida lineal respecte la il·luminació rebuda en un cert rang. La saturació dels SiPM es pot modelitzar mitjançant la equació  $^{[10]}$  1, on m és el nombre total de cel·les del dispositiu i  $\varepsilon$  el PDE.the photon detection efficiency.

$$N_{cel \cdot les disparades} = m * \left(1 - e^{-\frac{N_{fotons} * \mathcal{E}}{m}}\right)$$

(1)

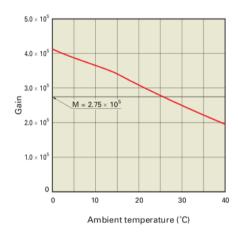

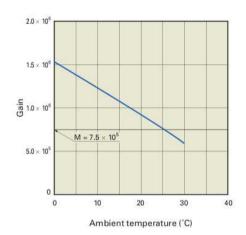

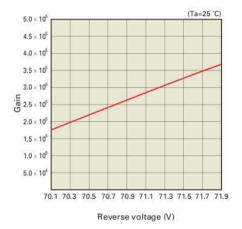

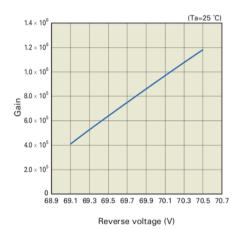

Els fotomultiplicadors de silici tenen una important dependència entre la variació de la tensió de trencament i la temperatura, de manera que també afecten el guany. El coeficient de temperatura depèn del procés de fabricació però és habitual en aquest tipus de dispositius. En el cas que es polaritzin un conjunt de dispositius amb la mateixa tensió caldrà poder variar la tensió en el node de connexió amb la electrònica de lectura per a poder compensar aquestes variacions, de la mateixa manera que també pot variar la tensió de trencament entre diferents dispositius d'una matriu.

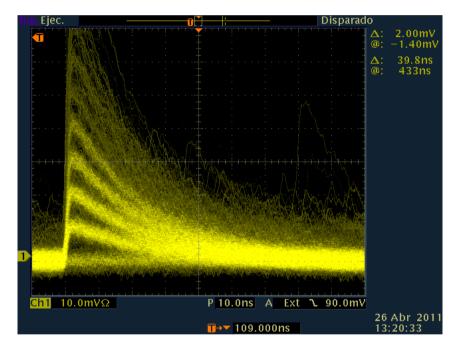

El fenomen anomenat com a After Pulsing és un efecte conegut que consisteix en la generació de senyal de forma espontània després d'un primer pic de senyal. És degut a l'acumulació de càrrega en els defectes del semiconductor. Aquesta càrrega atrapada es pot alliberar més tard. Si la càrrega s'allibera pot generar una nova allau. Els temps típics d'alliberament són des dels pocs ns a centenars de ns. Les primeres càrregues alliberades no afecten la senyal de sortida ja que les cel·les encara no s'han recarregat, però

incrementaran el temps de recuperació del dispositiu. Treballar a baixes temperatures fan aquest alliberament més lent, per tant l'efecte és més evident.

Un dels principals problemes dels SiPM és l'anomenat corrent d'obscuritat. Aquesta corrent es genera de forma espontània per càrregues excitades tèrmicament. Aquestes càrregues poden generar una allau en la cel·la que serà idèntica a una senyal generada per un fotó. El nombre d'allaus per temps dóna un resultat de comptes d'obscuritat (normalment en Hz).

Les principals avantatges i inconvenients dels Fotomultiplicadors de Silici es resumeixen en la taula següent:

| Avantatges                         | Inconvenients             |

|------------------------------------|---------------------------|

| Alta eficiència Quàntica           | Resistència a la radiació |

| Poca sensibilitat al camp magnètic | Baix PDE                  |

| Compacte i resistent               | Comptes d'obscuritat      |

| Baixa tensió (20V - 100V)          |                           |

| Matrius de dispositius             |                           |

Table 1: Avantatges i inconvenients dels Fotomultiplicadors de Silici

### Centellejadors

Un centelleiador és un material que exhibeix emissió de llum (sense escalfar-se) quan s'excita mitjançant radiació ionitzant. Aquesta radiació es composa per partícules que tenen prou energia cinètica individualment per alliberar un electró d'un àtom o molècula, ionitzant. Quan el material rep una partícula absorbeix la energia i la re-emet en forma de llum. Depenent del material, l'estat d'excitació pot ser meta-estable de forma que la relaxació es pot retardar algun temps (des de microsegons a hores). Les primeres utilitzacions de centellejadors es daten a principis del segle 20<sup>[13]</sup> però fins a 1944 no es van utilitzar de forma generalitzada combinant-los amb fotomultiplicadors convencionals (PMTs). En aquests detectors moderns el primer element en el camí de la partícula ionitzant és el cristall centellejador i la converteix a una senval lluminosa. Aquesta llum es converteix a una senyal elèctrica mitjançant un transductor (PMT, APD o SiPM) i llavors es processa. Els cristalls no són ideals i presenten variacions temporals importants en la generació de llum. Una vegada la llum s'ha generat aquesta ha de recórrer el camí fins el transductor que pot incrementar encara més la dispersió temporal, sobretot depenent de les dimensions del  $cristall^{[14]}$ .

Moltes de les propietats desitjades són; gran densitat, alta velocitat, bona linealitat, resistència a la radiació i baix cost. L'alta densitat redueix la necessitat de material per a produir llum de partícules d'alta energia i l'efecte Compton es redueix per partícules de més baixa energia. L'alta velocitat, amb temps de recuperació ràpids, porta a una millor resolució en les mesures i millor identificació del tipus de partícules mesurades, a més de reduir el temps de recuperació. La resistència a la radiació és necessària per mantenir els cristalls en detectors amb un ambient hostil. Finalment el cost també és un factor important ja que els cristalls solen necessitar processos de purificació complicats i terres rares per a la seva fabricació.

Les propietats típiques d'alguns centellejadors inorgànics es resumeixen en la taula 2. Els centellejadors orgànics tenen una densitat molt menor  $(1 \text{ g/cm}^3)$  i menys emissió de llum (al voltant del 50% del NaI(Tl)).

| Material                                                      | Densitat        | Densitat Longitud d'ona Índex de | Índex de  | Temps         | Llum emesa                   |

|---------------------------------------------------------------|-----------------|----------------------------------|-----------|---------------|------------------------------|

| Centellejador                                                 | $({ m g/cm^3})$ | at max.(nm)                      | refracció | relaxació(ns) | $(\mathrm{ph}/\mathrm{MeV})$ |

| NaI(Tl)                                                       | 3.67            | 415                              | 1.85      | 230           | 38000                        |

| CsI(Tl)                                                       | 4.51            | 540                              | 1.80      | 680,3340      | 40000,25000                  |

| $\mathbf{Bi}_{4}\mathbf{Ge}_{3}\mathbf{O}_{12}$               | 7.13            | 480                              | 2.15      | 300           | 8200                         |

| $\mathbf{BaF}_2$                                              | 4.89            | 220,310                          | 1.56      | 0.6,630       | 1500,9500                    |

| $\mathbf{CeF}_3$                                              | 6.16            | 310,340                          | 1.68      | 5,27          | 4400                         |

| $\rm YAlO_3(Ce)$                                              | 5.37            | 370                              | 1.95      | 27            | 18000                        |

| $\mathbf{Lu}_2\mathbf{SiO}_5(\mathbf{Ce})$                    | 7.4             | 420                              | 1.82      | 47            | 25000                        |

| $\mathbf{LaBr}_3(\mathbf{Ce})$                                | 3.79            | 350                              | 1.9       | 27            | 49000                        |

| BC-400                                                        | 1.03            | 420                              | 1.58      | 2.4           | 10000                        |

| BGO:                                                          |                 |                                  |           |               |                              |

| $\mathbf{Bi_4}(\mathbf{GeO_4})_3\\ \mathbf{LSO:}$             | 7.13            | 480                              | 2.15      | 300           | 2700                         |

| $ m Lu_2(SiO_4)O:Ce \ GSO:$                                   | 7.4             | 420                              | 1.82      | 42            | 28500                        |

| $\mathrm{Gd}_2(\mathrm{SiO}_4)\mathrm{O:Ce} \ \mathrm{LYSO:}$ | 6.71            | 440                              | 1.85      | 09            | 0092                         |

| $\mathbf{Lu}_{1.8}\mathbf{Y}_{0.2}(\mathbf{SiO}_4)0$ :Ce      | 7.1             | 420                              | 1.81      | 40            | 40000                        |

Table 2: Propietats de centellejadors inorgànics

### **Aplicacions dels SiPMs**

Els fotomultiplicadors de silicis es poden utilitzar en qualsevol aplicació on es necessiti la mesura de senyals febles de llum. Les aplicacions més habituals són; l'ús en la detecció de rajos gamma emesos per un isòtop introduït en el cos per detectar l'acumulació en diferents àrees (com per exemple en la tomografia d'emissió de positrons, PET) o els detectors de partícules d'altes energies per a usos comercials o d'investigació en les seves variants (com per exemple la construcció de calorímetres a l'LHC).

### Tomografia d'Emissió de Positrons, PET

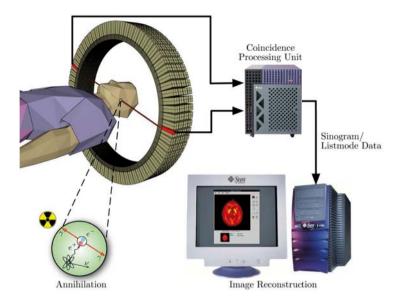

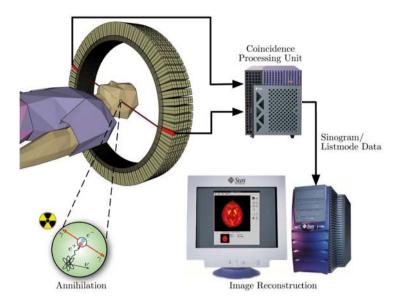

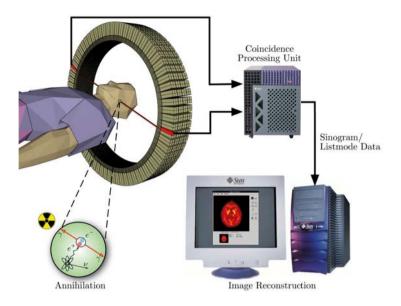

La Tomografia d'Emissió de Positrons (PET) és una tècnica d'imatge mèdica que produeix imatges en tres dimensions dels processos funcionals del cos. Els sistemes PET es basen en la detecció de parells de rajos gamma emesos indirectament per un isòtop introduït en el cos. Les dades produïdes per la concentració de parells de rajos gamma i el seu temps d'arribada s'utilitzen per a construir imatges en tres dimensions de l'activitat dins del cos. Els aparells actuals utilitzen sistemes combinats de raigs X però seria desitjable substituir-los per ressonància magnètica ja que no augmenten la radiació a la que s'exposa el pacient i millora el contrast en els teixits tous. En la figura 1 es pot veure a nivell esquemàtic un sistema PET.

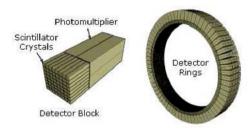

El bloc de detecció normalment està format per cristalls centellejadors (que converteixen el raig gamma a llum) seguits per tubs fotomultiplicadors (convertint la senyal de llum en una corrent elèctrica) i la electrònica de processat (amb amplificació i mesura del temps i de la senyal d'entrada). La resolució espacial final depèn de la mida dels cristalls i de la precisió del sistema global.

La combinació de sistemes PET amb raigs X o MRI donant mesures anatòmiques i metabòliques en el mateix aparell és molt útil ja que el pacient no es mou entre mesures. Això és més important en estructures amb variacions anatòmiques o en òrgans que es puguin moure.

Les dades generades per l'escàner són una llista d'esdeveniments en coincidència representant deteccions gairebé simultànies dels fotons aniquilats (en detectors situats a 180°). Cada coincidència representa una línia en l'espai connectant els dos detectors. Normalment és necessari molt processat per a generar les imatges finals.

Els sistemes PET només accepten esdeveniments vàlids al voltant de la finestra d'energia produïda per un raig gamma, 511keV. Si un esdeveniment es troba en aquesta finestra i amb coincidència amb un detector situat a

Figure 1: Esquema d'un sistema PET

l'altre costat l'esdeveniment s'accepta. Tota la resta es descarta. Per evitar l'acumulació de dades és important prendre aquestes decisions el més ràpidament possible en el detector.

Alguns cristalls tenen una emissió espontània de llum, emetent un espectre en la regió d'interès. Com a exemple Saint Gobain produeix el PRelude  $420^{[24]}$ , un centellejador basat en un isòtop del Luteci generant 3 raigs gamma en cascada de 307, 202 i 88 keV, essent el més probable una energia de 597keV.

### Temps de Vol

El Temps de Vol (ToF) és un mètode utilitzat per a mesurar el temps que triga una partícula per a recórrer una certa distància. Aquesta mesura s'utilitza per a determinar alguna propietat del medi de propagació o per a conèixer alguna propietat de la partícula. La partícula es pot detectar directa o indirectament. En sistemes PET els esdeveniments d'interès es detecten fàcilment mitjançant la coincidència. És una mesura indirecta ja que la partícula genera una senyal lluminosa en el centellejador i llavors aquesta senyal es converteix a corrent i és processada. La mesura de temps en els dos costats dels detectors ajuda a millorar la resolució sobre la posició on s'ha produït l'esdeveniment.

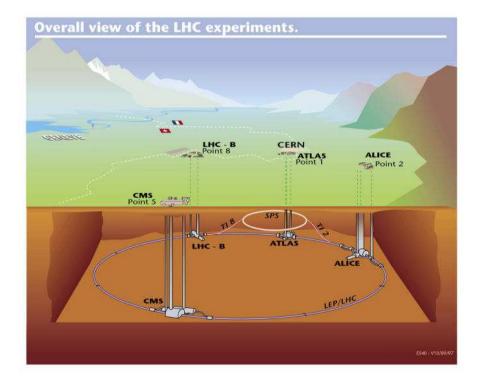

### **CERN i LHC**

El Centre Europeu per la Recerca Nuclear o Conseil Européen pour la Recherche Nucléaire (CERN) es va fundar el 1954 amb la intenció d'esdevenir una institució líder en el món en aquest camp de recerca. Es va construir en la frontera Suïssa i Francesa, a prop de Ginebra. Els seus edificis s'estenen al llarg dels dos costats de la frontera, de la mateixa manera que el túnel on hi ha l'accelerador més potent creat fins al moment, el Gran Col·lisionador d'Hadrons (LHC). Durant la seva història ha tingut diferents acceleradors i experiments donant lloc a diferents descobriments i premis. Avui en dia 20 països formen part dels membres d'aquesta col·laboració internacional. L'LHC és un col·lisionador protó-protó situat en un anell de 27km construït sota el terra.

### **LHCb**

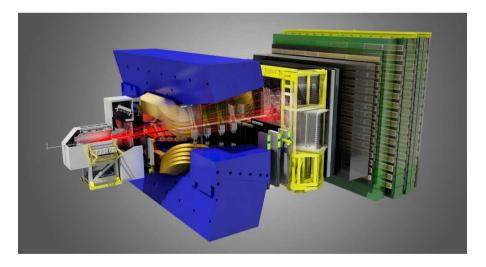

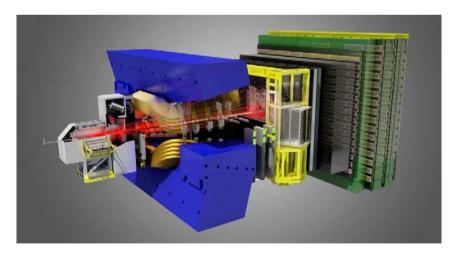

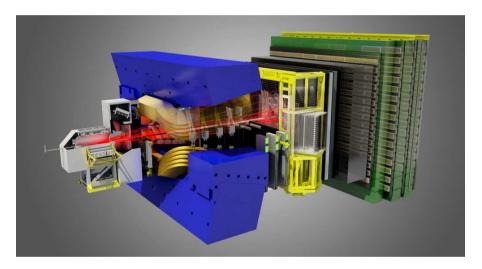

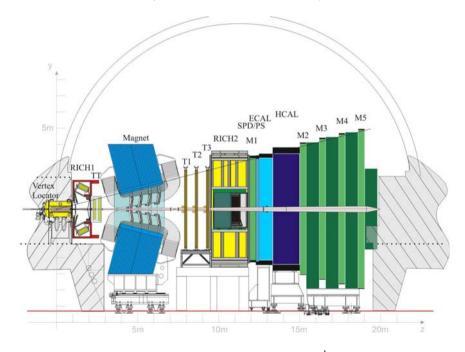

L'experiment Large Hadron Collider beauty (LHCb) és un dels experiments actuals al CERN (Ginebra). En la figura 2 es mostra el detector. LHCb és un espectròmetre amb un angle de cobertura aproximat de 15 a 300 mrad en el pla horitzontal i de 15 a 240 mrad en el pla vertical. Aquesta geometria està motivada pel fet que els parells de partícules bb produïts a LHC es produeixen majoritàriament en una direcció única.

Figure 2: LHCb detector $^a$

<sup>&</sup>lt;sup>a</sup>Imatge proporcionada per la col·laboració LHCb

Començant des del punt d'interacció, a l'esquerra de la figura, el detector consisteix en un sensor de tracking construït amb tires de silici envoltant la zona d'interacció (el detector de Vèrtex). Tot seguit hi ha un imant que genera un camp aproximat de 4Tm i que corba la trajectòria de les partícules. Tot seguit els RICH (Ring Imaging Cherenkov) que identifiquen partícules carregades distingint pions i kaons. Després d'aquest punt els detectors són grans telons verticals que defineixen diferents plans paral·lels de mesura. Un detector de silici cobrint una gran àrea (el trigger tracker, TT) en combinació amb un detector gasós (el Inner Tracker, IT, i Outer Traker, OT). Detectors de muons i finalment calorímetres (Hadrònic i Eelctromagnètic) per a mesurar l'energia de les partícules.

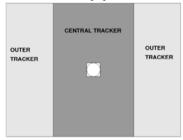

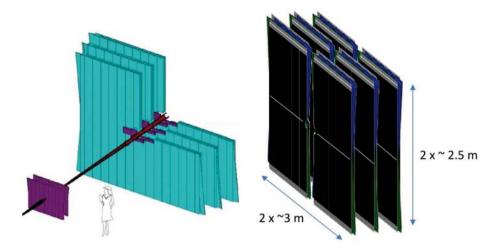

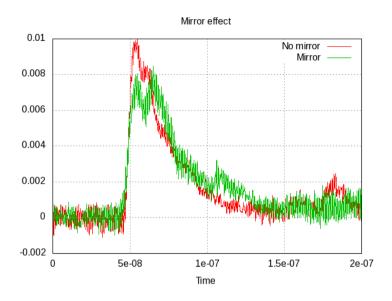

### SciFi Tracker

El tracker actual de LHCb està format pel detector gasós de l'OT i el detector de tires de silici de l'IT per cobrir la zona amb més ocupància al voltant de la canonada amb el feix de partícules. Per a l'actualització del detector s'ha escollit una nova tecnologia basada en fibres centellejadores<sup>[6]</sup>, amb fibres clares generant i transportant la senyal. La zona central es reemplaçarà per fibres centellejadores cobrint tota l'alçada del detector. Contindrà fibres de 2.5m separades per miralls en el punt mig i llegides per fotomultiplicadors de silici muntats als extrems.

Amb aquesta configuració el material es redueix al mínim. Un dels problemes principals és determinar les prestacions dels fotomultiplicadors de silici en radiació. Alguns estudis s'han realitzat mitjançant una font radioactiva de PuBe<sup>[6]</sup>, i s'han deixat mostres en el detector d'LHCb durant 2011.

Les tècniques per la producció de les matrius de SiPM encara es troben en desenvolupament. I s'han fabricat alguns prototips amb característiques adequades.

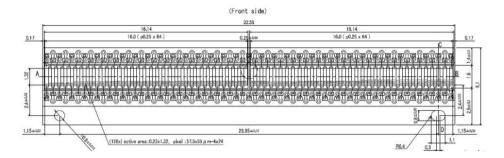

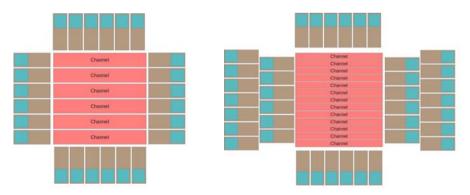

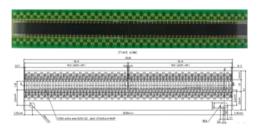

Una matriu de SiPMs a mida s'està desenvolupant per encaixar en la mida del mòdul evitant zona morta. Els prototips de Hamamatsu i Ketek consisteixen en matrius de 64 canals amb el càtode comú. Amb una àrea total de  $0.23 \times 1.32 \, \mathrm{mm}^2$  per canal, 96 micro-cel·les i una mida de  $57.5 \times 55 \, \mu \mathrm{m}^2$  per micro-cel·la. Els 128 canals es fabriquen unint dues oblees amb 64 canals amb un costat polit de forma que es redueix al mínim la distància entre les oblees.

### Model dels SiPM

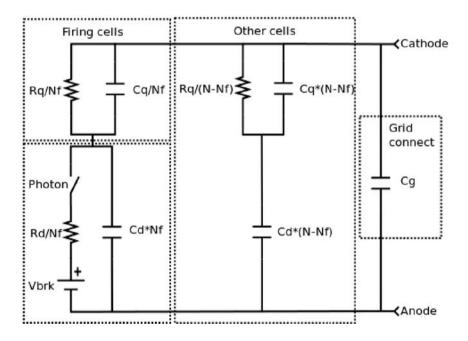

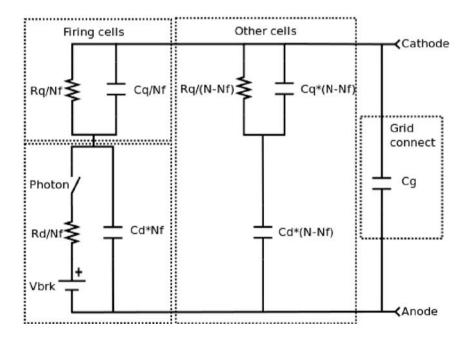

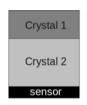

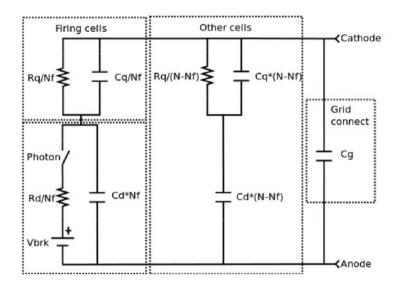

La utilització d'un model fiable és imprescindible per produir senyals fidels a la realitat al dissenyar la electrònica. Un model simple<sup>[26]</sup> s'ha implementat i utilitzat mitjançant eines SPICE. L'esquema del model es pot observar en la figura 3 amb els paràmetres corresponents en la taula 3.

En aquest model <sup>[26]</sup> les diferents cel·les es modelitzen com elements passius amb la diferència que les cel·les disparades tenen alguns elements més que la resta, que actuen com a càrrega.

Figure 3: Esquema del model

Degut a que la base d'una micro-cel·la és un díode amb una resistència de quenching per evitar la seva destrucció, el model incorpora una capacitat paràsita en paral·lel al díode, una font de voltatge i una resistència en sèrie. El díode començarà a conduir quan la font tingui un valor superior a la tensió de trencament i l'interruptor ideal es tanqui (simulant l'arribada de llum). Altres elements com la capacitat paràsita de connexió o la inductància paràsita dels pins es pot afegir al model en sèrie a la connexió.

| Paràmetre              | Descripció                    |

|------------------------|-------------------------------|

| $\mathbf{R}\mathbf{q}$ | Resistència Quenching         |

| $\mathbf{C}\mathbf{q}$ | Capacitat paràsita Rq         |

| ${f N}$                | $\text{Cel} \cdot \text{les}$ |

| $\mathbf{N}\mathbf{f}$ | Cel·les disparades            |

| $\mathbf{Cd}$          | Capacitat del Díode           |

| $\operatorname{Rd}$    | Resistència del Díode         |

| ${f Vbrk}$             | Tensió trencament             |

| $\mathbf{C}\mathbf{g}$ | Capacitat de connexió         |

Table 3: Paràmetres del model

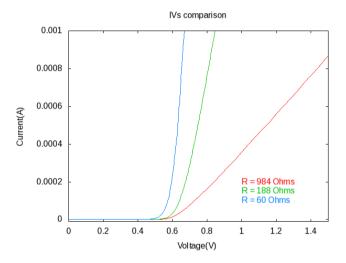

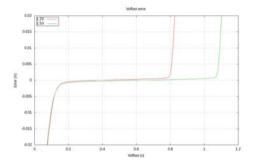

Per determinar la resistència de quenching el més fàcil és mesurar la corba IV del dispositiu. Quan es posi a conduir, la pendent de la corrent serà la resistència del dispositiu dividit pel número de dispositius en paral·lel.

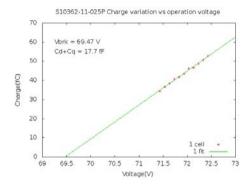

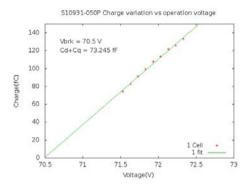

Per a determinar la suma de  $C_d$  i  $C_q$  es pot utilitzar la variació de càrrega generada per una sola cel·la en diferents tensions d'operació  $V_{op}$  [26]. D'aquesta manera també es pot estimar la tensió de trencament  $V_{brk}$  extrapolant el voltatge per una càrrega igual a zero.

Finalment el nombre de cel·les (N) i la capacitat dels terminals s'especifiquen al datahseet del dispositiu.

L'únic paràmetre no definit ni mesurable directament és la  $R_d$  però serà de l'ordre de centenars d'Ohms, sense afectar la forma de la senyal.

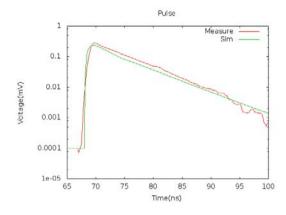

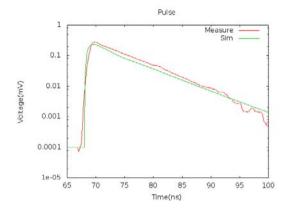

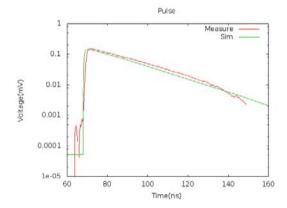

### Resultats de les simulacions

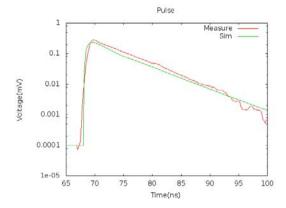

Utilitzant la forma del pic d'obscuritat i la seva amplitud, podem comparar la senyal amb les simulacions. Els paràmetres utilitzats es resumeixen en la taula 5. En la figura 4 hi ha la comparació entre una senyal simulada i la mesura corresponent.

| Paràmetre              | Valor                  |

|------------------------|------------------------|

| Rq                     | $300 \mathrm{k}\Omega$ |

| $\mathbf{C}\mathbf{q}$ | 5.7 fF                 |

| ${f N}$                | 1600                   |

| $\mathbf{Cd}$          | 12 fF                  |

| $\operatorname{Rd}$    | $1 \mathrm{k} \Omega$  |

| $\mathbf{C}\mathbf{g}$ | 15.8 pF                |

| $\mathbf{V}_{brk}$     | 69.47V                 |

Figure 5: S10362-11-025P paràmetres

Figure 4: Simulació d'una cel·la i mesura

### ASICs de lectura de SiPMs

Un resum de diferents opcions per a la lectura de fotomultiplicadors de silici formen aquesta secció, amb una descripció de les diferents arquitectures. És important tenir en compte que probablement no tots els desenvolupaments hi estaran recollits degut a la gran quantitat d'opcions. L'objectiu és obtenir una visió global de l'estat de l'art en el desenvolupament de circuits integrats per a la lectura de fotomultiplicadors de silici.

Les implementacions típiques de pre-amplificadors es basen en Amplificadors Sensibles a la Càrrega (CSA) o en etapes d'entrada en mode corrent. Cadascun d'ells té les seves avantatges i inconvenients. L'amplificador de càrrega o tensió permet una connexió del sensor tant en l'ànode com el càtode i normalment es troba amb un acoblament en alterna per poder variar el valor en contínua del node d'entrada. Les implementacions en mode corrent només permeten la connexió en un dels dos terminals (la direcció de la corrent ha de ser la correcta) i solen oferir millors característiques de velocitat.

Degut als diferents anys de fabricació i en diferents tecnologies els prototips no es poden comparar directament pel que fa el consum i l'àrea. Però per tenir una primera aproximació de com s'han realitzat les implementacions pot ser un valor interessant.

### Taules comparatives

Per tal de comparar algunes característiques de diferents ASICs els elements més interessants es resumeixen en les tables següents, 4 i 5. En la primera hi ha un resum de les sortides, tipus de sortides, magnitud mesurada, resolució i informació temporal. A la segona es resumeix el tipus d'etapa d'entrada, potència, àrea i tecnologia.

L'aproximació habitual és donar càrrega i informació temporal (realitzant una OR de diferents canals). Normalment aquesta mesura doble es realitza dividint en dos la senyal a la sortida del pre-amplificador, dividint-se en dos camins de senyal amb diferent processat. Es realitzen prototips amb molts canals degut als sistemes en els quals han d'anar instal·lats.

A les taules es pot veure que la lectura més popular és en càrrega. Sovint aplicant algun circuit per canviar la forma en el pre-amplificador. Aquests tipus de circuits s'utilitzen sovint en detectors de partícules, però no aprofiten les possibilitats temporals del sensor. Per altra banda la lectura en corrent s'utilitza menys i habitualment connectat al càtode.

Les implementacions diferencials no s'utilitzen massa degut a que el sensor és unipolar i normalment el consum se'n ressenteix i complica la connexió.

| $\mathbf{ASIC}$  | Sortides                       | ${ m Measura}$  | ${ m Resoluci}$    | Resolució Sortida Temporal |

|------------------|--------------------------------|-----------------|--------------------|----------------------------|

| $FLC\_SIPM$      | Multiplexat analògic           | Càrrega         | ı                  | No                         |

| MAROC3           | Multiplexat analògic i digital | Càrrega         | Fins 12 bits       | 64 + 20R                   |

| ${ m SPIROC2c}$  | Digital temps i càrrega        | Temps i Càrrega | 12  bits i  150 ps | Paraula digital            |

| ONIN             | Digital                        | Temps i amplada | sd09               | LVDS                       |

| $\mathbf{PETA}$  | Digital                        | Temps i energia | 28ps rms           | Paraula digital            |

| $\mathbf{BASIC}$ | Digital i analògic mux.        | Temps i energia | 8000               | OR temps                   |

| VATA64           | Multiplexat analògic i digital | Temps i càrrega | ı                  | Temps i analògic           |

| RAPSODI          | Digital                        | Temps i càrrega | ı                  | Temps                      |

| $	ext{TOFPET}$   | Digital                        | Temps i càrrega | $50 \mathrm{ps}$   | Paraula digital            |

Table 4: Sortides dels ASICs

| $\begin{array}{c cc} (\mathbf{mm}^2/\mathbf{ch}) & \mathbf{mW/ch} \\ 0.56 & 11 & \\ 0.25 & 2.5 & \\ 0.89 & \approx 2.5 & \\ 1 & 40 & \\ 0.66 & 86 & \\ 0.88 & > 2.65 & \\ 1 & 15 & \\ 4.5 & 100 & \\ 0.39 & 7 & \\ \end{array}$                                                                                                                                                                                                                                                                                                                                         | $\mathbf{ASIC}$  | $\operatorname{Tipus}$   | $\operatorname{Tecnologia}$           | Impedància           | Canals   |      | Potència      | $\mathbf{Any}$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|---------------------------------------|----------------------|----------|------|---------------|----------------|

| Càrrega $0.8 \mu \text{m}$ AMS         AC         18 $0.56$ 11           Corrent $0.35 \mu \text{m}$ SiGe AMS $\approx 50\Omega$ $64$ $0.25$ $2.5$ Carrega $0.35 \mu \text{m}$ SiGe AMS         AC $36$ $0.89$ $\approx 2.5$ Diff- Càrrega $0.25 \mu \text{m}$ IBM $\approx 20\Omega$ $8$ $1$ $40$ Diff-rencial $0.18 \mu \text{m}$ UMC $ 16$ $0.66$ $86$ Corrent $0.35 \mu \text{m}$ SiGe AMS $\approx 17\Omega$ $8$ $0.88$ $> 2.65$ Corrent $0.35 \mu \text{m}$ SiGe AMS $\approx 20\Omega$ $2$ $4.5$ $100$ Corrent $0.13 \mu \text{m}$ $10-60\Omega$ $64$ $0.39$ $7$ |                  | entrada                  |                                       |                      |          | _    | ${ m mW/ch}$  |                |

| Corrent $0.35 \mu m$ SiGe AMS $\approx 50 \Omega$ $64$ $0.25$ $2.5$ Carrega $0.35 \mu m$ SiGe AMS       AC $36$ $0.89$ $\approx 2.5$ Dif. Carrega $0.25 \mu m$ IBM $\approx 20 \Omega$ $8$ $1$ $40$ Diferencial $0.18 \mu m$ UMC       - $16$ $0.66$ $86$ Corrent $0.35 \mu m$ SiGe AMS $\approx 17 \Omega$ $8$ $0.88$ $> 2.65$ Corrent $0.35 \mu m$ SiGe AMS $\approx 20 \Omega$ $2$ $4.5$ $100$ Corrent $0.13 \mu m$ $10.60 \Omega$ $64$ $0.39$ $7$                                                                                                                   | $FLC_SIPM$       | Càrrega                  | $0.8 \mu \mathrm{m} \ \mathrm{AMS}$   | AC                   | 18       | 0.56 | 11            | 2004           |

| Càrrega       0.35 $\mu$ m SiGe AMS       AC       36       0.89 $\approx 2.5$ Dif. Càrrega       0.25 $\mu$ m IBM $\approx 20\Omega$ 8       1       40         Diferencial       0.18 $\mu$ m UMC       -       16       0.66       86         Corrent       0.35 $\mu$ m SiGe AMS $\approx 17\Omega$ 8       0.88       >2.65         Corrent       -       AC       64       1       15         Corrent       0.35 $\mu$ m SiGe AMS $\approx 20\Omega$ 2       4.5       100         Corrent       0.13 $\mu$ m       10-60 $\Omega$ 64       0.39       7          | MAROC3           | Corrent                  | $0.35\mu\mathrm{m}$ SiGe AMS          | pprox 200            | 64       | 0.25 | 2.5           | 2009           |

| Dif. Càrrega       0.25 $\mu$ m IBM       \$\approx 20\Omega       8       1       40         Diferencial       0.18 $\mu$ m UMC       -       16       0.66       86         Corrent       0.35 $\mu$ m SiGe AMS       \$\approx 17\Omega       8       0.88       >2.65         Corrent       -       AC       64       1       15         Corrent       0.35 $\mu$ m SiGe AMS       \$\approx 20\Omega       2       4.5       100         Corrent       0.13 $\mu$ m       10-60 $\Omega$ 64       0.39       7                                                     | ${ m SPIROC2c}$  | $\operatorname{Carrega}$ | $0.35\mu\mathrm{m}$ SiGe AMS          | AC                   | 36       | 0.89 | $\approx 2.5$ | 2012           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ONIN             | Dif. Carrega             | $0.25 \mu \mathrm{m} \; \mathrm{IBM}$ | pprox 200            | $\infty$ | 1    | 40            | 2003           |

| Corrent $0.35\mu m$ SiGe AMS $\approx 17\Omega$ 8 $0.88$ $>2.65$ Corrent       -       AC $64$ 1 $15$ Corrent $0.35\mu m$ SiGe AMS $\approx 20\Omega$ 2 $4.5$ $100$ Corrent $0.13\mu m$ $10-60\Omega$ $64$ $0.39$ $7$                                                                                                                                                                                                                                                                                                                                                   | $\mathbf{PETA}$  | Diferencial              | $0.18 \mu \mathrm{m} \; \mathrm{UMC}$ | ı                    | 16       | 0.66 | 98            | 2008           |

| Corrent - AC 64 1 15<br>Corrent 0.35 $\mu$ m SiGe AMS $\approx 20\Omega$ 2 4.5 100<br>Corrent 0.13 $\mu$ m 10-60 $\Omega$ 64 0.39 7                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\mathbf{BASIC}$ | Corrent                  | $0.35\mu\mathrm{m}$ SiGe AMS          | $pprox 17\Omega$     | $\infty$ | 0.88 | > 2.65        | 2008           |

| Corrent 0.35 $\mu$ m SiGe AMS $\approx 20\Omega$ 2 4.5 100<br>Corrent 0.13 $\mu$ m 10-60 $\Omega$ 64 0.39 7                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VATA64           | Corrent                  | 1                                     | AC                   | 64       | П    | 15            | 2007           |

| Corrent $0.13\mu m$ $10-60\Omega$ $64$ $0.39$ $7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RAPSODI          | Corrent                  | $0.35\mu\mathrm{m}$ SiGe AMS          | pprox 200            | 2        | 4.5  | 100           | 2008           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TOFPET           | Corrent                  | $0.13 \mu \mathrm{m}$                 | $10\text{-}60\Omega$ | 64       | 0.39 | 7             | 2012           |

Table 5: Propietats dels ASICs

### Disseny per PET

Els objectius principals per a un disseny multicanal que millori els sistemes actuals i utilitzable en sistemes PET es resumeix en els següents punts;

- Ample de Banda  $\approx 250 \mathrm{MHz}$

- Connexió directa al SiPM

- Valor de tensió DC controlable al SiPM

- Baixa impedància d'entrada

- OR ràpida entre tots els canals per a mesura temporal

- Mesura d'energia mitjançant una senyal digital del tipus Temps sobre un llindar (ToT)

- Minimitzar consum

- Bona linealitat

### **Arquitectura**

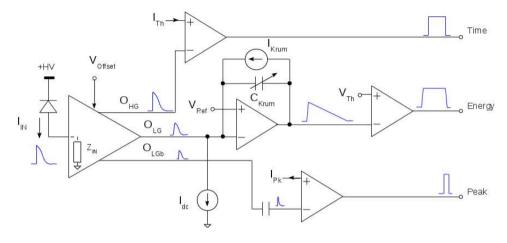

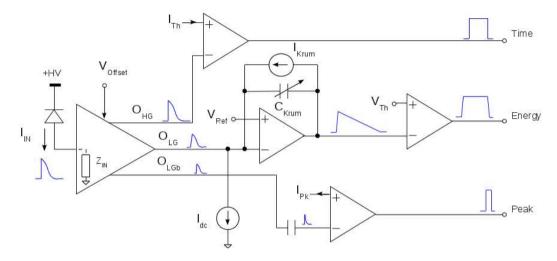

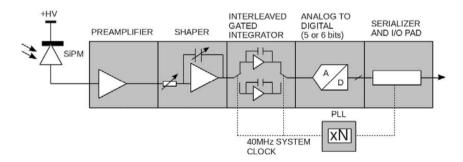

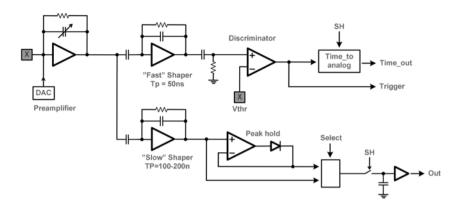

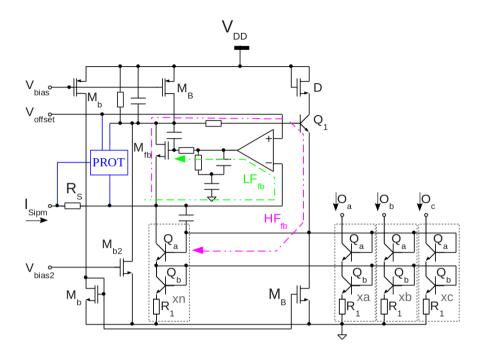

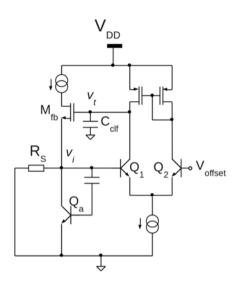

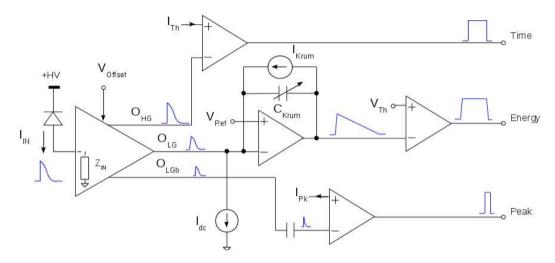

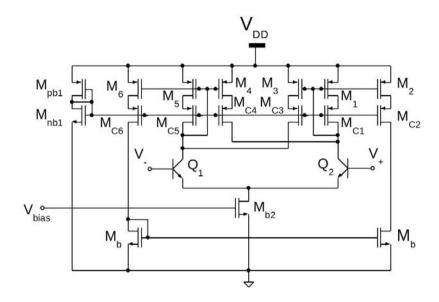

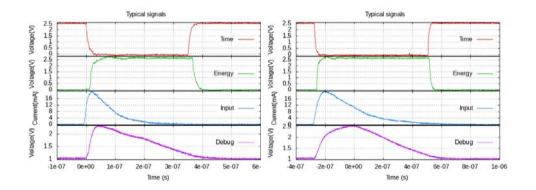

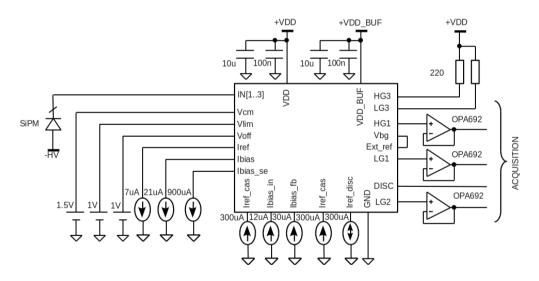

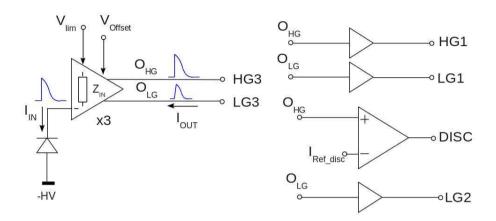

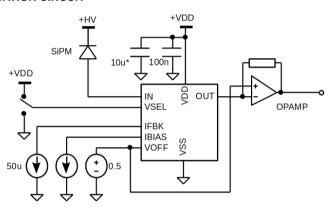

En la figura 6 es mostra un diagrama de blocs del canal analògic implementat. Després d'analitzar els ASICs anteriors sembla que la millor solució per la mesura és una etapa d'entrada en corrent. La etapa implementada permet controlar el valor en contínua del node d'entrada i generar còpies de la senyal d'entrada. En aquest cas es generen tres còpies que s'utilitzen per a tres mesures; temps, energia i apilament.

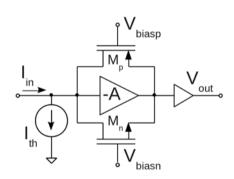

Per la mesura temporal l'habitual és utilitzar un dels camins de senyal i comparar directament amb un llindar per detectar un flanc. Aquest procediment dóna prou bons resultats. Altres processats són molt més complexos i milloren la resolució lleugerament [40]. Per evitar la complexitat s'ha escollit un comparador ràpid en corrent per aquesta aplicació.

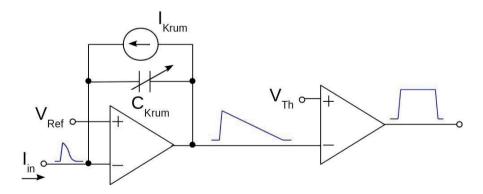

Per la mesura d'energia s'ha escollit una sortida digital degut a la seva flexibilitat en la lectura i els pocs recursos necessaris en l'ASIC (no cal ADC). Un integrador amb una corrent de descàrrega constant genera una senyal que va a un comparador amb histeresis. Utilitzant aquest circuit s'obté una sortida amb una amplada lineal respecte el pic de corrent d'entrada. D'aquesta manera s'eviten correccions a posteriori.

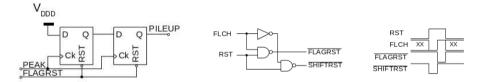

Per la mesura d'apilament simplement s'utilitza una altra branca amb un acoblament en alterna. La sortida de l'acoblament es passa per un comparador en corrent ràpid de manera que tenim una senyal digital curta per cada variació brusca de corrent a l'entrada. Aquesta senyal es passa llavors per dos flip-flops en cascada de forma que generen una senyal lògica a nivell alt si hi ha hagut dos pics o més. La sortida es guarda en un registre de 16 bits de forma que es pot llegir el resultat de tots els canals.

Aquesta arquitectura manté una connexió molt simple tant a l'entrada com a les sortides, sense la necessitat de components afegits i amb una interfície digital compatible amb una FPGA comercial.

Figure 6: Blocs del prototip

La detecció d'apilament és una novetat respecte altres implementacions i ajudarà els algoritmes de post-processat.

Un sistema de control lent permet ajustar tots els voltatges i corrents de polarització i operació (llindars dels comparadors, tensió en el node d'entrada, etc...) i està inclòs en el prototip.

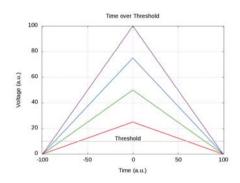

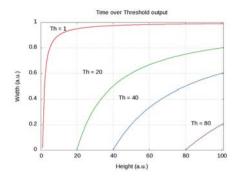

### Temps sobre Llindar Linial (TOT)

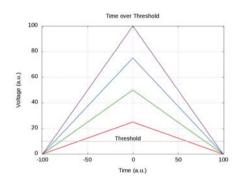

El Temps sobre Llindar o Time Over Threshold (TOT) és un mètode de processat en el qual una senyal analògica es compara amb un valor (llindar) fixe per obtenir una senyal digital representant l'alçada de la senyal analògica. Mesurant l'amplada de la senyal digital de sortida hauríem de poder estimar la entrada. Els sistemes TOT són molt simples i útils per a sistemes multicanal ja que redueixen recursos i consum. Però normalment presenten una linealitat molt dolenta.

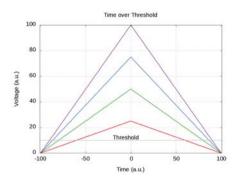

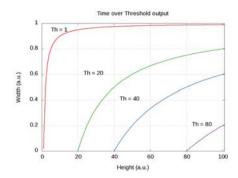

El comportament no lineal del TOT dependrà del processat de la senyal. Per exemple si un filtre Gaussià s'aplica, l'entrada es pot aproximar a un

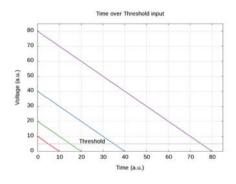

Figure 7: Entrada TOT

Figure 8: Sortida TOT per una entrada triangular

triangle. Utilitzant aquesta entrada <sup>[48]</sup> la no linealitat resultant es pot observar clarament depenent del valor llindar (a les figures 7 i 8). En alguns casos s'han utilitzat llindars dinàmics per evitar aquests efectes <sup>[48]</sup>, però si s'aconsegueix una senyal amb un temps de pujada molt ràpid i una baixada lineal el resultat de la mesura hauria de ser molt millor.

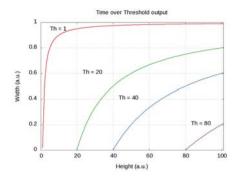

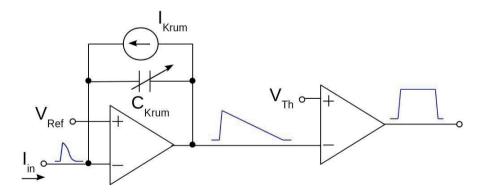

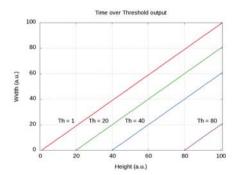

Utilitzant les propietats de la senyal del SiPM ens podem aproximar a la senyal desitjable a l'entrada. Utilitzant un integrador amb una corrent constant de descàrrega abans d'un comparador s'hauria d'obtenir un TOT lineal. L'esquema bàsic es pot veure en la figura 9. Una tècnica molt similar s'ha utilitzat en altres circuits de lectura de sensors [49],[50].

Figure 9: Esquema TOT lineal

Idealment el resultat del TOT es pot calcular fàcilment mitjançant la fórmula 2, tenint en compte com a entrada la càrrega (Q). Degut a que

el llindar  $(V_{Th})$ , la capacitat de realimentació  $(C_{Krum})$  o la corrent de descàrrega  $(I_{Krum})$  són constants la mesura haurà de ser lineal respecte Q. Els elements que introdueixen no linealitats seran el temps del flanc de pujada i la baixada de la senyal. Aquests efectes seran molt majors per senyals relativament petites en amplitud (petites per un sistema PET) o per a corrents de descàrrega molt petites.

$$T_{TOT} = \frac{Q}{I_{Krum}} - \frac{V_{Th}C_{Krum}}{I_{Krum}} \tag{2}$$

Una de les avantatges més importants d'aquesta estructura és la flexibilitat. Canviant la capacitat de realimentació i la corrent de descàrrega ens podem adaptar als requeriments de temps / resolució i corrent d'entrada de l'aplicació desitjada.

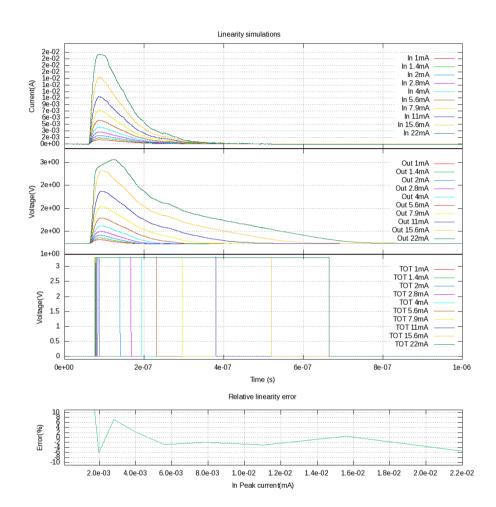

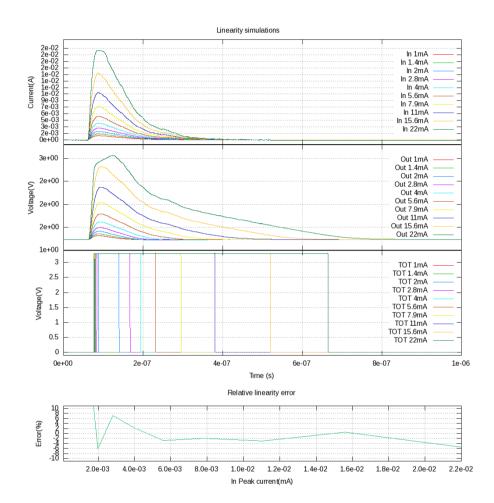

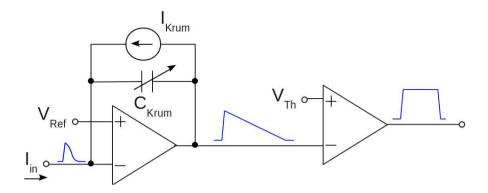

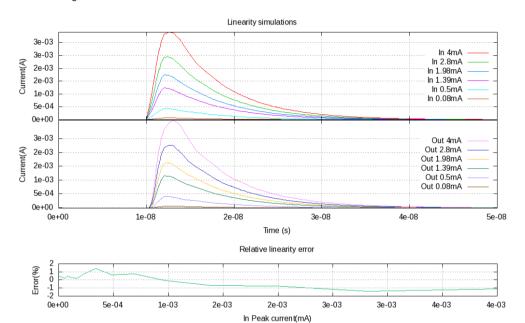

En la següent figura es poden observar unes simulacions de linealitat utilitzant una senyal d'entrada el més pròxima a la realitat (mesurada en un sensor amb un centellejador i una font radioactiva Na<sup>22</sup>). La primera gràfica mostra la corrent d'entrada, la següent la tensió de sortida de l'integrador i finalment la sortida del comparador digital abans de l'error de linealitat per a cada punt.

Figure 10: Simulació de linealitat

### Resultats

El prototip del FLEXTOT es va rebre l'Octubre del 2012, amb 30 mostres encapsulades en un format QFN64 i 10 mostres sense encapsular. Mentre es realitzava la fabricació es va dissenyar un sistema de test per tal de mesurar el més ràpidament el màxim de característiques possibles del prototip.

### Sistema de test

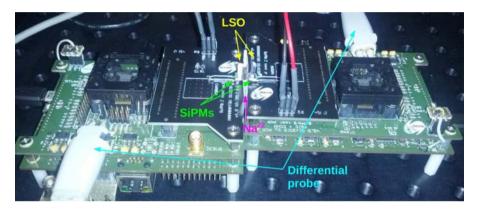

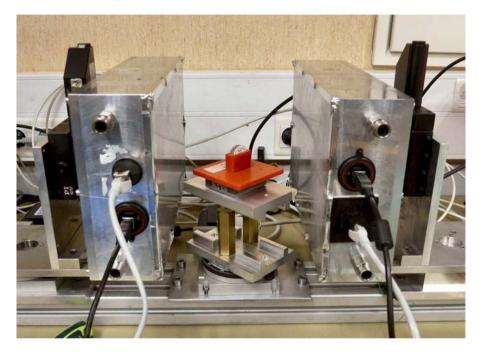

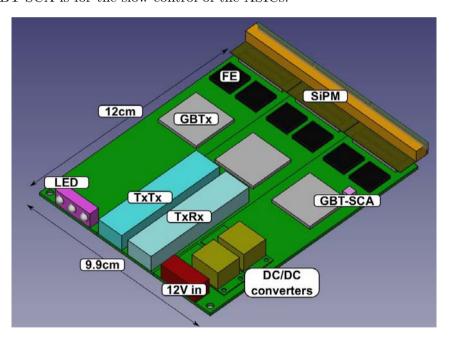

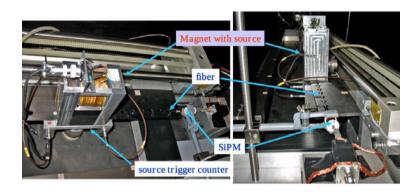

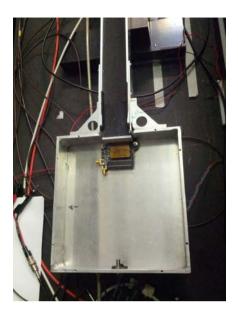

El sistema de test (en la figura 11) es basa en l'apilament de tres circuits impresos amb tots els elements necessaris; des del sensor fins a la comunicació de dades a un ordinador. L'únic element no inclòs és la font d'alt voltatge (< 100V)necessària per alimentar els sensors. La següent electrònica es troba en els diferents circuits (de dalt a baix);

- Sensor: en aquest circuit es poden soldar diferents sensors. El sensor es connecta directament al següent circuit. Una variant amb un circuit d'injecció es pot utilitzar per la calibració amb una corrent coneguda a l'entrada.

- Circuit Analògic: en aquest circuit bàsicament hi ha el prototip amb algun regulador, capacitat de desacoblament i resistències de protecció. També incorpora un parell d'amplificadors per a poder extreure senyals de prova directament a l'oscil·loscopi i interruptors d'alta freqüència (SPDT) per a desconnectar les entrades dels canals.

- Circuit Digital: en aquest circuit hi ha una FPGA de baix cost (Altera Cyclone III, EP3C) i un circuit de comunicacions FT2232 que es connecta al port USB d'un ordinador. Utilitzant aquest sistema es pot controlar tots els elements del circuit i del prototip i realitzar una adquisició de la sortida del prototip (amb una resolució de 5ns en la mesura de l'amplada del pols digital).

Les alimentacions VDDA i VDDD s'alimenten a 3.3V. El consum mig és de 10.7mW per canal o 7.7mW de consum analògic (excloent la potència de l'alimentació digital que inclou les cel.les estàndard, els comparadors ràpids i alguns convertidors digitals / analògics).

Un element important per evitar canviar la forma de la senyal d'entrada i maximitzar la corrent d'entrada és la impedància d'entrada. La mesura realitzada compleix els resultats esperats; amb el comportament inductiu esperat la impedància es manté a valors baixos  $(34\Omega)$  fins a uns 200MHz.

Figure 11: Sistema de test

Per tal de simular la senyal generada pels SiPM s'ha dissenyat un circuit que substitueix el dels sensors. Bàsicament es tracta d'un amplificador seguit d'un acoblament en alterna i una resistència en sèrie per mesurar el corrent. El pic es genera mitjançant un generador arbitrari per simular la forma de la senyal del SiPM.

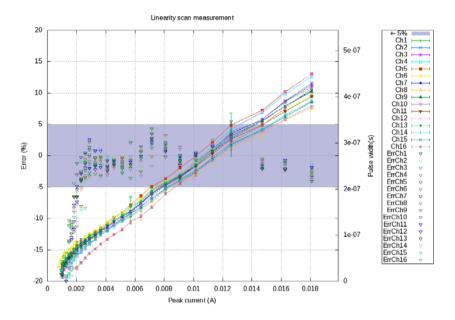

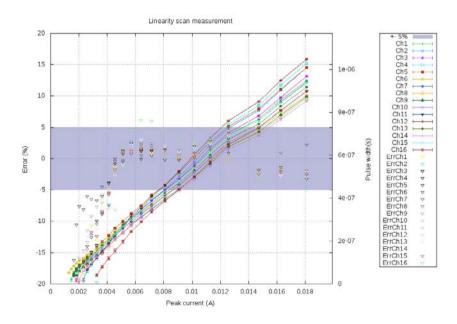

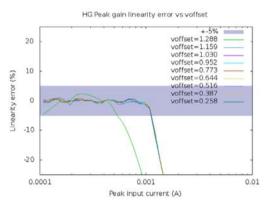

#### Linealitat

Per tal d'obtenir una millor linealitat en l'amplitud de la senyal injectada s'ha col·locat un atenuador programable entre el generador i la entrada del circuit. El generador es configura amb una amplitud màxima de sortida i es va atenuant mitjançant l'atenuador programable. Aquest sistema permet una millor linealitat en la senyal d'entrada que simplement variar l'amplitud en el generador.

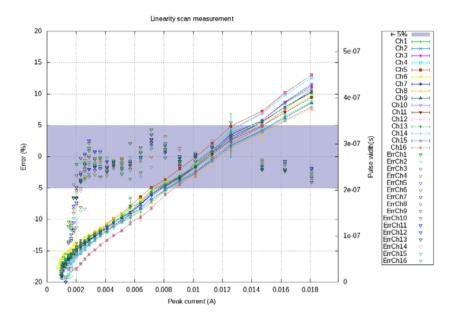

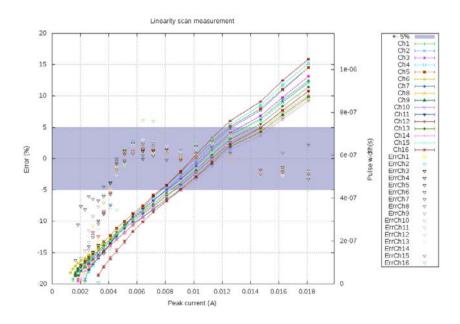

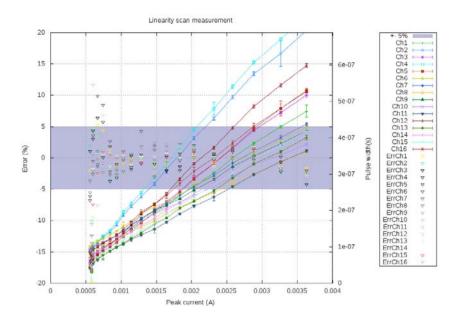

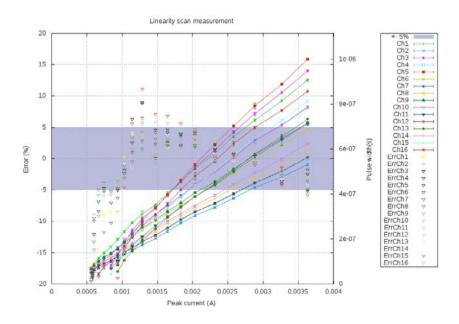

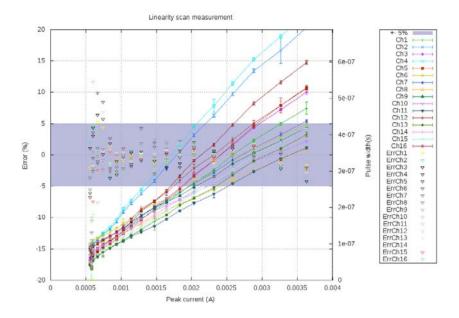

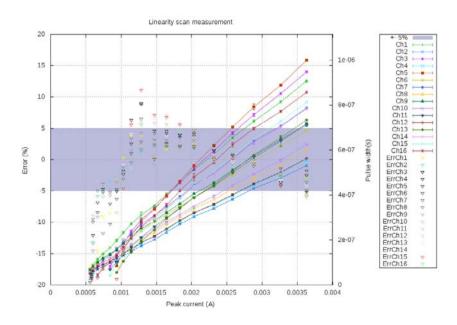

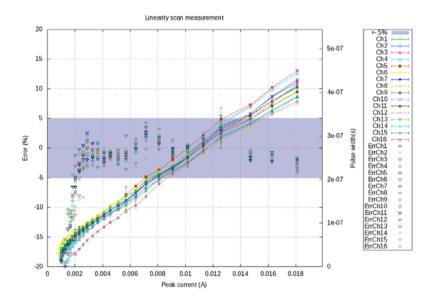

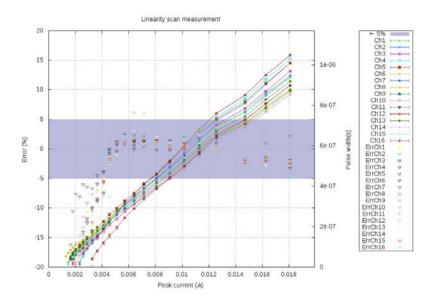

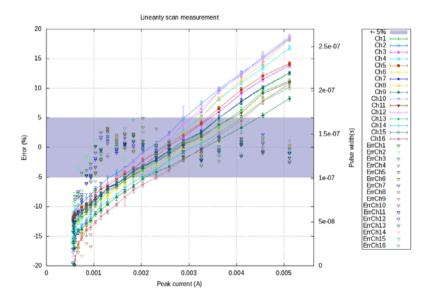

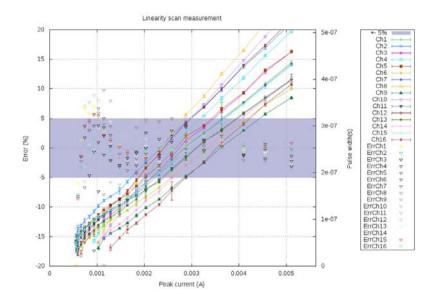

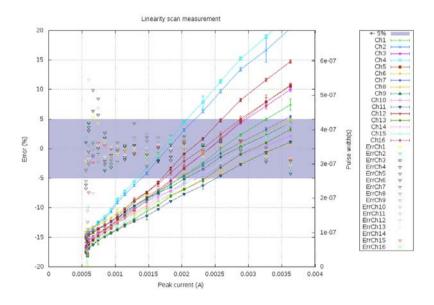

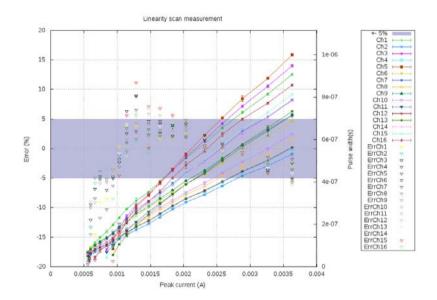

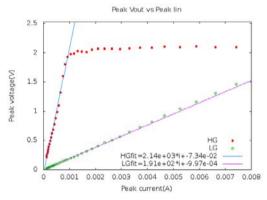

Degut als paràmetres de configuració del prototip alguna calibració és necessària per adaptar-se al rang de senyals d'entrada. Alguns exemples de les corbes de calibració resultants ens poden veure en els 16 canals en les figures 12, 14 per una constant de temps de l'entrada de  $\tau \approx 36$ ns i en les figures 13, 15 per una constant de temps  $\tau \approx 110$ ns.

Figure 12: Linealitat  $\tau \approx 36 \text{ns}$ , 18mA de rang

Figure 13: Linealitat  $\tau\approx$  110ns, 18mA de rang

Figure 14: Linealitat  $\tau \approx 36 \mathrm{ns},\,3.5 \mathrm{mA}$  de rang

Figure 15: Linealitat  $\tau \approx 110 \mathrm{ns}, 3.5 \mathrm{mA}$  de rang

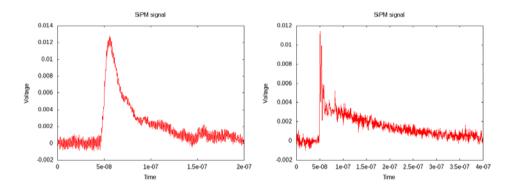

### Mesures amb SiPM

Després de caracteritzar elèctricament el prototip es col·loca un sensor real connectat al sistema de test. La senyal d'entrada tindrà un temps realista i evitarà qualsevol efecte del circuit d'injecció. Amb aquesta configuració es realitzen algunes mesures.

### **Fonts Radioactives**

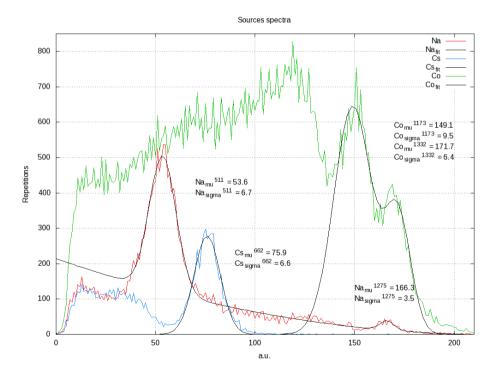

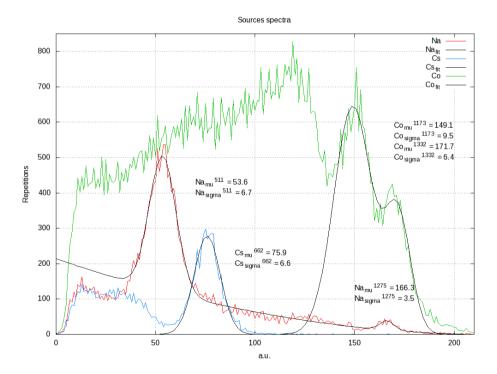

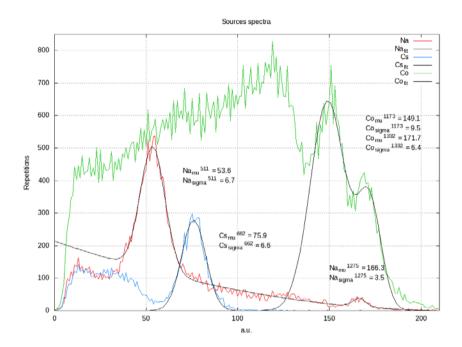

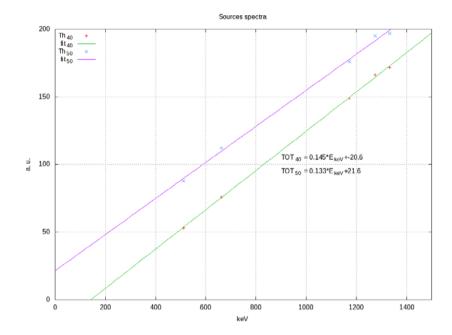

Per caracteritzar amb una senyal el més propera a la realitat s'utilitzen diferents fonts radioactives. Un petit cristall LSO (de 2x2x8 mm³) es col·loca sobre un canal del detector (de 3x3 mm²) i llavors una font radioactiva a prop. Primerament es mesura l'espectre del cristall sol per tal que es pugui restar a posteriori (el material del cristall té una emissió de partícules de diferent energia que generen llum).. Les fonts utilitzades són Na²², Co<sup>60</sup> i Cs¹³², i els resultats es resumeixen a la figura 16.

Figure 16: Mesura de l'espectre Na<sup>22</sup>, Co<sup>60</sup>, Cs<sup>137</sup>

Es pot observar la bona linealitat del sistema en tot el rang. Utilitzant la posició dels dos pics més externs s'obté una constant de calibració. Utilitzant aquesta constant es converteixen les resolucions  $(\sigma)$  mesurades a energia. La resolució calculada es resumeix a la taula 6. Com s'esperava millora lleugerament al augmentar l'energia.

| Font                | keV  | $\mu$ (comptes) | $\sigma$ (comptes) | Res.(%) |

|---------------------|------|-----------------|--------------------|---------|

| $Na^{22}$           | 511  | 53.3            | 7.1                | 9.6     |

|                     | 1275 | 166.3           | $3.5^{1}$          | -       |

| $\mathrm{Cs}^{137}$ | 662  | 75.9            | 6.6                | 6.9     |

| $\mathrm{Co}^{60}$  | 1173 | 149.1           | 9.5                | 5.6     |

|                     | 1332 | 171.6           | $6.4^{1}$          | _       |

<sup>&</sup>lt;sup>1</sup> Caldria més estadística

Table 6: Mesures de les Fonts radioactives

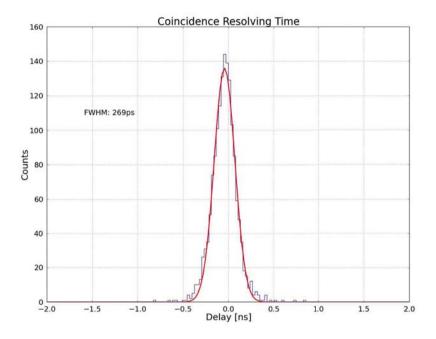

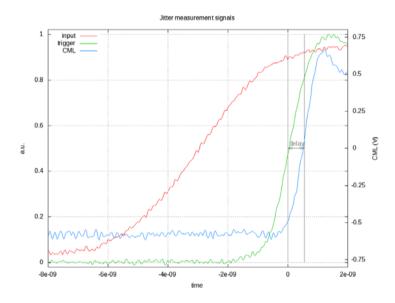

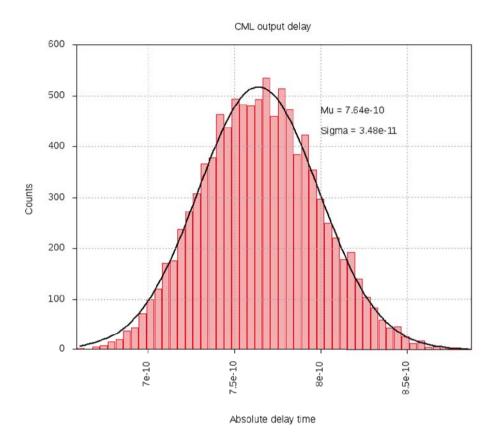

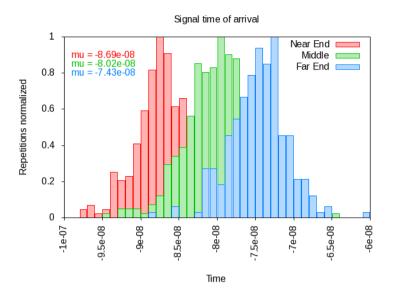

# Mesura de coincidència temporal

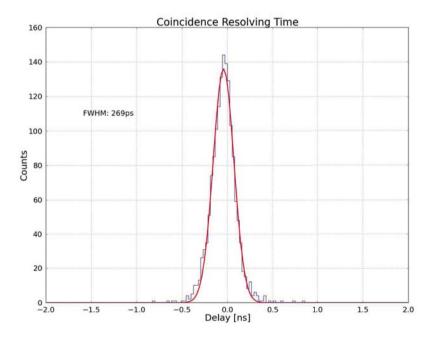

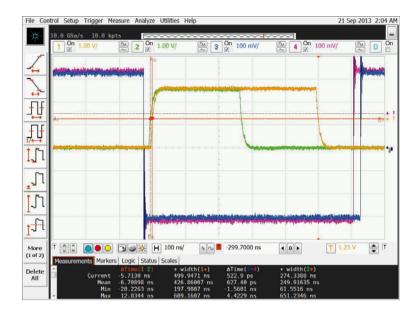

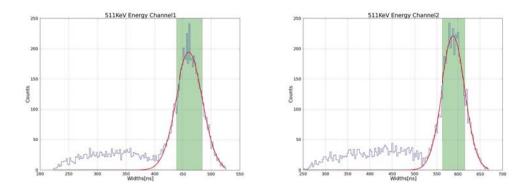

Per obtenir una primera estimació de la resolució temporal del sistema complet s'ha reproduït un sistema de coincidència en el laboratori. Dos sistemes de test amb un sol canal es col·loquen un davant de l'altre. Sobre els dos SiPM es situen cristalls (s'han probat LSO i LYSO) i una font radioactiva de Na<sup>22</sup> enmig. La sortida de temps i les d'energia dels dos canals es capturen amb l'oscil·loscopi.

Utilitzant l'espectre extret dels dos canals es seleccionen els esdeveniments dins del rang d'energies d'interès. Aquesta finestra es correspon al voltant dels 511keV ( $\pm 1\sigma$ ). Una vegada seleccionats els esdeveniments d'interès es representa el retard entre les dues sortides temporals dels dos sistemes de test. El resultat final es mostra en l'histograma de la figura 17 obtenint una resolució temporal per sota dels 300ps FWHM ( $\approx$ 115ps rms).

Figure 17: Mesura de coincidència

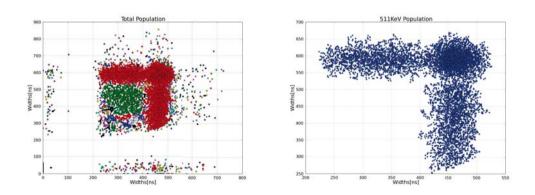

# Mesures en un sistema complet

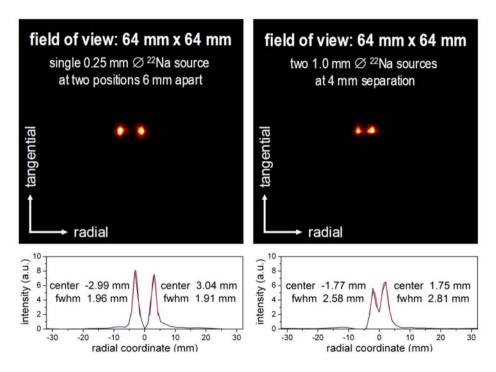

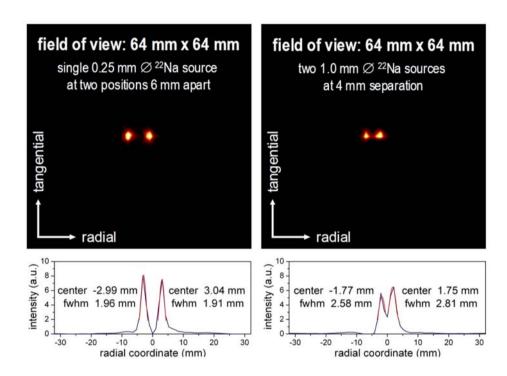

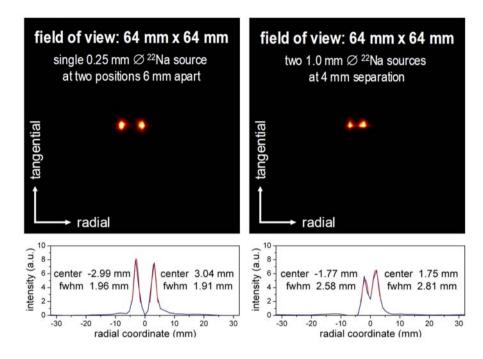

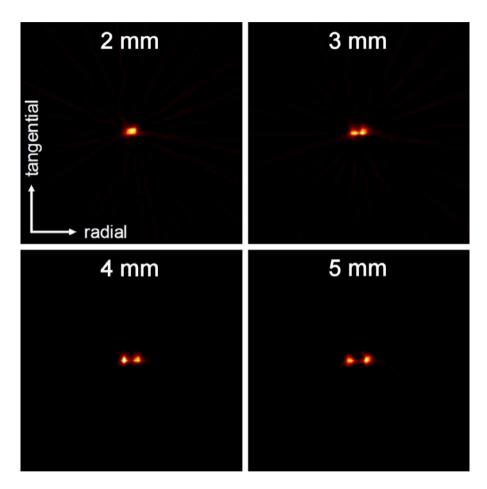

Algunes mesures preliminars s'han realitzat al CIEMAT amb un sistema que emula un sistema PET complet. Es tracta de dos sensors situats a dos costats d'una plataforma giratòria (d'aquesta manera no cal un anell complet de detectors ja que es fa girar la mosta). Al centre es situa una font radioactiva (Na<sup>22</sup>) i una vegada adquirides les dades s'apliquen els algoritmes de reconstrucció d'imatge. Un resultat de la imatge generada i la mesura de posició es pot veure en la figura 18.

En aquest cas s'han realitzat dues mesures, una primera amb una sola font radioactiva (de 0.25mm de diàmetre) i superposant la mesura en dues posicions, i una segona amb dues fonts radioactives (de 1mm de diàmetre) mesurant al mateix temps. La precisió en la mesura de posició resultant és de pocs milímetres com s'espera.

Figure 18: Mesura en un sistema complet

# Disseny per al Tracker SciFi

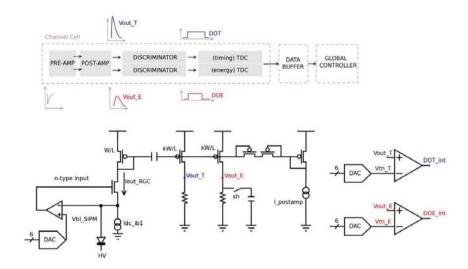

En el cas del disseny per a detectors de partícules cal que es compleixin unes restriccions temporals molt diferents (comparant amb PET). La re-utilització i implementació de la etapa d'entrada en una nova tecnologia i amb unes característiques temporals prou diferents són un repte per al disseny. En aquest cas es tracta d'una tecnologia més moderna amb una tensió d'alimentació molt inferior i completament CMOS.

El tracker és un sub-detector de LHCb que indica el camí que segueixen les partícules amb càrrega elèctrica que passa a través del detector i interacciona amb el material. Les partícules deixen una petita senyal elèctrica al moure's pel detector. Els detectors d'aquest tipus normalment utilitzen tires de silici o detectors gasosos (*straw tubes*). Una vegada s'ha generat, s'adquireix i processa i s'envia a un ordinador que reconstrueix la trajectòria de les partícules.

La tecnologia per a l'IT i l'OT es basarà en fibres centellejadores generant una senyal de llum i transportant-ne els fotons des d'on es generin fins a l'extrem on hi haurà els sensors. En el primer esborrany sobre com serà el detector es preveu utilitzar fibres de 2.5m cobrint almenys la zona central. Tot el detector es construirà mitjançant 3 panells cadascú dels quals amb 3 plans inclinats entre ells ( $\leq 5^{\circ}$ ) per crear els plans X-U-V-X. Cada pla està construït amb 5 capes de fibres de  $250\mu$ m de diàmetre i 2.5 m de llargada.

Un dels problemes més importants per a fer realitat aquest detector és la construcció dels mòduls de fibres. Algunes noves tècniques s'estan provant i desenvolupant per a la seva fabricació.

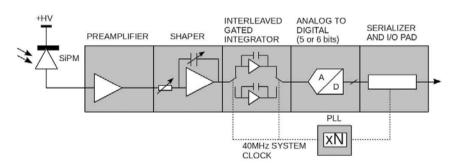

Per a dissenyar la electrònica de processat s'ha iniciat una col·laboració entre Barcelona i Clermont Ferrand, oberta a qualsevol altra institució de LHCb, per dissenyar el "low Power Asic for the sCIntillating FIbres traCker" PACIFIC.

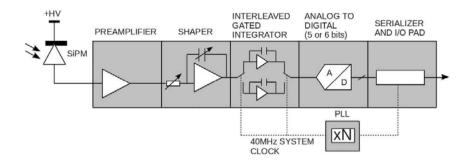

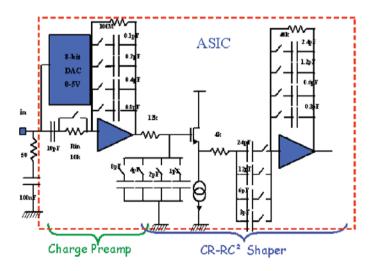

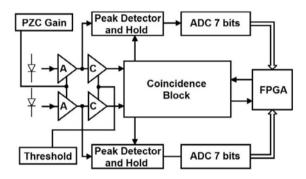

S'han estudiat diferents alternatives per al processat, però sembla que la més senzilla serà la solució base, incorporant un canal amb un pre-amplificador, *shaper*, integrador mostrejat i ADC.

### Resum de les especificacions

En la següent taula es pot veure un resum de les especificacions que haurà de complir la electrònica;

| Paràmetre                     | Valor                              | Unitat                 |

|-------------------------------|------------------------------------|------------------------|

| Canals                        | 64 o 128                           | -                      |

| Potència                      | 0.5  o  1                          | W                      |

| Encapsulat                    | BGA                                | -                      |

| Resolució temporal            | 25                                 | ns                     |

| Constant de temps sensor      | $\mathrm{de}\ 40\ \mathrm{a}\ 300$ | ns                     |

| Rang dinàmic                  | 0-64                               | $micro-cel\cdot les$   |

| Temps d'arribada de la senyal | 0-15                               | ns                     |

| Soroll referit a l'entrada    | ≤143                               | $\frac{pA}{\sqrt{Hz}}$ |

Table 7: Especificacions del PACIFIC

### **Arquitectura**

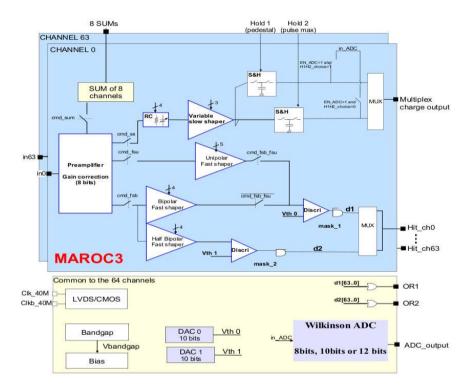

L'arquitectura del canal proposat per al PACIFIC es pot observar en la figura 19. Tot i que s'estan estudiant altres alternatives, específicament una digitalització ràpida seguida per un processat digital de la senyal, la solució més fàcil sembla realitzar un shaping de la senyal i integrar durant 25ns. Al no haver-hi temps mort entre mostra i mostra caldrà un doble integrador entrellaçat de forma que un estigui capturant al temps que l'altre torna a les condicions inicials. Després de l'integrador un convertidor analògic / digital generarà els valors representant l'amplitud a 40MHz. Finalment un enllaç sèrie (probablement diferencial seguint un estàndard) enviarà les dades a alta velocitat. Per aquest últim pas caldrà algun tipus de multiplicador de freqüència (com per exemple un PLL en la figura).

Algunes polaritzacions comunes i un control digital de les tensions, corrents i paràmetres d'operació també hauran d'estar integrats. Així que s'hauran de dissenyar blocs com convertidors digitals analògics ( en tensió i corrent), resistències variables i capacitats variables, connectats a algun bus de control.

Figure 19: Blocs del canal del PACIFIC

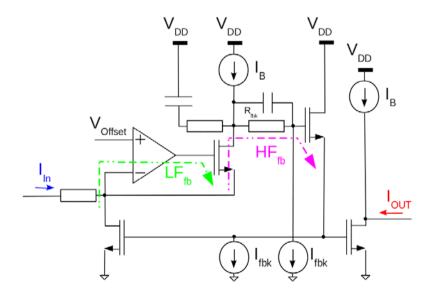

# Pre-amplificador

La etapa d'entrada és un amplificador en mode corrent amb la connexió directa al SiPM. L'objectiu és aconseguir les següents especificacions del bloc:

- Ample de banda ( $\approx 250 \mathrm{MHz}$ ).

- Baix consum (< 2mW, màxim de 8mW/canal en tot l'ASIC).

- Baixa impedància d'entrada ( $20\Omega < Z_{in} < 40\Omega$ ).

- Tensió controlada al node d'entrada ( $\approx 1$ V de rang).

- Soroll referit a l'entrada  $\leq 143 \frac{pA}{\sqrt{Hz}}$

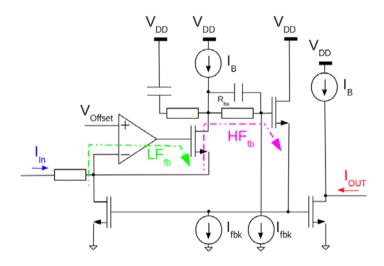

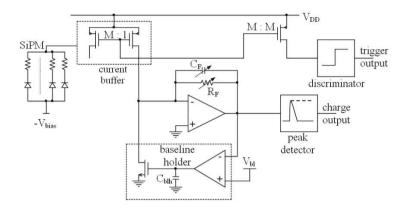

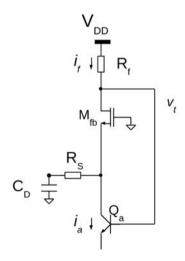

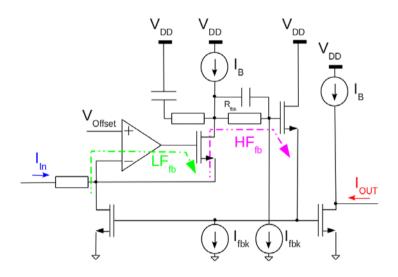

El circuit utilitzat com a referència per aconseguir aquestes característiques es pot veure en la figure 20. La etapa d'entrada es basa en la mateixa nova estructura amb una realimentació doble amb alguna petita variació per adaptar-se a una tecnologia més moderna (IBM  $0.13\mu$  m).

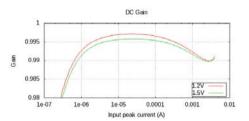

Aquest circuit permet una impedància d'entrada baixa per aconseguir la màxima corrent d'entrada i així la millor resolució temporal. HF $_{FB}$  és el llaç de realimentació d'alta freqüència que manté la impedància d'entrada baixa i constant (fins a certa freqüència). El segon camí LF $_{FB}$  és un llaç de realimentació a més baixa freqüència i proporciona un valor de contínua ( $V_{offset}$  in figure) al node d'entrada utilitzant el curtcircuit virtual de l'amplificador que regula el seguidor.

El disseny s'ha realitzat tenint en compte que el node dominant ha de ser el d'entrada degut a la gran capacitat paràsita del detector. D'aquesta manera la estabilitat es veurà encara més reforçada al connectar un sensor amb una gran capacitat paràsita a l'entrada.

Figure 20: Etapa d'entrada PACIFICr1

### Conclusions

En aquesta tesi s'ha descrit de forma detallada les propietats del sensor i els requeriments necessaris per a dissenyar la electrònica en dos àmbits ben diferenciats; física mèdica (PET) i detectors de partícules (SciFi Tracker). Prenent com a punt d'inici les implementacions realitzades anteriorment i proposant una nova solució amb una etapa amb doble realimentació per aconseguir un gran rang dinàmic i la possibilitat de configurar fàcilment el sistema. Un model del comportament del sensor s'ha utilitzat i ha sigut molt útil per al disseny de la electrònica. Els dos circuits dissenyats s'han comentat detalladament per a diferents tecnologies.

Els objectius principals per al sistema PET s'han complert amb el disseny d'una arquitectura multicanal i la connexió directa als SiPM amb el processat analògic. El prototipus s'ha dissenyat i testejat. L'ajust de voltatge al node d'entrada permet controlar el punt d'operació del sensor, mentre que els diferents camins de senyal permeten la realització de les diferents mesures amb una mesura de temps d'una resolució excel·lent, una mesura adequada de la energia i la detecció de l'apilament d'esdeveniments. Així doncs la etapa d'entrada compleix amb tot el que es demanava del circuit. Després del disseny i el test ja tan sols quedarà comprovar el seu funcionament en un detector real.

Les restriccions en el disseny del PACIFIC encarà s'estan concretant, i el primer prototipus descrit ha de servir com una primera etapa. El circuit dissenyat segueix la mateixa estructura que el de PET però portat a una tecnologia més moderna i simplificat per l'aplicació. Una vegada fabricat caldrà comprovar les seves prestacions. Mentre s'avança en el disseny de la resta d'etapes per tal de complir el calendari fixat.

# **Summary**

The aim of this thesis is to present a solution for the readout of Silicon Photo-Multipliers (SiPMs) arrays improving current implemented solutions. With this purpose a novel current mode input stage has been designed and tested. In first place focusing in general applications for medical imaging (Positron Emission Tomography, PET) and then using the same topology for a more constrained design in higghe energy physics (upgrade of Tracker detector at LHCb experiment).

SiPM are recently developed electronic devices<sup>[1]</sup> with photon counting capabilities improving current state of the art detectors regarding high voltage requirements, signal gain and magnetic field tolerance, while keeping at the same time excellent gain and timing characteristics, and a wide dynamic range. They are semiconductor devices still under development to improve yield, reduce dark count, provide multi-channel architectures and increase light sensitivity spectrum.

A Front End Readout Application Specific Integrated Circuit (ASIC) for SiPMs is presented with the following features: wide dynamic range, high speed, multi channel, low input impedance current preamplifier, low power consumption, SiPM voltage control, and timing, charge and pileup signal output.

The pre-amplifier input stage includes a novel circuitry with double feed-back loop to lower input impedance at the same time it keeps a constant DC value at the input node over the full range of operation and keeping the desired bandwidth.

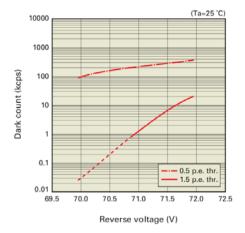

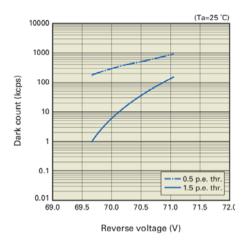

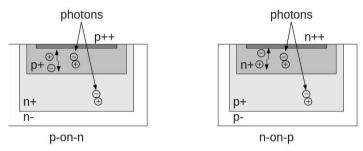

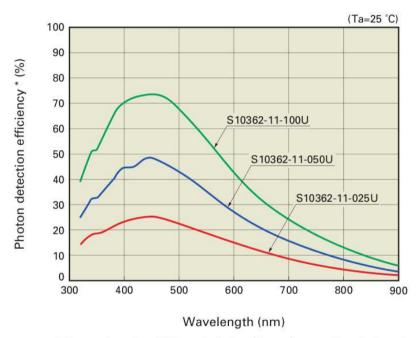

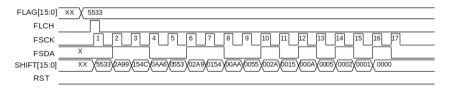

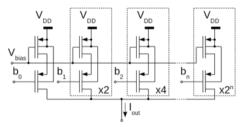

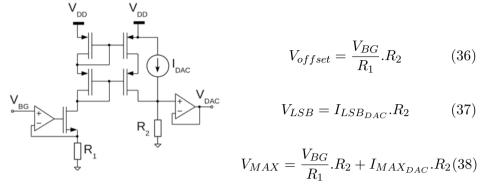

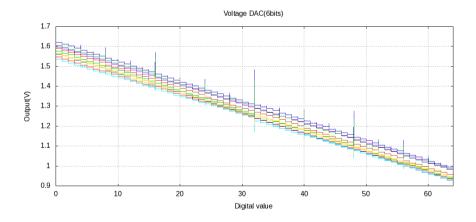

# Silicon Photo-Multipliers