# IMPROVING MULTITHREADING PERFORMANCE FOR CLUSTERED VLIW ARCHITECTURES

# Manoj Gupta

Barcelona, 2013

#### **Advisors**

Fermín Sánchez Josep Llosa

A THESIS SUBMITTED IN FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF **Doctor per la UPC**

Department of Computer Architecture Technical University of Catalonia

### **Abstract**

Very Long Instruction Word (VLIW) processors are very popular in embedded and mobile computing domain. Use of VLIW processors range from Digital Signal Processors (DSPs) found in a plethora of communication and multimedia devices to Graphics Processing Units (GPUs) used in gaming and high performance computing devices. The advantage of VLIWs is their low complexity and low power design which enable high performance at a low cost. Scalability of VLIWs is limited by the scalability of register file ports. It is not viable to have a VLIW processor with a single large register file because of area and power consumption implications of the register file.

Clustered VLIW solve the register file scalability issue by partitioning the register file into multiple clusters and a set of functional units that are attached to register file of that cluster. Using a clustered approach, higher issue width can be achieved while keeping the cost of register file within reasonable limits. Several commercial VLIW processors have been designed using the clustered VLIW model.

VLIW processors can be used to run a larger set of applications. Many of these applications have a good Lnstruction Level Parallelism (ILP) which can be efficiently utilized. However, several applications, specially the ones that are control code dominated do not exibit good ILP and the processor is underutilized. Cache misses is another major source of resource underutilization. Multithreading is a popular technique to improve processor utilization. Interleaved MultiThreading (IMT) hides cache miss latencies by scheduling a different thread each cycle but cannot hide unused instructions slots. Simultaneous MultiThread (SMT) can also remove ILP under-utilization by issuing multiple threads to fill the empty instruction slots. However, SMT has a higher implementation cost than IMT.

The thesis presents Cluster-level Simultaneous MultiThreading (CSMT) that supports a limited form of SMT where VLIW instructions from different threads are merged at a cluster-level granularity. This lowers the hardware implementation cost to a level comparable to the cheap IMT technique. The more complex SMT combines VLIW instructions

at the individual operation-level granularity which is quite expensive especially in for a mobile solution. We refer to SMT at operation-level as OpSMT to reduce ambiguity. While previous studies restricted OpSMT on a VLIW to 2 threads, CSMT has a better scalability and upto 8 threads can be supported at a reasonable cost.

The thesis also proposes several other techniques to further improve CSMT performance. One particular approach, Cluster renaming remaps the clusters used by instructions of different threads to reduce resource conflicts. Cluster renaming is quite effective in reducing the issue-slots under-utilization and significantly improves CSMT performance. The thesis also covers several other approaches e.g. heterogeneous merging where instructions from some threads are merged at operation-level (OpSMT) and some at cluster-level (CSMT). Number of threads merged using either approach is decided by the maximum allowed complexity (gate delays or transistor count etc.). The heterogeneous merging approach allows for a performance better than CSMT but without the full overhead of OpSMT.

The next discussed approach is a split-issue based approach where a VLIW instruction can be split and issued in multiple cycles instead of having to issue as an unit. Splitting a VLIW instruction allows more flexibility in issuing the instruction and further improves the performance.

The thesis discusses another hybrid approach that combines the best of IMT with CSMT. In this hybrid approach, multiple thread contexts are maintained and only the threads that the merging hardware can support are used in instruction merging. Maintaining more threads mean that if some threads are blocked because of cache misses, those can be replaced by other threads. As a result, a full pool of threads if available for merging and resource under-utilization is reduced.

Overall, CSMT and the other discussed orthogonal approaches can achieve a performance that is close to the more complex approach of merging instructions from different threads at operation-level but at a cost comparable to the simple IMT technique.

# Acknowledgements

I am greatly indebted to my supervisors Prof. Josep Llosa and Prof. Fermín Sánchez for their invaluable technical guidance and moral support. I would like to thank my other PhD colleagues Rakesh Ranjan, Indu Bhagat, Abhishek Deb, Miquel Moreto, Tanausu Ramirez and Govind SreekarShenoy for their cooperation, support and the great informal discussions. I would also like to thank the staff of Department of Computer Architecture at UPC Barcelona, in particular Trini, for their help. The work done in the thesis was supported by the Spanish Ministry of Science and Technology under contract CICYT TIN2007-60625, FI grant from AGAUR/Generalitat de Catalunya, SARC (Scalable computer ARChitecture) Project and HiPEAC European Network of Excellence and I would like to thank all of them for being enabler of my work. The thesis is dedicated to my parents who showed immense patience and provided me great moral support during the coarse of my work.

# **Contents**

| A۱ | bstrac  | et e e e e e e e e e e e e e e e e e e              | i    |

|----|---------|-----------------------------------------------------|------|

| A  | cknov   | vledgements                                         | iii  |

| In | dex     |                                                     | viii |

| Li | st of l | Figures                                             | ix   |

| Li | st of ' | Tables                                              | xiii |

| 1  | Intr    | oduction                                            | 1    |

|    | 1.1     | VLIW Processors                                     | 4    |

|    | 1.2     | Scalability Issues in VLIW Processors               | 9    |

|    | 1.3     | Clustered VLIW Processors                           | 10   |

|    | 1.4     | MultiThreading                                      | 12   |

|    | 1.5     | Contributions of the Thesis                         | 17   |

|    | 1.6     | Thesis Organization                                 | 19   |

| 2  | Exp     | erimental Platform                                  | 21   |

|    | 2.1     | VEX Architecture                                    | 21   |

|    | 2.2     | VEX Toolchain                                       | 24   |

|    | 2.3     | Simulating a MultiThreaded Processor                | 25   |

|    |         | 2.3.1 Baseline Architecture Configuration           | 25   |

|    |         | 2.3.2 Microarchitectural changes for multithreading | 27   |

|    | 2.4     | Benchmarks and Workloads                            | 28   |

|    |         | 2.4.1 Workload execution                            | 30   |

|    |         | 2.4.2 Thread Selection Policy                       | 31   |

|    | 2.5     | Summary                                             | 31   |

| 3 | Clus                                                             | ster-leve                              | el Simultaneous MultiThreading (CSMT)     | 33 |  |  |

|---|------------------------------------------------------------------|----------------------------------------|-------------------------------------------|----|--|--|

|   | 3.1                                                              | Introd                                 | uction                                    | 33 |  |  |

|   | 3.2                                                              | Cluste                                 | r-level Simultaneous MultiThreading       | 35 |  |  |

|   | 3.3                                                              | CSMT                                   | Performance Analysis                      | 40 |  |  |

|   | 3.4                                                              | Mergi                                  | ing Hardware Complexity Analysis          | 44 |  |  |

|   | 3.5                                                              | Summ                                   | ary and Conclusions                       | 45 |  |  |

| 4 | Clus                                                             | ster Rei                               | naming                                    | 47 |  |  |

|   | 4.1                                                              | Motiva                                 | ation                                     | 47 |  |  |

|   | 4.2                                                              | Cluste                                 | r Renaming                                | 49 |  |  |

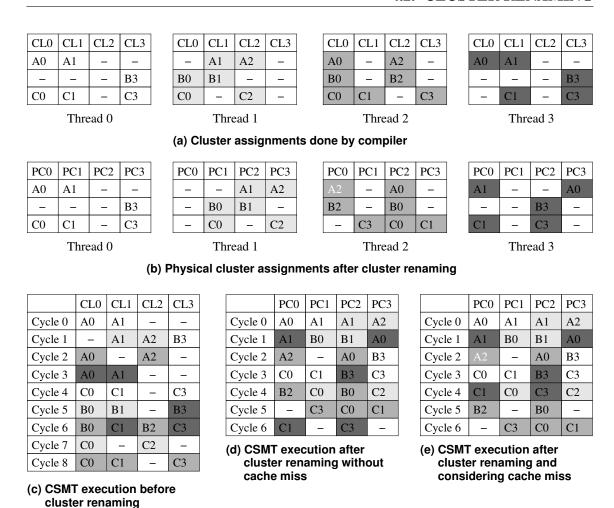

|   |                                                                  | 4.2.1                                  | Cluster Renaming Example                  | 52 |  |  |

|   | 4.3                                                              | Result                                 | · · · · · · · · · · · · · · · · · · ·     | 53 |  |  |

|   |                                                                  | 4.3.1                                  | Cluster Usage Analysis                    | 54 |  |  |

|   |                                                                  | 4.3.2                                  | Cluster Renaming Performance Improvements | 55 |  |  |

|   |                                                                  | 4.3.3                                  | CSMT Performance Comparison With IMT      | 57 |  |  |

|   |                                                                  | 4.3.4                                  | CSMT Performance Comparison with OpSMT    | 59 |  |  |

|   | 4.4                                                              | Summ                                   | ary and Conclusions                       | 60 |  |  |

| 5 | Heterogeneous Merging: Using CSMT and OpSMT Merging Hardware To- |                                        |                                           |    |  |  |

|   | geth                                                             | er                                     |                                           | 61 |  |  |

|   | 5.1                                                              | Motiva                                 | ation                                     | 61 |  |  |

|   | 5.2                                                              | Hetero                                 | ogeneous Thread Merging Schemes           | 65 |  |  |

|   | 5.3                                                              | Evalu                                  | ation                                     | 67 |  |  |

|   |                                                                  | 5.3.1                                  | Performance Analysis                      | 68 |  |  |

|   | 5.4                                                              | Summ                                   | ary and Conclusions                       | 71 |  |  |

| 6 | Clus                                                             | ster-leve                              | el Split-Issue                            | 73 |  |  |

|   | 6.1                                                              | Opera                                  | tion-level Split-Issue                    | 73 |  |  |

|   |                                                                  | 6.1.1                                  | Dataflow hazards                          | 75 |  |  |

|   |                                                                  | 6.1.2                                  | Implementation details                    | 76 |  |  |

|   | 6.2                                                              | Cluste                                 | r-level Split-Issue                       | 78 |  |  |

|   | 6.3                                                              | Implementing Cluster-level Split-Issue |                                           |    |  |  |

|   | 6.4                                                              | Issues                                 | with cluster-level split-issue            | 83 |  |  |

|   |                                                                  | 6.4.1                                  | Exceptions/Interrupts                     | 84 |  |  |

|   |                                                                  | 6.4.2                                  | Register file port contention             | 86 |  |  |

#### **CONTENTS**

|    |        | 6.4.3 Memory Port Contention                                      | 87  |

|----|--------|-------------------------------------------------------------------|-----|

|    |        | 6.4.4 Issues with Inter-cluster Communication                     | 88  |

|    | 6.5    | Performance Evaluation                                            | 89  |

|    | 6.6    | Summary and Conclusions                                           | 93  |

| 7  | Hyb    | orid MultiThreading                                               | 95  |

|    | 7.1    | Motivation                                                        | 95  |

|    | 7.2    | Hybrid MultiThreading                                             | 97  |

|    |        | 7.2.1 Interleaving Step                                           | 99  |

|    | 7.3    | Thread Selection Schemes                                          | 99  |

|    | 7.4    | Results                                                           | 103 |

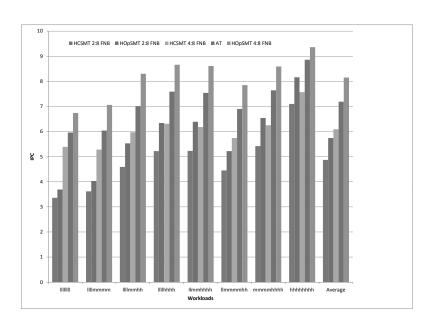

|    |        | 7.4.1 Performance Evaluation of HMT with FNB Policy               | 105 |

|    |        | 7.4.2 Detailed Performance Evaluation of Thread Selection Schemes | 106 |

|    | 7.5    | Summary and Conclusions                                           | 108 |

| 8  | Putt   | ting It All Together                                              | 111 |

|    | 8.1    | Motivation                                                        | 111 |

|    | 8.2    | Results                                                           | 114 |

|    | 8.3    | Summary and Conclusions                                           | 118 |

| 9  | Con    | clusions and Future Work                                          | 119 |

|    | 9.1    | Future Work                                                       | 121 |

| Bi | bliogi | raphy                                                             | 123 |

| A  | CSM    | MT Cost Analysis                                                  | 129 |

|    | A.1    | Introduction                                                      | 129 |

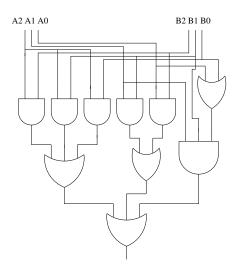

|    | A.2    | Thread Merge Hardware                                             | 130 |

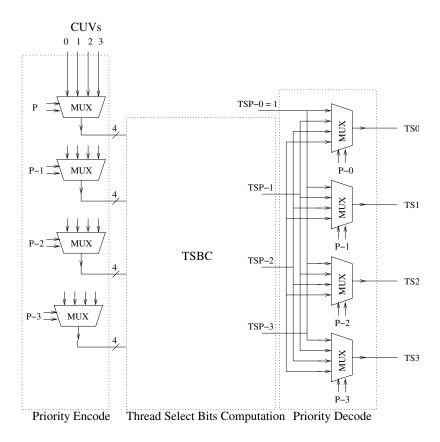

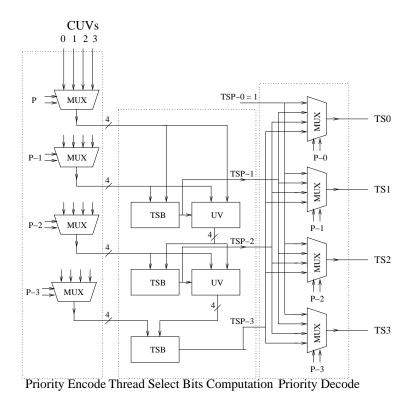

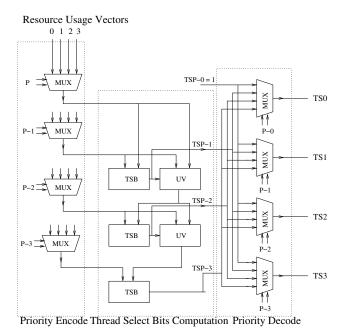

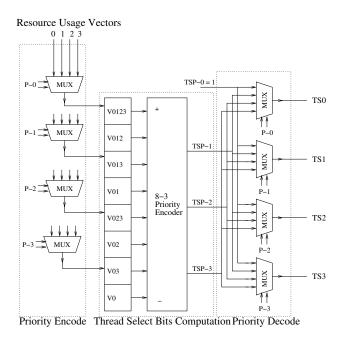

|    |        | A.2.1 Priority Encode                                             | 131 |

|    |        | A.2.2 Priority Decode                                             | 132 |

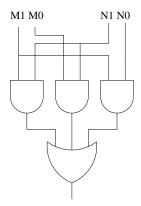

|    |        | A.2.3 Thread Select Bits Computation                              | 133 |

|    | A.3    | Serial Logic                                                      | 134 |

|    |        | A.3.1 Thread Select Bit block                                     |     |

|    |        | A.3.2 Usage Vector Computation block                              |     |

|    | A.4    | Parallel Logic                                                    | 137 |

|    | A.5    | Cost Analysis                                                     | 138 |

#### **CONTENTS**

|   |     | A.5.1   | Serial Lo  | gic                  | 39 |

|---|-----|---------|------------|----------------------|----|

|   |     |         | A.5.1.1    | Delay                | 39 |

|   |     |         | A.5.1.2    | Transistor Count     | 39 |

|   |     | A.5.2   | Parallel I | ogic                 | 40 |

|   |     |         | A.5.2.1    | Transistor Count     | 40 |

|   | A.6 | Results | 3          |                      | 42 |

| В | OpS | MT Cos  | st Analysi | s 1                  | 45 |

|   | B.1 | Introdu | iction     |                      | 45 |

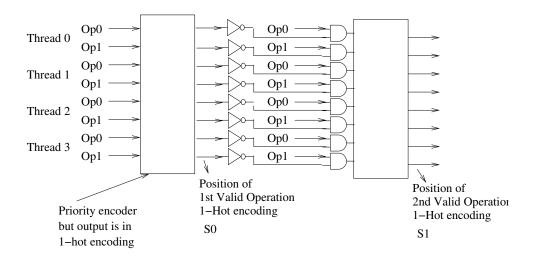

|   |     | B.1.1   | OpSMT '    | Thread Merge Control | 46 |

|   |     |         | B.1.1.1    | Serial logic         | 48 |

|   |     |         | B.1.1.2    | Parallel logic       | 50 |

|   |     |         | B.1.1.3    | Routing Computation  | 50 |

|   | B.2 | Cost A  | nalysis .  |                      | 51 |

|   |     | B.2.1   | Serial Lo  | gic                  | 51 |

|   |     | B.2.2   | Parallel I | ogic                 | 52 |

|   |     | B.2.3   | Routing (  | Computation          | 52 |

|   | В 3 | Daculto | ,          | 1                    | 55 |

# **List of Figures**

|     |     |        | 2  |

|-----|-----|--------|----|

|     |     |        |    |

|     |     |        | 3  |

|     | •   |        | 4  |

| roc | ess | or     | 5  |

|     |     |        | 6  |

|     |     |        | 7  |

|     |     |        | 8  |

|     |     |        | 9  |

|     |     |        | 11 |

|     |     |        | 12 |

|     |     |        | 14 |

|     |     |        | 22 |

|     |     |        | 23 |

|     |     |        | _  |

|     |     |        | 24 |

|     | •   | •      | 24 |

|     |     |        | 26 |

|     |     |        | 26 |

|     |     |        | 30 |

|     |     |        | 34 |

|     |     |        | 36 |

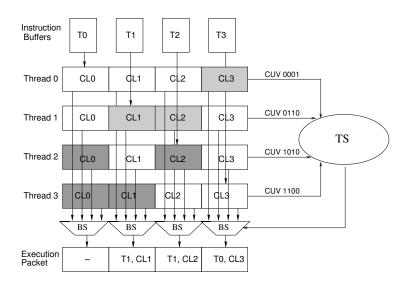

|     |     |        | 37 |

| usi | ng  |        |    |

|     |     |        | 37 |

|     |     | rocess |    |

#### LIST OF FIGURES

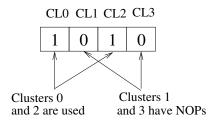

| 3.5  | Cluster Usage Vector                                              | 39 |

|------|-------------------------------------------------------------------|----|

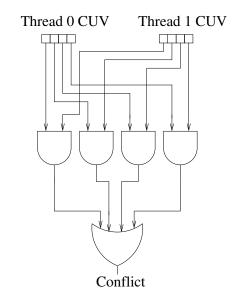

| 3.6  | CSMT conflict checking for 2 threads                              | 39 |

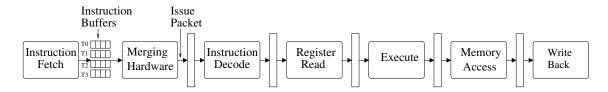

| 3.7  | Pipeline with extra stage for merging hardware                    | 40 |

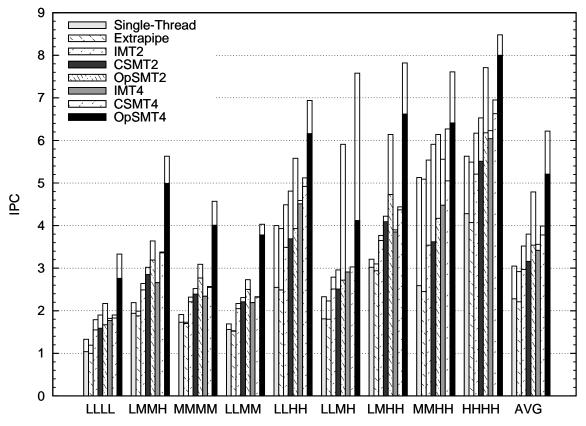

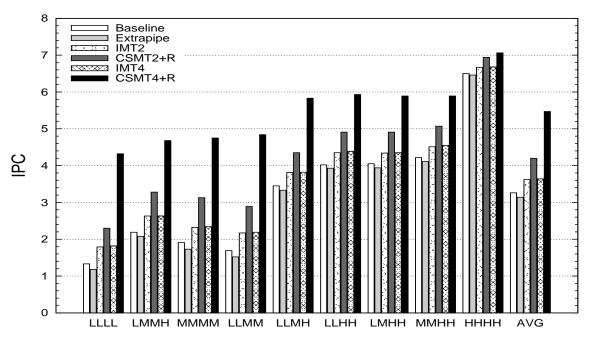

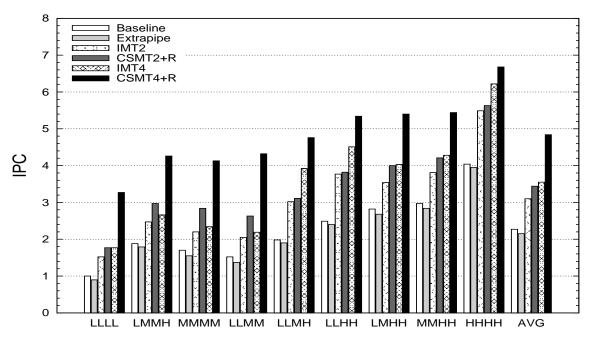

| 3.8  | CSMT performance                                                  | 41 |

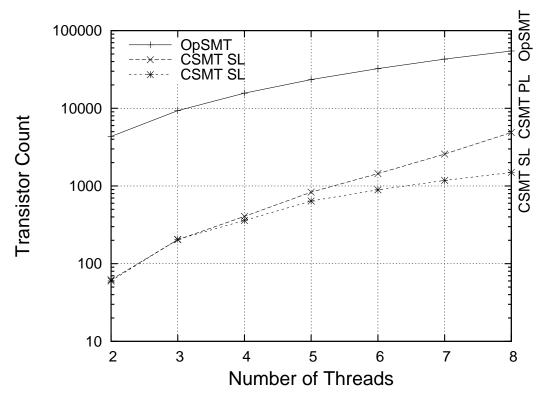

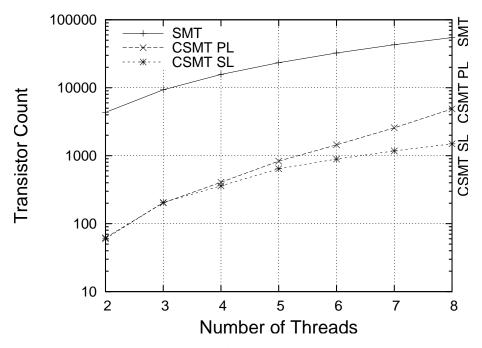

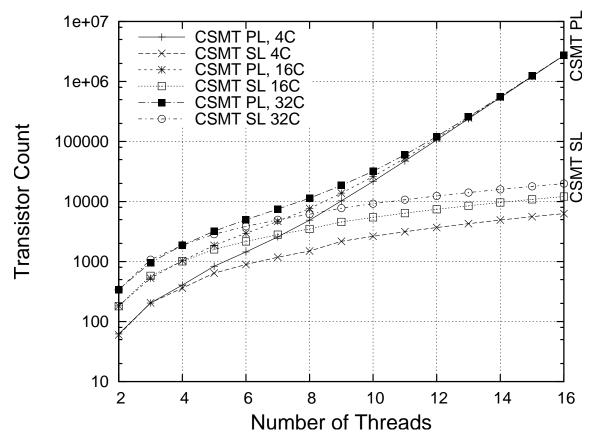

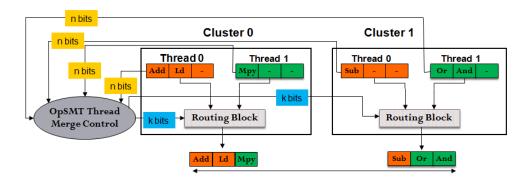

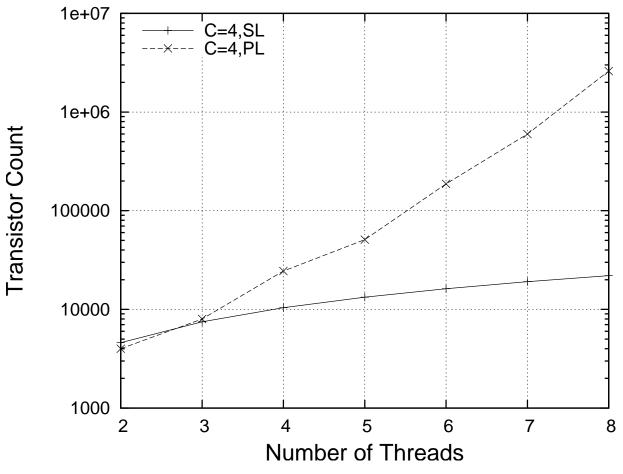

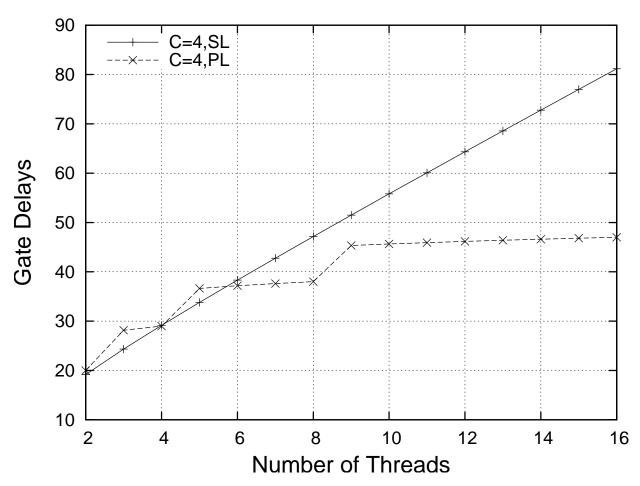

| 3.9  | Thread merging hardware transistor count for OpSMT and CSMT .     | 43 |

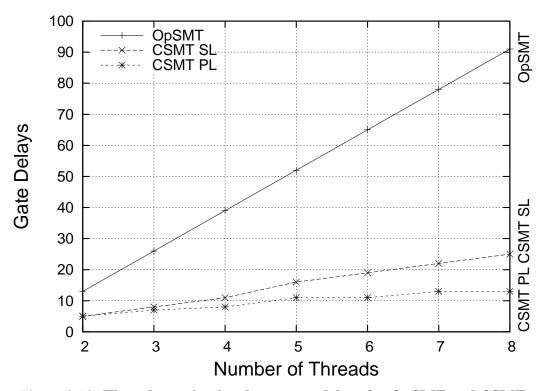

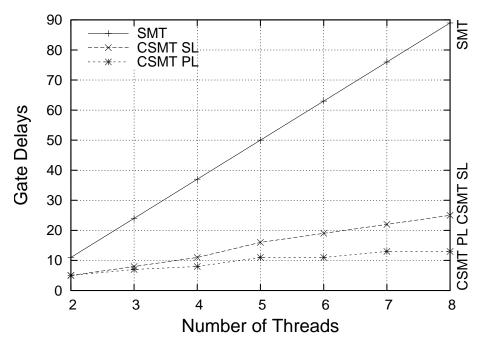

| 3.10 | Thread merging hardware gate delays for OpSMT and CSMT            | 43 |

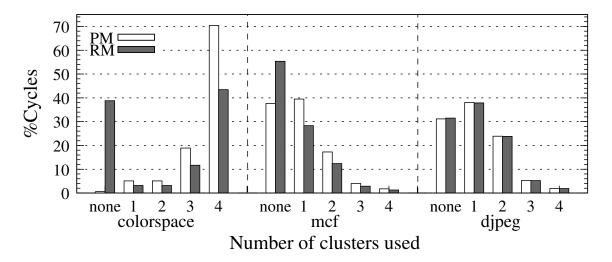

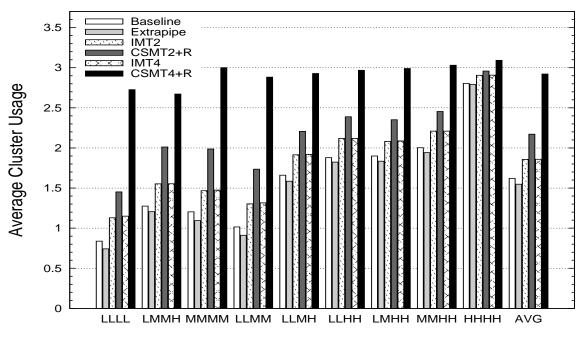

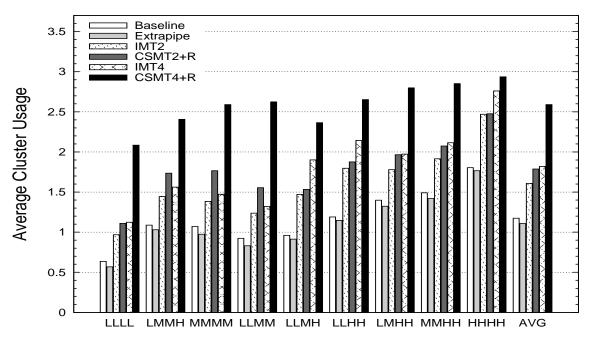

| 4.1  | Cluster usage                                                     | 48 |

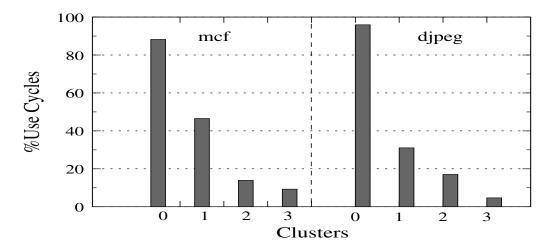

| 4.2  | Individual cluster use in mcf and djpeg                           | 49 |

| 4.3  | Shift tables for a 4-cluster architecture                         | 50 |

| 4.4  | Cluster renaming logic for a 4-cluster architecture               | 51 |

| 4.5  | CSMT execution on a 4-thread 4-cluster architecture using cluster |    |

|      | renaming.                                                         | 52 |

| 4.6  | Cluster usage with a perfect memory model                         | 54 |

| 4.7  | Cluster usage with a real memory model                            | 55 |

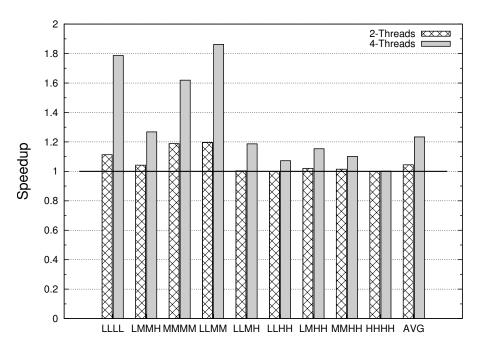

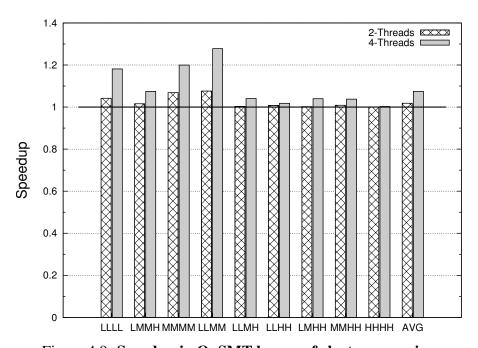

| 4.8  | Speedup in CSMT by use of cluster renaming                        | 56 |

| 4.9  | Speedup in OpSMT by use of cluster renaming                       | 56 |

| 4.10 | CSMT vs IMT, Perfect Memory                                       | 57 |

| 4.11 | CSMT vs IMT, Real Memory                                          | 58 |

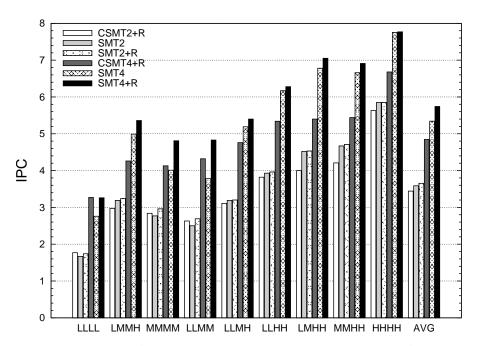

| 4.12 | CSMT performance comparison with OpSMT                            | 59 |

| 5.1  | OpSMT Performance                                                 | 62 |

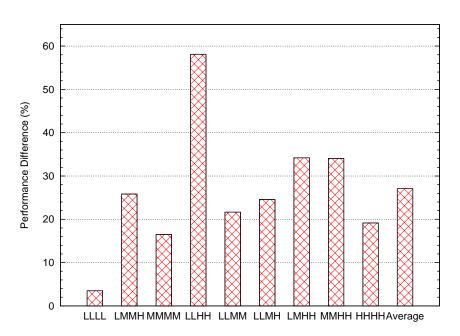

| 5.2  | OpSMT performance advantage over CSMT                             | 63 |

| 5.3  | CSMT and OpSMT thread merge control area                          | 63 |

| 5.4  | CSMT and OpSMT thread merge control delays                        | 64 |

| 5.5  | Mixed Merging Example                                             | 65 |

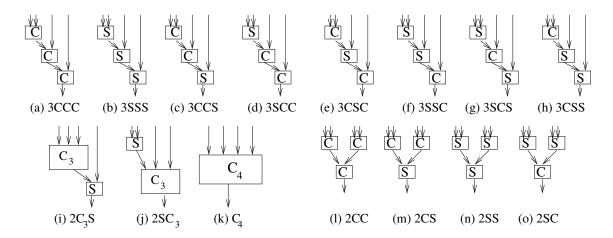

| 5.6  | Possible Merging Schemes for 4 Threads                            | 66 |

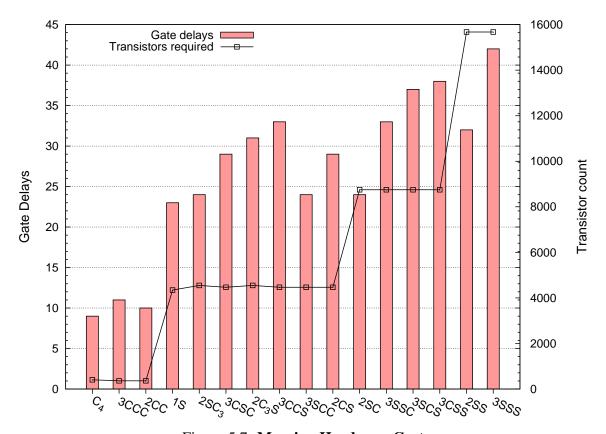

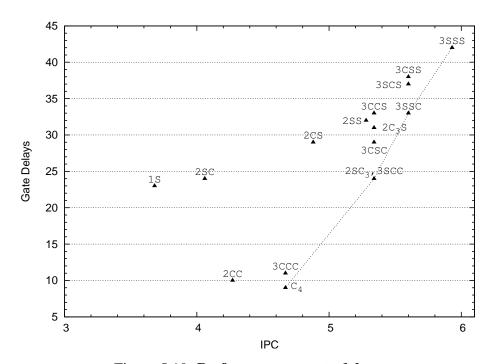

| 5.7  | Merging Hardware Cost                                             | 67 |

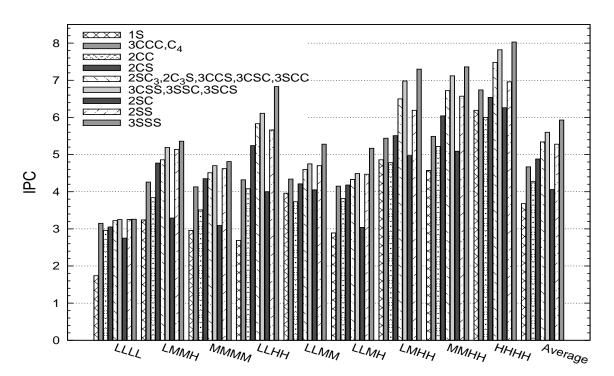

| 5.8  | Merging schemes performance                                       | 69 |

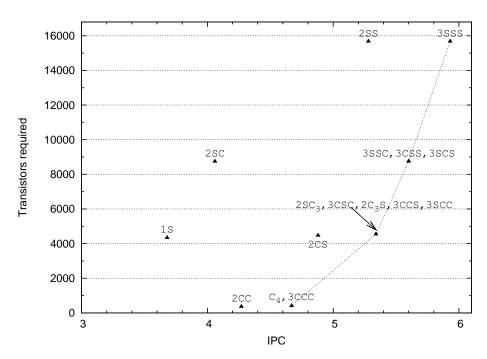

| 5.9  | Performance vs transistors incurred                               | 70 |

| 5.10 | Performance vs gate delays                                        | 71 |

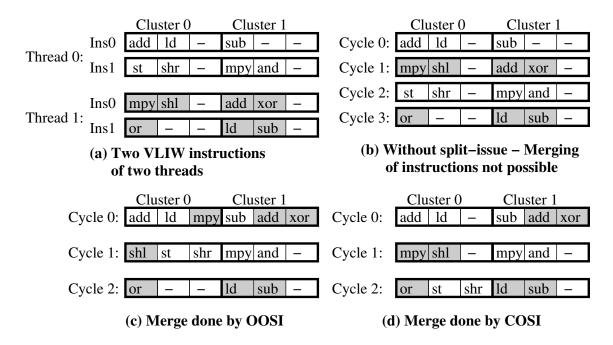

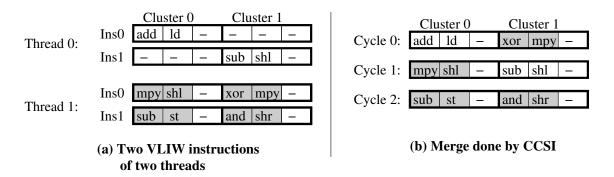

| 6.1  | Instruction Merging in OpSMT and CSMT                             | 74 |

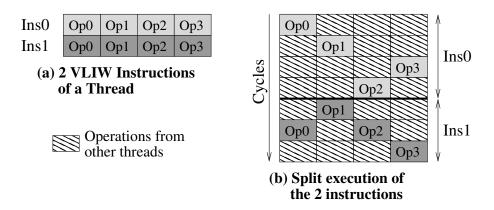

| 6.2  | Instruction Execution with Split-Issue                            | 74 |

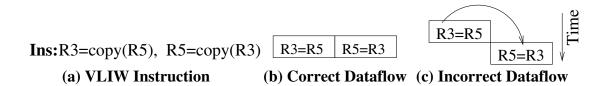

| 6.3  | Issues with Dataflow                                              | 75 |

| 64   | Working of Split-Issue                                            | 77 |

#### LIST OF FIGURES

| 6.5  | Applicability of split-issue                                                    |

|------|---------------------------------------------------------------------------------|

| 6.6  | Operation-level and cluster-level split-issue with operation-level merg-        |

|      | ing                                                                             |

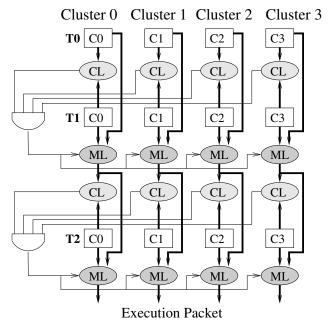

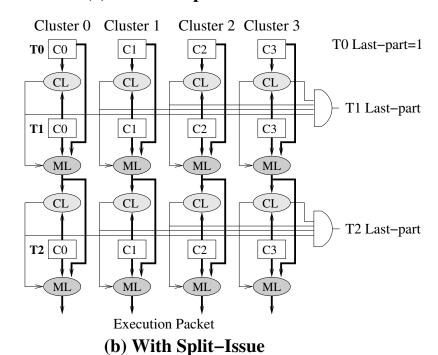

| 6.7  | Cluster-level split-issue with cluster-level merging 81                         |

| 6.8  | Merging Hardware                                                                |

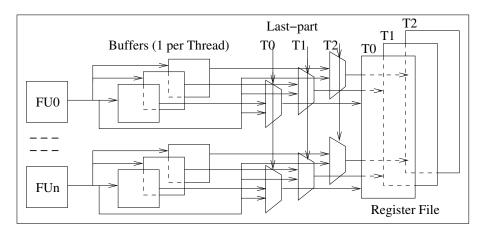

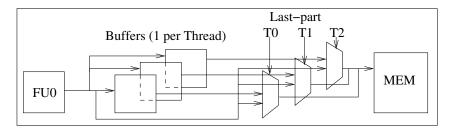

| 6.9  | Delaying updates to architectural state by using buffers                        |

| 6.10 | Buffer organization                                                             |

| 6.11 | Register File Organizations                                                     |

| 6.12 | Memory port contention because of delayed memory writes 87                      |

| 6.13 | Issuing inter-cluster communication operations                                  |

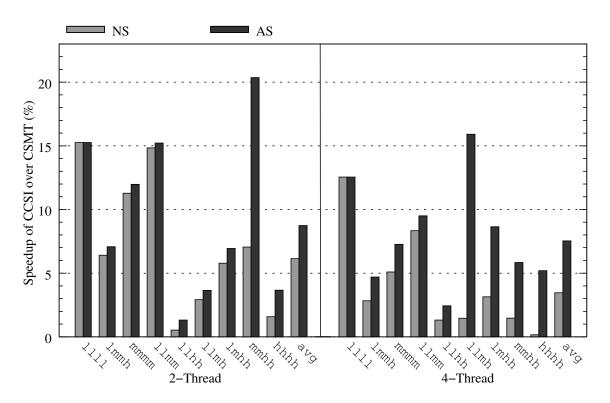

| 6.14 | Cluster-level split-issue (CCSI) speedups over CSMT 90                          |

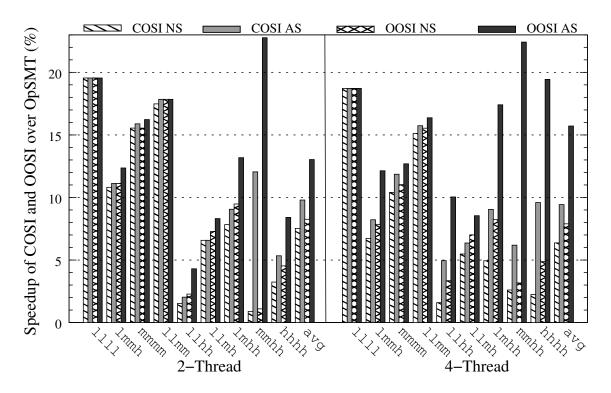

| 6.15 | Speedups obtained over OpSMT with cluster-level (COSI) and operation-           |

|      | level split-issue (OOSI)                                                        |

| 6.16 | Average Performance of all multithreading techniques                            |

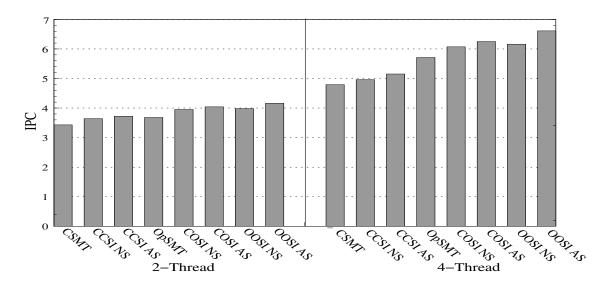

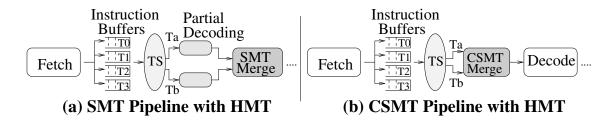

| 7.1  | A IDC for IMT COMT and Or CMT                                                   |

| 7.1  | Average IPC for IMT, CSMT and OpSMT                                             |

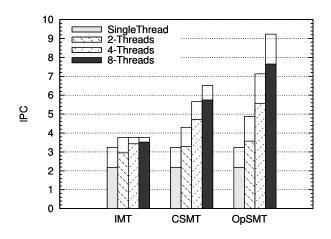

| 7.2  | HMT Pipeline                                                                    |

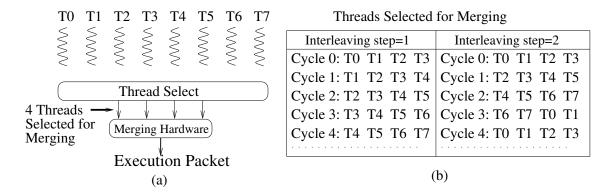

| 7.3  | Hybrid Multithreading Example                                                   |

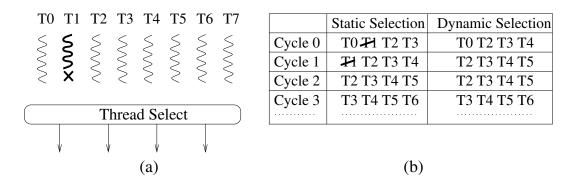

| 7.4  | Static vs Dynamic Thread Selection                                              |

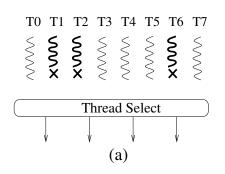

| 7.5  | Thread Selection Schemes                                                        |

| 7.6  | Static Thread Selection Hardware                                                |

| 7.7  | General Dynamic Thread Selection Hardware                                       |

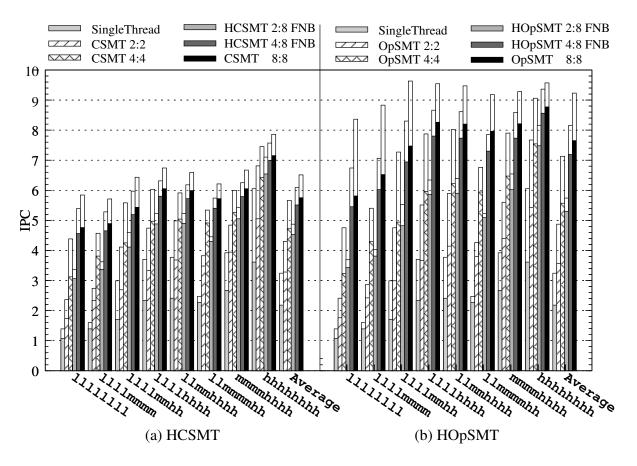

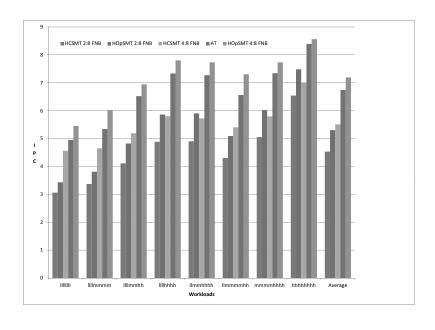

| 7.8  | IPC of the workloads for HMT with FNB policy                                    |

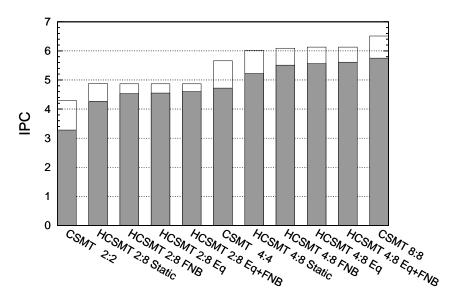

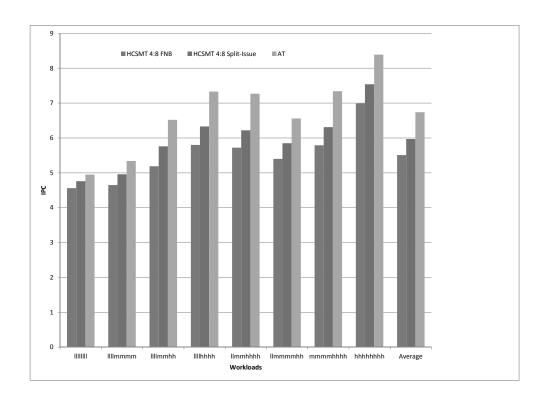

| 7.9  | Average Performance of Different Thread Selection Schemes for HC-               |

| 7.10 | SMT                                                                             |

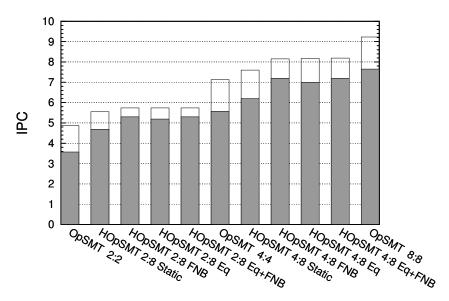

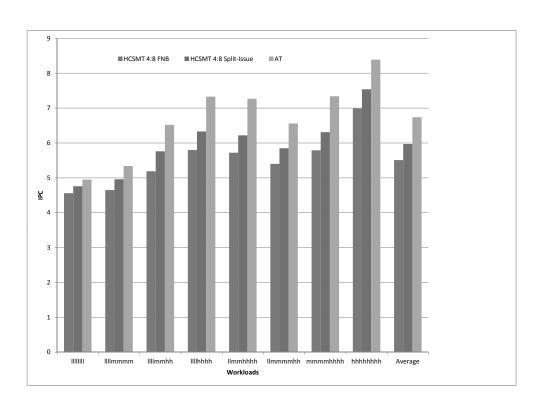

| 7.10 | <b>Average Performance of Different Thread Selection Schemes for HOpSMT</b> 107 |

| 8.1  | <b>All Schemes</b>                                                              |

| 8.2  | Merging Hardware                                                                |

| 8.3  | All Merging Example                                                             |

| 8.4  | Perfect memory Performance                                                      |

| 8.5  | Real memory Performance                                                         |

| 8.6  | Comparison with HCSMT with split-issue, Perfect Memory 116                      |

| 8.7  | Comparison with HCSMT with split-issue, Real Memory 117                         |

|      |                                                                                 |

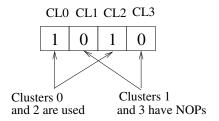

| A.1  | Example of Cluster Usage Vector 1010                                            |

#### LIST OF FIGURES

| A.2  | Thread merge hardware                               |

|------|-----------------------------------------------------|

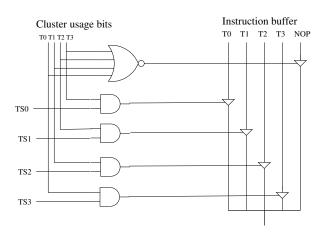

| A.3  | Bundle select logic (BS)                            |

| A.4  | Thread select logic (TS)                            |

| A.5  | Serial logic implementation for TS block            |

| A.6  | Thread select bit block (TSB)                       |

| A.7  | Usage vector computation block (UV)                 |

| A.8  | Parallel logic implementation for TS block          |

| A.9  | Validity computations for three thread combinations |

| A.10 | Transistor Count for CSMT                           |

| A.11 | Gate Delays for CSMT                                |

| B.1  | CSMT Thread merge hardware                          |

| B.2  | OpSMT Thread merge hardware                         |

| B.3  | OpSMT Serial Logic                                  |

| B.4  | <b>OpSMT Parallel Logic</b>                         |

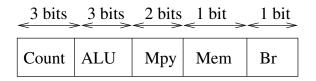

| B.5  | <b>OpSMT Resource Vector</b>                        |

| B.6  | <b>OpSMT Resource Routing</b>                       |

| B.7  | ALU/Operation Count Check                           |

| B.8  | Multiply Count Check                                |

| B.9  | <b>OpSMT Area</b>                                   |

| B.10 | OpSMT Gate Delays                                   |

# **List of Tables**

| 2.1 | Architectural configuration                | 27 |

|-----|--------------------------------------------|----|

| 2.2 | Benchmarks                                 | 29 |

| 2.3 | 4-Thread Workload configurations           | 29 |

| 2.4 | 8-Thread Workload configurations           | 29 |

| A.1 | Thread select bits for thread combinations | 36 |

# Chapter 1

## Introduction

Over the past decades, computers have made their way in all aspects of life and technology. Computers are present in a wide spectrum of products, not just personal computers or computing servers, ranging from handheld devices and digital electronics, automobiles to avionic systems, etc. There is an ever-growing need for higher computing power in any application domain. Processors are the computational brain and the core of any computing system. Hence it is imperative that techniques for improving the performance of processors continue being investigated.

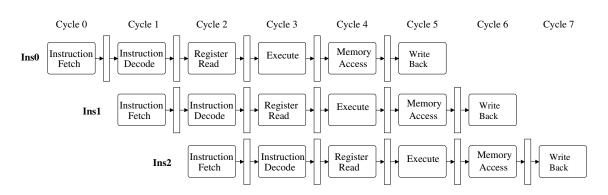

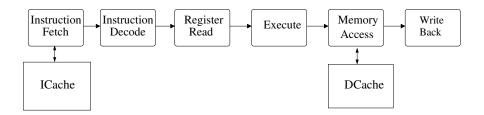

One of the most basic techniques to achieve higher performance is instruction pipelining [21]. Instruction Pipelining splits the execution of an instruction into several independent stages called pipeline stages. The output of each pipeline stage is connected to the input of next stage. Division into stages allows the processor to be clocked at a much higher clock speed that is limited only by the slowest pipeline stage. For instance, if the execution of an instruction is divided into p stages of equal delay, the processor with a clock frequency of f can now be theoretically clocked at a frequency  $p \times f$ . As a result, the runtime of a program with p instructions on a processor with p pipeline stages can be as low as p-times compared to an non-pipelined processor. Pipelining allows the processor to handle multiple instructions at the same time and reduces the overall exe-

Figure 1.1: A 6-stage pipeline

Figure 1.2: Execution on the 6-stage pipeline processor

cution time. Figure 1.1 shows a 6-stage pipeline viz. Instruction Fetch (IF), Instruction Decode (ID), Register Read (RR), Execute (EX), Memory Access (MA) and WriteBack (WB). The values passed from one pipeline stage to the next are placed in pipeline registers. Figure 1.2 shows instruction execution on the 6-stage pipelined processor already shown in Figure 1.1. In the execution shown in Figure 1.2, a new instruction is issued in the pipeline at every cycle. At cycle 0, instruction Ins0 is issued and enters the IF pipeline stage. At cycle 1, instruction Ins0 moves to ID pipeline stage and a new instruction Ins1 enters the IF pipeline stage, and so on. As there are six pipeline stages, up to six instructions are in-flight in the pipeline. Pipelining is a common feature in most current processors. For instance, Intel P5 microarchitecture (Pentium processor) had 5 pipeline stages (8 stages for floating point), Intel Prescott microarchitecture (Pentium 4 processor) had 31 pipeline stages, and the recently released Intel Atom Z500 processor had 16 pipeline stages. Note that while pipelining improves overall execution time of the program, the total time required to execute an individual instruction does not reduce by pipelining. In fact, individual instruction execution time worsens because:

- Dividing execution into pipeline stages of exactly equal delay is not possible.

- Pipeline registers required between the pipeline stages add to the total delay as well.

Note that for achieving peak performance, an instruction must be issued by the pipeline every cycle. However, to do so the new instruction must be independent of the instructions already in the pipeline i.e. the instruction should not depend on the results produced by the instructions in the pipeline. In the case that an independent instruction is not available, several cycles might be wasted before a new instruction can be inserted in the pipeline. Most processors employ a technique known as data forwarding to reduce the delays caused because of the data dependencies. Data forwarding requires a hardware logic known as bypass network and is discussed in greater detail later in this Chapter.

Ins0: add

$$\$r3 = \$r1, \$r2$$

Ins1: sub  $\$r5 = \$r7, \$r8$

Ins2: add  $\$r1 = \$r5, \$r3$  — Depends on Ins0 and Ins1

Figure 1.3: Data dependencies

So far, we have assumed that the processor can issue only one instruction at a given cycle. Many modern processors have multiple functional units and have the ability to execute multiple instructions concurrently. Executing multiple instructions at the same time can improve performance significantly. However, to execute multiple instructions simultaneously, no data dependencies must exist between the instructions. The code fragment shown in Figure 1.3 shows three consecutive instructions of a program. The first two instructions, Ins0 and Ins1, do not have any data dependencies. However, instruction Ins2 depends on the results generated by instructions Ins0 and Ins1. Therefore, instruction Ins2 can be executed only after both instructions Ins0 and Ins1 have finished their execution. If the processor has two functional units that can execute add and sub instructions, Ins0 and Ins1 can be executed in parallel and hence, execution can be completed in two cycles. On the other hand, a serial execution of the three instructions would have required three cycles. Thus, by executing independent instructions in parallel further improves processor performance. This phenomenon of exploiting parallelism at the instruction level for improving performance is commonly referred to as Instruction Level Parallelism (ILP). The number of instructions that the processor can issue at a given cycle is known as the issue width of the processor. The ability to extract the available ILP in an application is one of the keys to achieve higher performance in modern processors.

ILP can be extracted statically by the compiler or dynamically by the processor at runtime or using a combination of both. Superscalar processors e.g. Intel Pentium 4, IBM Power 5, etc. find independent instructions that can be issued simultaneously at runtime. To achieve high performance, superscalar processors typically employ out-of-order execution i.e. the instructions do not have to be executed in the program order but can start execution as soon as the input data is available (but commit in program order). For brevity, we would refer to superscalar out-of-order issue processors as superscalars in this chapter. In order to find independent instructions and accomplish out-of-order execution, superscalar processors require hardware structures like rename tables, issue queues, reorder buffers, etc. However, these structures have a high complexity, require large amount of

```

Ins0: add $r3 = $r1, $r2

VLIW0: add $r3 = $r1, $r2; sub $r5 = $r7, $r8

(Ins0 and Ins2 grouped as an unit)

VLIW1: add $r1 = $r3, $r7

Ins2: sub $r5 = $r7, $r8

VLIW1: add $r1 = $r3, $r7; add $r6 = $r8, $r3

Ins3: add $r6 = $r8, $r3

VLIW2: add $r7 = $r1, $r6

(a) Scalar code

(b) VLIW code

```

Figure 1.4: Scalar code vs VLIW code

transistors, and consume high energy and power. The complexity, power consumption and area requirements of these structures further increase significantly with the issue width of the processor [43]. Superscalar processors are popular in high performance desktop and server computing. However, superscalar processors with high issue width are not well suited for embedded systems, where low cost and low power is the prime requirement.

Embedded systems are widespread in current consumer electronics domain like Mobile phones, DVD players, Navigation devices etc. Traditionally, most embedded devices had a fixed set of applications and limited customizability. However, in recent times, there is a big rise in embedded devices that are highly customizable and have a big third-party application market rivaling personal computing e.g. smartphones like iphone, android based phones, etc. The application platform on many embedded devices is approaching desktop computing with a wide set of rich applications including a fully functional web platform. Embedded systems, in particular those that are battery operated, have a low power constrain. Besides, technology convergence like integration of audio, video, imaging, security, etc. demands even higher performance while keeping the low power constrain. Very Long Instruction Word (VLIW) processors is a popular approach to extract ILP and achieve high performance at a low power and design cost suitable for embedded domain. VLIW processors are explained in detail in the following section.

#### 1.1 VLIW Processors

VLIW processors exploit ILP by exposing the architecture details to the compiler, and ILP is extracted at compile time. The architecture details exposed to the compiler generally include the number of functional units of different types (ALU, multipliers, etc.) and their associated latencies, number of memory ports, the number of physical registers etc. In a VLIW processor, the compiler does the task of extracting the ILP in the program.

#### CHAPTER 1. INTRODUCTION

```

Cycle 0:

Ins0: add r3 = r1, r2

Cycle 0: Ins0: add $r3 = $r1, $r2; Ins2: sub $r5 = $r7, $r8

Cycle 1:

Ins1: add r1 = r3, r7

Cycle 1: Ins1: add $r1 = $r3, $r7; Ins3: add $r6 = $r8, $r3

Cycle 2: Ins2: sub r5 = r7, r8

Cycle 2: Ins4: add $r7 = $r1, $r6

Cycle 3:

Ins3: add r6 = r8, r3

Runtime parallelism detection

Cycle 4:

Ins4: add r7 = r1, r6

(a) In-order Execution

(b) Superscalar Execution

Cycle 0: VLIW0: add \$r3 = \$r1, \$r2; sub \$r5 = \$r7, \$r8

Cycle 1: VLIW1: add r1 = r3, r7; add r6 = r8, r3

Cycle 2: VLIW2: add r7 = r1, r6

Compile time parallelism detection

(c) VLIW Execution

```

Figure 1.5: Instruction execution on an in-order, Superscalar and VLIW Processor

The extracted ILP is specified to the hardware as a set of independent operations by the compiler forming a VLIW instruction. Operations, in the context of VLIW architectures, are the scalar instructions e.g. addition, multiplication etc. All the operations inside a VLIW instruction are issued as a unit by the hardware. Figures 1.4(a) and (b) show five scalar instructions Ins0-Ins4 and the corresponding VLIW code respectively. For the VLIW processor, the compiler identifies the parallelism among the instructions Ins0-Ins4. The identified independent scalar instructions are then grouped together by the compiler to form the VLIW instructions. For instance, the scalar instructions, Ins0 and Ins2, are grouped together as a single VLIW instruction, VLIW0, with two operations.

Next, Figure 1.5 shows the corresponding execution of the instructions shown in Figure 1.4 on an in-order single issue processor (Figure 1.5(a)), a superscalar (Figure 1.5(b)) and a VLIW processor (Figure 1.5(c)) respectively. Assuming that each instruction requires a single cycle to execute, the in-order processor takes five cycles to execute all the instructions. A superscalar out-of-order processor executes the same scalar code. However, the superscalar processor will identify the instructions that do not have any dependencies and execute them in parallel at runtime. For instance, instructions Ins0 and Ins2 (also Ins1 and Ins3) are independent and are executed in parallel. Thus, the execution will require only three cycles on a superscalar processor. The VLIW processor executes the compiler generated VLIW code i.e. instructions VLIW0-VLIW2 (not Ins0-Ins4) in-order. All operations in a VLIW instruction are executed simultaneously. Hence, the execution

Figure 1.6: VLIW vs Superscalar Pipeline

of the 3 VLIW instructions also takes three cycles on the VLIW processor but without requiring any runtime ILP identification hardware.

VLIW processors make no runtime instruction scheduling decisions and execute the compiler generated instructions in-order. Figures 1.6(a) and (b) show the execution pipelines for a VLIW and a superscalar processor respectively. The pipeline for the VLIW processor is similar to the pipeline already shown in Figure 1.2. For a VLIW architecture, the only difference is the presence of multiple pipelines to handle the execution of multiple operations. Superscalar processors, on the contrary, need extra pipeline stages and hardware to support out-of-order execution and ILP detection viz. register rename tables, issue queues, reorder buffers, etc. None of these hardware structures are required in VLIW architectures. This results in a significantly lower complexity, area and power requirements for VLIW processors as compared to superscalar processors. VLIW processors have been used in general purpose computing [8, 46, 24] but the issue of binary compatibility and difficulty to extract ILP in control intensive applications have limited their applicability. However, because of the low power, low cost and hardware simplicity advantages, VLIW processors have gained widespread popularity in most embedded computing realms [12, 49, 23] where binary compatibility is not critical. For instance, VLIW processors can be found in mobile phones, digital televisions, receivers and recorders, digital cameras, multifunction printers, etc. [15]. VLIW architecture is also commonly used in Graphics Processing Units (GPUs) [2], [40].

A VLIW execution model can be defined in terms of Unit Assumed Latency (UAL) or Non-Unit Assumed Latency (NUAL) depending on the architecturally visibility of the

(a) EQ Execution: Reusing register r1 (b) LEQ Execution: Reuse not possible

Figure 1.7: EQ and LEQ Execution

functional unit latencies. UAL execution semantics mimic a conventional sequential program by assuming each instruction has an unit latency (the compiler may be cognizant of the actual latencies for better scheduling but is not necessary). When the actual latency is greater than one, UAL model requires additional hardware mechanisms such as pipeline interlocking [21] to preserve the data dependencies in the instruction sequence. Starcore DSPs from Freescale [52] and Tigersharc processors from Analog Devices [55] use UAL execution model.

In the NUAL execution model, operations have architecturally visible non-unit latency. Operations may have different latencies, depending on the functional unit, and the compiler has to schedule the code while respecting the latency constraints. No interlocking hardware is required in a NUAL execution model. However, a program may have to be recompiled if there is any change in the functional units latencies in the NUAL execution model. On the other hand, no recompilation is required for UAL model. Many current VLIW processors use NUAL execution model [49, 23, 59]. NUAL execution model can be further subdivided into Equals (EQ) and Less-than-or-Equals (LEQ) execution models.

In EQ model, an operation accesses its operands at the specified time and writes back the result exactly at its latency time. On the other hand, in the LEQ model, the hardware can complete an operation in the same or fewer number of cycles than assumed by the compiler i.e. if the operation latency is L, the result is available between one and L cycles after executing the operation. Hence, any operation that uses the result must be scheduled after at least L cycles even if the actual latency is less than L. Figures 1.7(a) and (b) show an example of EQ and LEQ execution respectively. In the example mpy operation has a latency of 3 cycles and the rest have unit latencies. The EQ execution model assumes that result of mpy will be written to register r1 exactly after 3 cycles and can reuse the register

Figure 1.8: Register file bit cell

r1 in between. LEQ execution, on the other hand, assumes that execution may take less than 3 cycles and will not reuse register r1.

EQ model has the advantage of better register usage and better scheduling over LEQ because of the exact latency information usage. However, issues may occur when the control flow at runtime is different from the compile time assumptions. For instance, in events like exceptions, the control is transferred to the exception handling routine. This violates the assumed latency of the scheduled operations and may break the execution semantics. Hence, hardware support is required to save the status of the processor before executing exception handling code. LEQ model simplifies the implementation of runtime events like exceptions. Besides, LEQ model also offers a limited binary compatibility when the latency of some functional unit is reduced. EQ model, on the other hand, would require a recompilation of the program in case of any change in latencies. Note that recompilation is necessary for both LEQ and EQ models if other architectural assumptions like number of functional units, processor issue-width, register file specifications etc. are changed. TI C6 series VLIW DSPs from Texas Instruments [49] use EQ execution model while ST200 series VLIWs from ST [23] use LEQ execution model.

Figure 1.9: Bypass Network

#### 1.2 Scalability Issues in VLIW Processors

Many multimedia applications common in embedded domain exhibit significant amount of ILP, or at least regions with high ILP interleaved with low ILP regions. To exploit this ILP, VLIWs need to be designed with a significantly wide issue width, which is limited by the number of functional units (FUs). However, the number of FUs is limited by the scalability of the register file and the bypassing network.

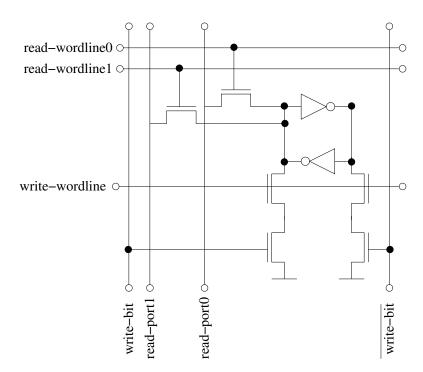

A register file is an array of the processor registers. The functional units of the processor read their inputs from the register file and write the produced results to the register file. Figure 1.8 shows a standard register file bit cell with two read ports and one write port. A bit cell requires one wordline for each port (either read or write), one bitline per read port, and two bitlines for each write port. Each port requires a new routing in both horizontal and vertical direction as shown in the Figure 1.8. Register file design is dominated by this routing and the area increase is proportional to the square of the number of ports. Besides, Register file access time grows linearly and the power consumption increase quadratically with the number of ports [47]. As the number of ports is proportional to the number of FUs which are proportional to the issue width, any increase in issue width results in a significant increase in area, delay and power consumption of the register file. For instance, a processor with an issue width of 4 requires 8 read ports and 4 write ports (assuming 2-input functional units). Doubling the issue width to 8 would result in a register file that has 4-times the area, 4-times more power consumption and 2-times the access time. Since register files already consume a significant processor area and power, and lie on the critical path, this limits any significant increase in the issue width.

The data bypassing network can impact processor area and cycle time in a similar way.

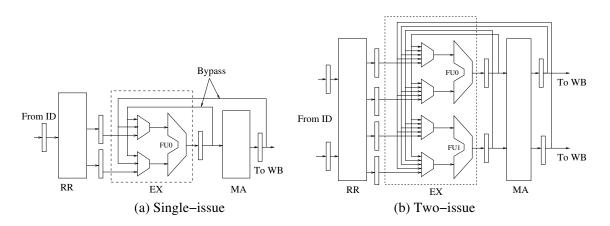

Data bypassing network is required to forward the values produced from the executed operations to the dependent operations in a processor pipeline. In the pipeline shown in Figure 1.2 consisting of 6 pipeline stages, IF, ID, RR, EX. MA, and WB, the result is generated at EX stage. However, the generated result is not written to the register file until the WB stage. In order to issue an instruction immediately after the currently executing instruction which may depend on the produced result, the results must be forwarded from the pipeline stages EX and MA as an input to all the functional units. Figures 1.9(a) and 1.9(b) show the bypass network required for the pipeline for a single-issue and processor with an issue width of two respectively. The bypass network has the following inputs: the values read from register file at RR stage, produced results at EX stage, and results at the MA pipeline stage. Assuming that each functional unit has 2 inputs, the total number of bypasses required is  $(2 \times I^2 \times S)$  where I is the issue width of the processor and S is the number of pipeline stages from execution to writing of the result of an instruction. The delay of the bypass network is given by  $T_{bypass} = 0.5 \times R_{metal} \times C_{metal} \times L^2$  where L is the length of the result wires, and  $R_{metal}$  and  $C_{metal}$  are the resistance and parasitic capacitance of metal wires per unit length respectively [43]. An increase in the issue width results in a linear increase in the length of the result wires, and hence, causes the bypass delay to grow quadratically with issue width. The quadratic increase of the bypass network in both area and delay with the issue width further impacts the scalability of the issue width of the processor. To scale the issue width in VLIWs, many semiconductor companies have adopted clustered VLIW approach as explained in the following section.

#### 1.3 Clustered VLIW Processors

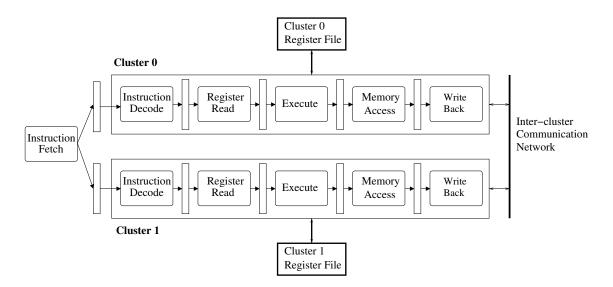

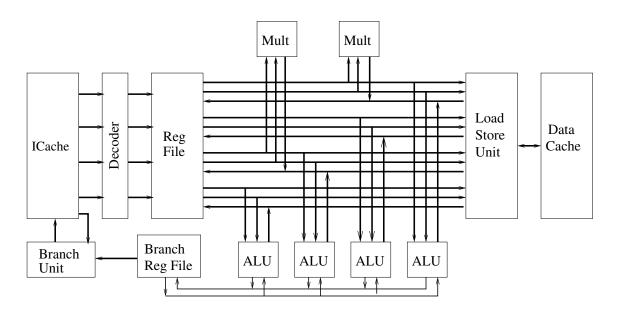

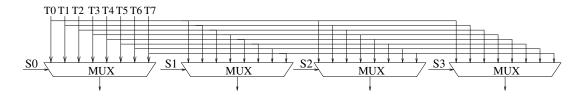

Clustered VLIW architectures tackle the issue of scalability by introducing more than one register file and clustering the FUs according to the register files they are connected to. Clustering allows higher levels of issue width than monolithic VLIW architectures, since register file ports and bypass network are determined by the issue width in a cluster. While issue width in a cluster can be kept low, the total issue width can be easily scaled by increasing the number of clusters. Higher issue width allows to achieve higher performance levels without scaling up the clock frequency, achieving a better power budget as well. Many VLIW processors have been designed using the clustered approach [23, 49, 59]. Figure 1.10 shows a sample 2-cluster VLIW processor pipeline. In the shown pipeline, the IF pipeline stage fetches the VLIW instruction and dispatches the operations to their

Figure 1.10: A 2-cluster VLIW Processor pipeline

destined clusters. The two clusters cannot access the register file of the other cluster and need to communicate through a separate intercluster communication network.

Implementation of clustering can either be architecturally invisible or can be exposed at the architectural level. When clustering is architecturally invisible, the compiler views the register file as a single monolithic unit. The hardware is responsible to create an impression of a non-clustered register file for preserving execution semantics. Architecturally invisible clustering is required if maintaining binary compatibility is important. Some VLIW processors like Sun MAJC 5200 [56] use invisible clustering.

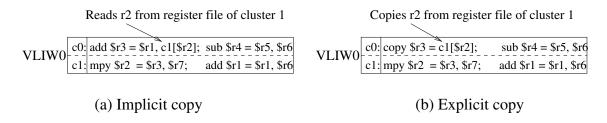

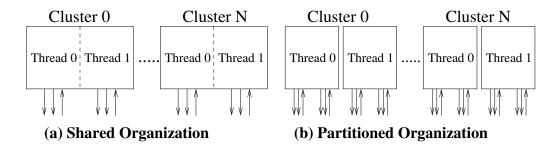

Exposing clustering at architectural level may break binary compatibility and requires a recompilation of the programs. However, on a positive note, compiler can take advantage of the clustering information to generate more efficient code. Architecturally visible clustering can be further subdivided into implicit-copying or explicit-copying depending on the intercluster communication specification in the instruction set. Implicit copying implies that an operation may read or write registers from a remote register file i.e. an operation can operate on a register belonging to the register file of a different cluster. TI C6x series [49] and NXP Trimedia VLIW processors [59] use implicit copying for intercluster communication.

Explicit copying requires explicit copy operations in the instruction set to move data across register file of different clusters. All other operations can operate only on the registers belonging to the local register file. ST200 series VLIW processors [23] are an example of explicit copy based clustering. Figures 1.11(a) and (b) show an example

Figure 1.11: Implicit and explicit copy

of implicit and explicit copy. In the case of implicit copy, the operation can directly use a register from the register file of the other cluster. For explicit copy, only copy operations are permitted to read registers from the register file of other cluster. Implicit copying requires extra bits in the operations encoding to address registers from other clusters. Besides, compiler has to model the intercluster communication details as well. Explicit copying, on the other hand, only requires addition of copy operations to the instruction set that are modeled like any other operations during scheduling. However, copy operations are issued using the standard issue slots, thus competing for issue slots with other operations. If the number of copy operations is significant, it results into a larger code size which may affect instruction cache performance. A detailed analysis of the intercluster communication models for clustered VLIW processors has been done in [53] and [17].

Performance of VLIW processors is closely coupled with efficient code generation from compiler. Modulo Scheduling (also commonly referred to as Software Pipelining) [44], [33], [35] is a popular compiler based to improve performance of VLIW procesors. Modulo Scheduling improves the ILP that can be exploited within loops in a program. With emerging popularity of clustered VLIW processors, modulo scheduling for clustered VLIW processors [48], [7], [65] is a popular research area.

#### 1.4 MultiThreading

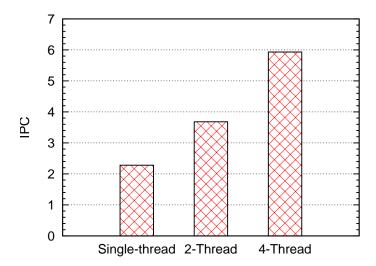

Some applications scale well with issue width. For instance, colorspace conversion [1] used in high performance printers has an average IPC (Instructions Per Cycle) of 3.9, 6.0 and 8.9 for an issue width of 4, 8 (2 clusters of 4) and 16 (4 clusters of 4) respectively, which makes a very high issue width processor desirable. However, the ILP exposed in many applications, or in some code regions, is limited and the processor is heavily under-utilized. Also, in a production environment, high ILP applications (like image processing)

coexist with low ILP applications (like control code or the OS itself). For instance, playing a DVD requires multiple threads for decryption (low ILP), video decoding (high ILP), audio decoding (medium ILP), etc. along with the operating system threads (low ILP).

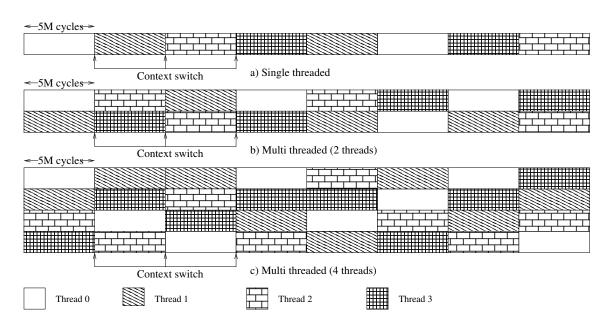

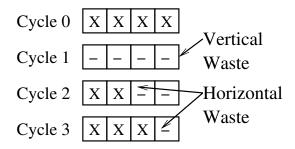

In the context of VLIW architectures, processor under-utilization can be described in terms of vertical and horizontal waste. Vertical waste are the cycles where no operations are issued at all. Horizontal waste is the under-utilization of the issue slots of the processor, i.e. number of operations issued in a cycle is less than the maximum number of operations that can be issued per cycle. Both vertical and horizontal waste arise because control and data dependencies in the program limit the number of operations that can be issued in a given cycle. Also, operations that have variable latency (for instance, memory operations) stall the processor if the actual latency is greater than the expected one, resulting in additional vertical waste. Multithreading is a popular approach for reducing the underutilization and improve processor performance. Multithreaded execution has received a lot of focus from researchers and many multithreading proposals exist in literature. An excellent survey on multithreaded processors can be found in [58].

Typically memory operations have the highest latency because of cache misses. Most initial multithreading proposals, therefore, were targeted to minimize vertical waste that arises due to memory latency cycles in a program as explained in the following lines.

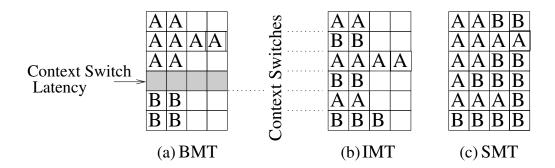

**Block MultiThreading** (BMT) [62, 39, 3] executes instructions from a single thread until it is blocked by a long latency event (a cache miss, for instance) [10, 13]. When that happens, a fast context switch gives control to a different thread so that most of the miss latency is hidden. However, a few vertical slots are still wasted due to context switch time. BMT has been used in several commercial processors [56, 6, 38].

Interleaved MultiThreading (IMT) [50, 4] does a zero cycle context switch every cycle, so that instructions from different threads are interleaved at execution time. Interleaved multithreading allows the removal of the bypass network and interlocking hardware, since control and data dependencies between the instructions in the pipeline are eliminated when the number of interleaved threads is greater or equal than the number of pipeline stages. However, doing so hinders single thread performance when only one thread is present. In order to hide cache misses, many threads are required. Moreover, it still does nothing to remove horizontal waste. A trivial modification consists of marking as blocked any thread that produces a cache miss and issuing instructions only from non-blocked threads. This modification achieves the best from both block and interleaved multithreading. In this paper, we use this variant of IMT for our evaluations. IMT has

Figure 1.12: Comparison of Multithreading Schemes

also been used in several commercial designs [50, 54, 27, 4].

Both, block and interleaved multithreading can reduce vertical waste by issuing instructions from different threads, but not horizontal waste.

Simultaneous MultiThreading (SMT) [57] reduces both the horizontal and vertical waste inside a processor. It issues multiple instructions from multiple threads each cycle. In contrast, BMT and IMT issue instructions from only one thread at a time. In a SMT processor, issue-slots are filled by operations of different threads, converting Thread Level Parallelism (TLP) into ILP. Also, latencies occurring in execution of single threads are hidden by issuing operations from other threads. As a SMT processor simultaneously exploits coarse and fine grain ILP, the resource usage is much more efficient than BMT or IMT. It relies on dynamic issue of instructions from different threads, and fits naturally with out-of-order superscalar processors. Hence, a SMT capability can be added to a conventional superscalar with little effort. SMT has found its use in several commercial superscalar processors [28, 31].

A comparison of the different multithreading approaches viz. BMT, IMT and SMT is shown in figures 5.6(a), 5.6(b) and 5.6(c) respectively for two threads A and B on a 4-issue VLIW processor. In the figures, each box in a row represents an issue slot. A box with a label indicates that the slot is in use by that particular thread and an empty box represents an unused issue slot. BMT and IMT can reduce vertical waste by issuing instructions from different threads, but not horizontal waste. In BMT, a few vertical slots are still wasted due to context switch time. Since IMT also reduces short stalls, IMT performance, in general, is a good upper bound for BMT as well. In contrast to BMT and IMT, SMT also removes horizontal waste in the processor. Next, we discuss several multithreading proposals targeted towards VLIW processors specifically.

**Kaxiras et al** [29] propose a SMT VLIW extension for StarCore (SC140) VLIW DSP, wherein the issue logic selects VLIW instruction packets from ready threads as many as

it can accommodate, and assigns them to functional units. They show that, for media applications, implementing SMT is a better option than Chip MultiProcessing.

**Iyer et al** [26] also implement SMT on a NUAL TI DSP processor. The focus of the study, however, is binary compatibility. They propose split issue to extend a previously proposed dynamic scheduling technique [45], and then show that split issue can be used to implement rigorous changes to processor hardware (changes which break program semantics in a VLIW, like changing number of functional units, changing operation latencies, implementing SMT, etc.) while maintaining binary compatibility. An analysis of the hardware required to implement SMT is lacking, however.

**Balanced MultiThreading** is a related multithreading technique proposed for high end out-of-order superscalar processors. Balanced multithreading combines the SMT ability with Block MultiThreading. To do so, extra thread contexts are stored in a special storage location on-chip. If a running thread encounters a L2 cache miss, it is swapped with one of the extra contexts. Use of balanced multithreading saves the register file space requirement for the extra thread contexts but several cycles are required for context swapping.

**Subset Static Interleaved Multithreading** (SSIMT) is a technique similar to Balanced MultiThreading. SSIMT combines Block MultiThreading with IMT for embedded VLIW Processors. SSIMT maintains several background thread contexts on-chip. The background threads are swapped with a running thread if that thread encounters a cache miss at a low swapping penalty.

Another class of multithreading proposals are addressed to increase the performance of a sequential program [51, 37]. These rely on extracting and spawning multiple threads from the same program (a thread here means any contiguous instruction stream, not just OS threads), which are executed in parallel, thereby improving the performance of the sequential program. The threads can be computation slices of the program or simply helper threads which do some tasks like prefetching or improving branch prediction. Threads are obtained at runtime with or without compiler support. Since our focus is on VLIW processors, we restrict to following proposals.

**Processor coupling** [30] statically schedules multiple threads and, at runtime, interleaves them into execution clusters, consisting of a set of FUs and a common register file. Threads are generated by the compiler through explicit fork and forall operations, communicate through registers and memory and are non speculative. **M-Machine** [14] uses processor coupling as the execution model. In M-Machine either complete VLIW

instructions are issued from a single thread or short instructions are issued from multiple compiler generated threads by executing each thread in a different cluster. In the latter case, threads have been compiled to use only a single cluster.

XIMD [63] also statically schedules multiple threads, but does not perform a runtime interleaving. It has multiple functional units and a large global register file. Each functional unit has a dedicated instruction sequencer to fetch instructions. A program is partitioned into several threads by the compiler or by a specialized partitioning tool. The XIMD compiler takes each thread and schedules it separately. Threads are then statically merged to increase static code density or to optimize the execution time. No speculative threads are allowed in XIMD.

Weld [42] architecture is aimed at increasing single program performance using compiler generated (speculative) threads in a multithreaded VLIW architecture. Weld architecture has the limited capability to issue each operation in a VLIW instruction separately. According to dependencies among issue packets, the compiler adds and sets a separability bit for each operation in the opcode. The hardware looks up this bit to decide whether it can issue an operation separately or not. The Weld architecture selects VLIW instructions from ready threads and issues them to available functional units. The design of the general Weld architecture involves extensive changes to the ISA, compiler support for effective generation of multiple threads, and additional hardware resources such as buffers for speculative load and store instructions, a thread synchronization hardware, and a complex operation welder. Operation welder dynamically fills issue slots from multiple threads to enable multithreading. The welder is implemented as a crossbar and because of the complex hardware, scalability is limited beyond two threads for cost/performance reasons [41].

**Barretta et al** [5] discuss a multithreaded extension to multi-cluster VLIW. The processor has two modes: single threaded and multithreaded. In single threaded mode, VLIW instructions are issued from a single thread that has been compiled to make use of all the clusters. In multithreaded mode, short VLIW instructions are issued from multiple threads (part of the same program) by executing each thread in a different cluster. In the latter mode, threads have been compiled to use a single cluster. Switching between modes is also compiler (or programmer) controlled. This approach does nothing to avoid vertical waste due to cache misses and cannot exploit TLP between different applications.

#### 1.5 Contributions of the Thesis

We note that very few multithreading proposals exist targeting clustered VLIW processors. Besides, the emphasis of those [5], however, is to improve the performance of a single program, using multithreading in a very limited way (each thread executes in a different cluster rather than using full system resources). For a VLIW processor, Block MultiThreading (BMT) and Interleaved MultiThreading (IMT) can reduce vertical waste by issuing instructions from different threads, but not horizontal waste. Simultaneous MultiThreading (SMT) removes horizontal waste as well. However, implementing SMT on VLIWs require complex structures making it unsuitable due to cost/area constraints. Also, proposals which study SMT on VLIW with an emphasis on hardware implementation [41] limit scalability of SMT to 2 threads.

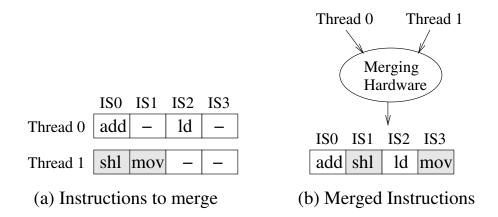

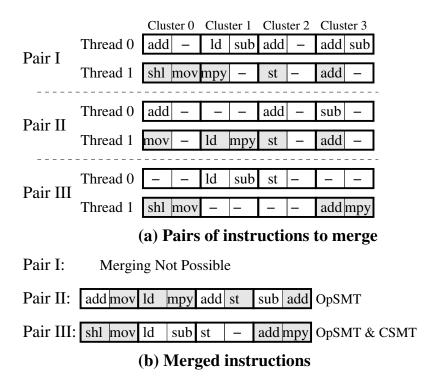

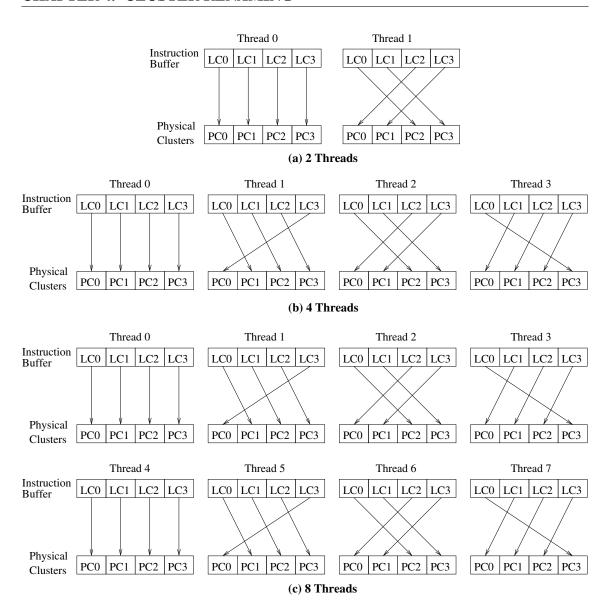

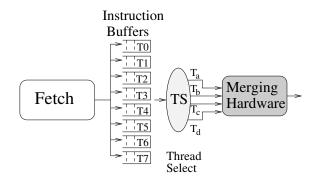

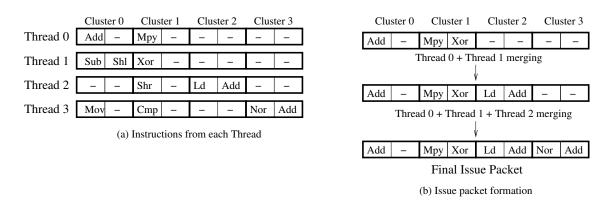

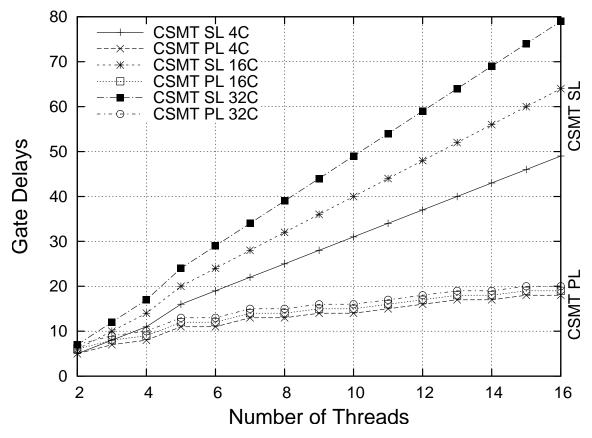

There is a considerable performance difference between IMT and SMT because of the ability of SMT to remove horizontal waste but at a higher hardware cost. Our first approach, named **Cluster-level Simultaneous MultiThreading** (CSMT) and discussed in Chapter 3, exploits Thread Level Parallelism (TLP) at the cluster level achieving a performance in between IMT and SMT. CSMT issues simultaneously VLIW instructions from multiple threads only if they use different clusters. In other words, CSMT uses a coarse grain merging at cluster level whereas SMT does a fine grain merging at the operation level. For clarity and to avoid confusion, we refer to SMT (merging at operation-level) as OpSMT henceforth. CSMT is transparent to the compiler and can be used either with compiler generated threads or with threads belonging to different applications. An analysis of hardware required to implement CSMT shows that the hardware overhead of CSMT is small and is comparable to low complexity multithreading schemes like IMT. Besides, CSMT is more scalable than OpSMT in terms of both gate delays and area overhead with increasing number of threads.

We also propose a technique named Cluster Renaming, discussed in details in Chapter 4, to further improve multithreading performance. Cluster renaming reduces cluster conflicts when several threads require the same cluster by mapping logical clusters, belonging to different threads, to different physical clusters. Cluster renaming has a low implementation overhead and is equally applicable to other multithreading techniques like OpSMT as well. Using CSMT and cluster renaming together, a significant amount of horizontal waste is removed and the obtained performance is close to OpSMT performance.

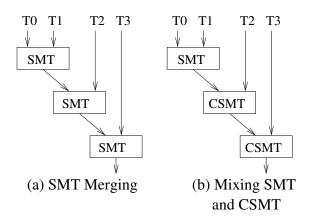

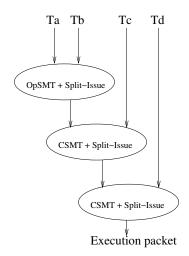

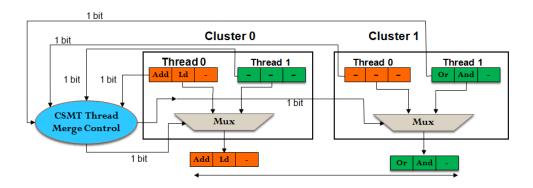

The cost of the merging hardware dictates the number of threads that can be merged

at a given cycle. However, the cost of merging hardware for CSMT is negligible when compared to OpSMT. Hence, for an OpSMT architecture, if extra threads are supported using CSMT, the additional cost incurred by the merging hardware is little. Our another proposal, explained in Chapter 5, is a heterogeneous merging approach that combines OpSMT and CSMT merging hardware. This approach supports more hardware threads than that can be supported using OpSMT merging hardware alone. For instance, while OpSMT can support only two threads, four threads can be supported by the heterogeneous merging approach where the first two threads are merged using OpSMT, and the result and the rest of threads are merged using CSMT approach. The final cost of the merging hardware for four threads is practically the same as the 2-thread OpSMT merging hardware cost. Hence, this approach allows higher performance without increasing merging hardware cost.

Operations in a VLIW instruction execute in a lock-step mode and hence, a VLIW instruction has to be issued in its entirety to honor execution semantics. The restriction to issue a VLIW instruction in entirety limits the number of instructions that can be issued simultaneously from different threads. For instance, on a 2-thead 3-issue VLIW architecture with 1 memory unit and 2 ALU units, if at a given cycle, the instructions of both threads require 1 memory unit and 1 ALU unit, then VLIW instruction from only one thread can be issued at that cycle. The remaining ALU unit cannot be used even though the other thread has ALU operations. Split-issue removes this restriction and allows a VLIW instruction to be issued in parts. Using split-issue improves resource usage efficiency and multithreading performance as it creates more opportunities for a VLIW instruction to be merged with VLIW instructions from other threads. A previously proposed technique, operation-level split-issue [26] does a split at the operation-level. However, doing a split at operation-level requires complex hardware for preserving execution semantics. Our proposal, cluster-level split-issue discussed in chapter 6, improves both OpSMT and CSMT performance at a very low hardware overhead while achieving performance close to operation-level split-issue.

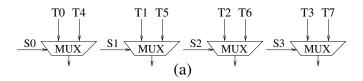

Both CSMT and OpSMT require a merging hardware to do resource constraints checking and combining instructions from different threads. The cost of the merging hardware increases significantly with an increase in number of threads and limits the number of threads can be merged at a given cycle. We propose Hybrid Multithreading (HMT) discussed in detail in Chapter 7, that allows supporting a high number of threads without affecting merging hardware cost. HMT tries to combine instructions from only a subset

of hardware threads every cycle. A different subset is used every cycle permitting all threads to make progress. HMT allows supporting more hardware threads and improves multithreading performance without impacting merging hardware cost.

## 1.6 Thesis Organization

The rest of the thesis is organized as follows: Chapter 2 discusses the basic infrastructure that includes VEX VLIW architecture and the compiler toolchain, simulation platform etc. used for evaluating the ideas proposed in the thesis. Chapter 3 focuses on CSMT, and its performance and hardware cost evaluation vs OpSMT. Detailed evaluation of OpSMT and CSMT hardware is discussed in the appendices. Cluster Renaming and its performance impact on CSMT and OpSMT is discussed in Chapter 4. Chapter 5 discusses the heterogeneous merging schemes where both CSMT and SMT are used simultaneously to improve multithreading performance. Cluster-level Split-Issue and its comparison with previous techniques is discussed in Chapter 6. Chapter 7 discusses Hybrid MultiThreading, a technique to support more hardware threads than the number of threads supported by merging hardware. Chapter 8 discusses the performance improvements achieved when all heterogeneous merging, hybrid multithreading and split-issue are combined. Finally, Chapter 9 concludes the thesis.

# Chapter 2

# **Experimental Platform**

In this chapter, we present the experimental infrastructure used to evaluate the proposals of the thesis. We describe the VEX VLIW architecture, the VEX toolchain, and the used benchmarks and workloads. We also discuss the experimental methodology used for evaluating multithreaded applications and the microarchitectural changes and requirements in the baseline VEX architecture for multithreading.

#### 2.1 VEX Architecture

VEX clustered architecture [61] forms the basis of the experimental work done in this thesis. VEX architecture is modeled upon the commercial 32-bit Lx/ST200 VLIW family [12] jointly developed by Hewlett-Packard (HP) and STMicroelectronics (STM). The ST200 VLIW processor family is targeted towards embedded media processing and STM has shipped in excess of 70 million of these VLIW processors.

VEX uses the following terminology for the VLIW instructions: an operation is the basic execution unit, the collection of operations scheduled to execute in the same cluster form a bundle and the collection of bundles scheduled to execute together is called an instruction<sup>1</sup>. The VLIW instructions are issued in-order. All the operations in a given VLIW instruction execute together in a lockstep mode at the same cycle. Also, within an instruction all operands are read before the results are written. In other words, if an operation reads a register r and another operation writes to the same register r within the same VLIW instruction, the read uses the old value of the register r and not the newer value generated by the writing operation. As a result, certain actions like swapping the values of a pair of registers are possible to perform in a single instruction. The architecture

<sup>&</sup>lt;sup>1</sup>Using the same terminology as the Lx architecture. In IA-64 terminology, an IA-64 instruction refers to a Lx operation and an IA-64 bundle refers to a Lx instruction

```

c0: add $r1= $r1, $r4; mpy $r4= $r2, 4;

c1: add $r5= $r2, $r7; xor $r9= $r1, $r8; sub $r11= $r15, $r7; mpy $r10= $r9, $r6;

c2: cmp $r4= $r10, $r5; nor $r6= $r11, $r7;

c3: add $r9= $r11, $r2;

```

#### Instruction Cluster 0 Cluster 1 Cluster 2 Cluster 3 1 Add 0 0 Mpy 0 1 Add 0 0 Xor 0 0 Sub 0 0 Mpy 0 1 Cmp 0 0 Nor 0 1 Add Bundle Instruction-stop Bit Cluster-start Bit Operation

(b) Instruction Encoding

Figure 2.1: Example of a VEX Instruction

also supports partial predication in the form of conditional select operations in order to eliminate some conditional branches. All the functional units are assumed to be fully pipelined. Clusters in VEX are architecturally visible and requires the compiler to take clustering and inter-cluster communication into account.

VEX uses a variable length instruction encoding to avoid wasting memory. To do so, the following two bits are reserved in every operation for sequencing and cluster encoding.

- **Instruction-stop bit:** indicates the end of a VLIW instruction.

- **Bundle-start bit:** indicates the beginning of a new bundle i.e. the current operation and the following operations are scheduled to execute in the next cluster forming a new bundle.

When the instruction-stop bit is set to '1', the current instruction is finished and the following operations belong to the next VLIW instruction. When the bundle-start bit is set to '1', the current operation and the following ones are scheduled in the next cluster starting a new bundle. For a 4-cluster implementation, an instruction can have a maximum of 4 bundle-start bits set to '1', and only the last operation of the instruction has the instruction-stop bit set to '1'. The numbering of the clusters starts from 0. In a 4-issue cluster, a bundle may contain 1 to 4 operations. An empty cluster can be encoded as an unit operation bundle with nop as the only operation. Note that encoding an empty cluster is required only if the instruction uses a higher cluster number. For instance, if an instruction uses cluster 0 and cluster 2, cluster 1 needs to be encoded but cluster 3 does

```

1. c0: cmpne $br1 = $r1, $r8; 	Sets branch register

2. c0: br $br1, L1; 	Branch to L1 if br1 is set

```

Figure 2.2: **Branching in VEX**

not have to be encoded as the last operation in cluster 2 will have the instruction-stop bit set. Figure 2.1(a) shows a sample VEX instruction that uses 4-clusters and Figure 2.1(b) shows the corresponding encoding of the operations in the instruction. Note that in VEX instruction encoding, operations do not have to be encoded in any fixed order within a bundle. For instance, operations add and mpy that are scheduled in cluster 0 in Figure 2.1, can be encoded in any order i.e. add can be encoded either before or after mpy. The hardware is responsible for dispatching operations to the appropriate functional units.

VEX follows the Non-Unit Assumed Latencies (NUAL) and Less-than-or-EQual (LEQ) VLIW execution model i.e. the functional unit latencies are exposed to the compiler and the hardware can complete an operation in the same or fewer cycles. The compiler is responsible for generating the correctly scheduled code eliminating the requirement for any interlocking hardware. The only exception to LEQ model is the memory accesses that may take longer than the assumed latency for reasons like cache misses. Whenever such a scenario arise, the execution is stalled until the architectural assumptions hold true.

VEX has two register files at each cluster, a general purpose register file and a branch register file. All operations operate on integer values and can access registers from only local register files i.e. an operation scheduled in cluster C can read and modify the registers that belong to the branch and general purpose register files of cluster C only. The only exception is the branch operation, which can read branch registers from the branch register file of the other clusters. Conditional branches in VEX are two phased: the first operation does the comparison and sets the branch register ahead of the actual branch, and the second is the actual control flow changing branch operation. Figure 2.2 shows an example of the branching in VEX where the first instruction cmpne sets the branch register. The later branch instruction br jumps to the specified location (L1) if the branch register \$br1 is set.

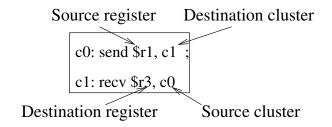

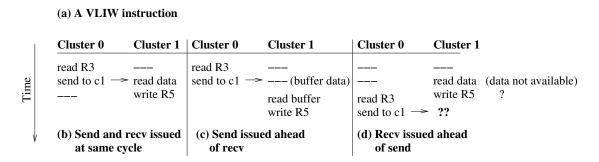

The inter-cluster communication in VEX is handled using explicit copy operations. The copies are implemented as a pair of send and recv operations that execute simultaneously in the source and destination clusters. Send operation specifies the destination cluster and a source register in the local register file and sends the value of the register to the specified cluster over the inter-cluster communication network. The corresponding

Figure 2.3: Inter-cluster communication in VEX

Figure 2.4: Simulation flow

recv operation retrieves the data from the specified source cluster and stores it in the specified destination register in the local cluster. Both send and recv have to be scheduled in the same VLIW instruction but in different bundles. Figure 2.3 shows a VLIW instruction that copies register r1 of cluster 0 to register r3 of cluster 1.

#### 2.2 VEX Toolchain

VEX toolchain consists of the VEX C compiler and a set of extra tools for performance evaluation, simulation and debugging. VEX allows changing various architectural parameters like issue width, number of clusters, composition of the clusters, etc. The VEX C compiler [61] is a derivative of the HP/ST ST200 C compiler, which itself is a derivative of the Multiflow compiler [36] that uses *Trace Scheduling* [16] as global scheduling algorithm and *Bottom Up Greedy* [11] as cluster assignment algorithm.

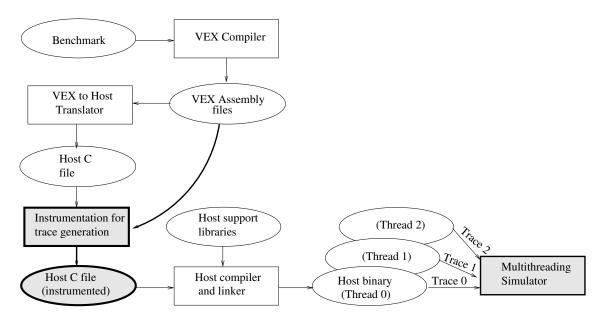

The VEX development toolchain uses a compiled simulation technique to run the programs developed for the VEX architecture on the host system by translating the VEX code to the binary of the host computer. This translation is done by first converting the generated VEX assembly code to C. The generated C files are then compiled with the host platform C compiler (e.g. gcc) and linked with the support libraries to generate a host binary. The compiler can be instructed to add profiling code to generate timing and cache profile statistics when the generated host binary is run. The statistics, however, is useful for a single-thread configuration only. Also, the toolchain is not capable of simulating a multithreaded processor. The following section discusses the methodology and the baseline architecture configuration used for evaluating multithreading performance.

## 2.3 Simulating a MultiThreaded Processor

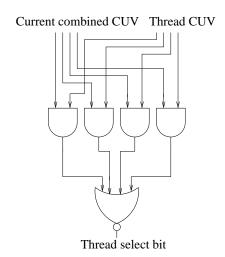

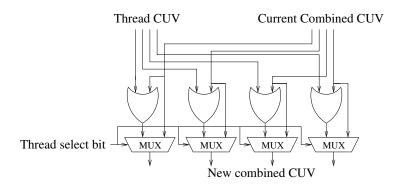

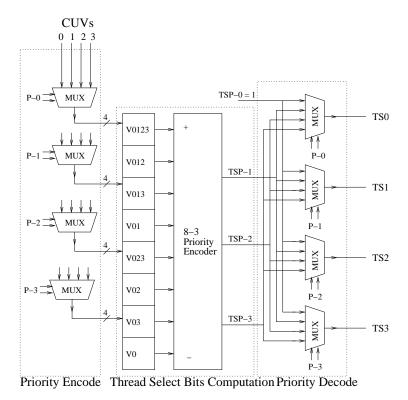

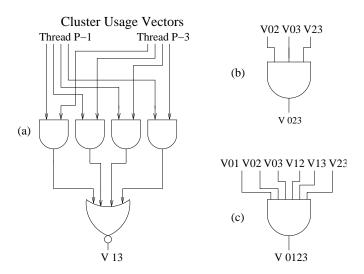

For a cycle accurate simulation with support for multithreading, we have developed a trace based simulator for the VEX microarchitecture. For generating trace information, we instrument the host C files generated by the translator to emit the program trace during the host binary execution. The trace includes the VLIW instructions that are executed and the memory addresses accessed for instruction cache and data cache. The trace information is fed to our simulator to simulate a multithreaded VLIW processor. Figure 2.4 shows the steps involved for obtaining the simulation results. The shaded parts in the figure are the extra steps that we have added for our experimental framework.