# TECHNICAL UNIVERSITY OF CATALONIA (UPC) DEPARTMENT OF SOFTWARE

### Ph.D. Dissertation

## Automatic Synthesis and Optimization of Chip Multiprocessors

Nikita Nikitin

Advisor: Prof. Jordi Cortadella

### Abstract

The microprocessor technology has experienced an enormous growth during the last decades. Rapid downscale of the CMOS technology has led to higher operating frequencies and performance densities, facing the fundamental issue of power dissipation. Chip Multiprocessors (CMPs) have become the latest paradigm to improve the power-performance efficiency of computing systems by exploiting the parallelism inherent in applications. Industrial and prototype implementations have already demonstrated the benefits achieved by CMPs with hundreds of cores.

CMP architects are challenged to take many complex design decisions. Only a few of them are:

- What should be the ratio between the core and cache areas on a chip?

- Which core architectures to select?

- How many cache levels should the memory subsystem have?

- Which interconnect topologies provide efficient on-chip communication?

These and many other aspects create a complex multidimensional space for architectural exploration. Design Automation tools become essential to make the architectural exploration feasible under the hard time-to-market constraints. The exploration methods have to be efficient and scalable to handle future generation on-chip architectures with hundreds or thousands of cores.

Furthermore, once a CMP has been fabricated, the need for efficient deployment of the many-core processor arises. Intelligent techniques for task mapping and scheduling onto CMPs are necessary to guarantee the full usage of the benefits brought by the many-core technology. These techniques have to consider the peculiarities of the modern architectures, such as availability of enhanced power saving techniques and presence of complex memory hierarchies.

This thesis has several objectives. The first objective is to elaborate the methods for efficient analytical modeling and architectural design space exploration of CMPs. The efficiency is achieved by using analytical models instead of simulation, and replacing the exhaustive exploration with an intelligent search strategy. Additionally, these methods incorporate high-level models for physical planning. The related contributions are described in Chapters 3, 4 and 5 of the document.

The second objective of this work is to propose a scalable task mapping algorithm onto general-purpose CMPs with power management techniques, for efficient deployment of many-core systems. This contribution is explained in Chapter 6 of this document.

Finally, the third objective of this thesis is to address the issues of the on-chip interconnect design and exploration, by developing a model for simultaneous topology customization and deadlock-free routing in Networks-on-Chip. The developed methodology can be applied to various classes of the on-chip systems, ranging from general-purpose chip multiprocessors to application-specific solutions. Chapter 7 describes the proposed model.

The presented methods have been thoroughly tested experimentally and the results are described in this dissertation. At the end of the document several possible directions for the future research are proposed.

## Acknowledgments

First of all, I would like to express gratitude to my Ph.D. advisor Prof. Jordi Cortadella for this unique opportunity to work on the thesis in the wonderful city of Barcelona, within a team of talented, open-minded and especially friendly colleagues. These have been great years of experience and unrivaled memories!

A special, sincere and warm Thanks to my family. To my Mom and Dad, grandmas and aunt who were always there to *listen*, share and support my endeavors. To my sister Lialya, eager to exchange the thoughts and feelings, good news and useful lessons learned. To Kate who changed my world with a blink of an eye. I love you all.

I would like to acknowledge and thank Prof. Valery Perekatov who noticed my abilities in research and convinced me this would be a worth path to follow. I am also very thankful to Prof. Alexander Marchenko who assisted me in gaining first industrial experience, which essentially contributed to my skills.

Another very special gratitude is to Dima Bufistov, Gladys Utrera and Josep Carmona, who became my friends almost as soon as I landed in Barcelona for the first time, guided me though the very first steps in Spain and kept assisting all these years. And my gratitude to Marc Galceran who has been an excellent guide during my first US trip. Thank you all so much!

A big thanks for sharing the amazing time together and helping with great ideas to all colleagues from UPC and Intel Corporation, especially to Javier de San Pedro, Cesc Guim, Mike Kishinevsky, Umit Ogras, Jordi Petit and Sat Chatterjee.

This time would not had been so exciting without all of you guys, who I met in the office S108 of Edifici  $\Omega$ . An astonishing team of the office mates with a great sense of humor and excellent problem solving capabilities (I'll never forget our puzzling activities at the whiteboard) is who I was awarded with for the thesis years.

Finally, this page would be incomplete without acknowledging the effort of all people at UPC who make the life of (international) students easier, and in particular, Mercè Juan Badia, Maria Serna and Anna Fàbregas. Thank you!

This work has been supported by a scholarship from Spanish Ministry of Science and Innovation (FPI grant BES-2008-004612), a gift from Intel Corporation and research project FORMALISM (CICYT TIN2007-66523).

## Contents

| 1        | Introduction |                                                    |    |  |  |

|----------|--------------|----------------------------------------------------|----|--|--|

|          | 1.1          | Design challenges for CMPs and NoCs                | 4  |  |  |

|          | 1.2          | Motivation and contributions                       | 7  |  |  |

|          | 1.3          | Document organization                              | 11 |  |  |

| <b>2</b> | $Th\epsilon$ | e Architecture of Chip Multiprocessors             | 13 |  |  |

|          | 2.1          | Processing cores                                   | 14 |  |  |

|          | 2.2          | Memory subsystem                                   | 16 |  |  |

|          | 2.3          | On-chip interconnects                              | 18 |  |  |

|          | 2.4          | Networks-on-Chip                                   | 21 |  |  |

|          | 2.5          | Related work                                       | 32 |  |  |

| 3        | Mo           | deling Networks with Constant Service-Time Routers | 41 |  |  |

|          | 3.1          | Model overview                                     | 42 |  |  |

|          | 3.2          | Queueing model                                     | 44 |  |  |

|          | 3.3          | Network model                                      | 50 |  |  |

|          | 3.4          | Experimental results                               | 52 |  |  |

|          | 3.5          | Conclusions                                        | 57 |  |  |

| 4        | Ana          | alytical Modeling of CMP Architectures             | 59 |  |  |

|          | 4.1          | The importance of contention: an example           | 59 |  |  |

|          | 4.2          | Analytical performance model                       | 61 |  |  |

|          | 4.3          | Analytical methods for latency estimation          |    |  |  |

|          | 4.4          | Extensions of the model                            |    |  |  |

|          | 4.5          | Experimental results                               | 72 |  |  |

|          | 4.6          | Conclusions                                        | 78 |  |  |

| 5                         | $Me^{i}$                                           | taheuristics for Architectural Exploration | 81  |  |

|---------------------------|----------------------------------------------------|--------------------------------------------|-----|--|

|                           | 5.1                                                | The Exploration Problem                    | 81  |  |

|                           | 5.2                                                | Transformations                            | 84  |  |

|                           | 5.3                                                | Exploration with Simulated Annealing       | 87  |  |

|                           | 5.4                                                | Exploration with Extremal Optimization     | 89  |  |

|                           | 5.5                                                | Experimental results                       | 90  |  |

|                           | 5.6                                                | Conclusions                                | 97  |  |

| 6                         | Static Task Mapping for Tiled Chip Multiprocessors |                                            |     |  |

|                           | 6.1                                                | An example of the mapping problem          | 100 |  |

|                           | 6.2                                                | A mathematical model                       | 102 |  |

|                           | 6.3                                                | Mapping by metaheuristics                  | 109 |  |

|                           | 6.4                                                | Experimental results                       | 114 |  |

|                           | 6.5                                                | Conclusions                                | 120 |  |

| 7                         | Lin                                                | k Allocation for NoC Topologies            | 123 |  |

|                           | 7.1                                                | Model overview                             | 124 |  |

|                           | 7.2                                                | The integer programming model              | 126 |  |

|                           | 7.3                                                | Experimental results                       | 137 |  |

|                           | 7.4                                                | Conclusions                                | 144 |  |

| 8                         | Conclusions and Future Work                        |                                            |     |  |

| $\mathbf{B}_{\mathbf{i}}$ | bliog                                              | graphy                                     | 148 |  |

## Chapter 1

## Introduction

The performance of microprocessors has improved drastically in the last few decades. For many years, the increase in operating frequencies, driven by the rapid downscale of the CMOS technology, has served the primary source for performance improvement of computing systems.

Several important architectural decisions have been introduced, which now represent widely adopted paradigms for microprocessor design [64]. Instruction pipelining is a technique used to increase the system throughput and fully exploit the benefits of the high clock rates. Superscalar processors improve single-threaded performance by addressing the instruction-level parallelism (ILP) inherent in applications. ILP refers to a group of instructions, for which the result of every instruction from the group does not depend on the result of the other instructions from the same group. Hence, superscalar architectures have multiple execution units to process such groups of instructions simultaneously. Out-of-order execution extends superscalarity for ILP-driven optimization. It offers on-the-fly reordering of instructions to prioritize execution of those, for which the input data has already been obtained.

The constantly increasing gap between the performance of the processing and memory units, known as the memory wall problem [136] imposed significant limitations on the overall performance of Von Neumann architectures. Luckily, the observation of the spatial and temporal locality of memory accesses made it possible to reduce the severity of this problem by incorporating fast, although low-capacity on-chip caches. As the manufacturing process advanced, the growing transistor budget was further used to alleviate this problem by incorporating larger caches, effectively hiding the memory access latency. However, as the cache latency increased with its size, the growth in the cache size was penalized. This led to the hierarchical organization of memory subsystem with several levels of on-chip cache, trading-off the hit-ratio and the access latency, and exploiting the locality of memory references.

The increase in transistor densities faced various issues in the system-level design. As the components of integrated circuits continued to shrink, the inter-component (a.k.a. global) interconnects became the main performance bottlenecks. Global wires, implementing the off-chip communication between components, introduced delays which were significantly greater than the clock period. While pipelining techniques helped to improve the communication throughput, the point-to-point latency of the off-chip communication remained an issue. The decrease in the transistor and wire sizes enabled the integration of several system components (such as processors, controllers and memories) in a single chip, leading to the concept of System-on-Chip (SoC). The SoC paradigm eliminated costly global wires by transferring the inter-component communication to the on-chip level.

Another fundamental issue caused by the increase in CMOS operating frequencies and transistor densities is *power dissipation* [131]. Both factors contributed to the rapid growth of power density of the integrated circuits, imposing heat dissipation as the main concern for system-level design.

Chip Multiprocessors (CMPs), which represent general-purpose SoC implementations, became the latest paradigm to raise the power-performance efficiency of computing systems by exploiting thread-level parallelism (TLP) [58]. Instantiation of several simple but power-efficient cores on die enabled simultaneous multithreading, as well as high data exchange rates between cores.

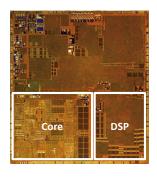

One of the examples of commercial CMP implementation is the Texas Instruments OMAP3530 mobile processor. The layout of this chip is shown in Figure 1.1(a). This multiprocessor is also an example of heterogeneous CMP, incorporating a general-purpose core with graphic accelerator and a digital signal processor (DSP). Heterogeneity contributes to optimize performance and power of the system, as different types of computing tasks can be assigned to different types of cores, which execute these tasks with the highest efficiency (e.g. DSP-related tasks will be typically assigned to DSP cores).

Prototype and industrial CMP implementations have demonstrated computing benefits obtained by CMPs with tens and hundreds of homogeneous cores [73, 118, 119, 74]. The Intel Single-chip Cloud Computer (SCC) processor is one of such examples [73]. The layout of this chip is shown in Figure 1.1(b). This CMP contains 48 processing cores of the Intel Pentium family. The chip is organized into 24 dual-core tiles, each having two L2 cache modules and an on-chip router. A 6x4 mesh-based on-chip interconnect network provides communication between the tiles as well as access to DDR3 memory controllers and I/O interface.

The example of SCC chip emphasizes the importance of the backbone component of CMP: the *on-chip interconnect*. Indeed, for a system to perform efficiently, communication between the cores, memory and input/output subsystems has to be balanced, in order to assure that none of the components is overloaded, while

(a) TI OMAP3530 processor [8]

(b) Intel 48-core SCC chip [73]

Figure 1.1: Examples of heterogeneous and homogeneous CMP implementations.

the others remain underutilized. Actually, the interconnect critically determines the major parameters of the developed system, including area, performance and power consumption. The concept of *Network-on-Chip* (NoC) was proposed about a decade ago and is now established as a leading methodology for the design of high-performance low-power interconnects for many-core systems [41, 92, 58]. In the following sections, the benefits and design issues of the NoC technology will be addressed in more detail.

While CMPs represent one extreme class of SoCs, which are designed to support a variety of applications, another extreme is a broad class of fully customized Application-Specific Integrated Circuits (ASICs). In contrast to the general-purpose processors, ASICs are developed for executing a particular application (or a group of applications). This fact allows the design-time customization of an SoC for the requirements of the target application and brings additional degree of speed-up and resource savings. However, custom designs also require significant engineering effort, trading-off the development and fabrication costs.

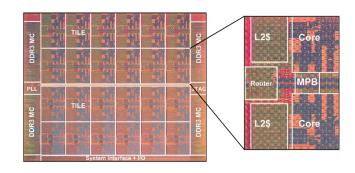

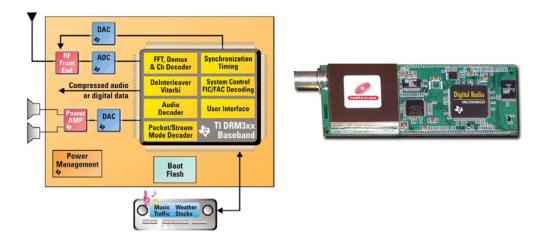

Figure 1.2 shows an example of an ASIC, found inside the Texas Instruments Digital Radio Mondiale Solution [9]. The SoC diagram (on the left) depicts a block diagram of the chip, with some functionalities being audio decoding, compression and user interface management. The use of a general-purpose core instead of a custom ASIC for this solution would consume area and power resources unnecessarily, most likely requiring an additional cooling module. This SoC represents a typical example about the cost of engineering an ASIC being amortized by an improvement in performance and decrease of the fabrication cost.

The main objective of this thesis is the design of methods and models for efficient synthesis and optimization of on-chip systems. While the majority of contributions in this work focus on general-purpose CMPs, they can also be applied (or extended)

Figure 1.2: An example of ASIC SoC implementation: Texas Instruments TMS320DRM300/350 Digital Radio Mondiale Solution [9]. Block diagram of the system (on the left) and hardware implementation (on the right).

to the ASIC domain. Synthesis of networks-on-chip, as a backbone of CMPs, is of particular interest in this work. Next section provides a deeper look into the CMP organization and presents an overview of the main design challenges for CMPs and NoCs.

## 1.1 Design challenges for CMPs and NoCs

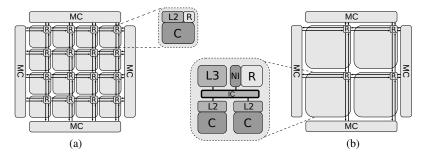

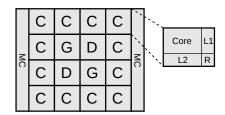

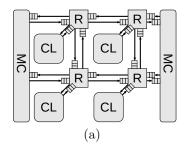

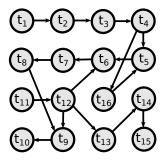

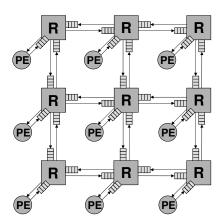

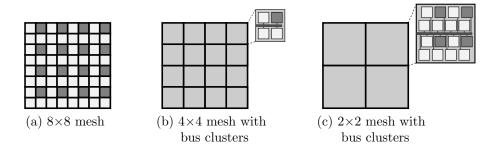

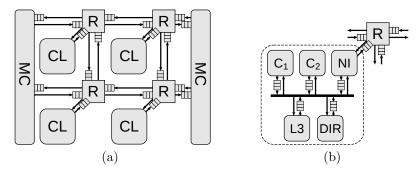

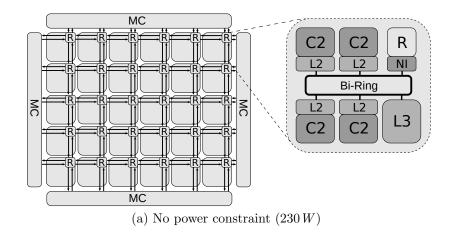

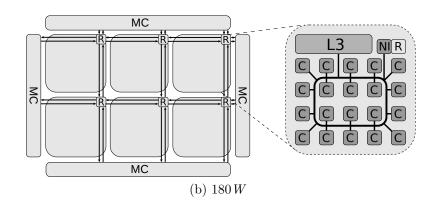

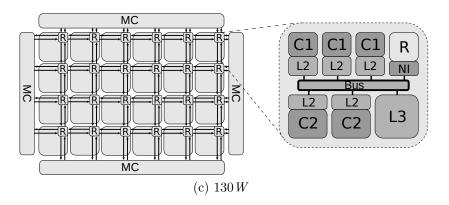

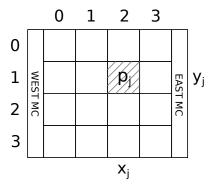

This section starts by explaining a generic organization of many-core CMPs.  $Tiled\ CMPs$  are an effective approach to architect general-purpose processors under the intense time-to-market pressure [87, 15]. The replication of tiles provides a rapid way of floorplanning many computing units in one chip and communicating them with scalable interconnect networks. Figure 1.3(a) shows an example of a CMP with 16 tiles, each one including a computing core (C) with private L1 cache, a larger on-chip cache (L2), and a router (R) that communicates with the on-chip interconnection network (a mesh). Four memory controllers (MC) provide access to the off-chip memory. Intel SCC chip (Fig. 1.1(b)) is one of the tiled CMP implementations.

To exploit the locality of memory references, hierarchical interconnects have been proposed [43, 15]. Several cores can be grouped into one cluster to share the on-chip cache, accessible through a local interconnect (e.g., bus, crossbar, ring, etc). Hierarchy increases the intra-cluster hit-ratio and reduces the traffic in the top-level interconnect. Figure 1.3(b) shows an implementation of a CMP with 4 clusters. Each cluster has two cores with private caches, a shared cache (L3), a local interconnect (IC), a router and a network interface (NI).

Figure 1.3: CMP layouts: (a) flat, (b) hierarchical.

Tile replication speeds up the engineering process by shifting the focus to the system-level design. Nevertheless, the design cycle remains a complex process, involving many stages, and only realizable by means of divide-and-conquer strategies. Furthermore, different models are employed at every stage, representing the trade-offs between the speed and the accuracy of modeling. For example, full-system simulation, which is indispensable for validating the chip before fabrication, would not be feasible for design exploration, which requires very fast estimators. As a result, a mismatch in estimating system parameters during the different stages may happen, so that the design stages have to be iterated until the desired constraints are met.

Below several issues are enumerated that are among the most challenging in the system-level design of CMPs:

- Design space exploration is the earliest stage in the design process. Given the vast space of design parameters and, therefore, possible configurations, the objective of this stage is to pick out a promising architecture, which will determine the system-level structure of the future chip. The models used at this stage have to provide very fast estimation of the architectural metrics, even at the expense of loss in precision.

- Physical planning issues are tightly coupled with those of the exploration problem. Some architectures, which exploration marks out as delivering the highest performance, may reveal floorplanning or routability problems after thorough modeling. Physical planning aims at performing and verifying the chip floorplan and routing.

- Quality of service (QoS) analysis and validation aim at the design of models for system performance. Both, analytical models and cycle-accurate simulation tools are indispensable to complete the design process. Fast analytical models are crucial to make the exploration of huge design spaces tractable, while cycle-accurate simulation is required at the late steps of the design process for QoS validation.

- System power management focuses on the development of power-saving techniques. Widely applied mechanisms include powering-off unused resources, such as cores and caches, as well as dynamic voltage and frequency scaling (DVFS) for power saving, without substantial performance penalties. The need for floorplanning the voltage regulators to support multiple voltage-frequency islands makes this task closely coupled with physical planning.

- Verification of functional correctness is another important objective aimed at design validation. Some of the issues include verification of deadlock- and livelock-freedom of the routing algorithms and cache coherency protocols, or proof of memory consistency.

The problems mentioned above focus on the efficient design of CMPs. Another challenging topic is related to the efficient usage of multiprocessors after fabrication. This topic refers to the problems of application mapping or scheduling onto many-core systems. The trends in system design demand novel methods for application mapping, which take into consideration the peculiarities of future CMPs, such as the advanced power management techniques.

### Interconnect design for SoCs

One of the major problems for CMP and ASIC SoC engineering is the design of the on-chip interconnect. The traffic and latency of on-chip communication considerably affect the overall system performance and resource requirements.

Network-on-chip realization of packet-based communication offers the benefits of both point-to-point and bus architectures: multiple routes for packets make parallel communication in a network feasible, while link sharing saves the interconnection resources. This fact promotes NoCs as the outperforming solution in terms of scalability. Other benefits of the on-chip networking are:

- Quality-of-Service guarantees. The QoS estimation techniques can be reused or adapted from macro-networking studies, providing the on-chip interconnection with better performance predictability.

- Fault-tolerance and reliability. Application of the advanced fault-tolerance and error-recovery algorithms, including the approaches known from generic networking, allows handling reliability problems in complex multiprocessing systems.

- Tolerance to design variability. One of the most serious problems that technology scaling brings is the increasing variability of design parameters. Globally

asynchronous locally synchronous (GALS) communication is one of the examples for coping with variability issues, which is facilitated by the modularity of NoCs.

The modern SoCs and NoCs require a thorough design process that involves a variety of problems: topology selection and mapping, physical planning, routing and switching schemes, and other optimization tasks. The large number of options and constraints makes it impossible to fully explore the solution space. On the other hand, dividing the design problem into smaller subproblems and doing a myopic optimization for each one of them may result in largely suboptimal solutions. Therefore, efficient techniques are required to combine the objectives of several design problems and intelligently explore the solution space for on-chip systems.

### 1.2 Motivation and contributions

The techniques developed in this thesis contribute to solve the problems of efficient design and usage of CMPs and NoCs. More precisely, the **objectives of the work** can be summarized as follows:

- Elaborate methods for efficient analytical modeling and design space exploration of CMPs, incorporating high-level models for physical planning (Chapters 3, 4 and 5).

- Propose a scalable application mapping algorithm onto general-purpose CMPs with power management techniques, for efficient deployment of many-core systems (Chapter 6).

- Address the issues of the on-chip interconnect design and exploration, by developing a model for simultaneous NoC topology customization and deadlock-free routing (Chapter 7).

In the following, each of the problems is considered in more detail.

#### Analytical modeling and design space exploration

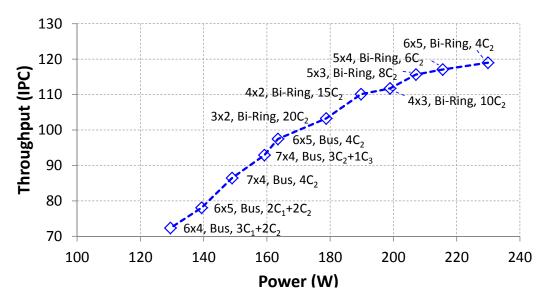

Given the vast space of design parameters, CMP designers are faced with the complex problem of selecting the best architecture subject to a set of constraints. The problem of design space exploration can be considered as the problem of efficient usage of chip resources, such as area and power. One of the possible formulation of the problem is maximization of the system throughput, subject to the constraints on the total chip area and power.

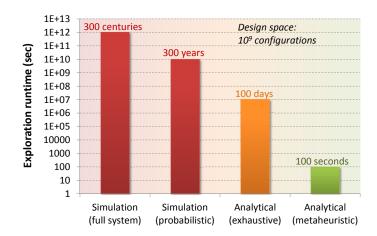

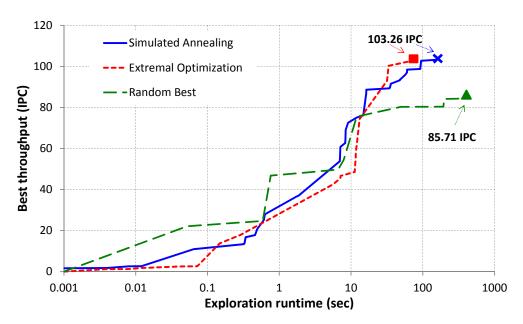

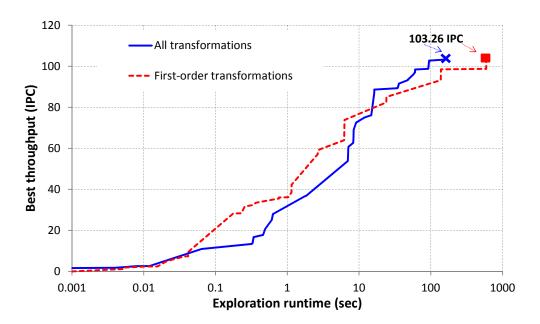

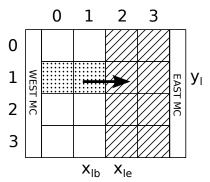

Figure 1.4: Comparison of runtimes for various exploration strategies.

Many design options must be explored, such as the variety of core implementations, interconnect types, topologies, cache hierarchies and memory management policies. Moreover, the amount of configurations increases drastically as the technology advances, allowing more cores and memory to fit into the chip area.

The complexity of the search space makes an exhaustive simulation-driven exploration prohibitively expensive. One of the ways to handle this problem is to decrease the number of points to be considered. Exhaustive exploration is replaced by an intelligent search strategy leveraging the methods of machine learning [77], design of experiments [124] or analytical optimization [31].

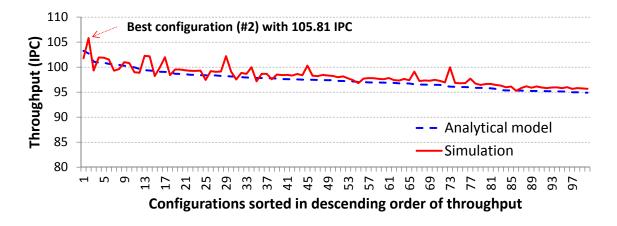

Another option to shorten the exploration time is to reduce the cost of evaluating every design point. In this scenario, analytical modeling becomes an effective alternative to simulation for rapidly pruning the design space during early exploration and selecting a small set of promising configurations. Along this line, several analytical models for CMP exploration have been recently proposed (e.g., [107, 31]).

However, the use of analytical models alone is not enough for efficient exploration. Figure 1.4 gives an idea of the ratio of exploration run times, when a simulator or an analytical model is used to estimate the cost of architectures. For a search space comprised of one billion configurations, the exploration task is intractable even when a fast probabilistic simulator is used. Analytical modeling reduces run time to approximately 100 days, which is a feasible period assuming the design cycle of several years, though the timing cost of fixing an error committed at this stage remains very high. Implementation of the intelligent search strategies (e.g. metaheuristics) on top of the analytical model allows to further decrease the search time to the order of minutes, making the exploration tool a very efficient instrument for the designer.

This thesis addresses the techniques for analytical modeling of CMPs and the on-chip interconnects in Chapters 3 and 4. A method for intelligent design space exploration is proposed in Chapter 5.

### Application mapping for tiled CMPs

From a certain point of view, a tiled CMP is similar to a coarse-granularity programmable array (FPGA), with general-purpose logic, specialized units (memories, DSPs) and a distributed communication network for routing. The main difference is that CMPs are software-configurable, whereas FPGAs are hardware-configurable. In a similar way a design has to be transferred to FPGA, an application has to be mapped onto the target CMP.

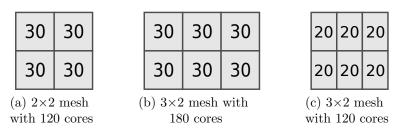

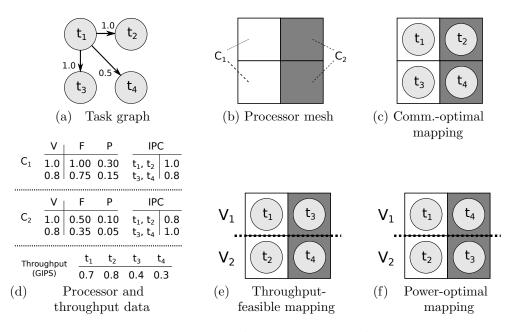

One of the peculiarities of mapping onto tiled CMPs is the presence of heterogeneous tiles, preserving the regularity of the structure, but introducing several classes of processors [86, 14, 38]. Such systems may include some specialized processors (e.g., graphics, DSP) or different implementations of the same architecture (e.g., in-order/out-of-order, multi-threading) with varied power-performance tradeoffs. Figure 1.5 depicts a tiled CMP with three classes of tiles: general-purpose cores (C), cores with graphics units (G) and DSPs (D).

CMPs are designed to operate under a certain power budget that assures the performance and thermal properties of the system. One of the most effective ways to manage power is to floorplan various voltage islands and assign the best voltage and frequency for each core [82].

Unfortunately, voltage islands have a high design cost. Firstly, the floorplanning of the system is constrained by the design of the power delivery network and the location of the level shifters. Secondly, and more important, power management requires different voltage regulators for each power supply. Off-chip regulators need extra area on the PCB that may be unacceptable if the system has a large amount of power domains. On-chip regulators involve a significant area overhead and power consumption due to the large inductances and switching capacitors required to provide a stable supply voltage [79].

Figure 1.5: Tiled heterogeneous CMP architecture.

It is therefore realistic to consider that future CMPs will have many cores (hundreds) and voltage islands with several cores (e.g., 4 or 8). This fact imposes an additional constraint in the task mapping problem: even though some cores could possibly run at lower voltages and frequencies, sharing the island with other cores may prevent from taking advantage of this flexibility. Hence, it is convenient to allocate tasks in a way that cores within the same voltage islands can share similar voltage/frequency parameters.

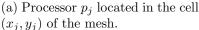

The mapping problem for tiled CMPs has to assume that the chip has already been manufactured. Therefore, the voltage islands have been already floorplanned and the maximum bandwidth of the links between cores is also known a priori. Another peculiarity of CMP mapping (as opposed to SoCs), is the presence of traffic to the off-chip memory, as well as the limited bandwidth of the memory controllers (MCs). Finally, the methods proposed for task mapping must be scalable and suitable to handle systems with hundreds of cores.

Chapter 6 describes the contribution of this thesis in the field of application mapping onto tiled heterogeneous CMPs with predefined voltage islands.

### Network-on-Chip topology customization and routing

Consider an example of a system, which is specified by a set of processing elements (PE), routers and communication requirements between PEs. Assume that the underlying system topology has been selected and the assignment of the PEs to the routers has been performed. Some of the design problems one would like to solve are:

- Finding a subset of links satisfying the communication requirements of the system and minimizing the design cost.

- Defining the routing paths for each pair of communicating PEs that satisfy the performance requirements.

- Guaranteeing that the selected routes to communicate PEs are deadlock-free.

The first problem can be referred to as the *link allocation* problem. The other two problems are related to the efficient *route assignment* with *deadlock avoidance*. These problems have different optimization criteria. By solving one of them optimally and independently from the others, no acceptable solution might be found when solving the subsequent problems. It is therefore necessary to devise non-myopic strategies to explore the solution space in a way that all design constraints are met and the implementation cost is minimized.

Chapter 7 describes the last contribution of this thesis for the simultaneous interconnect topology customization by link allocation and routing.

## 1.3 Document organization

The dissertation is organized as follows:

- Chapter 2 gives an overview of the chip multiprocessing technology and summarizes related work in the field of CMP and NoC synthesis and optimization.

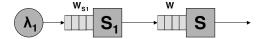

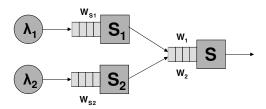

- Chapter 3 presents the first contribution of the thesis, which is an analytical model for a special class of networks-on-chip with constant-length data packets. This specific class of the interconnects finds application in CMP systems.

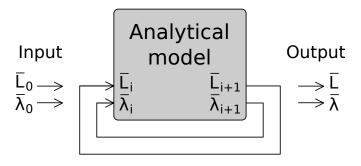

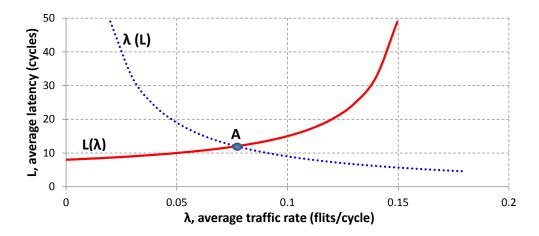

- Chapter 4 describes the second contribution of the thesis, representing an analytical modeling of the complete CMP. This section emphasizes the importance of modeling contention of the CMP interconnect and captures the cyclic dependency between the latency and traffic of memory requests.

- Chapter 5 proposes a metaheuristic-based intelligent search of the design space to eliminate the need for exhaustive architectural exploration for CMPs. This technique is the third contribution of the thesis.

- Chapter 6 addresses the issues of efficient usage of general-purpose CMPs after fabrication. A task mapping algorithm for tiled CMPs with multiple voltage islands for power management is proposed in this section, which is another contribution of this work.

- Chapter 7 represents the last contribution of the thesis, which is a mathematical model for simultaneous topology customization by link allocation and deadlock-free route assignment for NoCs.

- Chapter 8 concludes the work and outlines possible directions for future research.

## Chapter 2

## The Architecture of Chip Multiprocessors

This chapter provides a brief overview of the chip multiprocessor architecture, with the objective to understand the problem domain and help evaluating the contributions of this thesis. Last section of the chapter summarizes the work in the field, relevant to the problems considered in this dissertation.

When examining the organization of a chip multiprocessor, one may find certain similarities with the structure of a single-core processor. Basic components of the latter would include a processing unit (ALU), memory units (registers and L1-cache), a control unit, a datapath and an input/output subsystem. The components of a chip multiprocessor resemble most of those found in a single-core implementation:

- The *processing cores* are the computing units executing the instruction flow. These may be general-purpose or application-specific processors, offering various cost/performance trade-offs for a variety of workloads.

- The *memory subsystem* is a collection of memory units representing a trade-off between the memory capacity and access latency. On-chip components include the private and shared cache modules.

- The *on-chip interconnect* is the backbone of a chip multiprocessor, providing communication between the cores, memory units and input/output interface. The topic of interconnect design for efficient on-chip communication is of special interest for this work.

- The *input/output interface* is a set of controllers to interact with the off-chip components of the computing system. *Memory controllers* can be considered as a part of I/O interface, providing access to the off-chip memory. Another example is a Quick-Path Interconnect (QPI) [71].

For the problems addressed in this work, the cores, memories and on-chip interconnects represent the CMP components of major interest. In the following sections an overview of the design alternatives for each of these component types is given.

## 2.1 Processing cores

Cores are the main processing units executing the instruction flow. Modern CMP architectures include from several up to hundreds of processing units [73, 118, 119, 74]. The cores of a homogeneous CMP are identical, while heterogeneous architectures may include various combinations of core implementations for speeding-up particular applications. One of the popular examples of a heterogeneous CMP is the IBM Cell processor [38].

The first computing cores were implemented as sequential finite-state machines for loading, executing and writing the result of the instructions, as given by the original instruction flow. The processing of every instruction could take several cycles limiting the overall performance of the core, measured in *instructions per second*.

It was observed that in the given implementation certain modules of computing logic would *stall* while waiting for the other modules to complete their job: for example, the execution unit would wait for the instruction loading to bring the data in for processing. Instruction *pipelining* was proposed to introduce parallelism and increase the effective load of independent pipeline modules [22]. The flow of instruction processing is divided into several stages and every stage is executed within an individual clock cycle in a pipelined fashion. The stages of a typical pipeline include instruction *fetch*, *decode*, *execute* and *memory write*. Although this technique does not improve the latency of executing a single instruction, it raises the core throughput and enables higher operating frequencies.

It was further noticed that the instruction flow of many applications is inherently parallel, in the sense that there exist groups of instructions whose result does not depend on the other instructions in the group. This property is referred to as instruction-level parallelism (ILP) of the application. All instructions in every such group can be executed in parallel without affecting the result of the program. This observation led to the decision of supplying cores with multiple execution units, which could handle parallel instructions simultaneously, reducing the total execution time of the program. Cores with replicated execution units are referred to as superscalar.

Still, superscalarity enabled the execution of multiple instructions in parallel only when the instructions followed one another in the original instruction flow. In other words, superscalar architectures represented an example of *in-order* execution of the instruction flow. Performance was considerably penalized in cases when a long-

latency memory request was issued, causing the whole pipeline to stall for a long number of cycles.

Out-of-order execution was proposed to extend the benefits of ILP by locally reordering the instruction flow, and giving priority to those instructions for which the input data had already been computed. An analysis of dependencies in the instruction flow is required to guarantee that the program result is not affected by the manipulations with the order.

While superscalar and out-of-order architectures aim at automating the search of ILP by hardware, Very Long Instruction Word (VLIW) [54] architectures delegate the responsibility of finding ILP to software, either at the compiler or programmer level. VLIW processors realize a set of "wide" instructions, each implementing several operations (e.g. a sum, an increment and a multiply). The task of defining the instruction patterns is deferred to software, which is shown to be convenient for certain application domains, where such operation patterns are common (e.g. DSP or numerical computations).

Finally, simultaneous multi-threading (SMT) [126] emerged to exploit the thread-level parallelism (TLP), as opposed to ILP. There are two primary sources of TLP. First, as in the case of VLIW architectures, TLP can be specified explicitly by the programmer within the software development process. Second, TLP often appears due to the fact that one core is commonly used to run several applications simultaneously. Hence, modern cores implement multi-threading support by replicating the thread-processing units.

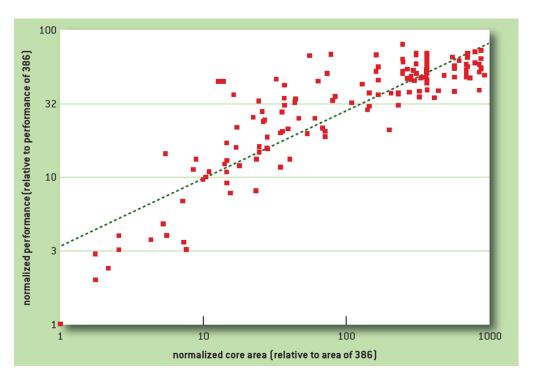

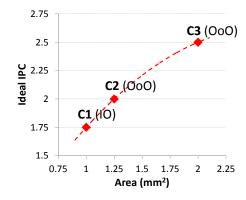

An interesting observation regarding the efficiency of advances in single-core implementations is known as the *Pollack's rule* [29] [116]. It states that the core performance, in terms of *instructions per cycle*,  $IPC_c$ , only grows as a square root of the core area  $A_c$ :

$$IPC_c = \alpha \cdot \sqrt{A_c}$$

where  $\alpha$  denotes the performance of a basic core chosen for comparison. Figure 2.1 plots an illustration of Pollack's rule from [42], constructed for more than a hundred of real processor implementations, using the data from Stanford CPU Database [4]. The performance and area of Intel 80386 processor are used as a baseline.

This rule has served as one of the motivations for chip multiprocessing, favoring instantiation of a multitude of simpler cores rather than several complex designs, for the purpose of throughput optimization [108]. However, it is worth noting that Pollack's rule only predicts a generic trend between performance and cost of single core architectures. Depending on the type of workload, the amount of ILP and TLP in the executed application, a CMP with more complex out-of-order cores may deliver more throughput than the one comprised of many simple core implementations.

Figure 2.1: Pollack's rule for processing cores [42], [4].

The problem of searching for the throughput-optimal CMP architecture, given a library of components and application workloads, is one of the major problems addressed by this thesis.

## 2.2 Memory subsystem

Processing cores execute *instructions* that operate on *data*. Both instructions and data are stored in *memory*, and hence its organization has a significant impact on the overall performance of the computing system.

Since its conception, dynamic RAM technology continuously evolved, with about 15% increase in performance and  $2\times$  increase in density every two years [29]. At the same time, the performance of processing cores advanced exponentially, leading to the constantly growing gap between the performance of computing and memory units, known as the memory wall [136].

The principle of *locality* of the memory references helped to alleviate the memory wall problem. It was observed that at least two major types of locality are inherent to the memory access patterns. *Temporal locality* refers to the fact that if a particular memory address is accessed at some moment in time, it is very likely that the same address will be requested *again* in the near future. *Spatial locality* observes also that

Figure 2.2: Hierarchical organization of memory subsystem.

if a particular memory address is accessed at some moment in time, it is very likely that the *nearby* addresses will be requested in the near future.

These observations made it possible to effectively reduce the average memory latency by organizing fast caches of moderate sizes, even when it is not feasible to supply fast and large memory which would store all data requested by applications. According to the principle of locality, the regions of memory which have a high probability of being accessed in the near future are loaded and kept in the caches for improving the average memory latency.

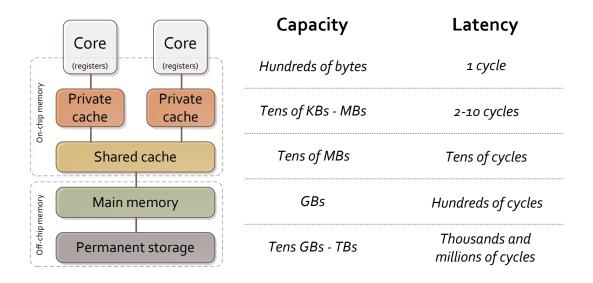

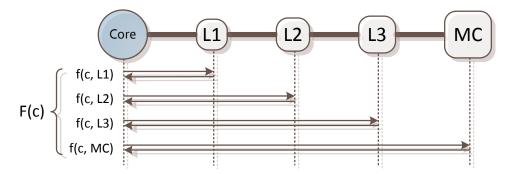

The introduction of caches led to *hierarchical* organizations of the memory subsystem, which includes several layers of memories of increasing sizes and latencies. Figure 2.2 gives an overview of the hierarchical organization. In addition to the core registers, which have a very fast access time, but a limited capacity of only hundreds of bytes, the on-chip memory subsystem is represented by several levels of cache. The fastest private first-level cache, L1, typically has the latency of several cycles and a capacity of tens of kilobytes. A larger private cache, L2, can be added, providing capacities of several MBs and latencies around ten cycles. A *shared* cache of a larger size, often called a *last-level cache*, LLC is included to extend the onchip memory with a flexible storage, which can be redistributed among the cores according to the needs of the executed applications.

The off-chip memory subsystem includes the main dynamic RAM and the permanent storage. The capacities of the former have the order of GBs at the expense of

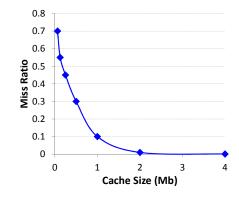

Figure 2.3: Power-law cache miss model.

an increase in latency of  $10 \times$  or more. Dynamic RAM is backed up by a significantly slower, though non-volatile memory, which provides virtually infinite capacity.

One of the problems in the design space exploration of CMP systems is how to properly architect the memory subsystem, in terms of specifying the number of levels in the hierarchy, distributing cache capacity across the hierarchy levels and organizing cache sharing.

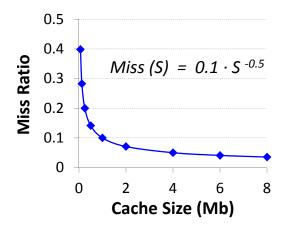

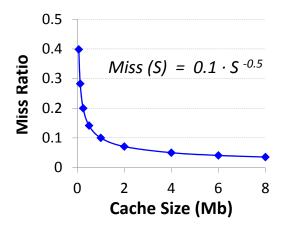

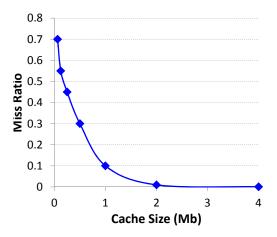

A possible way to characterize an application from the perspective of its memory requirements, is a model that defines the *miss ratio as a function of the cache size*. Miss ratio for a given cache size is defined as the fraction of memory accesses for which the data has not been found in the cache. Figure 2.3 plots an example of a miss-ratio curve, approximated with a power-law:

$$MR = MR_0 \cdot S^{-\alpha}$$

where  $MR_0 = 0.1$  and  $\alpha = 0.5$ . Power-law was found to be a good analytical function approximating the cache miss behavior [63]. The miss-ratio dependency on cache size will be actively used in this work to represent the application model.

## 2.3 On-chip interconnects

On-chip interconnect is a backbone of a CMP, realizing data communication between the processing and memory units of a system.

This section overviews two basic on-chip interconnect architectures, crossbars and buses, summarizing their advantages and drawbacks and motivating the need for on-chip networking, which is introduced in the next section.

### Crossbars

The simplest and most intuitive way of organizing the communication between several components is by using point-to-point connections, such as a *crossbar*. This organization provides every pair of communicating components with a private link, resulting into a high degree of parallelism in data transmission.

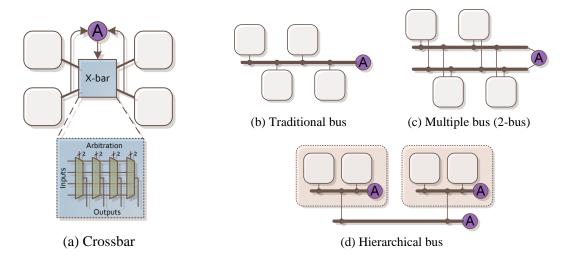

Figure 2.4(a) shows one possible implementation of a crossbar connecting four components <sup>1</sup>. Generally, every receiver will have a single queue for incoming data arriving from all senders. Hence, an arbiter is required to resolve the cases of contention, i.e. when several inputs request the same output port. In the depicted implementation, arbitration signals are used as select signals for input multiplexers, assigning the winning inputs to every output.

In some special cases of high-performance crossbars a dedicated queue may exist for every sender-receiver pair. In this case crossbar resembles a collection of buffered point-to-point links performing independently, so arbitration between different inputs is not needed.

The main issue with crossbars is their limited scalability, since the amount of resources (mainly links) increases quadratically with the quantity of attached components. Although academic research has demonstrated that crossbar configurations with up to 128 components are possible [113], industrial implementations reveal a rather conservative view on crossbar scalability, with the maximum system size not exceeding several dozens of components.

In application-specific systems, where the communication flows are known at design time, interconnect topologies can be customized to produce *partial crossbars*, which save resources by eliminating certain communication paths. Several methodologies for automatic ASIC-driven generation of partial crossbars have been proposed in the literature, e.g. [97], [94].

#### Buses

The fact that communication between a pair of components normally does not occur continuously in every cycle results in crossbar underutilization. This observation led to the paradigm of *resource sharing* for on-chip communication, which is traditionally represented by the family of *bus* topologies.

Buses can be seen as the opposite of a crossbar: while the latter implements a dedicated link for commuting every pair of components, bus provides a single shared link for any communication, making this architecture very resource-efficient. Figure 2.4(b) shows a single bus connecting four components, and its arbiter. The

<sup>&</sup>lt;sup>1</sup>Here and further in this chapter, components are illustrated with rounded-corner squares, while arbiters are represented by circles labeled with 'A' inside.

Figure 2.4: Interconnect solutions for four components: (a) crossbar, (b)-(d) buses.

sender issues a request for bus access to the arbiter. Once granted the ownership, the sender establishes communication through the bus with the receiver and data is transmitted. Upon the end of data transmission, the bus ownership is returned to the arbiter.

Note that this communication policy is intrinsically sequential in the sense that the next sender can not start transmitting data before the previous sender has finished the transmission. This limitation imposes a serious bandwidth penalty for the case when two or more low-latency communications need to be realized simultaneously.

Another problem of bus scalability is the growing latency due to the long links required to connect all components. Bus pipelining can alleviate the problem for transferring large amounts of data in a single communication, but point-to-point latency remains an issue.

Several extensions of a single bus have been proposed to tackle the mentioned problems. The *multiple bus* topology is an extension of the traditional single bus architecture, implementing several transmission lines and enabling certain degree of parallelism in bus transactions. Figure 2.4(c) presents a 2-bus organization with two links, which allow up to two simultaneous data transmissions. Assuming that two different senders request communication with two different receivers at the same time, the arbiter may assign one of the available links for every sender-receiver pair. As a result, both communications occur simultaneously without affecting each other.

Another bus extension is the *hierarchical bus* topology, shown in Figure 2.4(d). This architecture is beneficial for the communication patterns where certain degree of locality of the on-chip requests is observed. Components that require high

inter-communication bandwidth are organized in clusters and communicate via local buses, supplied with dedicated arbiters. In case an inter-cluster communication is needed, it is realized via the global bus. Note that local communication is performed through shorter (hence, faster) local buses, effectively decreasing the average point-to-point communication latency. Hierarchical architectures can be extended to an arbitrary number of levels straightforwardly.

It is clear that the performance improvement obtained by adding multiple bus links or hierarchy levels comes at the cost of additional resources, such as area and power, and represents one of the most important trade-offs in bus design. Other common trade-offs include synchronous vs. asynchronous bus operation, separation of signal types (address, control, data) over different physical links vs. multiplexing of signals on the same physical link.

A number of bus standards and communication protocols have been adopted and extensively used. Some of the most popular standards include the Advanced Microcontroller Bus Architecture (AMBA) [1], and STBus [7].

## 2.4 Networks-on-Chip

Inspired by the idea of macro-networks, the Network-on-Chip (NoC) concept was introduced to tackle the scalability issues of the on-chip communication [92], [41]. This notion changes the interconnection paradigm from routing wires to sending data packets across the network [41]. NoCs represent a trade-off between high-performance point-to-point connections and resource-efficient buses, since they offer both, data transfer parallelism and link sharing between the flows.

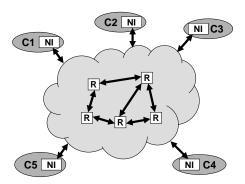

The network-on-chip abstraction is depicted in Figure 2.5. A network is composed of a set of routers (R), and physical links between them. The exact topology may

Figure 2.5: Network-on-Chip abstraction.

vary broadly, from regular meshes and rings in general-purpose CMPs to highly irregular solutions in ASICs. Cores (C1-C5) are connected to the network via the network interfaces (NI). The role of the NI is to convert the data generated by the cores into the packets that can be sent through the network, and vice versa, decode the packets arriving at the destination nodes. The term node is used to denote a generic traffic injector or consumer, connected to a network, which can be a processing core, a cache memory or any other type of on-chip device, such as a memory controller.

Typical objectives in NoC design are the low-latency, high-bandwidth communication and the easiness of network scalability. Although similar to those of the traditional macro-networks, the requirements for on-chip networks include several specific properties:

- Low area is an essential requirement to improve the chip yield, manufacturability and reduce leakage power of the interconnect.

- *Higher bandwidth*, compared to the traditional networks, is needed to incorporate additional transactions, such as the traffic of cache-coherency protocols and accesses to the shared memory.

- Fault-tolerance and reconfiguration abilities are important for guaranteeing the interconnect correctness and performance in the presence of faulty components.

- Variability handling becomes a necessary property for designing robust systems, given the increasing uncertainty of the CMOS devices implemented with deep-submicron technologies.

In the rest of this section, the main design issues for NoCs are outlined, such as the selection of network *topology*, *switching* technique, *flow control* mechanism and *routing* algorithm. At the end of the section an overview of the NoC router internals is provided.

## Topology

The topology of the network-on-chip is an essential design parameter which critically affects the performance and cost of the on-chip communication. Topology primarily determines the communication bandwidth and latency by defining the number of on-chip routers and links, their relative position and connectivity.

The classification of NoC topologies can be done according to different criteria, among which the most interesting in our context are the following:

- Direct vs. indirect topologies. Direct topologies assure that every router has a connection to at least one node, while indirect topologies allow routers which only have connections to other routers.

- Flat vs. hierarchical topologies. Hierarchy typically resembles tree-like structures with clearly marked clusters of local communication. As in case of hierarchical bus, these topologies are effectively embedded in systems with significant locality of the on-chip communication.

- Regular vs. irregular topologies. Regularity can be defined as a presence of a certain pattern or symmetry when connecting links to routers, as well as in distribution of the link lengths and hop counts. Regular topologies are better fit for general-purpose designs, while irregular topologies allow to benefit from design-time specialization.

Typical trade-offs in topology design can be analyzed by enumerating the most common topological properties:

- Bisection bandwidth is defined as the minimal bandwidth over all possible partitionings of the topology into two equal halves. This property is often used to predict the performance of the network analytically.

- Network *diameter* is the maximum number of hops between any pair of nodes. Diameter minimization is an important objective for improving the network performance.

- Link count and router count define the total number of links and routers respectively, and are used to approximate the resource cost of the network.

- Router degree represents the number of input and output ports of the router and is closely related to the delay propagation through the router and the area and power consumed by the router.

Finding the balanced choice of the aforementioned parameters for the given communication pattern and performance constraints, so as to minimize the resource cost, constitutes the topology selection problem for network-on-chip. The problems of topology exploration and application-specific customization are among the important problems addressed by this thesis. For this reason, a broader glance at the topological choices relevant for this work is next presented.

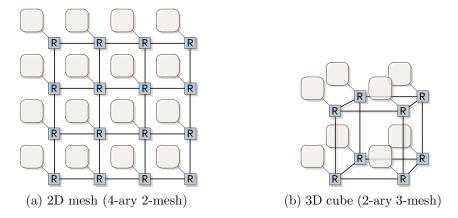

#### Meshes

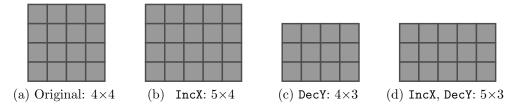

A 2-dimensional mesh, depicted in Fig. 2.6(a), is the most widely adopted topology for network-on-chip, both in research and industry. Its popularity is determined by several factors, such as regularity, good physical properties and scalability. The layout of regular 2D mesh facilitates the chip floorplanning and is especially valuable for *tiled* architectures, which are popular for rapid prototyping of many-core systems. Indeed, to extend the mesh to an arbitrary number of nodes one simply needs to add rows or columns to the mesh without the need to redesign the basic network components, such as routers and links.

The family of mesh topologies is known as k-ary n-meshes, where k defines the number of nodes per dimension and n is the number of dimensions. Meshes with dimensions of three and higher have a limited applicability due to issues of physical implementation. Figure 2.6(b) sketches a 3D mesh (cube), which despite its nice theoretical properties, has to be planarized when implemented in traditional CMOS technology. Planarization leads to an increase of delay in certain links, so the final performance of this topology will be strongly affected by physical implementation. It is worth noting that with the emergence of three-dimensional semiconductor technologies (e.g. stacked memories), 3D topologies become more popular. However, the interest in meshes of higher dimensions is still limited to the research community.

Although meshes can adopt any arbitrary number of components without significant design effort, they are considered to be poorly scalable: the network diameter grows linearly with the mesh dimensions and its bisection bandwidth scales slower than the communication requirements, as the number of components increases.

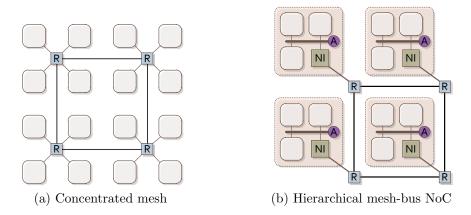

Concentrated mesh or C-mesh was proposed to decrease the average latency in traditional meshes (Fig. 2.7(a)). The reduction in latency is obtained through the increase of router degree and concentration of larger number of nodes at one router. Although this organization incurs a penalty on network throughput, it becomes beneficial when a certain degree of traffic locality is observed.

Another family of solutions that improve network performance in presence of local traffic is *hierarchical* mesh-based topologies. An example of two-level mesh-bus architecture is shown in Fig. 2.7(b). Similar to a hierarchical bus, this topology implements individual low-latency bus interconnects for local communication in clusters. Additionally, a high-throughput global mesh is responsible for inter-cluster communication. The benefit of hierarchical approach is the separation of local and global traffic for eliminating their interference, although at the cost of additional resource consumption.

Hierarchical meshes are of high interest for this work, since they are considered as a promising architecture for low-power high-performance interconnects of CMPs with hundreds or even thousands of computing units.

Figure 2.6: K-ary n-mesh topologies.

Figure 2.7: Extensions of 2D meshes.

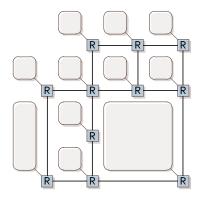

Figure 2.8: Irregular mesh topology.

Finally, irregular meshes represent a specific class of mesh-based topologies, which are especially popular among the ASIC community, where heterogeneous nodes (i.e. cores, memories) appear frequently. Heterogeneity of node sizes leads to irregular floorplans, which as Figure 2.8 proposes, can be arranged in a grid of a fine granularity and effectively connected by a mesh-based structure. The obtained mesh may miss some routers, as compared to a regular implementation; the links may have different lengths and router degrees may vary - explaining the "irregular mesh" terminology. The fact that the interconnect topology is grid-based speeds-up the design time considerably, making irregular meshes popular for application-specific systems. The aspects related to mesh topology customization are considered later in this thesis.

#### Tori and rings

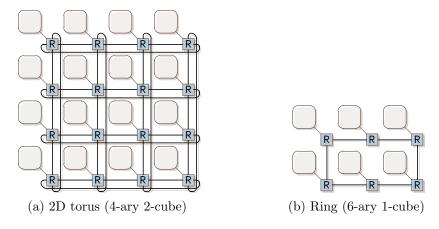

A two-dimensional torus is another widely used solution for NoCs and represents a mesh with added wraparound links, as in Fig. 2.9(a). The torus family is denoted as k-ary n-cubes, with the same notation for k and n as in the case of meshes.

Tori of dimension two and higher are exposed to the same planarization problems as high-dimension meshes. Depending on the implementation, wraparound links may exhibit delays similar to traversing the whole chip in one dimension. For certain chip sizes this results into a severe mismatch between the predicted link delay and its silicon realization, causing a noticeable performance penalty.

One-dimensional tori, also known as rings (Fig. 2.9(b)) represent another example of broadly applied topologies, due to several convenient properties. First, rings are regular symmetric topologies which are easily floorplanned and implemented in silicon. One can choose among uni-directional and bi-directional ring implementations to explore typical cost/performance trade-off. Another reason for using rings

Figure 2.9: K-ary n-cube topologies.

is the low router degree, consisting of only three ports for uni-directional or four ports for bi-directional rings, thus simplifying router design and cost significantly.

The drawback of rings is the low bisection bandwidth, which is however compensated by low area and power requirements, making rings a good choice for hierarchical interconnect architectures.

#### Fat-trees and butterflies

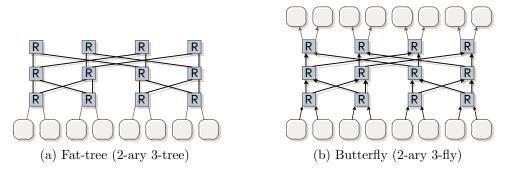

As opposed to meshes and tori, which are examples of direct topologies, fat-trees represent indirect topologies, implemented as multistage interconnect networks (MINs), as shown in Fig. 2.10(a). The data has to traverse several stages of intermediate routers in order to reach destination.

The main benefit of this topology is the high bisection bandwidth, which scales linearly with the number of network nodes. Nevertheless, the cost of increased bandwidth is paid with the augmenting number of routers. Even more important, the problem of physical implementation of the MIN-based topologies in silicon appears due to the complex wiring between routers. Fat-tree topologies continue raising interest in the domain of optical interconnects. Recent techniques aimed at improving the physical planning of NoCs based on fat-trees [138].

Butterfly networks are also based on MINs and similar in their physical structure to fat-trees. However, these are uni-directional interconnects, with sender and receiver nodes situated along the opposite sides of the network (Fig. 2.10(b)). The routing path between any sender-receiver pair in butterfly network has a predetermined number of stages. The drawback of this topology is the existence of only one path between a communicating pair of nodes. This observation requires additional mechanisms for implementing fault-tolerance techniques in the presence of faulty links or routers.

A similar notation is used for k-ary n-trees and k-ary n-flies, where k denotes the number of nodes connected to each router and n is the number of MIN stages.

Figure 2.10: Trees and butterflies.

### Switching

The switching technique determines the policy for allocating the network resources required for data transmission through the interconnect. Several switching schemes are considered in this section.

The technique of reserving a dedicated channel between sender and receiver is referred to as *circuit switching*. Prior to any data transmission, a path has to be allocated between the two nodes, guaranteeing that all shared resources have been properly allocated and the data can be commuted avoiding interference with other flows. Once the data transmission has been completed, the path is deallocated and its resources are released to favor communication of other flows.

The major benefit of circuit switching is the absence of contention between different flows. This property eliminates the need for buffering resources, effectively reducing the NoC area and power requirements. On the other hand, the need for path allocation and deallocation not only introduces a performance penalty, but also reduces the amount of parallelism in communication. Indeed, the requirement to establish and maintain a path between different parts of the network reserves resources unnecessarily, blocking the data transmission of the other flows with a high probability.

Packet switching is an alternative approach which does not require path reservation, since the data packets determine their paths independently as they propagate through the network. Sending data in packets allows communication at a finer level of granularity. The downside of the technique is a chance for contention when several packets compete for the same shared resource, such as a network link. This implies the allocation of buffer resources across the network so that the packets can be temporarily stored and then forwarded, after contention has been resolved.

The basic implementation of packet switching is hence referred to as *store-and-forward*. Every router input is provided with a buffer space, with a size greater or equal to the size of one data packet. In this scenario, a blocked packet is stored in the input buffer and waits for the output channel to be released. Consequently, the requirements for a packet to continue transmission is the availability of the output channel as well as the sufficient amount of buffer space at a receiving router.

The requirement for the complete packet to arrive at the router input before initiating its transmission through the router was found too restrictive. Since packets are typically formed by a number of smaller fragments, called *flits* (flow units), the header flit of the packet was allowed to start transmission through the router before the whole packet arrived to the router input. This approach was called virtual cutthrough and allowed for slight performance improvement over the store-and-forward technique.

Later, the virtual cut-through scheme was extended and applied to the whole sequence of flits. This new scheme was called *wormhole* switching. The wormhole paradigm considers a packet as a sequence of flits, led by the header flit. As the header flit propagates through the network, it establishes the path, so that the subsequent flits follow the same path in order, experiencing no contention from the other packets. The path is reserved until the tail flit of the packet propagates, deallocating the resources. In this sense packet propagation resembles the behavior of a worm, stretching across several network routers, and contributing to the name of the technique. Wormhole switching considerably reduces the buffering requirements of a NoC, though the inter-packet contention is increased, as distributed packets block a higher number of router resources.

The addition of virtual channels to wormhole switching allows to alleviate the contention problem at the cost of larger buffer space. The concept of a virtual channel is used to denote a buffered logical channel for transmitting data between sender and receiver. Virtual channel has a dedicated physical buffer, however one physical link is multiplexed between several virtual channels. Assuming N virtual channels, the total buffer space of the router inputs is subdivided into N smaller buffers, while N virtual links are multiplexed over one physical link. This organization enables the support of N message classes, whose packets are stored in individual buffers at every router, and hence avoid blocking packets among different message classes.

The wormhole technique is the widely adopted scheme for switching in NoCs and is the one that will be assumed in the work presented in this thesis.

#### Flow Control

The mechanisms of flow control actually govern the process of packet and flit propagation in the network. They define the conditions for the data units to advance and guarantee the correctness of data transmission.

A simple approach to manage data propagation is for the receiver to send an acknowledgment to the sender, once the data has been received. For this purpose, an ack signal is emitted by the receiver if the data has been accepted successfully, or a negative acknowledgment nack otherwise. This scheme is known as ack/nack flow control.

An alternative approach, which eliminates the unnecessary data transmission if the receiver is not ready to accept data, is to supply every sender with a go/stop signal governed by the receiver. The receiver maintains the signal in the go state while it is ready to accept new data and changes it to the stop state otherwise.

A more advanced flow control technique is realized by means of *credit exchange* between sender and receiver. Every sender is assigned an initial number of credits, specifying the amount of data units which the sender is allowed to transmit. The

sender can only transmit data when its credit is positive. The transmission of every data unit decrements the number of available credits. This mechanism prevents the buffer overflow at the receiver if the initial number of credits does not exceed the buffer size. The receiver in turn supplies sender with additional credits as soon as the data units depart from the buffer so that the sender is able to resume data transmission.

### Routing

The routing strategy has a significant impact on network performance. Routing algorithms are used to determine the actual paths of packet propagation through the network. Every path is defined by the sequence of links and routers that the packet uses to travel between the sender and the receiver.

Routing algorithms can be classified according to the following criteria [92]:

- Static vs. dynamic routing. Static (also known as deterministic) algorithms define the paths for every sender-receiver pair prior to the beginning of data transmission and these paths remain fixed throughout the communication process. Dynamic (also known as adaptive) algorithms generate paths for every packet, considering the current state of the network, typically with the objective of avoiding congestion regions and minimize packet latency.

- *Minimal* vs. *non-minimal* routing. Minimal algorithms generate routes with the minimum hop-count between source and destination nodes, while non-minimal algorithms can favor longer paths for better communication properties (e.g. load distribution or fault tolerance).

- Source vs. distributed routing. In source routing, the complete path for a packet is defined at the source node and is incorporated in the packet header for taking routing decisions as the packet propagates through the network. In distributed routing the directions for a packet at every router are taken locally, typically by using routing tables.

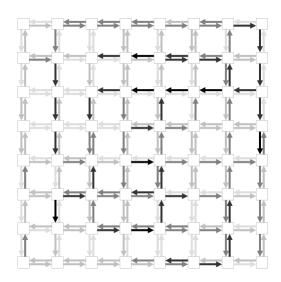

An important and widely-used category of deterministic minimal routing algorithm, suited for regular topologies such as meshes and tori, is dimension-ordered routing [92]. With this approach, an order for the dimensions of the topology is defined and the packets are always sent according to the selected order of dimensions. A popular dimension-ordered algorithm for 2D topologies is XY-routing, when the packets are first routed in the X-dimension and then by the Y-dimension.

Deadlock avoidance is one of the important properties of the routing algorithm, which can be achieved by dimension-ordered routing in certain topologies (i.e. meshes and hypercubes) or alternatively by prohibiting routes from taking certain turns of the topology [59, 34]. A generic approach to guaranteeing deadlock freedom for both static and adaptive routing algorithms is based on resolving cyclic dependencies in the channel dependency graph [50, 52].

#### Router Architecture

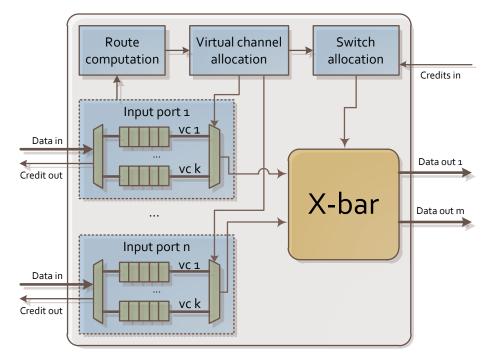

A router is a basic building block of an on-chip network, which performs the principle tasks for enabling communication: data buffering, arbitration and switching. The architecture of an on-chip router is highly dependent on its implementation. Figure 2.11 outlines a generic structure of a router with n inputs, m outputs and k virtual channels [58].

The main components include the input buffers, routing and switching logic, and a crossbar switch. The internal operation of a router can be well understood by considering how a single flit traverses the router. This process can be summarized by the following steps:

- Buffering is performed when a flit arrives at an input port. For this purpose, every input port implements a collection of buffering slots, which can be separated into k groups to support k virtual channels. In the latter case, the arriving flits are demultiplexed from the physical link and stored in the appropriate buffer. Credits are delivered to the sender as the buffer slots become available, to resume data transmission.

- Route computation is the first step in calculating the output port, to which the flit has to be transmitted. The route computation logic can be designed either to extract the routing information from the flit itself, as in source routing, or to consult the routing tables, as in distributed routing.

- Virtual channel allocation is the following step, aimed at configuring the index of the virtual channel at the output port. The virtual channel allocation logic also selects the flit to be transmitted in the current cycle, among the flits waiting for transmission at the input virtual channels (as shown in the figure).

- Switch allocation aims at configuring the crossbar to connect the selected inputs with the outputs, according to the routing decision for the current cycle.

- Switch traversal finalizes the process of router traversal for a flit, after which the flit continues its path through the output link.

Figure 2.11: On-chip router architecture.

Note that depending on the implementation, some of the previous stages can be pre-computed (e.g. route computation) or performed in parallel (e.g. virtual channel and switch allocation), effectively reducing the router latency.

# 2.5 Related work

This section presents an overview of the state-of-art related to the problems addressed by this thesis.

# Analytical modeling of on-chip interconnects

The problem of analytical modeling of on-chip interconnects aims at estimating the system parameters (e.g. throughput, power, total latency) analytically, without the need for simulation. In this section we consider the problem of modeling the total latency for the data requests to traverse the interconnect from source to destination nodes. This latency consists of two terms. The first term is the *static* (or *hop-count*) latency, which depends on the geometrical distance between the source and destination nodes, and hence can be predicted statically, once the interconnect topology and the routing function have been defined. The second component is the *dynamic*

Figure 2.12: Queueing model for (a) mesh NoC and (b) bus-based cluster.

(or *contention*) latency. Contention happens in the interconnect when several data requests compete for the same shared resource, such as a bus or a NoC link. This results in additional delays experienced by the data in the buffers (queues) distributed over the on-chip interconnect.

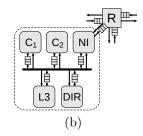

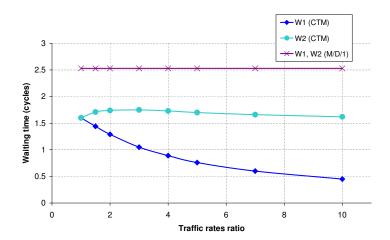

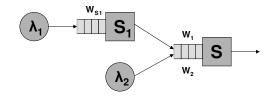

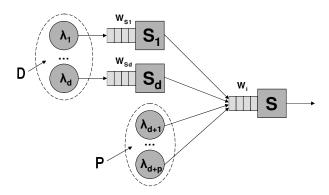

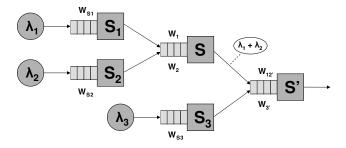

The first analytical models appeared for basic types of multiprocessor interconnection networks, such as buses, multiple buses and crossbars [23, 121]. The emergence of more complex on-chip interconnects attracted a variety of novel techniques to the traffic modeling problem.

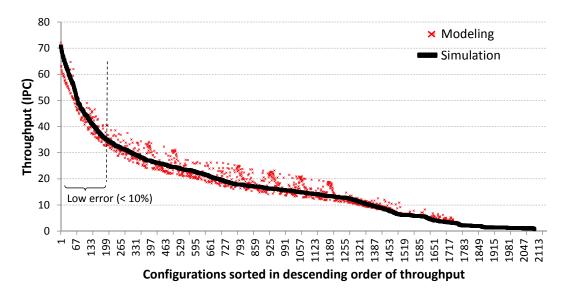

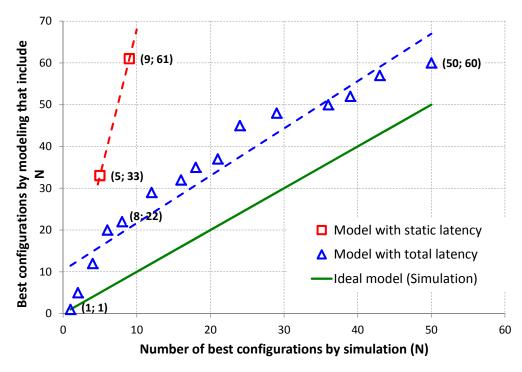

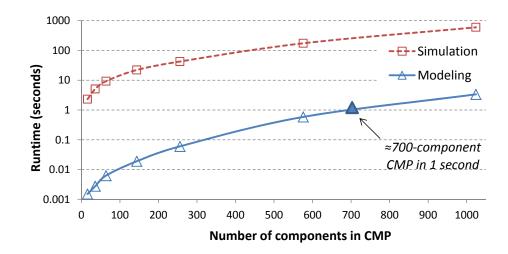

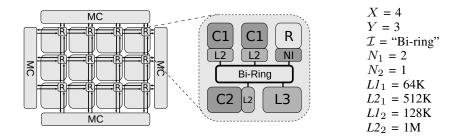

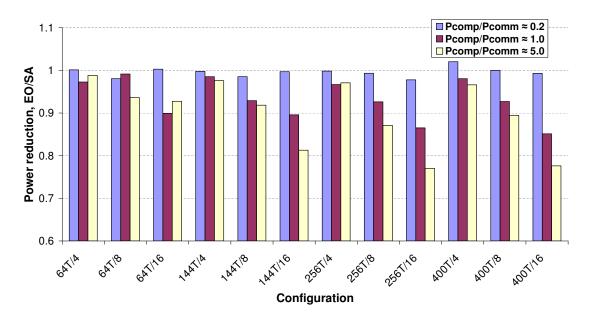

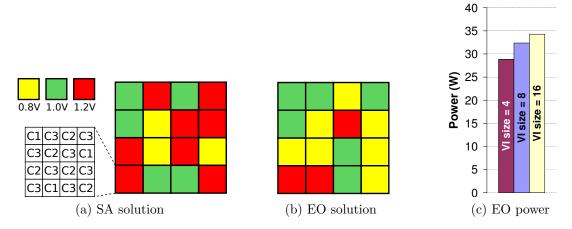

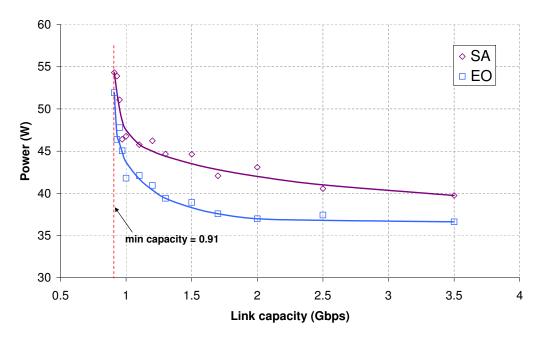

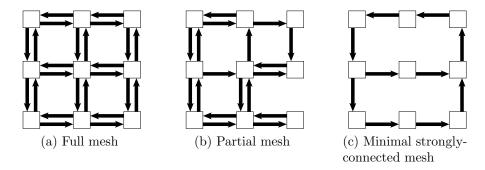

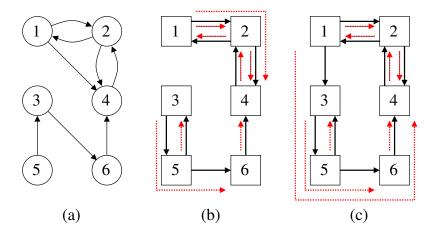

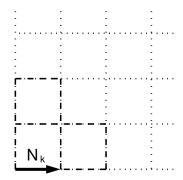

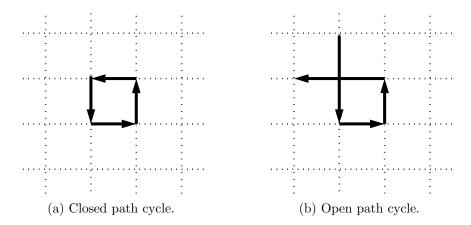

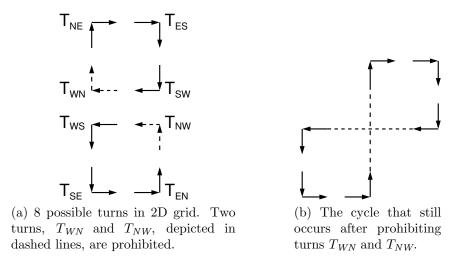

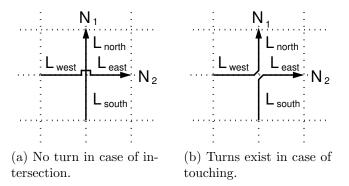

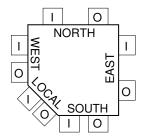

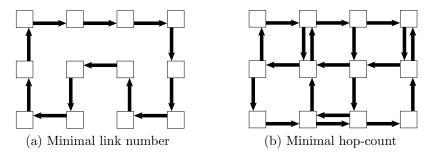

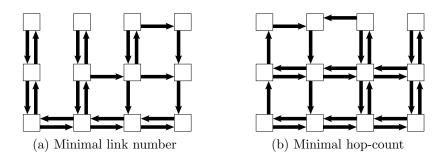

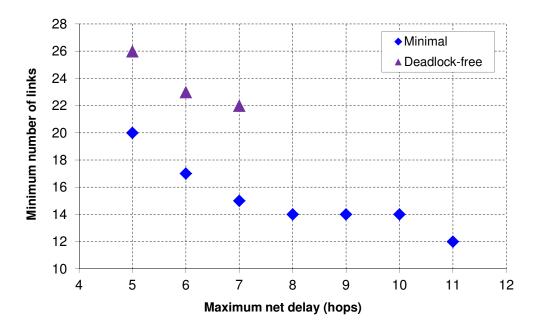

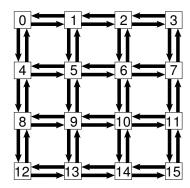

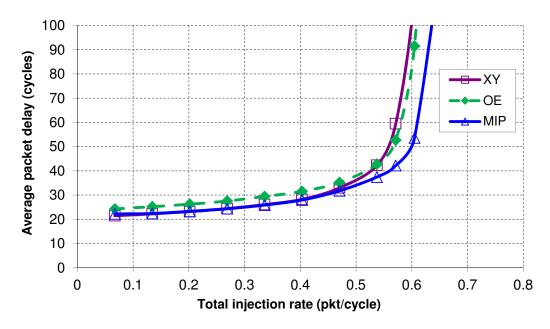

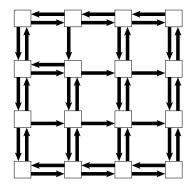

Figure 2.12 depicts a generic structure of a CMP with a hierarchical network-onchip interconnect. Without loss of generality, a two-level hierarchical interconnect is shown, with a 2D mesh at the top level. Figure 2.12(a) shows the queueing representation of the top-level mesh. The mesh routers (R) have up to five inputbuffered ports to store the incoming flits. The primary ports of the routers are connected to the clusters (CL), which in case of a flat CMP organization may consist of one device (e.g. a core with private caches in Figure 1.3(a)). Figure 2.12(b) presents an example of queueing model for a bus-based cluster, corresponding to one tile of the hierarchical CMP. This cluster consists of five devices, communicating via a shared bus: two cores with private caches, an instance of an L3 shared cache, a directory and a network interface. Every device has a buffer to store the requests to the bus. To distribute the off-chip memory traffic uniformly over the mesh and avoid high contention of certain routers, memory controllers may have multiple connections to the mesh, as shown in Figure 2.12(a).