# Universidad de Murcia Facultad de Informática

Sincronización y Comunicación Eficientes en Arquitecturas Many-Core CMP

Efficient Synchronization and Communication in Many-Core Chip Multiprocessors

José Luis Abellán Miguel 2012

## Universidad de Murcia

#### Facultad de Informática

Departamento de Ingeniería y Tecnología de Computadores

# Sincronización y Comunicación Eficientes en Arquitecturas Many-Core CMP

Tesis Doctoral

Autor: José Luis Abellán Miguel

Directores:

Juan Fernández Peinador Manuel Eugenio Acacio Sánchez

Murcia, Septiembre de 2012

### Resumen

En la última mitad del siglo XX los computadores sufrieron una constante evolución en rendimiento propiciada principalmente por el aumento de la escala de integración, que habilitaba cada vez más transistores disponibles para incorporar novedades arquitectónicas, o para aumentar el tamaño de las memorias en el chip. Esta tendencia fue ya predicha por Gordon E. Moore [42], quien ya en 1965 expuso que el número de transistores por área de silicio sería doblado cada dieciocho meses por los sucesivos avances tecnológicos. La otra causa importante para el aumento del rendimiento fue el crecimiento incesante de la frecuencia de procesamiento en cada nueva generación de chips, haciendo la circuitería cada vez más rápida. De este modo, los microprocesadores alcanzaron niveles de complejidad demasiado altos requiriendo de procesos de verificación cada vez más costosos en tiempo y valor económico. Disponiendo de un sólo núcleo de procesamiento, estas arquitecturas uniprocesador estaban fundamentalmente enfocadas a la extracción de paralelismo a nivel de instrucción (Instruction-Level Parallelism en inglés, o ILP), en el que se aprovechaba al máximo la ejecución simultánea de instrucciones que podían emitirse de manera independiente. Los esfuerzos de los arquitectos de computadores para extraer cada vez más ILP, originaron nuevos diseños que incluían ejecución fuera de orden y especulativa, predictores de saltos muy sofisticados, cauces de ejecución segmentados con muchas etapas y con una anchura de emisión considerable, etc. Aún así, el beneficio de rendimiento obtenido se veía cada vez más limitado por la influencia de: las dependencias verdaderas entre instrucciones por los riesgos de datos tipo Read-After-Write (RAW); los riesgos de control por las instrucciones de salto; o por los llamados riesgos estructurales, que serializan la ejecución de instrucciones que presentan un conflicto en el uso de un mismo recurso hardware como una unidad funcional aritmético-lógica.

A partir del presente siglo, tanta complejidad se unió al hecho de que la frecuencia de operación estaba alcanzando niveles en los que la temperatura de los chips se estaba volviendo inmanejable. Por ello, se inició un proceso de renovación de los procesadores en los que se redujo la frecuencia de operación, pero se incorporaron varios núcleos de procesamiento en el mismo chip. Esto condujo a un nuevo concepto de arquitectura denominada multiprocesador en un sólo chip o CMP. En los diseños de los CMPs, se primó más la extracción del paralelismo a nivel de hilo (Thread-Level Parallelism, o TLP) que intentar extraer más ILP. Así, el rendimiento por ciclo de ejecución comenzó a aumentar de nuevo consiguiéndose superar a los mejores uniprocesadores desarrollados hasta la fecha. A medida que más y más núcleos iban integrándose en los CMPs, estos sistemas evolucionaron a lo que hoy en día se denomina CMPs de muchos núcleos, o many-core CMPs. Los many-core CMPs están alcanzando ya el centenar de núcleos de ejecución como el procesador Tile-Gx con 100 núcleos [145]. Para simplificar el diseño de estas arquitecturas y para hacerlas escalables, se diseñan en base a un esquema modular, en el que se define un bloque básico de cómputo compuesto por un núcleo, niveles de caché privados y un fragmento de una caché compartida global, además de un enrutador que conecta con el resto de bloques de cómputo. La manera en la que se conectan todos los bloques que conforman un many-core CMP está basado en una red escalable punto-apunto como una malla 2D. Otro aspecto importante de estos sistemas es que su programación tiene que ser lo más sencilla posible para simplificar la tarea al programador. Lo más común es que estos sistemas implementen un sistema de memoria compartida [29]. Mediante éste, las operaciones de comunicación y sincronización entre los hilos de ejecución se realiza mediante operaciones de acceso a posiciones de memoria convencionales, así como instrucciones especiales para el caso de la sincronización como Load-Linked/Store-Conditional (LL/SC), o de lectura-modificación-escritura como test&set.

Sin embargo, desde el año 2004 se ha experimentado un proceso de disminución en el crecimiento constante del rendimiento principalmente por motivos de consumo excesivo de energía, tamaño de los transistores alcanzando la escala atómica, grandes costos de diseño, fabricación y verificación de los chips, etc. Lo cual ha hecho que de nuevo se reconsideren las arquitecturas actuales para idear una manera de mejorarlas sin tales problemas iniciándose una tendencia denominada *More-than-Moore* [150]. Mediante esta, los nuevos diseños arquitectónicos comparten circuitería basada en tecnología digital CMOS y tecnología menos escalable pero más rápida en transmisión de señales como las no digitales: analógica, RF u óptica.

En esta tesis hemos identificado tres de los mayores cuellos de botella para el rendimiento y escalabilidad de las arquitecturas many-core CMP. En particular, los mecanismos de sincronización de barrera y cerrojo cuando presentan alta contención, es decir, cuando hay un gran número de hilos competiendo por el uso de la barrera o bien por el acceso a la sección crítica (SC) que protege el cerrojo. Téngase en cuenta que habrá más probabilidad de contención conforme más TLP se esté extrayendo de arquitecturas many-core CMPs con cada vez más núcleos. Otro problema identificado es la eficiencia en el mantenimiento de la coherencia del uso de los bloques de memoria en todos los niveles de la jerarquía de memoria de estos sistemas de memoria compartida. Un protocolo de coherencia implementado en hardware para mayor eficiencia será el encargado de llevar a cabo esta tarea. A medida que el número de núcleos sea cada vez mayor en las arquitecturas *many-core* CMP, mayor será la actividad del protocolo para garantizar la coherencia de todas las posiciones de memoria compartidas que se utilicen para comunicar y sincronizar cada nueva generación de many-core CMPs con un mayor número de hilos. Para paliar estas deficiencias en el rendimiento y aprovechar más el rendimiento de estas arquitecturas, hemos propuesto tres mecanismos hardware que se explicarán más abajo: GBarrier, para un mecanismo de barreras eficiente; GLock, que proporciona un manejo de la contención en el acceso a las SC protegidas por cerrojos de manera justa y eficiente; y ECONO, un protocolo de coherencia muy simple que aporta gran eficiencia a bajo costo. Además, siguiendo la tendencia More-than-Moore, hemos considerando tecnología analógica actual llamada G-Lines para obtener un mayor rendimiento en nuestras propuestas. G-Lines utilizan tecnología analógica para transmitir señales de un sólo bit a lo largo de una línea que puede abarcar la totalidad de un chip a muy bajo costo y en un sólo ciclo de reloj. Por otro lado, también hemos considerado una implementación de las mismas basadas en una metodología estándar de diseño actual que se utiliza en los procedimientos convencionales de fabricación de chips, a la que llamaremos simplemente *Estándar*.

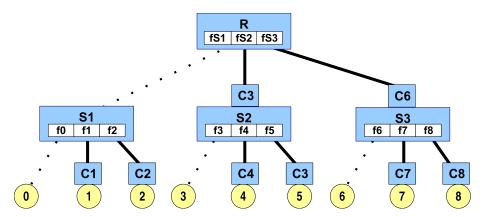

A continuación se exponen nuestras tres propuestas junto a los resultados más relevantes que hemos obtenido en los estudios realizados en esta tesis. Para superar el cuello de botella que supone la ejecución de barrera en máquinas *many-core* CMP de memoria compartida, hemos propuesto *GBarrier*. *GBarrier* es un novedoso mecanismo hardware especialmente diseñado para la ejecución de barreras de manera eficiente eliminando todas las limitaciones de rendimiento en las implementaciones basadas en software, e incluso en otras muchas, también hardware, implementadas hasta el día de hoy. En particular, nuestra propuesta consiste en dos componentes principales. El primero es una red especializada

de muy bajo costo integrada en el CMP que puede ser escalada fácilmente utilizando una esquema jerárquico. El segundo componente es un protocolo de sincronización muy simple que es ejecutado por los controladores de la red especializada. Las razón principal por la cual GBarrier es mucho más eficiente que la inmensa mayoría de las propuestas actuales, basadas en el uso de operaciones sobre posiciones de memoria compartida para la sincronización, se debe a que para la sincronización nuestro mecanismo no afecta al sistema de memoria en absoluto. La gran ventaja de esto es que evitamos toda la actividad de coherencia y todo el tráfico de red debido a la operación de barrera que las otras implementaciones necesitan y que restringe la escalabilidad, como explicamos anteriormente. Nuestra propuesta ha sido escenificada en otros contextos de operación exponiendo cómo podríamos abordarlos satisfactoriamente: la sobrecarga en la integración de varias GBarriers en un mismo CMP; cuando no todos los hilos de ejecución disponibles utilizan la barrera (GBarrier para subconjuntos de todos los núcleos del CMP); y el uso de GBarrier en arquitecturas con núcleos con soporte para múltiples hilos simultáneos (arquitecturas SMT).

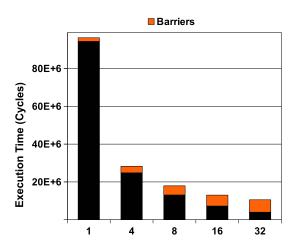

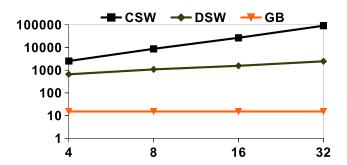

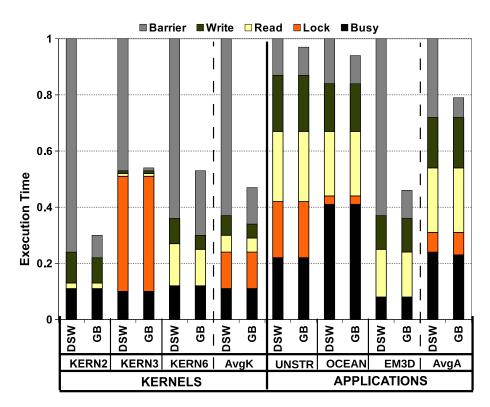

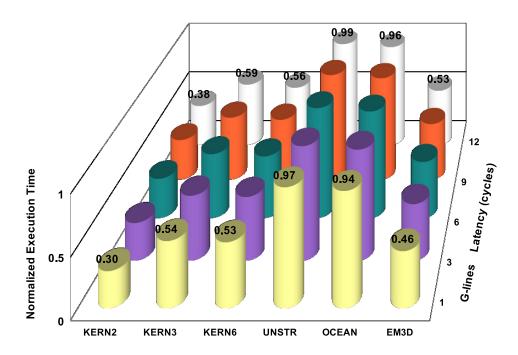

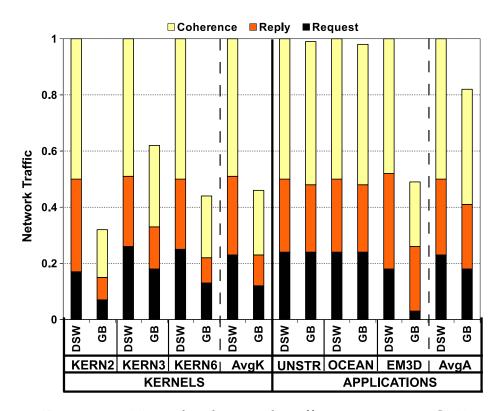

Para evaluar GBarrier, hemos considerado dos implementaciones para sintetizar nuestra infraestructura de barrera utilizando la tecnología de G-Lines y la Estándar anteriormente mencionadas. Un estudio preliminar de rendimiento potencial de ambas revela que las diferencias en términos de consumo de área y de energía pueden considerarse despreciables por los mínimos recursos hardware que requiere nuestro diseño (unos pocos controladores y cableado de anchura de un sólo bit). La diferencia estriba en que la tecnología de G-Lines proporciona mayor rapidez en las transmisiones de nuestro protocolo de sincronización, consiguiendo una barrera de menor latencia. Por otro lado con la Estándar, nuestro mecanismo se podría plasmar directamente en un circuito siguiendo los procesos actuales de fabricación de chips. Hemos integrado ambas implementaciones para GBarrier en un entorno de simulación denominado Sim-PowerCMP. A partir del cual, hemos modelado un many-core CMP de 32 núcleos de ejecución sobre el que ejecutar una serie de aplicaciones paralelas para obtener el rendimiento que ofrece nuestra propuesta (benchmarks). Así, hemos comparado rendimiento utilizando la mejor barrera software hasta el momento (barrera en árbol), tres núcleos de aplicación (o kernels) y tres aplicaciones científicas. Como conclusión de este estudio podemos decir que en cuanto a tiempo de ejecución ambas implementaciones obtienen reducciones en tiempo de ejecución muy similares, por tanto nuestro diseño para barrera no depende de tecnología no estándar para obtener una implementación de barrera eficiente en many-core CMPs. Más específicamente, para los kernels y aplicaciones científicas, las reducciones medias

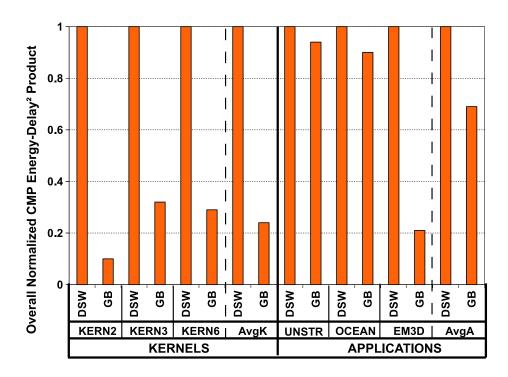

en tiempo de ejecución son del 54% y del 21%, del 53% y del 18% en tráfico de red. La razón es porque nuestra propuesta evita el tiempo dedicado al mantenimiento de coherencia de las posiciones de memoria compartidas que la implementación software emplea, y tampoco inyecta tráfico de red en la red de interconexión principal del CMP, evitando así congestión de la red por este tráfico que compite por los mismos recursos de red que el tráfico de petición y recepción de datos de las aplicaciones paralelas ejecutadas. Por otro lado, hemos evaluado la reducción del consumo de energía utilizando para ello la métrica energy-delay² product (ED²P), obteniendo reducciones medias del 76% y 31% para los kernels y aplicaciones científicas respectivamente.

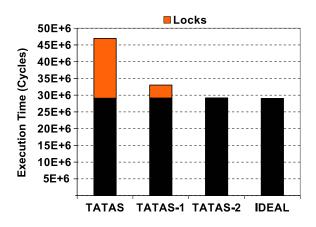

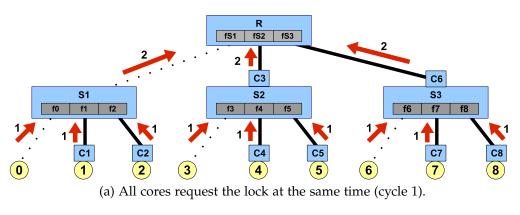

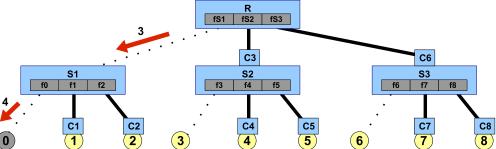

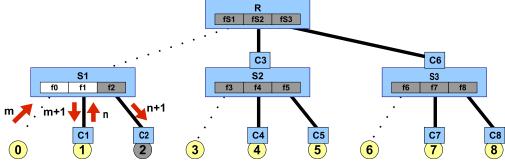

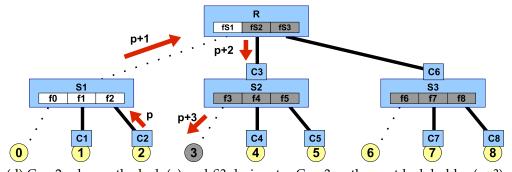

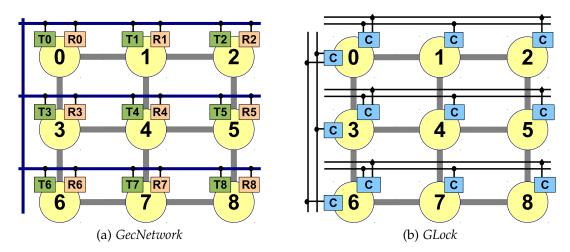

Por otro lado, para superar los problemas de rendimiento y escalabilidad de las operaciones de sincronización mediante cerrojo, hemos propuesto GLock. Nuestra propuesta está especialmente diseñada para cuando existe una alta contención en el acceso a las SC protegidas por el cerrojo, porque en este caso, las implementaciones tradicionales de cerrojo tiene serios límites de rendimiento y escalabilidad. *GLock* está basado en dos componentes principales. El primero es una red especializada de muy bajo costo integrada en el CMP, mientras que el segundo es un protocolo de sincronización basado en paso de mensajes y en transferencia de un token que será el que determine el hilo que tiene el acceso exclusivo a la SC. Debido al hecho de que nuestra propuesta se dedica a los cerrojos altamente contendidos, su ejecución se puede simultanear con otras implementaciones de cerrojos que no presentan una alta contención, tales como las implementaciones tradicionales software que utilizan instrucciones especializadas test-and-test&set. Como consecuencia de un análisis que hemos llevado acabo sobre el conjunto de benchmarks que hemos utilizado para evaluar nuestra propuesta, hemos obtenido que el número de cerrojos distintos que están altamente contendidos es bastante reducido. En particular, hemos detectado un máximo de dos cerrojos en nuestros benchmarks con alta contención por lo que hemos integrado dos *GLocks* para la evaluación.

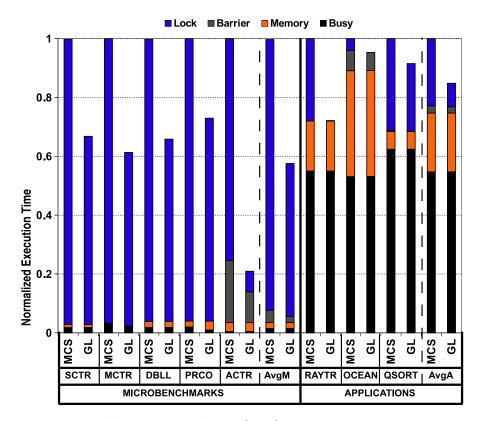

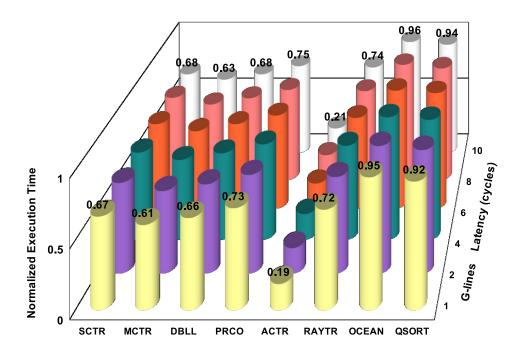

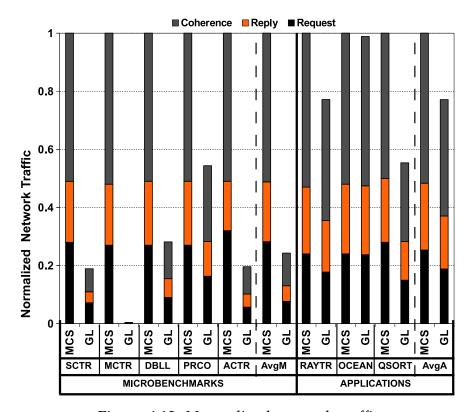

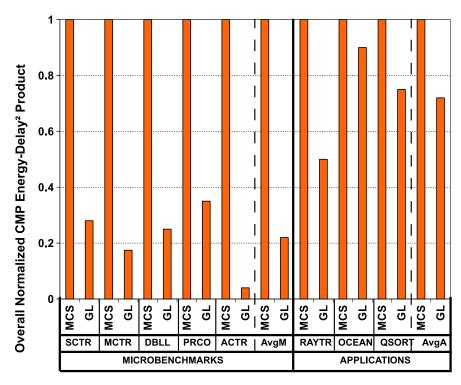

La evaluación de *GLock* también se ha llevado a cabo utilizando los dos tipos de tecnología *G-Lines* y *Estándar*, llegando a las mismas conclusiones que para *GBarrier*, es decir, existen diferencias poco significativas en el rendimiento que ofrecen ambas propuestas, con lo que *GLock* no depende de tecnología no estándar para obtener una implementación muy eficiente para cerrojos altamente contendidos; la tecnología de *G-Lines* proporciona la implementación más rápida; y finalmente, la *Estándar* reduce los costes derivados de la fabricación del *GLock* en un chip, por seguir una metodología estándar de desarrollo. Ambas implementaciones han sido integradas en Sim-PowerCMP para un *many-core*

CMP de 32 núcleos, comparando el rendimiento de nuestra propuesta frente a la mejor implementación software hasta la fecha (MCS [77]), y hemos utilizado un conjunto significativo de benchmarks basados en microbenchmarks y aplicaciones científicas. Las estadísticas de rendimiento ofrecen las siguientes reducciones medias frente a MCS: en el tiempo de ejecución del 42 % y 14 % para los microbenchmarks y aplicaciones científicas respectivamente; en tráfico, del 76 % y 23 %; y en consumo de energía utilizando la métrica ED<sup>2</sup>P, del 78 % y 28 %, para los microbenchmarks y aplicaciones científicas respectivamente.

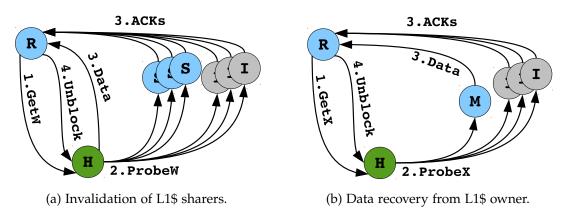

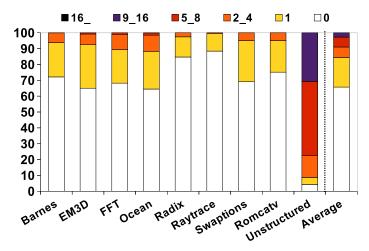

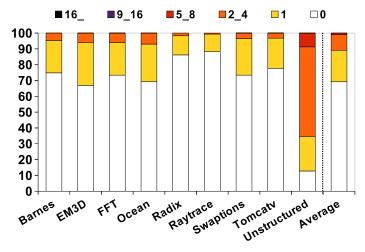

Finalmente, se ha propuesto también en esta tesis un protocolo de coherencia para many-core CMPs denominado Express Coherence Notification, o simplemente ECONO. En el mantenimiento de la coherencia, ECONO hace uso de mensajes especiales que son enviados de manera atómica y en difusión (broadcast) llamados mensajes Atomic Coherence Notification (ACN). Estos mensajes son enviados a través de una red dedicada de mínimo coste implementada mediante tecnología de G-Lines para máxima eficiencia (experimentos demuestran que la tecnología Estándar no es capaz de obtener gran rendimiento para envíos de mensajes en broadcast para todos los núcleos de una arquitectura many-core CMP). Para la implementación de ECONO, hemos obtenido una primera versión, 4-hop ECONO, que utiliza cuatro saltos en el camino crítico para hacer coherente una escritura sobre un bloque que produce un fallo de caché, y que requiere actuación del protocolo sobre otras copias del bloque de datos. Esta versión ha sido mejorada introduciendo el concepto de mensajes ACN imprecisos que envían en broadcast un subconjunto de la dirección del bloque en cuestión, y también hemos reducido a tres saltos el camino crítico obteniendo la versión 3-hop ECONO, reduciendo así el tráfico por la red de interconexión del CMP y, por tanto, el consumo de energía.

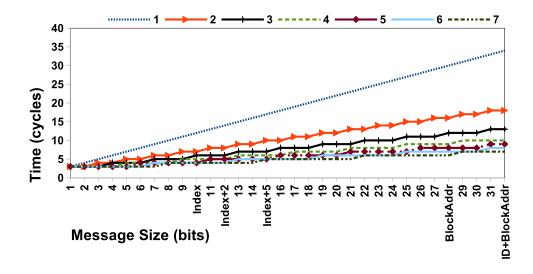

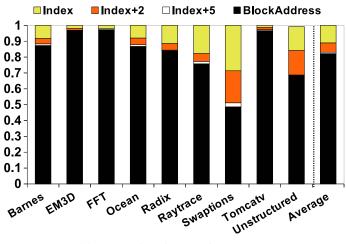

Para evaluar las distintas implementaciones de *ECONO*, hemos simulado un *many-core* CMP de 16 núcleos usando Simics-GEMS. En cuanto al máximo rendimiento potencial, hemos obtenido que *ECONO* con una red especializada compuesta por tres líneas globales implementados mediante tecnología de *G-Lines*, ofrece el mejor compromiso entre latencia del mensaje y costo en área. Por otro lado, en cuanto a la implementación de *ECONO* con mensajes *ACN* imprecisos, la configuración *Index+5* es la mejor opción. Finalmente, hemos cuantificado los beneficios en rendimiento de las anteriores versiones de *ECONO* en comparación a dos protocolos de coherencia contemporáneos: *Hammer* y *Directory*. Las principales conclusiones de este estudio son las siguientes: nuestra propuesta tiene el diseño más simple, requiere una sobrecarga en área del chip similar a *Hammer*, obtiene un rendimiento similar a *Directory*, y constituye la

implementación más eficiente en términos de energía. Finalmente, dada la gran simplicidad de nuestra propuesta, hemos identificado una serie de optimizaciones que se podrían aplicar y que utilizan algunos protocolos actuales para mejorar el rendimiento, tales como filtrado de mensajes para reducir el costo energético del envío atómico y en *broadcast* de los *ACNs*, o bien utilizar el concepto de coherencia directa, en el que se evita dirigir mensajes al directorio del protocolo, reduciendo el número de saltos en el camino crítico en el mantenimiento de la coherencia enviando dichos mensajes directamente el poseedor del bloque de datos solicitado. Podríamos implementar esto último incluyendo en el mensaje *ACN*, que es recibido de manera global, el identificador del siguiente propietario del bloque.

De todo lo anterior podemos asegurar que nuestras propuestas resuelven de una forma eficiente los problemas de rendimiento derivados de implementaciones ineficientes para sincronización mediante barrera y cerrojo en situaciones de alta contención, y de los protocolos de coherencia que han de gestionar un número mayor de compartidores de bloque, en las arquitecturas *many-core* CMP.

# Índice

| Re | esumen en español                                                               | 11  |

|----|---------------------------------------------------------------------------------|-----|

| Ą  | gradecimientos                                                                  | 17  |

| Re | esumen                                                                          | 21  |

| Ín | dice                                                                            | 25  |

| Li | sta de figuras                                                                  | 29  |

| Li | sta de tablas                                                                   | 31  |

| 1  | Introducción                                                                    | 33  |

| 2  | Metodología de evaluación                                                       | 43  |

| 3  | GBarrier: Un mecanismo hardware para barreras                                   | 61  |

| 4  | <i>GLock</i> : Un mechanismo hardware para cerrojos altamente contendidos       | 99  |

| 5  | ECONO: Un protocolo de coherencia simple y eficiente basado en difusión atómica | 135 |

| 6  | Conclusiones y vías futuras                                                     | 171 |

| Bi | bliografía                                                                      | 196 |

## **Agradecimientos**

La elaboración de esta tesis ha sido un gran reto que no habría podido superar sin la ayuda de aquellas personas que forman parte de mi vida. A ti Inma, mi esposa, por todo lo que significas para mí, lo que me has ayudado en todos estos años, lo que hemos sufrido y disfrutado juntos, por tus consejos, el ánimo que siempre me das, tu cariño y mucho más. A mis padres por la educación y todos los valores que he recibido de ellos que me han ayudado a abrir puertas en la vida, por el ánimo que siempre me habéis dado, por vuestra ayuda incondicional y por vuestros consejos. Mamá, porque eres un ejemplo de superación para mí, por tu constancia y perfeccionismo. Papá, por el ejemplo de responsabilidad y lucha que me ha ayudado a ser más fuerte, tu disciplina y organización. A mis hermanos que siempre están ahí y a los que intento dar humildemente ejemplo. Alicia, por tus consejos, tu ayuda y por creer en mí. Pedro, aunque eres aún pequeño, paso muy buenos momentos contigo que me ayudan a desconectar. A mis suegros, Antonia y Joaquín, que me han ayudado en todo y me han acogido como a un hijo desde el primer día. También a mis cuñados, Alex, Marian y Mario, con los que me divierto mucho y con los que es un placer estar. A mis primos-hermanos Alberto y Juan Antonio, con los que he compartido grandes momentos a lo largo de mi vida, con los que he disfrutado y reído mucho. A mis tíos y abuelos, sólo espero que estéis orgullosos de mí y que sepáis que os he echado de menos. También me gustaría dar las gracias a familiares no tan directos como Justo Ireno, tu experiencia como Ingeniero Informático siempre me ha servido de timón de barco, y también a Antonio, por nuestras charlas sobre informática y tecnología que realmente son un gozo.

Mencionar también a mis compañeros de fatiga durante los largos años de carrera como mi amigo Miguel Ángel y mi amigo Fernando, éste último con el que también he convivido en el máster. Sin vosotros desde luego que hubiera sido muchísimo más difícil alcanzar los objetivos. Como no, también nombrar

a mis compañeros de trabajo y amigos: Alberto, Ana, Antonio, Chema, Dani, Dani Sánchez, Epi, Ginés, Juanma, Ricardo, Rubén y Toni. Gracias por hacer del laboratorio un lugar muy agradable de trabajo y por la gran ayuda que me habéis ofrecido en todas las ocasiones que os he requerido.

Thanks to professor Davide Bertozzi for giving me the opportunity to work as a part of his team at UNIFE. My stay in Ferrara was most definitely an enriching experience where I learnt a lot, and I worked with very hard-working and wonderful guys, willing always to help me, such as Daniele Ludovici, Hervè Tatenguem and Alessandro Strano. They really allowed me to spend a very pleasant internship that I will never forget. I would like also to thank my colleague from Bologna, Andrea Marongiou, for his kindness and all those hours we spent discussing designs and results.

A mis directores de tesis, Manolo y Juan, los mejores directores de tesis que podría tener. Vuestra profesionalidad, disciplina, constancia, entrega y pasión por vuestro trabajo, me han ayudado a madurar muchísimo y a ser lo que soy a día de hoy. Gracias por darme la oportunidad de iniciar mis estudios de doctorado en el departamento, por creer en mí desde un primer momento e intentar siempre orientarme por el mejor camino. Sin duda, me habéis hecho disfrutar de este mundo apasionante de la investigación.

Finalmente, agradecer también a la Fundación Séneca (Agencia de Ciencia y Tecnología de la Región de Murcia) por su vital apoyo económico mediante una Beca-Contrato Predoctoral de Formación del Personal Investigador (FPI).

A todos, ¡MUCHAS GRACIAS!

## Universidad de Murcia Facultad de Informática

Departamento de Ingeniería y Tecnología de Computadores

# Efficient Synchronization and Communication in Many-Core Chip Multiprocessors

PhD Thesis

By José Luis Abellán Miguel

Advised by Juan Fernández Peinador Manuel Eugenio Acacio Sánchez

Murcia, September 2012

## **Abstract**

Multicore architectures (chip-multiprocessors or CMPs) constitute nowadays the best way to take advantage of the increasing number of transistors available in a single die. In particular, they provide higher performance and lower energy consumption than more complex unicore architectures. This is due to the fact that these architectures mainly focus on exploiting thread-level parallelism (TLP) rather than instruction-level parallelism (ILP). As the number of cores increases in these throughput-oriented machines, they are referred to as many-core CMPs. To ease the programmability task, these systems commonly adopt a shared-memory programming model in which communications and synchronizations among threads are accomplished by means of memory access instructions on shared variables. This thesis focuses on outperforming three of the major problems that restrict efficiency and scalability in future shared-memory tiled many-core CMPs: the synchronization operations of barriers and locks, and the cache coherence protocol.

Regarding barrier synchronization, traditional software-based barrier implementations for shared memory parallel machines tend to produce hot-spots in terms of memory and network contention as the number of cores increases. To completely remove such negative side effects we develop *GBarrier*. Our proposal is a hardware-based barrier mechanism especially aimed at providing efficient barriers in future many-core CMPs. To this end, our proposal deploys a dedicated *G-Line*-based network to allow for fast and efficient signaling of barrier arrival and departure. Since *GBarrier* does not have any influence on the memory system, we avoid all coherence activity and barrier-related network traffic that traditional approaches introduce and that restrict scalability. To implement *GBarrier*, we consider two different technologies. The first is a state-of-the-art full-custom technology, namely *G-Lines*, whilst the second is a cost-effective mainstream industrial toolflow with an advance 45 nm technology, or *Standard* technology for

short. Both *GBarrier* implementations report very similar reductions in execution time, thus not making our proposal so dependent on a full-custom technology to achieve extremely efficient synchronization in many-core CMPs. In particular, through detailed simulations of a 32-core CMP, we compare *GBarrier* against one of the most efficient software-based barrier implementations for a set of kernels and scientific applications. Evaluation results bring important average reductions when the kernels and scientific applications are considered: 54% and 21% in execution time, respectively; 53% and 18% in network traffic, respectively; and also 76% and 31% in the energy-delay<sup>2</sup> product metric for the full CMP, respectively.

With respect to lock synchronization, this is a key programming primitive for shared-memory many-core CMPs. The problem is that, as the number of cores increases so does the degree of contention that a single lock may exhibit, but in this case, conventional software implementations cannot meet the desirable levels of performance and scalability. Meanwhile, most existing hardware-supported lock proposals require modifications at some level of the memory hierarchy, thus degrading QoS of applications through synchronization traffic. To overcome such performance limitations, we propose GLock, a dedicated network infrastructure along with a token-based message-passing protocol to provide a non-intrusive, extremely efficient and fair implementation for highly-contended locks. As for GBarrier, two implementations of GLock that leverage G-Lines and Standard technologies are considered. We conclude that by leveraging both technologies significant reductions in execution time can be obtained with a negligible performance gap between them. Besides, both implementations require a minimal power dissipation and a marginal on-chip area overhead. As a result, our GLock proposal is not so dependent on full-custom technology to provide very efficient synchronization for highly-contended locks in many-core CMPs. More specifically, when compared GLock against the most efficient software-based lock using a set of microbenchmarks and real applications, we obtain average reductions of: 42% and 14% in execution time, respectively; 76% and 23% in network traffic, respectively; and 78% and 28% in the energy-delay<sup>2</sup> product (ED<sup>2</sup>P) metric for the full CMP, respectively.

Finally as to the coherence protocol, the design of an efficient coherence protocol for shared-memory many-core CMPs should take into account several aspects related to efficiency such as on-chip area overhead, energy consumption, and performance. Nevertheless, another important metric to be considered is its resulting complexity. In fact, one may opt to sacrifice some efficiency in exchange for a simpler verification process. The problem is that all these requirements are

very difficult to meet in a single coherence protocol at once. To accomplish this, we propose Express Coherence Notification (ECONO), a cache coherence protocol aimed at providing simultaneously a simple and efficient design. To maintain coherence, ECONO relies on express coherence notifications which are broadcast atomically over a dedicated lightweight on-chip network. For the implementation of this special network, differently to GBarrier and GLock, we only rely on the state-of-the-art G-Lines technology since the Standard technology is not enough to obtain an efficient and very fast implementation for the ECONO's notifications. We implement and evaluate ECONO utilizing full-system simulation and a representative set of benchmarks. As compared to two contemporary coherence protocols, Hammer and Directory, ECONO has the simplest design, requires an area overhead similar to Hammer and reports performance results similar to Directory. Particularly, ECONO achieves an average reduction of 2% in execution time and an average reduction of 3% in network traffic, when compared to Directory. In addition, our experimental evaluation also leads to conclude that ECONO is also the most energy efficient design.

# **Contents**

| Ex         | ctend | ed abstract in Spanish                            | 5  |

|------------|-------|---------------------------------------------------|----|

| Ta         | ble o | of contents in Spanish                            | 13 |

| A          | cknov | wledgments                                        | 17 |

| <b>A</b> l | bstra | c <b>t</b>                                        | 21 |

| Co         | onten | ts                                                | 25 |

| Li         | st of | Figures                                           | 29 |

| Li         | st of | Tables                                            | 31 |

| 1          | Intr  | oduction                                          | 33 |

|            | 1.1   | Towards Many-core CMPs                            | 34 |

|            | 1.2   | A Shared-Memory Programming Model                 | 36 |

|            | 1.3   | The Slowdown in Exponential Growth of Performance | 36 |

|            | 1.4   | The Synchronization Problem                       | 37 |

|            | 1.5   | The Cache Coherence Problem                       | 38 |

|            | 1.6   | The G-Lines Technology                            | 40 |

|            | 1.7   | Thesis Motivation and Contributions               | 41 |

|            | 1.8   | Thesis Organization                               | 42 |

| 2          | Eva   | luation Methodology                               | 43 |

|            | 2.1   | Target System                                     | 43 |

|            | 2.2   | Simulation Tools                                  | 44 |

|            |       | 2.2.1 Sim-PowerCMP                                | 45 |

#### Contents

|   |     | 2.2.2     | Simics-GEMS                                             | <u>1</u> 7     |

|---|-----|-----------|---------------------------------------------------------|----------------|

|   |     | 2.2.3     | Mainstream Industrial Toolflow                          | 18             |

|   | 2.3 | Bench     | ımarks                                                  | 52             |

|   |     | 2.3.1     | Microbenchmarks                                         | 52             |

|   |     | 2.3.2     | Kernels                                                 | 53             |

|   |     | 2.3.3     | Scientific and Real Applications                        | 54             |

|   | 2.4 | Metri     | cs and Methods                                          | 57             |

| 3 | GBa | arrier: 1 | An Efficient Infrastructure for Barrier Synchronization | 51             |

|   | 3.1 | Introd    | luction and Motivation                                  | 61             |

|   | 3.2 | The G     | Barrier Synchronization Mechanism 6                     | 63             |

|   |     | 3.2.1     | Dedicated On-Chip Network Architecture 6                | 64             |

|   |     | 3.2.2     | Synchronization Protocol                                | 55             |

|   |     | 3.2.3     | Programmability Issues                                  | 68             |

|   |     | 3.2.4     | Implementation of Master and Slave Controllers 6        | 59             |

|   |     | 3.2.5     | Implementation Costs for GBarrier                       | 72             |

|   |     | 3.2.6     | Generalization of the GBarrier mechanism                | <sup>7</sup> 4 |

|   | 3.3 | Perfo     | rmance Implications                                     | 78             |

|   |     | 3.3.1     | Implementation Technologies                             | 78             |

|   |     | 3.3.2     | Raw Performance Statistics                              | 30             |

|   | 3.4 | Evalu     | ation 8                                                 | 32             |

|   |     | 3.4.1     | Experimental Setup                                      | 32             |

|   |     | 3.4.2     | Barrier implementations                                 | 33             |

|   |     | 3.4.3     | Performance Results                                     | 35             |

|   | 3.5 | Relate    | ed Work                                                 | 93             |

|   | 3.6 | Concl     | usions                                                  | 97             |

| 4 | GLo | ck: An    | Efficient Infrastructure for Highly-Contended Locks 9   | 99             |

|   | 4.1 | Introd    | luction and Motivation                                  | 99             |

|   | 4.2 | The G     | <i>GLock</i> Synchronization Mechanism                  | )2             |

|   |     | 4.2.1     | Dedicated On-Chip Network Architecture                  | )2             |

|   |     | 4.2.2     | Synchronization Protocol                                | )4             |

|   |     | 4.2.3     | Programmability Issues                                  | )7             |

|   |     | 4.2.4     | Implementation of <i>GLock</i> 's controllers           |                |

|   |     | 4.2.5     | Implementation Costs for GLock                          |                |

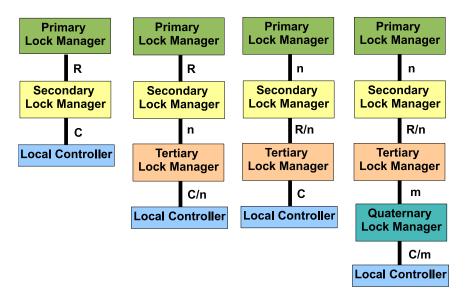

|   |     | 4.2.6     | Generalization of the <i>GLock</i> Mechanism            | .3             |

|   | 4.3 | Perfo     | rmance Implications                                     |                |

|   |     | 4.3.1     | Implementation Technologies                             | .6             |

|    |       | 4.3.2   | Raw Performance Statistics                        |

|----|-------|---------|---------------------------------------------------|

|    | 4.4   | Evalua  | ation                                             |

|    |       | 4.4.1   | Experimental Setup                                |

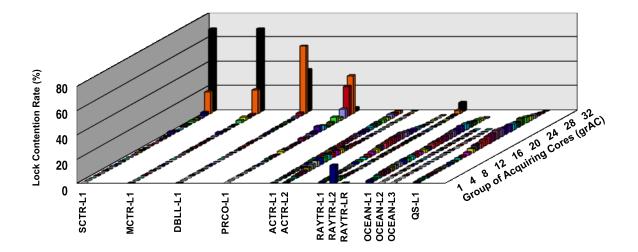

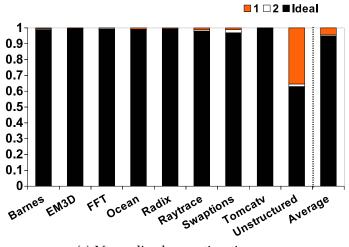

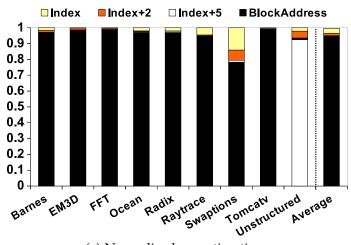

|    |       | 4.4.2   | Post-morten Analysis of Benchmarks                |

|    |       | 4.4.3   | Lock Implementations                              |

|    |       | 4.4.4   | Performance Results                               |

|    | 4.5   | Relate  | d Work                                            |

|    | 4.6   | Conclu  | usions                                            |

| 5  | ECC   | NO: A   | Simple and Efficient Cache Coherence Protocol 135 |

|    | 5.1   | Introd  | uction and Motivation                             |

|    | 5.2   | Two C   | Contemporary Coherence Protocols                  |

|    |       | 5.2.1   | Hammer                                            |

|    |       | 5.2.2   | Directory                                         |

|    | 5.3   | ECON    | O Coherence Protocol                              |

|    |       | 5.3.1   | Baseline Operation                                |

|    |       | 5.3.2   | Extensions to the Baseline ECONO                  |

|    |       | 5.3.3   | Physical Implementation                           |

|    | 5.4   | Perfor  | mance Implications                                |

|    |       | 5.4.1   | <i>ACN</i> Latency                                |

|    |       | 5.4.2   | Hardware Resources                                |

|    |       | 5.4.3   | Power Dissipation                                 |

|    |       | 5.4.4   | Scalability                                       |

|    | 5.5   | Evalua  | ation                                             |

|    |       | 5.5.1   | Experimental Setup                                |

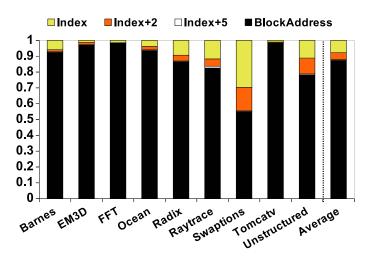

|    |       | 5.5.2   | Characterization of the ECONO Protocol 154        |

|    |       | 5.5.3   | Performance Results                               |

|    | 5.6   | Relate  | d Work                                            |

|    | 5.7   | Conclu  | usions                                            |

| 6  | Con   | clusion | ns and Future Ways 171                            |

|    | 6.1   | Conclu  | usions                                            |

|    | 6.2   |         | e Ways                                            |

| Bi | bliog | raphy   | 181                                               |

# **List of Figures**

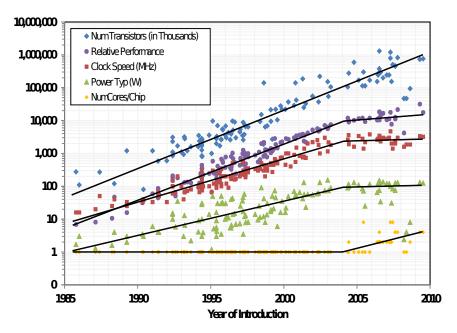

| 1.1  | 17 Transistors, frequency, power, performance, and cores over time (1985-2010). Source: D. Patterson, UC-Berkeley | 37  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 2.1  | 3×3-core CMP architecture with a 2D-mesh topology                                                                 | 44  |  |  |  |

| 2.2  | How parallel applications are transformed for simulation in Sim-                                                  |     |  |  |  |

|      | PowerCMP                                                                                                          | 45  |  |  |  |

| 2.3  | Architecture of the Simics-GEMS simulation framework                                                              | 47  |  |  |  |

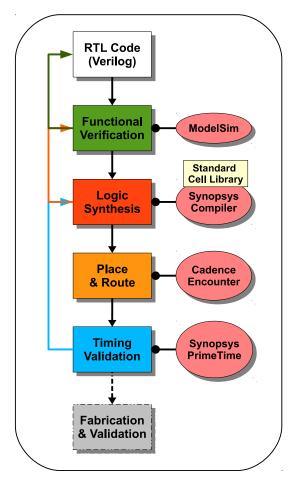

| 2.4  | Mainstream industrial toolflow                                                                                    | 49  |  |  |  |

| 3.1  | Fraction of time due to barriers in EM3D                                                                          | 62  |  |  |  |

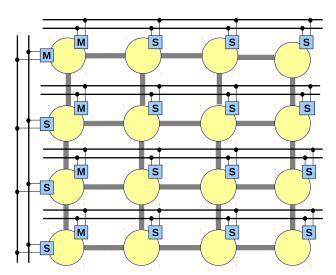

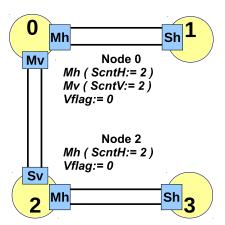

| 3.2  | GBarrier architecture for a 16-core CMP with a 2D-mesh network 6                                                  |     |  |  |  |

| 3.3  | GBarrier for a 4-core CMP with a 2D-mesh network showing initial                                                  |     |  |  |  |

|      | state of registers and flags                                                                                      | 66  |  |  |  |

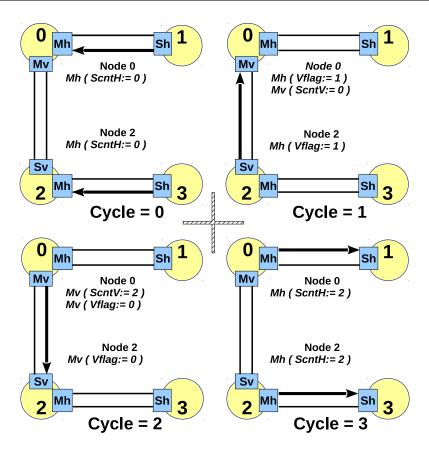

| 3.4  | Barrier synchronization under GBarrier                                                                            | 67  |  |  |  |

| 3.5  | Encapsulating the <i>GBarrier</i> functionality into the <i>GL_Barrier</i> method                                 | 69  |  |  |  |

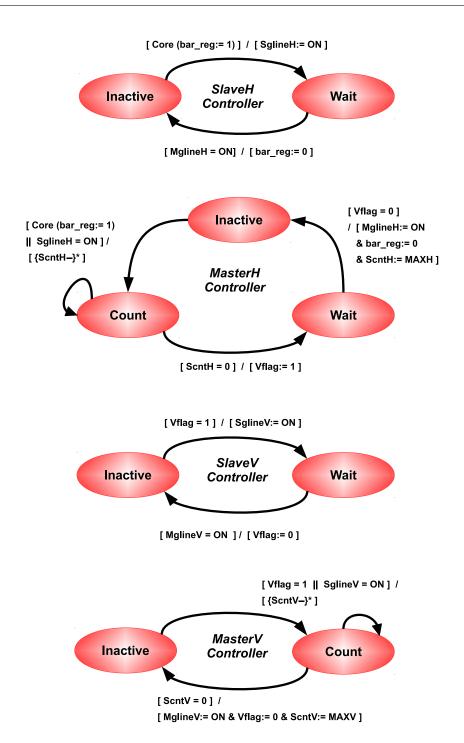

| 3.6  | Finite state automata that implement the <i>G-Line</i> controllers                                                | 70  |  |  |  |

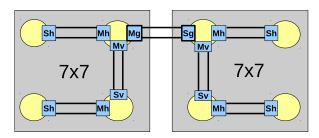

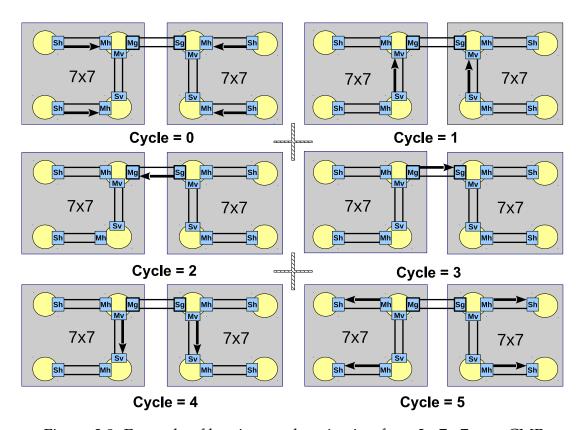

| 3.7  | Hierarchical <i>GBarrier</i> for a $2\times7\times7$ -core CMP                                                    | 76  |  |  |  |

| 3.8  | Example of barrier synchronization for a $2\times7\times7$ -core CMP                                              | 76  |  |  |  |

| 3.9  | Average times for three different barrier mechanisms                                                              | 85  |  |  |  |

| 3.10 | Normalized execution time over a 32-core CMP                                                                      | 86  |  |  |  |

| 3.11 | Normalized execution times for the benchmarks depending on the                                                    |     |  |  |  |

|      | latency of the <i>G-Lines</i> (a 32-core CMP is assumed)                                                          | 89  |  |  |  |

|      | Normalized network traffic over a 32-core CMP                                                                     | 91  |  |  |  |

| 3.13 | Normalized ED <sup>2</sup> P metric for the full CMP                                                              | 92  |  |  |  |

| 4.1  | Potential benefits for Raytrace when using ideal locks                                                            |     |  |  |  |

| 4.2  | GLock architecture for a 9-core CMP with a 2D-mesh network                                                        | 103 |  |  |  |

#### LIST OF FIGURES

| 4.3  | Logical view of the <i>link</i> -based network for a 9-core CMP with a 2D-mesh network                                                                | 104 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4  | Example of lock synchronization under the <i>GLock</i> mechanism                                                                                      |     |

| 4.5  | Encapsulating the <i>GLock</i> functionality into the lock/unlock library-                                                                            | 100 |

| 2.0  |                                                                                                                                                       | 108 |

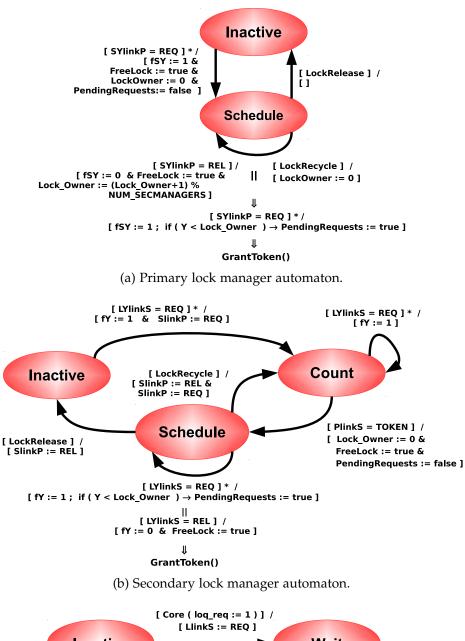

| 4.6  | Finite state automata that implement the <i>GLock</i> 's controllers                                                                                  | 110 |

| 4.7  | C++-like pseudo-code for the GrantToken function in order to assign                                                                                   |     |

|      | the token                                                                                                                                             | 111 |

| 4.8  | Different schemes to incorporate additional levels into the initial three-level hierarchy (the left-most scheme) for an $R \times C$ -core CMP with a |     |

|      | 2D-mesh network                                                                                                                                       | 114 |

| 4.9  | Lock contention rate                                                                                                                                  |     |

| 4.10 | Normalized execution time                                                                                                                             |     |

|      | Normalized execution times of benchmarks depending on <i>G-Lines</i>                                                                                  |     |

|      | latency running on a 32-core CMP                                                                                                                      | 128 |

| 4.12 | Normalized network traffic                                                                                                                            |     |

| 4.13 | Normalized energy-delay $^2\ product\ (ED^2P)$ metric for the full CMP                                                                                | 130 |

| 5.1  | Examples of coherence scenarios under the <i>Hammer</i> protocol                                                                                      | 138 |

| 5.2  | Examples of coherence scenarios under the <i>Directory</i> protocol                                                                                   |     |

| 5.3  | Examples of coherence scenarios under the baseline <i>ECONO</i> protocol.                                                                             |     |

| 5.4  | Format of the <i>ACN</i> messages for both implementations of <i>ECONO</i>                                                                            |     |

| 5.5  | Extra HW resources per Tile: C, T and R controllers                                                                                                   | 146 |

| 5.6  | Dedicated networks required for a 9-tile CMP                                                                                                          | 147 |

| 5.7  | Propagation delays for ACN messages using different G-Lines for the                                                                                   |     |

|      | GecNetwork                                                                                                                                            | 149 |

| 5.8  | Performance depending on the number of <i>GecNetworks</i>                                                                                             | 155 |

| 5.9  | Performance characterization for different types of ACN messages                                                                                      | 158 |

| 5.10 | Effect on L1 cache misses depending on the use of the <i>state</i> and <i>sharing</i>                                                                 |     |

|      | filters                                                                                                                                               | 159 |

| 5.11 | Characterization of coherence activity in the <i>Directory</i> protocol                                                                               | 161 |

| 5.12 | Normalized execution times                                                                                                                            | 162 |

| 5 13 | Normalized network traffic                                                                                                                            | 163 |

# **List of Tables**

| 2.1 | Summary of the evaluation methodology                                              |

|-----|------------------------------------------------------------------------------------|

| 3.1 | Hardware Cost of GBarrier for a 2D-mesh CMP layout with R rows                     |

|     | and C columns ( $R \times C = N$ cores)                                            |

| 3.2 | Raw statistics using <i>G-Lines</i> and <i>Standard</i> technologies for a single  |

|     | GBarrier in a 32-core CMP layout                                                   |

| 3.3 | CMP baseline configuration                                                         |

| 3.4 | Configuration of the benchmarks used in this chapter 84                            |

| 3.5 | Speedups for the scientific applications                                           |

| 3.6 | Normalized execution times for <i>G-Lines</i> and <i>Standard</i> technologies 88  |

| 4.1 | Cost of GLock for a 2D-mesh CMP layout with R rows and C columns                   |

|     | for a total of $R \times C = N$ cores                                              |

| 4.2 | Raw statistics using G-Lines and Standard technologies for a single                |

|     | GLock in a 32-core CMP layout                                                      |

| 4.3 | CMP baseline configuration                                                         |

| 4.4 | Configuration of the benchmarks and lock-related characteristics 122               |

| 4.5 | Speedups for the real applications                                                 |

| 4.6 | Normalized execution times for <i>G-Lines</i> and <i>Standard</i> technologies 127 |

| 5.1 | Hardware cost of ECONO architecture for a 2D-mesh CMP layout 150                   |

| 5.2 | CMP baseline configuration                                                         |

| 5.3 | Benchmarks and input sizes                                                         |

Chapter

## Introduction

For the last half-century, computers have been doubling in performance and capacity every couple of years. Such phenomenal progress is a consequence of the well-known Moore's Law that has been basically sustained till 2000s thanks to the continuous advances in semiconductor technology, to obtaining ever-shrinking transistor sizes, and achieving ever higher clock frequencies. This allowed computer architects to make use of the ever-increasing amount of silicon resources to design more and more sophisticated and ever-faster pipelines in uniprocessor systems, in order to better exploit the instruction level parallelism (ILP) present in sequential programs. Nonetheless, at the beginning of this century this successful strategy has come to an end mainly due to the thermal-power issues. The response was a shift towards parallel architectures that mainly focus on exploiting thread level parallelism (TLP) rather than ILP, laying the foundation of the core era. Multicore architectures, multiprocessor in general, are systems specially tailored to the exploitation of massive throughput by incorporating many simpler and lower-frequency computing units. This paradigm shift towards this throughput-oriented machines brings about new fundamental challenges to harness their ever-increasing peak potential power. Therefore, it is imperative that programmers can deal with a simple and efficient programming model such as a shared-memory programming model [29]. Nevertheless, computer architects must struggle to mitigate some performance bottlenecks related to this intuitive programming model. For instance, when considering synchronization operations, such as locks and barriers, or when ensuring coherence across all levels of a memory hierarchy through a cache coherence protocol implemented in hardware.

#### 1.1 Towards Many-core CMPs

The steady evolution of computing has been made possible mainly thanks to the contribution of the three following factors: *technology scaling* that propitiates opportunities for *architectural innovations* and *advances in compilation*. The technology roadmap for semiconductor technology was already predicted by Gordon E. Moore who stated in 1965 that the number of transistors per silicon area would double every eighteen months due to the transistors getting smaller every successive process technology [42]. This is commonly known as the Moore's Law and, surprisingly, it is expected to remain valid and continue well into the future [5,16].

Over the years, we can identify two major different trends that have marked and guided manufacturing of every new computing architecture at industry. The first-stage trend that took a longer period of time was valid till approximately year 2000 by following a virtuous cycle, by which computer architects obtained higher performance in every new design basically by shrinking feature sizes and increasing frequency of circuits. In this way, an increased transistor density enabled more and more space on chip for incorporating ever complex designs with very-deep instruction pipelines [43], highly speculative [117], out-of-order processors [46] and larger on-chip cache hierarchies [109]. The main purpose to do so was to increase the amount of work performed in each cycle allowing more and more capability to execute multiple instructions from the same (sequential) program simultaneously, i.e., the extraction of ILP. However, since year 2000 and despite new progress in integration technology, the efforts to design very aggressive and very complex wide issue superscalar processors in this trend came to a stop. While there is still a little ILP left to be extracted, RAW (readafter-write) data hazards between consecutive instructions, control hazards due to branch instructions, as well as structural hazards which serialize the execution of instructions that try to use the same hardware resource at the same time (i.e. an arithmetic and logic unit, or ALU), made impossible to increase performance without a considerable effort [72]. Moreover, even the investment of the ever larger on-chip caches reached the point of diminishing return [86]. As a result, every new performance improvement has been empirically close to the square root of the number of required transistors [72]. Besides, a higher and higher clock frequency for a faster circuitry involves important heat problems and high energy consumption. Moreover, the efforts to maintain manageable parameters for the thermal-power issues such as increased threshold voltage to control leakage, or limited supply-voltage scaling, decrease the performance benefits of transistor

scaling [56]. All above problems were identified as the *Power, Memory*, and *ILP Walls* [85].

The second-stage and current trend consists of a paradigm shift towards multi-core architectures. Instead of scaling performance by improving single core performance as was done in the past, the growing of performance is achieved by putting multiple cores onto a single chip and usually connecting them through a shared memory [30], thereby effectively integrating a complete multiprocessor on one chip. This type of systems are commonly referred to as chip multiprocessors or CMPs. In this systems, rather than ILP, they improve system performance by exploiting thread-level parallelism (TLP). CMPs have important advantages over very wide-issue out-of-order superscalar processors. In particular, they provide higher aggregate computational power, multiple clock domains, better power efficiency, and simpler designs. Additionally, the use of simpler cores reduces the cost of design and verification in terms of time and money.

While the number of cores currently offered in general-purpose CMPs has already gone above ten (e.g. the 6-core 2-die AMD's Magny-Cours design [115], the 18-core BlueGene/Q [114], or the 16-core SPARC T3 [73]), now that the Moore's Law will make it possible to double the number of processing cores per chip every 18 months [86], very soon there will be available on-chip the resources required to integrate dozens of cores or even hundreds of them. CMPs of this kind are commonly referred to as many-core CMPs. Examples of this new generation of CMPs can be the following. The 48-core Single-chip Cloud Computer [55], an experimental research microprocessor developed by Intel in the context of the Tera-scale Computing Research Program. The Intel Polaris [92] which is a prototype with 80 cores. And the Tile-Gx Processor [145] from Tilera Corporation which is comprised of up to 100 cores on a chip. For the success of this kind of systems in the future, all elements that could compromise system scalability must be avoided. One of such elements is the interconnection network. As stated in [124], the area required by a shared interconnect, like a bus, as the number of cores grows has to be increased to the point of becoming impractical. Hence, it is necessary to turn to a scalable interconnection network.

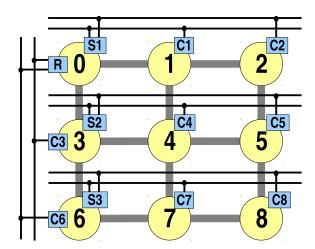

In this thesis, we focus on tiled many-core CMPs [93,103] which are designed as arrays of identical or close-to-identical building blocks known as tiles, that provide a scalable alternative to current small-scale CMP designs and help in keeping complexity manageable. In these architectures, each tile is comprised of a processing core (or even several cores), one or several levels of caches, and a network interface or router that connects all tiles through a tightly integrated and lightweight point-to-point interconnection network (e.g., a two-dimensional

mesh). Differently from shared networks, point-to-point interconnects are suitable for many-core CMPs because their peak bandwidth and area overhead scale with the number of cores.

#### 1.2 A Shared-Memory Programming Model

The different threads of a parallel program need to communicate and synchronize in order to carry out a task cooperatively to completion. For this matter, two popular types of general-purpose communication abstractions exist, which provide a link between the software (programming model) and the hardware (physical implementation). Threads can exchange information by sending messages (message passing model), or by merely accessing and modifying shared memory locations (shared memory model).

This thesis focuses on a shared memory model, as is widely regarded as a more intuitive model than message passing for the development of parallel programs [90] and nowadays is the prevalent model in most CMPs [72], and the common belief is that future many-core CMP architectures will also implement this memory model. Particularly, the hardware-managed, implicitly-addressed, coherent caches memory model [75]. With this memory model, all on-chip storage is used for private and shared caches that are kept coherent by hardware. Communication between threads is performed by writing to and reading from shared memory. In order to guarantee the integrity of shared data structures, most current systems support synchronization through a combination of hardware (special instructions, such as *LL/SC*, or atomic read-modify-write instructions, such as *test&set*, that operate on shared memory) and software (higher-level mechanisms such as locks or barriers implemented atop the underlying hardware primitives) [29].

#### 1.3 The Slowdown in Exponential Growth of Performance

In the near term, there are new challenges to tackle with in the multicore revolution. It is due to the fact that, although for every technology generation the transistor integration is doubled and the number of cores on chip grows apace, a flattened curve for the growth of performance has been appreciated [127] mainly due to reducing power and frequency parameters to alleviate the thermal-power

Figure 1.1: Transistors, frequency, power, performance, and cores over time (1985-2010). *Source: D. Patterson, UC-Berkeley.*

issues by adjusting to a realistic power budget and thermal envelope. Figure 1.1 depicts such a new trend observed since 2004 that shows flattening curves for performance, frequency and power, while the number of transistors and cores keep the expected growing. This demands new research efforts to develop new architectural solutions in order to continue with the exponential growth of performance to be kept alive in the future. In an attempt to continue in that direction, this thesis identifies two of the most severe performance bottlenecks in many-core CMPs, synchronization and the maintenance of cache coherence, and proposes hardware-based infrastructures to mitigate them as the core count increases in future developments. To gain insight into these main problems to continue with scalable performance, the next two sections delve into them and introduce our proposals.

## 1.4 The Synchronization Problem

By relying on a shared-memory programming model to execute parallel applications in many-core CMPs, conventional implementations of synchronization operations, such as barrier and locks, rely on shared variables which are atomically updated. In particular, when considering global barriers and highly-contended locks (i.e. there is a significant amount of threads requesting the lock at the same time), without the proper hardware support, this kind of software-based implementations cannot provide good scalability as the number of cores increases.

Regarding barrier implementations in software, as we will discuss in Chapter 3, the use of shared variables implies a performance bottleneck, an evergrowing amount of resources and high energy consumption requirements. In more depth, the cache coherence protocol must come into play to maintain memory consistency across all levels of the memory hierarchy. In turn, coherence activity translates into traffic injection in the interconnection network that may interfere with application-related traffic. On the other hand, the busy-waiting required to wait for the completion of the barrier synchronization on locally-cached shared variables has also significant implications on the energy consumed by the L1 caches.

As to the software implementations for the highly-contended locks, as we will expose in Chapter 4, these operations are very critical to performance since lock contention causes serialization. Therefore, an implementation based on the use of shared variables is not efficient enough due to the performance bottlenecks, the ever-growing amount of resources and high energy consumption requirements, that they produce as explained above.

In this thesis we address these two problems separately. Particularly, we deal with neither shared variables nor traffic injection into the main interconnect to implement these mechanisms for tiled many-core CMPs. Instead, we design a dedicated on-chip network infrastructure to implement a very efficient hardware-based barrier, and another one that achieves very efficient hardware support for highly-contented locks.

## 1.5 The Cache Coherence Problem

The communication and synchronization operations among threads in shared-memory parallel machines occurs implicitly as a result of reading from and writing to shared variables. The order by which all threads see the changes in the shared variables is defined according to a particular memory consistency model [133]. CMPs normally include a memory hierarchy with one or more levels of private caches to each core to avoid the increasing gap between processor and memory speeds (i.e. the *Memory Wall* [149]). The reason is that the smaller and faster private levels absorb the vast majority of memory accesses due to the

exploitation of temporal and spatial locality that applications exhibit, thereby reducing the average memory access latency and network traffic in the CMP's interconnect. As a result, in a given instant of time, there could be several copies of a particular memory location (or block) in the private caches. If a core modifies its local copy without any further action, subsequent memory accesses on the remaining sharers' copies of the memory block would read or write a stale block resulting in data incoherence. While this task could be solved in software by programmers (like in message-passing programming) a hardware-based coherence protocol is commonly in charge to do that. Clearly, the main benefit is a simplification in programming because all caches are completely transparent to software. Moreover, the coherence protocol precludes application's execution from any data incoherence by guaranteeing that each read to every memory block returns the latest value written to it, and the semantic is that each write to the same memory location appears to be seen in the same order by all processors [87].

From all above, we can affirm that the efficiency of communication and synchronization operations among threads is highly dependent upon the efficiency of the cache coherence protocol. In consequence, a great deal of attention has long been devoted to the development of cache coherence protocols, with a first-order goal of achieving scalability and efficiency in each new generation of sharedmemory parallel machines. In this way, in the late 80s and the beginning of the 90s there were a number of shared memory multiprocessors with a processor count even reaching several hundreds in a scalable and efficient manner, such as the SGI Origin 2000 [74]. Since then, latency/bandwidth tradeoffs have brought a broad variety of coherence proposals such as those that follow a broadcast-based (snooping) approach, or the point-to-point based (directory) cache coherency protocols. However, in the context of many-core CMPs, different technological parameters and constraints must be considered. For example, cache-to-cache miss latencies are relatively shorter and the on-chip bandwidth is much larger than for the "off-chip" systems of the 90s. On the other hand, design decisions are severely constrained by power dissipation.

As we will expose in Chapter 5, the design of an efficient coherence protocol for shared-memory many-core CMPs should take into account several aspects related to efficiency such as on-chip area overhead, energy consumption, and performance. Nevertheless, another important metric to be considered is its resulting complexity. In this thesis, we propose an efficient and simple coherence protocol to meet with those requirements at once.

## 1.6 The *G-Lines* Technology

The continuous improvements in CMOS transistors following the Moore's Law will come to a stop in the near future because of several challenges: unsustainable power dissipation, physical limits of transistors reaching atomic scale dimensions, process and device variability, no real performance increases with scaling, and expensive R&D and manufacturing costs. To overcome that, chipmakers have recently begun to reconsider the *More-than-Moore* trend [150], where added value to devices is provided by incorporating functionalities that do not necessarily scale according to the Moore's Law. That is the reason why the future roadmap for semiconductor technology integrates both digital and non-digital technologies in the same chip [56]. Examples for the latter technology are: analog circuits, RF, optical technology, etc.

In this thesis, we make use of a state-of-the-art analog technology, namely Global Lines technology, or G-Lines from now on. G-Lines have already been successfully integrated in a silicon substrate in order to enable speed-of-light point-to-point communications. Chang et al. [126] and Jose et al. [9] showed early point-to-point circuits allowing transmission-line, wave-like velocity for 10 mm of interconnect. Nonetheless, this initial implementation suffers from significant overheads in terms of power dissipation and die area. A great effort has been devoted to overcome such limitations. For instance, Ito et al. [48] extended G-Lines to support broadcast, multi-drop and bidirectional transmissions. This contribution enables both low-latency and multi-drop ability on a transmission line with low-power dissipation. However, their results still exhibit several integration density issues. Additionally, Ho et al. [122] and Mensink et al. [39] have shown that a capacitive feedforward method of global interconnect reduces both power dissipation and die area overheads. In particular, they achieve nearly single-cycle delay for long wires with voltage-mode signaling. As a result, every G-Line is basically a shared wire that broadcasts 1-bit messages (signals from now on) across one dimension of the chip in a single clock cycle. A practical use of G-Lines is presented by Krishna et al. [142] in the context of networks-on-chip (NoC). Krishna et al. leveraged G-Lines using multi-drop connectivity and the S-CSMA collision detection technique to enhance a flow control mechanism (EVC) in terms of latency and power dissipation. In particular, these G-Lines are used to broadcast the control signals of EVC in order to communicate the availability of free buffers and virtual channels much more accurately. Furthermore, the authors employ the S-CSMA technique to calculate how many virtual channels or free buffers are demanded at any time in order to grant requests accordingly.

As we will see, in this thesis we also leverage this technology to deploy dedicated *G-Line*-based networks on chip, in order to implement synchronizations and coherence protocols to overcome the previously described performance limitations in future many-core CMPs.

#### 1.7 Thesis Motivation and Contributions

Many-core CMPs demand new solutions to keep up with the exponential growth in performance as historically has been made and predicted. The previous sections have exposed some of the major actual performance limitations which are present in this kind of systems that we have categorized in synchronization and coherence problems (Sections 1.4 and 1.5). We have also considered to make use of special technology in Section 1.6 that, due to its extremely fast nature and minimal area overhead and power dissipation, helped us provide very efficient hardware-based implementations to overcome such performance limitations.

The main contributions of this thesis are summarized as follows:

- An *efficient hardware-based barrier implementation*, namely *GBarrier*, based on two main components. First, a very lightweight dedicated on-chip network that could be deployed in a hierarchical layout for scalability. And second, a very simple synchronization protocol. By levering both full-custom *G-Lines* technology and a nowadays standard toolflow to implement our proposal, we have found significant performance improvements for a simulated many-core CMP in terms of execution time, network traffic and energy consumption in comparison to the most efficient software-based barrier to date. Finally, we conclude that our proposal is not so dependent on full-custom technology to achieve significant improvements, by requiring negligible on-chip area and minimal power dissipation for both technologies.

- An efficient hardware-based infrastructure for highly-contended locks, namely GLock, which deploys a dedicated on-chip network and relies on a simple token-based messaging-protocol in order to provide an extremely efficient and completely fair lock implementation. To implement GLock, we have also considered two technologies: full-custom G-Lines technology and standard technology. Independently of the type of technology used, our proposal achieves significant improvements in execution time, network traffic and energy consumption when comparing this metrics with respect to the

most efficient software-based implementation for highly-contended locks. Moreover, *GLock* requires minimal on-chip area overhead and negligible power dissipation for both technologies.

• A simple and very efficient cache coherence protocol, namely ECONO, is designed for future many-core CMPs. In ensuring coherence, our proposal relies on express coherence notifications which are broadcast atomically over a dedicated lightweight on-chip network leveraging *G-Lines* technology for superior efficiency. While our protocol meets simplicity in its design, a performance comparison in a simulated many-core CMP platform against two contemporary coherence protocols, brings about a high efficiency in terms of execution time, network traffic, and is the most energy efficient design.

All the contributions of this thesis have been published in national conferences [66], [70], relevant international peer reviewed conferences [63], [65], [64], [67], [71] and relevant peer reviewed journals [69], [68]. Moreover, *ECONO* is currently being considered for publication in an international peer reviewed conference.

## 1.8 Thesis Organization

The rest of this thesis is organized as follows:

- Chapter 2 discusses the many-core CMP architecture considered, delves into the simulation tools employed, and gives a description of the workloads and metrics used throughout the thesis.

- Chapter 3 presents and evaluates our *GBarrier* proposal for barrier synchronization in many-core CMPs.

- Chapter 4 presents and evaluates our *GLock* proposal for highly-contended locks in many-core CMPs.

- Chapter 5 presents and evaluates our *ECONO* proposal for a simple and efficient coherence protocol in many-core CMPs.

- Chapter 6 summarizes the main conclusions of the thesis and points out future lines of work.

## **Evaluation Methodology**

This chapter presents the experimental methodology that we have followed throughout this thesis to implement and evaluate our proposals. For that, we start in Section 2.1 by describing the target system that we based on to incorporate our hardware optimizations. The simulation tools used are presented in Section 2.2 The descriptions of the benchmarks running on top of the simulation tools appear in Section 2.3. Finally, Section 2.4 discusses the metrics and methods to quantify the performance benefits that our proposals achieve and, at the end of this section, we summarize in a table the main characteristics of this evaluation methodology.

## 2.1 Target System

We choose a tiled CMP design as reference because its modular nature has made it popular in several commercial many-core designs [53,54,121]. The basic architecture is designed as arrays of identical or close-to-identical building blocks knowns as tiles, overlaid over a point-to-point interconnect typically forming a mesh-based network-on-chip. From now on, this kind of system will be referred to as tile-based many-core CMP, or simply many-core CMP.

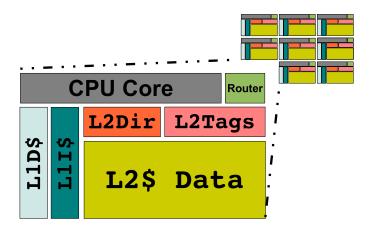

An example of this kind of system is shown in Figure 2.1 for a  $3\times3$ -core CMP with a 2D-mesh layout. We can observe that each tile has a processing core, one level of private cache, a slice of the level-two cache along with its directory entries, and some routing logic. Considering that part of the appeal of CMPs is their ability to exploit TLP and provide higher throughput than a wider-issue uniprocessor while consuming less energy per operation, we have modeled the

Figure 2.1: 3×3-core CMP architecture with a 2D-mesh topology.

processing cores of our CMP architecture after lightweight, in-order processors. Split instruction and data caches are available at the private level, while the second level is unified, physically distributed but logically shared amongst all processing cores. Private caches are kept coherent across the unordered network through an on-chip distributed directory protocol. The L1 caches maintain inclusion with the L2 cache, trading off some on-chip capacity for lower design complexity in the coherence controllers. Moreover, we use the less significant bits of the block address to determine the home tile for every memory block.

While our proposals have been specifically designed for a many-core CMP, different settings for this basic system have been evaluated in function of the type of simulation tool employed as well as the optimization proposed. This is the reason why we defer the specific details of each simulated system to the chapter where the particular proposal is described, optimized and evaluated.

## 2.2 Simulation Tools

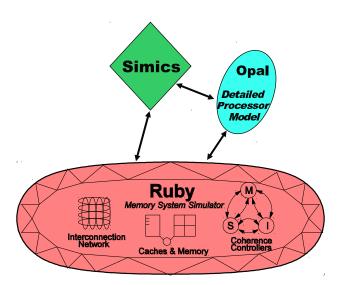

As our proposals have their own idiosyncrasies and involve different optimizations in the context of many-core CMPs, we have chosen two different simulation tools: Sim-PowerCMP, to implement *GBarrier* and *GLock*; and Simics-GEMS, to implement *ECONO*. Moreover, we utilize a toolflow to determine efficiency using a current industrial standard cell design methodology.

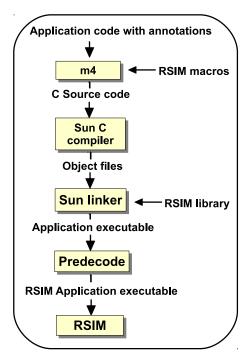

Figure 2.2: How parallel applications are transformed for simulation in Sim-PowerCMP.

#### 2.2.1 Sim-PowerCMP

Sim-PowerCMP [3] is a detailed architecture-level power-performance simulation tool that models tiled-CMP architectures with a shared L2 cache on-chip and a MESI directory-based cache coherence protocol. Particularly, this simulator is based on a Linux x86 port of RSIM [24] and models a CMP architecture consisting of arrays of replicated tiles connected over an on-chip network. Each tile contains a processing core with primary caches (both instruction and data caches), a slice of the L2 cache, and a connection to the on-chip network as shown in Figure 2.1. Sim-PowerCMP estimates power dissipation by implementing already proposed and validated power models for both dynamic power (from Wattch [27], CACTI [52]) and leakage power (from HotLeakage [155]) of each processing core (including the L1 caches), the shared multi-bank L2 cache, as well as the interconnection network (from Orion [49]).

To run parallel applications on top of the Sim-PowerCMP performance simulator, we have to follow a particular process that transforms a parallel application code into a runnable code for this simulator. It is shown in the block diagram

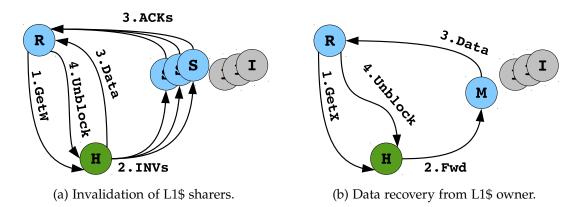

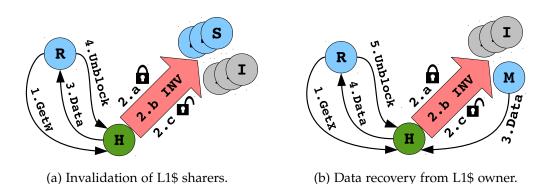

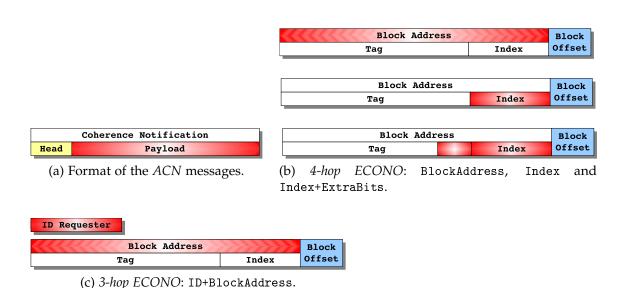

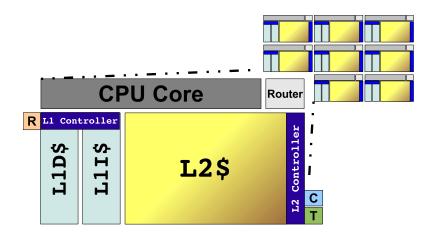

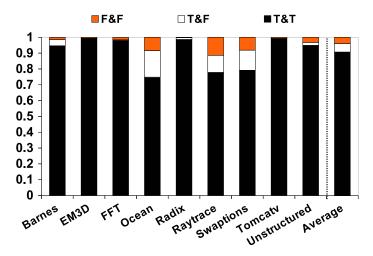

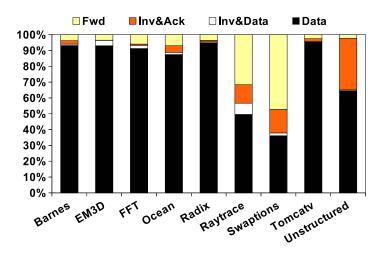

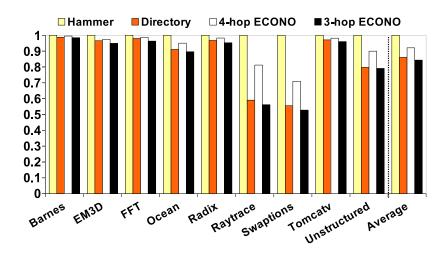

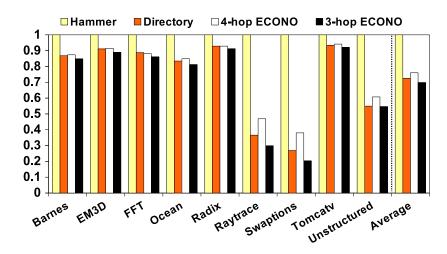

illustrated in Figure 2.2. As shown in the figure, the first step is to write the applications in C with annotations that add parallel shared memory semantics to C. In all cases, the programs use the annotations proposed by Boyle et al. [58] (usually known as PARMACS macros). In consequence, the *m*<sup>4</sup> preprocessor transforms the parallel programs into plain C sources substituting the parallel shared memory annotations into C statements or suitable library calls, using the set of PARMACS macros included in the RSIM distribution. We must consider that, like RSIM, Sim-PowerCMP simulates applications compiled and linked for SPARC V9/Solaris using ordinary SPARC compilers and linkers. In this way, the Sun SPARC C compiler for Solaris is used to generate the relocatable object files that the Sun linker links together (along with the RSIM library, C library and math library), to create an executable SPARC application. For faster processing and portability, the Sim-PowerCMP simulator actually interprets applications in an expanded, loosely encoded instruction set format. For that, a predecoder is finally used to convert the executable SPARC application into this internal format, which is then fed into the simulator.