# **TESI DOCTORAL**

Títol Contributions to Formal Communication Elimination for System Models with Explicit Parallelism

Realitzada per Francesc-Xavier Babot Pagès

en el Centre La Salle. Universitat Ramon Llull

i en el Departament d'Informàtica

Dirigida per Prof. Miquel Bertran Salvans

# RESUM

Els mètodes de *verificació formal* s'estan usant cada vegada més en la indústria per establir la correctessa i trobar els errors en *models de sistemes*; per exemple la descripció de hardware, protocols, programes distribuïts, etc. En particular, els verificadors de models ho fan automàticament per sistemes d'estats finits, però estan limitats degut al problema de l'explosió d'estats; i la *verificació formal interactiva*, l'àrea d'aquesta tesi, es necessita.

L'enfocament de la verificació automàtica treballa sobre el sistema de transicions del model, el qual defineix la seva semàntica. Aquest sistema de transicions té sovint molts estats, i sempre una mida gran comparada amb la mida del model del sistema, el qual és sempre infinit. Aquestes consideracions suggereixen un enfocament de *verificació estàtica* com els d'aquesta tesi, evitant els sistemes de transicions, treballant directament sobre el model del sistema, en principi, la complexitat computacional hauria de ser menor. L'enfocament estàtic d'aquest treball es fa sobre models de sistemes expressats en *notació imperativa* amb *paral·lelisme* explícit, sentències de *comunicacions síncrones* i *variables d'emmagatzematge* locals.

Els raonaments d'equivalència són molt empleats per números, matrius i altres camps. Tanmateix, per programes imperatius amb paral·lelisme, comunicacions i variables, encara que potencialment sigui un mètode de verificació molt intuïtiu, no han estat massa explorats. La seqüencialització formal via l'eliminació de comunicacions internes, l'àrea d'aquesta tesi, és una demostració basada en el raonament estàtic d'equivalències que, donat que disminueix la magnitud del vector d'estats, pot complementar altres mètodes de demostració. Es basa en l'aplicació d'un conjunt de lleis, apropiades per tal propòsit, com reduccions de reescriptura del model del sistema. Aquestes depenen de la noció d'equivalència i de les suposicions de justícia.

Aquesta tesi contribueix a la quasi inexplorada àrea de l'eliminació de comunicacions formal i seqüencialització de models de sistema. Les lleis estan definides sobre una equivalència feble: equivalència d'interfície. L'eliminació de comunicacions està limitada a models sense seleccions, per exemple models en els quals les comunicacions internes no estan dins de l'àmbit de sentències de selecció. Aplicacions interessants existeixen dins d'aquest marc. Les lleis són vàlides només per justícia feble o sense justícia. Aquesta ha estat desenvolupada seguint la semàntica proposada per Manna i Pnueli per a sistemes reactius [MP91, MP95]. S'han formulat les condicions d'aplicabilitat per les lleis de la pròpia eliminació de comunicacions. A més a més, es proposa un procediment de construcció de demostracions per l'eliminació de comunicacions, el qual intenta aplicar automàticament les lleis de la eliminació. També s'ha dissenyat un conjunt de procediments de transformació, els quals garanteixen que la transformació equivalent sempre correspon a l'aplicació d'una seqüència de lleis. Degut a que la construcció de les demostracions és impracticable, normalment impossible, sense l'ajuda d'una eina, s'ha desenvolupat un demostrador interactiu per la construcció semiautomàtica de la seqüencialització de models de sistemes i demostracions d'eliminació. Tant els procediments de transformació com els de l'eliminació de comunicacions estan integrats en l'eina. Amb l'ajuda del demostrador s'ha construït la demostració de seqüencialització d'un model, no trivial, de processador pipeline. Per aquest exemple s'ha assolit una reducció, respecte del model original, de la cota superior del nombre d'estats de  $2^{-672}$ .

Malgrat l'enorme quantitat d'esforç dedicat a l'àrea, abans i durant la tesi, encara queda molt treball per a que l'eliminació de comunicacions i la seqüencialització sigui realment un mètode pràctic. No obstant els resultats d'aquesta tesi han establert els fonaments i han donat l'estímul necessari per continuar l'esforç.

# RESUMEN

Los métodos de *verificación formal* se están usando cada vez más en la industria para establecer la corrección y encontrar los errores en *modelos de sistemas*; por ejemplo, la descripción de hardware, protocolos, programas distribuidos, etc. En particular, los verificadores de modelos lo hacen automáticamente para sistemas de estados finitos, pero están limitados debido al problema de la explosión de estados; y la *verificación formal interactiva*, el área de esta tesis, es necesaria.

El enfoque de la verificación automática trabaja sobre el sistema de transiciones del modelo, el cual define su semántica. Este sistema de transiciones tiene a menudo muchos estados, y siempre un tamaño grande comparado con el tamaño del modelo del sistema, el cual es siempre infinito. Estas consideraciones sugieren un enfoque de *verificación estática* como los de esta tesis, evitando los sistemas de transiciones, trabajando directamente sobre el modelo del sistema, en principio, la complejidad computacional tendría que ser menor. El enfoque estático de este trabajo se lleva a cabo sobre modelos de sistemas expresados en *notación imperativa* con *paralelismo* explícito, sentencias de *comunicaciones síncronas* y *variables de almacenamiento* locales.

Los razonamientos de equivalencia son muy empleados para números, matrices y otros campos. Sin embargo, para programas imperativos con paralelismo, comunicaciones y variables, aún teniendo la potencialidad de ser un método de verificación muy intuitivo, no han sido muy explorados. La secuencialización formal vía la eliminación de comunicaciones internas, el área de esta tesis, es una demostración basada en el razonamiento estático de equivalencias que, ya que disminuye la magnitud del vector de estados, puede complementar otros métodos de demostración. Se basa en la aplicación de un conjunto de leyes, apropiadas para tal propósito, como reducciones de reescritura del modelo del sistema. Éstas dependen de la noción de equivalencia y de las suposiciones de justicia.

Esta tesis contribuye a la casi inexplorada área de la eliminación de comunicaciones formal y secuencialización de modelos de sistema. Las leyes están definidas sobre una equivalencia débil: equivalencia de interfaz. La eliminación de comunicaciones está limitada a modelos sin selecciones, por ejemplo modelos en los cuales las comunicaciones internas no están dentro del ámbito de sentencias de selección. Aplicaciones interesantes existen dentro de este marco. Las leves son válidas sólo para justicia débil o sin justicia. Esta ha sido desarrollada siguiendo la semántica propuesta por Manna y Pnueli para sistemas reactivos [MP91, MP95]. Se han formulado las condiciones de aplicabilidad para las leyes de la propia eliminación de comunicaciones. Además, se propone un procedimiento de construcción de demostraciones para la eliminación de comunicaciones, el cual intenta aplicar automáticamente las leves de la eliminación. También se ha diseñado un conjunto de procedimientos de transformación, los cuales garantizan que la transformación equivalente siempre corresponde a la aplicación de una secuencia de leyes. Debido a que la construcción de las demostraciones es impracticable, normalmente imposible, sin la ayuda de una herramienta, se ha desarrollado un demostrador interactivo para la construcción semiautomática de la secuencialización de modelos de sistemas y demostraciones de eliminación. Tanto los procedimientos de transformación como los de la eliminación de comunicaciones están integrados en la herramienta. Con la avuda del demostrador se ha construido la demostración de secuencialización de un modelo, no trivial, de procesador pipeline. Para este ejemplo se ha logrado una reducción, respecto del modelo original, de la cota superior del número de estados de  $2^{-672}$ .

A pesar de la enorme cantidad de esfuerzo dedicado al área, antes y durante esta tesis, todavía queda mucho trabajo para que la eliminación de comunicaciones y la secuencialización sea realmente un método práctico. Sin embargo los resultados de esta tesis han establecido los cimientos y han dado el estímulo necesario para continuar el esfuerzo.

# ABSTRACT

Formal verification methods are increasingly being used in industry to establish the correctness of, and to find the flaws in, system models; for instance, descriptions of hardware, protocols, distributed programs, etc. In particular, model checking does that automatically for finite-state systems, but it is limited in scope due to the state explosion problem; and interactive formal verification, the broad area of this thesis, is needed.

Automatic verification approaches work on the transition system of the model, which defines its semantics. This transition system has often infinitely many states, and always a large size compared to the size of the system model, which is always finite. These considerations suggest that *static verification* approaches such as those of this thesis, avoiding the transition system, working directly on the system model would have less computational complexity, in principle. The static approach of this work is carried out on system models expressed in *imperative notations* with explicit *parallelism* and *synchronous communication* statements, and with local *storage variables*.

Equivalence reasoning is heavily used for numbers, matrices, and other fields. However, for imperative programs with parallelism, communications, and variables, although having the potentiality of being a very intuitive verification method, it has not been much explored. Formal sequentialization via internal communication elimination, the area of this thesis, is a static equivalence reasoning proof that, since it decreases the size of the state vector, could complement other proof methods. It is based on the application of a set of laws, suitable for that purpose, as rewriting reductions to a system model. These proofs need both proper communication elimination laws and auxiliary basic laws. These depend on the notion of equivalence and on the fairness assumptions.

This thesis contributes to the almost unexplored area of formal communication elimination and system model sequentialization. The laws are defined over a weak equivalence: interface equivalence. Communication elimination is confined to selection-free models, i.e. models none of whose inner communications are within the scope of selection statements. Interesting applications already exist within this framework. The laws are valid only with weak fairness or no fairness. It has been developed following the same semantics as Manna and Pnueli for reactive systems [MP91, MP95]. Applicability conditions for the proper communication elimination laws are derived. In addition, a communication elimination proof construction procedure, which attempts to apply the elimination laws automatically is proposed. A set of transformation procedures, guaranteeing that the equivalence transformation always corresponds to the application of a sequence of laws have been designed as well. Since the construction of elimination proofs is impractical, even impossible, without a tool, an *interactive prover* for semi-automatic construction of system model sequentialization and elimination proofs has been developed. Both transformation and communication elimination procedures are integrated within the tool. As a non-trivial example, a sequentialization proof of a *pipelined processor* model, has been constructed with the help of the prover. A reduction, with respect to the original model, of  $2^{-672}$  on the upper bound on the number of states has been achieved in this example.

In spite of the huge amount of effort already devoted to the area, before and during this thesis, much work still needs to be done until communication elimination and sequentialization become a practical method. Nevertheless the results of this thesis have established its foundations and given the necessary encouragement for continuing the effort.

# ACKNOWLEDGEMENTS

First and foremost, I would like to express my deep gratitude to my advisor, Prof. Miquel Bertran, for his enthusiasm, constant support and invaluable encouragement throughout all the thesis. I am indebted to him for the opportunity of working in an original and interesting research area.

I would also like to express my sincere gratitude to former director of *La Salle*, *Universitat Ramon Llull*, Prof. Daniel Cabedo, who passed away on June 2006, and to Prof. Josep Martí, then chief of studies, for their acceptance, patience, and economical support during the first half of my Ph.D. work.

I also thank the people of the grup de recerca en sistemes distribuits, together with its head August Climent for the support of the work; also the departament d'informàtica of La Salle, Universitat Ramon Llull in general. Specially I am very grateful to Anna Villoslada and Gabriel Salvà for helping me in different aspects during this work.

I would like to extend the acknowledgment to the group of *General Systems Development* company: Albert Duran, Miquel Porta, Joan-Andreu Margalef and Román Duch. They always supported and helped me in the usage and maintenance of PADD/RALE, the distributed program development environment used in my thesis; and in many other ways during this research work.

I am really glad that Prof. Zohar Manna accepted my visit to his group at *Stanford University*, and for his invaluable comments along the thesis. Also many thanks to Tomás Uribe, Nikolaj Bjørner, Bernd Finkbeiner, and Henny Sipma, for introducing me to the temporal verification methodologies. Special thanks to Bernd Finkbeiner who followed and encouraged this work from its beginning. Also the criticism of Prof. Ricardo Peña at a certain stage of the work is appreciated.

The initial inspiration of the research leading into this thesis, occurred during the sabbatical stay of my thesis advisor at the Rutherford Appleton Laboratory, British Science and Engineering Research Council, invited by Dr. Robert Witty, also inventor of Dimensional Flowcharting, the tree-like notation from which PADD was born. Together with my advisor, I would like to acknowledge this and express my gratitude to Dr. Robert Witty.

I am also grateful to the coauthors of my communications and articles: Miquel Bertran, August Climent, Jordi Riera, and Miquel Nicolau, for their help while writing the papers, and to all the anonymous referees.

This research work would have not been possible without funding. In this regard, I would like to thank *General Systems Development* company, *La Salle*, and the partial support from the spanish *Ministerio de Educación y Ciencia* under the CICYT project TIN2006-14738-C02-02.

Last but not least, the final acknowledgement is addressed to my family. I would like to thank my parents Joan and Maria Dolors, and my brother Jordi for their unconditional support and patience. To them and to my friends I dedicate this thesis.

# CONTENTS

|                                                                       |                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| List of                                                               | Figure                                                                                                      | S                                                                                                                                                                                                                                                                                                                                                                                                      | xvii                                                  |

| List of                                                               | Tables                                                                                                      | ;                                                                                                                                                                                                                                                                                                                                                                                                      | xix                                                   |

| List of                                                               | Proce                                                                                                       | dures                                                                                                                                                                                                                                                                                                                                                                                                  | xxi                                                   |

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5 \\ 1.6 \\ 1.7 \\ 1.8 \\ 1.9 \\ 1.10$ | Motiva<br>Impera<br>Forma<br>Static<br>Comm<br>Limita<br>The N<br>Interfa<br>Elimin<br>Forma                | <b>on</b>                                                                                                                                                                                                                                                                                                                                                                                              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <ol> <li>2.1</li> <li>2.1</li> <li>2.2</li> </ol>                     | A Tree<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>2.1.7<br>2.1.8<br>2.1.9<br>2.1.10<br>2.1.11 | Notations and Grounding Notions         -like Notation         Introduction         Basic Statements         Sequence         Scoped Descriptions         Sequential Iteration         Parallelism         Connections         Internal and External Connections         Selection         Abstract Communication Pairs         Communications Selection         Introduction         Basic Statements | $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |

|    |      | 2.2.3 Compound Statements                                                                      | 20         |

|----|------|------------------------------------------------------------------------------------------------|------------|

|    |      | 2.2.4 Related Notions                                                                          | 21         |

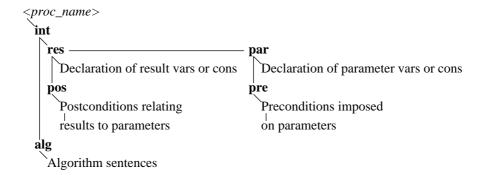

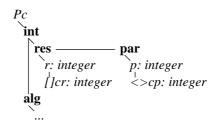

|    | 2.3  | Modular Procedures in PADD                                                                     | 21         |

|    |      | 2.3.1 Procedure Interface                                                                      | 22         |

|    |      | 2.3.2 Procedure Reference                                                                      | 24         |

|    | 2.4  | Modular Procedures in the Textual Notation                                                     | 24         |

|    |      |                                                                                                | 24         |

|    |      |                                                                                                | 25         |

|    | 2.5  | Basic Notions for the Formal Semantics                                                         | 26         |

|    | 2.6  | Semantics of the Notation                                                                      | 28         |

|    |      | 2.6.1 Introduction                                                                             | 28         |

|    |      | 2.6.2 Auxiliary Notions                                                                        | 28         |

|    |      | 2.6.3 Formal Semantics                                                                         | 29         |

|    | 2.7  | Interface Behaviors                                                                            | 81         |

|    | 2.8  | Interface Equivalence                                                                          | <b>8</b> 4 |

|    |      | 2.8.1 The Notion                                                                               | <b>8</b> 4 |

|    |      | 2.8.2 Deadlock Introduction                                                                    | 6          |

|    |      | 2.8.3 Substitution Rules                                                                       | 6          |

|    | 2.9  | Laws for Interface Equivalence                                                                 | 87         |

|    |      | 2.9.1 Introduction                                                                             | 87         |

|    |      | 2.9.2 Repository of Laws                                                                       | 88         |

|    |      | $2.9.2.1  \text{Concatenation}  \dots  \dots  \dots  \dots  \dots  \dots  3$                   | 88         |

|    |      | $2.9.2.2  \text{Cooperation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | <b>3</b> 9 |

|    |      | 2.9.2.3 Cooperation and Concatenation                                                          | <b>3</b> 9 |

|    |      | 2.9.2.4 Elimination of Redundant Variables and Statements 4                                    | 0          |

|    | 2.10 | Conclusion                                                                                     | 1          |

| _  |      |                                                                                                |            |

| 3. |      |                                                                                                | 3          |

|    | 3.1  |                                                                                                | 3          |

|    | 3.2  | 0                                                                                              | 4          |

|    |      |                                                                                                | 4          |

|    |      |                                                                                                | 7          |

|    |      | 3                                                                                              | 64         |

|    | 3.3  |                                                                                                | 66         |

|    |      |                                                                                                | 66         |

|    |      | 0                                                                                              | 57         |

|    |      |                                                                                                | 57         |

|    | 0.4  | 0                                                                                              | 68<br>80   |

|    | 3.4  | Conclusion                                                                                     | 60         |

| 4  | Δ    | Communication Elimination Reduction Procedure                                                  | 53         |

| •• |      |                                                                                                | ;3         |

|    | 4.2  | Binary  | y Commu     | nication Elimination                                                                   | 65  |

|----|------|---------|-------------|----------------------------------------------------------------------------------------|-----|

|    |      | 4.2.1   | Determin    | ne the Orders                                                                          | 66  |

|    |      | 4.2.2   | Construe    | ct Top Level Statements                                                                | 72  |

|    |      | 4.2.3   | Applicat    | ion of Elimination from a Binary Cooperation                                           | 75  |

|    |      | 4.2.4   | Remove      | Nil Statements                                                                         | 83  |

|    |      | 4.2.5   | Remove      | Sequence and Parallelism Associations                                                  | 85  |

|    |      | 4.2.6   | Overall     | Computational Complexity                                                               | 86  |

|    | 4.3  | A Cor   | nmunicati   | on Elimination Example                                                                 | 87  |

|    | 4.4  | Elimir  | nation from | m a k-ary Cooperation                                                                  | 102 |

|    | 4.5  | Gener   | al Commu    | inication Elimination                                                                  | 103 |

|    | 4.6  | Concl   | usions      |                                                                                        | 105 |

| 5. | The  | Intera  | active Pr   | over Tool                                                                              | 107 |

|    | 5.1  | Interfa | ace Comp    | onents and Overview                                                                    | 107 |

|    | 5.2  | The In  | nput State  | ement and its Preprocessing                                                            | 108 |

|    | 5.3  | The B   | asic Laws   | : Representation and Application                                                       | 112 |

|    |      | 5.3.1   | Notation    | al Conventions                                                                         | 112 |

|    |      | 5.3.2   | Notation    | for the Laws                                                                           | 112 |

|    |      | 5.3.3   | Procedu     | re Apply                                                                               | 114 |

|    |      |         | 5.3.3.1     | Structure Matching                                                                     | 115 |

|    |      |         | 5.3.3.2     | Verification of Conditions                                                             | 117 |

|    |      |         | 5.3.3.3     | Example                                                                                | 119 |

|    |      |         | 5.3.3.4     | $Transformation \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 120 |

|    | 5.4  | The T   | ransforma   | tion Procedures                                                                        | 122 |

|    |      | 5.4.1   | Introduc    | tion                                                                                   | 122 |

|    |      | 5.4.2   | Reposito    | ry of Transformation Procedures                                                        | 123 |

|    |      |         | 5.4.2.1     | Communication Elimination                                                              | 123 |

|    |      |         | 5.4.2.2     | Cooperation Permutation                                                                | 123 |

|    |      |         | 5.4.2.3     | Cooperation Associativity                                                              | 125 |

|    |      |         | 5.4.2.4     | Binary Cooperation Associativity                                                       | 127 |

|    |      |         | 5.4.2.5     | Cooperation Flattening                                                                 | 128 |

|    |      |         | 5.4.2.6     | Concatenation Permutation                                                              | 130 |

|    |      |         | 5.4.2.7     | Concatenation Association                                                              | 132 |

|    |      |         | 5.4.2.8     | Concatenation Flattening                                                               | 134 |

|    |      |         | 5.4.2.9     | Cooperation and Concatenation                                                          | 136 |

|    |      |         | 5.4.2.10    | Elimination of Redundant Variables                                                     | 138 |

|    | 5.5  | Concl   | usion       |                                                                                        | 138 |

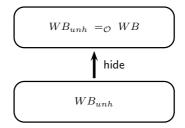

| 6. | Cori | rectne  | ss Proof    | of a Pipelined Processor Architecture                                                  | 141 |

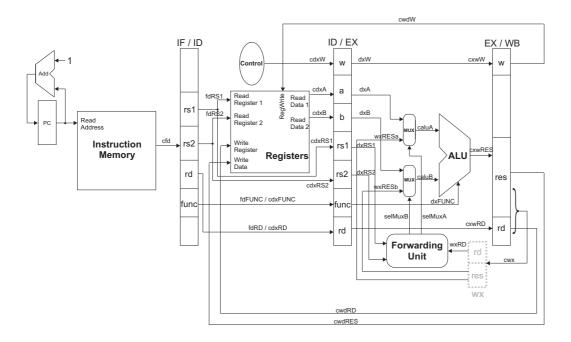

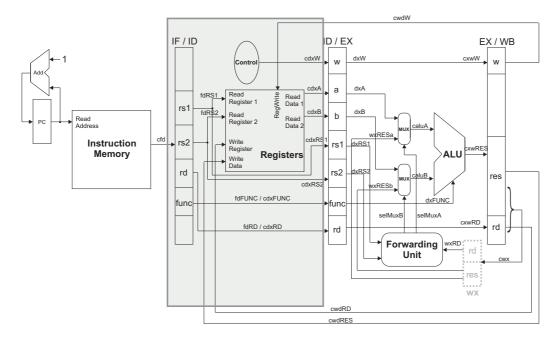

|    | 6.1  | Introd  | luction to  | the DLX Processor                                                                      | 141 |

|    | 6.2  | Simpl   | ified DLX   | -like Model                                                                            | 143 |

|    |      | 6.2.1   | Global V    | <sup>7</sup> iew                                                                       | 143 |

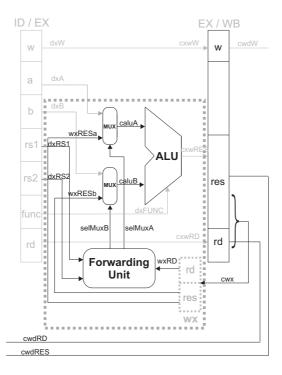

|    |       | 6.2.2                   | Forwarding Unit                                                                                                                              | 145 |

|----|-------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

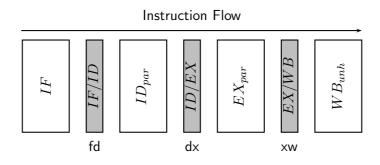

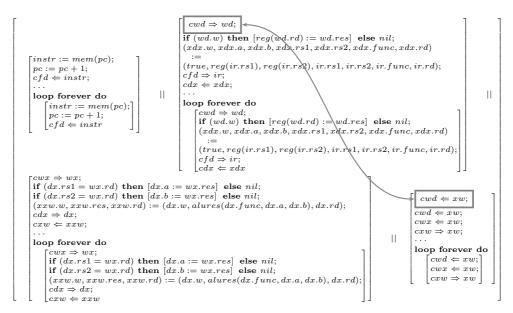

|    |       | 6.2.3                   | The $Pipeline_2$ Model                                                                                                                       | 146 |

|    |       |                         | 6.2.3.1 Data Types                                                                                                                           | 147 |

|    |       |                         | $6.2.3.2  \text{Procedure } IF  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                             | 147 |

|    |       |                         | 6.2.3.3 Procedure $ID_{par}$                                                                                                                 | 148 |

|    |       |                         | 6.2.3.4 Procedure $EX_{par}$                                                                                                                 | 150 |

|    |       |                         | 6.2.3.5 Procedure $WB_{unh}$                                                                                                                 | 152 |

|    |       | 6.2.4                   | The $Pipeline_1$ Model $\ldots \ldots \ldots$                                 | 153 |

|    |       |                         | $6.2.4.1  \text{Procedure } IF  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                             | 153 |

|    |       |                         | 6.2.4.2 Procedure $ID_{seq}$                                                                                                                 | 154 |

|    |       |                         | 6.2.4.3 Procedure $EX_{seq}$                                                                                                                 | 154 |

|    |       |                         | $6.2.4.4  \text{Procedure } WB \dots $ | 155 |

|    |       |                         | 6.2.4.5 Procedure $Pipeline_1 \ldots \ldots \ldots \ldots \ldots \ldots$                                                                     | 155 |

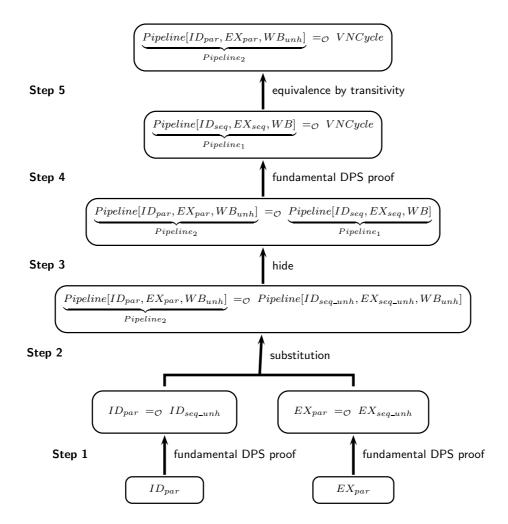

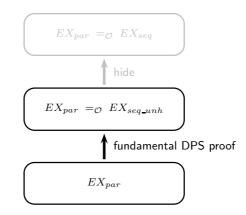

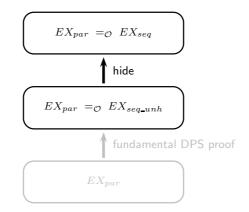

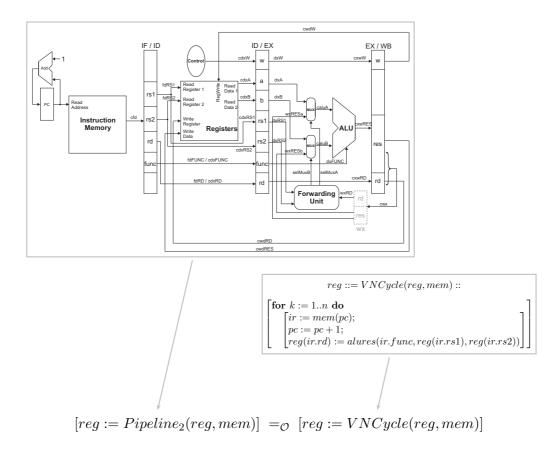

|    | 6.3   | Proof                   | Schema                                                                                                                                       | 157 |

|    |       | 6.3.1                   | Overview                                                                                                                                     | 157 |

|    |       | 6.3.2                   | State Vector Reduction                                                                                                                       | 161 |

|    |       | 6.3.3                   | Proof of $Pipeline_1$                                                                                                                        | 162 |

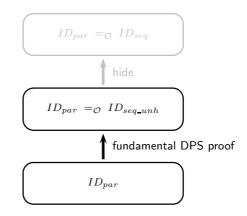

|    |       | 6.3.4                   | Proof of $ID_{par}$                                                                                                                          | 180 |

|    |       | 6.3.5                   | Proof of $ID_{seq\_unh}$                                                                                                                     | 185 |

|    |       | 6.3.6                   | Proof of $EX_{par}$                                                                                                                          | 186 |

|    |       | 6.3.7                   | Proof of $EX_{seq\_unh}$                                                                                                                     | 192 |

|    |       | 6.3.8                   | Proof of $WB_{unh}$                                                                                                                          | 193 |

|    |       | 6.3.9                   | Final Step. Application of the Substitution Rule                                                                                             | 194 |

|    | 6.4   | Conclu                  | usion                                                                                                                                        | 195 |

| 7. | Con   | clusio                  | ns and Future Work                                                                                                                           | 197 |

|    | 7.1   | Summary and Conclusions |                                                                                                                                              |     |

|    | • • = | 7.1.1                   | Ground Notions                                                                                                                               | 197 |

|    |       | 7.1.2                   | Applicability Conditions for the Laws                                                                                                        | 198 |

|    |       | 7.1.3                   | Communication Elimination Procedures                                                                                                         | 198 |

|    |       | 7.1.4                   | An Interactive Prover                                                                                                                        | 199 |

|    |       | 7.1.5                   | An Example of Sequentialization Proof                                                                                                        | 199 |

|    |       | 7.1.6                   | Difficulty of Sequentialization                                                                                                              | 199 |

|    |       | 7.1.7                   | A Final Concluding Word                                                                                                                      | 200 |

|    | 7.2   | Future                  | e Work                                                                                                                                       | 200 |

|    |       | 7.2.1                   | Further Automation of DPS Proofs                                                                                                             | 200 |

|    |       |                         | 7.2.1.1 Cooperation Substatement Closening                                                                                                   | 200 |

|    |       |                         | 7.2.1.2 Concatenation Substatement Closening                                                                                                 | 202 |

|    |       |                         | 7.2.1.3 Iterative Redundant Variable Elimination                                                                                             | 203 |

|    |       |                         | 7.2.1.4 General Substatement Closening                                                                                                       | 203 |

|    |       | 7.2.2                   | Further Generalization of Communication Elimination Laws .                                                                                   | 204 |

|    |       |                         | 7.2.2.1 Introduction                                                                                                                         | 204 |

|        |         | 7.2.2.2       | Top Statements with $P$ Partition                                                                        | 204 |

|--------|---------|---------------|----------------------------------------------------------------------------------------------------------|-----|

|        |         | 7.2.2.3       | Alternative Construction of Top Statements                                                               | 206 |

|        | 7.2.3   | Deadloc       | k Situations                                                                                             | 208 |

|        | 7.2.4   | Eliminat      | tion of Communications within Selection Scopes and                                                       |     |

|        |         | Non-disj      | joint Pairs                                                                                              | 210 |

|        |         | 7.2.4.1       | Example                                                                                                  | 211 |

|        |         | 7.2.4.2       | Difficulties of general elimination                                                                      | 212 |

|        | 7.2.5   | Complet       | teness                                                                                                   | 214 |

| A. Sou | ndness  | s of the      | Laws                                                                                                     | 217 |

| A.1    |         |               |                                                                                                          |     |

|        | A.1.1   |               | tion of the auxiliary laws                                                                               |     |

|        | A.1.2   |               | nication Elimination Laws                                                                                |     |

| A.2    |         |               | $em 6 \ldots \ldots$ |     |

| B. Pro | of of I | $Pipeline_1$  |                                                                                                          | 233 |

| B.1    |         | -             | Concatenation Transformation                                                                             |     |

| B.2    | Conca   | tenation (    | Commutativity                                                                                            | 239 |

| B.3    | Redun   | idant Vari    | iable Elimination                                                                                        | 243 |

| B.4    |         |               | Von Neumann Body                                                                                         |     |

| B.5    | Tail S  | tatements     | 3                                                                                                        | 269 |

| C. Pro | of of I | $D_{par}$ and | d $EX_{par}$                                                                                             | 277 |

|        |         | -             |                                                                                                          |     |

|        |         | -             |                                                                                                          |     |

# LIST OF FIGURES

#### Figure

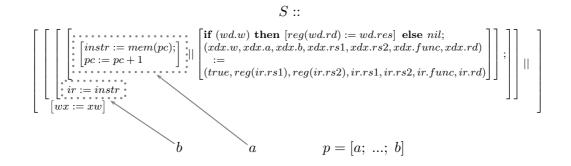

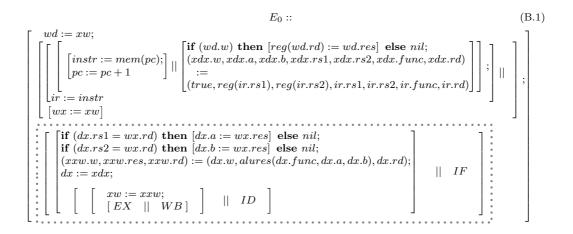

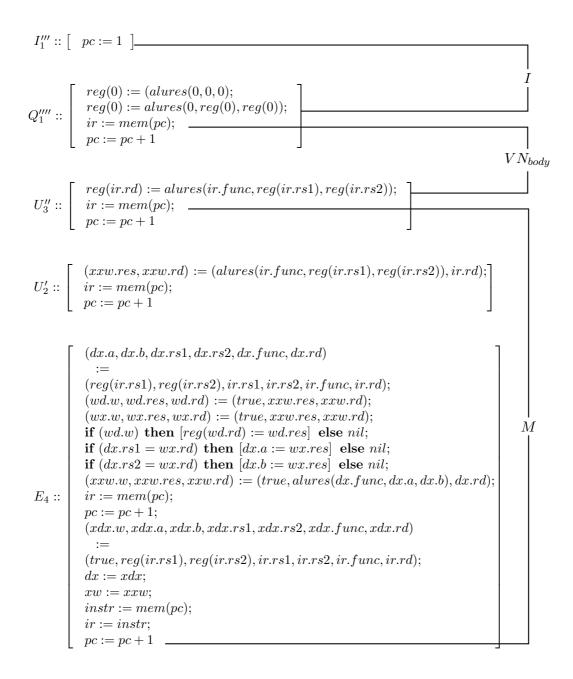

#### 6.16.21446.31466.46.56.6EX stage block diagram 1506.76.8 Hierarchical proof schema ..... 158

Page

# LIST OF TABLES

| Table        | Pag                                                                                                                                                           | e |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $2.1 \\ 2.2$ | An interface computation schema of the $Pc$ procedure $\ldots \ldots \ldots 33$<br>Interface behaviour schema of the $Pc$ procedure $\ldots \ldots \ldots 33$ | _ |

| 4.1          | Computation complexity of BIN-COMELI                                                                                                                          | 7 |

| 6.1          | $Pipeline_2$ R-Type instructions. Arithmetical operations 14                                                                                                  | 3 |

| 6.2          | Pipeline <sub>2</sub> R-Type instructions. Logical operations                                                                                                 | 4 |

| 6.3          | Local variables of procedure $IF$                                                                                                                             | 7 |

| 6.4          | Local variables of procedure $ID_{par}$                                                                                                                       | 0 |

| 6.5          | Local variables of procedure $EX_{par}$                                                                                                                       | 2 |

| 6.6          | Local variable of procedure $WB_{unh}$                                                                                                                        | 3 |

| 6.7          | Local variables of $VNCycle$                                                                                                                                  | 2 |

| 6.8          | Variables of $Pipeline_2$                                                                                                                                     | 3 |

# LIST OF PROCEDURES

| Proced | ure                                                                                                      | Page |

|--------|----------------------------------------------------------------------------------------------------------|------|

| 1      | BIN-COMELI – binary communication elimination                                                            | 66   |

| 2      | STEP1 – determine the orders of $S^{l}(\ell)$ and $S^{r}(m)$                                             | 66   |

| 3      | STRUCTORDER – determine the structural order                                                             | 70   |

| 4      | STEP2 – put top level statements in the standard form                                                    | 73   |

| 5      | COMMSTAT – communicating statements                                                                      | 76   |

| 6      | $\label{eq:communication} \text{COMMPRECEDE} - \text{communication order precedence restriction}  . \ .$ | 76   |

| 7      | STEP3 – proper communication elimination                                                                 | 77   |

| 8      | STEP4 – elimination of redundant $nil$ statements                                                        | 84   |

| 9      | STEP5 – elimination of redundant statement associations                                                  | 86   |

| 10     | COMELI – elimination form a selection-free BCS                                                           | 102  |

| 11     | GEN-COMELI – general elimination form a selection-free BCS                                               | 104  |

| 12     | APPLY – apply a law                                                                                      | 115  |

| 13     | COOPPERMUT – cooperation permutation                                                                     | 124  |

| 14     | COOPASSO – cooperation association                                                                       | 125  |

| 15     | BINCOOPASSO – binary cooperation association                                                             | 127  |

| 16     | COOPFLAT – cooperation flattening                                                                        | 130  |

| 17     | CONCATPERMUT – concatenation permutation                                                                 | 131  |

| 18     | CONCATASSO – concatenation association                                                                   | 133  |

| 19     | CONCATFLAT – iterative concatenation flattening                                                          | 135  |

| 20     | COOPCONCAT – cooperation and concatenation                                                               | 136  |

| 21     | ITEVARELIM – iterative redundant variable elimination                                                    | 203  |

# Chapter 1 INTRODUCTION

The work reported in this thesis is about formal static communication elimination from imperative programs and parallel program sequentialization, all via equivalence reasoning. These are relatively unexplored topics. Thus, this chapter defines and delimits the corresponding areas, and provides some motivation. It also introduces the broad fields to which these topics pertain. The base theory which is needed for the development of the proper thesis work is identified as well, but its review is left for the second and third chapters.

# 1.1 Motivation

Equivalence reasoning is extensively used for numbers and matrices. Research on equivalence reasoning in the area of concurrency and distribution has been carried out in the very specific field of process algebras and action systems, such as CCS [Mil80, Mil89], CSP [Hoa85] and ACP [BK84, BK85], where the equivalence is defined on state transition systems and computation trees. These models are very abstract, they are far from the intuitiveness of an imperative programming notation with variables and boolean conditions. Effort on equivalence reasoning at the more intuitive level of imperative program text is still needed for distributed, concurrent and reactive system models.

Imperative concurrent, reactive and distributed programs, with explicit parallelism and synchronous, handshaking, communications, are the framework of this thesis. With them both software and hardware system models can be constructed. This work contributes to the study of equivalence reasoning for these programs via communication elimination and sequentialization. Equivalence reasoning for imperative concurrent and distributed programs, although having the potentiality of being a very intuitive verification activity, remains substantially unexplored within the broad field of interactive verification. Therefore, conceptually, it deserves further attention.

An impediment for the widespread use of verification in engineering is the needed expertise of the engineer in mathematical logic. Equivalence proofs remain at the imperative notation level and its transformation laws; thus removing obstacles for engineers. There is no need to go into invariants and predicate calculus. Mathematical reasoning is only needed to justify soundness of the laws and the equivalences. This has to be done only once, but not by the verifying engineer. In spite of not being a general verification approach, this intuitiveness and simplicity gives and additional motivation for studying the method and its application scope.

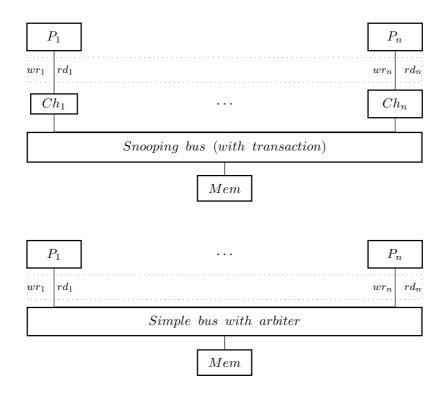

The widely researched area of *model checking* is affected by the state explosion problem, since the checkers operate on the semantic model: the finite transition system of the model program. Model checking algorithms have exponential complexity in the size of the program. The algorithms studied in this thesis for the automation of communication elimination and sequentialization proofs have polynomial complexity in the size of the program, as will be apparent. Although these proofs are not a general verification method, their complexity reduction makes their study appealing.

# **1.2 Imperative Notations with Synchronous Communications**

Verification at the level of the source program is addressed in this work. Notation has been recognised as a very important element in general, and for verification in particular. Some of the pioneers of verification designed structured imperative notations like Pascal so that verification was more natural, or even possible. As a side comment, think about developing arithmetic in roman numerals. The notations used in this work are imperative with parallelism and synchronous communications and fall under the influence of Pascal.

Imperative notations with explicit parallelism and communication statements provide an intuitive, explicit, and complete framework to express distributed programs and system models with perspective and clarity. OCCAM [IL85, IL88, Jon87], ADA [Dep83, TDB<sup>+</sup>06], the *simple programming language* SPL of Manna and Pnueli [MP91, MP95], PROMELA of the SPIN model checker [Hol91], and the *sharedvariable language*<sup>++</sup>, SVL<sup>++</sup>, in [dRdBH<sup>+</sup>01] are representatives of them.

To add motivation to study verification methods for imperative notations with parallel processes and synchronous communications, as this work does, it is interesting to realize that recent approaches to improve operating systems and general concurrent program correctness and dependability, advocate for the use of concurrency in the form of parallel processes with local storage, communicating via rendez-vous; the notational framework of this work. [Lee06] is an example, proposing *coordination languages* for expressing this type of communication among sequential processes composed in parallel, as a way to avoid the more problematic shared storage concurrency. Also, in order to attain the above aims, new operating systems designed as microkernels, with operating system processes around them have been proposed in [THB06]. In an example of this approach, Minix3 [HBG<sup>+</sup>06], the microkernel offers rendez-vous as the only means of interprocess communication.

An unavoidable problem in system development is mapping: the transformation of the verified model into distributed software, or hardware, pertaining to the real world. Mapping, into distributed software systems, of imperative programs with parallelism and simple rendez-vous has been extensively treated in the literature for an even more general notation: multiparty interaction, the notation IP (*Interactive Processes*). The references [FF96, CRTC99, PCT04] are quite illustrative.

# **1.3 Formal Verification Methods**

Formal methods are increasingly being used in industry to establish the correctness of system models and to find the flaws in them; for instance, descriptions of hardware and protocols. In particular, model checking [CE81, QS82, Hol91, MD93, CGP99, MOSS99, Mer01, BK08] does that automatically for finite-state systems. However, model checking is limited in scope due to the state explosion problem. Most practical system descriptions, notably those of software, are therefore not directly amenable to finite-state verification methods since they have very large or infinite state spaces. For such systems, interactive theorem proving, for instance with the PVS prover [OSRSC01a, SORSC01, OSRSC01b], or with STeP [BBC+95, BBMC+00], or with ACL2 [KM09], has so far been the only viable alternative; in spite of its use requiring manual effort and mathematical sophistication. Model checking often requires much interaction in practice, for example for arriving at an initial model suitable for checking. However, research on model checking for models with dynamic data structures is underway [dMGMJS07, dMGMS08]. New paradigms and methods that combine the ease of use of model checking with the power and flexibility of theorem proving are needed. Such hybrid techniques started to emerge [MBSU98, SUM99]. Anyway, interactive verification is unavoidable and needs further research; the effort reported in this dissertation contributes to it.

The formal methodology presented in this work is another interactive verification approach, named *Distributed Program Sequentialization* (DPS). The goal is to obtain a simpler model equivalent in some sense to the original distributed system. It is based on equivalence proofs using a suitable set of laws applied as reductions to a program. An interactive prover tool is mandatory to carry out and store these proofs.

#### **1.4 Static Verification versus State Explosion**

Though there are many different approaches to automatic verification of programs, they are all limited by the space which is available on a given machine. Even small programs may have a significantly large state-space, so that verifying programs which implement solutions to realistic problems is difficult.

Automatic verification approaches work on the transition system of the program, defining the semantics of the distributed system. This transition system has often infinitely many states, and always a large size compared to the size of the program modeling the distributed system, which is always finite. The situation in which small programs correspond to exponentially large models is known as the state-explosion problems. In order to grasp the magnitude of this problem, suppose, for instance, that the number of variables of a program is n, each holding an integer of m bits. The number of states may then be of the order of  $2^{n \times m}$ , whereas the size of the program remains of an order close to n. The size of the control-flow graph is proportional to the number of statements in the program. The size of the transition system is much larger since it is also proportional to the sizes of the variable domains. It is the size of the transition systems which creates the difficulty in automatic verification.

Static analysis is the process of examining the control-flow graph of the program (the system) to extract information on its semantics, without creating the semantic model. The syntactic model is significantly smaller than the transition system since it expands only the program counter and not the program variables, which are the source for the enormous size of the semantic model. These considerations suggest that static automatic verification approaches, avoiding the transition system, working directly on the program would have less computational complexity, in principle. Following this line of work, static analysis methods for state reduction [CGL94, KLM<sup>+</sup>98, YG04] have been proposed as a step prior to model checking. They reduce the size of the transition system and hence the complexity of model checking. The verification, thus benefiting from its computational complexity advantages. The size of the transition system would be reduced, indirectly, by working on the source program, as the work of this thesis does.

# 1.5 Communication Elimination and Equivalence Reasoning

Sequentialization via internal communication elimination [BBCN01] is a static equivalence reasoning proof. It is based on the application of a set of laws, suitable for that purpose, as reductions to a program. There are *proper* communication elimination laws, whose application removes communication statements, and auxiliary, or basic, laws. After communications have been removed, parallel processes are disjoint and can be reorganized with other laws, and redundant variables can also be eliminated. When all this has been possible, a sequential program is obtained.

```

\begin{bmatrix} \mathbf{local} & a, b, x, y, z & : \mathbf{integer} \\ \mathbf{local} & \alpha, \beta & : \mathbf{channel of integer} \\ P_a :: [\mathbf{produce} \ a; \ \alpha \leftarrow a;] \\ || \\ P :: \begin{bmatrix} \alpha \Rightarrow x \ ||\beta \Rightarrow y]; \\ || \\ P_b :: [\mathbf{produce} \ b; \ \beta \leftarrow b;] \end{bmatrix}

```

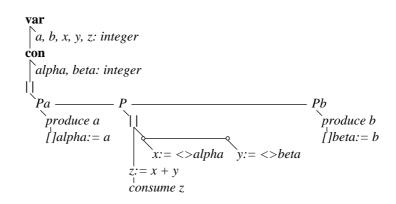

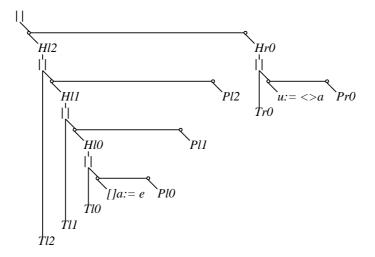

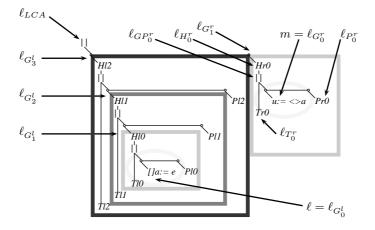

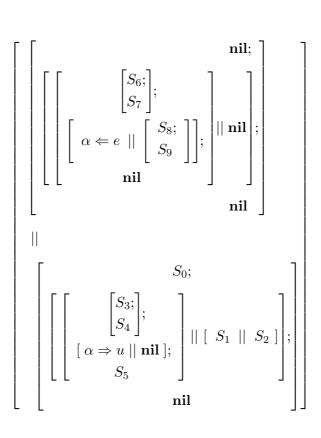

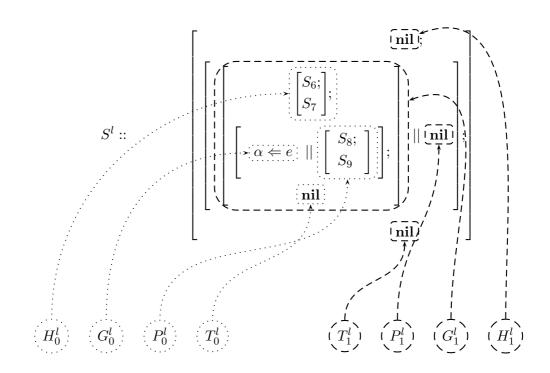

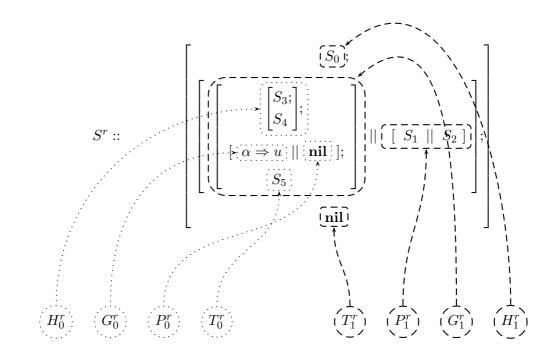

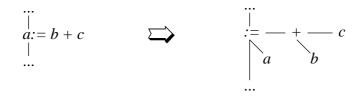

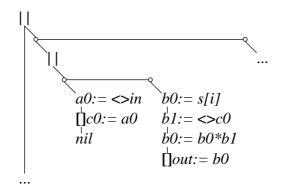

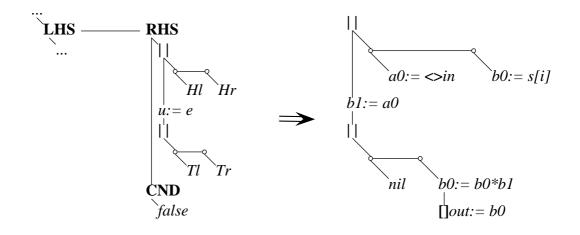

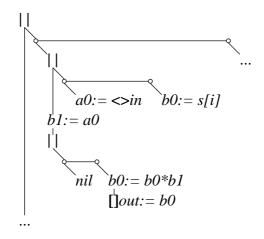

As an illustration of communication elimination and sequentialization, consider the above SPL program, having top-level parallel or cooperating disjoint processes  $P_a$ , P and  $P_b$ . The inner process P is a concatenation whose first substatement is a parallel composition of two synchronous communication, receive, substatements over channels  $\alpha$  and  $\beta$ . They match with synchronous communication, send, substatements, over the same respective channels, in processes  $P_a$  and  $P_b$  respectively. The same program expressed in PADD, another notation used in this work [BDP+09], would be:

The elimination of synchronous communications, via  $\alpha$  and  $\beta$ , followed by sequentialization, would give the equivalent program:

$\begin{bmatrix} \mathbf{local} & a, b, z & : \mathbf{integer} \\ \mathbf{produce} & a; \mathbf{produce} & b; \\ z := a + b; \\ \mathbf{consume} & z \end{bmatrix}$

This form reflects the essential function of the original program, and can be verified, much more easily, with sequential program verification methods. The work of this dissertation concentrates on the unexplored area of communication elimination and equivalence reasoning as illustrated by the above example. Other static transformation systems were proposed in [dFS98, SO99, Sch99], exploring communication elimination in frameworks different from imperative distributed programs with parallelism and synchronous rendez-vous communication.

Equivalence reasoning with communication elimination has applications in formal design. Actually, using it in the opposite direction, as communication introduction. This is commented in subsection 1.10.

# **1.6** Limitations of this Work

This work applies to a certain class of models only. But, in addition, the assumptions on the underlying scheduler are restricted to weak fairness or no fairness at all. Strong fairness is prohibited, since some of the laws are not valid under this assumption. Parallel statements in the model should be *disjoint*: no written variables being shared. Data is communicated among parallel processes via *synchronous message passing* only.

The results of this thesis are restricted to programs none of whose communication statements are under the scope of selections. Only sequential and parallelism operators are accepted, like the example above. Nevertheless interesting examples, like the pipeline processor in chapter 6, fall under this class. This limitation stems, on purpose, from a research plan. Obviously elimination of communications outside selection scopes is more tractable than general elimination. Nevertheless it is complex enough to be approached in isolation. The plan was to tackle the selection free case, taking its solution as a base, and then enter into the elimination of communications under selections. In fact, we are, as a joint effort outside the thesis scope, in an advanced stage with respect to the latter case. The difficulties of elimination for general programs, where communications may be under selections, are illustrated in subsection 7.2.4.2. The complexity of analyzing the closely related problem of synchronization of concurrent programs has been treated in [Tay83, Ram00].

# 1.7 The Need for Laws in a Suitable Equivalence

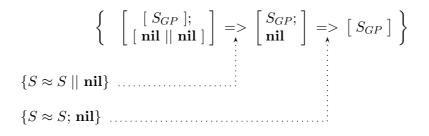

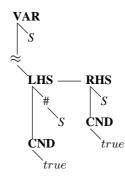

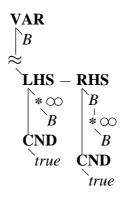

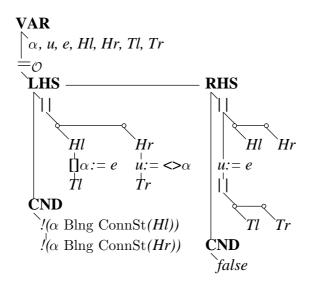

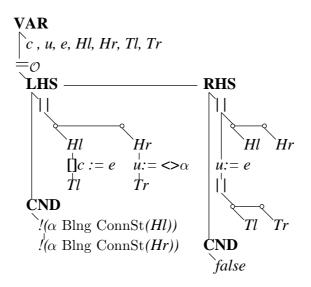

The transformation overviewed above needs laws such as P; nil  $\approx P$ , P||nil  $\approx P$ , and associativity of parallelism, which are auxiliary since they do not eliminate any communication statement. It also requires a proper communication elimination law such as:

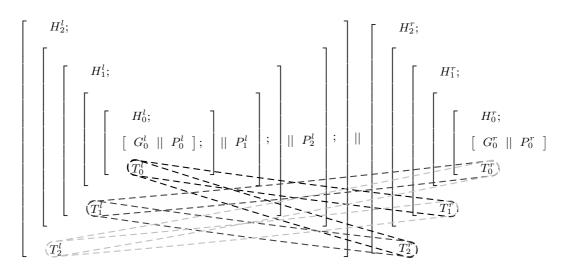

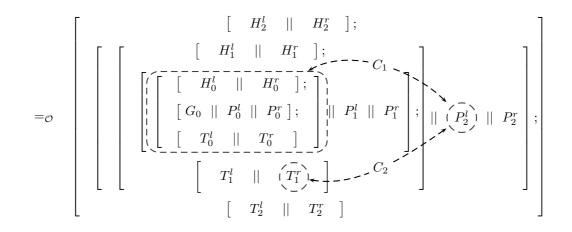

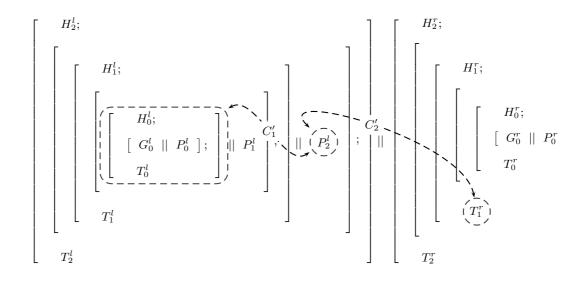

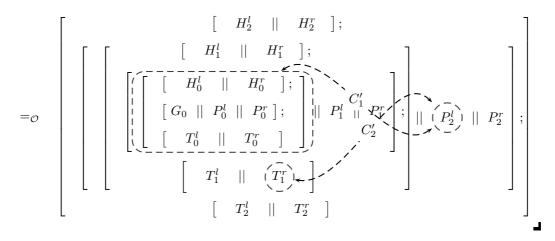

$$\begin{bmatrix} H^{l}; \\ \alpha \leftarrow e ; \\ T^{l} \end{bmatrix} \mid \begin{bmatrix} H^{r}; \\ [\alpha \Rightarrow u \mid | P^{r}]; \\ T^{r} \end{bmatrix} \equiv \begin{bmatrix} [H^{l} \mid | H^{r}]; \\ [u := e \mid | P^{r}]; \\ [T^{l} \mid | T^{r}] \end{bmatrix}$$

which is an instance of the communication elimination schema given in section 3.2.2.  $H^l$  and  $H^r$  statements do not communicate over channel  $\alpha$ . The equivalence symbol is general and will be given concretion in section 2.8.

This law, applied from left to right, eliminates the communication statements over  $\alpha$ , replacing their function with the assignment u := e. The auxiliary laws are necessary in order to transform the program into a form ready for structure matching with an elimination law.

The soundness of the laws depends on the notion of equivalence and on the fairness assumptions [MP91]. A set of laws for OCCAM was given in [RH88]. Although a simple communication elimination law was included, rather than communication elimination, the focus there was to obtain normal forms and to define the semantics of the notation. Communication closed layered systems are a special class of distributed systems, introduced in [EF82]. Some laws for them are given in [dRdBH<sup>+</sup>01], in the framework of SVL<sup>++</sup>. For instance, sequential-parallelism transformation and iteration unfolding transformation laws. The aim there was formal design by transformation, but no communication elimination law was reported. Communication elimination proofs in this thesis use the latter as auxiliary laws. Some laws for SPL are given in [MP91], with a very clear SPL semantics, based on fair transition systems (FTS), but none is for communication elimination. Thus, the work to be presented may be regarded as a concrete continuation line of all these works.

As a needed grounding work for this dissertation, a set of relations for communication elimination was given and proved sound in [BBCN01]. Its cardinality had to be unbounded and strong fairness had to be prohibited. Only weak fairness or no fairness at all are compatible with the soundness of these laws. In this earlier work, the notion of equivalence was assimilated to the congruence of [MP91], a very strong equivalence. This had the drawback of limiting the formulation of most communication elimination laws to unidirectional refinements. The need of working with a weaker equivalence, for all laws and avoiding the asymmetry of refinement relations, was outstanding.

# **1.8 Interface Equivalence and Substitution Rules**

The notion of *interface equivalence* [BBC05b] is weaker than congruence, but strong enough to preserve the input/output relation of distributed programs and to lead to laws for communication elimination. It was also developed as a needed grounding work for this dissertation. There are many other equivalences in the literature, within process algebras [vG01], in the polychrony framework [GTL02], etc. It would be interesting to study interface equivalence in their perspective. A very interesting order among many equivalences has been reported in [dFEGR05, dFEVGR07, dFEGR09]. There, the weakest is *trace equivalence*. Interface equivalence is at the level of trace equivalence. In it all computations with the same intermediate results, but with different relative orders, are equivalent. Interface equivalence is justified in a semantics where each statement denotes a set of *interface behaviors*. These extend the notion of *reduced behavior* given in [MP91]. In order to capture the complete input/output relation, the former adds auxiliary variables, in addition to the usual data state variables, to record the values traversing synchronous channels. This makes explicit the fact that values may be input or output via channels, as well as via proper variables. All these notions were introduced since they were the minimal extensions needed while keeping this work within the framework Manna and Pnueli books. In this semantic context, the grounding work with streams introduced in [Bro97, Bro99, Bro01] is important, but in the concrete imperative program context of this work a new model, where both channel and variable values were explicitly taken into account and distinguished, was needed. The work on compatibility of components [dA03] has some relation also.

Important components of equivalence reasoning are a procedure reference unhiding rule and a rule for the substitution between procedure reference statements, to equivalent procedures. These allow proof decomposition. Conditions for the validity of such substitutions are also given and their justification outlined in [BBC05a] and in this work. Altogether, equivalence and substitution rules establish the necessary base theory for formal interface equivalence reasoning about distributed programs.

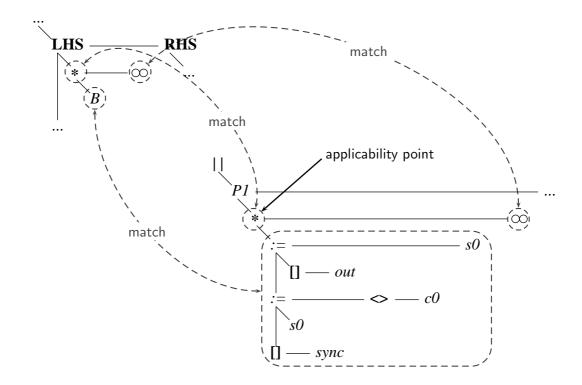

# 1.9 Elimination Procedures and Program Sequentialization Proofs

For the elimination of communications under any nested structure of parallelisms, an infinite set of communication elimination laws are required, [BBCN01]. Nevertheless, communication elimination procedures exist for the automatic application of the laws as reductions. Preliminary work towards the justification of a communication elimination procedure was undertaken in [BBCN01, BBC05b]. Proper communication elimination laws were mathematically justified in the new weaker equivalence in [BBC05a], and their complete set of applicability conditions was derived as part of this thesis. In addition, a communication elimination reduction procedure was proposed and justified, as part of this thesis also.

The inner communication-free program which results from the communication elimination procedure can be transformed interactively, with another set of laws, into a sequential program with less variables than the initial distributed program, but equivalent to it. The whole proof constitutes a *distributed program sequentialization* (DPS) proof. Since it decreases the size of the state vector, it could complement and be combined with other proof methods, such as model checking or interactive verification [BBMC<sup>+</sup>00, KM97] as a succeeding step, reducing overall proof complexity. In many cases, only an equivalent purely sequential program has to be verified. Such is the case for the pipeline processor example presented in chapter 6. Nowadays combining different formal techniques is a promising direction for verifying complex hardware and software system models. Nevertheless, this line is not explored in this dissertation.

A DPS proof of a distributed fast Fourier transform was outlined in [BBCN01]. The result of another DPS proof of a pipelined processor model, carried out with the help of a tool which implements a communication elimination procedure, was reported in [BBC05b], without going into its steps. A very detailed report of the steps of the proof is given in the present work, which also analyzes the substantial state-space reduction obtained with it.

# 1.10 Formal Parallelization

The reported work is very relevant in the popular area of parallelization in formal design. Communication elimination and sequentialization proofs are reversible, since they are equivalence proofs. Consequently any sequentialization proof can be reinterpreted as a formal parallelization process. The laws used in this work would be applied then in the reverse direction; as a parallelism and communication introduction step. References [SSB04, SJ00] provide examples in hardware / software partitioning. A sequential specification is transformed, introducing parallelism and communications into a model of a hardware implementation. Formal design is not treated in this thesis. It is an area of future work, section 7.2 of chapter 7.

At the beginning of our work [BBCN01] both communication elimination and introduction were envisaged. Although the work evolved with a bias to elimination and sequentialization, it could have evolved in the opposite direction. The adaptation of the procedures and tools of this dissertation to formal parallelization is proposed as future work.

# 1.11 Contributions and Plan of this Thesis

For self containment reasons, and as an introduction to the presentation of the main results of this thesis, chapter 2 treats notation and background notions which, although needed for the presentation, do not form part of this thesis, whose main contributions are the following:

- Formulation of *applicability conditions* for the communication elimination law schema, for selection-free programs. This is discussed in chapter 3 and was presented in [BBC05a].

- A communication elimination *proof construction procedure*, which attempts to apply the elimination laws automatically. This is treated in chapter 4. The elimination procedure is integrated within a prover tool.

- A set of *transformation procedures*, that guarantee that the equivalence transformation always corresponds to the application of a sequence of laws. They have been implemented to mechanize some tedious parts of DPS proofs. They are detailed in chapter 5, and are integrated within a prover tool.

- The design and development of an *interactive prover tool* for the semi-automatic construction of distributed program sequentialization proofs. The construction of these proofs is impractical, even impossible, without such a tool. It is described in chapter 5.

- A sequentialization proof of a pipelined processor model, carried out with the help of the tool, with the communication elimination procedure embedded in it. This proof example is detailed in chapter 6.

Throughout this thesis, communication elimination is confined to selection-free programs, i.e. programs none of whose inner communications are in the scope of selection statements. Interesting applications can already be attempted within this framework. The thesis work has created the essential base for the needed extension, which is underway as continuation work.

\_\_\_\_\_

# Chapter 2

# MODELING NOTATIONS AND GROUNDING NOTIONS

This chapter is on notation: syntax, semantics, and related grounding notions on which the proper dissertation work depends. The mathematical apparatus needed to justify communication elimination and DPS equivalence proofs in the notation, the main concern of this dissertation, integrates various notions, which should be defined with precision. Although this mathematical apparatus has been covered elsewhere, this chapter gives an overview, without going into proofs.

After introducing two syntactic forms of modeling notation, a common semantics is discussed: the fair transition systems of Manna and Pnueli with the extended notion of interface behavior. An equivalence based on interface behaviors, some basic laws for this equivalence, procedure unhiding/encapsulation rules, and procedure reference substitution rules constitute a minimal set of notions required to construct equivalence proofs for distributed system models. This chapter presents all these topics, which will prepare the reader to go into proper communication elimination laws, a procedure for their automatic application, the interactive prover tool embedding it, and complex DPS proofs. All these are left for other chapters.

# 2.1 A Tree-like Notation

#### 2.1.1 Introduction

This section introduces informally the modeling notation, PADD [BDP+09], of the prover tool. It adopts an explicit tree form: *dimensional flowcharting*, proposed in [Wit77] and further elaborated into *dimensional design* [Wit81]. An algebraic formalization of dimensional design is given in [Ber88].

Both, models to be equivalence proved and the tool itself are expressed in PADD.

As a side comment, a modeling and simulation based distributed program development environment, RALE, exists for this notation and quite a number of interesting systems have been developed in it at the *General Systems Development* company [GSD]. The following are some of them: a simulator for an open air active noise cancellation system where both the acoustic field and the digital signal processing algorithms are modeled, a simulator of a packet switching communications network for a power utility providing telecontrol, IP-routing, file transfer, and other sorts of services, and many other systems. To give an idea of order of magnitude, the telecommunication network model has about 3000 processes and 5000 communication connections (to be explained later in this chapter).

It should be stressed that, for this dissertation work, PADD is just another syntactic form for the variant of SPL which has been used. Its formal semantics is the same as the one described for such a variant later in this chapter.

#### 2.1.2 Basic Statements

The basic statements are **skip**, **nil**, **stop**, the assignment u := e, and the communication statements, send and receive, to be introduced later. Storage variables are declared within a **var** construct.

#### 2.1.3 Sequence

Sequential composition of statements, also referred to as *concatenation*, is expressed by connecting them with vertical edges.

$$\begin{array}{c} \vdots \\ p1 \\ p2 \\ \vdots \\ pn \end{array}$$

The execution order starts with the upper statement, and continues down the list. Execution ends when the last statement in the list ends.

#### 2.1.4 Scoped Descriptions

Comments are scoped descriptions. They consist of a line of text describing its lower diagonal tree, its scope.

... statements executed before those being described scoped description

... statements being described

... statements executed after those being described

Execution of a diagonally refined comment means execution of its diagonal subtree. When it ends, execution continues at the statements connected vertically under the description line. Within the notation, the diagonal edge denotes *refinement*. Scoped descriptions may be used recursively.

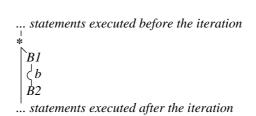

## 2.1.5 Sequential Iteration

A sequential conditional iteration consists of the symbol '\*', denoting the fact that an iteration occurs at this point of a sequence, and the iteration body, standing at its diagonal lower subschema (its refinement).

The boolean expression b can stand at any point of the body. The semicircle at its left makes it more explicit. B1 and B2 are the parts of the body that execute before and after the boolean condition. Both are optional but at least one of them should be present.

Repetition takes place while the boolean evaluates to true. Otherwise exit occurs, and execution continues with the process connected vertically under the iteration symbol '\*'.

The usual indexed iteration, as shown above, is available also. B is the body of the iteration, whose execution is repeated.

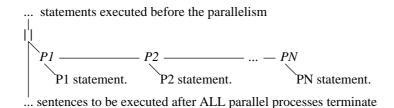

## 2.1.6 Parallelism

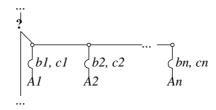

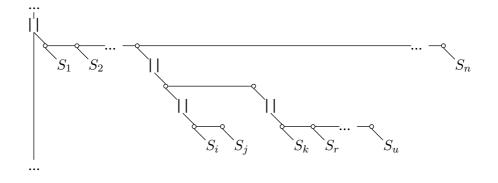

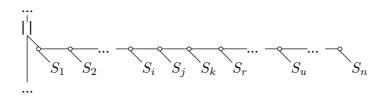

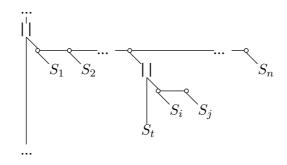

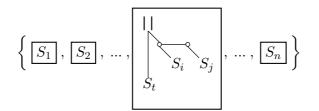

Parallelism is always explicit. The following is the typical parallelism schema connecting  ${\cal N}$  statements in parallel

The execution of each of the statements corresponds to a process, which is a term expressing the dynamical aspect of a statement. Parallel composition of statements is also referred to as *cooperation*. It is defined with the parallel composition construct. The items in the composition have a heading label Pi. Labels are connected horizontally. The symbol '||' represents the whole parallelism within a sequence. The horizontal list of processes is its lower diagonal refinement, connected to it by the diagonal edge.

Execution starts by creating and starting all processes. The relative order of execution of their component subprocesses is unknown, in principle. Execution ends only when all process end, and continues with the sentence connected in sequence after the symbol '||'.

## 2.1.7 Connections

Connections are typed but memoryless points which enable synchronized half-duplex point to point communication between two parallel processes. They are declared before the parallelism operator, as in the following schema.

```

\begin{bmatrix} con \\ con1: TypeCon1 \\ con2: TypeCon2 \\ \dots \\ P1 - \dots - PN \\ \dots \\ \dots \\ \dots \\ \dots \\ \dots \\ \dots \end{bmatrix}

```

Connections will be used within the processes connected in parallel in order to send and receive values. Communication takes place when communication statements are executed. This will be explained later. The **con** construct declares connections to be used within an algorithm. Their scope is the vertical subschema under the keyword **con**. They are unseen anywhere else.

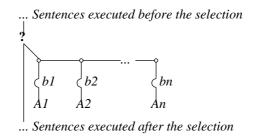

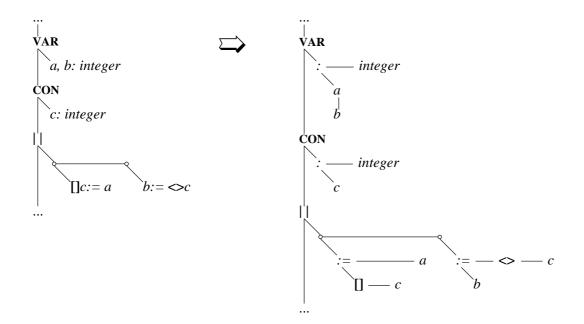

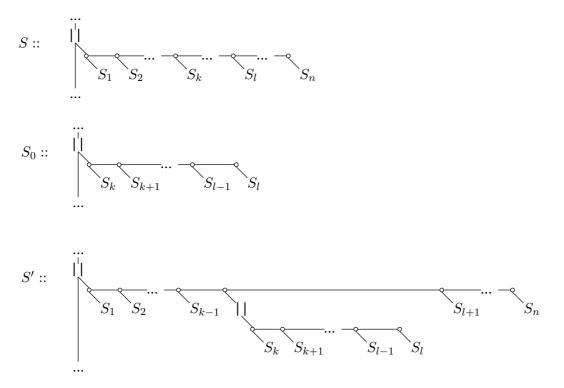

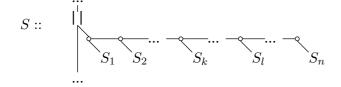

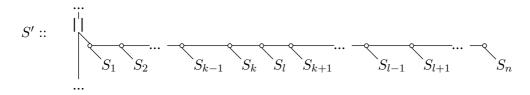

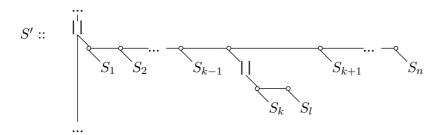

A **con** construct with a parallel composition of processes communicating through the declared connections within its scope, defines the framework for a network of communicating processes.