# HPC memory systems: Implications on system simulation and check-pointing

# Rommel Sánchez Verdejo

Supervisor: Dr. Petar Radojković

Advisor: Dr. Eduard Ayguadé

Department of Computer Architecture Universitat Politècnica de Catalunya

This dissertation is submitted for the degree of  $Doctor\ of\ Philosophy$

Barcelona, 2021

| From the past and to | the future, for my | family friends and colle | agues. |

|----------------------|--------------------|--------------------------|--------|

|                      |                    |                          |        |

|                      |                    |                          |        |

|                      |                    |                          |        |

# Acknowledgements

In the first place, I would like to thank my supervisor, Petar Radojković, for the trust he deposited on me to become member of the memory systems for High Performance Computing (HPC) group; his detail-oriented guidance, support, and honest feedback had complemented my professional growth since our first conversations up to the complete realization of this work.

To the Barcelona Supercomputing Center (BSC), for creating the world-class research institution that enable all of its members to perform at their best.

To the Universitat Politècnica de Catalunya (UPC) and the efforts that had established the bond with BSC. Particularly, to Eduard Ayguadé for keeping those bonds alive along with his strong supervision in all of our work as Ph.D. students. To Joana Munuera and Nuria Sirvent, who year to year, help us to clear all the paperwork and the administrative tasks.

To Leonardo Bautista-Gómez, for the opportunity to work closely under his advise extending the Fault Tolerant Interface (FTI) library so that I could follow my research project.

To the members of my pre-defense committee: Adrià Armejach, Eduardo Quiñones, and Lluc Álvarez who amid the COVID-19 pandemic, pushed me further to deliver the best out of this thesis.

To my BSC Ph.D. peers: Kazzi Asifuzzaman, Milan Radulovic, Darko Živanović, and David Zaragoza who helped me at different points and levels on the road of the Ph.D. formation. To Kallia Kronacli, Rajiv Nishtala, Sicong Zhuang, Renan Fisher, Tomasz Patejko and Isaac Boixaderas for their friendship along the way.

To all the authors in the free software community that have written millions of lines of code and documentation that we all use in our daily basis to complete our goals for work and fun. To finish with the professional acknowledgements, to all the authors in the indexed engineering and scientific databases that allows knowledge to keep spreading.

On the personal side, the first and most important person I have to acknowledge is to my mother, María del Carmen Yolanda Verdejo Aguilar, for whose infinite love and support had allowed me reach this far.

To the extended members of my family: Alfonso, Félix and Aarón Verdejo for their extensive support throughout my lifetime. To my father, who taught me that among humans, reason is always stronger than physical strength.

To my friends, Eduardo Ruiz Duarte and Omar Lara Salazar, whose (un)human and philosophical advises, had being there for some time now.

To Elizabeth Lozano Lozano, who had showed me the true value of honesty and love.

To Eria López (Siri en el exilio), her long-standing friendship had always shown me a different perspective from my natural approach. Also, to demonstrate to me that with tight discipline, goals are achieved, despite the injuries along the way.

To Szófia Bendefy for her long standing love and support through the last year of this process.

To the Spanish Government, the Generalitat de Catalunya, the province of Barcelona and the Sant Just Desvern Ajuntament to provide me with a wonderful experience living abroad.

Part of this work was supported by the collaboration agreement between Samsung Electronics Co., Ltd. and the Barcelona Supercomputing Center (BSC); Spanish Ministry of Science and Technology (project TIN2015-65316-P); Generalitat de Catalunya (contracts 2014-SGR-1051 and 2014-SGR-1272); the Severo Ochoa Programme (SEV-2015-0493) of the Spanish Government.

#### Abstract

The memory system is a significant contributor for most of the current challenges in computer architecture: application performance bottlenecks, and operational costs in large data-centers as HPC supercomputers. With the advent of emerging memory technologies, the exploration for novel designs on the memory hierarchy for HPC systems is an open invitation for computer architecture researchers to improve and optimize current designs and deployments. System simulation is the preferred approach to perform architectural explorations due to the low cost to prototype hardware systems, acceptable performance estimates, and accurate energy consumption predictions. Despite the broad presence and extensive usage of system simulators, their validation is not standardized; either because the main purpose of the simulator is not meant to mimic real hardware, or because the design assumptions are too narrow on a particular computer architecture topic.

This thesis provides the first steps for a systematic methodology to validate system simulators when compared to real systems. We unveil real-machine's micro-architectural parameters through a set of specially crafted micro-benchmarks. The unveiled parameters are used to upgrade the simulation infrastructure in order to obtain higher accuracy in the simulation domain. Next, to evaluate the accuracy on the simulation domain with respect to the real machine, we propose the *retirement factor*, an extension to a well-known application's performance methodology. Our proposal provides with a new metric to measure the impact of simulator's parameter-tuning when looking for the most accurate configuration for the simulator's parameters. We further present the *delay queue*, a modification to the memory controller that imposes a configurable delay for all memory transactions that reach the main memory devices. Evaluated using the *retirement factor*, the *delay queue* allows to identify the sources of deviations between the simulator infrastructure and the real system.

Memory accesses directly affect application performance, both in the real-world machine as well as in the simulation accuracy. From single-read access to a unique memory location up to simultaneous read/write operations to a single or multiple memory locations, HPC applications memory usage differs from workload to workload. A property that allows to glimpse on the application's memory usage is the workload's memory footprint. In this work, we found a link between HPC workload's memory footprint and simulation performance.

Actual trends on HPC data-center memory deployments and current HPC application's memory footprint lead us to envision an opportunity for emerging memory technologies: to include them as part of the reliability support on HPC systems. Emerging memory technologies such as 3D-stacked DRAM are getting deployed in current HPC systems but in limited quantities in comparison with standard DRAM storage; therefore, they are suitable for low memory footprint HPC applications. We exploit and evaluate this characteristic enabling a Checkpoint-Restart (CR) library to support a heterogeneous memory system deployed with an emerging memory technology. Our implementation imposes negligible overhead while offering a simple interface to allocate, manage, and migrate data sets between heterogeneous memory systems. Moreover, we showed that the usage of an emerging memory technology it is not a direct solution to performance bottlenecks; correct data placement and crafted code implementation are critical when comes to obtain the best computing performance.

Overall, this thesis provides a technique for validating main memory system simulators when integrated in a simulation infrastructure and compared to real systems. In addition, we explored a link between the workload's memory footprint and simulation performance on current HPC workloads. Finally, we enabled low memory footprint HPC applications with resilience support while transparently profiting from the usage of emerging memory deployments.

# Contents

| $\mathbf{A}$ | bstra             | act                                                  | vi |

|--------------|-------------------|------------------------------------------------------|----|

| 1            | Intr              | roduction                                            | 1  |

|              | 1.1               | Current challenges for Memory Systems in HPC         | 2  |

|              | 1.2               | Thesis Contributions                                 | 4  |

|              |                   | 1.2.1 System Simulation for Memory Exploration       | 4  |

|              |                   | 1.2.2 Opportunities for Emerging Memory Technologies | 4  |

|              | 1.3               | Thesis Organization                                  | 5  |

| 2            | Stat              | te Of The Art                                        | 7  |

|              | 2.1               | Background                                           | 8  |

|              |                   | 2.1.1 Requirements                                   | g  |

|              | 2.2               | CPU Simulators                                       | 11 |

|              | 2.3               | Memory Simulators                                    | 13 |

|              | $\frac{2.5}{2.4}$ | Hardware Performance Counters                        | 14 |

|              | 2.5               | CPU Micro-benchmarks                                 | 15 |

|              | 2.6               | Memory Micro-benchmarks                              | 16 |

|              | 2.7               | Validation in the State Of The Art                   | 17 |

|              | 2.8               | Decision Process                                     | 19 |

| 3            | Exp               | perimental Methodology                               | 20 |

|              | 3.1               | Hardware Platform                                    | 21 |

|              | 3.2               | Simulation Model                                     | 22 |

| 4            | Mic               | ero-benchmark Design                                 | 26 |

|              | 4.1               | Micro-benchmarks Proposal                            | 27 |

|              | 4.2               | Instruction Latency and Port Utilization             | 29 |

|              |                   | 4.2.1 Micro-benchmark Evaluation                     | 30 |

|              | 4.3               | Memory Hierarchy Discovery Characterization          | 32 |

|              | 4.4               | Summary                                              | 34 |

| 5            | Per               | formance Evaluation                                  | 35 |

|              | 5.1               | Experimental Environment                             | 35 |

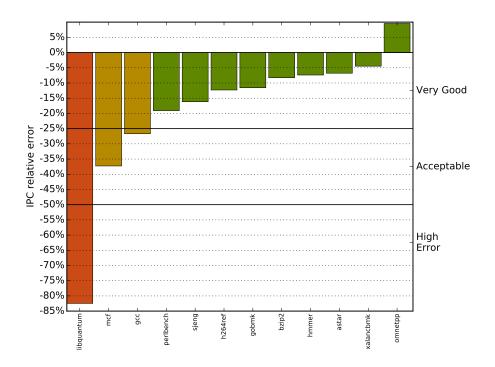

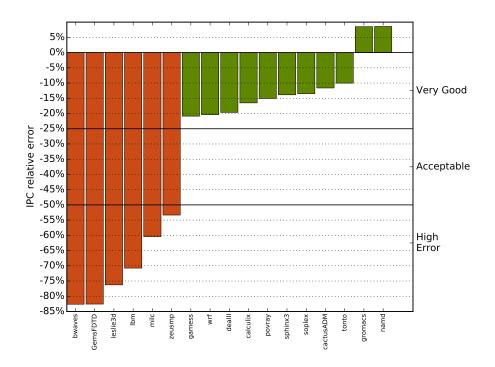

|              | 5.2               | SPEC CPU2006 Performance Evaluation                  | 37 |

Contents

|   | 5.3        | V                                                                | 39<br>40        |

|---|------------|------------------------------------------------------------------|-----------------|

|   | 5.4        | 5.3.2 SPEC CPU2006 floating-point set                            | 41<br>43        |

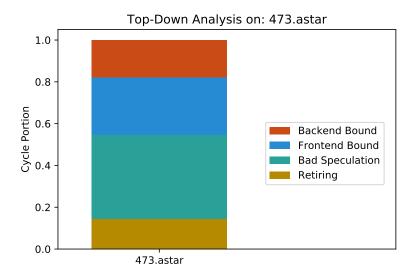

| 6 | Ton        | -Down Method and the Retirement Factor                           | 44              |

| U | 6.1        |                                                                  | <b>44</b><br>44 |

|   | 6.2        | Top-Down Implementation                                          | 46              |

|   | 6.3        | Top-Down for Micro-architecture Comparison                       | 48              |

|   | 6.4        | The Retirement Factor                                            | 50              |

|   | 6.5        | Summary                                                          | 52              |

| 7 | The        | Delay Queue and Top-Down Evaluation                              | 53              |

|   | 7.1        | The Delay Queue                                                  | 54              |

|   | 7.2        | SPEC CPU2006 Analysis Using Top-Down and the Retirement Factor . | 55              |

|   | 7.3        | Impacts of Hardware Prefetchers and Address Translation          | 57              |

|   | 7.4        | Memory Utilization                                               | 60              |

|   |            |                                                                  | 62              |

|   | 7.5        | Summary                                                          | 64              |

| 8 | Opp        | portunities For Emerging Memory Systems: Check-pointing in       |                 |

|   | Het        | 0 0                                                              | <b>65</b>       |

|   | 8.1        |                                                                  | 66              |

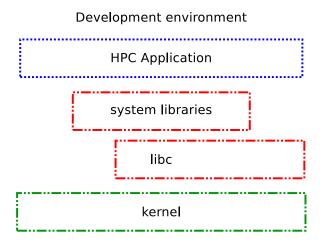

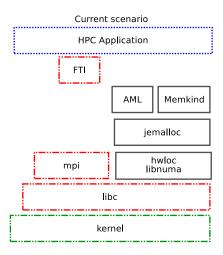

|   | 8.2        | System Libraries                                                 | 67              |

|   |            | 8.2.1 libc                                                       | 67              |

|   |            | 8.2.2 Computer Topology and System Libraries                     | 68              |

|   |            | 8.2.3 Memory Allocation                                          | 69<br>71        |

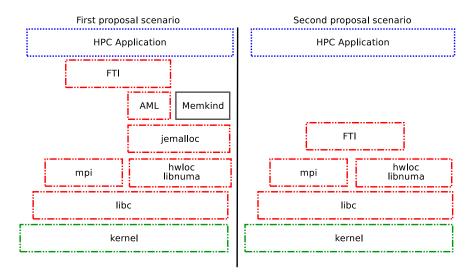

|   | 8.3        | Methodology                                                      | 73              |

|   | 8.4        | Implementation                                                   | 75              |

|   | 0.1        | 8.4.1 FTI Integration with AML                                   | 75              |

|   |            | 8.4.2 FTI's Native Implementation                                | 76              |

|   | 8.5        | Evaluation                                                       | 78              |

|   |            | 8.5.1 Experimental Setup                                         | 78              |

|   |            | 8.5.2 Sensitivity to Code Implementation and Data Location       | 78              |

|   |            | 8.5.3 Implementation Impacts on FTI_Checkpoint()                 | 80              |

|   | - <b>-</b> | 8.5.4 Impacts on Real-World HPC Applications                     | 81              |

|   | 8.7        | Summary                                                          | 84              |

| 9 | Cor        | aclusions                                                        | <b>85</b>       |

|   | 9.1        | Impacts of System Simulation                                     | 85              |

|   | 9.2        | Opportunities for Emerging Memory                                |                 |

|   |            | Technologies                                                     | 86              |

|   | 9.3        | Future Work                                                      | 88              |

| Contents                | X   |

|-------------------------|-----|

| A Instruction Latencies | 89  |

| References              | 103 |

| List of Figures         | 119 |

| List of Tables          | 121 |

# CHAPTER 1

#### Introduction

Supercomputers, also known as High Performance Computing (HPC) systems, had become a technology pillar of our society's lifestyle. Governments and enterprises through public and private funded institutions, make available cutting-edge computing systems to a multi-disciplinary group of researchers to solve the most challenging defiances of humanity. For example, to find appropriate treatments and a possible vaccine for the COVID-19 throughout the SARS-CoV-2 outbreak in Europe, researchers from different scientific fields requested High Performance Computing (HPC) resources that were quickly allocated from the European Union representatives [42].

A HPC system comprises large clusters of thousands of single-computers connected through high-speed networks. Each one of these single-computers has a computing performance peak, which combined adds to a greater computing power. The preferred metric to measure computing power is Floating-point Operations per Second (FLOPS). During the 2010's decade, the performance of HPC systems went from a few peta FLOPS (PFLOPS: 10<sup>15</sup> FLOPS) up to hundreds of PFLOPS: as per June 2020, the fastest supercomputer peaks at 415.5 PFLOPS [40]. It is expected that in 2021 the HPC roadmap will meet a tangible milestone: the power-on of the first exascale computer [5]<sup>1</sup>. An exascale supercomputer is a system that could compute at least a single exaFLOPS (EFLOPS): 10<sup>18</sup> FLOPS. To reach the global peak computing power, every processor in the supercomputer must maximize its throughput by minimizing idle time. Code and data must be delivered to the processor at the right moment in the right shape. Bringing and returning data into and out of the CPUs cores are challenging tasks that are constantly revisited by the research community.

<sup>&</sup>lt;sup>1</sup>There is a chance for China's Tianhe-3 supercomputer will be powered-on in late 2020. On July 2020, China's National University of Defense Technology (NUDT), the research institution that will host the supercomputer, have not disclosed any further information.

From the abstraction of an infinite tape in the formal definition of a Turing Machine up to today's banks of electronic memory cells, the memory subsystem is an inherent piece of a computing system. Nowadays, the memory subsystem comprises a multi-level memory hierarchy where the closest levels to the CPU have faster access time than the subsequent levels. In fact, CPU silicon vendors built the first levels of the memory hierarchy within the same silicon package; these levels are known as memory caches. The memory that is found outside the silicon package is known as main memory.

The different access times on the memory hierarchy generally translates to idle times for the processor. As the manufacturing processes had evolved, the processor could compute data faster than what the memory subsystem could load or store. This behavior was first named the memory wall [145] and studied in subsequent years [58]. Even with CPU micro-architectural techniques such as CPU's Out of Order (OoO) execution or data-prefetching as attempts to minimize processor's idle time, sometimes the processor must stall its execution until the memory transactions completes, making the memory subsystem a major contributor to bottlenecks for computing performance.

# 1.1 Current challenges for Memory Systems in HPC

Throughout the last 40 years, in a combination of cost and performance [77, 63], the predominant technology used for main memory is DRAM. Unfortunately, application requirements are pushing DRAM to its physical limits: as memory capacity rises, the energy consumption also increases; the manufacturing miniaturization process affects reliability and therefore security; and lastly, the DRAM protocol imposes bandwidth limitations.

Memory capacity: The trend to have more data-intensive applications in the HPC data-centers is growing [153, 118, 25]. To run such applications, larger amounts of memory are required to be physically installed in the computing node. Due to the internal structure of DRAM, which includes a capacitor that must be constantly refreshed even when the memory cells are not used, the main memory is responsible for an approximate two-thirds of the power consumption of a computing system [23]. This represents a major challenge for scalability with respect to power efficiency in HPC data centers: the more DRAM devices, the higher the power consumption will be.

Memory reliability and security: In an attempt to reduce the number of main memory devices in a system, DRAM manufacturers have increased the density of the memory cells within the same device; an approach that has strong consequences: uncorrected error rates in DRAM devices increase when manufacturing technology scales down [150]. Researchers have analyzed the impact of the miniaturization process finding serious implications for data integrity. Particularly, Rowhammer [84] is a technique that exploits the electrical characteristics of DRAM devices leading to critical system failures, or even computer security breaches [109]. Even with the presence of Error Correcting Codes (ECC) logic and software-counter measures in HPC computing systems [60], reliability in DRAM devices is still an open challenge.

Memory bandwidth: The inclusion of several cores into the same processing unit allows HPC applications to exploit parallel processing; multiple cores might request for several memory transactions at the same time. The amount of in-flight requests in the memory hierarchy stresses the cache coherency protocol increasing the latency per memory request. Each one of the processing cores within a processor is generally designed so that their first and second levels of memory caches are not shared with the other cores. The capacity of such caches holds from some KiB up to a few MiB. Moreover, in HPC systems, a third level of cache (commonly referred as Last Level Cache (LLC)), is found to be shared among all cores in the same processor package with capacities that hold up to tens of MiB. In multi-threaded applications, the Operating System (OS) schedules the execution of threads trough context switching. If the HPC application wisely exploits memory locality and memory level parallelism, the theoretical maximum bandwidth for DDR3 and DDR4 might be quickly achieved while the CPU cores could still have idle cycles due to in-flight memory transactions.

Software interfaces: Furthermore, as the emerging memory technologies continue to evolve, so must the software interfaces. A common rule from OS designers is to provide the application developer with hardware-abstraction layers that require little or no understanding of the underlying hardware. Unfortunately, for emerging heterogeneous memory technologies, this is not always the case. Most HPC applications are not prepared to support emerging memory technologies integration. Although some important efforts have been made to bring automatic assignment for memory resources to the applications, developers must know the low-level details of the memory hierarchy to exploit emerging memory technologies; in most cases, this is a specialized knowledge that ends up in a computer programmer specialist coding for this purpose.

#### 1.2 Thesis Contributions

System simulation is the preferred option for computer architecture researchers to propose and evaluate novel designs to solve memory hierarchy challenges. This thesis analyzes the implications of system simulation for memory exploration in HPC systems, and proposes a methodology for their validation in regards of real systems. Moreover, we analyzed the performance impact of enabling HPC applications to use an emerging memory system.

#### 1.2.1 System Simulation for Memory Exploration

Nowadays, system simulators require the modeling of sophisticated features found in real-world computing platforms such as multi-core CPUs, different memory devices and, the interconnects which couple them together. In this work we describe a methodology to validate system simulators in regards to real-world hardware so that results are suitable for memory exploration.

Using a real machine as the target system to mimic in simulation, we proposed a set of micro-benchmarks to discover micro-architectural parameters on both, the CPU and the memory hierarchy. Then, we integrated the obtained parameters on the real machine into the simulator infrastructure so that the simulator infrastructure behaves accordingly. After an initial evaluation, we discovered a discrepancy on memory simulation, particularly on workloads with high memory usage. In order to locate the source of the differences between the real machine and the simulator infrastructure, we proposed an architectural modification to the memory controller that inserts a delay of the memory transactions that goes to main memory. To identify the impacts of such change, we further proposed an extension to a well-known Cycle Per Instruction (CPI) stack analysis to evaluate different configuration scenarios. Finally, we analyzed the effects of hardware prefetching and address translation. By analyzing the address translation and virtual memory usage, our results pushed us to further explore the memory footprint of HPC applications where we found a link with simulation performance.

# 1.2.2 Opportunities for Emerging Memory Technologies

One way to overcome hardware reliability problems in HPC systems is done through Checkpoint-Restart (CR). CR is a technique used in current HPC applications where application's data status is saved into a secondary storage so that in the event of a failure, the computation performed up to that moment along with current application's status is not completely lost.

Emerging memory technologies bring improvements to the memory hierarchy either by decreasing access times, reducing power consumption, or some advances in the manufacturing process. Although they are still deployed with in small capacity configurations making their usage suitable for low memory footprint HPC workloads. Given these conditions, we envision an opportunity for these workloads to profit from actual emerging memory technologies such as Multi-Channel DRAM (MCDRAM) integrations found in some HPC data centers. To achieve this goal, we enabled a software CR library to make usage of different memory technologies. If the memory footprint of a given variable within the scope of the HPC application is compact enough to fit into the current deployment of an emerging memory technology, we enable the HPC application with the reliability support while transparently profiting from the usage of such emerging memory technology.

# 1.3 Thesis Organization

This thesis is comprised by this introduction, 7 chapters, an appendix, and an overall conclusion with the following structure:

- Chapter 2 describes the basic definitions and requirements for the simulation infrastructure. Moreover, introduces the state-of-the-art projects that we considered relevant for this research.

- In Chapter 3, the experimental methodology is described along with a description of the micro-architectural models for the real targeted HPC system as well as the for the two system simulators we used in this work is presented.

- In Chapter 4, the design assumptions and the challenges of the proposed microbenchmarks for parameter-discovery in the real system CPU and the memory hierarchy are described. The Chapter elaborates on the execution environment for the micro-benchmarks in both systems (real and simulated). Lastly, the Chapter describes the formal mechanism to extract experimental measurements.

- In Chapter 5, a classical approach to validate system simulators in the state-ofthe-art is presented. The results are discussed.

- In Chapter 6, we propose the usage of the Top-Down methodology for microarchitectural comparison. Furthermore, we extend the methodology to allow us

measure the differences among the real system and the simulator infrastructure. This extension is named the retirement factor.

- In Chapter 7, we propose an architectural modification to the memory controller to mitigate gaps in memory simulation. We further stretch-out our retirement factor for two purposes: 1. we used our memory simulation mitigation to locate the source of differences between the systems under test, and 2. to measure the impact of hardware prefetchers and address translation in the real system when compared to the simulation infrastructure. Lastly, we found a relation between workload's memory footprint and simulation performance.

- In Chapter 8, we conduct a case-study for low-memory footprint applications to use heterogeneous memory systems while transparently enabling them with reliability support.

- In Chapter 9, the conclusions and further directions of this work are presented.

- Finally, Appendix A extends Chapter 4 with a table that includes the upgraded instruction latencies on the CPU simulator.

#### State Of The Art

In the last years, the trend to propose new designs in computer architecture is steeply changing. The tendency had been known as a new golden age in computer architecture [64]. In the previous decades, the hardware tech giants were the only players in the proposal's stage. Year after year, Independent Hardware Vendors (IHVs) position their latest products to the market so that everyone would have to consume their designs. For computer architecture researchers, it meant a spiral where a product is reviewed extensively, and new proposals arose to extend commercial designs. Unfortunately, industrial hardware designs are not publicly available; researchers had to find an open mechanism to reproduce results from actual hardware. Such restrictions had driven researchers to work in system simulators that enable the community to test and evaluate their designs, comparing them with real-world computers.

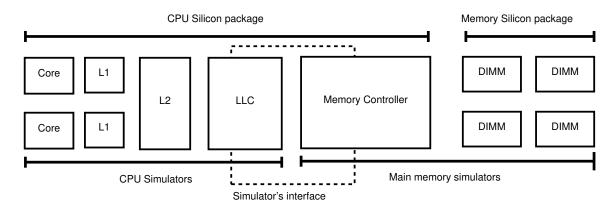

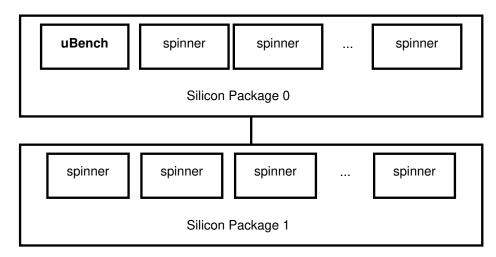

Figure 2.1 When CPU and memory simulators are coupled, the timings of the memory request between the LLC and the memory controller could be easily overlooked or misinterpreted.

2.1 Background

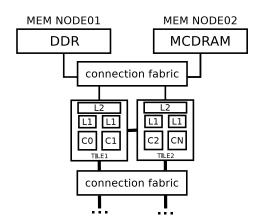

Figure 2.1 depicts two major domains of system simulators: CPU system simulators include micro-architectural logic along with its memory caches while memory system simulators integrate the memory controller logic and up to the passive memory devices (the DRAM DIMMs). The significant difference between the simulator domain and the real domain is the memory controller's location. To the best of our knowledge, all current HPC systems integrate the memory controller into the same silicon package as the CPU. The reason relies in the physical improvements to decrease the latency imposed by current DRAM technologies. In the simulation domain, the physical constraints are not always included in the simulated model.

As the exascale era is getting closer [5], cycle-accurate simulators are hitting a wall in simulation time. Researchers showed that a full execution of a single benchmark of the SPEC CPU2006, takes over 1 year in the most detailed configuration of the gem5 CPU simulator [21] and, over 1 week in the most simplified configuration possible. In contrast, the same workload execution in a native system consumes less than 1 hour [126]. New strategies to speed up CPU and main memory simulation are being proposed [85, 90, 30, 125] in an exchange of cycle-accuracy simulation [21, 122]. Though, every benefit comes with a price; when cycle-accurate simulation is combined with approximate simulation, results must be taken with caution [91, 138].

# 2.1 Background

A system simulator <sup>1</sup> is generally a software or software-hardware (hybrid) solution that mimics to some extent a hardware design. It provides the researcher with tools to propose changes to the baseline design or extend the characteristics towards a new solution.

According to state-of-the-art definitions [43, 8], system simulators could be categorized as follows:

- Detail of Simulation

- Functional simulators: emulate the behavior of the simulated processor, generally not considering the micro-architectural characteristics. For this reason, the execution is faster than any other simulation.

<sup>&</sup>lt;sup>1</sup>For the scope of this thesis, we will use the term *computer simulator* or *system simulator* to refer a software entity that provides an evaluation of computer architecture programmed model.

2.1 Background 9

- Timing simulators: they consider the micro-architectural states of the processor. According to the details provided in the internal states, they can be sub-categorized as:

- \* Cycle-level: mimics the micro-architecture at cycle level; although they are not as accurate as a Register-Transfer Level (RTL) cycle-accurate simulation, they could provide information on some of the underlying components of a micro-architecture.

- \* Event-driven and Interval-driven: targets simulation by events instead of cycles. Both simulators could break the simulation in windows of events like cache-misses or number of instructions.

- Integrated Timing and Functional simulators: in order to speed simulation time, these techniques are mixed to provide a new type of simulator. Two commonly referred techniques are: Functional-first simulator and Timing-first simulator. As an example of the first, a functional simulator in the frontend could feed with execution traces (in memory or through a file system backed-up file) to a backend timing simulator. An example of the second would be to use a functional simulator to validate (within a given error range) the execution of a timing simulator.

- Scope of the target

- **Full-system**: simulates an entire platform allowing the simulator to boot the simulated machine and load an OS.

- User-level or Application-level: the simulator executes the targeted workload within OS process execution boundaries.

- Input Driven

- **Trace-driven**: the simulator consumes *execution traces* (often, file-system backed-up files) which consist of collected information useful to the simulator to recreate the execution of the targeted workload.

- **Execution-driven**: As oppose to the trace-driven approach, the simulator executes the targeted workload as if it were the targeted machine.

# 2.1.1 Requirements

At the Barcelona Supercomputing Center (BSC) memory systems group, we are not focused uniquely in the CPU features but also in the memory hierarchy where 2.1 Background 10

the interactions with the main memory devices are in our particular interest. The requirements of the *Memory Systems group for HPC* for the simulation study are:

#### • Simulation time

Simulation time: we considered a reasonable time for executing a simulation in less than 72 hours. e.g., it is impractical to wait for a week or more into a single experiment to complete [126].

#### • HPC applications

- Simulation of large-scale HPC applications: Message Passing Interface (MPI) applications with tens, hundreds, even thousands of processes [16].

- HPC applications have repetitive behavior: the main loop of the applications performs similar processing on different data.

- In an exploratory execution on the real platform, our targeted workloads lasts in average 10 s to complete the 50 billion of instructions.

- User-level simulation (not full-system) is sufficient for our research. We prefer to avoid full-system simulation in order to reduce the simulation time.

#### • CPU

- The simulator has to be validated against real hardware. Although the correctness of the system simulator is often provided via validation of real hardware. Most of the CPU simulators in the state-of-the-art, are validated versus outdated micro-architectures.

- Simulation of high-end x86 multi-core processors such as Intel's Sandy Bridge: the HPC architecture installed on most of the MareNostrum 3 nodes.

- We cannot simulate only in-order cores. Our purpose is to stress the memory hierarchy up to the main memory. This decision implies to include OoO cores, to allow the micro-architecture to continue fetch, decode, and dispatch instructions after a single load or store.

- Simulation of at least one socket. BSC memory group is interested in the memory hierarchy: in current architectures main memory is shared among all the processes that run on a node. In order to have a representative use case, we have to simulate all the processes that execute on a single node. A

2.2 CPU Simulators

possible option is to simulate a single socket and the corresponding memory (the memory directly connected to this socket) claiming that this is good enough because:

- \* The HPC system should be advanced enough to allocate application's data into the same Non-Uniform Memory Access (NUMA) node, (see Section 8.2.2).

- \* Access to remote memory location causes additional latency and system contention that leads to performance loss [107, 37]. Nodes in the MareNostrum 3 supercomputing cluster are 2-socket systems. Memory transactions originated in on socket with reference to the other, are served through the Intel technology.

#### Main memory

- \* The primary objective of the simulation infrastructure is the analysis of HPC main memory systems.

- \* DRAMsim2 [122] is considered the standard tool for memory system simulation. DRAMsim2 is a cycle-accurate model of a DRAM memory controller, DIMMs, and buses by which they communicate. All major components in a modern memory system are modeled as their own respective objects within the source code, including ranks, banks, command queue, the memory controller, etc. DRAMsim2 was developed by University of Maryland and validated against manufacturer Verilog models. DRAMsim2 can be integrated with various CPU simulators (although not all of them) using a reasonably fairly simple interface.

#### 2.2 CPU Simulators

The most widely used CPU system simulator is **gem5** [21]. Since 2002, more than a hundred publications are referred to improve, extend, or use this simulator. It originated as a merge of the CPU's pipeline M5 simulator [22] and the memory hierarchy inherited from GEMS [99]. The gem5 is a multi-architecture simulator that can perform cycle-accurate, event-driven or hybrid (both, event-driven and cycle-accurate) simulation. Moreover, gem5 can perform as a full-system or user-level simulator. Regarding the x86 Instruction Set Architecture (ISA), the micro-architecture implementation is not explicitly bound to a specific Intel's or AMD's product; gem5 act as a functional ISA

2.2 CPU Simulators

simulator. To achieve main memory simulation, gem5 might use internal memory models or integrate an external memory simulator.

Sniper [30] is among the most used simulators. Sniper is the result of an enhancement of the Graphite parallel simulation infrastructure [106]. The simulator implements several features for the x86 micro-architecture, such as multi-threading, DVFS support, or the implementation of hardware prefetchers. Sniper is a user-level, event-based (Interval-Core model) simulator [52]. For main memory access, the simulator uses a fixed latency model with the option to add a normal distribution on top of it. Sniper does not provide the possibility to add an external memory simulator.

MARSSx86 [112] is a full-system x86 simulator built on top of QEMU [14] enabling OS execution. For the CPU simulation, MARSSx86 extends PTLsim [147], a cycle-accurate simulator that models a generic processor's pipeline. For the x86 micro-architecture, it aims to behave as an Intel Core 2, Intel Pentium 4, or an AMD K8. In 2005, MARSSx86 was the first available full-system x86 open-source simulator.

TaskSim [120] is a trace-driven multi-core simulator developed at the BSC aimed to simulate large-scale HPC applications. A task in TaskSim is the computation performed between application's synchronization events; these events are used as milestones in an interval-based simulation. MUSA [59] implements a simulation infrastructure that uses TaskSim for the computation phases. Traces are recorded during an execution of a compile-time instrumented binary. Some of the details of the underlying architecture, such as the Instruction Per Cycle (IPC) performance, are measured and recorded so that the simulator uses this information to extrapolate performance metrics. MUSA allows detailed DRAM simulation through external memory simulators.

**ZSim** [125] is a user-level simulator developed by researchers at Stanford University and the MIT. Currently, it is the fastest CPU simulator attaining up to 300 MIPS being capable of performing a simulation of over a thousand cores. It uses Dynamic Binary Translation (DBT) through Intel PIN [97] allowing faster execution times compared to other simulators. ZSim is an interval-based simulator, where two phases are involved; 1) the *Bound phase*, where every core is simulated in isolation from each other to enable fast parallel simulation, and 2) the *Weave phase*, where the simulation is corrected to account for a potential collision between concurrent memory accesses. ZSim supports two alternatives for the main memory simulation: an internal memory model based on the M/D/1 queue contention, and a software interface to use an external memory simulator.

In **HSCC** [94], authors propose a mechanism to exploit the memory access patterns on application's memory working-set with a page-locality granularity. In their proposal,

the authors have extended ZSim CPU simulator with a one-level Translation Lookaside Buffer (TLB) allowing virtual-to-physical address translations and tracking application's memory requests at page level. In the proposal, a flat memory space is divided between two memory technologies: a DRAM and a non-volatile region, where the DRAM acts as a cache for the non-volatile region. To provision memory heterogeneity, HSCC's researchers had used NVMain2.0 [114] as the external main memory simulator for both DRAM and non-volatile memory.

# 2.3 Memory Simulators

For a detailed simulation on the DRAM devices, a specialized DRAM simulator has to be integrated with a CPU simulator. On the main memory simulators, an effort has been made to address a detailed simulation of the DRAM devices, the memory controller, and the interconnect to access it. In 2012 ISCA, winners of the Memory Scheduling Championship presented **USIMM** [32]: a trace-based simulation infrastructure for DRAM devices focusing on the memory controller scheduling algorithm. In the same year, Jeong [80] et al. had proposed **DrSim**; a traced-based DRAM simulator prepared to interact with a specific version of **gem5**. Unfortunately, to the best of our knowledge, neither of these simulators are maintained any longer.

DRAMsim [142] is the first open-source cycle-accurate DRAM simulator. Developed to explore different physical parameters to achieve optimal memory system performance, authors have abstracted several timing models for technologies such as: SDRAM, DDR, DDR2, DRDRAM, and FB-DIMMs. Limitations mentioned by Wang et al. in DRAMsim original work, were addressed in 2011 by Rosenfeld et al. in DRAMsim2 [122] proposal. DRAMsim2 provides a detailed timing simulation of main memory following DDR2 and DDR3 standards. DRAMsim2 were validated against Micron's DDR3 DRAM Verilog models [105] where no timing constraints violations were detected.

Ramulator [85] (2016), is the most recent open-source DRAM simulator. Because of their state-machine abstraction model, authors claim to speed-up simulation execution up to 3 times faster with respect to state-of-the-art main memory simulators. Moreover, Ramulator enables some of the high-end DRAM standards and technologies such as GDDR5 or HBM. Regarding validation, DRAM DDR3 timings in Ramulator were also validated against Micron's DDR3 DRAM Verilog models [105], where no constraints violations were detected.

**NVmain2.0**'s [114] main focus is to simulate non-volatile technologies such as STT-MRAM, ReRAM o PCRAM, as well as die-stacked DRAM caches. It is also validated against Micron's Verilog models [105]. The authors claim to outperform DRAMsim2 in speed simulation.

By the moment of the writing of this manuscript <sup>2</sup> researchers released **DRAM-Sim3** [92], a cycle-accurate DRAM simulator validated against DDR4 Verilog models. The simulator improvements from DRAMsim2 include bank-groups, self-refresh timings, new GDDR5 models, and incorporates performance and thermal co-simulation. Moreover, it includes Hybrid Memory Cube (HMC) logic simulation and High Bandwidth Memory (HBM) dual-command issue.

#### 2.4 Hardware Performance Counters

Hardware Performance Counters (HWPC) are a computer architecture mechanism that allows visibility of particular events within the micro-architecture. HWPC are generally accessible through a set of registers mapped into a specific memory space, or through mailbox interfaces. To access such interfaces, researchers had proposed drivers and libraries that simplify the HWPC abstraction for programming purposes.

In Linux, the proposal that has been widely adopted in the kernel for HWPC access is **perf\_events** [74]. The initial version to support them was merged into mainline kernel in version 2.6.31 [66], where the interface between user requests and the kernel is enabled through the sys\_perf\_event\_open system call<sup>3</sup>. On recent versions of the Linux kernel, different access policies enable HWPCs measurements with different granularity, such as: per process, per thread, per core or socket-wise. Moreover, for security reasons, there are further restrictions according to the user's credentials and access controls.

On top of sys\_perf\_event\_open, there are some libraries that enables user-land access to the perf subsystem. The Performance Application Programming Interface (PAPI) [132], is among the most used libraries that enables an easy access interface to HWPC on diverse CPUs and also, off-chip counters for external devices such as some GPUs. The Perfmon2 or libpfm4, in its latest release [143], supports Linux's perf\_events, and the abstraction extends portability to Windows and MacOS.

<sup>&</sup>lt;sup>2</sup>Therefore, not included in the results from our study but deserves to be mentioned in this document.

$<sup>^3</sup>$ In Linux 2.6.31 was originally named, perf\_counter\_open() but renamed to perf\_event\_open() in 2.6.32.

**EXEgesis** [57] is an ambitious project that extracts instruction-level micro-architectural micro-operation (micro-operation) latency solely using vendor's documentation. The researcher's objective is to provide compilers with micro-architectural information for code generation. At the moment of the writing of this thesis, EXEgesis supports only Intel's x86-64 (via an Intel Software Developers Manual [70] parser). EXEgesis also identifies micro-operation execution port scheduling, i.e., execution units where the micro-operations are executed.

Furthermore, HWPCs might be accessed through direct configuration of Model Specific Registers (MSRs). Remarkable initiatives are using this approach: Agner's Fog [50], provides source-code of a Linux kernel module for x86-64 machines that enables access to HWPC through a simple interface. LIKWID [134] is a framework that provides tools for application performance. One of the tools, likwid-perfctr, enables application developers to measure HWPCs. The measurements might be taken externally, through a command line wrapper utility or, through an Application Programmer Interface (API) for specific code sections within the application. HWPCs are read using the msr mechanism deployed within the Linux kernel. Intel Architecture Code Analyzer (IACA) [71]<sup>4</sup> is a tool that provides estimates about execution-units utilization for several families of Intel's micro-architectures. To use IACA, a binary needs to be instrumented at compile time. Once compiled, the binary is statically analyzed. A similar approach is used by llvm-mca [38], using the information available in LLVM's compilation phase to measure the processor's throughput and resource utilization.

# 2.5 CPU Micro-benchmarks

A well-known on-line resource for micro-architectural details is published by **Agner's Fog** [49]. He has historically collected a comprehensive list of latency, throughput, and execution-units utilization of several CPUs from different IHVs. The list is built upon a set of scripts that execute a set of pre-defined micro-benchmarks. The scripts and source code for his micro-benchmarks are available on his research website [50]. His code supports execution on Linux and Windows OSs with support for single and multiple threads. Administrative privileges are required to load and run Agner's micro-benchmarks.

In **uops.info** [1] the researchers provide a complete list [3] of instruction latency, throughput, and execution-units utilization for all families of Intel micro-architecture.

$<sup>^4</sup>$ In Q3-2019 IACA has been declared End-Of-Life (EOL) by Intel but still available for download.

Their proposal is based on the concept of blocking instruction, a construct that enables them to characterize the execution-unit scheduling accurately with respect of the state-of-the-art techniques. Although the interface to execute the micro-benchmark is released (nanoBench [2]), at the moment of writing this document, the source code for such construct it is not publicly available.

**likwid-bench** is a tool within the LIKWID framework [134], that allows an automatic generation of micro-benchmarks. The framework provides a series of generic micro-benchmark kernels which are parameterized by command line switches.

Microprobe [18] is a framework to automatically generate micro-benchmarks. Originally designed to estimate the power consumption of multi-threaded applications running on a multi-core system. Microprobe also allows micro-architectural parameter characterization such as the usage of functional units. The framework is composed of a set of modules that assist the automatic code generation through a comprehensible configuration script. One of the modules, the ISA definition module, is provisioned with details about the targeted micro-architecture. In the original publication [18], researchers used an IBM's POWER7 micro-architecture. Currently, the open-source release [68], supports RISC-V micro-architecture.

# 2.6 Memory Micro-benchmarks

To the best of our knowledge, the first tool that had helped the memory research is **STREAM** [102]. In STREAM's first version, sustained memory bandwidth is measured using impressively simple kernels written in standard C and Fortran. To achieve multiprocessing, STREAM uses OpenMP and MPI. On the one hand, these characteristics made STREAM platform-portable; but on the other hand, details and control over the memory accesses are left to the compiler and OpenMP's runtime.

LMBench [103] is constantly referred in the state-of-the-art. LMBench's main focus is to measure transfers between the processors and the members of the memory hierarchy, such as the primary storage or the main memory. As a consequence, it measures main memory latency as well as it performs cache capacity discovery.

**RAMspeed** [119] by Alasir Enterprises, provides 18 specialized kernels (INT, FLOAT, and SSE), that access data in different reading/writing patterns to measure memory performance. Another tool provided by an enterprise is the Intel Memory Latency Checker (imlc) [141]. The tool is distributed in binary-only form, making it difficult to operate outside the predefined command-line arguments. An essential

contribution of this tool is the ability to switch off the hardware prefetchers (privileged credentials are required).

**Pmbw** [20] collects old requirements from STREAM, LMBench, and imlc, exporting a multi-core, multi-architecture bandwidth-latency memory tool. Pmbw provides 21 hand-crafted assembly-code and compiler-ready kernels to achieve such goal.

In **PROFET** [116], the authors provide two different tools to characterize main memory latency and memory bandwidth. An interesting contribution in the proposal is about memory bandwidth measurements: the tool instruments kernels that deliver a ratio of read/write instructions deploying 25 kernels that achieve bandwidth utilization from 50% up to 100% with a granularity of 2%. A second contribution is cache pollution awareness: to avoid unnecessary misses on the cache hierarchy, write memory transactions make usage of non-temporal ISA instructions.

As an extension **uops.info** [1], in **nanoBench** [2] authors provide several Python scripts that explore, discover, and characterize the cache levels of the memory hierarchy. Since the objective for the main research targets CPU micro-architecture, main memory is not covered by nanoBench.

Lastly, a remarkable framework that identifies the complexity and the challenges to write a memory benchmark tool is found in **Hopscotch** [6]. Authors provide tools that characterize the elements on the memory hierarchy such as latency and bandwidth utilization. The tools are deployed with a configurable interface to use different memory access patterns that resemble real-world applications.

#### 2.7 Validation in the State Of The Art

The gem5 CPU simulator was originally validated against an Alpha machine. For newer versions, the validation of the simulator versus the real hardware has been delegated to the gem5 community. For instance, Burtko et al. [27], validate gem5 in dual-core configuration versus an ARM Cortex-A9 where the researchers reported differences in the benchmarks' execution time ranging between 1.39% and 17.94%. The benchmarks used in their work are SPLASH-2 [144] and ALPBench [88]. Anoter community validation effort between gem5 and real hardware is presented by Gutierrez et al. [62]. In said work, researchers have modified and extended gem5 to behave as a VExpress development board (an ARM processor with DDR2 as main memory) where they used the CPU ARM subsystem within the gem5's 03 Core Model and GEMS' SimpleDRAM for the main memory accesses. The workload chosen to evaluate performance is the SPEC CPU2006

benchmarks. Researchers claimed to achieve an average absolute error of 5% with this configuration.

Sniper was validated originally against an Intel Core 2 machine [29]. On a further effort, Sniper was validated against an Intel Xeon X5550 processor (Nehalem microarchitecture) using a set of the SPLASH-2 benchmarks [144]. The validation results show that Sniper's IPC error concerning the actual hardware is below 25%. Let's point out that Sniper uses a fixed memory latency for main memory accesses where a 65 ns value is used for validation in the original paper.

TaskSim was originally validated versus an IBM Cell processor. In MUSA (that uses TaskSim to simulate computation phases), authors validate their infrastructure against an Intel Xeon E5-2670 machine using the NAS Parallel Benchmarks [11], HYDRO [89], and SPECFEM3D [87]. In the study, the authors reported achieving relative errors below 10 %.

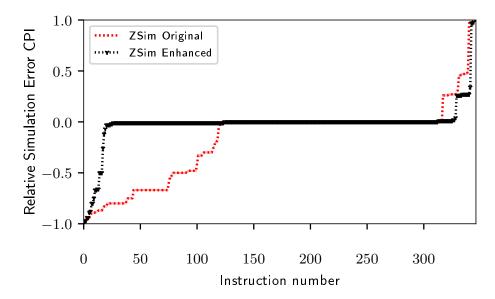

The ZSim simulator is validated against an Intel Xeon L5640 machine (Nehalem architecture) with the internal M/D/1 memory model using SPEC CPU2006 and PAR-SEC [19] benchmarks. The authors reported IPC errors of below 10% between the two systems. The ZSim authors clarified that using DRAMsim2 will restrict the simulation to 3 MIPS, landing outside their design goals. Therefore, the validation with DRAMsim2 is not performed in the original paper.

Work introduced by Akram and Sawalha [7] surveys state-of-the-art x86 CPU simulators. In the experimental section, they tested four simulators: gem5, Multi2sim [136], PTLSim [147] and Sniper. The chosen workloads used for the analysis are SPEC CPU2006 and MiBench [61]. In their configuration, they have not reported the usage of any external memory simulator. For their analysis, they used an Intel Core i7 processor (Haswell micro-architecture) as the targeted system to model. Their results presented a broad set of discrepancies among simulation executions.

DiagSim [81] proposes a method that detects changes in IPC's patterns. The method points out where the differences between the real system and a simulator drift away. The authors categorized micro-architectural features through a set of diagnostics bounded together through a dependency map. A diagnose is in fact, a micro-benchmark for the targeted ISA. By running each diagnose through several iterations with different input parameters, micro-benchmarks can identify fluctuations in the IPC behavior. The researchers admitted that identify the IPC might need manual interaction, and no multi-threading scenarios were considered.

2.8 Decision Process 19

| Name                                      | Full-system/<br>User-level | Trace-/Execution-driven | Multi-threaded/<br>Sequential | CPU<br>complexity   | Validated<br>for                   | External DRAM simulator |

|-------------------------------------------|----------------------------|-------------------------|-------------------------------|---------------------|------------------------------------|-------------------------|

| gem5 [21]                                 | Both                       | Both                    | Sequential                    | OoO                 | ARM (partial)                      | Yes                     |

| Sniper [30]                               | User-level                 | Both                    | Multi-threaded                | OoO                 | x86 (Nehalem)                      | No                      |

| ZSim [125]                                | User-level                 | Execution               | Multi-threaded                | OoO                 | x86 (Westmere)                     | Yes                     |

| TaskSim(MUSA) [120, 59]<br>MARSSx86 [112] | User-level<br>Full-system  | Trace<br>Execution      | Sequential<br>Sequential      | in-order/OoO<br>OoO | x86 (SandyBridge)<br>x86 (Nehalem) | Yes<br>No               |

Table 2.1 Overview of reviewed CPU simulators.

| Name            | I    | Trace-/Execution-<br>Sequential | Multi-threaded/<br>technologies | Memory                          |

|-----------------|------|---------------------------------|---------------------------------|---------------------------------|

| DRAMSim2 [122]  | Both | Sequential                      | No                              | DDR{2,3}                        |

| Ramulator [85]  | Both | Sequential                      | No                              | DDR{2,3,4}, GDDR5, HBM, WIO1/2  |

| NVMain2.0 [114] | Both | Sequential                      | No                              | DDR{2,3}, STT-RAM, PCRAM, ReRAM |

Table 2.2 Overview of reviewed DRAM simulators.

#### 2.8 Decision Process

Table 2.1 summarizes the CPU simulators we considered to use for this work. In full-system or hybrid mode simulation, gem5 lasts for a significant amount of time (several hours up to weeks) [126]. Sniper won't allow co-simulation with external main memory simulator. MUSA extends TaskSim capabilities to perform OoO for multiple ISAs and allows co-simulation with an external DRAM simulator, but it was still in development by the moment we performed the experiments about this thesis. The current implementation of the x86 ISA in MARSSx86 is outdated, and neither provides an interface to simulate DRAM concurrently. The only simulator that covers our requirements of reasonable execution time and DRAM co-simulation is ZSim.

For main memory simulators, Table 2.2 summarizes our considerations. Because all of them technically satisfy our requirements, the decision to chose one simulator among them was grounded on state-of-the-art reputation. Ramulator and NVmain2.0 are relatively new proposals, whereas DRAMsim2 has been extensively used within the computer architecture since 2011. Up to 2020, the number of paper citations for each one of them in the IEEE site is: 435 for DRAMsim2, 73 for Ramulator, and 54 for NVMain2.0. Moreover, programming interfaces to work with DRAMsim2 are broadly available i.e., ZSim already include support code for DRAMsim2.

**Decision:** For the CPU we decided to use the execution driven simulator ZSim, and DRAMsim2 for the main memory simulation.

# **Experimental Methodology**

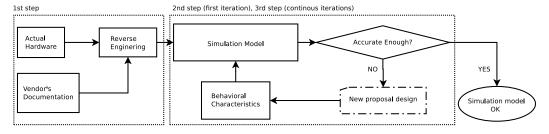

Figure 3.1 introduces the flow to design, upgrade, and tune system simulators. The first step when approaching computer architecture simulation is recognizing the similarities and differences between the real-world system and the state-of-the-art simulators. In this work, we decided to use an x86 CPU simulator that was designed to behave as a previous generation micro-architecture (Nehalem) from our targeted machine (Sandy Bridge). Therefore, we first identified the differences between the system and the CPU simulator using the vendor's available documentation: the Intel's Software Developer Manual [70] and the Intel's Optimization Guide [69]. Furthermore, we decided to include current reverse engineering efforts published in the state-of-the-art [101]. For main memory, the chosen DRAM simulator is designed to support the DDR2 and DDR3 standards; as our target model uses DDR3 memory devices and is validated versus Verilog models, we assume the memory model is accurate.

The second step consisted of matching and discovering those characteristics beyond vendor's documentation. To achieve this goal, we used the concept of microbenchmarking: execution of synthetic programs with an iterative loop comprised only of a single instruction. During micro-benchmark execution, we observed the

Figure 3.1 Iterative process of integrating and validating new features to a system simulator (simulation model).

micro-architectural resource activity using Hardware Performance Counters (HWPC) in the real machine. Because only one instruction is executed per micro-benchmark, fewer resources are utilized by the underlying micro-architecture, allowing us to discern resource utilization out of the scope of the execution of the micro-benchmark. Moreover, the micro-benchmark kernel is specially crafted to avoid micro-architectural optimization techniques designed to boost single-instruction performance.

To extract information from real machine execution, we used HWPC: special registers designed to provide information about the micro-architecture. If the corresponding HWPCs are not present in the simulator, we implemented them according to vendor's documentation. Implementing a non-existing HWPC in the simulator is not a straightforward task; system simulators are coded in high level languages, where the code logic attempts to mimic the micro-architectural details but it is not the same as the micro-architecture itself. For example, speeding the simulation time became a software-specific feature that imposes serious restrictions when attempting to implement and extract the corresponding micro-architectural details. Finally, the last stage on the second step consists of comparing both systems with their respective HWPC measurements. If discrepancies arose in the simulator, we updated the simulator's logic with values that correspond to those extracted from our micro-benchmark execution in the real machine.

If simulator's accuracy is not sufficient, a third step (optional) on the validation flow is to propose a novel design integrating it back to the simulation infrastructure so that a new comparison and assessment could be made. It is a common practice from IHVs to hide documentation of important architectural features so that they can keep a commercial advantage over competitors. Also, when implementing real-world models, researchers deliberately take some features out, for example, to speed the simulation process. Both conditions leave space for design proposals to explore new alternatives to achieve efficient computing, but also to accurately match existing designs.

#### 3.1 Hardware Platform

The targeted computing system we aimed to simulate is built upon a dual-socket platform; each socket embodies an Intel Xeon E5-2670 Sandy Bridge EP processor operating at 3.0 GHz [72]. By the moment we began this research Sandy Bridge was a micro-architecture still used at large by smaller Tier-0 systems [40]. Specifically, MareNostrum 3 supercomputer was based on over 3,000 nodes with 2x Sandy Bridge EP processors.

3.2 Simulation Model

In MareNostrum 3 systems, the main memory is populated by 4x 4 GiB DIMMs devices connected to the processor using four DDR3-1600 channels [124]. Each processor comprises eight cores; the hyper-threading feature has been disabled like in most HPC systems [31, 40]. The running OS is a SUSE Linux distribution running on top of a 3.0 Linux kernel [93].

For the simulation infrastructure, we chose to work with the integration of ZSim and DRAMsim2 system simulators. ZSim [125] is a user-level, execution-driven CPU simulator originally developed to behave as an Intel Westmere micro-architecture. DRAMsim2 [122] is a cycle-accurate model of a DRAM memory controller, the DIMMs passive devices, and buses by which they communicate. It has been validated against the DRAM manufacturer's Verilog models [105].

#### 3.2 Simulation Model

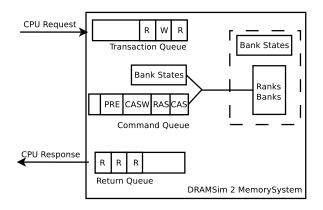

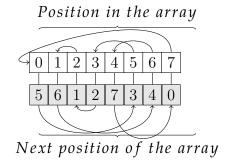

The simulation model of DRAMsim2 is depicted in Figure 3.2 In a simplistic view, the model consist in three queues: 1. the Transaction Queue, 2. the Command Queue, 3. and the Response Queue. When CPU memory transactions arrive, they are submitted to the Transaction Queue. An internal algorithm translates the incoming requests into DRAM commands which fill the Command Queue. To prevent timing violations and data hazards among transactions, the DRAM commands are scheduled according to the Bank State status issuing the corresponding timing simulation in an OoO manner. Once the transaction's simulation is finished, the Response Queue is filled with the simulated transaction and the Memory Model updates the Bank States table while keeping record of latency achieved during transactions. When an external simulator is hooked to DRAMsim2 as the transaction originator, that latency is reported back to the external simulator as the memory access latency; when DRAMsim2 is used in traces mode, the latency is logged accordingly.

Since DRAM is an industry standard for all memory IHVs, the parameters to configure the main memory simulator are mainly the accurate timings for the passive devices. We configured the simulator's technical characteristics found in the vendor's documentation for the DIMM packages [124]. Table 3.1 summarizes the timing parameters for our DDR3-1600 targeted model. Physical parameters such as temperature, might affect the DRAM simulation; on DRAMsim2 they are treated as an external simulation, not affecting the access latency to the passive device. Despite the fact that updating technical characteristics should be enough for DRAMsim2 to get correct timings (latency) between the memory controller and the passive devices, we still need

3.2 Simulation Model

Figure 3.2 DRAMSim2's Memory controller model.

| Parameter | Description                                      | Value |

|-----------|--------------------------------------------------|-------|

| tBURST    | Burst Length                                     | 4     |

| tCAS/tCL  | Column Access Strobe latency                     | 11    |

| tRTP      | Read To Pre-charge delay                         | 6     |

| tCCD      | Column to Column Delay                           | 4     |

| tWTR      | Write To Read delay                              | 6     |

| tRTRS     | Rank to Rank Switching time                      | 1     |

| tCWD      | Column Write Delay                               | 10    |

| tWR       | Write Recovery time                              | 12    |

| tCKE      | Next power up for an idle device                 | 4     |

| tCMD      | Command transport duration                       | 1     |

| tXP       | Exit power down with DLL on to any valid command | 5     |

| tRCD      | Row to Column Delay                              | 11    |

| tRP       | Row Pre-charge                                   | 11    |

| tRRD      | Row activation to Row activation Delay           | 5     |

| tRFC      | Refresh Cycle time                               | 208   |

Table 3.1 DRAM DDR3-1600 parameters used in our simulated model.

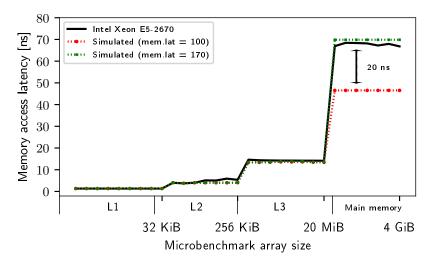

to characterize the maximum access time (worst-case scenario) from the CPU to retire a memory instruction. Since this objective is part of the integration of the CPU and main memory simulators, we designed a set of micro-benchmarks for this purpose.

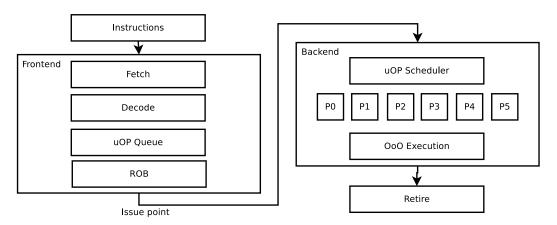

For the CPU model, Figure 3.3 depicts a diagram of the Sandy Bridge micro-architecture. The diagram is divided in two sections; the *frontend* on the left side, and the *backend* on the right side. On Intel's microprocessors, the *frontend* is the portion of the micro-architecture that takes the byte stream from the Instruction cache, recognizes and tags every instruction to later break them into smaller portions of execution called micro-operations micro-operations. The smaller operations are organized into a queue which serves the Reorder Buffer (ROB) for OoO execution. When possible, the ROB issues up to 4- micro-operations to the micro-operation-scheduler. The micro-operation

3.2 Simulation Model

Figure 3.3 Simplified diagram of an Intel's Sandy Bridge micro-architecture.

scheduler along with the execution units (also called *ports of execution*) make up the backend portion of the micro-architecture. The instruction retirement takes place when load and store transactions are cleared and data could be written back to the micro-architectural registers.

The chosen simulator was developed with the intent to behave as an x86 Westmere system. Westmere (2010) is a micro-architecture upgrade of the manufacturing process of the Nehalem micro-architecture (2008) [70]. Sandy Bridge (2011) introduces micro-architectural changes over Westmere, among the most noticeable are:

- 1. The four branch predictors in Nehalem are improved, non-fully documented but mentioned that number of bits has an extended range.

- 2. A new micro-operation cache holding up to 1536 micro-operations.

- 3. The L1 instruction cache is improved in associativity from 4-way to 8-way.

- 4. The L1 TLB adds several entries dedicated to large pages, from 7 to 16.

- 5. The capacity of the ROB is increased from 128 to 160 entries.

- 6. The number of register files dedicated to renaming is doubled, using 160 entries for integer operations and 144 entries for vector instructions.

- 7. The execution unit scheduler improved its capacity to hold from 36 to 54 microoperations entries in the reservation station.

- 8. From the six execution units available, three are kept for arithmetic operations supporting the new vector extensions and three ports are specialized for memory transactions. On Westmere, two ports were used for store operations and one

| micro-architecture feature      | Westmere           | Sandy Bridge                                   | ZSim                             |

|---------------------------------|--------------------|------------------------------------------------|----------------------------------|

| L1 iTLB entries                 | 142                | 144                                            | N/A                              |

| micro-operation cache entries   | N/A                | 1536 8-way                                     | N/A                              |

| ROB entries                     | 128                | 160                                            | $128 \rightarrow 160$            |

| ROB register files              | 128                | 144  int + 160  vector                         | $128 \rightarrow 144$            |

| micro-operation scheduler slots | 36                 | 54                                             | $36 \rightarrow 54$              |

| execution units for loads       | 2                  | 2                                              | 2                                |

| load buffer entries             | 32                 | 64                                             | $32 \rightarrow 64$              |

| execution units for stores      | 2                  | 1                                              | $2 \rightarrow 1$                |

| store buffer entries            | 32                 | 36                                             | $32 \rightarrow 36$              |

| L1i size associativity          | 32 KiB 4-way       | 32 KiB 8-way                                   | 32 KiB* 4-way                    |

| L1d size associativity          | 32 KiB 4-way       | $32 \mathrm{KiB}$ 8-way                        | $32 \mathrm{KiB}^* 4\text{-way}$ |

| L2 size associativity           | 256 KiB 8-way      | $256\mathrm{KiB}$ 8-way                        | 256 KiB* 8-way                   |

| LLC size associativity          | 4 MiB-30 MiB 8-way | $3 \mathrm{MiB}\text{-}20 \mathrm{MiB}$ 20-way | $20 \mathrm{MiB^*}\ 20$ -way     |

**Table 3.2** Comparison of micro-architectural features. On the ZSim column, the '\*' stands for configurable entries, and the ' $\rightarrow$ ' for the parameters to update.

for load transactions. On Sandy Bridge, two ports are dedicated to address generation and load requests leaving the execution unit with only one port for store operations.

- 9. The number of entries of the load and store buffers is increased from 32 to 64 entries for the load buffer, and from 32 to 36 entries for the store buffer.

- 10. On the most exclusive product line of processors for HPC in Westmere, the LLC size is 30 MiB. In Sandy Bridge, the largest LLC capacity is limited up to 20 MiB with a 20-way policy. Moreover, the LLC is connected through all cores by a ring bus. Maurice et al. [101] reversed engineered the hashing algorithm used on Sandy Bridge to reduce congestion and equitably distribute traffic on the LLC.

Table 3.2 introduces a comparison over the two micro-architectures and the CPU simulator. Each row in the table describes a micro-architectural feature. Every column belongs to each one of the compared systems: the ZSim CPU simulator, Westmere (the micro-architecture that ZSim aims to model), and Sandy Bridge (the micro-architecture of the targeted system, also deployed on the MareNostrum 3 computing nodes). On the ZSim's column we also integrate the static changes derived from this upgrading process, meaning the corresponding numbers that the simulators should update to behave as the new targeted system.

# Micro-benchmark Design

Our micro-benchmark proposal allows to extract the number of micro-operations and the execution unit utilization. Both parameters are a vital source for accuracy in x86 CPU simulation since determine the *instruction latency*. Moreover, the micro-benchmark proposal allows us to discover main memory access latency.

Our simulation model targets an Intel's Sandy Bridge micro-architecture. Although Intel's x86 ISA is known to be a Complex Instruction Set Computer (CISC), the processor's frontend implements a decoder which breaks every instruction into simpler operations that resembles a Reduced Instruction Set Computer (RISC) architecture. Each one of these operations are known as micro-operation (micro-operation). Some instructions are broken into a single micro-operation, while others into more. Originated at the frontend, the micro-operations are delivered to the backend so that the computing units execute them when possible. These units are generally known as execution units or ports of execution. On modern architectures, some execution units are prepared to compute not only generic processing work but specialized operations such as memory related operations or intense arithmetic computations. To properly assign work to the execution units, a scheduler arbitrates the execution of micro-operations. According to scheduling policies, the execution units might present a non-balanced distribution when executing the micro-operations. Moreover, there are some instructions which need a sequencer intervention leading to a dynamic execution of micro-operations based on instruction's parameters.

In this section, we elaborate the assumptions and design considerations in the proposal of the micro-benchmark for CPU micro-architectural parameter extraction and main memory access latency.

| Name                                                    | Description                                                                              | Event                                       | Umask          |

|---------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------------|----------------|

| CPU_CLK_UNHALTED INSTRUCTIONS RETIRED                   | Cycles where CPU is not halted<br>Instructions until the last micro-operation is retired | 0x3C<br>0xC0                                | 0x01<br>0x00   |

| UOPS_DISPATCHED_PORT.PORT_0                             | and the last mets operation is isomed                                                    | 0xA1                                        | 0x01           |

| UOPS_DISPATCHED_PORT.PORT_1 UOPS_DISPATCHED_PORT.PORT_2 | Number of cycles during one uop is dispatched to the execution unit                      | $\begin{array}{c} 0xA1 \\ 0xA1 \end{array}$ | 0x02<br>0x0C   |

| UOPS_DISPATCHED_PORT.PORT_3 UOPS_DISPATCHED_PORT.PORT_4 | an approximation of the execution unit $\{0,1,2,3,4,5\}$                                 | 0xA1<br>0xA1                                | $0x30 \\ 0x40$ |

| UOPS_DISPATCHED_PORT.PORT_5                             |                                                                                          | 0xA1 $0xA1$                                 | 0x40<br>0x80   |

**Table 4.1** Hardware Performance Monitoring Counters used to characterize instruction latency and execution unit (port) utilization.

## 4.1 Micro-benchmarks Proposal

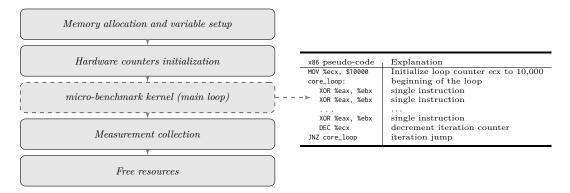

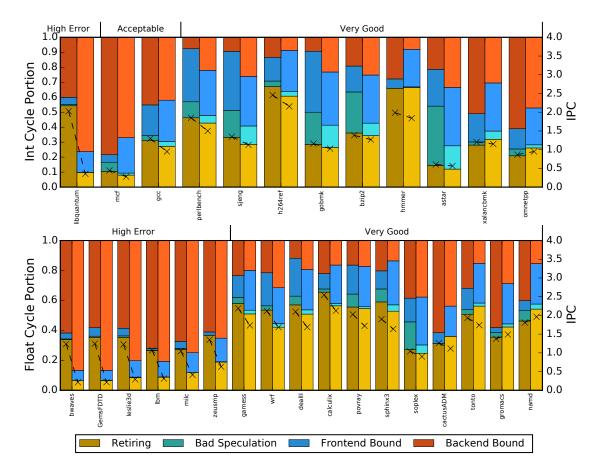

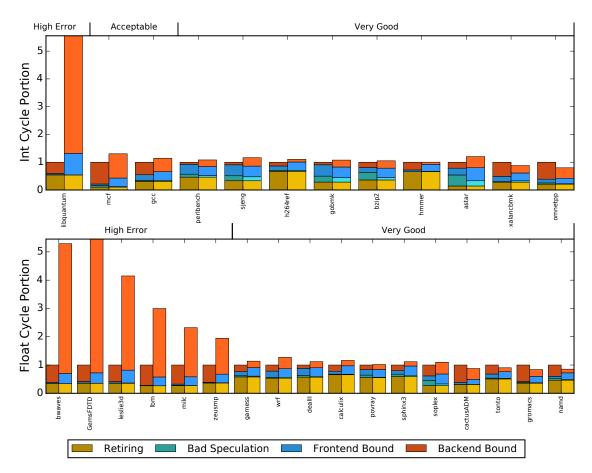

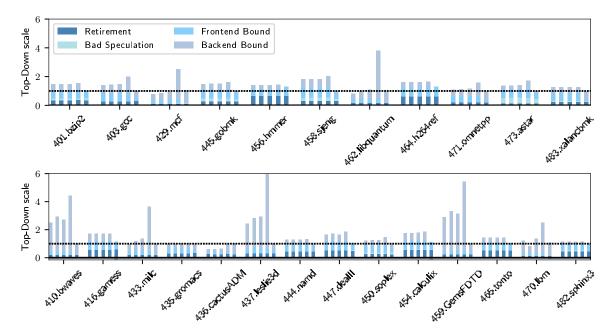

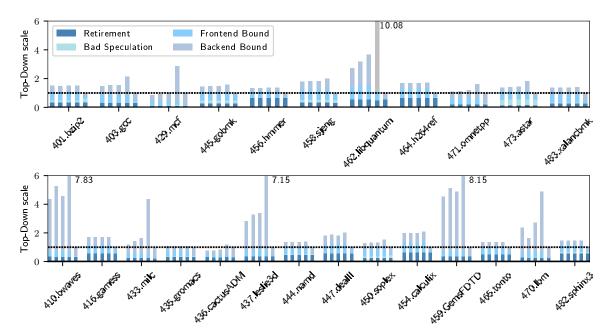

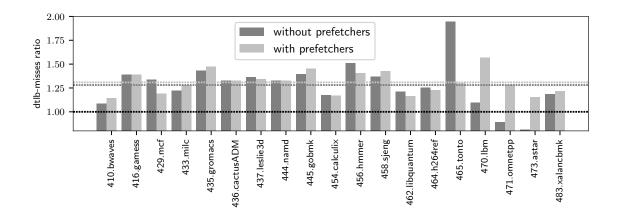

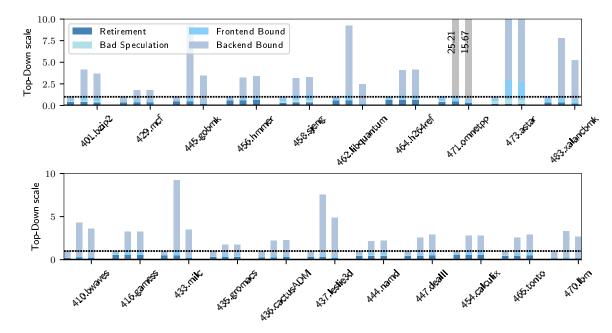

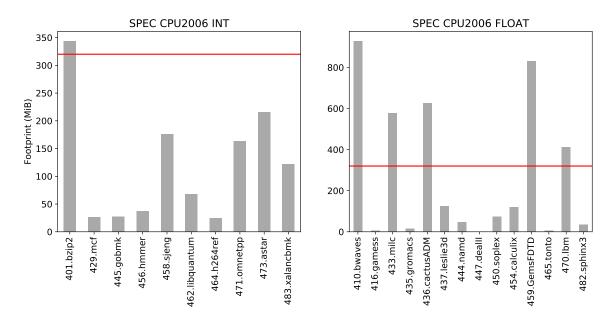

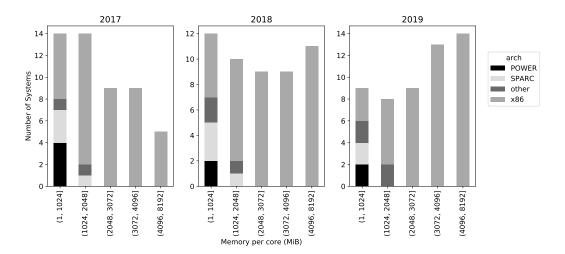

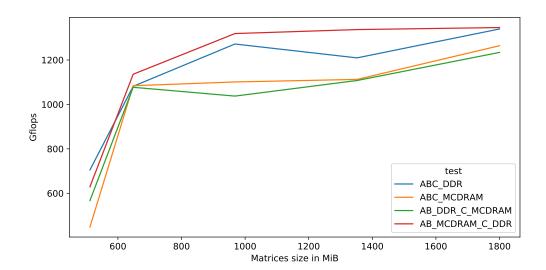

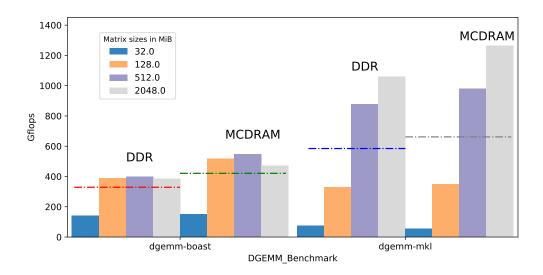

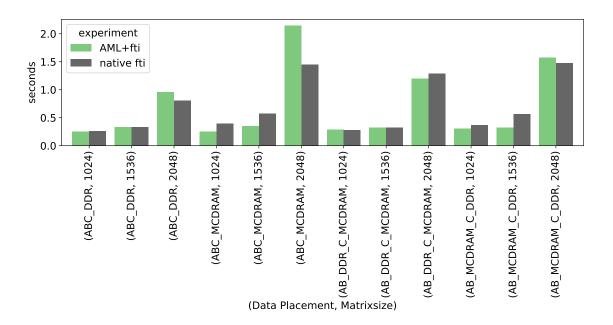

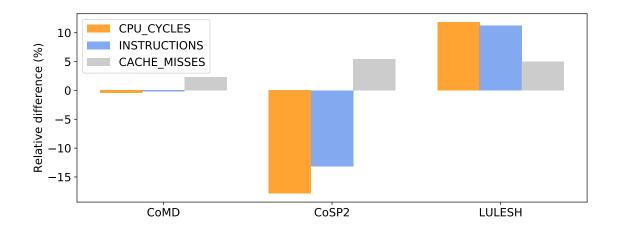

Parameters extraction is a task that has been around for some time in the computer architecture community (Section 2.5). Our micro-benchmark proposal allows micro-architectural characterization considering the micro-architecture limitations of our targeted simulator. The micro-benchmarks are designed to run as a user-level application on top of a Linux kernel with non-administrative privileges. The design of the micro-benchmarks consists of two sections: the OS interactions and the micro-benchmark main loop. Figure 4.2 portrays the general characteristics of the micro-benchmark.