# Parallel architectures and runtime systems co-design for task-based programming models

## **Emilio Castillo Villar**

ADVERTIMENT La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del r e p o s i t o r i i n s t i t u c i o n a l UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) i el repositori cooperatiu TDX (<a href="http://www.tdx.cat/">http://www.tdx.cat/</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei UPCommons o TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a UPCommons (\*framing\*). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

ADVERTENCIA La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del repositorio institucional UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) y el repositorio cooperativo TDR (<a href="http://www.tdx.cat/?locale-attribute=es">http://www.tdx.cat/?locale-attribute=es</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio UPCommons No se autoriza la presentación de su contenido en una ventana o marco ajeno a UPCommons (<a href="https://reming/framing/">framing/</a>). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING** On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the i n s t i t u t i o n a l r e p o s i t o r y UPCommons (<a href="http://upcommons.upc.edu/tesis">http://upcommons.upc.edu/tesis</a>) and the cooperative repository TDX (<a href="http://www.tdx.cat/?locale-attribute=en">http://www.tdx.cat/?locale-attribute=en</a>) has been authorized by the titular of the intellectual property rights **only for private uses** placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading nor availability from a site foreign to the UPCommons service. Introducing its content in a window or frame foreign to the UPCommons service is not authorized (framing). These rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

# PARALLEL ARCHITECTURES AND RUNTIME SYSTEMS CO-DESIGN FOR TASK-BASED PROGRAMMING MODELS

# **Emilio Castillo Villar**

Barcelona, 2018

A thesis submitted in fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Department of Computer Architecture Technical University of Catalonia

# PARALLEL ARCHITECTURES AND RUNTIME SYSTEMS CO-DESIGN FOR TASK-BASED PROGRAMMING MODELS

## **Emilio Castillo Villar**

Barcelona, 2018

**ADVISORS: Miquel Moretó Planas**

> Universitat Politècnica de Catalunya Barcelona Supercomputing Center Julio Ramón Beivide Palacio

Universidad de Cantabria

**COLLABORATORS: Marc Casas Guix**

> Barcelona Supercomputing Center Lluc Álvarez Martí

> Barcelona Supercomputing Center

**Abhinav Bhatele**

Lawrence Livermore National Laboratory

Nikhil Jain

Lawrence Livermore National Laboratory

A thesis submitted in fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY / DOCTOR PER LA UPC

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

| Acta de calificación de tes                                                | sis doctoral             |                                 | Curso académico:                          |

|----------------------------------------------------------------------------|--------------------------|---------------------------------|-------------------------------------------|

| Nombre y apellidos                                                         |                          |                                 |                                           |

| Programa de doctorado                                                      |                          |                                 |                                           |

| Unidad estructural responsable del programa                                |                          |                                 |                                           |

| Resolución del Tribunal                                                    |                          |                                 |                                           |

| Reunido el Tribunal designado a tal e<br>titulada                          |                          |                                 | expone el tema de su tesis doctoral       |

| Acabada la lectura y después de ditribunal, éste otorga la calificación:   | dar respuesta a          | las cuestiones for              | muladas por los miembros titulares del    |

| □ NO APTO □ A                                                              | APROBADO                 | ☐ NOTABLE                       | SOBRESALIENTE                             |

| (Nombre, apellidos y firma)                                                |                          | (Nombre, apellidos y fil        | ma)                                       |

| Presidente/a                                                               |                          | Secretario/a                    |                                           |

| (Nombre, apellidos y firma)                                                | (Nombre, apellidos y fir | rma)                            | (Nombre, apellidos y firma)               |

| Vocal                                                                      | Vocal                    |                                 | Vocal                                     |

|                                                                            | 1                        |                                 |                                           |

|                                                                            | _ de                     | de                              |                                           |

| El resultado del escrutinio de los voto Permanente de la Escuela de Doctor | -                        | ENCIÓ CUM LAUD                  |                                           |

| (Nombre, apellidos y firma)                                                |                          | (Nombre, apellidos y fil        | ma)                                       |

| Presidente/a de la Comisión Permanente de<br>Doctorado                     | e la Escuela de          | Secretario/a de la<br>Doctorado | Comisión Permanente de la Escuela de      |

| Barcelona, de                                                              | de                       |                                 |                                           |

| Mención Internacional en                                                   | el título de d           | doctor o docto                  | ora                                       |

| • Como socrotario/a dal tribunal b                                         | ago constar quo          | narto do la tosis o             | doctoral, como mínimo el resumen y las    |

|                                                                            | _                        |                                 | abituales para la comunicación científica |

|                                                                            |                          | _                               | n España. Esta norma no se aplica si la   |

| estancia, los informes y los exper                                         | rtos provienen de        | un país de habla h              | ispana.                                   |

| (Nombre, apellidos y firma)                                                |                          |                                 |                                           |

|                                                                            |                          |                                 |                                           |

| Secretario/a del Tribunal                                                  |                          |                                 |                                           |

# **Abstract**

The increasing parallelism levels in modern computing systems has extolled the need for a holistic vision when designing multiprocessor architectures taking in account the needs of the programming models and applications. Nowadays, system design consists of several layers on top of each other from the architecture up to the application software. Although this design allows to do a separation of concerns where it is possible to independently change layers due to a well-known interface between them, it is hampering future systems design as the Law of Moore reaches to an end. Current performance improvements on computer architecture are driven by the shrinkage of the transistor channel width, allowing faster and more power efficient chips to be made. However, technology is reaching physical limitations where the transistor size will not be able to be reduced furthermore and requires a change of paradigm in systems design.

This thesis proposes to break this layered design, and advocates for a system where the architecture and the programming model runtime system are able to exchange information towards a common goal, improve performance and reduce power consumption. By making the architecture aware of runtime information such as a Task Dependence Graph (TDG) in the case of Asynchronous Task-based Programming (ATaP) models, it is possible to improve power consumption by exploiting the critical path of the graph. Moreover, the architecture can provide hardware support to create such a graph in order to reduce the runtime overheads and making possible the execution of fine-grained tasks to increase the available parallelism. Finally, the current status of inter-node communication primitives can be exposed to the runtime system in order to perform a more efficient communication scheduling, and also creates new opportunities of computation and communication overlap that were not possible before. An evaluation of the proposals introduced in this thesis is provided and a methodology to simulate and characterize the application behavior is also presented.

# **Abstract**

El aumento del paralelismo proporcionado por los sistemas de cómputo modernos ha provocado la necesidad de una visión holística en el diseño de arquitecturas multiprocesador que tome en cuenta las necesidades de los modelos de programación y las aplicaciones. Hoy en día el diseño de los computadores consiste en diferentes capas de abstracción con una interfaz bien definida entre ellas. Las limitaciones de esta aproximación junto con el fin de la ley de Moore limitan el potencial de los futuros computadores. La mayoria de mejoras actuales en el diseño de los computadores provienen fundamentalmente de la reducción del tamaño del canal del transistor, lo cual permite chips mas rápidos y con un consumo eficiente sin apenas cambios fundamentales en el diseño de la arquitectura. Sin embargo, la tecnología actual esta alcanzando limitaciones físicas donde no será posible reducir el tamaño de los transistores motivando así un cambio de paradigma en la construcción de los computadores.

Esta tesis propone romper este diseño en capas y abogar por un sistema donde la arquitectura y el sistema de tiempo de ejecución del modelo de programación sean capaces de intercambiar información para alcanzar una meta común: La mejora del rendimiento y la reducción del consumo energético. Haciendo que la arquitectura sea consciente de la información disponible en el modelo de programacion, como puede ser el grafo de dependencias entre tareas en los modelos de programación *dataflow*, es posible reducir el consumo energético explotando el camíno crítico del grafo. Además la arquitectura puede proveer de soporte hardware para crear este grafo con el objetivo de reducir el *overhead* de construir este grado cuando la granularidad de las tareas es demasiado fina. Finalmente, el estado de las comunicaciones entre nodos puede ser expuesto al sistema de tiempo de ejecución para realizar una mejor planificación de las comunicaciones y creando nuevas oportunidades de solapamiento entre cómputo y comunicación que no eran posibles anteriormente. Esta tesis aporta una evaluación de todas estas propuestas así como una metodología para simular y caracterizar el comportamiento de las aplicaciones.

# Acknowledgments

Those who know me know as well the last couple years had been a long and hard path towards this goal. I had the support of many people whom I like to briefly thank in the following lines:

The list of people who have made this possible in one way or another is extremely big, their friendship and unconditional support under all the circumstances that have arose in the past years is something that I will never be grateful enough.

My brother Javier Castillo, thank you for showing me research and always keep me in the right path.

My Ph.D advisor and co-advisors, Miquel Moretó, Ramón Beivide and Marc Casas, thank you for your understanding and support in difficult situations that went against your interests.

Mateo Valero, thank you for your friendship, thank you for making all of this possible.

Cristobal Camarero, most of what I know and I am able to do is thanks to you.

Kotaro Nakayama and Yutaka Matsuo from the University of Tokyo. Your understanding, support and concern has been always beyond words.

José Luis Bosque, thanks for helping me both professionally and personally all these years.

All the RoMoL team, especially Lluc Álvarez, César Allande and Adrian Barredo.

Martin Schulz from the Technical University of Munich, Abhinav Bhatele and Nikhil Jain from the Lawrence Livermore National Laboratory. Thank you for hosting me last year and work hard side-by-side to make this thesis come to a successful end.

Satoshi Matsuoka from Tokyo Tech. Thank you always for your kindness and advice.

My parents supported me throughout all these years and their efforts guaranteed me an education and a future.

Old colleagues at the University of Cantabria, Pablo Fuentes, Iván Pérez, Fernando Vallejo, Enrique Vallejo, Carmen Martínez, Rafael Menéndez and Esteban Stafford.

All my friends in Spain, USA, and Japan. Too many to list all of them here but I will always feel grateful to all of you.

### **Financial Support**

This work has been supported by the Spanish Government (Severo Ochoa grants SEV2015-0493, SEV-2011-00067), by the Spanish Ministry of Science and Innovation (contracts TIN2015-65316-P, TIN2012-34557, TIN2013-46957-C2-2-P, TIN2016-76635-C2-2-R and TIN2016-81840-REDT), by Spanish Ministry of 41 Education, Culture and Sports under grant FPU2012/2254, by Generalitat de Catalunya (contracts 2014-SGR-1051 and 2014-SGR-1272), by the RoMoL ERC Advanced Grant (GA 321253) and the European HiPEAC Network of Excellence. The Mont-Blanc project receives funding from the EU's Seventh Framework Programme (FP7/2007-2013) under grant agreement No. 610402 and from the EU's H2020 Framework Programme (H2020/2014-2020) under grant agreement No. 671697 and No. 671610. This work was partially performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344.

# **Contents**

| Al | bstrac | et .    |                                                          | j  |

|----|--------|---------|----------------------------------------------------------|----|

| A  | cknov  | vledgmo | ents                                                     | v  |

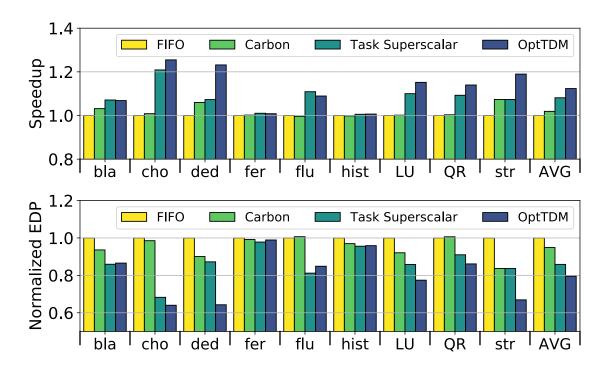

| In | dex    |         |                                                          | xi |

| 1  | Intr   | oductio | on .                                                     | 1  |

|    | 1.1    | Thesis  | s Objectives and Contributions                           | 3  |

|    |        | 1.1.1   | Efficient Power Management based on Task Criticality     | 4  |

|    |        | 1.1.2   | Flexible Hardware Support for Task Dependence Management | 4  |

|    |        | 1.1.3   | Towards a Seamless ATaP-MPI Interoperability             | 5  |

|    | 1.2    | Thesis  | S Structure                                              | 6  |

| 2  | Bac    | kgroun  | d and Related Work                                       | 9  |

|    | 2.1    | Paralle | el Multiprocessor Systems                                | 9  |

|    |        | 2.1.1   | Shared Memory Multiprocessor Systems                     | 10 |

|    |        | 2.1.2   | Distributed Multiprocessor Systems                       | 10 |

|    |        | 2.1.3   | Asymmetric Multiprocessor Systems                        | 12 |

|    | 2.2    | Paralle | el Programming Models                                    | 13 |

|    |        | 2.2.1   | Threading and Fork-Join Programming Models               | 13 |

|    |        | 2.2.2   | Asynchronous Task-based Programming Models               | 15 |

|    |        | 2.2.3   | Programming Models for Distributed Environments          | 17 |

|    |        | 2.2.4   | Communication in Hybrid MPI+ATaP Models                  | 18 |

|    | 2.3    | The O   | mpSs Programming Model                                   | 20 |

|    |        | 2.3.1   | Task Dependence Graph                                    | 21 |

|    |        | 2.3.2   | Task Scheduling                                          | 23 |

|    |        | 2.3.3   | Task Life Cycle                                          | 24 |

|   | 2.4                      | Archit   | ecture and  | ATaP Runtime Co-Design                            | 26 |

|---|--------------------------|----------|-------------|---------------------------------------------------|----|

|   |                          | 2.4.1    | Runtime     | System Hardware Support                           | 26 |

|   |                          | 2.4.2    | Exploitin   | ng Runtime System Information In the Architecture | 28 |

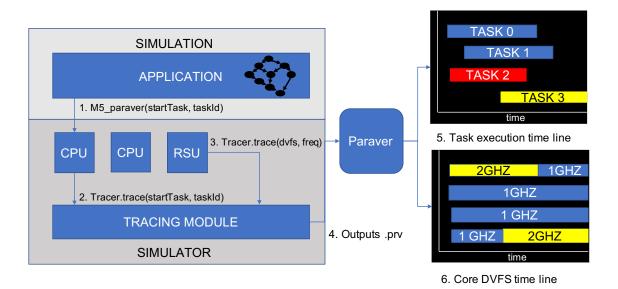

| 3 | Exp                      | eriment  | tal Frame   | work and Toolset                                  | 31 |

|   | 3.1                      | Simula   | ation Infra | structure                                         | 31 |

|   | 3.2                      | HPC C    | Cluster     |                                                   | 32 |

|   |                          | 3.2.1    | Workloa     | d Management                                      | 34 |

|   | 3.3                      | Softare  | e Stack .   |                                                   | 34 |

|   |                          | 3.3.1    | Operatin    | g System and Build Toolchain                      | 34 |

|   |                          | 3.3.2    | ATaP Mo     | odel Runtime System                               | 35 |

|   |                          | 3.3.3    | MPI & P     | SM2                                               | 35 |

|   | 3.4                      | Perfor   | mance An    | alysis Tools                                      | 36 |

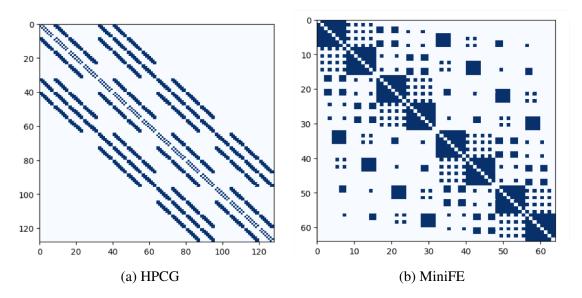

|   | 3.5                      | Bench    | marks       |                                                   | 38 |

|   |                          | 3.5.1    | Shared N    | Temory Workloads                                  | 38 |

|   |                          | 3.5.2    | Distribut   | ed workloads                                      | 40 |

|   |                          |          | 3.5.2.1     | Point-to-point Benchmarks                         | 40 |

|   |                          |          | 3.5.2.2     | Benchmarks with Collective Communications         | 42 |

| 4 | Imp                      | roving l | Power Co    | nsumption Through Task Criticality                | 45 |

|   | 4.1                      | Limita   | tions of sc | heduling algorithms                               | 46 |

|   | 4.2                      | Critica  | ality-Aware | e Task Acceleration                               |    |

|   |                          | Using    | DVFS Red    | configurations                                    | 47 |

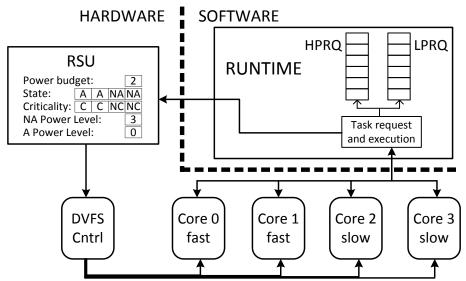

|   |                          | 4.2.1    | Criticalit  | y-Aware Runtime-Driven DVFS Reconfiguration       | 47 |

|   |                          | 4.2.2    | Architec    | tural Support for DVFS Reconfiguration            | 49 |

|   |                          |          | 4.2.2.1     | RSU Management                                    | 49 |

|   |                          |          | 4.2.2.2     | RSU Operation                                     | 50 |

|   |                          |          | 4.2.2.3     | RSU Virtualization                                | 51 |

|   |                          |          | 4.2.2.4     | Area and Power Overhead                           | 51 |

|   |                          |          | 4.2.2.5     | Integration of RSU and TurboMode                  | 51 |

|   | 4.3                      | Evalua   | ation       |                                                   | 52 |

|   |                          | 4.3.1    | Criticalit  | y-Aware Task Scheduling                           | 52 |

|   |                          | 4.3.2    | Criticalit  | y-Aware Task Acceleration                         | 53 |

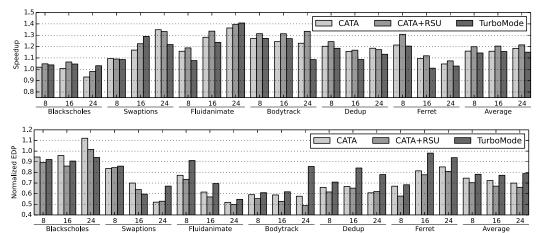

|   |                          | 4.3.3    | Architec    | turally Supported CATA                            | 54 |

|   | son with Other Proposals | 55       |             |                                                   |    |

## **CONTENTS**

|   | 4.4  | Remar    | rks                                                | 57 |  |

|---|------|----------|----------------------------------------------------|----|--|

| 5 | Imp  | roving l | Performance Through Fine-Grained Tasking           | 59 |  |

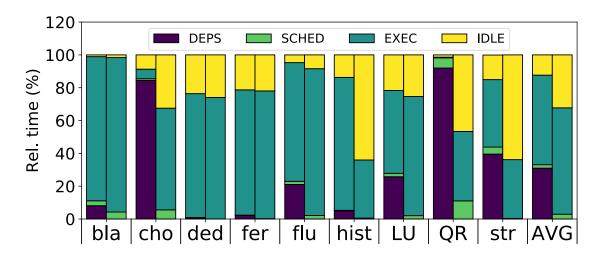

|   | 5.1  | Charac   | cterizing Runtime System Activity                  | 60 |  |

|   | 5.2  | TDM I    | Design                                             | 62 |  |

|   |      | 5.2.1    | Runtime System - Architecture Interface            | 63 |  |

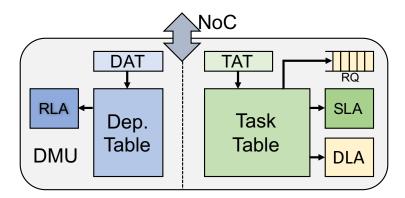

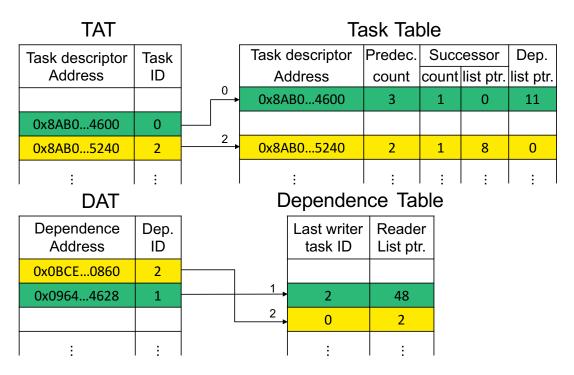

|   |      | 5.2.2    | DMU Hardware Design                                | 64 |  |

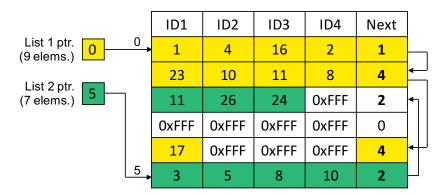

|   |      |          | 5.2.2.1 Task and Dependence Identifier Renaming    | 65 |  |

|   |      |          | 5.2.2.2 Task and Dependence Tracking               | 65 |  |

|   |      | 5.2.3    | Operational Model                                  | 66 |  |

|   |      |          | 5.2.3.1 Task Creation                              | 66 |  |

|   |      |          | 5.2.3.2 Task Finalization                          | 68 |  |

|   |      |          | 5.2.3.3 Implementing Task Schedulers in Software   | 68 |  |

|   |      | 5.2.4    | Additional Considerations                          | 69 |  |

|   | 5.3  | Design   | n Space Exploration                                | 70 |  |

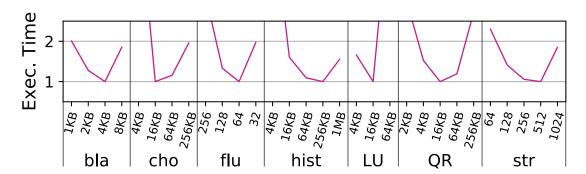

|   |      | 5.3.1    | Benchmarks and Task Granularity                    | 70 |  |

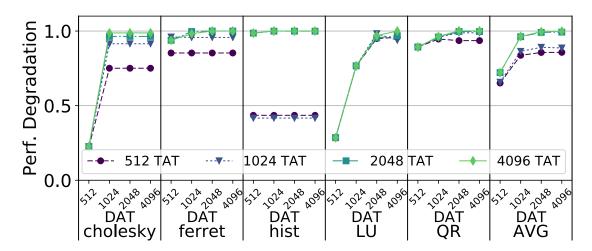

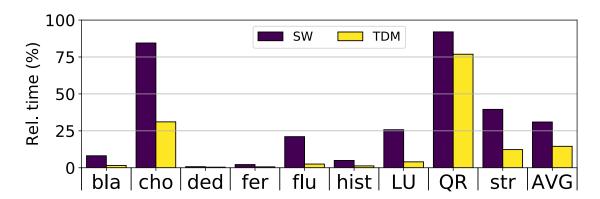

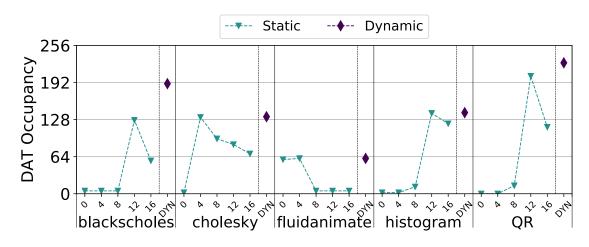

|   |      | 5.3.2    | TAT, DAT and List Arrays                           | 71 |  |

|   |      | 5.3.3    | DMU Access Latency                                 | 73 |  |

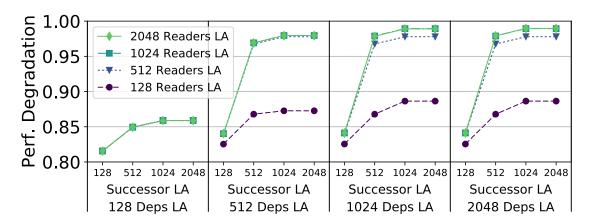

|   |      | 5.3.4    | DMU Area and Power Overhead                        | 74 |  |

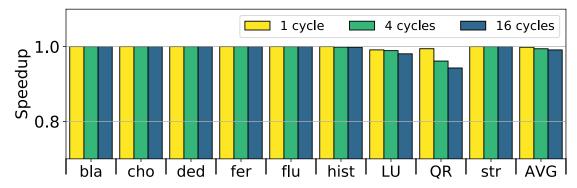

|   |      | 5.3.5    | Runtime Overhead Reduction                         | 74 |  |

|   |      | 5.3.6    | Index Bit Selection for DAT                        | 75 |  |

|   | 5.4  | Flexib   | le Scheduling with TDM                             | 76 |  |

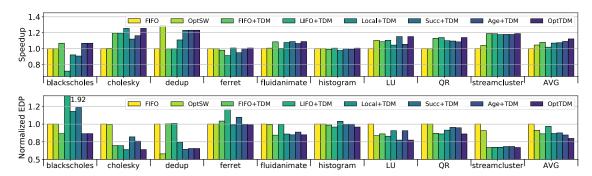

|   |      | 5.4.1    | Performance Evaluation                             | 77 |  |

|   |      | 5.4.2    | Energy Efficiency                                  | 78 |  |

|   |      | 5.4.3    | Comparison with Other Proposals                    | 79 |  |

|   | 5.5  | Remar    | rks                                                | 81 |  |

| 6 | Easi | ng Con   | nmunication Bottlenecks Through The Runtime System | 83 |  |

|   | 6.1  | · ·      |                                                    |    |  |

|   | 6.2  | Exposi   | ing MPI Activity to ATaP Runtimes                  | 86 |  |

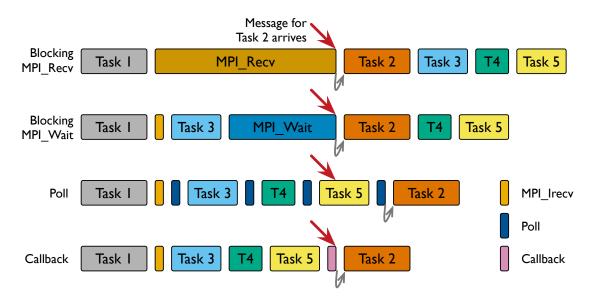

|   |      | 6.2.1    | Extending MPI to Support Event Handling            | 87 |  |

|   |      | 6.2.2    | Mechanisms for Event Delivery                      | 88 |  |

|   |      |          | 6.2.2.1 Polling-based Notification                 | 88 |  |

|   |      |          | 6.2.2.2 Callback-based Notification                | 89 |  |

|   |      | 6.2.3    | Changes to the OmpSs runtime                       | 90 |  |

|      |         | 6.2.4    |           | ping Computation with Collectives                   |     |

|------|---------|----------|-----------|-----------------------------------------------------|-----|

|      | 6.3     | Perfor   | mance Eva | aluation                                            |     |

|      |         | 6.3.1    |           | for Point-to-point Benchmarks                       |     |

|      |         | 6.3.2    | Results f | For Collective Benchmarks                           |     |

|      |         |          | 6.3.2.1   | Fast Fourier Transform                              |     |

|      |         |          | 6.3.2.2   | MapReduce                                           |     |

|      |         | 6.3.3    |           | ty of the collectives benchmarks                    |     |

|      |         | 6.3.4    | _         | son with Task-Aware MPI Library                     |     |

|      | 6.4     | Remar    | ks        |                                                     | 101 |

| 7    |         | -        |           | me-Aware Architecture                               | 103 |

|      | 7.1     |          |           | A 17 A T. 1 . T. 4                                  |     |

|      | 7.2     |          |           | ware Architecture Hardware Extensions               |     |

|      |         | 7.2.1    |           | e and Integration with the Runtime System           |     |

|      |         | 7.2.2    | 7.2.2.1   | rdware Design                                       |     |

|      |         |          | 7.2.2.1   | Task Criticality Identification                     |     |

|      |         | 7.2.3    |           | onal Model                                          |     |

|      |         | 1.2.3    | 7.2.3.1   | Task Creation, Dependence Analysis, and Task Criti- | 107 |

|      |         |          | 7.2.3.1   | cality Detection                                    | 107 |

|      |         |          | 7.2.3.2   | Ready Task Retrieval and Scheduling                 |     |

|      |         |          | 7.2.3.3   | Task Execution                                      |     |

|      |         |          | 7.2.3.4   | Task Finalization                                   |     |

|      |         |          | 7.2.3.5   | Task Unlocking on MPI Message Arrival               |     |

|      | 7.3     | Remar    |           |                                                     |     |

| 8    | Con     | clusions | S         |                                                     | 113 |

|      | 8.1     | Goals,   | Contribut | ions and Main Conclusions                           | 113 |

|      | 8.2     | Future   | Work      |                                                     | 115 |

|      | 8.3     | Public   | ations    |                                                     | 116 |

| Bil  | bliog   | aphy     |           |                                                     | 119 |

| т :. | st of I | Figures  |           |                                                     | 133 |

| Lß   | ,       | 0        |           |                                                     |     |

| CO | NT | ידי | NΠ | ГS |

|----|----|-----|----|----|

|    |    |     |    |    |

Glossary 139

# Chapter 1

# Introduction

Current trends in computer architecture research are being heavily driven by the end of Moore's Law, which predicted that the number of transistors in integrated circuits doubles every two years. For decades the increasingly available transistors were used to improve the Instructions per Cycle (IPC) in-order processors could execute by adding pipelines, branch-predictors and cache memories that greatly increased the instruction throughput of single-core processors. As the transistor count kept rising in a silicon die, computer architects were able to improve the Instruction Level Parallelism (ILP) of sequencial programs by using superscalar and Out-Of-Order execution creating opportunities to hide latency of long memory accesses.

Furthermore, Dennard's scaling stated that the power density of MOSFET transistors stays constant as their size decreases allowing to increase the frequency while the power remains constant. However, Dennar scaling broke down around 2005 and 2007 and the stagnation of CPU clock frequencies due to the impossibility of dissipating the generated power density led to the rise of multi-core systems thanks to the increasingly available transistors in the silicon die. This made Task Level Parallelism (TLP) possible and allowed real parallelism in single-chip systems.

The high levels of concurrency offered by multi-core systems are hard to exploit through programming models based on thread primitives. Thus, new programming models have emerged to deal with such architectures and the *Programmability Wall*. Asynchronous Task-based Programming (ATaP) models and runtimes such as OpenMP 4.0 [92], Charm++ [2], HPX [66], OmpSs [38], and Legion [11] implement a dataflow execution model where the programmer splits the code in sequential pieces of work, called *tasks*, and specifies the data and control dependences between them creating a Task Dependence Graph (TDG). With this information, the runtime system manages the parallel execution, scheduling tasks to cores and taking care of synchronization among them. These models

not only improve programmability, but also can increase performance by avoiding global synchronization points, enabling the user to focus on programming aspects related to their problem domain without worrying about cross-platform performance issues. Under the hood, the runtime systems are designed to automatically optimize for different application scenarios and system specifications.

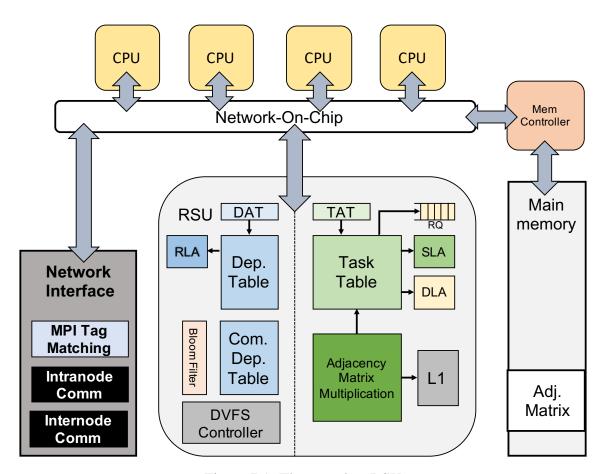

The algorithmic information that the runtime system holds on ATaP models offers several opportunities to tackle the most common issues that computer architects face today; The *Power Wall*, where processor clock stagnated due to the impossibility of effectively dissipating the power density once that frequency reaches a certain threshold, and the *Memory Wall* where the main memory latency does not decrease fast enough to keep up with the processor timing requirements. This PhD thesis envisions a *Runtime-Aware Architecture* (RAA) in which the software runtime system and the hardware are co-designed so that the hardware layer can provide support for expensive task management operations and some decisions at the architectural level such as power management, or inter-node communication are driven by the information obtained at the runtime system layer.

The Power wall originated due the impossibility of keep increasing the frequency of processors due to the power and thermal dissipation constrains that the CMOS technology imposes. Modern computer systems implement different hardware mechanisms that allow reconfiguring the computational capability of the system, aiming to maximize performance under affordable power budgets. For example, per-core power gating and Dynamic Voltage and Frequency Scaling (DVFS) are common reconfiguration techniques available on commodity hardware [36, 68]. However, the problem of optimally using these reconfiguration mechanisms remains open. The information in the TDG can be exploited to open new power savings opportunities and performance gains taking into account its critical path. Tasks outside of the critical path in the TDG can be executed in simpler processing elements or at lower clock frequencies using reconfiguration mechanisms such as DVFS. Asymmetric chip multiprocessor systems present a power-efficient alternative to classical symmetric chip multiprocessor systems by combining high performance out-of-order cores with more power efficient but slower in-order cores. Tasks can be scheduled to the cores by looking at their criticality in the TDG [32] or the speedup they could obtain from running in the big cores [63]. In a RAA, the architecture can provide the metrics the runtime system needs to efficiently map tasks to processing elements and offer mechanisms to perform transparent migration of such tasks when needed.

The increasing number of cores per processor forces developers to decrease the gran-

ularity of the tasks to prevent starvation and expose large degrees of concurrency to the hardware, which favors load balancing and provides more flexibility to exploit constructive interference on shared resources. However, it can also bring large software overheads due to the runtime system activity, which involves creating the tasks, tracking the dependences between them, and scheduling them to cores. All these actions require synchronizing threads to perform complex operations on internal data structures of the runtime system. Different solutions have been proposed to support fine-grained parallelism on multi-cores [39, 59, 60, 71, 116]. These approaches manage fine-grained tasks completely in hardware, relying on specific execution models to scale to large core counts. However, pure hardware solutions suffer from limited adaptability to changes in the software layers. Task support in shared memory programming models is continuously evolving, incorporating new features such as dependence domains or task nesting that are not easy to support at the architecture level. Moreover, implementing a fixed scheduling policy in hardware reduces the adaptability to different application and system characteristics.

Finally, one of the main attractions of ATaP models and runtimes is their potential to automatically expose and exploit the overlap of computation with communication. This refers to the benefit that comes from having multiple tasks on a physical core or process so that when one task is waiting for messages to arrive, another task can use the idle core for useful computation. When ATaP applications are executed on distributed memory systems, inter-node communication is typically handled by calls to a messaging library (in most cases, the Message Passing Interface or *MPI*). Some ATaP models allow explicit calls to MPI whereas in other models, communication primitives are translated to MPI calls by the runtime [38, 113]. The interoperability of the messaging library and the ATaP model has been subject of extensive research, from the programmer explicitly calling communication primitives [82] to the runtime system abstracting the message exchanging [2, 11]. All these works treat the communication layer as a black-box entity and there is a clash on the design philosophies between both, the ATaP and the communication model, preventing to achieve better performance unless the MPI runtime and the ATaP runtime system collaborate together as proposed in this work.

## 1.1 Thesis Objectives and Contributions

The main goal of this thesis is to study scenarios where the software/hardware co-design of a multi-core architecture and the programming model runtime system can be beneficial and use the underlying resources in an efficient and transparent way to the programmer.

The contributions of this dissertation explore several critical scenarios for parallel architectures: power management, parallel workloads performance and load balancing, And inter-process communication in distributed memory systems. This thesis advocates for an integrated proposal to benefit from the information that lives in the intersection of the runtime system and the architecture, enabling the latter to exploit runtime level information or propose mechanisms to ease bottlenecks at the runtime system layer by exploiting lower layers internal state information.

#### 1.1.1 Efficient Power Management based on Task Criticality

The TDG offers a rich degree of information that can be exploited by ATaP runtime systems opening a wide range of performance and power optimization opportunities.

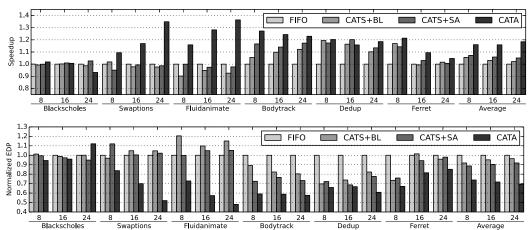

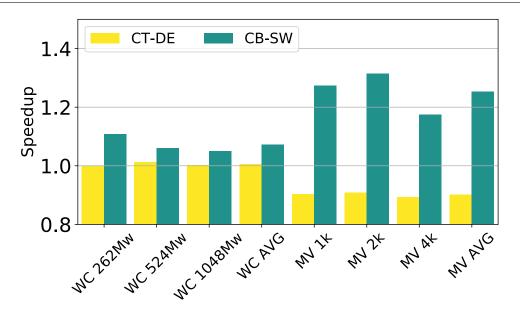

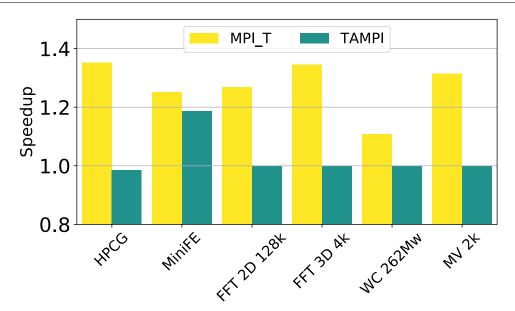

Based on the observation that task criticality information can be exploited to drive hardware reconfigurations, we propose a Criticality Aware Task Acceleration (CATA) mechanism that dynamically adapts the computational power of a task depending on its criticality. As a result, CATA achieves significant improvements over a baseline static scheduler, reaching average improvements up to 18.4% in execution time and 30.1% in Energy-Delay Product (EDP) on a simulated 32-core system.

The cost of reconfiguring hardware by means of a software-only solution rises with the number of cores due to lock contention and reconfiguration overhead. Therefore, novel architectural support is proposed to eliminate these overheads on future manycore systems. This architectural support minimally extends hardware structures already present in current processors, which allows further improvements in performance with negligible overhead. As a consequence, average improvements of up to 20.4% in execution time and 34.0% in EDP are obtained, outperforming state-of-the-art acceleration proposals not aware of task criticality.

The following sections describe the mechanism and its operational model as well as the integration with the runtime system and a complete evaluation of performance and energy savings of the proposal.

#### 1.1.2 Flexible Hardware Support for Task Dependence Management

The growing complexity of multi-core architectures has motivated a wide range of software mechanisms to improve the orchestration of parallel executions. Task parallelism

#### **CHAPTER 1. INTRODUCTION**

has become a very attractive approach thanks to its programmability, portability and potential for optimizations. However, with the expected increase in core counts, fine-grained tasking is required to exploit the available parallelism, which increases the overheads introduced by the runtime system.

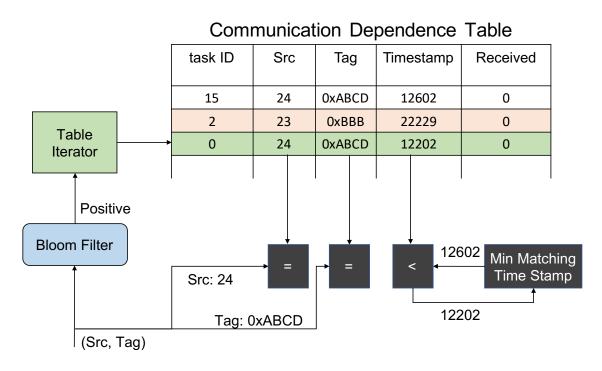

This work presents Task Dependence Manager (TDM), a hardware/software co-designed mechanism to mitigate runtime system overheads. TDM introduces a hardware unit, denoted Dependence Management Unit (DMU), and minimal ISA extensions that allow the runtime system to offload costly dependence tracking operations to the DMU and to still perform task scheduling in software. With lower hardware cost, TDM outperforms hardware-based solutions and enhances the flexibility, adaptability and composability of the system. Results show that TDM improves performance by 12.3% and reduces EDP by 20.4% on average with respect to a software runtime system. Compared to a runtime system fully implemented in hardware, TDM achieves an average speedup of 4.2% with  $7.3 \times$  less area requirements and significant EDP reductions. In addition, five different software schedulers are evaluated with TDM, illustrating the flexibility and performance gains of our approach.

#### 1.1.3 Towards a Seamless ATaP-MPI Interoperability

.

Communication in hybrid parallel and distributed applications is usually handled by the MPI Library. In such applications, computation and communication phases are welldefined and isolated from each other limiting the potential computation-communication overlap.

ATaP models are gaining popularity to address the programmability and performance challenges in high performance computing. One of the main attractions of these models and runtimes is their potential to automatically expose and exploit overlap of computation with communication.

ATaP models can deal with communication by either allowing the programmer to place explicit MPI calls in the tasks code, or the runtime system can be communication aware and schedule data transferences when appropriated. Although this exposes a transparent and natural computation-communication overlap, there are still some inefficiencies due to the lack of information sharing between the ATaP and the communication layer runtime systems.

This chapter explore how information about MPI internals can be exposed and used

in a task-based runtime system to make better scheduling and task-creation decisions. In particular, we present two mechanisms for exchanging information between MPI and a task-based runtime, and analyze their trade-offs. Further, we present a detailed evaluation of the proposed mechanisms implemented in MPI and a task-based runtime. We show improvements of up to 16.3% and 34.5% for proxy applications with point-to-point and collective communication, respectively.

#### 1.2 Thesis Structure

The document contents are organized as follows:

- Chapter 2 reviews parallel architectures and programming models and provides the necessary information to understand the rest of the chapters.

- Chapter 3 describes all the tools and benchmarks used for the evaluation of the presented proposals.

- Chapter 4 presents *Criticality-Aware Task Acceleration (CATA)* a mechanism to drive the power management of a multi-core chip multiprocessor. The chapter explains the problems that previous alternatives faced and later describes the proposed solutions and their evaluation.

- Chapter 5 introduces *Task Dependence Manager (TDM)* a flexible solution proposing hardware support to accelerate the Task Dependence Graph construction while keeping the task scheduler in software. First the motivation behind the proposal is explained by analyzing the bottlenecks of a runtime system, then the architecture of *TDM* is detailed and a complete design space exploration and evaluation are provided.

- Chapter 6 explores how the blocking time of worker threads can be reduced when using MPI taskified calls by exposing MPI and network interface related events to the ATaP model runtime system. Two alternatives events delivery mechanisms are described and evaluated, as well as a new proposal for performing computation/communication overlap when using collectives.

- Chapter 7 details how all these proposals interact together, lays the theoretical foundations of a Runtime Aware Architecture, and explains the operational model and integration of all the components with their interface.

#### **CHAPTER 1. INTRODUCTION**

• Finally, Chapter 8 concludes the dissertation by remarking the main contributions and providing an insight of future work.

# Chapter 2

# **Background and Related Work**

This Chapter introduces the background context and does an analysis of the state-of-the-art for all the concepts laid out in this thesis. Section 2.1 describes multiprocessors systems focusing on their memory models, shared memory and distributed memory multiprocessor systems, the concept of asymmetric multiprocessor systems is also detailed. Section 2.2 explains parallel programming models, starting from the omniscient threading programming model and OpenMP basic parallel constructs to the more complex ATaP models that can be used in both shared and distributed memory systems. Section 2.3 introduces OmpSs, the programming model used in this thesis and explains its most relevant characteristics. Next we detail hardware support for task-based programming models proposals present in the literature. Finally, we focus on distributed environments and explain the classical MPI programming model and how ATaP models interact with the communication library.

## 2.1 Parallel Multiprocessor Systems

Multiprocessor systems date from the era of the large mainframes in the 1960s [47]. However, it was not until the 1980s that these systems became common in computing infrastructures. The first systems consisted of bus-based multiprocessors with snooping caches [43] that were primitive implementations of the coherence protocols present on current multiprocessors. Many advances were done in those years, laying the foundations for both shared and distributed memory systems.

#### 2.1.1 Shared Memory Multiprocessor Systems

Most common shared memory systems provide a hierarchical shared memory address space to a series of processors managed through a memory coherence protocol implemented in hardware. The coherence protocol has the responsibility of making one processor changes to the private levels in the memory hierarchy visible to other processors in the system and coordinate the access to the shared memory locations to provide support for atomic operations used to implement inter-processor synchronization primitives.

Usually these systems include multiple full-fledged physical processors holding directories of memory locations that they can access either locally or by requesting them through the interconnection network. We refer to such schema as *distributed shared memory processors* or *Non-Uniform Memory Access (NUMA)* since physically separated memories can be accessed as a logically unified and shared space.

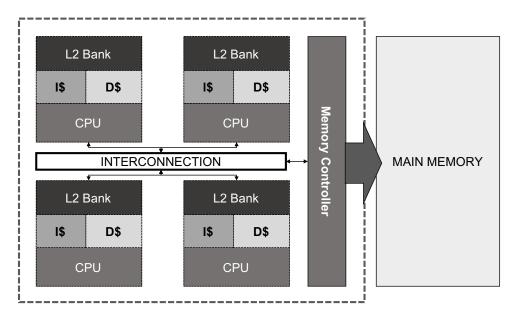

While original shared memory systems consisted of physically independent processors, the increasing number of transistors in a silicon die [85], the ILP limitations and the stagnation of processor frequencies motivated a shift into the design of processors. Rather than devote more transistors to exploit ILP, hardware support for TLP was devised bringing in Simultaneous Multi-Threading (SMT) in which a subset of the processor structures holding the architectural status are replicated [123]. Eventually the increasingly available transistor count per silicon die allowed to integrate several processor into a single die, resulting in the Chip MultiProcessors (CMP), a trend that started with the IBM POWER4 [119], the world's first dual core processor. Figure 2.1 shows a CMP with four cores and two levels of cache. Each core has a private instruction and data L1 cache, and a shared distributed L2 cache that is accessed through the interconnection network. Nowadays, multiprocessor systems range from 4-8 cores for mobiles and desktop computers and up to 72 cores as in the Intel Xeon Phi or the AMD Threadripper.

## 2.1.2 Distributed Multiprocessor Systems

While shared memory systems offer the programmer a logical unified shared memory address space between all the processing elements in the system, distributed memory systems have multiple address spaces where data is shared through a message passing protocol using the interconnection network. In this thesis we focus on distributed memory multiprocessor High Performance Computing (HPC) systems, which, are composed of several independent nodes connected together using a low-latency high-bandwidth in-

Figure 2.1: Example of a chip multiprocessor system.

terconnection network. Typically, each node houses one, two or four CMPs in a NUMA shared memory fashion and is connected to other nodes using a low latency high bandwidth network protocol such as Infiniband or Myrinet. In several machines, accelerators such as GPUs or FPGAs can be present in a subset or all the nodes providing heterogeneous computing capabilities.

The core count in the world fastest supercomputers has dramatically increased in the recent years. According to the Top500 list [1] which is published twice every year, in 1998 the #1 Supercomputer, ASCI RED had 9,152 cores. Ten years later, in 2008, Roadrunner was made of 122,400 cores, and in 2018, Summit consists of 2,282,544 cores. The growing number of cores in CMPs make possible this continuous increase while keeping energy and cooling costs in a reasonable budget. However, it is complicated for programmers to take advantage of such large-scale system as message sending and reception are left to the application programmer or programming model designers. Heterogeneity is also present in the Top500 systems and is becoming increasingly important in order to achieve Exascale; 27.4% of the systems in the Top500 list of November 2018 uses some kind of accelerator. Summit hosts 27,648 Nvidia Volta GV100 GPU accelerators connected directly to the POWER9 CPUs with the NVLink interconnection.

#### 2.1.3 Asymmetric Multiprocessor Systems

While shared memory multiprocessor systems are usually conceived as symmetric systems where all the processing elements in the system share the same characteristics, the heterogeneity of workloads and current power constraints in embedded and large scale systems design has motivated the design of asymmetric systems, in which the processing elements can exhibit different performance ratios. However, it is worth mentioning that current homogeneous systems can exhibit from negligible to moderate asymmetry in performance due to variability in the manufacturing process, or not proper cooling as demonstrated in [81, 106].

Heterogeneous systems are asymmetric by nature as their elements do not provide the same capabilities. Such systems are usually targeted to certain problem cases such as accelerators for graphics, cryptography, vector operations and communications among others. Another factor that guides the asymmetric system design is power efficiency. In-order cores offer a trade-off in power/performance when compared to power hungry out-of-order architectures. The ARM big.LITTLE processor is an Asymmetric Multi-core (AMC) architecture that combines both classes of cores on two core clusters of 4 cores each; a high-performance cluster based in the Cortex A-57 architecture, and a low-power consumption cluster with Cortex A-53 cores. In this system, high-preforming cores can run critical tasks while the smaller cores are targeted to non-critical low-resources demanding processes guided by the OS scheduler. However, in multi-threaded workloads, is the programmer responsibility to map each thread to a core taking in account the differences in performance.

In general, asymmetric systems have serious drawbacks in terms of flexibility as different phases of an application might be optimally executed in different computation units. Consequently, the overhead of moving tasks and their associated data to different computation units can neglect the expected energy improvements. An alternative is to have a highly reconfigurable hardware that adapts to the actual requirements of the running application. Reconfiguring the underlying hardware eliminates the data movement burden, but adds new issues as the reconfigurations must be coordinated to avoid an explosion in terms of power consumption.

Current systems offer many different hardware mechanisms that allow reconfiguring the computation power of the system. For example, in SMT processors, the number of SMT threads per core or the decode priority can be adjusted [18, 125], while in multi-

cores, the prefetcher aggressiveness, the memory controller or the last-level cache space assigned to an application can be changed [33, 62, 102]. More recently, reconfigurable systems that support core fusion or that behave like traditional high performance out-of-order cores, but can be transformed to a highly-threaded in-order SMT core when required, have been shown to achieve significant reductions in terms of energy consumption [56, 70]. Also, per-core power gating and DVFS are common reconfiguration techniques available on commodity hardware [36, 68]. However, the problem of optimally reconfiguring the hardware is not solved in general as all the above mentioned solutions rely on effective but ad-hoc mechanisms that are applicable to a reduced set of reconfiguration problems, they are difficult to combine [125], and they introduce a significant burden on the programmer.

Multiple techniques to exploit heterogeneous architectures and reconfiguration capabilities have been proposed, such as migrating critical sections to fast cores [117], *fusing* cores together when high performance is required for single-threaded code [56], reconfiguring the computational power of the cores [70], *folding* cores or switching them off using *power gating* [125], or using *application heartbeats* to assign cores and adapt the properties of the caches and the TLBs according to the specified real-time performance constraints [52].

## 2.2 Parallel Programming Models

### 2.2.1 Threading and Fork-Join Programming Models

One of the most common parallel programming models in production-grade software nowadays is the explicit use of light-weight processes named threads. A thread is a analogous to a forked process which shares the application text, data and heap segments with its parent process. A thread also retains its own architectural context such as the CPU registers including the instruction pointer, and the memory stack. Most common operating systems provide facilities to create and manage threads through the use of the POSIX Threads (pthreads) programming interface [86]. Pthreads or System-Level Threads (SLTs) can be created by a single POSIX API call, and they are scheduled as independent processes that can run in any core of the system, the pthread interface also provides means to synchronize threads when accessing to shared memory regions through the use of semaphores.

An alternative to SLTs are User Level Threads (ULTs) [83]. ULT libraries allocate a

set of resources (processors and memory) and manage thread creation and scheduling in user-level space through a runtime system. ULTs are usually mapped to a pool of existing SLTs but providing extended capabilities such as more complex and safer synchronization mechanisms and faster thread creation and context switching or custom scheduling to better exploit locality.

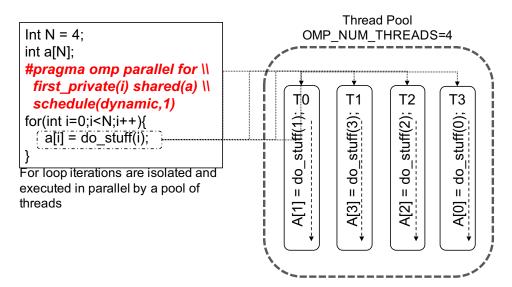

The complexity of programming using threads has driven the creation of mechanisms to ease the programmability of parallel systems. OpenMP is a set of compiler directives for C, C++ and FORTRAN based on *pragma annotations*. The programmer adds the #pragma omp parallel directive preceding the blocks of code that will run in parallel. OpenMP offers a #pragma omp parallel for directive for parallelizing for loops without inter-iteration dependences. Loop iterations scheduling across threads can be configured by the schedule directive. Alternatively, work can be distributed among threads by using the parallel section annotation and the following block of code will be scheduled for execution in any free thread if no affinity restrictions are placed. In OpenMP, access to the data can be controlled by declaring data as shared or private in the omp directives; first private is a special case used to make a local copy of a shared variable before the execution of the forked code. In addition, thread synchronization and access to shared data can be protected with the use of critical, atomic or barrier annotations. Figure 2.2 shows an example of how several threads execute parallel for loop iterations using a dynamic scheduler which maps iteration ranges to any available free thread.

In OpenMP source codes, the compiler detects the parallel blocks and abstracts them into functions that are passed as arguments to the OpenMP runtime system API. Moreover, the compiler also inserts the relevant API calls for synchronization in shared data management. The OpenMP runtime system consists of a pool of worker threads and a scheduler with work-queues to execute the parallel functions once they are created. This runtime system is also in charge of coordinating access to the shared data.

OpenMP sets the basis of modern parallel programming models where the cooperation between the compiler and a runtime systems allows programmers to express parallelism in easier and platform-agnostic environments closer to the algorithmic concepts rather than complex operating system level libraries and architectural concepts. Furthermore, this synergy allows to find hidden parallelism thanks to the analysis of the original source code and even increase performance by providing means to exploit data locality that programmers would not be aware of.

Figure 2.2: OpenMP parallel for implementation

#### 2.2.2 Asynchronous Task-based Programming Models

Programming current large scale parallel systems has motivated a resurgence of ATaP models over explicit threading and fork-join approaches due to the programmability-performance trade-off they offer. This section aims to provide an insight on the most relevant ATaP models.

Task constructs are subroutines that can be executed asynchronously and in parallel in different threads. Tasks have synchronizing dependences among them to structure the control flow of the application. OpenMP 3.0 [91] introduced basic task constructs in the programming model that OpenMP 4.0[92] extended with data dependences annotations in order to create a dataflow ATaP programming model. The OpenMP 4.0 runtime system analyzes this annotations and creates the TDG as will be detailed in section 2.3. Programming models such as OmpSs [38] or StarPU [7] follow this schema.

Habanero [113] proposes a set of extensions to the C and Java languages to create asynchronous tasks with dataflow capabilities using futures, a language construction that allows tasks to synchronize and exchange data. Habanero also proposes phasers [112] for control synchronization. Codelets [128] are collections of instructions that are executed atomically and created a Codelet Graph (CDG) through the use of data and control dependences. Codelets rely on a hierarchical and heterogeneous abstract machine model to schedule and execute the work units. Intel Thread Building Blocks (TBB) [103] is a C++ template library with multiple constructions for parallel operations such as *parallel\_for*,

parallel\_scan or parallel containers among many others. TBB allows the use of tasks that are created in a recursive manner with control dependences to synchronize them throughout the hierarchy. Furthermore, Intel TBB 4.0 introduces flow graph annotations, which allow to specify a dataflow graph between different tasks. Cilk [17] includes a set of C and C++ extensions that allows to *spawn* and *sync* tasks. However, dataflow annotations have been added outside of the standard language by Vandierendonck et al. [124].

Charm++ [2] decomposes work in units called *chares*. Chares are C++ objects that offer a series of entry points that other chares can directly invoke. The runtime system then sends the appropriate messages to synchronize and exchange data between chares in a transparent way to the programmer. Charm++ offers mechanisms to easily map chares to tensor-like data structures, distribute them, and overdecompose data volumes in more chares than processing elements. Moreover, as chares entry method invocation is non-blocking, Charm++ allows programmers to specify control dependences to ensure structured flow control between chares.

Legion [11] creates abstractions for both computation and data. Computation is written as tasks with data partitions as their inputs and output. The Legion runtime system then builds a TDG using the inputs and outputs information in a dataflow manner. Partitions are logical abstractions of data expressed as array-of-structures or structures-of-arrays. The Legion programming model allows multiple versions of the data to be alive at a given moment and the runtime system is responsible for moving the data across the system to the node where the task requiring that specific version will be executed.

The use of ATaP models provides a hardware abstraction that allows programmers to efficiently write portable code without caring about low-level details while increasing the programmability of parallel systems. Moreover, these programming models can increase the performance of applications through the use of generic optimizations at the runtime system level such as data locality aware scheduling in NUMA systems, or tasks schedulers that favors load balancing. In addition, some of this programming models, such as Charm++ or Legion, allow applications to run in distributed computing environments with virtually no changes to the application code, effectively hiding the complexity of distributed programming to the application developers. To conclude, the benefits of ATaP models, portability, programmability and performance are key in modern computing infrastructures and noteworthy to remark.

#### 2.2.3 Programming Models for Distributed Environments

Early distributed systems programming relies on the explicit use of the communication hardware to send messages across the network interconnecting all the nodes composing the computer. This approach, while providing great levels of performance hindered application portability and programmability as most of the interconnection technologies and interface code are system-specific. As a result, an effort has been made to provide a layer of abstraction on top of the communication one to ease programmability and portability efforts. As a consequence, the current de-facto standard for distributed memory communication is the Message Passing Interface (MPI) [114], an easy-to-use, portable, high-performing abstraction on top of most low-level communication technologies present in distributed memory clusters.

MPI provides an interface to send data by calling point-to-point or collective send and receive operations. Point-to-point primitives involve communication within a pair of nodes, while collective operations involve a group of nodes. Collective operations are highly tuned to the underlying communication technology and they execute different algorithms for a single collective operation based on the network topology and the size of the messages [120].

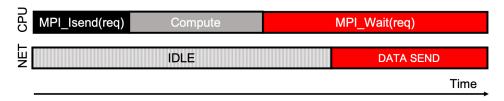

MPI offers two communication models; blocking and non-blocking communication. In the blocking model, whenever a blocking call is invoked the execution cannot progress until the message has been copied to a safe location. In the alternative non-blocking communication, the call returns immediately, but it is the programmer's responsibility to poll the status of the pending messages to ensure the progress and completion of the communication. Although, using non-blocking calls allows overlapping communication and computation, the MPI layer does not make any progress until MPI\_Test or Wait calls on specific requests are invoked, resulting in no effective overlap at all unless explicit mechanisms are used as demonstrated in [50]. Figure 2.4 shows how the actual message is not send until a specific wait is invoked on the MPI request, thus overlap is not guaranteed unless is driven through specific threads.

In order to overcome this limitation, Hoefler and Lumsdaine [50] study the implications of using a dedicated thread to constantly advance the progress engine. They compare this approach to manual and hardware interrupts-driven progression by using the Infiniband RDMA engine. In addition, Buettner et al. [22] propose to taskify communication and offload the MPI\_Test call required to move the progress engine to the OpenMP run-

Figure 2.3: Non-blocking communication does not guarantee overlapping

time.

This progress engine limitations arise from MPI design being heavily influenced by Bulk-Synchronous programming models, resulting in limited interoperability with parallel shared-memory programming models. Although the standard [42] and MPI vendors thrive to enhance this interoperability, some of the MPI characteristics require changes to the standard or restrict some capabilities such as wildcards in order to efficiently parallelize the MPI message matching engine.

MPI alternatives such as the Adaptive Message Passing Interface (AMPI) [57], appeared to enhance the multi-threading support of MPI. AMPI implements MPI ranks as user migratable lightweight threads instead of full-fledged OS processes. AMPI is written in top of Charm++ and takes advantage of the dynamic load-balancing and scheduling algorithms it offers, allowing regular MPI applications to benefit from these characteristics without the need of being rewritten.

#### 2.2.4 Communication in Hybrid MPI+ATaP Models

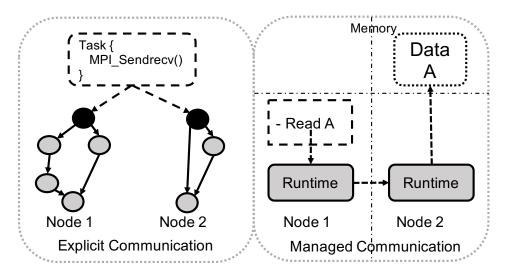

MPI is employed inside ATaP programming models using two different approaches. The *explicit communication* model requires the programmer to insert the relevant MPI calls in the application code and do a manual orchestration of all the MPI ranks as illustrated in figure 2.4 left hand side. OpenMP 4.0 [92], OmpSs [38], Codelets [128], Habanero [113] or StarPU [7] are ATaP models used for shared memory systems that require explicit communication in order to take advantage of distributed systems.

Alternatively, other programming models hide communication from the programmer by letting the runtime detect accesses to remote data and perform the required transferences. This approach is called *implicit communication* or *Runtime managed* as shown in figure 2.4 right hand side. Some examples of this model follows. Charm++ employs a communication interface that relies on active messages built on top of MPI. Legion [11] detects accesses to partitions of data in remote nodes and internally schedules data trans-

Figure 2.4: Different communication mechanisms for ATaP models

ferences by means of communication threads and active messages. HPX [66] offers a PGAS model in which tasks can directly address memory in any node with the runtime system taking care of data movement.

Improving the MPI and programming model interoperability has been am extensive subject of research, Marjanovic et al. [82] present one of the first works focused on the interoperability of a task-based asynchronous programming models, such as OmpSs, with MPI. Instead of doing synchronized phases of communication and computation, as in the Bulk Synchronous Programming Model, MPI calls are placed inside of asynchronous tasks scheduled by the runtime system effectively opening new opportunities for communication and computation overlap. Chatterjee et al. [29] goes one step further and integrates MPI within Habanero providing wrapped MPI calls that the runtime executes asynchronously in dedicated communication threads. Labarta et al. [73] present the Task-Aware MPI library (TAMPI), a similar approach to improve the interoperability between MPI and OmpSs. TAMPI intercepts blocking calls to MPI and converts them into their non-blocking counterpart. The resulting MPI calls are managed by the TAMPI library, which periodically polls for the completion of the MPI calls and ensures correctness. However, TAMPI is limited to point-to-point communications and requires polling to query for completion of specific calls. Kamal et al. [67] make use of ULTs in the MPICH 2 [45] to build an MPI-aware scheduler for coroutines that are swapped in and out for execution depending on the status of the MPI runtime. Lu et al. [77] follow a similar approach by doing the context switch of ULTs inside the MPI to avoid the expensive MPI locking operations. Stark et al. [115] integrate MPI with Qthreads and convert

Figure 2.5: Execution flow in an asynchronous task-based programming model that uses a TDG.

blocking MPI calls to non-blocking calls, using their status to drive the scheduler in a similar way to TAMPI.

#### 2.3 The OmpSs Programming Model

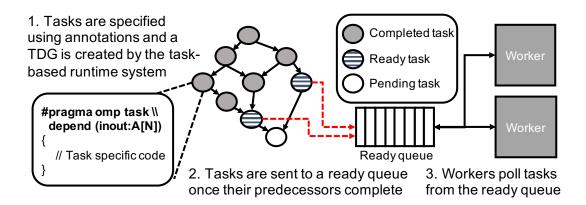

ATaP models such as OpenMP 4.0 [92] and OmpSs [38], conceive the execution of a parallel program as a set of tasks that may depend upon each other. Typically, the programmer defines code blocks (functions and/or classes) and adds annotations to declare 1) what constitutes a task, 2) what data is used by each task, called input dependences or input, and 3) what data is produced by each task, called output dependences or output. Based on this information, the runtime system manages the parallel execution using a TDG, a directed acyclic graph where the nodes are tasks and the edges are the dependences between these tasks.

Figure 2.5 shows a simple example of a TDG. A task is marked as ready only when all its predecessors have completed their execution, otherwise it is considered a pending task. Ready tasks are added to a *ready queue* (or another appropriate data structure depending on the scheduling algorithm). When idle, worker threads interact with the scheduler and retrieve tasks for execution. When a task completes, it is marked as such in the TDG and its successors are unlocked. Examples of such a programming model are tasks in OmpSs [38] and OpenMP 4.0 [92] with dependence clause extensions and Legion [11], in which dependences between tasks are expressed using regions.

This thesis uses the task constructions in OmpSs [38], which have been adopted as the task extensions for OpenMP 4.0. The programmer creates tasks using pragma annotations

#### **Algorithm 1:** Algorithm for *TDG* creation.

```

Data: task object

Data: task memory locations list

for location in locations do

if lastWriter of location != NULL then

| lastWriter.successors.add(task) task.predecessors++;

end

if location.dir == IN then

| location.readers.add(task);

end

if location.dir == OUT then

| for reader in location.readers do

| reader.successors.add(task); task.predecessors++;

end

| location.readers.flush(); location.lastWriter = task;

end

end

```

with the input and output dependences specified as shown in Figure 2.5. The compiler replaces these annotations with calls to the runtime system, and the tasks are dynamically created and destroyed during the application execution. In this work, we employ Nanos++ 0.10a [38], the runtime of OmpSs, which uses pthreads bound to specific cores as worker threads.

#### 2.3.1 Task Dependence Graph

In ATaP programming models such as OpenMP4 and OmpSs, tasks are declared in the code by the use of pragma annotations #pragma omp depend(in: (..), out: (..), inout:(..)). These pragma annotations precede the code blocks that are executed asynchronously and specify the list of memory locations that the tasks read in, write out or read and write inout. The runtime system takes this information and uses it to construct the TDG as detailed in Algorithm 1, The runtime system holds several data structures such as a list of reader tasks and the last writer task for every memory location expressed as dependences. In addition, tasks hold a list with their successors in the TDG and the count of their predecessors.

Task dependence analysis can be extended to track memory regions when accessing data with multiple dimensionality. In this case, the locations object tracks the dimensions accessed and the TDG creation algorithm uses this information to find the access overlaps within tasks [21].

Figure 2.6: Criticality assignment with bottom-level and static policies, and Criticality-Aware Task Scheduling.

Once the TDG is constructed, the runtime system employs it to keep track of the execution. Furthermore, this TDG holds important information such as task criticality that can help runtime decissions like task scheduling.

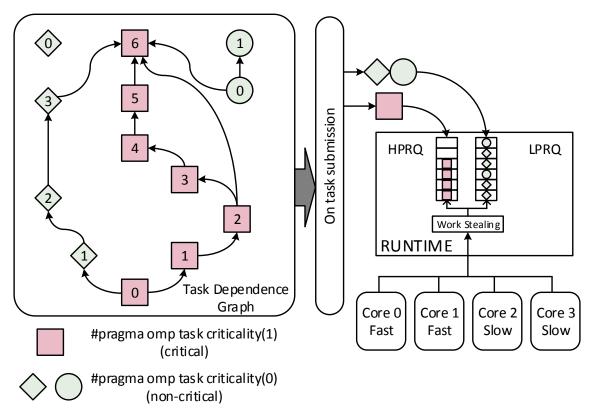

Criticality represents the extent to which a particular task is in the critical path of a parallel application. In general, criticality is difficult to estimate as the execution flow of an application is dynamic and input-dependent. Two approaches can be used to estimate the criticality of a task.

One approach is to dynamically determine the criticality of the tasks during the execution of the application, exploring the TDG of tasks waiting for execution and assigning higher criticality to those tasks that belong to the longest dependence path [32]. Figure 2.6 shows a synthetic example of this method. In the TDG on the left, each node represents a task, each edge of the graph represents a dependence between two tasks, and the shape of the node represents its task type. The number inside each node is the *bottom-level* (BL) of the task, which is the length of the longest path in the dependence chains from this node to a leaf node. The criticality of a task is derived from its BL, where tasks with the highest BL and their descendants in the longest path are considered critical. Consequently, the

square nodes in Figure 2.6 are considered critical.

The bottom-level approach does not require any input from the programmer and it can dynamically adapt to different phases of the application. However, this method has some limitations. First, exploring the TDG every time a task is created can become costly, specially in dense TDGs with short tasks. Second, the task execution time is not taken into account as only the length of the path to the leaf node is considered. Third, only a sub-graph of the TDG is considered to estimate criticality and some tasks marked as critical in such partial TDG may not be critical in the complete TDG.

Another approach is to statically assign criticality to the tasks, either using compiler analysis or allowing the programmer to annotate them. For this purpose, the task directive in OpenMP 4.0 can be extended to specify criticality, #pragma omp task criticality(c). The parameter c represents the criticality level assigned to the given task type. Critical tasks have higher values of c, while non-critical tasks have a value of c=0. The bottom left part of Figure 2.6 shows how this directive is used to assign the criticality of the three different task types in the example, where square nodes are considered critical, while triangular and circular nodes are estimated as non-critical. In this example and for the sake of simplicity, tasks are assigned to the same criticality level with both approaches (static annotations and bottom-level), but this does not happen in general.

The main problem of static annotations is that estimating the criticality of a task can be complex and input dependent. However, by analyzing the execution of the application it is feasible to identify tasks that block the execution of other tasks, or tasks with long execution times that could benefit from running in fast processing elements.

The task criticality information obtained with any of these approaches can be exploited by the runtime system in multiple ways, specially in the context of asymmetric or heterogeneous systems.

#### 2.3.2 Task Scheduling

The task scheduler is a fundamental part of ATaP runtime systems. Its goal is to assign tasks to cores, maximizing the utilization of the available computational resources and ensuring load balance. The typical scheduler of ATaP runtime systems assigns tasks to available cores in a *first in, first out* (FIFO) manner without considering the criticality of the tasks. In this approach, tasks that become ready for execution are kept in a ready queue until there is an available core. There are several scheduling policies that can be applied in ATaP models, some of them FIFO variants such as *last in, first out* (LIFO)

scheduler which allows to do an in-depth TDG traversal. Priority-based schedulers are other alternatives in which tasks are sorted in a ready queue according to their priority which can be based on aging or explicitly defined by the programmer.

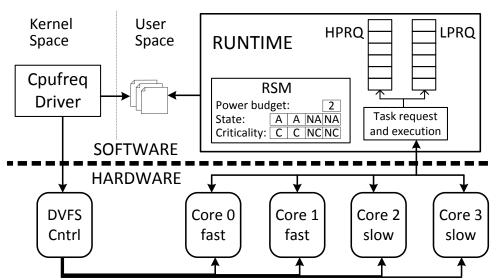

However, since the TDG offers a rich degree of information, it is possible to deploy new scheduling mechanisms that exploit this knowledge in order to increase the system efficiency. The scheduler can apply graph partitioning techniques to the TDG to reduce expensive data transferences in NUMA systems by executing tasks reusing data in the same NUMA socket [109]. Criticality can also be used to guide scheduling decissions as in the Criticality-Aware Task Scheduler [32] (CATS), mainly focused on heterogeneous architectures, ensuring that critical tasks are executed on fast cores and assigning noncritical tasks to slow cores. As shown in Figure 2.6, CATS splits the ready queue in two: a high priority ready queue (HPRQ), and a low priority ready queue (LPRQ). Tasks identified as critical are queued in the HPRQ and non-critical ones in the LPRQ. When a fast core is available it requests a task to the HPRQ, and the first ready task is scheduled on the core. If the HPRQ is empty, a task from the LPRQ can be scheduled on a fast core. If no tasks are ready, the core remains idle until some ready task is available. Similarly, slow cores look for tasks in the LPRQ. Task stealing from the HPRQ is accepted only if no fast cores are idling. Figure 2.6 illustrates the runtime system extensions and the scheduling decisions for the synthetic TDG on the left.

#### 2.3.3 Task Life Cycle

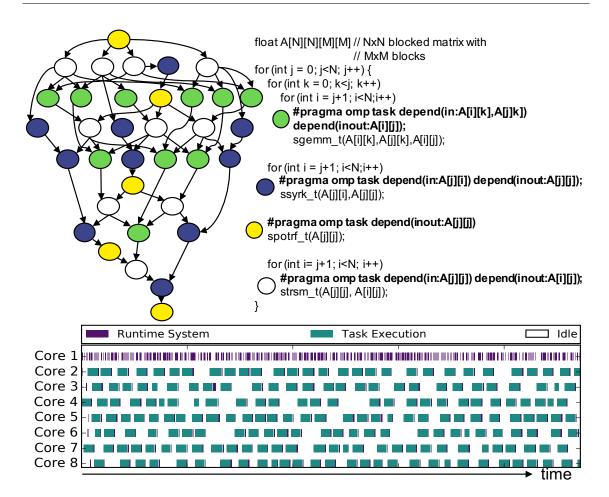

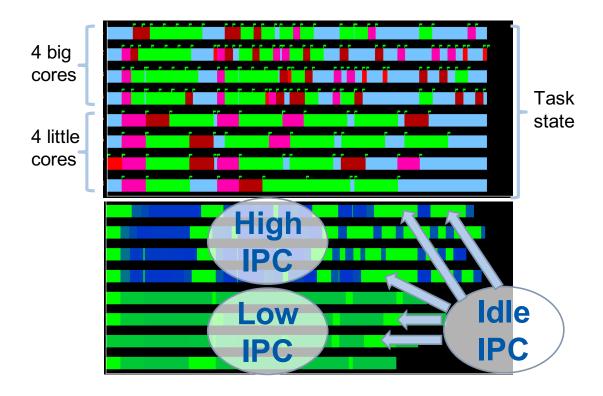

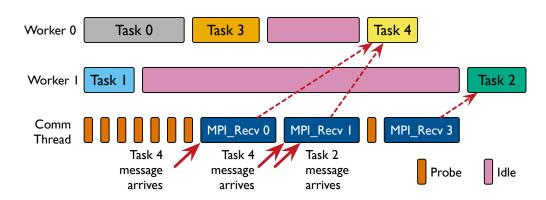

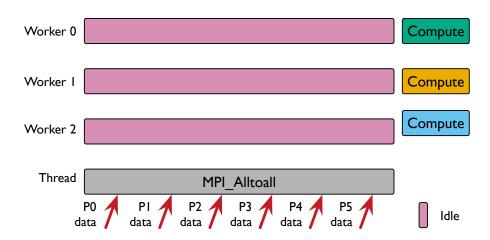

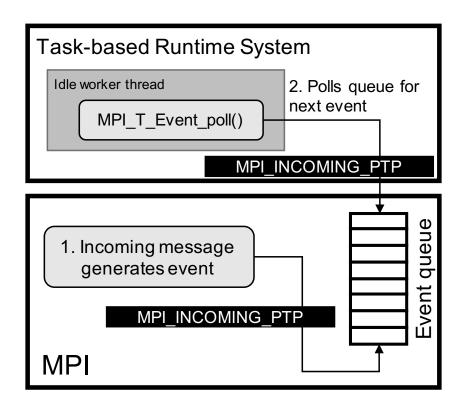

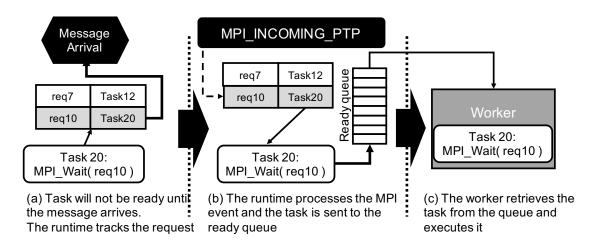

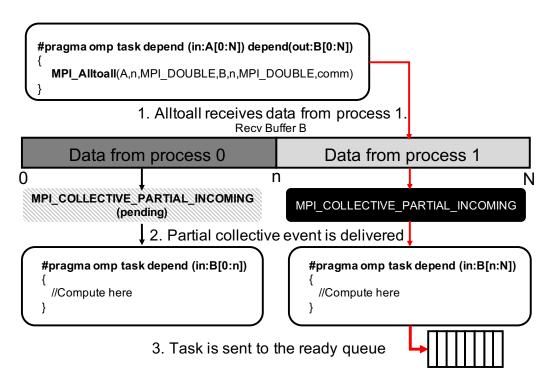

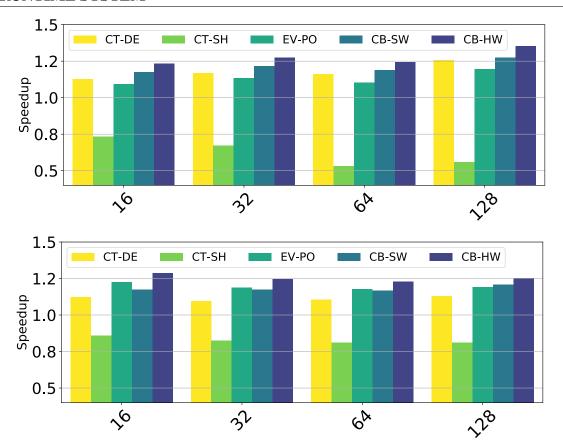

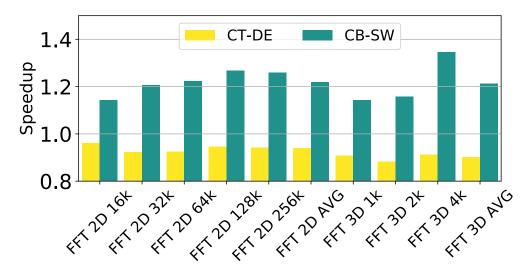

ATaP programming models use a decoupled execution model where tasks are created in program order and are executed asynchronously following the synchronization rules defined by the dependences. All threads may execute runtime system activity as well as tasks defined in the application source code. Figure 2.7 shows the execution timeline of the Cholesky benchmark on an 8-core system. In this experiment, core 1 performs most of the runtime system activities while the other cores mainly execute tasks.