**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

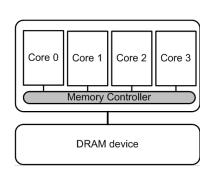

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

# A Multi-core Processor for Hard Real-Time Systems

Marco Paolieri

2011

A THESIS SUBMITTED IN FULFILLEMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy / Doctor per la UPC

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

## A Multi-core Processor for Hard Real-Time Systems

#### Marco Paolieri

2011

Advisor:

Francisco J. Cazorla Almeida

Barcelona Supercomputing Center

Co-Advisors:

Eduardo Quiñones

Barcelona Supercomputing Center

Mateo Valero Cortés

Universitat Politècnica de Catalunya

A THESIS SUBMITTED IN FULFILLEMENT OF THE REQUIREMENTS FOR THE DEGREE OF Doctor of Philosophy / Doctor per la UPC

Departament d'Arquitectura de Computadors Universitat Politècnica de Catalunya

#### Acknowledgments

Before concluding my PhD I would like to spend few words to thank all the people that helped me and supported me during this *adventure*. It seems like yesterday that I started and instead another chapter of my life is already at the end. I am really glad to have decided to do a PhD because I think I learnt a lot from the people who surrounded me both at personal and professional level.

First and foremost I want to thank my advisor Francisco J. Cazorla and my coadvisors Eduardo Quiñones and Mateo Valero. It has been an honor to be their PhD student. Thanks to them I have learnt what *research* truly means!

The work done in this thesis was part of an FP7 European project called Multi-Core Execution of Hard Real-Time Applications Supporting Analysability (MERASA - grant agreement number FP7-216415). I am especially grateful to Prof. Theo Ungerer to be the coordinator of such a great project and to all the other partners from University of Augsburg, Université Paul Sabatier, Rapita Systems Ltd., Honeywell International s.r.o.: Pascal Sainrat, Guillem Bernat, Zlatko Petrov, Hugues Casse, Christine Rochange, Sascha Uhrig, Mike Gerdes, Irakli Guliashvili, Michael Houston, Florian Kluge, Stefan Metzlaff, Jörg Mische and Julian Wolf.

Many thanks to all my colleagues and friends from BSC, and in particular from the CAOS group with whom I shared the office. Four years have passed so fast that it seems like yesterday I was jumping on the metro towards the university to start my first day as a *PhD student* in the beautiful city of Barcelona...and now I can finally remove the word *student*. I will miss a lot Barcelona and BSC!

A special thank to my friend Edu for his great help, advices and presence. He was always there when I had questions, doubts or problems. I really enjoyed all the business trips we had together.

Thanks to my Italian friends in the group: Roberto and Alessandro. Roberto thanks for all the advices and all the support! Ale, I will never forget all the time we spent together, having lunch and discussing about anything, trying to figure out how we could open our business.

I express deep gratitude and heartfelt thanks to my parents Paolo and Ida for standing by me. They always have given a good ear to me and helped me. I would also like to thank them for the advices and the guidelines they gave me whenever I was low!

A really special thank to Mara, who has always been by my side for these four years, and during the last three she made Barcelona even more beautiful! She is always able to make me happy and make every day special.

Lastly, thanks to those I have forgotten..sorry about that!

"You've got to find what you love. And that is as true for your work as it is for your lovers. Your work is going to fill a large part of your life, and the only way to be truly satisfied is to do what you believe is great work. And the only way to do great work is to love what you do. If you haven't found it yet, keep looking. Don't settle. As with all matters of the heart, you'll know when you find it. And, like any great relationship, it just gets better and better as the years roll on. So keep looking until you find it.

Don't settle."

Steve Jobs

#### Abstract

The increasing demand for new functionalities in current and future hard real-time embedded systems, like the ones deployed in automotive and avionics industries, is driving an increment in the performance required in current embedded processors. Multicore processors represent a good design solution to cope with such higher performance requirements due to their better performance-per-watt ratio while maintaining the core design simple. Moreover, multi-cores also allow executing mixed-criticality level workloads composed of tasks with and without hard real-time requirements, maximizing the utilization of the hardware resources while guaranteeing low cost and low power consumption.

Despite those benefits, current multi-core processors are less analyzable than single-core ones due to the interferences between different tasks when accessing hardware shared resources. As a result, estimating a meaningful *Worst-Case Execution Time* (WCET) estimation – i.e. to compute an upper bound of the application's execution time – becomes extremely difficult, if not even impossible, because the execution time of a task may change depending on the other threads running at the same time. This makes the WCET of a task dependent on the set of inter-task interferences introduced by the co-running tasks. Providing a WCET estimation independent from the other tasks (*time composability* property) is a key requirement in hard real-time systems.

This thesis proposes a new multi-core processor design in which time composability is achieved, hence enabling the use of multi-cores in hard real-time systems. With our proposals the WCET estimation of a HRT is independent from the other corunning tasks. To that end, we design a multi-core processor in which the maximum delay a request from a  $Hard\ Real$ -time  $Task\ (HRT)$ , accessing a hardware shared resource can suffer due to other tasks is bounded: our processor guarantees that a request to a shared resource cannot be delayed longer than a given  $Upper\ Bound\ Delay\ (UBD)$ .

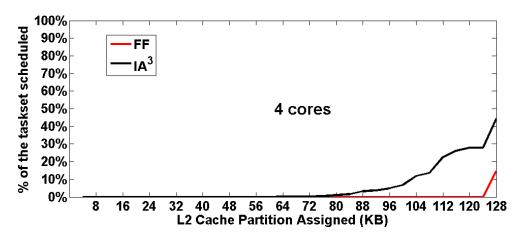

In addition, the UBD allows identifying the impact that different processor configurations may have on the WCET by determining the *sensitivity* of a HRT to different resource allocations. This thesis proposes an off-line task allocation algorithm (called IA<sup>3</sup>: Interference-Aware Allocation Algorithm), that allocates tasks in a task set based on the HRT's sensitivity to different resource allocations. As a result the hardware shared resources used by HRTs are minimized, by allowing Non Hard Real-time Tasks (NHRTs) to use the rest of resources. Overall, our proposals provide analyzability for the HRTs allowing NHRTs to be executed into the same chip without any effect on the HRTs.

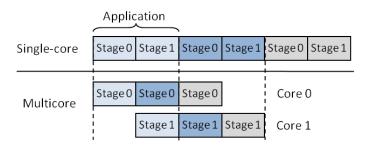

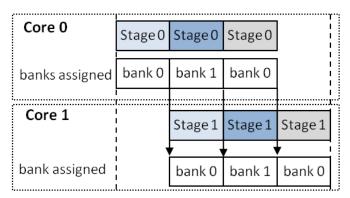

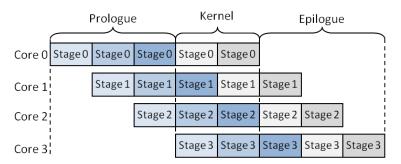

The previous first two proposals of this thesis focused on supporting the execution of multi-programmed workloads with mixed-criticality levels (composed of HRTs and NHRTs). Higher performance could be achieved by implementing multi-threaded applications. As a first step towards supporting hard real-time parallel applications, this thesis proposes a new hardware/software approach to guarantee a predictable execution of software pipelined parallel programs.

This thesis also investigates a solution to verify the timing correctness of HRTs without requiring any modification in the core design: we design a hardware unit which is interfaced with the processor and integrated into a functional-safety aware methodology. This unit monitors the execution time of a block of instructions and it detects if it exceeds the WCET. Concretely, we show how to handle timing faults on a real industrial automotive platform.

## Contents

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | Challenges of Future Hard Real-Time Systems                      | 3  |

|   | 1.2  | Possible Solutions to Achieve High Performance Guaranteeing Time |    |

|   |      | Composability                                                    | 6  |

|   | 1.3  | Thesis Contributions                                             | 8  |

|   | 1.4  | Thesis Structure                                                 | 11 |

| 2 | Exp  | erimental Setup                                                  | 13 |

|   | 2.1  | Introduction                                                     | 13 |

|   | 2.2  | Evaluation Tools                                                 | 14 |

|   | 2.3  | WCET Analysis                                                    | 19 |

|   | 2.4  | Benchmarks                                                       | 20 |

|   | 2.5  | Evaluation Criteria                                              | 27 |

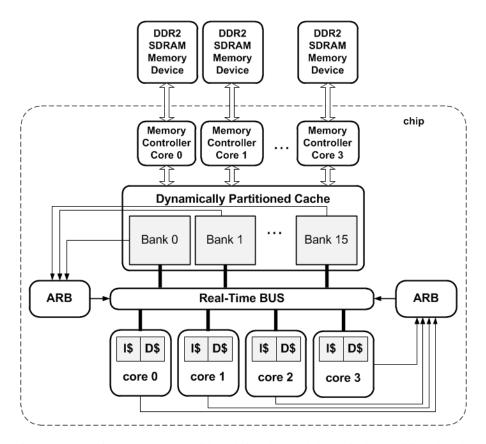

| 3 | Pred | lictable On-Chip Shared Resources: the Bus and the Cache         | 29 |

|   | 3.1  | Introduction                                                     | 29 |

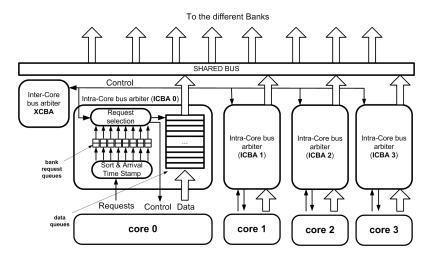

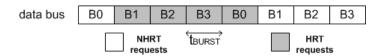

|   | 3.2  | Interference-Aware Bus Arbiter                                   | 33 |

|   | 3.3  | Analyzing the Shared Cache                                       | 38 |

|   | 3.4               | Computing a Safe WCET Estimation on multi-core Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 42  |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

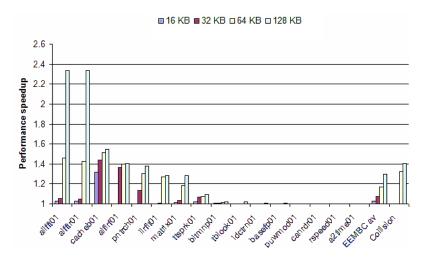

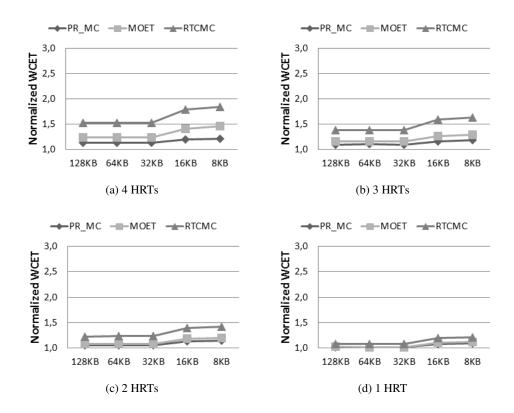

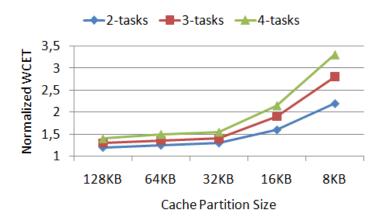

|   | 3.5               | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45  |

|   | 3.6               | Grouping Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51  |

|   | 3.7               | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53  |

|   | 3.8               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 54  |

| 4 | D                 | Patelle Off Chin Changl Danson Ale DDAM Manager Contains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| 4 |                   | lictable Off-Chip Shared Resource: the DRAM Memory System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57  |

|   | 4.1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57  |

|   | 4.2               | DDRx-SDRAM Fundamentals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60  |

|   | 4.3               | An Analytical Model to Compute the UBD of a Memory Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62  |

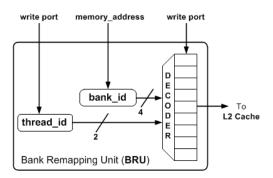

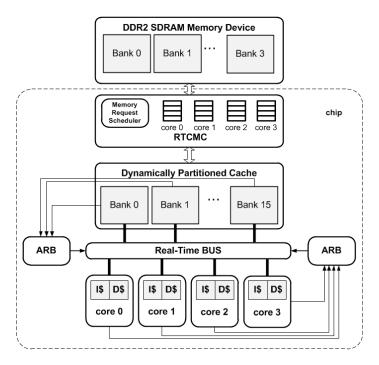

|   | 4.4               | The Real-Time Capable Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73  |

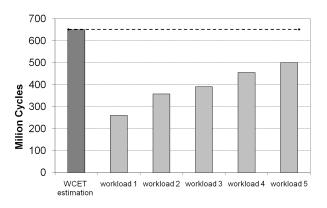

|   | 4.5               | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78  |

|   | 4.6               | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89  |

|   | 4.7               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 90  |

| 5 | IA <sup>3</sup> : | Interference-Aware Allocation Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93  |

|   | 5.1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93  |

|   | 5.2               | Our Proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97  |

|   | 5.3               | Test Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107 |

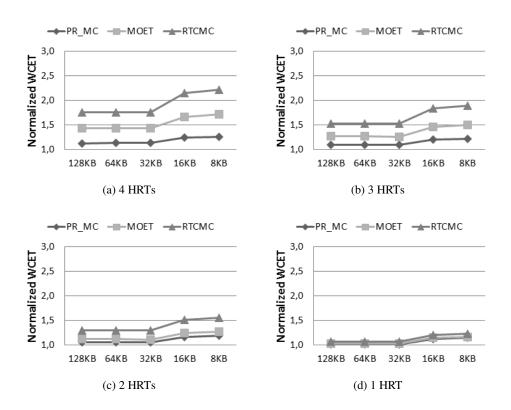

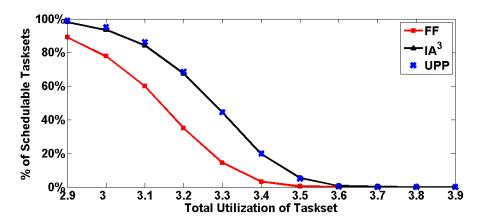

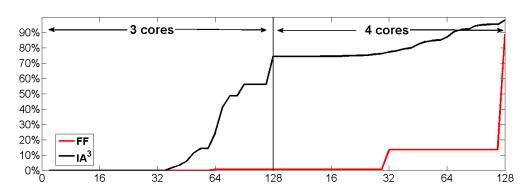

|   | 5.4               | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 109 |

|   | 5.5               | Additional Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 112 |

|   | 5.6               | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 114 |

|   | 5.7               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 116 |

| , | A TC!             | and Star Transport Day Patella Days II days Patella | 110 |

| 6 |                   | rst Step Towards Predictable Parallel Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 119 |

|   |                   | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

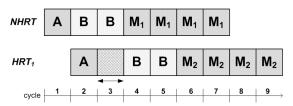

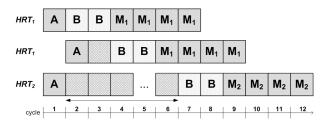

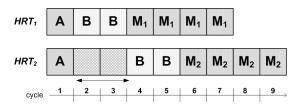

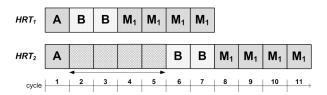

|   | 6.2               | The Software-Pipelined Parallel Programming Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|   | 6.3               | Our Proposal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 123 |

|   | 6.4               | WCET Analysis of a Software-Pipelined Parallel Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 128 |

|   | 6.5               | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 131 |

|   | 6.6               | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 134 |

| 7   | WCl    | ET On-line Monitoring in an Automotive Environment | 137 |

|-----|--------|----------------------------------------------------|-----|

|     | 7.1    | Introduction                                       | 137 |

|     | 7.2    | Background on Timing Issues                        | 138 |

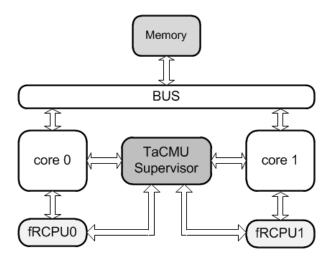

|     | 7.3    | Our Solution: the TaCMU                            | 143 |

|     | 7.4    | Results                                            | 149 |

|     | 7.5    | Related Work                                       | 151 |

|     | 7.6    | Summary                                            | 152 |

| 8   | Cone   | clusions                                           | 153 |

|     | 8.1    | Thesis Conclusions                                 | 153 |

|     | 8.2    | Future Work                                        | 156 |

| Bil | oliogr | aphy                                               | 159 |

| A   | Publ   | ications                                           | 169 |

|     | A.1    | Conferences                                        | 169 |

|     | A.2    | Journals                                           | 170 |

|     | A.3    | Workshops                                          | 170 |

|     | A.4    | Posters                                            | 171 |

|     | A.5    | Submitted Papers                                   | 171 |

| В   | Glos   | sary                                               | 173 |

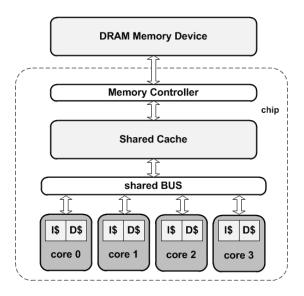

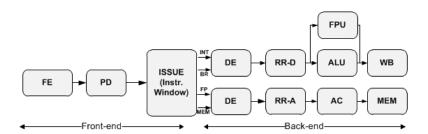

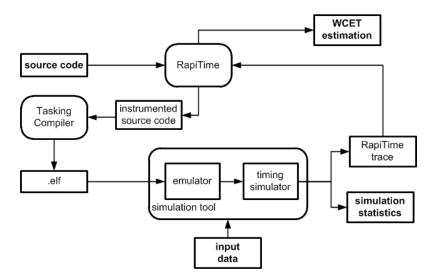

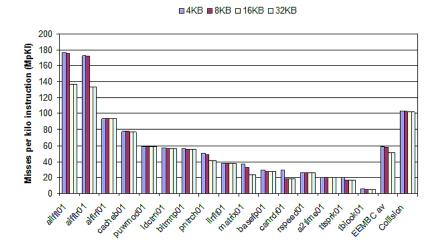

## CHAPTER 1

#### Introduction

Real-time embedded systems surround us in every-day life: they are present when we listen to music, switch on the TV, drive a car or flight on an airplane. The correctness of these systems does not only rely on the functional correctness of their operations but also on their time correctness: it is required to guarantee that the execution time of an operation never exceeds its corresponding deadline. To do so, a Worst Case Execution Time (WCET) analysis has to be derived. The WCET estimation of a task is an upper bound estimation of the maximum execution time an operation can take to execute on a specific hardware platform.

Real-time embedded systems can be classified into several categories depending on the *severity* of their time constraints; among them we identified three main classes: *hard real-time*, *soft real-time* and *firm real-time*.

• Hard Real-time systems composed of Hard Real-time Tasks (HRTs) are in charge of controlling the most critical functions of a system, e.g. the brake control system in a car and the flight control system in an airplane. HRTs must never miss any deadline, since the consequence of missing a deadline could

involve critical failures or loss of human lives. Thus, computing safe WCET estimations becomes mandatory.

- Soft real-time systems are composed by soft real-time tasks. The usefulness of a result degrades after its deadline, thereby degrading the system's Quality of Service (QoS). Hence such systems can allow missing some deadlines because the consequence is a reduction of the Quality of Service (QoS) [25] [24] [26]. Examples of soft real-time systems are video algorithms and image processing, where deadline misses involve a decreased service quality (e.g., dropping frames while displaying a video).

- Firm real-time systems are in the border between hard and soft real-time systems. An example of such systems are Software-Defined Radio applications [64]. Missing a deadline neither has catastrophic consequences like for hard real-time systems nor involves a quality of service degradation like for soft real-time systems, but it is highly undesirable and it may fail to comply with a given standard, hence being not functionally correct.

In this thesis we focus on hard real-time systems. The market for this kind of systems is really important: it has experienced unprecedented growth over the last five years and is expected to continue to grow steadily for the foreseeable future. A study performed by the international ARC Advisory Group claims that this market is expected to increase with an yearly rate of over 12% [1], reaching an overall market of \$2.5 billion in 2012. Gartner Inc. has recently reported that the semiconductor content in automotive safety systems will increase from \$2.2 billion in 2009 to \$4.3 billion in 2014 [29].

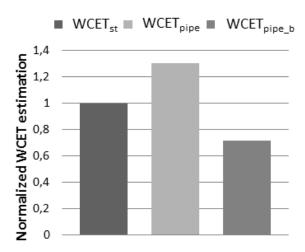

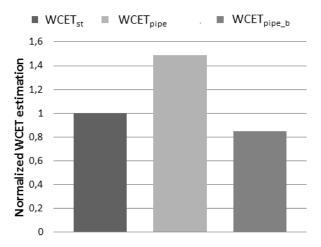

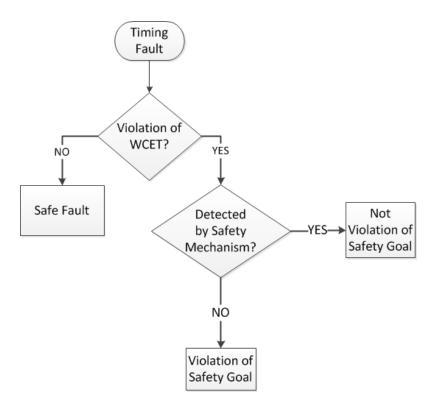

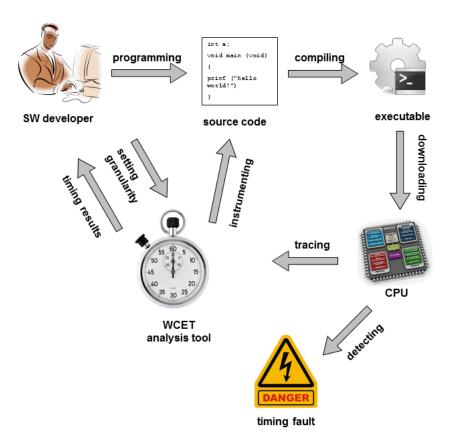

Like in any other computing system in hard real-time systems it is necessary to ensure functional correctness. In addition to that, like any other embedded system, a hard real-time system must satisfy the stringent requirements in terms of low power consumption, low cost and low weight. One of the main requirements that distinguish hard real-time systems from any other type of systems is the level of *assurance* on the functional and time correctness of the system. This additional requirement is neces-