**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

# CASTELL: A HETEROGENEOUS CMP ARCHITECTURE SCALABLE TO HUNDREDS OF PROCESSORS

## Felipe Cabarcas Jaramillo

ADVISORS:

**Alex Ramirez Bellido**

Universitat Politècnica de Catalunya

Barcelona Supercomputing Center

Mateo Valero Cortés

Universitat Politècnica de Catalunya

Barcelona Supercomputing Center

Submitted to the Departament d'Arquitectura de Computadors in partial fulfillment of the requirements for the degree of

Doctor of Philosophy on Computer Architecture at the Universitat Politècnica de Catalunya

July 2011

# **Acknowledgments**

To my advisors Alex Ramirez and Mateo Valero without their support this project had not been possible.

The help of other students was very important for me. To Pieter Bellens, for his collaboration on the CellSs. To all who have been involved on the simulator especially Carlos, Augusto and Milan.

I deliberately left Alex Rico out of the list of the simulator, because he deserves a very special mention; we have been together since the beginning, since the first week, and he has gave me hours of technical discussions and his friendship.

Thanks to Xevi, Oriol, Miquel and Alex for making lunch time enjoyable and for their friendship.

To all the projects that have gave support: the European Network of Excellence HIPEAC-2 (ICT-FP7-217068), the ENCORE project (ICT-FP7-248647) and the IBM-BSC MareIncognito project. Program AlBan, the European Union Program of High Level Scholarships for Latin America scholarship No. E05D058240CO.

Finally, to the two institutions that gave me most of the financial support: the Barcelona Supercomputing Center and the Universidad de Antioquia that also gave me the time to come to Barcelona to pursue this degree.

## **Abstract**

Technology improvements and power constrains have taken multicore architectures to dominate microprocessor designs over uniprocessors. At the same time, accelerator based architectures have shown that heterogeneous multicores are very efficient and can provide high throughput for parallel applications, but with a high-programming effort. We propose Castell a scalable chip multiprocessor architecture that can be programmed as uniprocessors, and provides the high throughput of accelerator-based architectures.

Castell relies on task-based programming models that simplify software development. These models use a runtime system that dynamically finds, schedules, and adds hardware-specific features to parallel tasks. One of these features is DMA transfers to overlap computation and data movement, which is known as double buffering. This feature allows applications on Castell to tolerate large memory latencies and lets us design the memory system focusing on memory bandwidth.

In addition to provide programmability and the design of the memory system, we have used a hierarchical NoC and added a synchronization module. The NoC design distributes memory traffic efficiently to allow the architecture to scale. The synchronization module is a consequence of the large performance degradation of application for large synchronization latencies.

Castell is mainly an architecture framework that enables the definition of domain-specific implementations, fine-tuned to a particular problem or application. So far, Castell has been successfully used to propose heterogeneous multicore architectures for scientific kernels, video decoding (using H.264), and protein sequence alignment (using Smith-Waterman and clustalW). It has also been used to explore a number of architecture optimizations such as enhanced DMA controllers, and architecture support for task-based programming models.

# **Contents**

| A  | Acknowledgments |                                                    |     |  |  |  |  |

|----|-----------------|----------------------------------------------------|-----|--|--|--|--|

| Al | ostrac          | et                                                 | iii |  |  |  |  |

| 1  | Intr            | oduction                                           | 1   |  |  |  |  |

|    | 1.1             | Motivation                                         | 2   |  |  |  |  |

|    | 1.2             | Objective                                          | 4   |  |  |  |  |

|    | 1.3             | Thesis Overview                                    | 5   |  |  |  |  |

|    | 1.4             | Document Structure                                 | 6   |  |  |  |  |

|    | 1.5             | Historical Context                                 | 6   |  |  |  |  |

| 2  | Prog            | gramming Model                                     | 9   |  |  |  |  |

|    | 2.1             | State of the Art                                   | 9   |  |  |  |  |

|    | 2.2             | OmpSs                                              | 10  |  |  |  |  |

|    |                 | 2.2.1 Irregular task dependence graph applications | 10  |  |  |  |  |

|    |                 | 2.2.2 CellSs                                       | 11  |  |  |  |  |

|    | 2.3             | Conclusions                                        | 12  |  |  |  |  |

| 3  | Cast            | tell                                               | 13  |  |  |  |  |

|    | 3.1             | State of the Art                                   | 13  |  |  |  |  |

|    | 3.2             | The Castell Architecture                           | 15  |  |  |  |  |

|    |                 | 3.2.1 Master processors                            | 16  |  |  |  |  |

|    |                 | 3.2.2 Worker processors                            | 16  |  |  |  |  |

|    |                 | 3.2.3 Shared Last Level Cache                      | 17  |  |  |  |  |

|    |                 | 3.2.4 Memory Controllers                           | 17  |  |  |  |  |

|    |                 | 3.2.5 Synchronization Module                       | 18  |  |  |  |  |

|    |                 | 3.2.6 Network On Chip                              | 18  |  |  |  |  |

|    | 3.3             | Memory Spaces                                      | 18  |  |  |  |  |

|    | 3.4             | Conclusions                                        | 21  |  |  |  |  |

| 4  | Exp             | erimental Methodology                              | 29  |  |  |  |  |

|    | 4.1             | Tasksim                                            | 29  |  |  |  |  |

|    | 4.2             | Benchmarks                                         | 34  |  |  |  |  |

#### **CONTENTS**

|   | 4.3  | Addition  | nal applications .  |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 35 |

|---|------|-----------|---------------------|-------------|---------|---|-----|------|---|---------|---|---|-------|------|

|   |      | 4.3.1     | H.264/AVC Decod     | er          | <br>    |   |     | <br> |   | <br>    |   |   |       | . 35 |

|   |      | 4.3.2     | FASTA Smith-Wat     | erman       | <br>    |   |     | <br> |   | <br>    |   |   |       | . 36 |

|   | 4.4  | Conclus   | ions                |             | <br>    |   |     | <br> | • | <br>    | • |   |       | . 36 |

| 5 | Off- | Chip Me   | morv                |             |         |   |     |      |   |         |   |   |       | 37   |

|   | 5.1  | -         | I State of the Art  |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 38 |

|   | 5.2  |           | Work                |             |         |   |     |      |   |         |   |   |       |      |

|   | 5.3  |           | cture               |             |         |   |     |      |   |         |   |   |       |      |

|   |      |           | Memory System       |             |         |   |     |      |   |         |   |   |       |      |

|   |      |           | Storage schemes     |             |         |   |     |      |   |         |   |   |       |      |

|   | 5.4  |           | of Memory Latency   |             |         |   |     |      |   |         |   |   |       |      |

|   | 5.5  | -         | of Memory Bandwa    |             |         |   |     |      |   |         |   |   |       |      |

|   | 5.6  | •         | of Memory Interlea  |             |         |   |     |      |   |         |   |   |       |      |

|   | 5.7  |           | ions                |             |         |   |     |      |   |         |   |   |       |      |

|   | 3.1  | Conclus   | ions                |             | <br>•   | • | • • | <br> | • | <br>• • | • | • | <br>• | . 42 |

| 6 |      | Level C   |                     |             |         |   |     |      |   |         |   |   |       | 51   |

|   | 6.1  | Related   | Work                |             | <br>    |   |     | <br> |   | <br>    |   |   |       |      |

|   | 6.2  | Archited  | cture               |             | <br>    |   |     | <br> |   | <br>    |   |   |       |      |

|   | 6.3  | _         | of Memory Latency   |             |         |   |     |      |   |         |   |   |       |      |

|   | 6.4  | Impact of | of Memory Bandw     | dth         | <br>    |   |     | <br> |   | <br>    |   |   |       |      |

|   | 6.5  | Cache E   | Banks               |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 57 |

|   | 6.6  | Cache I   | nterleaving         |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 59 |

|   | 6.7  | The Cac   | che as a bandwidth  | filtering . | <br>    |   |     | <br> |   | <br>    |   |   |       | . 60 |

|   | 6.8  | Conclus   | ions                |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 60 |

| 7 | On-  | Chip Syn  | chronization        |             |         |   |     |      |   |         |   |   |       | 63   |

| • | 7.1  |           | Work                |             |         |   |     |      |   |         |   |   | <br>  |      |

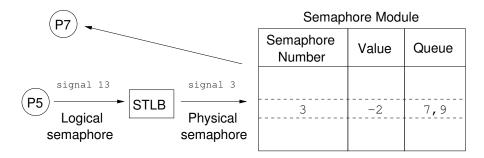

|   | 7.2  |           | re Semaphores .     |             |         |   |     |      |   |         |   |   |       |      |

|   |      |           | Virtualization      |             |         |   |     |      |   |         |   |   |       |      |

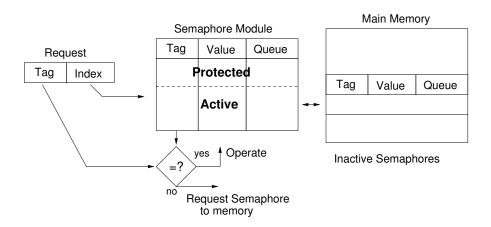

|   |      |           | Active and Inactive |             |         |   |     |      |   |         |   |   |       |      |

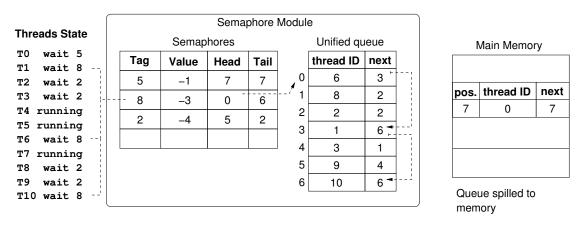

|   |      |           | Semaphore waiting   | •           |         |   |     |      |   |         |   |   |       |      |

|   |      |           | Required Hardward   |             |         |   |     |      |   |         |   |   |       |      |

|   |      |           | API                 |             |         |   |     |      |   |         |   |   |       |      |

|   |      |           | ISA                 |             |         |   |     |      |   |         |   |   |       |      |

|   | 7.3  |           | Semaphores          |             |         |   |     |      |   |         |   |   |       |      |

|   | 7.4  |           | ions                |             |         |   |     |      |   |         |   |   |       |      |

|   | 7.4  | Conclus   | ions                |             | <br>• • | • | • • | <br> | • | <br>• • | • | • | <br>• | . 02 |

| 8 | Netv | vork On   | -                   |             |         |   |     |      |   |         |   |   |       | 71   |

|   | 8.1  | Related   |                     |             |         |   |     |      |   |         |   |   |       |      |

|   | 8.2  | Design    | Space Exploration   |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 72 |

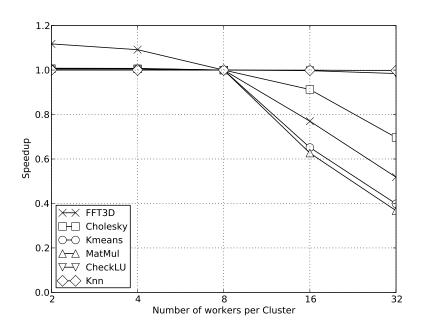

|   |      |           | Workers per Cluste  |             |         |   |     |      |   |         |   |   |       |      |

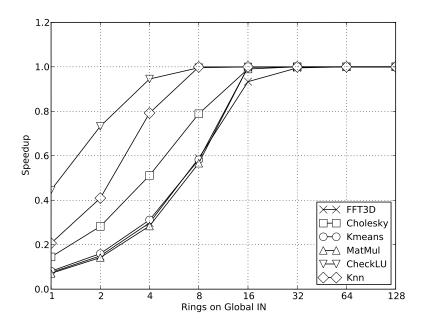

|   |      | 8.2.2     | Number of Rings     |             | <br>    |   |     | <br> |   | <br>    |   |   |       | . 73 |

|   | 0.2  | C 1       |                     |             |         |   |     |      |   |         |   |   |       | 7/   |

#### **CONTENTS**

| 9   | Rese   | arch Impact          | 7 |

|-----|--------|----------------------|---|

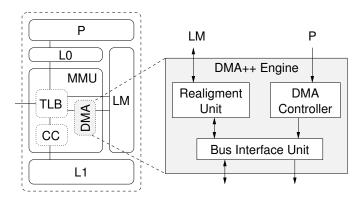

|     | 9.1    | DMA++                | 7 |

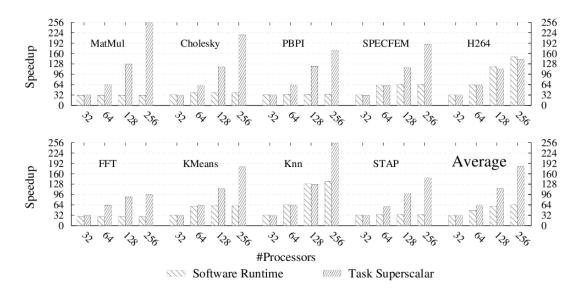

|     | 9.2    | TaskSs               | 7 |

|     | 9.3    | Bioinformatics       | 7 |

|     |        | 9.3.1 Smith Waterman | 7 |

|     |        | 9.3.2 ClustalW       | 8 |

|     | 9.4    | Conclusions          | 8 |

| 10  | Con    | clusions             | 8 |

| Bil | oliogi | aphy                 | 8 |

| Lis | t of I | ligures              | 9 |

| Lis | t of T | Cables               | 9 |

## Chapter 1

# Introduction

Hardware's natural parallelism and humans natural sequential thinking have influenced computer architecture in opposite directions. Hardware designers know that they can easily increase throughput, adding processing units to work in parallel. They also know that such systems have to be programmed, and since humans are better writing sequential than parallel programs, they have designed more sequential machines. Nonetheless, there has been some very successful parallel systems: supercomputers for large scientific applications and graphic processing units (GPUs) for computer graphics. Moreover, designers have used hardware parallelism at different levels to improve systems performance: VLIW, superscalar processors, SIMD functional units, etc. Most of the time, though, computer architects have struggled to make processors as fast as possible for sequential programs, making naturally parallel hardware behave like a sequential machine.

However, there is a paradigm shift on computer architecture from single- to multi-core<sup>1</sup> chips, motivated by the exhaustion of traditional design techniques and the increasing number of transistors available to designers. Whereas frequency scaling and instruction level parallelism (ILP) have reached their limit; Moore's law keeps motivating the industry, which keeps reducing transistor's size.

Parallel architectures are as old as computer systems; for example, early supercomputers, of the 70's, such as the CDC Star100, the Cray-I and Texas instrument's ASC were vector processors. Actually, until the introduction of microprocessors, most computing systems were parallel designs for scientific applications. Microprocessors and personal computers changed the focus of computer system designs, and for the last 40 years, computer architecture has mainly focused on sequential programs.

Chip multiprocessors (CMPs) were first proposed in 1996 by Olukotun et al.[34] in their work: "The case for single-chip multiprocessor". They observed that technology issues were going to limit performance of superscalar processors and that multi-processors were better than large uni-processors for parallel programs. They considered that simple processors could use faster clocks, and could work together to execute sequential programs as good as superscalars ones if they were faster, and could work together to execute sequential programs. Even though multi-processors have not been successful for sequential programs, most modern microproces-

<sup>&</sup>lt;sup>1</sup>Core and processor will be use interchangeably throughout this thesis to describe an independent processing element, while chip or microprocessor will be used to describe an integrated circuit that contain one or more cores.

sors contain more than one core.

From the software side, parallel applications include both sequential and parallel parts with distinct characteristics each. In general, while parallel sections are usually the raw computation with simple control flow, sequential sections contain complex control flow. Sequential sections are, usually, related with scheduling, data preparation, result management, etc. This difference between sequential and parallel sections, favors heterogeneous designs, which have processors with different characteristics.

Castell is a computer architecture framework that can integrate hundreds of heterogeneous processors in a single chip, with scalable performance for parallel scientific applications, without increasing programming effort.

#### 1.1 Motivation

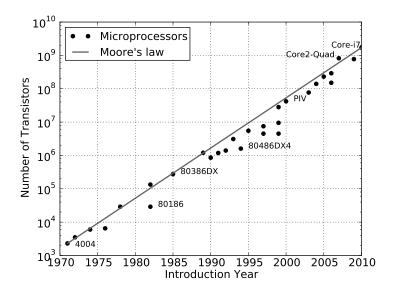

Technology improvements have been reducing the size of transistors since the 70s, providing computer architects with increasing resources to improve their designs. Figure 1.1 shows the evolution of the number of transistors per chip of Intel's microprocessors; it can be seen that the number has increased following Moore's Law: the number of transistors duplicates every 2 years. Architects have used the increasing number of transistors, for example, to increase pipeline stages for higher instruction throughput; this has made conditional branches a problem, requiring additional transistors to build better branch predictors and hardware support to recover from miss predictions. Architects have also increased the size of caches; this way applications have larger storage closer to the processors. These are two examples that shows how computer architects have traditionally used the additional transistors to increase performance.

Figure 1.1: Number of transistors evolution of Intel's microprocessors and Moore's law.

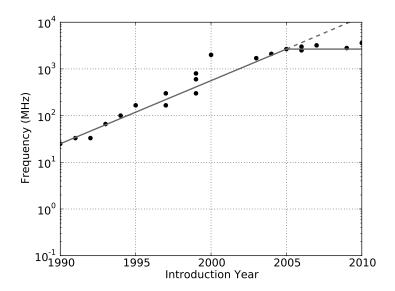

However, the key factor for the throughput increase, of the last 40 years, has been transistors speed. Technology development not only has reduced the size of transistors; it has also made them faster. Figure 1.2 shows the frequency evolution of Intel's processors from 1990 to 2010. It can be seen that the switching frequency increased constantly until 2005, but it has stopped.

Figure 1.2: Intel's microprocessors frequency evolution.

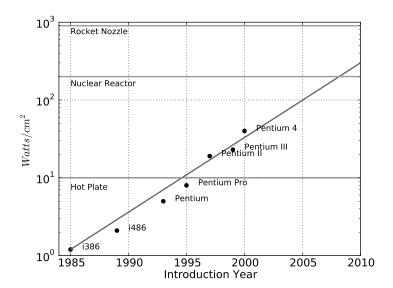

Chip manufacturers can increase the speed of transistors further, but as it can be seen in Figure 1.3, the power density was also increasing ( $P = CfV_{dd}^2$ ) with this and the size reduction<sup>2</sup>. The consequence is that chips are getting hotter and wasting more energy; furthermore, it is clear that a chip should not reach the power density of a nuclear reactor.

The question, then, is how to use the increasing number of transistors, which are not getting faster, to keep increasing throughput. The direct solution is to exploit natural parallelism of hardware. Most people in the community agree that chip multiprocessors is the solution to keep increasing performance of microprocessors. However, there is no agreement on the architecture that will be successful. Moreover, it is not likely to be a solution that fits all needs.

On one side of the spectrum we have ASICs; which are the fastest and more efficient designs for a single purpose. On the opposite side we have the general-purpose processors; which are highly programmable but not very efficient for one purpose. Midway between these two types of integrated circuits, we find special purpose processors; which are not as programmable as the general-purpose processors, but are more efficient for one purpose, even though they are not as efficient as ASICs.

Multi-core architectures proposals are as diverse as: general-purpose processors replicated several times sharing the last level cache; different types of processors with local memories and

<sup>&</sup>lt;sup>2</sup>Graph adapted from: "New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies", Fred Pollack, Intel Corporation, MICRO 32 Conference keynote, 1999.

Figure 1.3: Intel's microprocessors power density evolution.

caches; or academic ones with many processors connected with a reconfigurable connecting fabric that, at compile time, routing is created depending on the data-flow of the program [26]. As could be expected, each architecture has some advantages and some disadvantages, but in most of the cases, the performance is directly proportional to the programmability effort.

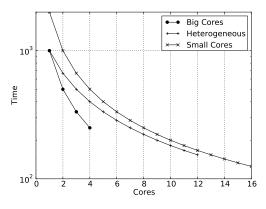

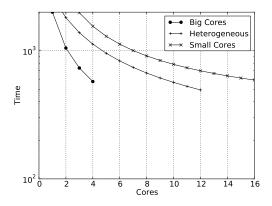

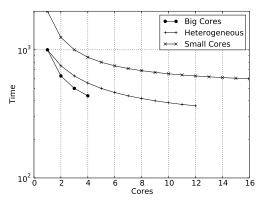

Figure 1.4, which uses Pollack's rule to compare the performance of different architectures given several application characteristics. The rule says: Microprocessor performance increase due to microarchitecture advances is roughly proportional to the square root of the increase in complexity; which basically says that doubling the number of logical units only achieves 40% improvement. It can be seen, from the Figures, that heterogeneous architectures can have similar performance to the best homogeneous architecture in different scenarios.

The purpose of this thesis is to find a design that can be as efficient as special purpose processors, but with the programmability of general-purpose ones. Besides programmability, there are several key features that limit the performance of a parallel computer system: coherency of the memory modules, memory latency, memory bandwidth, and synchronization latency. This thesis addresses all of these features.

### 1.2 Objective

The main objective of this thesis is to propose a chip multiprocessor architecture framework with the performance of special-purpose processors and the programmability of general-purpose architectures.

The architecture should be general purpose and scalable, so it can adapt to different types of requirements and the increasing number of transistors.

Given that one on the main problems of any architecture is the gap between memory and processing performance, we study and propose ways to reduce or deal with this gap.

#### 1.3 Thesis Overview

Castell is a heterogeneous multi-core architecture framework that combines general-purpose processors and accelerators with a bandwidth oriented memory system.

Software development is a problem for heterogeneous multiprocessors such as Castell. Therefore, we have chosen OmpSs, a task-based programming model, which is briefly described in Chapter 2. OmpsSs has shown promising results for parallel algorithms, providing performance and simplifying programmability—even in cases of irregular parallelism. It relies on a runtime system that, based on tasks inputs and outputs dependencies, dynamically schedules tasks depending on the available resources and manages data transfer across address spaces; this way programmers are not forced to divide the algorithms statically and decide how to schedule depending on expected resources.

With the programming model defined, we present Castell in Chapter 3. It is a combination of general-purpose processors for the runtime and accelerators for throughput computation.

In Chapter 4 we present the simulation infrastructure and the applications used to run the experiments. TaskSim provides a cycle accurate simulation infrastructure for heterogeneous multiprocessor experiments. We contributed to the design of TaskSim; which is a trace-based simulator, of multi-processor systems, that models: processors, caches, interconnection network, memory controllers, memory modules, etc.

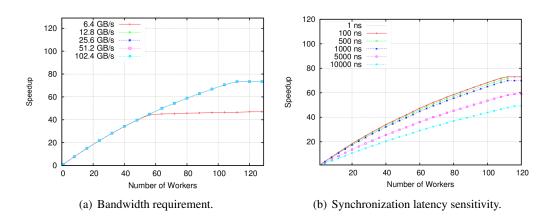

While most architectures memory systems are designed to reduce memory latency, since this is the main cause of processor stalls; Castell's memory system is designed for high bandwidth. Chapters 5 and 6 show that memory latencies, several times larger than that of current SDRAMs, do not reduce performance of applications if double buffering is used for programming (OmpSs provides the double buffering automatically); but memory bandwidth of current systems can reduce significantly the performance. This is a crucial result for Castell which determines the bandwidth oriented design.

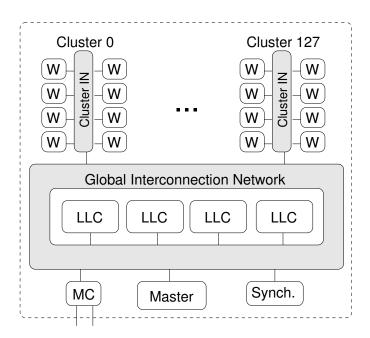

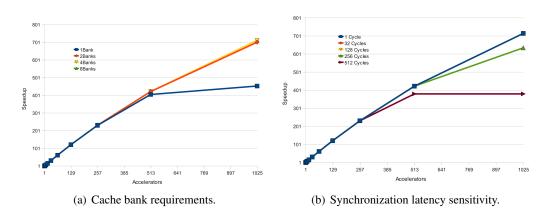

In Chapter 5 we study the storage schemes designed for bandwidth and the performance degradation of different memory interleaving. Then, in Chapter 6, we observe that the current state of the art SDRAM and number of chip pins are not enough to provide the bandwidth in the case of a 256-processor Castell, so we added a last-level cache that gives the required memory bandwidth. The bandwidth-oriented cache is distributed, shared and fine-grain interleaved, such that consecutive line-size accesses are distributed in different cache banks.

While memory latency gets hidden by the programming model and the use of the DMA engines, synchronization latency can degrade applications performance significantly on Castell. In Chapter 7, we introduce the high level synchronization mechanism of Castell: hardware semaphores. The architecture only needs to support some basic ISA instructions, in order to use this module. This hardware implementation provides the synchronization latency required.

The interconnection network on any multiprocessor is very important, since it is the way data and instructions move through the architecture. In Chapter 8 we show that the network-on-chip design is hierarchical to provide scalability and fair access to shared resources.

Finally, in Chapter 9 we present the impact of this thesis. Castell has been used to implement several parallel architectures: H.264 video decoder, Smith Waterman and ClustalW sequence aligners. It has also been used to propose hardware innovations: DMA++ a data transfer engine for unaligned transfers, and TaskSs a hardware accelerator for task management. In these works, Castell is used as the base architecture and I also provided support for simulations.

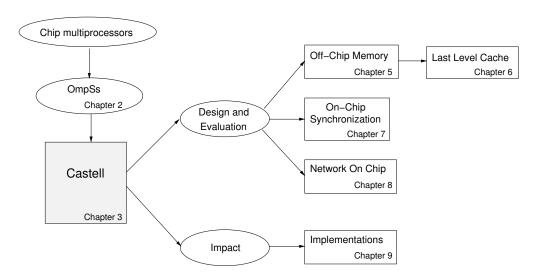

#### 1.4 Document Structure

Figure 1.5 shows the structure of the thesis. The main objective is the design of a chip multiprocessor framework, which takes us to the first issue, how to program parallel applications for heterogeneous multicores. We chose OmpSs because it is a promising parallel programming model for heterogeneous architectures. The architecture framework is presented in Chapter 3 which is a consequence of the evaluation of the following chapters.

The memory system was designed to provide high bandwidth, Chapter 5 presents the offchip memory design, and Chapter 6 the last level cache design. While the memory latency is not a problem, the synchronization latency is, so Chapter 7 presents the hardware solution. The glue to all the structures of the architecture is the interconnection which is presented in Chapter 8.

Finally, the impact of Castell is presented in Chapter 9, where we show the different implementations that have been made in our group with Castell as a framework.

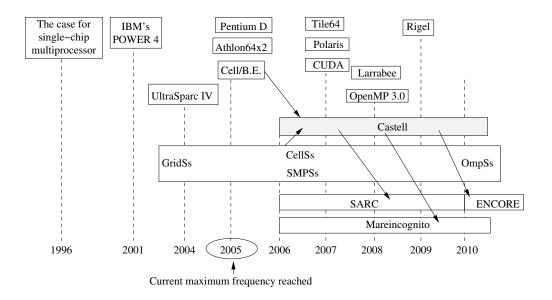

#### 1.5 Historical Context

Figure 1.6 shows a schematic view of the environment and main influences of Castell since the thesis started. The first proposal of a single-chip multiprocessor was in 1996. IBM presented the first multi-core microprocessor, the POWER 4, on 2001, when it was clear the end of frequency scaling. In 2005, Intel and AMD presented their first multi-cores, and the consortium IBM-Toshiba-Sony developed a revolutionary microprocessor architecture for the PlayStation 3 console, the Cell/B.E. It showed good performance for gaming, but what surprised more was its high performance per Watt on scientific applications.

The Cell/B.E. inspired us to design Castell with the combination of OmpSs for programma-bility. OmpSs is a programming model developed at the Barcelona Supercomputing Center for parallel applications based on OpenMP with the addition of tasks features of the CellSs. Castell has contributed to important European research projects such as SARC, ENCORE; as well as to the BSC and IBM Mareincognito project.

(a) Fully parallel code.

(b) 10 percent serial code.

(c) 25 percent serial code.

Figure 1.4: Heterogeneous versus Homogeneous cores using Pollack's rule. Assuming a fix chip area, the graphs show a performance potential for different serial and parallel code mix of applications. we compare three types of architectures: big cores, small cores, and heterogeneous.

Figure 1.5: Thesis Overview.

Figure 1.6: Castell environment and impact.

## Chapter 2

# **Programming Model**

Chip multiprocessors are becoming complex and heterogeneous, for example, Intel, AMD, NVIDIA, and IBM have microprocessors with general-purpose processors and programmable accelerators. Most of these designs target graphics with GPUs as accelerators. However, they are not easy to program.

A parallel program execution on a heterogeneous multiprocessor system not only requires the application to be divided into tasks; it also requires a correct mapping of tasks to processors, data distribution to optimize locality, task synchronization, etc. These features complicate programmability of heterogeneous systems. In this Chapter, we review OmpSs, the programming model used in this thesis and developed at the Barcelona Supercomputing Center.

#### 2.1 State of the Art

The programmability of a multiprocessor system depends on many factors, such as the number of logical address spaces, the differences between processors, but mainly on how automatic is the process of mapping the application to the hardware. In other words, how much help the compiler requires, from the programmer, to generate code that efficiently uses the underlying hardware.

Large multiprocessor systems, such as supercomputers, are mostly programmed using the message passing interface (MPI) API. In these systems, with distributed memory, programmers not only have to divide applications in tasks, but they also have to distribute data to program messages for synchronization.

Shared memory systems are usually programmed using either OpenMP or Pthreads. OpenMP has been a successful API for shared memory model multiprocessor architectures in scientific applications. Based on compiler directives, it generates parallel loops, performs the required thread creation, and synchronization. While OpenMP is very good for regular applications, Pthreads is used for more irregular parallel applications. Pthread is a low-level API for thread creation and management. The programmer has to decide how to divide the application, launch tasks and synchronize them.

OpenMP 3.0 increases the parallelism that can be expressed with older versions. In addition to parallel loops, it allows parallel tasks. Therefore, independent tasks can be executed in parallel. However, OpenMP 3.0 still requires that tasks are independent. Prior to OpenMP 3.0,

Cilk [5] extended C and gave the programmer the responsibility of expressing all parallelism and how tasks interact, the runtime was responsible for scheduling only.

Another important example is the unified parallel C (UPC), a low-level C programming extension. The programmer sees a single shared address space which is partitioned, and variables are associated with the physical threads. UPC is an implementation of a Single Program Multiple Data (SPMD) computation model, but the parallelism is statically distributed at the beginning of the execution.

The above examples, are some of the most common parallel programming tools, but the availability of parallel systems has increased the number of programming libraries, APIs, languages and models. For example, Sequoia is a parallel programming language that exposes the memory hierarchy to the programmer. This can also help creating very efficient programs, but it requires the programmer to divide the application and to map it to the underlying hardware.

The use of the Cell/B.E. [16] and GPUs for scientific applications has motivated the creation of programming models for heterogeneous architectures. For example, NVIDIA created the CUDA platform to use their GPUs as GPGPUs. CUDA extends C for NVIDIA's GPUs; it takes care of many of the low-level details of the architecture. However, CUDA still requires programmers to divide the application to map the underlying hardware which sometimes is not trivial.

In the case of the Cell/B.E., its Cell SDK contains a C library that requires programmers to manage almost every aspect of the underlying hardware: thread creation and management, data transfer between processors, synchronizations, management of private memories, etc. However, as in the case of GPUs, there are several higher level libraries and programming models that use the low-level libraries and present users a simplified interface. CellSs [4] is one of these proposals. In CellSs, programmers divide applications into tasks and the runtime takes care of task dependencies, data transfers, and task scheduling to available processors.

OmpSs combines ideas from CellSs, SMPSs, GPUSs, ClusterSs (which we refer as StarSs) and OpenMP; it allows users to exploit both loop parallelism and task parallelism using the compiler and runtime; the result is that it takes care of the hardware details and managing parallelism.

## 2.2 OmpSs

OmpSs is a task-based programming model for heterogeneous multiprocessors systems. It extends OpenMP 3.0 with all the features of the StarSs data-flow programming model. StarSs is the generic name for the different architecture-dependent data-flow programming models developed at the Barcelona Supercomputing Center (BSC). They include SMPSs (for homogeneous shared-memory architectures), CellSs (for the Cell/B.E.), GPUSs (for Nvidia GPUs), and ClusterSs (for distributed memory clusters).

#### 2.2.1 Irregular task dependence graph applications

An important feature of task-based programming models is their ability to extract parallelism from applications with a complex (or irregular) dependence graph between tasks.

Cholesky decomposition is an operation over a symmetric, positive-definite matrix. It converts a matrix into the product of a lower triangular matrix and its conjugate transpose.

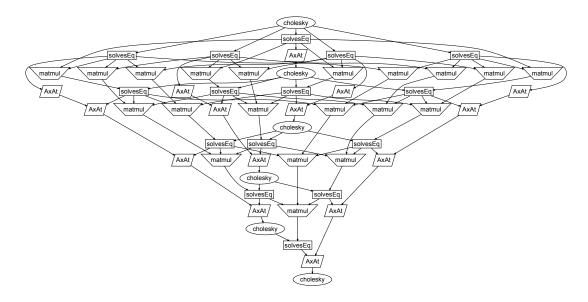

Figure 2.1: Inter-task dependence graph of a small 6x6 Cholesky decomposition.

Figure 2.1 shows the very irregular inter-task dependence pattern of a block-partitioned form of a  $6 \times 6$  block Cholesky decomposition. However, coding such dependence pattern in the OmpSs programming model is fairly simple, since the dependence graph is dynamically built by the runtime library, and the parallelism is dynamically detected and exploited.

The available parallelism in Cholesky depends on the maximum width of the graph, and diminishes when the algorithm progresses.

#### 2.2.2 CellSs

CellSs is a programming model for the Cell/B.E. which allows users to write sequential programs with a single address space. Programmers have to divide the application in tasks that can be executed on the synergistic processing elements (SPEs), but most hardware features are hidden to the users. CellSs consists of a source-to-source compiler and a supporting runtime library. The compiler translates C code, with annotations of tasks' inputs and outputs, into a standard C code with calls to the supporting runtime library.

The runtime system manages data and task scheduling without any explicit programmer intervention. This is similar, in spirit, to out-of-order (OOO) processors that automatically detect data dependencies among multiple instructions, build the dynamic data-flow graph, and dispatch instructions to multiple functional units. In CellSs, the data flow graph is not bounded by the instruction window, the granularity of instructions is much larger, and it does not require in-order commit to support precise exceptions as in OOO.

Moreover, the use of a software runtime manager provides flexibility to the programming model, as it is shown with the OmpSs extensions, since the architecture can change without having to change the program. However, an evaluation of the required speed of the runtime system for the architecture is beyond the scope of this work, but, as shown in Etsion et al. [13] and Kumar et al. [23], hardware acceleration of the runtime manager's critical sections is desirable for certain applications and specially as the number of workers increase.

This class of programming models is very flexible because the runtime knows about data dependencies. The use of the task graph at run-time allows the scheduler to reduce the system's memory bandwidth by making locality-aware dispatch decisions, as well as hide memory latencies by planning data transfers ahead of time, automatic double buffering.

As will be shown in Chapters 5 and 6, the ability of the runtime system to overlap data transfers with computation (double-buffering) using the DMA controllers, allows applications in Castell to tolerate very high memory latencies (up to thousands of CPU cycles), which permits designing a memory hierarchy that prioritizes bandwidth over latency.

#### 2.3 Conclusions

Heterogeneous multiprocessor systems require new parallel programming models. OmpSs can handle the increasing heterogeneity of these systems, as it presents programmers with a sequential view of the programs and let the runtime handle the parallelism and hardware features that are critical for performance.

Software should opportunely use hardware features like DMA engines, synchronization mechanisms, or cache size for efficient execution. By making the runtime take care of these features, OmpSs has to be tuned for each architecture, but relieves programmers and compilers of these performance-critical operations. Moreover, it also can manage optimization decisions like double buffering—which are critical for performance in some systems. This way the programmer can concentrate on dividing the code in tasks that can be parallel and keeping the code correct.

## Chapter 3

# Castell

On-chip parallel computation is currently the preferred solution to increase microprocessors raw processing performance, within a given power budget [33]. However, chip multiprocessors (CMPs) struggle with programmability and scalability issues such as cache coherency, off-chip memory bandwidth and latency.

Heterogeneous multiprocessor systems as GPGPUs and the Cell/B.E. can obtain close to peak performance in parallel applications, and very high performance per Watt compared to SMP systems, due to the efficient use of their special purpose accelerators. Castell takes the best from these systems and the best from the symmetric multiprocessor (SMP) systems—their programmability—to create an architecture that it is scalable and easy to program.

#### 3.1 State of the Art

We can classify multiprocessor systems from the point of view of the similitude of their components in two types: homogeneous and heterogeneous. All processors architecture is the same in homogeneous systems. While processors, in heterogeneous systems, can have different ISA, different memory hierarchy, different processing units, etc.

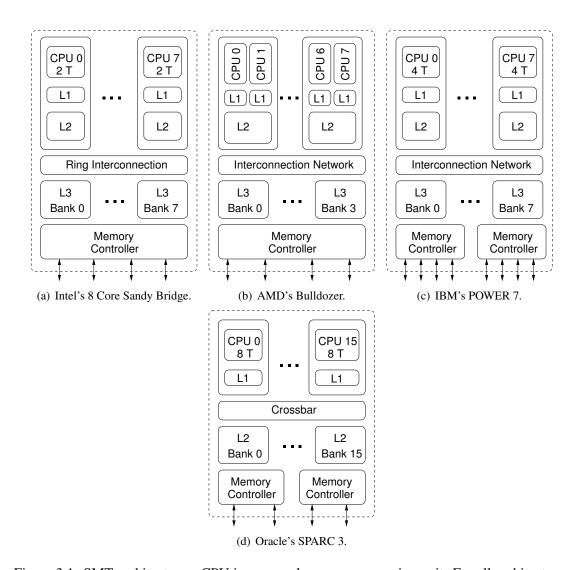

In general, as Figure 3.1 shows, in homogeneous architectures or symmetric multiprocessors (SMP) there are several processors (all the same) connected together to the last-level cache through an interconnection network.

Most chip manufacturers offer, at least, one SMP system, below we show their main characteristics:

- Intel's Sandy Bridge (Figure 3.1(a)) contains up to 8 superscalar cores. Each core is dual threaded and has a private L1 and L2 Cache, while the L3 is shared. The cores are connected with a 4 ring interconnect: request, snoop, acknowledge and a 32B wide data ring. The caches are snooped coherent. The L3 is inclusive (valid bits for the L2's), distributed and partitioned with one slice of the L3 cache for each core. The address mapping uses a single hash function, but all cores can access the entire L3.

- AMD's Bulldozer (Figure 3.1(b)) contains up to 8 superscalar cores, organizes in pairs, called modules. Each module contains 2 cores that share the L2, a large floating point unit

and the SIMD, but each contains its own private L1. The L3 is shared by all modules. The module as an entity is not visible by the OS. The L1's are write-through.

- IBM's POWER 7 (Figure 3.1(c)) has 8 cores. The processors are 4-threaded simultaneous multithreaded (SMT). Private L1 and L2 caches per core while the the L3 is shared. The L3 management moves data to the closest region to a core automatically to reduce latency through different mechanisms: data can be cloned in several regions for shared data, and data can also be protected, mark as private to a core.

- Oracles's SPARC T3 (Figure 3.1(d)) contain 16 cores. The cores support 8 physical threads. The L1 cache is private per core, while the L2 cache is distributed (fine-grain interleaved) and banked.

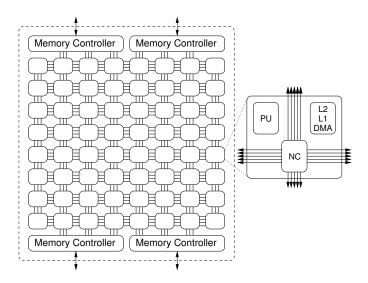

- Tilera's Tile64 (Figure 3.2) contains 64 (simple 32bit RISC VLIW) cores. Figure 3.2 shows the 2D mesh of tiles architecture. Private L1 cache and L2 cache, but the collections of L2s create a logical distributed L3 cache. Each Tile also contain a 2D-DMA engine that can be used for transfers between memory-cache, cache-memory or cache-cache.

All of these processors contain one or more memory controllers, and they have a single address space.

On the other hand, there exist many heterogeneous multiprocessors systems; for example, the systems-on-a-chip (SoC) or embedded systems used for applications like hand-held devices. Given that they are battery-powered, they have to be very efficient. Most of them include a simple general purpose processor and a set of accelerators for image or audio processing, data compression and communication accelerators. However, they are not used, at least not now, for high-performance application. The exceptions are NVIDIA's GPUs and the Cell/B.E. designed with the same philosophy as the others, but their high performance encouraged scientists to used them for parallel applications.

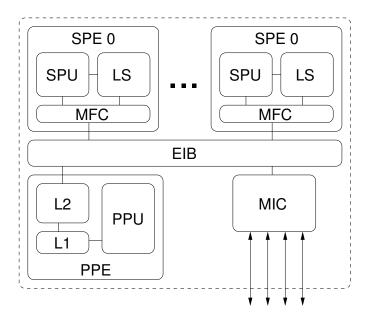

Figure 3.3 depicts an architecture view of the Sony-Toshiba-IBM Cell/B.E. [16]. It was the first commercial product to include a general purpose superscalar processor and highly programmable accelerators on a single chip. It contains a general-purpose processor (PPE), and 8 vector processors (SPEs). While the PPE has a regular memory hierarchy with coherent L1 and L2 caches, the SPEs' only see their non-coherent private memories (or LS)—storing both instructions and data. The SPEs use a DMA controller (MFC) to access the memory system. All processors, SPEs and PPE, are connected through a single 4-ring interconnect (EIB) to the memory controller (MIC).

GPUs are designed for graphic acceleration with different vendors designs being very similar. They contain tens of simple processors that work with the same program counter, with limited data sharing between different processing threads, and some special functional units (shared by several processing units) for texture computation. GPU systems require a general-purpose processor to run the OS and schedule work into the GPUs. The GPUs and the general-purpose processor have different address spaces, with a DMA engine on the GPU that can asynchronously transfer data between the two address spaces.

The most interesting GPU from the point of view of general-purpose processing is NVIDIA's Tesla (Figure 3.4), which can be programmed using CUDA. Programs are divided into a very

large number of threads, which are split in blocks that run the same kernel. Within a block, threads can communicate using shared memory, but threads between blocks can only communicate through global memory and atomic operations. Furthermore, the L2 is very small in relation to the number of processors that can run simultaneously, so its objective is to reduce latency for shared data when used close in time.

Beside the SMP version of Intel's Sandy Bridge, there is a version with a GPU integrated. In this version, the L3 ways are divided in coherent and no coherent, for the CPUs and GPUs respectively. The coherency of the GPU data must be enforced by software, and data can be shared between different domains with synchronization instructions. This is similar to NVIDIA's Tegra 2 and AMD Fusion processors. Tegra 2 combines a dual core ARM Cortex-A9 with a GPU, and a set of accelerators for video, audio, imagine and display. AMD Fusion processors combines AMD general-purpose processors with ATI's GPUs.

We summarize the characteristics of homogeneous and heterogeneous systems in Table 3.1.

| Homogeneous                | Heterogeneous                 |  |  |  |  |

|----------------------------|-------------------------------|--|--|--|--|

| Processors all equal       | Different types of processors |  |  |  |  |

| Single address space       | Multiple address spaces       |  |  |  |  |

| Coherent cache hierarchy   | Private or no cache hierarchy |  |  |  |  |

| Low performance efficiency | High performance efficiency   |  |  |  |  |

| Easy to program            | Hard to program               |  |  |  |  |

Table 3.1: Homogeneous vs. heterogeneous systems for parallel applications.

Because computer architecture is a very dynamic research and commercial area, many things have changed since the beginning of this thesis 5 years ago:

- Only a few general-purpose processors contained the memory controller inside the chip. IBM's POWER 4 and Alpha's 21364 did have it on-chip.

- Intel and AMD processors were mainly uni-core processors (even though they had already

presented their first dual core processors), they still relied on the north bridge for memory

controller, and there was not any proposal to include a GPU inside their general purpose

processors.

- GPUs were not used for general-purpose processing and CUDA had not been released.

From academia, Castell is very similar to Rigel [22] in that both architectures have a hierarchical organization and are designed to be programmed in a task-based programming model. The main differences are: the use of local memories by Castell and only regular cache hierarchy on Rigel, and the idea of single program multiple data (SPMD) model of Rigel while Castell does not make this type of restriction on the programming model.

#### 3.2 The Castell Architecture

Castell is a heterogeneous architecture framework designed for a master-worker execution model. The design relies on performance features that task-based programming models can provide au-

tomatically. Then, Castell scalability is a consequence of the architecture design and the software using the hardware features. The programmability is left to OmpSs.

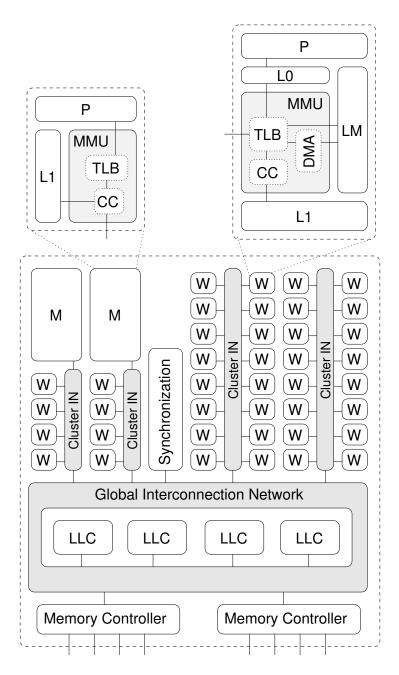

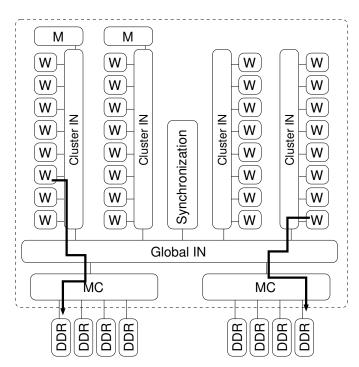

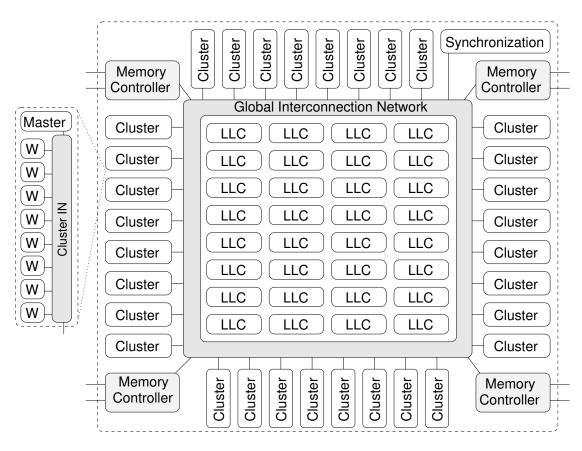

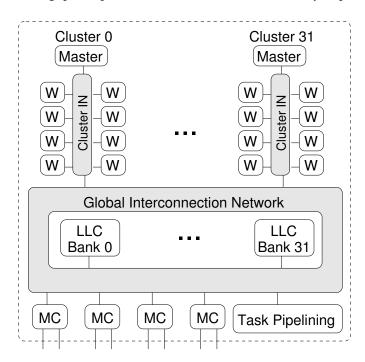

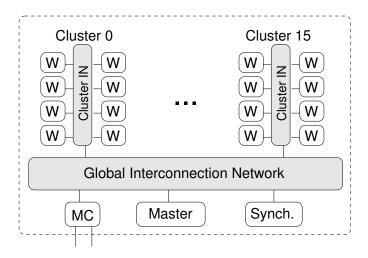

Castell consists on a combination of different processors, caches, memory controllers and a synchronization unit, connected through a hierarchical interconnection network, on a single chip. We designed Castell to be managed at runtime in a master-worker mode. Figure 3.5 shows a logical view of Castell. The (M)aster processors run the OS, the application main () routine and the runtime system. They generate tasks to be off-loaded to the specialized (W)orker processors, as indicated by a software runtime scheduler. The number of Masters and the configuration of clusters is implementation dependent.

Processors have direct load/store access to all memory locations: all scratchpad memories and the off-chip memory. In addition, processors access off-chip memory through a distributed LLC. The Workers contain a DMA controller for asynchronous data transfer between scratchpad memories and main memory that allows overlapping of data transfer and computation.

Key to Castell is the runtime management software, which detects and exploits task-level parallelism across multiple Workers much in the same way as an out-of-order superscalar processor dynamically detects instruction-level parallelism to exploit multiple functional units. This hides most of the architecture complexity, including processor diversity, DMA engines, and manual management of the scratchpad memories. The runtime ability to schedule data transfers ahead of time allows applications to tolerate long memory latencies, which led us to focus the architecture design on providing sufficient bandwidth to feed data to all Workers.

#### 3.2.1 Master processors

One of the Master processors starts applications at the main() subroutine of the program. From there, the application can spawn multiple parallel threads that the runtime allocates to other Master processors. As these processors main functionality is to spawn tasks for Workers sequentially, their single thread performance is critical to the system as a whole. Therefore, they consist of a high-performance out-of-order design [40].

Because Masters execute the software whose data access pattern is unknown at run-time—the runtime and main() are not annotated—, they only access memory through the cache hierarchy. Masters contain coherent instruction and data L1 caches with a coherency protocol to exploit locality. This allows runtime data to be close to the Masters, which combined with their OOO execution, gives them the required speed for task generation and management.

#### 3.2.2 Worker processors

In addition to the regular cache hierarchy provided to the Masters, Workers also feature a local scratchpad memory (LM). The local memories are mapped at run-time into the application's logical address space and are accessed through regular load/store instructions. This means that a memory access from a Worker has to go through the TLB in the memory management unit (MMU) in order to be steered towards the Worker local memory, another local memory, or through the cache hierarchy.

In order to avoid the latency penalty involved in sequential access to both the TLB and the local memory or the L1 cache, Workers first check a logically indexed and tagged write-through

L0 cache that behaves like a vector cache, allowing unaligned load and store operations [38]. Unaligned L0 accesses can cause two cache misses that two properly aligned L1 or local memory accesses resolve. Since both L1s and local memories only service L0 misses, they do not have to support unaligned accesses, improving their efficiency.

To avoid coherency problems, between local memories and the cache hierarchy, local memories are non-coherent, and therefore, L1 caches only capture addresses in the DRAM physical range. That is, memory address accesses to any scratchpad memory, are not cached. Further details are described below in Section 3.3.

In addition, each worker features a DMA controller to overlap data transfer and computation. The DMA controller is capable of copying data between the local memory and the off-chip memory or the other local memories.

#### 3.2.3 Shared Last Level Cache

All off-chip memory traffic goes through a distributed (or banked) shared last level cache (LLC) that captures both misses from the L1 caches, as well as DMAs transfers from/to off-chip memory.

The distributed structure of the LLC eliminates the need to maintain coherency across its blocks, since each datum is mapped to one block based on its physical address. In addition, it enables the use of fine-grain interleaving to increase cache bandwidth on accesses to consecutive addresses. Since programs use DMAs to transfer data between local memories and main memory, the LLC typically encounters coordinated accesses to multiple cache lines. Fine grain interleaving enables the cache to serve multiple parts of a single DMA request in parallel increasing the effective bandwidth observed by requester.

The distributed nature of the cache leads to a nonuniform cache access time. However, the architecture handles long (and variable) latencies without any impact on performance. Thanks to the runtime management of data transfers, applications can exploit the size and bandwidth benefits of the distributed cache without suffering any of the latency penalties.

Since the local memory addresses are not cached on the L1, the LLC only needs to maintain coherency with the Masters' L1 caches. Such coherency engine is simplified because:

- The shared LLC is inclusive.

- The LLC contains the directory state which only needs an entry line.

- The directory only keeps per-cluster presence bits, not per-L1—invalidations are broadcasted inside each involved cluster.

Chapter 6 explores the design details and performance obtained with the LLC.

#### 3.2.4 Memory Controllers

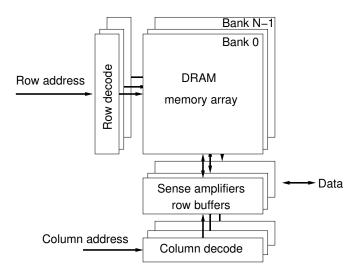

The memory controllers (MCs) connect the chip to the DRAM modules. Each MC supports several DRAM channels with request queue and FIFO scheduler per-channel. Therefore, requests to a given channel are handled in order, but they can execute out of order with respect to requests sent to other channels.

Similar to the shared cache design, the global address space is fine-grained interleaved across the different MCs. Given the bulk nature of memory accesses caused by the common use of DMA transfers, such a fine-grained interleaving provides better memory bandwidth than coarse-grained, as it parallelizes a typical DMA transfer both across MCs and channels. Further details will be presented on Chapter 5.

Furthermore, because the memory controllers interleave requests from many Workers, it is unlikely that a page buffer from a DRAM-bank will be reused for two consecutive requests. For this reason, we employ a closed-page DRAM policy [21].

#### 3.2.5 Synchronization Module

Parallel applications are usually very sensitive to synchronization latency and, therefore, hardware mechanisms are critical for CMPs; Castell is not an exception, as it is shown in Chapter 7. For an architecture with hundreds of cores, the accesses to shared resources can become a bottleneck if the synchronization mechanism is slow. Castell uses a module that implements semaphore synchronization in hardware, which are very slow in software since they require OS intervention. The proposed module allows applications and the runtime system to rely on a well-known synchronization mechanism.

#### 3.2.6 Network On Chip

In order to connect hundreds of on-chip components, Castell uses a hierarchical K-bus organization. A K-bus is a collection of buses in which a node that wants to transmit something through the network requests permission to the K-bus arbitrator. If there is no previous request for communication with the same destination port, the node is dynamically assigned to one of the buses. A 2-ring bus there can have up to 2 simultaneous data transfers in a given cycle, as long as there are no transfers to the same destination port.

As shown in Figure 3.5, we have organized Castell's Workers in clusters of 8 processors plus a Master (when needed). Each one of the clusters uses a 2-ring bus for its intra-cluster network. Each cluster has a single (full-duplex) port connecting it to the global interconnect. Further details will be presented on Chapter 8.

#### 3.3 Memory Spaces

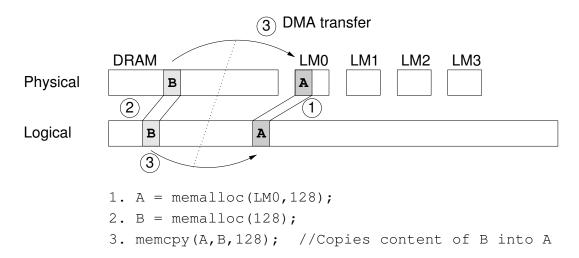

Architectures with local memories are commonly considered hard to program given that they require managing the different address spaces manually. Castell only has a single logical address space but multiple physical spaces. This simplifies programmability, as in Villavieja et al. [55], we have created a new malloc instruction called memalloc to let applications map a physical memory range of a Workers' local memory to a logical range and memopy translates to a DMA transfer, as shown in Figure 3.6. The new memalloc (LM, SIZE) allows the programmer to specify the target physical range; in Figure 3.6, A is a vector of size 128 that is allocated into the local memory 0 (LM0). Similarly, B is a vector created with a memalloc without target parameter so the physical address range of the DRAM is used, then the memopy becomes a DMA transfer from DRAM to LM0.

When a processor modifies a variable located on a local memory, the cache hierarchy is not affected because these regions are not cached. This implies that, the cache coherency traffic is low if most of the work is performed on the local memories. Even though the execution should prioritize the use of local memories to reduce cache coherency—as software banking on SMPs—, last level caches would still contain DMA traffic. Chapter 6 shows that the last level cache filters and reduces off-chip traffic. The following example illustrates the use of Castell single logical address space.

Chapter 2 introduced OmpSs, but it was mentioned that the experiments on this thesis were performed using CellSs. However, Castell's Workers contain both local memory and L1 cache and a single logical address space, but there is no architecture with these characteristics. The Cell/B.E., with programs written with CellSs, was chosen to collect the traces for the simulations and, therefore, the experiments are limited to programs that only use the local memory of the Workers. These results are valid for Castell, with both L1 and local memories, because the L1s are there to host shared variables, and their main objective is to extend the programmability of the architecture and provide backward compatibility. Note that applications can be written to use only local memories, but it is a hard limitation for the programmer or programming model.

Let's suppose we want to compute the equation

$$E = f(A, B0) + g(A, B1) + h(A, B2)$$

(3.1)

where A is a large vector (size M) that does not fit on the LLC, while B0, B1, B2, and E are vectors (size N) and all together fit on the L1 of any processor.

A parallel version of equation 3.1 can be written in OmpSs as Program 1 shows. The construct #pragma omp task includes device (CastellW) indicating that the code is to be executed on a Castell Worker. Tasks' inputs and outputs are used by the runtime to take advantage of the local memories. The memalloc allows the runtime to allocate space on the Workers local memories—renaming the output variables and making DMA transfers. Then, the local variables of the function compute do not point to main memory locations, but to local memory locations.

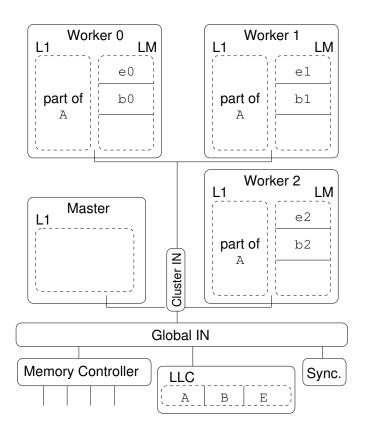

The execution of Program 1 is described in Figures 3.7 and 3.8 (which depicts a Castell implementation with one Master and 3 Workers). This example shows that the runtime can allocate and transfer data to the Workers; so programmers do not have to worry about managing the local memories, writing programs for a determined number of processors and size of local memories. The runtime allocates tasks variables in the local memoies while they fit on them.

The pseudocode on Figure 3.7 is an example of how the equation is executed on Castell, given the OmpSs code just described. Vectors B0, B1, B2, are packed on B. Figure 3.8 shows a snapshot of the state of the local memories and caches of the workers during computation. Each Worker has a local copy of the required vector (b0, b1, and b2) and a temporal buffer for their part of E (e0, e1, or e2), but they access the shared vector A (A) since it does not fit on their L1 cache. By allocating the small vectors on the local memories, and copying data to them, the vectors would be captured by the LLC, but local modifications would not generate coherency traffic. Similarly, shared vector A is present on the L1s and LLC, but it does not compete for space on the L1s with local variables. This way, the programmer knows that the variables of interest are close to the processing units, and they do not enter in conflict with the

#### **Program 1** OmpSs skeleton code to compute Equation 3.1.

```

#pragma omp task device(CastellW)

input(A) input(b0) output(e)

void f(float A[M], float b0[N], float e[N]) { }

#pragma omp task device(CastellW) \

input(A) input(b1) output(e)

void g(float A[M], float b1[N], float e[N]) { }

#pragma omp task device(CastellW) \

input(A) input(b2) output(e)

void h(float A[M], float b2[N], float e[N]) { }

#pragma omp task input(E0) input(E1) input(E2) output(E)

void sum(float E0[N], float E1[N], float E2[N], float E[N]) { }

compute (float* A, float* B, float* E)

float E0[N],E1[N],E2[N]; //temp buffers

f(A,&B[0],E0)

q(A, &B[N], E1)

h(A, &B[2*N], E2)

sum(E0,E1,E2,E)

}

```

shared variables.

#### 3.4 Conclusions

Castell uses a number of domain-specialized accelerators as Workers, to run the bulk of the application, and a few high-performance processors, as masters, to run the operating system and orchestrate the application. It contains a module for fast synchronization and a hierarchical interconnection network.

These features, combined with multiple physical, and single logical, address spaces that give users a unified memory view can be easily programmed with OmpSs. This ensures that OpenMP programs can be run on Castell and allows programmers to construct, from a familiar base, their programs.

Since the introduction of the microprocessor, general-purpose processors have dominated the market, motivated by their programmability and the constant performance increase (based primarily on frequency and the ILP). However, this increase has reached its limit, and chip multiprocessors are starting to dominate the market. Because special-purpose processors can be faster and more efficient than general-purpose processors, the increase in transistors is making multicore systems heterogeneous, to provide balance between performance and programmability. This is motivating microprocessors with different types of processors even in the personal computer market. Castell is a proposal in this direction.

Figure 3.1: SMT architectures. CPU is a general purpose processing unit. For all architectures the L1, L2 and L3 are the cache levels.

Figure 3.2: Tilera's Tile 64 microprocessor.

Figure 3.3: Cell/B.E. from Sony, Toshiba and IBM. SPE is synergistic processing element, and SPU synergistic processing unit; LS is local store; MFC is the memory flow controller, it contains the DMA controller; EIB is the element interconnect bus; PPE is the Power processing element, and the PPU is the power processing unit; MIC is the Memory interface controller.

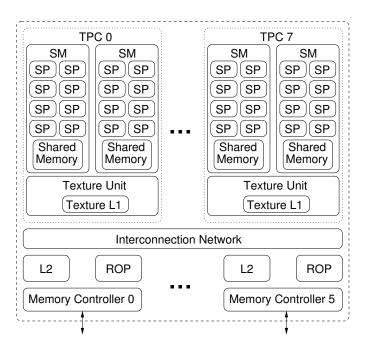

Figure 3.4: Nvidia's Tesla GPU architecture. SP are scalar processors, SM are streaming multiprocessor, ROP is raster operation processor, and TPC is texture processor cluster.

Figure 3.5: a 40-Worker Castell example. In this figure, M stands for Master, W is Worker, IN is Interconnection Network, P is processing unit, CC is cache controller, L0, L1 and LLC are cache level 0, 1 and last; MMU is Memory Management Unit, LM is Local Memory, DMA is a direct memory access unit, and TLB is the Translation Lookaside Buffer.

Figure 3.6: Castell's multiple physical and single logical memory spaces. The API is modified to allow software to indicate a physical memory target for allocation of the malloc. The copy between memory locations when there is more than one physical spaces is converted to a DMA transfer.

| Master                                                                                                                                                                                                                                                                                 | Worker 0                           | Worker 1                           | Worker 2                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|

| A=malloc(M); init(A); B=memalloc(3N); init(B); E=memalloc(N); init(E); e0=memalloc(W0,N); e1=memalloc(W1,N); e2=memalloc(W2,N); b0=memalloc(W0,N); memcpy(b0,B[0]); dispatch(T0); b1=memalloc(W1,N); memcpy(b1,B[N]); dispatch(T1); b2=memalloc(W2,N); memcpy(b2,B[2N]); dispatch(T2); | sync(b0);<br>f(A,b0,e0);<br>end(); | sync(b1);<br>g(A,b1,e1);<br>end(); | sync(b2);<br>h(A,b2,e2);<br>end(); |

| Dam (1,00,01,02),                                                                                                                                                                                                                                                                      |                                    |                                    | end (),                            |

Figure 3.7: Execution example of Equation 3.1 with the use of memalloc and memcpy on Castell. memcpy are DMA transfers and they are asynchronous, so Workers require a sync instruction before they start computing with the data being transfered. The tasks are T0, T1,T2.

Figure 3.8: State of the local memories and caches during execution of Workers' tasks of the code on Figure.

# Chapter 4

# **Experimental Methodology**

There are two elements that are almost always present in computer architecture research: a simulation infrastructure and a set of applications. Most computer architecture research requires a simulation infrastructure to run experiments because analytical modeling has not been successful predicting processors performance. This is mainly because computer programs cannot be modeled as stochastic processes. So researchers have to use simulators and real programs to test their designs. These two elements are key to research and the success of an architecture. In this Chapter, we describe the set of applications and the multiprocessor simulator (TaskSim) used in this work.

Simulators are very useful to analyze and to improve the performance of software running on well known architectures; but they are also used to predict the performance of new architectures or new features of known ones. However, as we pointed out in the Introduction, single-thread performance is no longer improving, so even though systems are getting larger and faster, simulators are not getting any faster. The problem is that simulation speed determines the size of the architectures and the level of detail at which they can be tested in a reasonable time. Therefore, existing cycle-accurate simulation infrastructures of microarchitectures can not simulate large-scale systems.

At the same time, the design of a chip multi-core system requires a detailed evaluation of the memory system, the cache contention and the interconnection network. Otherwise, simulation of downsized versions will lead to incorrect scalability assumptions. TaskSim allows us to simulate hundreds of processors in a reasonable time modeling in detail critical scalability features.

#### 4.1 Tasksim

TaskSim is a scalable event-driven simulator targeting large-scale accelerator-based architectures. For the experiments of this thesis, I have helped developing several modules; in particular, I have worked on the CPU, the cache and the DRAMs; I also helped making all modules work together and in the development of engine. The key for its scalability is the use of a task-level abstraction for accelerators simulation. Therefore, since our evaluations do not require accelerators microarchitectural modeling, we obtain cycle-accurate simulations only with the detailed simulation of data transfers and inter-accelerator synchronization on the shared resources in the architecture (caches, memory and interconnection). Because accelerators have task data loaded

in their local memories and compute only locally, external events do not interfere with task execution (task execution isolation); therefore, no detailed timing of task execution is required, only task duration from the original execution.

On top of the task-level abstraction, TaskSim is built around an event-driven simulation framework that avoids the simulation of inactive hardware components and idle time. This is accomplished by skipping *empty* cycles (cycles with no activity) and selectively executing only the hardware components with scheduled activity or receiving external requests in a given cycle. This allows TaskSim to simulate hundreds of accelerators in minutes without loss of accuracy for macro-architecture scalability studies.

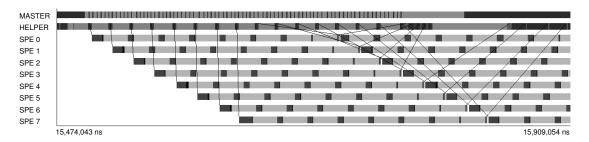

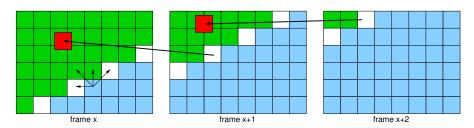

These characteristics allow TaskSim to target the simulation of large parallel applications coded in a master-worker task-offload computational model. As an example, Figure 4.1 shows a graphical representation of a chunk of a CellSs [4] application execution on a Cell/B.E. processor. Each one of the horizontal bars represents the state of an application thread along time. The different gray levels represent the computational phase types. For example, light gray on the MASTER (a thread on the PPE) is task generation, while light gray on the HELPER (another thread of the PPE) represents task scheduling. Light gray on the SPEs represents task execution. Darker grays levels in each processor type represents other execution phases. In addition, the trace contains information about the inter-task dependencies, shown as black lines between different threads. Tasksim uses all this information to schedule tasks satisfying their dependencies.

Figure 4.1: Graphical representation of a CellSs application trace from a Cell/B.E. execution. The different gray levels represent different computation phases of the processors and the black lines between processors represent communications and synchronizations.

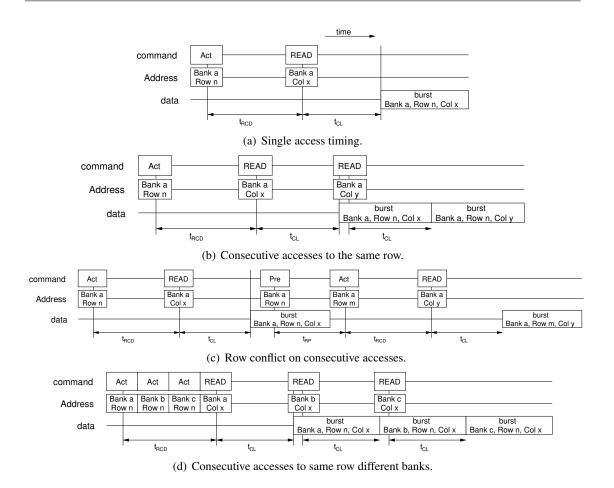

As previously mentioned, computational phases, such as task execution, are not simulated in detail. Instead, they are simulated as a single instruction with duration obtained from the trace file. However, TaskSim ignores the duration of CPU phases involving access to shared resources in the architecture, such as waiting for DMA transfers, and their duration is given by the behaviour of DMA transfer during simulation. This is obtained by a detailed simulation of DMA controllers, caches, interconnection, memory controllers, and DRAM DIMMs.

The information contained on traces allows the simulator to group all tasks on a single task list, and dynamically schedule them to the processors. The dependence information is required to verify the execution correctness, so that no task is scheduled before all its dependencies are satisfied—even though the scheduling order may differ from that of the original trace because of the increased number of worker processors.

#### **CHAPTER 4. EXPERIMENTAL METHODOLOGY**

#### Application Execution

#### TaskSim Traces

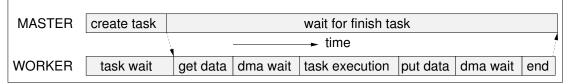

|           | MASTER                                                             |                                                               | WORKER                                                                                                                                                                                            |

|-----------|--------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL se | reate task, 30us emaphore 1 rait for finish task, 200us emaphore 2 | CPU WAIT CPU DMA GET CPU CPU DMA WAIT CPU CPU DMA PUT CPU CPU | task wait, 40us semaphore, 1 get data, 5us address, size get data, 5us dma wait, 10us  task execution, 120us put data, 5us address, size put data, 5us address, size put data, 5us dma wait, 10us |

|           |                                                                    | DMA WAIT                                                      |                                                                                                                                                                                                   |

|           |                                                                    | CPU                                                           | end, 5us                                                                                                                                                                                          |

|           |                                                                    | SIGNAL                                                        | semaphore, 2                                                                                                                                                                                      |

#### TaskSim Simulation

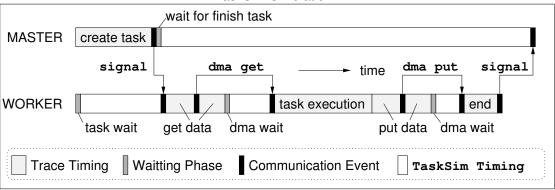

Figure 4.2: TaskSim traces and simulation example.

As can be seen in Figure 4.2, *computational phases* are execution periods happening between two communication events. Communication events can be either synchronization events (such as semaphores) or data transfers (DMA get, put, and DMA wait). Note that the name of the phase can change between communications as *task execution* becomes *put data*. However, if a Worker performs a DMA transfer in the middle of a task, we consider two separate computation phases (as in *get data* and *put data*). TaskSim makes zero all original waiting phases timings—task wait, dma wait for finish task—and simulates data transfer, and synchronization latencies reproducing the execution of the application.

The computation phase abstraction requires to get the execution duration values from different sources. We consider three different sources where they can be obtained from:

- 1 Native execution on a real system where the application is instrumented to dump computation durations to a trace file.

- 2 An off-line simulation of the accelerator microarchitecture—computation duration can be obtained from a separate cycle-accurate model of the accelerator pipeline with simulation of just one processor, not all of them.

- 3 An analytical model which allows for quick approximations based on frequency scaling, superscalar issue width, etc.

All three methods, described above, need to be combined with an application-level trace describing the inter-task synchronization and DMA transfers, so that TaskSim can rebuild the execution on the projected muticore, and model the memory and interconnection systems in cycle-accurate detail.

The biggest benefit of abstract CPU simulation is that most of the simulated time does not consume any computational resources on the host machine. This is a consequence of skipping most of the simulated cycles which correspond to computational phases of accelerators.

For example, simulating a  $4096 \times 4096$  matrix multiplication of a Cell/B.E.-like architecture incurs only a 400x slowdown compared to native execution. Moreover, simulating a target platform with 256 accelerators, 32 cache banks, 4 MICs, and 8 DRAMs (32x more processors than the Cell B.E.), is only 1.5x slower. As a result, simulation time is almost independent of the target architecture size.

#### Simulator validation

We configure TaskSim to model a single-chip Cell/B.E. system matching as close as possible its architecture, paying careful attention to the interconnection and memory parameters.

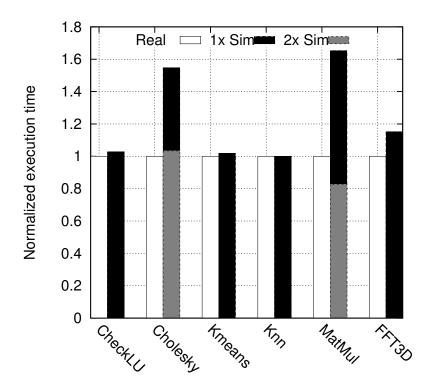

Figure 4.3 compares real execution time, on the Cell/B.E., with simulations for a set of applications. Details of the applications can be found in the following section.

The results, which are normalized to the real execution time, show an accurate simulation for most benchmarks. As mentioned before, the CPU abstraction does not introduce errors; on the contrary, it eliminates a big source of simulation error due to microarchitecture behavior simulation.

However, MatMul and Cholesky show significant differences for 1x simulation (no modification of the original phase durations is performed). The problem with these benchmarks is that

Figure 4.3: Comparison of real Cell/B.E. execution time and TaskSim simulations. 1x means that no change has been performed on the traces, while 2x means that computation phases have being speed up by this factor.

they are dominated by master thread speed. Therefore, a significant part of the prediction error is due to the execution overhead introduced by the instrumentation tracing mechanism—altering the real execution time.

In experiments where a comparison to a real execution is necessary (for a single application), we could instruct the simulator to apply a correction factor to some phases. In particular, we show simulation results for MatMul and Cholesky with a master thread twice as fast at the trace. It shows that the difference to the original is significantly reduced.

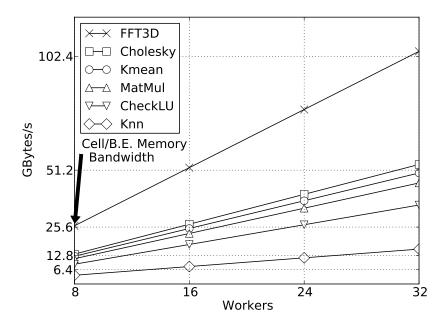

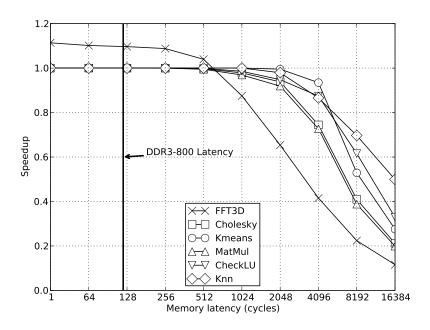

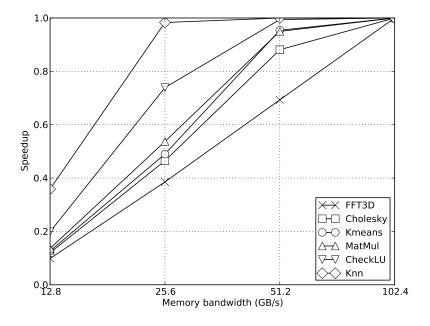

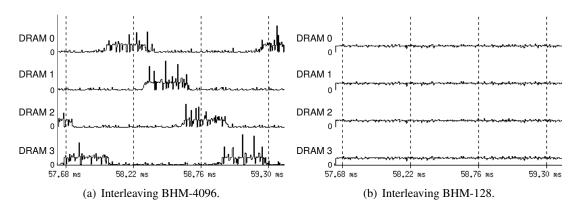

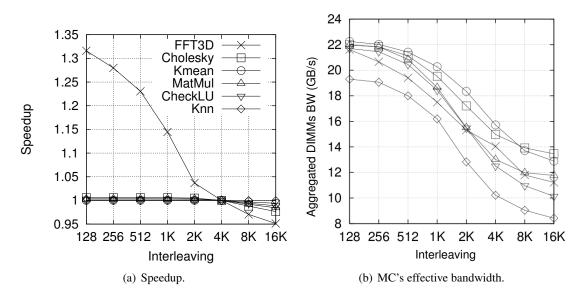

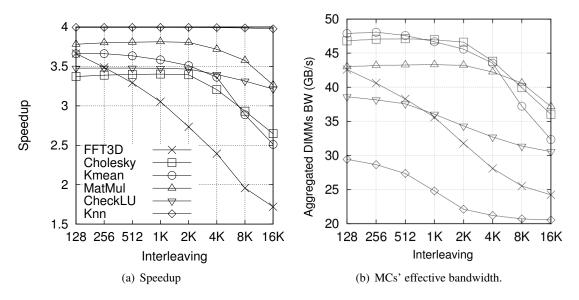

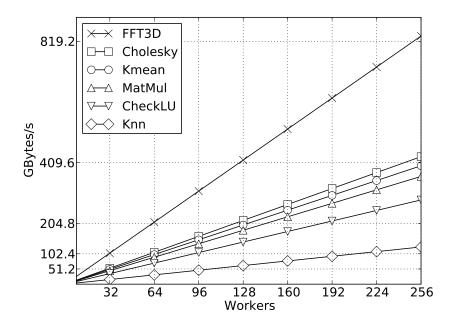

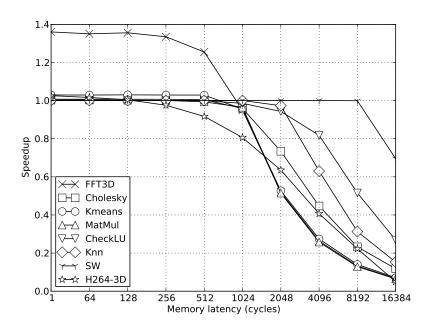

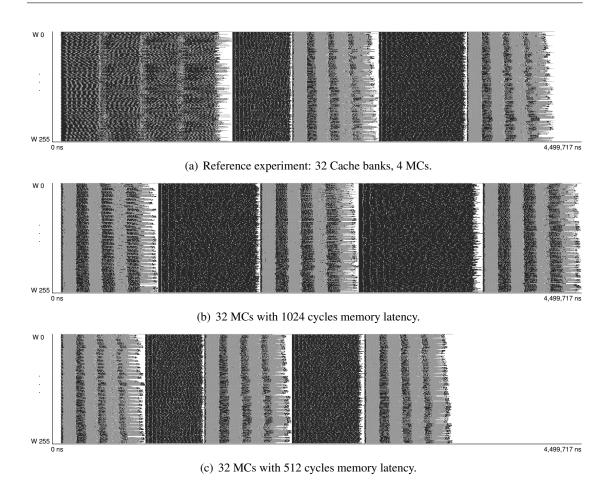

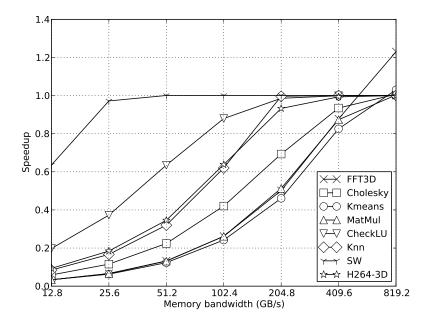

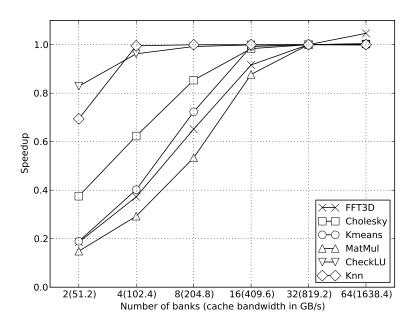

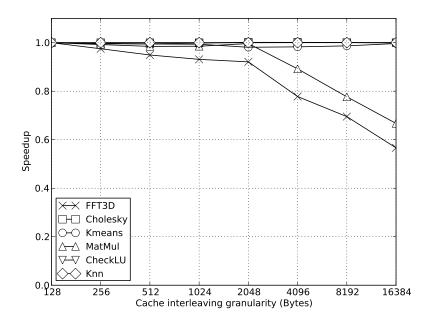

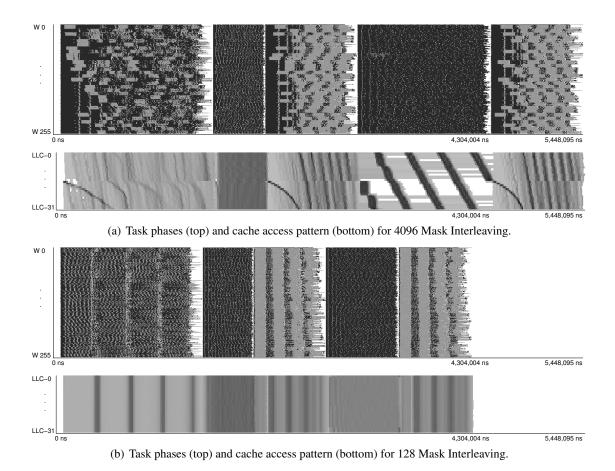

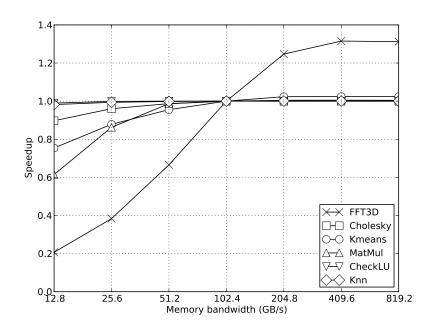

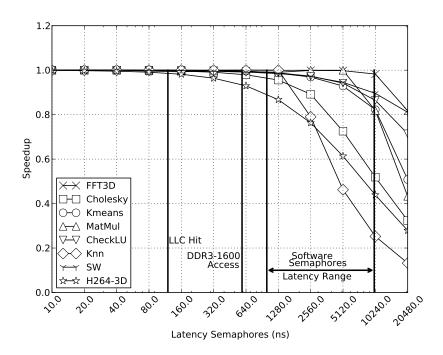

However, the important point from these results is one of the limitations of the Cell/B.E. architecture—the PPE speed.