# HARDWARE/SOFTWARE CO-DESIGN FOR DATA-INTENSIVE GENOMICS WORKLOADS

#### NICOLA CADENELLI

Dissertation submitted in partial fulfillment of the requirements for the Doctoral Degree in Computer Architecture

Universitat Politècnica de Catalunya - BarcelonaTECH

October 2019

Nicola Cadenelli: *Hardware/Software Co-design for Data-Intensive Genomics Workloads*.

Dissertation submitted in partial fulfillment of the requirements for the Doctoral Degree in Computer Architecture, 13<sup>th</sup> October 2019.

supervisors:

David Carrera

Jordà Polo

AFFILIATION:

Department of Computer Architecture Universitat Politècnica de Catalunya - BarcelonaTECH

LOCATION:

Barcelona, Spain

# COLOPHON The image in the title page is a derivative of "Hospital de Sant Pau" by Nicky Boogaard, used under CC BY 2.0. This image is licensed under CC BY 2.0 by Nicola Cadenelli. This document was typeset using the typographical look-and-feel classicthesis developed by André Miede. The style was inspired by Robert Bringhurst's seminal book on typography "The Elements of Typographic Style".

Se ghè de na, ghè de na!

Where we love is home, home that our feet may leave, but not our hearts.

— Oliver Wendell Holmes, Sr.

Since the last decade, the main components of computer systems have been evolving, diversifying, to overcome their physical limits and to minimize their energy footprint. Hardware specialization and heterogeneity have become key to design more efficient systems and tackle ever-important problems with ever-larger volumes of data. However, to fully take advantage of the new hardware, a tighter integration between hardware and software, called hardware/software co-design, is also needed. Hardware/software co-design is a time-consuming process that poses its challenges, such as code and performance portability. Despite its challenges and considerable costs, it is an effort that is crucial for data-intensive applications that run at scale. Such applications span across different fields, such as engineering, chemistry, life sciences, astronomy, high energy physics, earth sciences, et cetera.

Another scientific field where hardware/software co-design is fundamental is genomics. Here, modern DNA sequencing technologies reduced the sequencing time and made its cost orders of magnitude cheaper than it was just a few years ago. This breakthrough, together with novel genomics methods, will eventually enable the long-awaited personalized medicine. Personalized medicine selects appropriate and optimal therapies based on the context of a patient's genome, and it has the potential to change medical treatments as we know them today. However, the broad adoption of genomics methods is limited by their capital and operational costs. In fact, genomics pipelines consist of complex algorithms with execution times of many hours per each patient and vast intermediate data structures stored in main memory for good performance. To satisfy the main memory requirement genomics applications are usually scaled-out to multiple compute nodes. Therefore, these workloads require infrastructures of enterprise-class servers, with entry and running costs that that most labs, clinics, and hospitals cannot afford. Due to these reasons, co-designing genomics workloads to lower their total cost of ownership is essential and worth investigating.

This thesis demonstrates that hardware/software co-design allows migrating data-intensive genomics applications to inexpensive desktop-class machines to reduce the total cost of ownership when compared to traditional cluster deployments. Firstly, the thesis examines algorithmic improvements to ease co-design and to reduce workload footprint, using NVMs as a memory extension, and so to be able to run in one single node. Secondly, it investigates how data-intensive algorithms can offload computation to programmable accelerators (i.e., GPUs and FPGAs) to reduce the execution time and the energy-to-solution. Thirdly, it explores and proposes techniques to substantially reduce the memory footprint through the adoption of flash memory to the point that genomics methods can run on one affordable desktop-class machine.

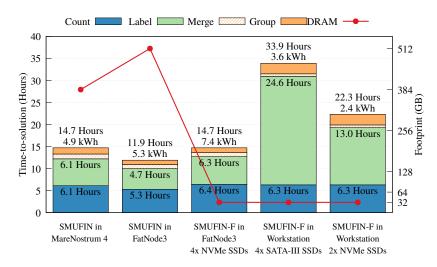

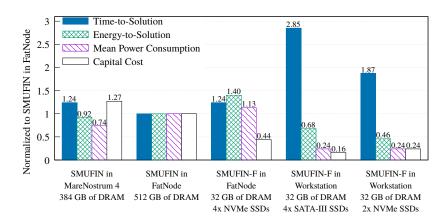

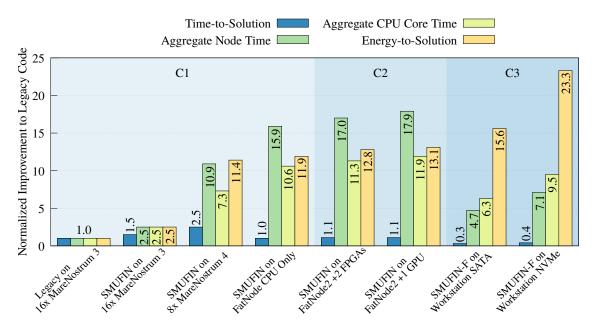

To demonstrate this thesis, we do the exercise to co-design SMUFIN, a state-of-the-art real-world genomics method that was originally deployed on 16 nodes MareNostrum 3, where, per each patient, it needed around 10 hours and 56 kWh to complete its execution. Thanks to algorithmic improvements, an NVM used as main memory extension, and accelerators, we made it possible to execute SMUFIN on one single enterprise-node with 512 GB of main memory in 9

hours and as few as 4.3 kWh, a 13.1x improvement. However, we were able to run SMUFIN on a desktop-class machine only thanks to the adoption of NVMe as an alternative to main memory. In this affordable node with a 6-core i7 and only 32 GB of main memory, SMUFIN suffers a considerable slow-down, requiring 22.4 hours, but it consumes only 2.4 KWh, a 23.3x improvement compared to the original deployment. Compared to the single enterprise-node, this desktop machine costs only 1/4 as much, and requires only approximately 1/2 of energy per patient. As a result, a cluster of multiple desktop-class machines costs half as much compared to a cluster of servers and consumes half as much energy while maintaining a similar throughput. These results prove that hardware/software co-design allows significant reductions in the total cost of ownership of data-intensive genomics methods, easing their adoption on large repositories of genomes and also on the field.

# CONTENTS

| 1  | INT  | RODUCTION                                              | 1  |

|----|------|--------------------------------------------------------|----|

|    | 1.1  | Thesis Context                                         | 1  |

|    | 1.2  | Thesis Contributions                                   | 4  |

| 2  | BAC  | KGROUND                                                | 9  |

|    | 2.1  | General Purpose Accelerators                           | 9  |

|    | 2.2  | Non-Volatile Memories                                  | 10 |

|    | 2.3  | Genomics                                               | 12 |

|    | 2.4  | The SMUFIN Method                                      | 13 |

| 3  | ALG  | ORITHMIC IMPROVEMENTS TO REDUCE WORKLOAD FOOTPRINT     | 19 |

|    | 3.1  | Refactoring Monolithic Software for Modularity         | 19 |

|    | 3.2  | Chains of Bloom filters to Identify non-unique k-mers  | 22 |

|    | 3.3  | Manual Swapping to Non-volatile Memory                 | 23 |

|    | 3.4  | Evaluation and Results                                 |    |

|    | 3.5  | Related Work                                           | 29 |

|    | 3.6  | Final Considerations                                   | 31 |

| 4  | OFF  | LOADING COMPUTATION TO ACCELERATORS                    | 33 |

|    | 4.1  | Identifying Candidates for Accelerator Offloading      | 33 |

|    | 4.2  | Virtualizing Accelerators Memory                       | 39 |

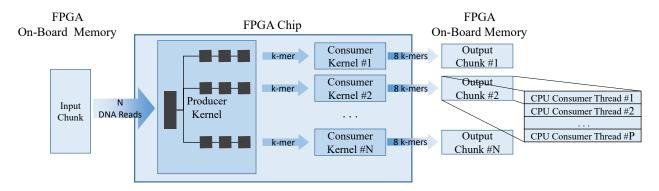

|    | 4.3  | Porting GPUs Code to FPGAs                             | 42 |

|    | 4.4  | Evaluation and Results                                 | 48 |

|    | 4.5  | Related Work                                           |    |

|    | 4.6  | Final Considerations                                   | 58 |

| 5  | MEN  | MORY FOOTPRINT REDUCTION THROUGH FLASH KEY-VALUE STORE | 59 |

|    | 5.1  | K-mer Counting with Sort-Reduce                        | 59 |

|    | 5.2  | Key-Value Store for Histogram Lookup                   | 61 |

|    | 5.3  | Splitting the Histogram Into Key-Value Cache and Store | 63 |

|    | 5.4  | Evaluation and Results                                 | 65 |

|    | 5.5  | Related Work                                           | 73 |

|    | 5.6  | Final Considerations                                   | 75 |

| 6  | CON  | ICLUSIONS AND FUTURE WORK                              | 77 |

|    | 6.1  | Conclusions                                            | 77 |

|    | 6.2  | Future Work                                            | 82 |

| BI | BLIO | GRAPHY                                                 | 87 |

# LIST OF FIGURES

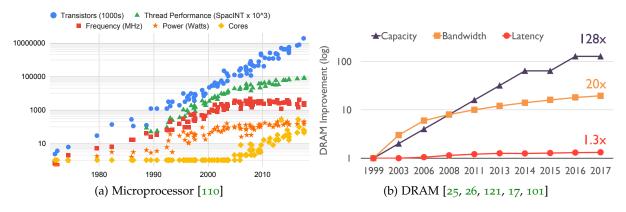

| Figure 1                                            | Microprocessor and DRAM trends in the last decades                              | 1          |

|-----------------------------------------------------|---------------------------------------------------------------------------------|------------|

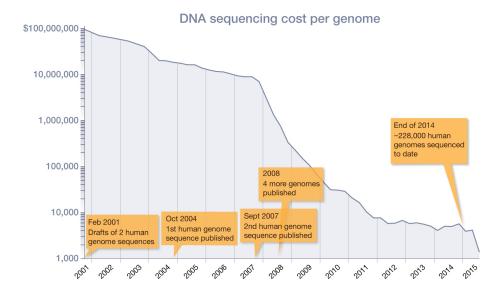

| Figure 2                                            | DNA sequencing costs and number of sequenced genomes trends in the last decades | _          |

| Eigung a                                            |                                                                                 | 3          |

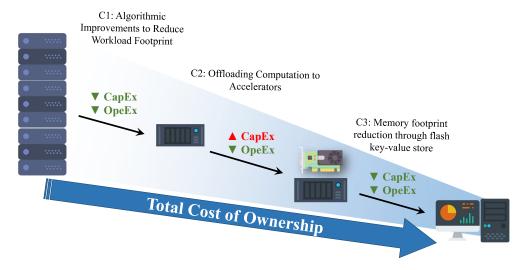

| Figure 3                                            | Graphic representation of the contributions of this thesis                      | 5          |

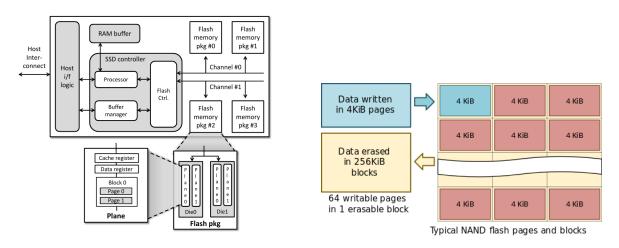

| Figure 4                                            | Internal SSD architecture and functioning.                                      | 11         |

| Figure 5                                            | Hierarchy of k-mers, stems, and roots                                           | 14         |

| Figure 6                                            | Simplified example of SMUFIN candidate break-point detection and re-            |            |

|                                                     | construction                                                                    | 16         |

| Figure 7                                            | Example result of SMUFIN showing a candidate mutation                           | 17         |

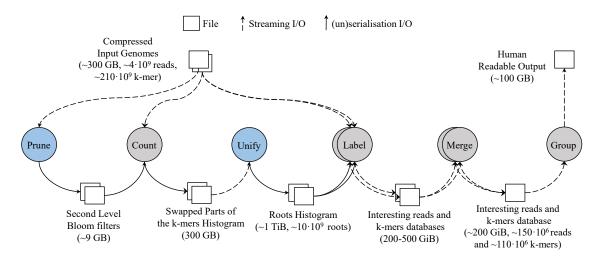

| Figure 8                                            | SMUFIN modular structure using partitions and units                             | 22         |

| Figure 9                                            | SMUFIN extended structure                                                       | <b>2</b> 5 |

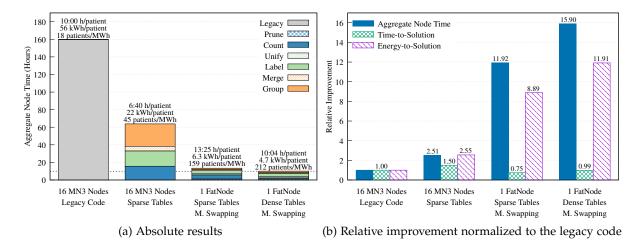

| Figure 10                                           | Aggregate node time, time-to-solution and energy-to-solution of the pro-        |            |

|                                                     | posed and legacy SMUFIN                                                         | 28         |

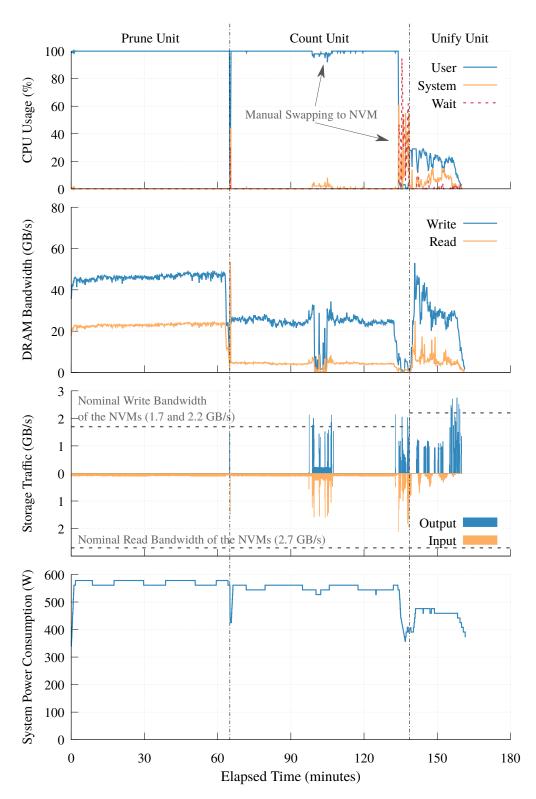

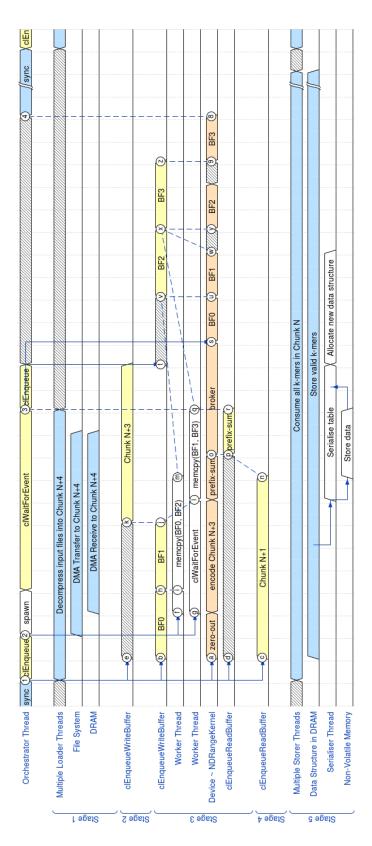

| Figure 11                                           | System traces of SMUFIN k-mer Counting algorithm                                | 30         |

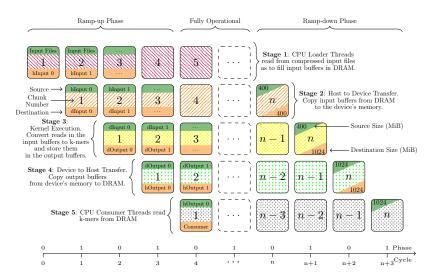

| Figure 12                                           | Double buffering pipeline used to offload computation to accelerators           | 35         |

| Figure 13                                           | Activity at every cycle of the double buffering pipeline with memory vir-       |            |

|                                                     | tualization                                                                     | 40         |

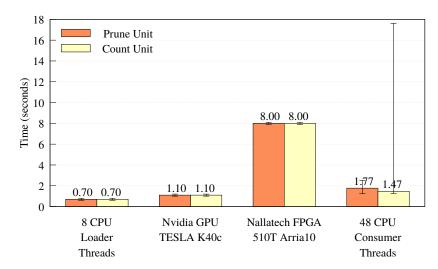

| Figure 14                                           | Performance comparison of GPU-style kernels running on GPU and FPGA.            | 42         |

| Figure 15                                           | Overview of the FPGA Producer-Consumers kernels and data flow                   | 47         |

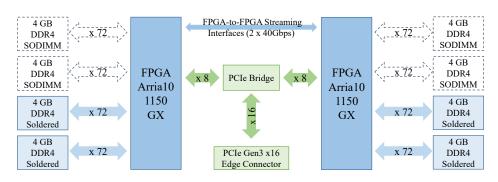

| Figure 16                                           | Diagram of the Nallatech 510T dual-FPGA board                                   | 49         |

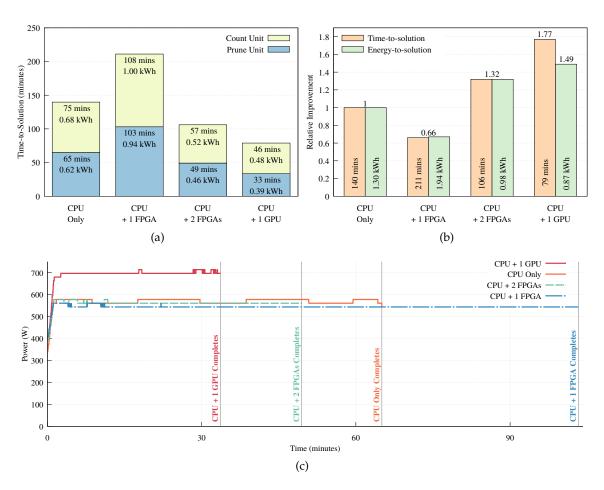

| Figure 17                                           | Time-, Energy-to-solution and Power Consumption of SMUFIN k-mer count-          |            |

|                                                     | ing algorithm with CPU and with accelerators                                    | 50         |

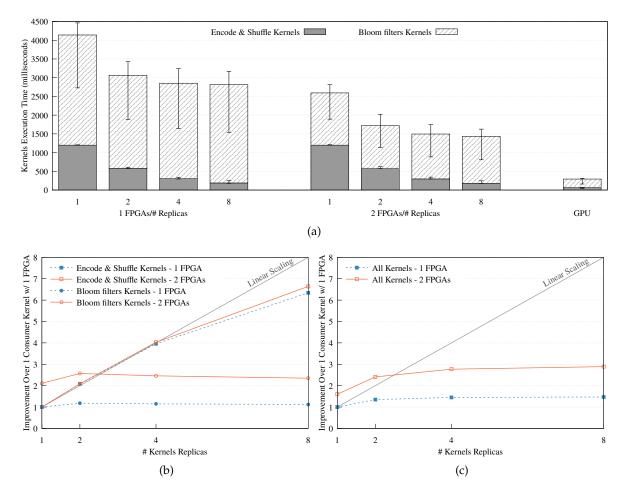

| Figure 18                                           | Performance comparison of OpenCL kernels running on FPGAs and GPU.              | 52         |

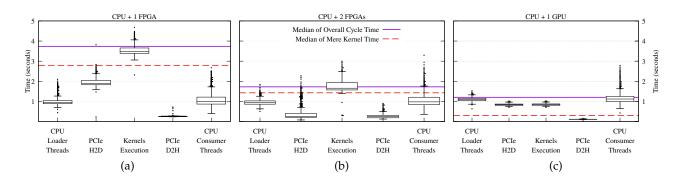

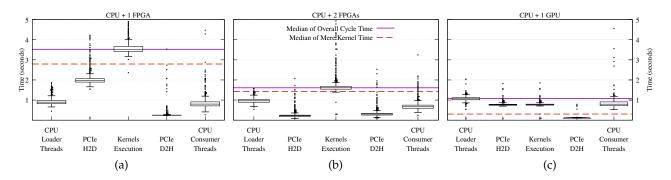

| Figure 19                                           | Distribution of execution time of each stage of the software pipeline during    |            |

| O ,                                                 | the Prune unit                                                                  | 53         |

| Figure 20                                           | Distribution of execution time of each stage of the software pipeline during    |            |

| O                                                   | the Count unit                                                                  | 54         |

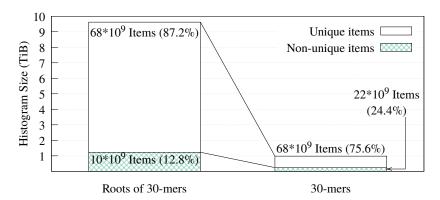

| Figure 21                                           | Size of the k-mer counting histogram using the root and k-mer format            | 61         |

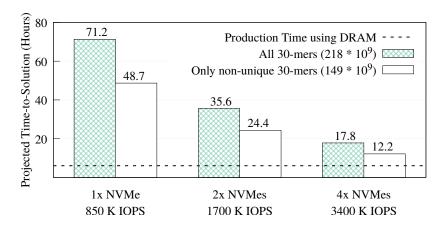

| Figure 22                                           | Projection of the time-to-solution for SMUFIN's Label unit on an hypo-          |            |

| 8                                                   | thetical RAID-0 of NVMe drives                                                  | 61         |

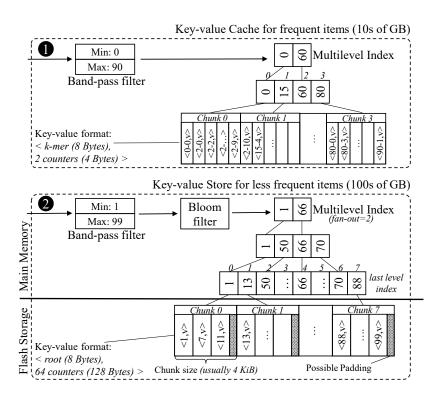

| Figure 23                                           | Example of the proposed key-value cache and store and their internal data       |            |

| - 1 <b>- 1- 1- 1- 1- 1- 1- 1- 1- 1- 1- 1- 1- 1-</b> | structures.                                                                     | 65         |

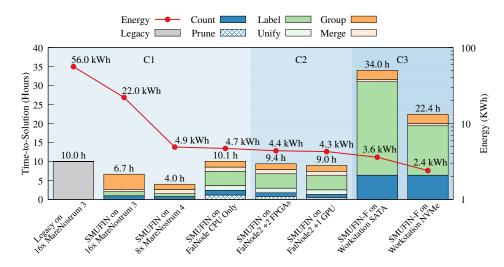

| Figure 24                                           | Time- and Energy-to-solution of SMUFIN and SMUFIN-F                             | 67         |

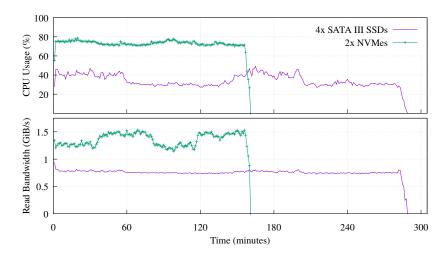

| Figure 25                                           | CPU usage and Read Bandwidth of the proposed Label unit                         | 68         |

| Figure 26                                           | Normalized time-, energy-to-solution, mean power consumption, and cap-          | 00         |

| 116410 20                                           | ital cost of SMUFIN and SMUFIN-F                                                | 60         |

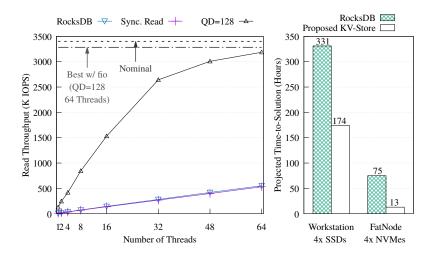

| Figure 27                                           | Throughput comparison of the proposed key-value store vs. RocksDB               |            |

| 1 15 UIC 4/                                         | THOUGHPUT COMPANION OF THE PROPOSED REY VALUE STOLE VS. INCRESOD                | / U        |

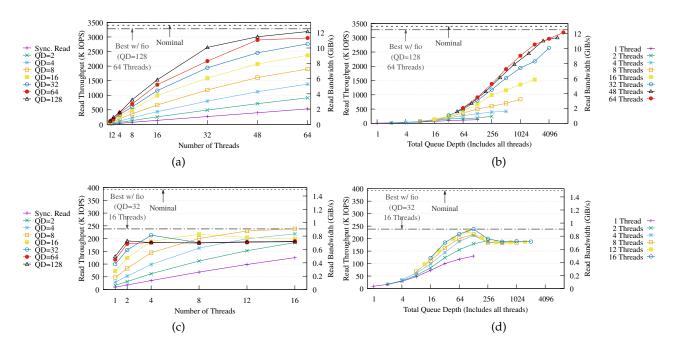

| Figure 28 | Throughput and throughput versus total queue depth of the proposed        |            |

|-----------|---------------------------------------------------------------------------|------------|

|           | KV-Store with 4x NVMes and with 4x SATA III SSDs                          | 72         |

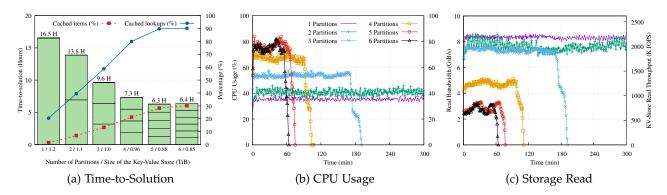

| Figure 29 | Time-to-solution, Cache Effectiveness, CPU usage, and Storage Read of the |            |

|           | proposed Label unit with 1 to 6 partitions                                | 73         |

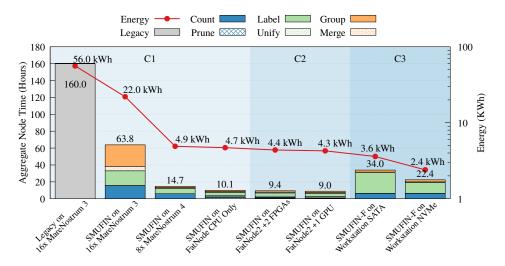

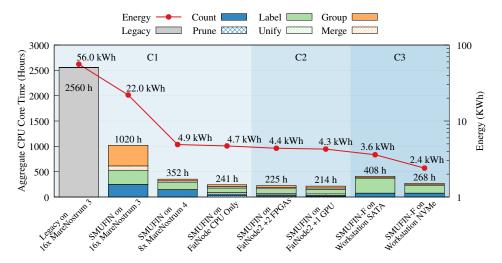

| Figure 30 | Time- and energy-to-solution of all SMUFIN versions                       | 78         |

| Figure 31 | Aggregate node time and energy-to-solution of all SMUFIN versions         | 78         |

| Figure 32 | Aggregate CPU core time and energy-to-solution of all SMUFIN versions     | 78         |

| Figure 33 | Relative improvement of time-to-solution, node time, aggregate CPU core   |            |

|           | time, and energy-to-solution of all SMUFIN versions over the legacy code. | <b>7</b> 9 |

|           |                                                                           |            |

# LIST OF TABLES

| Table 1 | Number of different roots in a typical input data set                     |

|---------|---------------------------------------------------------------------------|

| Table 2 | Experimental setup used for the experiments of the first contribution 26  |

| Table 3 | GPU Kernels times                                                         |

| Table 4 | Experimental setup used for the experiments of the second contribution 49 |

| Table 5 | FPGA Resources used, Clock Frequency, and Compilation Time of the         |

|         | FPGA design                                                               |

| Table 6 | Experimental setup used for the experiments of the third contribution 66  |

#### INTRODUCTION

#### 1.1 THESIS CONTEXT

Computer systems are in continuous evolution, and they have come a long way. In the last decade, the main components of computer systems, such as processing units and memory, reached physical limits and have been evolving, diversifying, to overcome these limits, but also to minimize their energy footprint and the humongous costs related to run power-hungry systems at scale.

One example of these physical limits is the so-called "power wall", or breakdown of Dennard scaling or MOSFET scaling, reached in the middle of the last decade [16, 144]. Due to this limit, the more we scale the lithography process of transistors, the more impractical it is to keep increasing the clock frequency of microprocessors because they would dissipate too much heat that commodity cooling cannot manage. As Figure 1a shows, this forced a dramatic change in the design of microprocessors. In particular, the impracticality of higher frequency led manufacturers, always seeking for better performance, to move from single-core to multi-core chips [110]. At the same time, many-core chips, such as GPUs, also started to be used for general-purpose computing, and they now offer chips with thousands of cores. In pursuit of even more power-efficient computing, the interest also expanded to more specialized chips, such as FPGAs, and also to application-specific chips ASIC (e.g., TPU).

A second physical limit is the ending of DRAM scaling; which makes DRAM capacity, cost, and power consumption difficult to scale further. Furthermore, as Figure 1a shows, DRAM latency is mildly reducing; augmenting the speed gap between processors and main memory. Manufacturers are still striving to find alternatives to DDRx SDRAM that offer lower latency, higher capacity, and lower power at the same time. In the meantime, new kinds of memory technology have

Figure 1: (§1) Microprocessor and DRAM trends in the last decades.

emerged, each with its trade-off. An example is Reduced Latency DRAM (RLDRAMx) which offers 4x lower latency than the DDRx DRAM chip, but its cost/bit is significantly higher, up to 39x [25]. A second example is the high bandwidth memories, such as GDDR and HBM, that were created to deliver high bandwidth to feed the thousands of compute units of accelerators. Compared to DDRx, these memories offer lower power consumption but worse latency, which is not entirely an issue given the parallel nature of accelerators. Another example is the non-volatile memories, such as NAND memory and Phase-Change Memory (PCM), that were created to provide much lower power consumption and affordable price/GB ration than DDRx. Compared to DDRx, NVM memories offer better power consumption and prices, but orders of magnitude higher latency and much lower bandwidth. For this reason, they are rapidly being adopted as a new memory tier between main memory and storage to provide significant capacity with low power consumption and low cost.

All these major shifts in the hardware landscape are allowing humankind to advance scientific computing, and they are enabling us to tackle ever-important problems with ever-larger volumes of data. At the same time, these shifts demand radical changes also on the software side. For instance, to improve the software performance at lower clock frequency, traditionally sequential code needed to be adapted to take advantage of multiple cores. To harness accelerators and their forms of parallelism, new programming models and algorithms have been developing. To take advantage of the new non-volatile memory, a new protocol and changes in user and kernel code have been carrying out. Therefore, while hardware heterogeneity has become key to design more efficient systems, it requires tighter integration between hardware and software. This integration is what we call hardware/software co-design. From an appliance standpoint, hardware/software co-design is the cooperative design of the hardware and software aimed to meet some requirements by exploiting possible synergies between hardware and software. A non-exhaustive list of possible requirements includes: make the execution time shorter, reduce the energy-to-solution, or do not exceed a set power consumption limit. While the former requirement is the most common, application executed at a large scale might be more interested in reducing the total energy consumed, even if this might imply longer execution times.

While hardware specialization and diversification are fundamental for more efficient systems, they introduce new challenges. First, it is difficult to identify the best hardware for a given workload. This challenge requires a broad view and understanding of all the different hardware. Plus, it takes a good knowledge of the application and its external requirements (e.g., need to execute the application on-premises). Second, if the software uses proprietary programming models or libraries, the portability of the application to similar hardware from different vendors is restricted. Third, there are no guarantees on performance portability when moving one application from one platform to another. Finally, co-design is an iterative and time-consuming process that needs to evolve together with new and emerging technologies that might change the hardware landscape. Although these challenges, hardware/software co-design is particularly crucial for data-intensive applications that run at scale, such as climate models, cosmological simulations, data compression, molecular dynamics, et cetera.

Another field where hardware/software co-design is fundamental is genomics. Here, modern DNA sequencing technologies greatly reduced the sequencing time and, like Figure 2 shows, made its cost orders of magnitude cheaper than it was just a few years ago. The rate of progress

Figure 2: (§1) As DNA sequencing costs have plummeted, the number of sequenced genomes has increased dramatically. Cost data from NHGRI Genome Sequencing Program [50], information about genome sequences published before 2011 from [45], and chart from Genetic Science Learning Center [24].

in this field is unparalleled and, as DNA sequencing becomes more affordable and available, more and more human genomes are sequenced. This breakthrough, together with novel genomics methods, will eventually enable the long-awaited personalized medicine, which selects appropriate and optimal therapies based on the context of a patient's genome; potentially changing medical treatments as we know them today. However, the broad adoption of such methods is limited by their capital and operational costs. In fact, genomics pipelines consist of complex algorithms with execution times of many hours per each patient and vast intermediate data structures stored in DRAM for good performance; requiring to scaled-out to multiple compute nodes to satisfy the main memory requirement. Therefore, these workloads require infrastructures of enterprise-class servers, with entry and running costs that quickly become unmanageable with many patients and that most labs, clinics, and hospitals cannot afford. This poses two challenges. First, the processing of large repositories of genomes becomes expensive, and it requires a considerable amount of resources, even for a supercomputing facility. Second, the adoption of such methods in the field by physicians and researchers is limited by energy and hardware costs. Due to these reasons, we believe that co-designing genomics workload to lower their total cost of ownership is essential and worth investigating.

This thesis wants to demonstrate that hardware/software co-design allows migrating dataintensive genomics applications to inexpensive desktop-class machines to reduce the total cost of ownership when compared to traditional cluster deployments.

To prove this statement, we do the exercise to co-design SMUFIN [95], a state-of-the-art reference-free genomics algorithm. SMUFIN is a leading method for detecting mutations acquired by an organism after conception instead of inherited from a parent, called somatic mutations. The

#### 1.2 THESIS CONTRIBUTIONS

peculiarity of the SMUFIN method is that it does not require a full genome reconstruction or alignment against a reference; like other methods do. The SMUFIN method is supposed to run at scale on thousands of patients to identify relations between DNA mutations and cancerous tumors. These relations are key to discover the origin of tumors and must be understood to predict the types of cancer a patient might develop; which is fundamental to enable effective and personalized treatments. Nevertheless, the software implementation of this method takes multiple hours on multiple enterprise-class nodes consuming tens of KWh per every single patient. As an example, we estimated that to process the over 100'000 genomes of the European Genome-phenome Archive (EGA) [74] the original deployment of SMUFIN in 16 nodes of MareNostrum 3 would require over 256 millions CPU core hours and over 5.6 GWh. Numbers that directly translate to excessive costs that limit the broad adoption of the method.

Like other data-intensive applications, the software implementation of the SMUFIN method has characteristics and requirements that differ from those of more traditional high-performance applications. Some of the differences include but are not limited to: the application is data-intensive, and the main memory requirements dictate the number of compute nodes required; there is minimal communication between compute nodes; the amount of I/O increases with the number of nodes used.

#### 1.2 THESIS CONTRIBUTIONS

This thesis produces three contributions that all revolve around the same main topic: hard-ware/software co-design of data-intensive workloads. Each contribution delves into a separate co-design; investigating distinct challenges and proposing solutions to different problems. The contributions can be summarized as follows:

- C1: Examine algorithmic improvements to ease co-design and to reduce workload footprint using NVMs as a memory extension to be able to run in one single node.

- C2: Investigate how data-intensive algorithms can offload computation to programmable accelerators (i.e., GPUs and FPGAs) to reduce the execution time and the energy-to-solution.

- C3: Explore and propose techniques to substantially reduce the memory footprint through the adoption of flash memory to the point that data-intensive workload can run on one single desktop-class machine that uses only consumer-grade hardware.

Even these three contributions are independent of each other, in the scope of this thesis they are part of one incremental work and, as Figure 3 illustrates, they all follow the same trajectory toward a lower total cost of ownership (TCO). This is accomplished by reducing the capital expenditures of the hardware, lowering the operating expenses of the electric bill, or both at the same time. The first contribution lowers both costs at the same time; reducing the workload footprint to just one node to minimize the waste of resources and to reduce the energy-to-solution. The second contribution reduces the operating costs; by slightly increasing the capital cost to buy additional hardware accelerators that can be more power-efficient. Finally, the third contribution lowers both costs; targeting inexpensive and low-power desktop-class machines rather than enterprise nodes. Here, the much lower computational capability translates to longer execution

Figure 3: (§1.2) Graphic representation of the three contributions of this thesis, all following a trajectory towards a lower Total Cost of Ownership (TCO).

times. However, the power consumption is reduced to the point that the energy-to-solution is also reduced despite the longer time-to-solution. Besides, this class of machine does not need an air-cooled server room; further reducing the total cost of ownership. This third contribution is the key to ease the adoption of the SMUFIN method – and potentially other methods – by researchers in their labs and enables genomics analysis on-premises by physicians.

#### 1.2.1 Algorithmic Improvements to Reduce Workload Footprint

The **first contribution** of this thesis is a set of algorithmic improvements that aim to reduce workload footprint and ease the co-design of data-intensive applications. This contribution is motivated by the observation that applications have different stages, each one with its footprint and requirements. However, monolithic applications have to request enough resources to meet the requirement for the execution of all stages; wasting resources. This problem is particularly relevant for data-intensive applications with a memory footprint that exceeds the amount of memory in a compute node. In fact, in such cases, the only way to meet the memory requirement is to scale-out the application to multiple nodes to obtain enough aggregated memory; possibly requesting more compute resources than needed; wasting CPU time and energy. This first contribution of this thesis aims to reduce the footprint of workloads by minimizing this waste of resource; thus, reducing the operational costs. Besides, it suggests techniques to lower the main memory requirements to enable genomics applications in one single node; thus, reducing the capital expenses.

The algorithmic improvements of this first contribution are three. First, to minimize the waste of resources, this thesis proposes to redesign the application using a modular structure made of multiple stages, called *units*. This structure allows the sizing of the workload footprint based on the resource demands of each distinct unit. To fit the execution into one single compute node with less memory than required this structure also admits breaking most demanding units into multiple *partitions*, to be executed sequentially one after another. Second, to reduce DRAM

#### 1.2 THESIS CONTRIBUTIONS

requirement of the most demanding units, this thesis suggests a manual swapping mechanism to flush data structures from the main memory to non-volatile memory. Third, to reduce the memory requirement even further, this thesis analyses alternative and memory-efficient data structures. While the first two improvements are general, and applications from other domains, beyond genomics, could benefit from it, the third improvement is more specific to genomics workloads.

Results showed that we were able to reduce the workload footprint of SMUFIN to the point that it can be executed in just one node with 512 GB of main memory and one non-volatile memory of 1.6 TB (used as memory extension) rather than the usual from 16 nodes, each with 128 GB of main memory, at a similar time-to-solution and more than 10x lower aggregate node time and energy-to-solution. A considerable part of the algorithm proved to be CPU bound; suggesting that accelerators could be leveraged to offload some of the compute-intensive work.

The work performed in this area resulted in the following publications:

[20] <u>Nicola Cadenelli</u>, Jordà Polo, and David Carrera. Accelerating K-mer Frequency Counting with GPU and Non-Volatile Memory. In 2017 IEEE 19th International Conference on High-Performance Computing (HPCC), pages 434-441, December 2017.

[22] David Carrera Perez, Jordà Polo, <u>Nicola Cadenelli</u>, David Torrents Arenales, and Mercè Planas. A Computer-Implemented and Reference-Free Method for Identifying Variants in Nucleic Acid Sequences, January 2018. Patent No.: WO/2018/007034.

#### 1.2.2 Offloading Computation to Accelerators

The **second contribution** of this thesis is a study that aims to investigate the offloading of computation to programmable accelerators like GPUs and FPGAs for data-intensive applications. This contribution is motivated by the observation that data-intensive applications that process large volumes of data can easily become CPU bound, particularly when being executed in one single node. Therefore, programmable accelerators that offer a high degree of parallelism can be efficiently used to offload some of the computation. However, their adoption requires an arduous exploration to determine the best kind of accelerator and a careful co-design that aims to overcome possible bottlenecks. This second contribution targets accelerators that have significant costs and, usually, increase the power consumption of a compute node. However, their adoption is justifiable if it yields a reduction of the execute time, thus lowering the energy-to-solution. Motivation that is particularly true for applications meant to run at scale, where the energy costs are more relevant than the capital expenditures.

The topics of the study of this second contribution are many. First, the study focuses on offloading CPU intensive operations. Then, to overcome memory constraints of accelerators, it proposes and prototypes a method to virtualize accelerators' memory in host DRAM. Next, it delves into portability issues that arise when porting the code from one kind of accelerator to another. In this scope, the study also shows how single components of accelerator (i.e., off-chip memory and PCIe connection) can hinder performance, particularly for data-intensive applications. Finally, the study analyses and discusses power and energy consumption with and without accelerators.

Thanks to the modular structure given to the application in the first contribution, the study is isolated to only a few units of the SMUFIN pipeline.

Results showed that offloading to GPUs and FPGAs can reduce both time- and energy-to-solution with improvements up to 1.8x for both metrics. A thorough analysis of the application uncovered that in the faster execution, with one GPU, the main bottleneck is the main memory latency of the CPU that must be paid to randomly access the principal data structures stored in main memory; suggesting that the algorithm could benefit from building the main hash table in a different manner that minimizes the random updates.

The work carried out in this field produced the following publications:

[20] <u>Nicola Cadenelli</u>, Jordà Polo, and David Carrera. Accelerating K-mer Frequency Counting with GPU and Non-Volatile Memory. In 2017 IEEE 19th International Conference on High Performance Computing (HPCC), pages 434-441, December 2017.

[21] <u>Nicola Cadenelli</u>, Zoran Jaksić, Jordà Polo, and David Carrera. Considerations in using OpenCL on GPUs and FPGAs for throughput-oriented genomics workloads. *Future Generation Computer Systems*, 94:148-159, 2019. ISSN 0167-739X.

#### 1.2.3 Memory footprint reduction through flash key-value store

The **third contribution** of this thesis is the exploration of co-design aimed to reduce the memory footprint of data-intensive applications through a flash key-value store. This key-value store, optimized for NAND-flash storage, provides an alternative way to store the TB-size intermediate data structures that are usually kept in main memory. This contribution is motivated by two main observations. First, new flash NVM technologies are getting better and cheaper. Second, as of today, NVMs constitute a valid alternative to DDR SDRAM, which instead is a stable technology whose prices are not decreasing. However, replacing main memory with flash storage does not come for free and has its challenges. In particular, one needs to overcome the four orders of magnitude longer latency and two orders of magnitude larger access granularity of flash storage over DRAM.

This third contribution targets commodity PCIe NVMe and SATA-III SSD drives that can be placed into desktop-class machines. Compared to enterprise machines with hundreds of GB of main memory and high-end CPUs, target desktop-class machines consume less power at the cost of considerably lower compute capabilities that could lead to noticeable longer execution times. However, these target machines are profitable if, through co-design efforts, it is possible to limit the performance penalty on the selected workload so that the energy-to-solution is still lower than on the faster enterprise machine. Furthermore, desktop-class machines considerably reduce the capital expenditures of the hardware, and since these machines are deployed in regular offices, without the need for air-conditioned server rooms, their use further cuts capital and operational costs.

The exploration of this third contribution has different outcomes. First, it presents a method to generate and access large intermediate data structures in flash storage as opposed to DRAM memory. Second, it proposes a novel key-value store implementation that uses domain-specific information to perform efficient in-memory caching. Next, it investigates and proves how mul-

#### 1.2 THESIS CONTRIBUTIONS

tiple CPU threads and asynchronous direct I/O with deep queues are required to exploit the high level of parallelism offered by flash storage. Finally, it provides scalability and cost analyses of a solution based on a desktop-class machine furbished with NVM drives against an enterprise-class machine with hundreds of GB of main memory.

Results showed that we reduced the system requirements for the entire SMUFIN method to the point that it can run to completion on an affordable desktop with a 6-core i7 and 32 GB of memory instead than on an enterprise machine with four times as many cores and 512 GB of DRAM. A cluster of multiple desktop-class machines costs half as much compared to a cluster of servers and consumes half as much energy while maintaining a similar throughput.

The work carried out in this third contribution assembled the following pending publication:

[Under Revision] <u>Nicola Cadenelli</u>, Sang-Woo Jun, Jordà Polo, Andy Wright, David Carrera, and Arvind. Enabling genomics pipelines in commodity machines with flash storage.

This thesis is organized as follows. Chapter 2 introduces some background knowledge on general-purpose accelerators, non-volatile memories, genomics applications, and the SMUFIN method. Chapter 3 describes and evaluates the first contribution explaining the algorithmic improvements used to reduce workload footprint to the point that we can run the SMUFIN method in one single node with node. Chapter 4 presents and evaluates the second contribution describing how we offloaded part of the k-mer counting algorithm to general-purpose accelerators, such as GPUs and FPGAs, to reduce time- and energy-to-solution. Chapter 5 details and evaluates the third contribution presenting how flash storage can be leveraged to enable data-intensive genomics on commodity desktop-class machines. Finally, Chapter 6 presents conclusions, shows overall results that stretch from the first to the third contribution, and it discusses possible future works.

#### BACKGROUND

#### 2.1 GENERAL PURPOSE ACCELERATORS

The so-called "power wall", or breakdown of Dennard scaling reached in the middle of the last decade, forced a dramatic change in the design of microprocessors. In pursuit of even more power-efficient computing, this inflection point in microprocessor design rose the interest in accelerators. As of today, accelerators can have different forms, such as Graphics Processing Units (GPUs), Application Specific Integrated Chips (ASICs), Field Programmable Gate Arrays (FPGAs), and even System-on-Chip (SoC). Each with its advantages and design trade-offs.

In this work, we focus on programmable accelerators like GPUs and FPGAs. Thanks to the parallelism offered by both kinds of these accelerators, they have been key to process the large volumes of data of today's applications: particularly for high-throughput computations that exhibit data-parallelism. GPUs are popular due to their embarrassingly parallel architecture that offers multithreaded SIMD (Single Instruction Multiple Data) with thousands of cores. On their hand, FPGAs are known for their higher efficiency in parallel processing. Besides, they allow adding other interfaces (e.g., networking), which might be critical for some use cases and that GPUs usually do not have.

Accelerators in the form of GPUs turn the massive computational power of modern graphics chipset into general-purpose computing power. Applications requiring a tremendous number of vector operations can achieve several orders of magnitude higher performance than a conventional CPU. In order to leverage the potential of a GPU, an application needs to: be parallelizable using thousands of threads all doing the same instruction at the same time; have low as possible branch divergence; perform coalesced accesses to global memory; and make use of on-chip memory which offers higher bandwidth and lower latency than the other memories, local and global, in the GPU.

Field Programmable Gate Arrays (FPGAs) are integrated circuits that allow programming customized digital logic in the field even after manufacturing. What makes FPGAs different is that they allow the creation of sets of instructions that could be executed in a single clock cycle, while CPU or GPU would require multiple cycles. Moreover, FPGAs accomplish parallelism by duplicating the logic that each algorithm needs. In contrast, other architectures achieve parallelism replicating the entire generic computation hardware multiple times, potentially duplicating unnecessary components for a given problem. Another difference is that in FPGAs the logic of each instruction is connected to others creating complex vines of logic in a pipeline fashion. This means that after a ramp-up phase, the pipeline sustains a constant throughput that well suits stream processing.

#### 2.2 NON-VOLATILE MEMORIES

Today, both GPUs and FPGAs can be programmed with high-level languages like OpenCL, a portable programming language that allows executing the same code across a variety of platforms. Even though OpenCL offers code portability, performance portability between different hardware platforms is not guaranteed due to the fundamental differences among architectures. Consequently, the porting of an application from one architecture to another requires a consistent refactoring of the offloaded code to adopt device-specific optimizations. Additionally, being a more mature product, GPU boards are typically equipped with a high-performance onboard memory (e.g., GDDR5X or HBM2) and a high-speed full-duplex interconnection (e.g., PCIe Gen3 x16 with a dual copy engine). Whereas, discrete FPGA boards are, as of today, a still younger product that is catching up, and that usually offers much less performing memory (e.g., DDR4) and a slower half-duplex connection with the host system (e.g., PCIe Gen3 x8 with a single copy engine). While these differences seem of secondary importance, they can be critical for the data-intensive application. In fact, interconnection technologies between CPUs and accelerators are very important for data-intensive workloads, where huge volumes of data must be continuously moved back and forth in order to be processed. Here, when the interconnection bandwidth is lower than the throughput offered by computational units, the interconnection becomes the bottleneck of the application. Besides, to allow simultaneous copies in both directions and the overlapping of data transfers with computation devices must be equipped with two independent copy engines.

#### 2.2 NON-VOLATILE MEMORIES

Disk access time can be one of the critical parts for every-day applications, and it becomes even more crucial when dealing with huge volumes of data. Non-volatile memory (NVM) storage came into play to help to provide lower access time and even energy gains over electromechanical disks. NVMs are taking the place of old rotational disks in many systems. In large-scale enterprise systems, they are being used as staging areas to overcome the I/O burstiness that characterize some applications and the huge requirement of central memory [44]. Moreover, this allow a post-execution reuse of data for in-situ data analysis [43, 126, 85, 127]. Besides being used as traditional disks with conventional file systems, NVM storage can be used as persistent memory by memory-mapping files, or even the entire device using it as a block device. In this way, data can be accessed using processor load and store instructions – as volatile memory is accessed – but would not be lost across power loss. Because of these characteristics, new non-volatile memory storage are changing the traditional memory hierarchy and are considered a third memory tier along with memory and storage [76].

In order to fully exploit the potential of NVM, software changes are required from the kernel to the application level. These changes are needed to minimize the storage software overhead caused context switches, data copies, interrupts, resource synchronization, and et cetera [118]. To this end, the Non-Volatile Memory Express (NVMe) specification was created. NVMe was architected from the ground-up to capitalize on the low latency and internal parallelism of NVM storage devices, mirroring the parallelism of contemporary CPUs and applications. As a result, NVMe reduces I/O overhead, power consumption, and latency while, at the same, increases the possible level of parallelism. Compared to previous logical interfaces, NVMe is designed to have

up to 64 thousand queues, each of those queues can have up to 64 thousand commands at the same time.

Most of today's NVM drives are made using NAND technology, which offers an endurance that could not be enough with data-intensive workloads. Emerging Phase-Change Memories (PCM) technologies can provide a better lifetime (in terms of write cycles) and better performance [23] than NAND drives. Thanks to the recent 3DXPoint, PCM is reaching the market as NVMe drives but also as NVDIMMs [136, 54]. This technology might complement, or even replace, NAND drives and DRAM. In the meantime, hybrid solutions like PCM/SSD hybrid solid-state storage [43] and PCM/DRAM hybrid main memory [140] have been proposed.

#### 2.2.1 Flash Devices Architecture and Practical Knowledge

Figure 4: (§2.2.1) Internal SSD architecture [6] (left) and NAND flash memory writes data in 4 KiB pages and erases data in 256 KiB blocks [135] (right).

At first blush, one could think that getting a flash device and a way to access it is enough to start benefit from it. However, this is far from the truth, and programmers must understand the internal structure. SSD controllers receive I/O requests from the host via an interface connection (i.e., PCIe) and uses the Flash Translation Layer (FTL) to translate logical pages of incoming requests to physical pages. Memory cells are grouped into grids, called blocks, which in turn are arranged into planes. Block and page sizes vary from drive to drive, but typical flash page sizes include 4 KiB, 8 KiB, or 16 KiB, while a block can contain tens or thousands of pages. Each page can have a few bytes of metadata region to store fields like: bad block indicator, Error-Detection Code (EDC), Error-Correction Code (ECC), Block Sequence number, et cetera [12, 67]. Figure 4 shows the internals of SSD internal architecture.

Aside from understanding the internal architecture, there is some practical knowledge should be borne in mind:

Reads and writes are aligned on page size, and it is not possible to read or write less than

one page at once. Even if a read or write operation affects a few bytes, a full page is read or

written, amplifying the I/O size. Therefore, to maximize throughput small writes should

#### 2.3 GENOMICS

be buffered to be written performing a single large write to batch all the small writes only when the buffer is full.

- A NAND-flash page can only be written if it is in the *free* state. When data is modified, the content of the page is copied into an internal register, updated, and the new version is stored in a different *free*, which means that the data is not updated in place. Once the data is written to the destination page, the original page is marked as *stale* until it is erased.

- Erases are performed at a block-granularity. Thus, it is not possible to erase individual pages, and it is only possible to erase whole blocks at once. Besides, flash memory must be erased before it can be rewritten. The erase command is triggered automatically by the garbage collection process in the drive controller when it needs to reclaim *stale* pages to make free space.

- Flash devices suffer from an undesirable phenomenon called write amplification (WA), where the actual amount of physical information written is a multiple of the logical amount intended to be written. This effect is due to the way flash devices work. In particular, to the garbage collector trying to move pages so to free up an entire block to be erased. This phenomenon increases the number of physical writes required, shortening the drives lifetime. The extra writes also consume bandwidth to the flash memory, which reduces random write performance. This phenomenon can be mitigated using techniques like over-provisioning, data compression, and implementing *TRIM* command. However, to diminish the write amplification effects, writes should be aligned with the page size and should use a granularity that is a multiple of a flash page [48].

#### 2.3 GENOMICS

The typical input of a genomics application consists of hundreds of GB of sequenced DNA samples. Such samples are stored in a compressed form and include short sequenced strings of DNA nucleobases called *reads*. Each sequenced human genome typically contains  $10^9$  to  $10^{10}$  reads, depending on some factors such as depth of coverage, which indicates how many times each DNA position is represented in the sequenced genome. The length of each read is in the order of 10s to 10os of bases that are represented by the four character alphabet {A, C, G, T}. Along with each base in a sequenced sample, there is also an associated score that measures its quality, doubling the amount of data. There are continuous technological improvements in sequencing, which allow longer reads, and this is likely to increase the amount of data available for further genomics analysis.

Methods to find mutations typically align reads from a sequenced sample to a reference genome. Somatic mutations are particularly challenging because they usually involve comparing normal and tumoral samples from the same patient, and reads carrying variations are harder to align [39]. Current reference-based approaches tend to be very specialized and use different algorithms to target a particular kind of variant [36]. For instance, Mutect [32] and Platypus [107] are designed for single nucleotide variants (SNV), and Pindel [142], DELLY [125], and BreakDancer [28] are designed for structural variants (SV) with different characteristics. Hence, defining a

complete catalog of variation generally requires complex pipelines with combinations of multiple methods.

Emerging reference-free methods have the potential to provide more accurate results, but they also require significant computational and memory resources. Methods to detect single nucleotide polymorphisms (SNP) based on De Bruijn graphs [113] like Cortex [53], Bubbleparse [80], and NIKS [98] easily exceed the memory of a server with 512 GB of DRAM; with human datasets, processing a single chromosome can take as much as 105 GB [130], and memory for processing whole human genomes is expected to be much higher. Other methods like DiscoSnp use a cascade of Bloom filters to represent De Bruijn graphs [31, 33] and manage to keep a significantly lower memory footprint [130]. These variant calling methods are limited in scope and target a particular kind of non-somatic mutation.

SMUFIN, the user-case for this thesis, differs from the other methods because it is a comprehensive reference-free method that targets somatic mutations, and all kinds of variants, from SNVs to large SVs. Like many genomics applications, SMUFIN relies on splitting DNA reads into smaller pieces called k-mers. k-mers of a nucleic acid read are all the possible sub-sequences within the original read of length k. The amount of k-mers in a read of length M is M - k + 1. For instance, the number of 8-mers in a sequence of 10 bases is 10 - 8 + 1 = 3, meaning an example read ACGGCAGCTG has the following 8-mers: ACGGCAGCT, and GGCAGCTG. Counting the frequencies of k-mers is an important algorithm in bioinformatics that is used by many methods for different kinds of studies. The main applications for k-mer frequency counting are: sequence assembly, to reconstruct the original DNA sequence [133, 55]; sequence comparison, to extract knowledge of biodiversity between different environmental conditions [90, 11, 129, 99]; sequence clustering, to discover the feature of some sequence [143, 60, 19]; sequence alignment and variant calling [82, 65]; to predict secondary structures of RNAs [89, 30]; et cetera [139]. What makes SMUFIN k-mer frequency counting different from this method is that it operates on a couple of whole human genomes, normal and tumoral samples, of the same patient, making the memory footprint even higher in the order of few TBs.

#### 2.4 THE SMUFIN METHOD

SMUFIN [95, 20] is a leading algorithm and implementation for detecting somatic mutations that detects both point and structural somatic mutations without full genome reconstruction or alignment against a reference. Since SMUFIN is *reference-free*, it avoids costly alignment, which often takes 70% of the genome analysis pipeline [137]. Additionally, by not aligning against a reference genome, SMUFIN can detect complex structural variations more effectively [95], and it could work on species where reference genomes may be incomplete or unavailable [79].

The end goal of SMUFIN is to reveal the exact mutations found in a tumorous sample, therefore allowing doctors to produce personalized medicine for those specific mutations. In its current state, SMUFIN is a research tool used by scientists, and as a result, it is desirable for SMUFIN to produce and keep more data to create a better picture of the potential mutations seen in the genome. SMUFIN has built-in parametrization to allow scientists to specify what k-mer combinations and reads are *interesting*, and this tuning can have a significant impact on the sizes of data in the later phases in SMUFIN. This work assumes settings that biologists have used for explor-

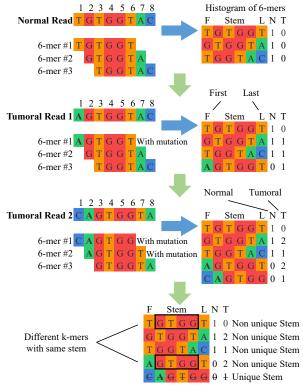

Figure 5: (§2.4.1) Hierarchy of k-mers, stems, and roots showing all the k-mers that map to the root CGTA.

atory research so far. In the future, different settings may be used for clinicians using SMUFIN as a tool to produce personalized medicine.

#### 2.4.1 SMUFIN Overview

SMUFIN assumes no prior knowledge of the structure or the location of mutations. Instead, it uses k-mer counts for the normal and tumor sample to determine possible mutations. In the simplest case, a k-mer that is common in tumoral reads but is not seen in normal reads is expected to be part of a mutation. This is useful for detecting the presence of mutations, but it is not sufficient to align the normal and tumoral reads together to reconstruct the mutation.

To find k-mers that are useful for reconstructing mutations, one can look for k-mers that match in the middle k-2 bases, called the *stem* of a k-mer, but do not match in the first or last base. The simplest case is when of two k-mers with matching stem, one is only found in the normal sample, and the other only in the tumoral sample. In this case, these k-mers are likely to be the start or end of a mutation. Thus, they can be used to align DNA reads from both samples together to reveal the structure of the mutation.

Since DNA sequencing produces reads from both strands of the DNA, and mutations affect both strands equally, it is also useful to be able to refer to the frequency counts of the k-mers as they would appear in the other strand of the DNA, i.e., its reverse complement, to further improve the quality of the results. SMUFIN groups k-mers of the same stem with their reverse complement using their *root*, a canonicalized stem obtained by taking the first of the stem and its reverse complement in alphabetical order. The hierarchy of k-mers, stems, and roots can be seen in Figure 5. The software implementation of SMUFIN produces a histogram indexed by root, such that each time one searches for a k-mer in the histogram, it returns the counts for all the 64 k-mers with the same root,  $(4 \cdot 4 \cdot 2 =)$  32 for the normal data set and as many for the tumoral data set.

To decide what reads and k-mers are interesting for further mutation reconstruction and analysis, biologists define a set of criteria that reads and k-mers must meet. The set of criteria comprises characteristics of each single reads (e.g., contains a particular sequence of bases, quality markers of the bases in the reads) but also on the k-mers of a read (e.g., frequency counts of the k-mers and other k-mers from the same root). These criteria are used to construct the *interesting reads and k-mers database* which can be thought of as a set of two tables: one containing interesting reads, and the other containing interesting k-mers. Each read in the reads table contains a

Table 1: Number of different roots in a typical input data set with a breakdown of unique and different non-unique roots when using 30-mers. The number of different roots represent the number of entries in the histogram.

|                                       | Numbers in Billions | Percentage |

|---------------------------------------|---------------------|------------|

| Different roots                       | 78                  | 100 %      |

| Roots of unique 30-mers               | 68                  | 87.2 %     |

| Roots of different non-unique 30-mers | 10                  | 12.8 %     |

bit vector denoting which k-mers in it are interesting, implicitly creating pointers to the k-mer table. Each k-mer in the k-mers table contains the IDs of the reads where this k-mer occurs, implicitly creating a pointer to the reads table. This database structure is efficient for constructing groups of reads containing a particular k-mer. Reads in such a group can be aligned for mutation reconstruction and further analysis.

#### 2.4.2 SMUFIN Algorithm

Conceptually, the SMUFIN algorithm is organized into three phases: k-mer counting, labeling, and grouping.

**K-mer counting:** The k-mer counting phase takes in sets of reads from two data sets: one normal and one tumoral. Depending on the sequencing machine, each read can be on the order of 80 to 150 bases long, and each base in the read has a corresponding quality score representing the confidence of the sequencing machine on the correctness of the base. In a typical sequenced genome sample, each part of the DNA appears in tens of different reads, resulting in a sample data set with billion of reads [49]. This input is around 310 GB of compressed FASTQ files and around 740 GB when uncompressed. These reads are then divided into k-mers. SMUFIN uses k values in the range of 24 < k < 32. According to the domain experts involved in the original algorithm construction, this range of k-mers is unique enough to align to genomes accurately, and at the same time, general enough to accurately pinpoint mutations. For values outside this range results might become either too general (for k <= 24) or too selective (for k >= 32) producing results with poor sensitivity and specificity.

For each k-mer in each read, the corresponding entry in the histogram is incremented. Figure 6a shows a simplified example of k-mer counting. The full size of this histogram is about 78 billion roots, which would require almost 10 TB of memory. However, like Table1 reports, many of these roots can be regarded as sequencing errors [18] in the input data, and they only appear in a single read. To identify and remove these unique items, we use a list of all items seen in the input. The application throws out all the unique roots reducing the size of the histogram down to around 1 TB and the memory footprint of the application to around 2 TB. This histogram, once built, is not updated further, but is read 100s of billions of times by the labeling phase.

**Labeling:** The labeling phase constructs the *interesting reads and k-mers database*, described earlier in Section 2.4.1, making one additional pass through all the input data set. This step requires a histogram lookup of each k-mer of each input read to determine if the read and k-

Normal Read T G T G G T A C

Tumoral Read 1 A G T G G T A C

Tumoral Read 2 C A G T G G T

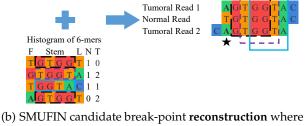

- (a) SMUFIN candidate break-point **detection** with 3 sample reads of length 8 and a histogram of 6-mers. In this example the stems GTGG and TGGT are potential point of divergence, and their neighboring bases are candidate break-point for a mutations.

- (b) SMUFIN candidate break-point **reconstruction** where the "Tumoral read 1", containing a candidate stems, is aligned with all other reads containing at least one of the stems in "Tumoral read 1". In this example, the second base of the aligned block (\*) is a candidate break-point for a single point mutation.

Figure 6: (§2.4.2) Simplified example of SMUFIN candidate break-point detection and reconstruction. In this example, the candidate break-point is for a single point mutation, where a single nucleotide base is changed. In reality, a candidate break-point might be the beginning or end of a larger mutation, such as a structural mutation or a virus.

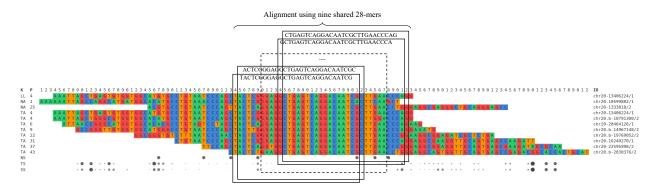

Figure 7: (§2.4.2) Example result of SMUFIN showing a candidate mutation.

mers are interesting. The root-indexed histogram offers data locality in accessing all the k-mer counters of the same root, which is necessary to determine if a read and k-mer are interesting for candidate break-point reconstruction. The database created in this step is implemented using RocksDB [123]. The read table in the database can be easily constructed sequentially by scanning through all the input reads, but the construction of the k-mer table requires random-access insertions. Depending on the set of criteria defined by the biologists, the size of the resulting database can vary significantly; for standard executions, it contains up to 150 million reads and 110 million k-mers, and its size is around 200 GB.

**Grouping:** The final phase of SMUFIN is grouping reads with the same interesting k-mers together to reconstruct the mutations. This is done by looking in the interesting reads and k-mers database and clustering reads with the same interesting k-mers. Once the groups of reads are assembled, they are aligned with each other according to where the matching k-mers were found. If the position of matching k-mers do not agree between normal and tumoral reads, then there may be a mutation, either insertion or deletion, causing the alignment to be off. Figure 6b shows a simplified example of grouping, and Figure 7 shows an example result for one candidate mutation.

#### ALGORITHMIC IMPROVEMENTS TO REDUCE WORKLOAD FOOTPRINT

This chapter describes the first contribution of this thesis. This contribution aims to reduce the footprint of workloads to target fewer nodes, if not just one. This contribution is motivated by the observation that monolithic data-intensive applications might have different requirements during the execution, and this might lead to wastes of resources, particularly when running on multiple nodes. The idea is to explore techniques to limit the waste of resources and to reduce the workload footprint; thus, lowering both capital and operational costs.

The main parts of this contribution are various. First, in Section 3.1 we present a modular software structure that is driven by the resource requirement to reduce the waste of resources and target one single machine. Second, in Section 3.2 we explore alternative and more memory-efficient data structures. Third, in Section 3.3 we suggest a manual swapping mechanism to non-volatile memory that allows extending the main memory of a system with NVM storage to reduce the main memory requirement. Next, in Section 3.4 we evaluate the different techniques and discuss results. Here we compare the legacy code of the application running on multiple nodes with a new version that adopts the solutions proposed in this contribution, and that can run in one customized single node with 512 GB of DRAM and an NVM drive used as memory extension.

#### 3.1 REFACTORING MONOLITHIC SOFTWARE FOR MODULARITY

Read-world applications usually have different stages, each one with its own footprint and requirements. However, monolithic applications have to request enough resources to meet the requirement for the execution of all stages, wasting resources when executing less demanding stages. This waste of resources is particularly relevant for data-intensive applications with some stages characterized by memory footprint that exceeds the amount of memory in a compute node. In such cases, the usual way to meet the memory requirement is to scale-out the entire application to multiple nodes to obtain enough aggregated memory to meet the requirement of just one part of it. Besides, scaling to multiple nodes to meet the main memory requirement usually implies to over-allocate the compute resources, wasting even more CPU time and energy.

To minimize the waste of resources this thesis proposes to redesign the application using a modular structure made of multiple stages, called *units*. This structure allows the sizing of the workload footprint based on the resource demands of each distinct unit. To fit the execution into one single compute node with less memory than required this structure also admits breaking most demanding units into multiple *partitions*, to be executed sequentially one after another.

#### 3.1.1 Design Applications as a Sequence of Smaller Units

To reduce the workload footprint, we propose a structure based on the resources demands of each algorithmic step of an application. In this structure, each step is considered a unit and the application consists of a sequence of units. When executing the application, each unit is executed sequentially, scaling to the number of nodes that better suit the unit itself.

Although simple, this structure offers other advantages. The structure fits well with scientific applications that run for hours because each change between two units is the natural moment to perform check-pointing. With check-points between units, this structure allows taking advantage of the heterogeneity offered by the computing facility of today. In fact, it is straightforward to execute a unit in the kind of node that better meets the requirement of that particular unit. For instance, if the performance of a unit scales well with the number of CPU threads, then that unit could be executed in nodes with high-end nodes. Instead, if another unit requires a considerable amount of main memory, then it should be run in "big memory" nodes that offer TB of DRAM at the cost of lower compute power. This structure allows reducing the workload footprint closer to its real resource demand, limiting the waste of resources, and lowering the operational costs.

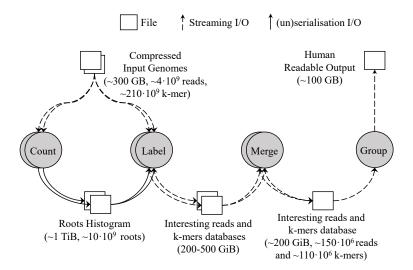

For SMUFIN, we mapped the three phases of its algorithm, described in Section 2.4.2, to a structure with as many units:

Count: Unit that performs the k-mer frequency counting step. It reads the input genomes in a streaming fashion and builds the histogram in DRAM. Once the entire input data set is processed, it dumps to storage the *root histogram* containing all interesting, non-unique, roots. The work in this unit is parallelized using two different kinds of CPU threads: *Loader* and *Consumer*. The Loader threads are committed to (i) load the compressed input files from storage to memory, (ii) perform quality checks on the reads, (iii) generate and encode all the k-mers in their 64-bit form, and (iv) send the k-mers to the Consumer threads. The Consumer threads, instead, read incoming k-mers from the Loader threads and insert them in the list of all roots seen and, only if the root is already seen, it gets into the root histogram. Communication between Loader and Consumer threads happens via dedicated lock-free single-producer single-consumer queues. The Count unit has a DRAM footprint of approximately 2 TB to fit the root histogram and the list of all roots seen in DRAM. This substantial memory footprint dictates the workload footprint.

**Label:** Unit that performs the labeling step. It reads the input genomes in a streaming fashion once more and consults the root histogram, loaded in main memory, to identify interesting reads and k-mers for mutation reconstruction. This unit adds interesting items to the *interesting reads* and k-mers database. This unit has a high DRAM footprint (more than 1 TB), needed to store the histogram, and it benefits from CPU with many CPU threads.

**Group:** Unit that performs the grouping step. It reads the *interesting reads and k-mers database* in a streaming fashion to group reads with the same interesting k-mers that are stored into a human-readable output. The unit has a relatively low memory footprint. It needs no more than a hundred GB, but it can also run in machines with few tens GB at the cost of lower execution time.

Due to their high main memory requirements, Count and Label units are likely to run in multiple nodes or either in "big memory" nodes with plenty of main memory. Differently, the Group unit can now run in just one node, saving resources.

#### 3.1.2 Splitting Units into Partitions

Like SMUFIN, it is reasonable to imagine applications with DRAM footprints that exceed the main memory of one single node, and that for this reason requires to scale-out to multiple nodes. Running on multiple and different nodes might not be a problem when running a workload on data centers and cloud computing services. Nevertheless, when targeting in-house computing, this has a direct impact on capital and operational costs.

To target one single compute node, we propose to split the most demanding units into multiple partitions, each for a disjoint part of the main data set domain. Each partition can then be executed as needed: sequentially in a single machine, concurrently in multiple nodes, or a combination of the two. Obviously, this partitioning depends from application to application, and it is not always possible; for instance, due to data dependencies between partitions. However, it matches well with genomics workloads. In fact, as described in Section 2.3, many genomics applications usually work with relatively small sub-strings, whose domain can easily be split using the first, for example, n bases to split the sub-strings domain, generates 4<sup>n</sup> parts <sup>1</sup>. This allows splitting the domain easily. However, due to the natural distribution of DNA strings that is not proportional, and it is likely to lead to very unbalanced partitions where some partitions have many more items than others. For example, given a DNA sample, the k-mers that begin with AAA or TTT are many times more numerous than those starting with CGA or CGC.

For SMUFIN, we created balanced static partitions so that the memory requirement for each partition is similar. This required to collect frequency data for representative input data set for values of n up to 5. Then, we executed many bin packing problems with different numbers of bins. For each problem, the partitions were the bins, the five bases the items, and the frequency of the five bases were the weights. With this method, we were able to create balanced partitions schemes that are distributed with the binary. Furthermore, we decided to use the same partitioning scheme to divide each partition into many sub-partitions further to spread the work between the different Consumer threads. In this way, each thread can now work on dedicated data structures; thus, minimizing the need for synchronization between threads.

A partitioning, like the one we propose, that splits the data domain into disjoint partitions that can be executed independently has two minor drawbacks. First, every partition needs to read the entire input data set. This is not a problem when running each partition sequentially, but it might create a considerable amount of I/O between compute nodes and storage when executing the application with many partitions in parallel, each on a different node. Second, if two consecutive units are likely to be executed with a different number of partitions, then, the outputs generated in the first unit might need to be reorganized to the number of partitions used in the second unit; either merging it into fewer partitions or splitting it into more partitions.

For SMUFIN, where the Count and Label units have similar workload footprint but the Group unit instead is candidate to be executed with one partition, we added a new optional fourth unit, named Merge, in between the Label and the Group unit. Like its name suggests, the job of this new unit is to merge the output of the different partitions of the Label unit into one database. If the Label unit is executed with just one partition than, the Merge unit is not needed. Figure 8

<sup>1 4&</sup>lt;sup>n</sup> because each DNA base can assume four different values, one for each possible nucleobases – Adenine (A), Cytosine (C), Guanine (G), Thymine (T).

Figure 8: (§3.1) SMUFIN modular structure using partitions and units. In this example the application is executed using two partitions; thus, Count and Label units are executed twice reading the whole input genomes two times for each unit. The Merge unit takes care to fuse the output of the Label partitions into one so that the Group Unit needs to be executed only once.

shows an example of the modular structure of SMUFIN, using the four units – Count, Label, Merge, and Group.

Thanks to this modular structure, applications can be executed in just one single node using multiple sequential partitions. The drawback is that, compared to a scale-out solution to multiple nodes, the time-to-solution is likely to increase. However, thanks to the modularity of the proposed solution, the CPU time does not necessarily increase. Instead, since we minimized the waste of resources, it is expected to decrease.

For SMUFIN, the number of partitions required to meet the memory requirement of the Count and Label unit directly impacts the time-to-solution. Thus, solutions that relax this memory requirement could effectively reduce the execution time.

#### 3.2 CHAINS OF BLOOM FILTERS TO IDENTIFY NON-UNIQUE K-MERS

Genomics applications that work on big data sets, like whole-human genomes, usually want to focus on parts of the DNA that are repeated many times in the DNA sample. The simplest way to do this is to build a list of all items seen. However, with billions of different items, this list can get as big as hundreds of GB. SMUFIN builds this table on the fly during the Count unit, and it keeps track of all items seen. This table is consulted per each item, but only those items already in the list are added to the roots histogram. With 87 billions of different items, the size of this histogram can be as big as 1 TB and is approximately half of the memory footprint of the Count unit.

As a more memory efficient alternative, we propose an approach based on Bloom filters. A Bloom filter is a space-efficient data structure that is used to tell if an item is in a given set or not. The only drawback of Bloom filters is that they accept false positives – items that are not in

the set, but that are thought to be. However, this probability of false positives can be reduced at the cost of a higher memory footprint, more hashing, and more memory accesses. To distinguish from unique and non-unique items, we propose a chain of two Bloom filters. In the chain, all items are added to the first Bloom filters, and they get added to the second filter only if they are already present in the first. At the end of the process, the second filter can tell which items are seen more than once and which are not. In this case, the false positives are those items though to be seen multiple times, but that they are seen only once. For whole-human genome analyses with billions of items, this structure requires only tens of GB and offers a much more memory efficient alternative to a list with all items, that instead requires hundreds of GB.

For SMUFIN, where there can be as many as 78 billion different items and 68 billion unique items (see Table 1), this Chain of Bloom filter is considerably smaller than the list of all items. For instance, with a false positive of 1%, the size of the filters is approximately 84 GB and 11 GB for the first and the second level, meaning that the entire input can be processed in just one partition. Besides, once fully built, the first filter can be discarded, and only the second and smaller filter needs to be used in the following Count unit. We integrated this method by adding an additional unit called Prune. This unit is executed before the Count unit. Its goal is to add all roots to the chain of Bloom filter so that the second level can, then, be used in the Count unit to drop unique items. This is an optional unit that requires to read the entire input data set one extra time, but that helps to lower the DRAM requirement of the next Count unit, thus lowering the number of partitions needed.

#### 3.3 MANUAL SWAPPING TO NON-VOLATILE MEMORY

Data-intensive applications that build vast data structure resident in main memory need to run either on multiple nodes or in one single node, using a partitioning scheme like the one presented in Section 3.1. However, even if the second option is possible, the main memory requirement might lead to many partitions, which, in turn, increase the time-to-solution. One obvious way to reduce DRAM footprint of data-intensive applications is to store the data structure on storage, for example using a key-value store, rather than in main memory. This solution comes with a clear performance penalty, but new NVM drives with few GB/s of bandwidth might offer a valid comprise<sup>2</sup>.