Universitat Politècnica de Catalunya

Departament d'Enginyeria Electrònica

## Mixed-Signal Alternate Test and Binning Using Digitally Encoded Signatures

Thesis submitted in partial fulfillment of the requirements for the PhD Degree issued by the Universitat Politècnica de Catalunya in its Electronic Engineering Program

Álvaro Gómez Pau

Advisors:

Joan Figueras Pàmies Luz Balado Suárez

JULY 2017

## Acknowledgments

After all these years of research, it comes the time of wrapping things up and writing the thesis. It has not been an easy journey although I have enjoyed every step. On the other hand, I would have not overcome all the difficulties alone, that is why I am grateful to so many people.

First of all, I would like to thank my advisors, Professor Joan Figueras and Professor Luz Balado, for their dedication, advice, trust, support and guidance during my thesis. They have dedicated an endless number of hours discussing, reviewing and guiding me through the amazing world of research. They have been a model to follow, not only in research, but also in facing my professional life.

My gratefulness also goes to all the members and staff of the Departament d'Enginyeria Electrònica at ETSEIB, and specially to those of the QINE research group. Since the beginning of this journey, they all have made me feel like being at home.

I am also grateful to Professor Abhijit Chatterjee from Georgia Institute of Technology and Professor José Pineda de Gyvez from Eindhoven University of Technology for hosting my two short-term research stays in 2013 and 2014, respectively. They introduced me to amazing research topics.

I do not want to forget anyone, but my mind is not capable of remembering all the names of those who, in one way or another, have contributed to my research or have helped me during the course of these years. To all of them, thank you very much.

This thesis has been possible thanks to PhD scholarship BES-2011-044129 under the project TEC2010-18384, funded by the Spanish Ministry of Economy and Competitiveness. Also, the two short-term research stays, EEBB-I-13-07342 and EEBB-I-14-09005, have been funded by the Spanish Ministry of Economy and Competitiveness.

Last but not least, I would like to express my huge gratitude to my family and Neus. They have been my greatest support during all these years. Their help, warmth, understanding and affection have been a fundamental pillar. I would like also to say sorry because all the time that would have had to be ours and it was this thesis. It will be certainly rewarded.

Thank you all!

Álvaro Gómez Pau Barcelona, May 2017

ii

# Contents

| 1        | Intr | oduction                                                         | 1  |

|----------|------|------------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                       | 2  |

|          | 1.2  | Objectives                                                       | 3  |

|          | 1.3  | Thesis Organization and Contributions                            | 3  |

| <b>2</b> | Stat | te of the Art                                                    | 11 |

|          | 2.1  | Alternate Test of Mixed-Signal Circuits                          | 12 |

|          | 2.2  | State of The Art Methods in Alternate Test                       | 13 |

|          |      | 2.2.1 Regression Techniques                                      | 13 |

|          |      | 2.2.2 Classification Techniques                                  | 16 |

|          | 2.3  | Alternate Test of MEMS Systems                                   | 19 |

|          | 2.4  | Binning of Mixed-Signal Circuits                                 | 20 |

|          | 2.5  | Selection of Alternate Measurements                              | 22 |

| 3        | Alte | ernate Test and Binning Based on Octree Encoded Signatures       | 23 |

|          | 3.1  | Test of Mixed-Signal Circuits Using Digitally Encoded Signatures | 23 |

|          |      | 3.1.1 Octree Encoding Fundamentals                               | 24 |

|          |      | 3.1.2 Test Using Octree Data Structures                          | 28 |

|          |      | 3.1.3 Efficiency Metrics                                         | 28 |

|          | 3.2  | Test Application: Band-Pass Biquad Filter                        | 31 |

|          |      | 3.2.1 Filter Design and Test Specifications                      | 31 |

#### CONTENTS

|   |      | 3.2.2  | Alternate Measurements Space                                                                                | 32       |

|---|------|--------|-------------------------------------------------------------------------------------------------------------|----------|

|   |      | 3.2.3  | Statistical Training Phase                                                                                  | 34       |

|   |      | 3.2.4  | Simulation Results                                                                                          | 36       |

|   | 3.3  | Test A | application: Low-Pass Biquad Filter with Boundary Densification                                             | 40       |

|   |      | 3.3.1  | Statistical Training Phase with Boundary Densification $\ . \ . \ .$                                        | 40       |

|   |      | 3.3.2  | Simulation Results                                                                                          | 48       |

|   | 3.4  | Binnir | ng of Mixed-Signal Circuits Using Digitally Encoded Signatures .                                            | 51       |

|   |      | 3.4.1  | Octree Encoding for Quality Binning                                                                         | 54       |

|   |      | 3.4.2  | Binning Using Octree Data Structures                                                                        | 56       |

|   |      | 3.4.3  | Efficiency Metrics: Bin Escapes                                                                             | 57       |

|   | 3.5  | Binnir | ng Application: 4th Order Band-Pass Butterworth Filter $\ldots$ .                                           | 57       |

|   |      | 3.5.1  | Filter Design and Bin Specifications                                                                        | 57       |

|   |      | 3.5.2  | Alternate Measurements Space                                                                                | 59       |

|   |      | 3.5.3  | Statistical Training Phase                                                                                  | 60       |

|   |      | 3.5.4  | Simulation Results                                                                                          | 61       |

|   |      | 3.5.5  | Comparison with Support Vector Machines Classifier                                                          | 64       |

|   | 3.6  | Summ   | ary and Comments                                                                                            | 66       |

| 4 | Alte | ernate | Test of Heterogeneous Systems                                                                               | 71       |

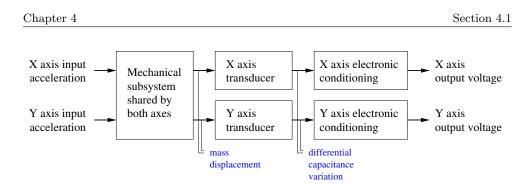

|   | 4.1  | Integr | ated MEMS Capacitive Accelerometers                                                                         | 71       |

|   |      | 4.1.1  | Mechanical Subsystem                                                                                        | 72       |

|   |      | 4.1.2  | Capacitive Transducer Subsystem                                                                             | 73       |

|   |      | 4.1.3  | Electronic Conditioning Subsystem                                                                           | 74       |

|   | 4.2  |        | g Characterization and Excitation of Dual Axis Capacitive Ac-<br>meters                                     | 74       |

|   |      | 4.2.1  | Vertical Spinning Proposal                                                                                  | 75       |

|   |      | 4.2.2  | Lissajous Compositions Under Parametric Defects                                                             | 76       |

|   |      | 4.2.3  | Metric Definition $\ldots$ | 82       |

|   |      | 4.2.4  | Diagnosis Efficiency Evaluation                                                                             | 82       |

|   |      |        |                                                                                                             |          |

|   | 4.3  |        | cation to Accelerometer Sensitivity Test Using Octrees                                                      | 83       |

|   | 4.3  |        | cation to Accelerometer Sensitivity Test Using Octrees Statistical Training Phase                           | 83<br>83 |

iv

#### CONTENTS

|          | 4.4  | Applie  | cation to Accelerometer Axis Misalignment Diagnosis                                    | . 90  |

|----------|------|---------|----------------------------------------------------------------------------------------|-------|

|          |      | 4.4.1   | Misalignment Metric Evaluation                                                         | . 92  |

|          |      | 4.4.2   | Misalignment Diagnosis Efficiency Evaluation                                           | . 92  |

|          |      | 4.4.3   | Experimental Setup                                                                     | . 95  |

|          |      | 4.4.4   | Experimental Results                                                                   | . 97  |

|          | 4.5  | Summ    | hary and Comments                                                                      | . 99  |

| <b>5</b> | Imp  | proving | g Octree Tessellation Efficiency                                                       | 103   |

|          | 5.1  | Octree  | e Ensemble                                                                             | . 103 |

|          |      | 5.1.1   | Multi-Directional Tessellations in the Measurements Space .                            | . 104 |

|          |      | 5.1.2   | Test Application: Band-Pass Biquad Filter                                              | . 105 |

|          |      | 5.1.3   | Simulation Results                                                                     | . 109 |

|          | 5.2  | Multi   | ple Specification Band Guarding                                                        | . 116 |

|          |      | 5.2.1   | Multiple Specification Band Guarding in the Indirect Measurements Space                | . 117 |

|          |      | 5.2.2   | Test Application: Band-Pass Butterworth Filter                                         | . 118 |

|          |      | 5.2.3   | Simulation Results                                                                     | . 122 |

|          | 5.3  | Summ    | nary and Comments                                                                      | . 130 |

| 6        | Sele | ection  | and Acquisition of Analog Signatures                                                   | 133   |

|          | 6.1  | Select  | ion of Analog Signatures for Mixed-Signal Testing                                      | . 134 |

|          |      | 6.1.1   | Criterion for Selecting a Subset of Alternate Measurements for<br>Mixed-Signal Testing | . 134 |

|          |      | 6.1.2   | Test Application: Band-Pass Biquad Filter                                              | . 137 |

|          |      | 6.1.3   | Simulation Results                                                                     | . 140 |

|          | 6.2  | Acqui   | sition of Analog Signatures for Mixed-Signal Testing                                   | . 143 |

|          |      | 6.2.1   | Adaptive Signature Generator System                                                    | . 143 |

|          |      | 6.2.2   | Adaptive Signature Generator System Setup                                              | . 146 |

|          |      | 6.2.3   | Experimental Results Testing a Biquad Filter                                           | . 152 |

|          | 6.3  | Summ    | nary and Comments                                                                      | . 155 |

| 7        | Cor  | nclusio | ns and Future Work                                                                     | 159   |

|          | 7.1  | Contr   | ibutions and Conclusions                                                               | . 159 |

| vi           |                       |                |    |      |      | CONT | ENTS  |

|--------------|-----------------------|----------------|----|------|------|------|-------|

|              | 7.2                   | Future Work .  |    | <br> | <br> |      | . 161 |

| $\mathbf{A}$ | $\operatorname{List}$ | of Publication | ıs |      |      |      | 165   |

# List of Figures

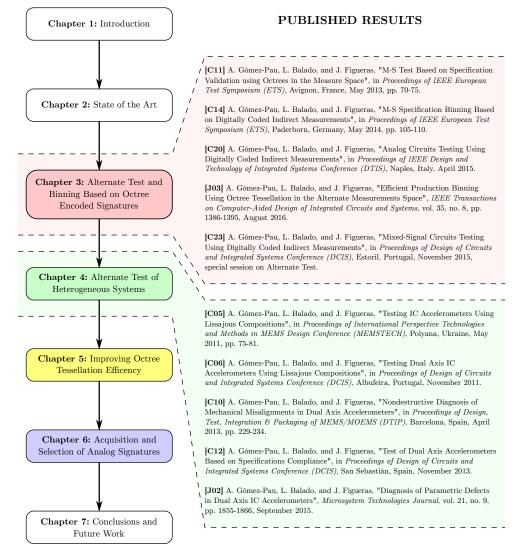

| 1.1 | Thesis roadmap and published results for chapters 3 and 4                                                                                           | 5  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

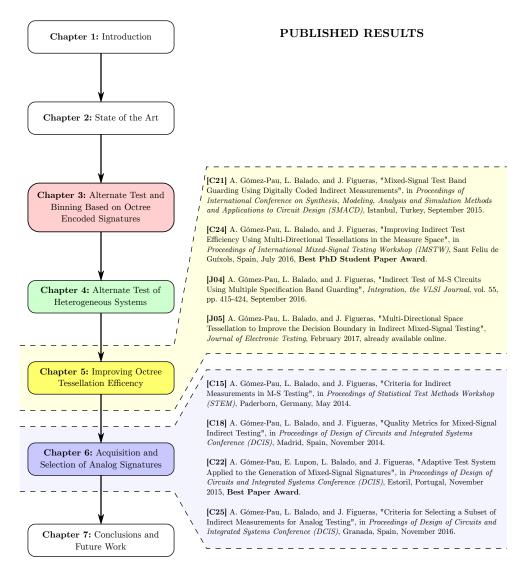

| 1.2 | Thesis roadmap and published results for chapters 5 and 6                                                                                           | 6  |

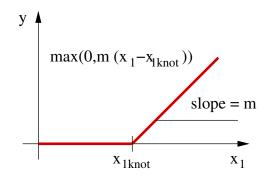

| 2.1 | Example of MARS basis function                                                                                                                      | 15 |

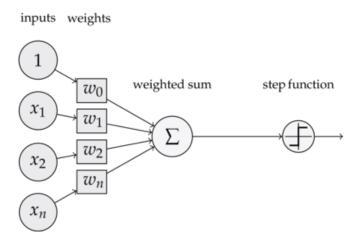

| 2.2 | Basic perceptron structure                                                                                                                          | 17 |

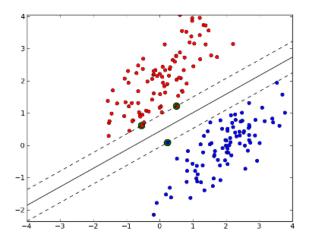

| 2.3 | Example of linear SVM machine separator and the generated bound-<br>ary with maximum margin separation. The support vectors are also<br>highlighted | 18 |

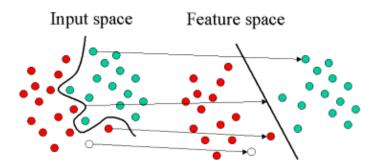

| 2.4 | Example of a non linear SVM machine separator after the transforma-<br>tion of the input space using a non linear kernel function.                  | 19 |

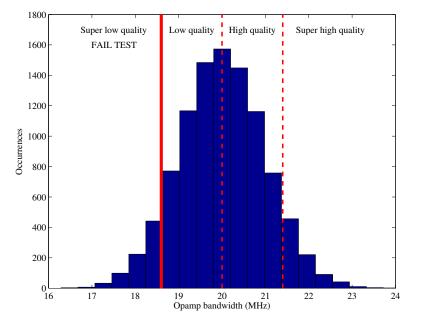

| 2.5 | Example of performance bins for alternate analog and mixed-signal quality binning                                                                   | 21 |

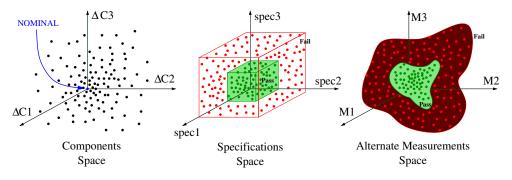

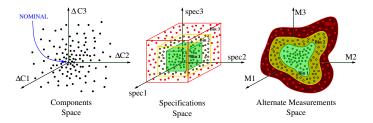

| 3.1 | Components, specifications, and measurements spaces $\ldots \ldots \ldots$                                                                          | 24 |

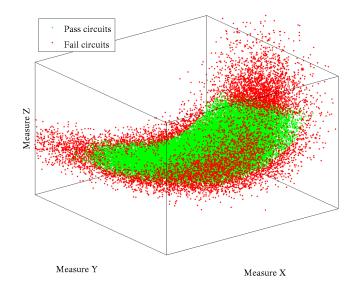

| 3.2 | Example of alternate measurement space                                                                                                              | 25 |

| 3.3 | Example of a quadtree generated with random data $\ldots \ldots \ldots \ldots$                                                                      | 26 |

| 3.4 | Two dimensional octree encoding two clusters                                                                                                        | 27 |

| 3.5 | Graph representation of the octree shown in Figure $3.4$                                                                                            | 27 |

| 3.6 | Algorithm implementing the testing procedure using octrees                                                                                          | 28 |

| 3.7 | Example of octree node data structure defined in ANSI C $\ . \ . \ . \ .$                                                                           | 31 |

| 3.8 | Band pass filter schematic                                                                                                                          | 31 |

| 3.9 | Analog signature generation and compaction                                                                                                          | 33 |

#### LIST OF FIGURES

| 3.10 | Analog signature generation using orthogonal signal composition $\ . \ .$ .                                          | 34 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

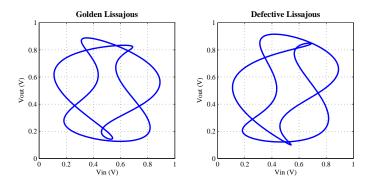

| 3.11 | Example of Lissajous compositions as analog signatures $\ldots \ldots \ldots$                                        | 34 |

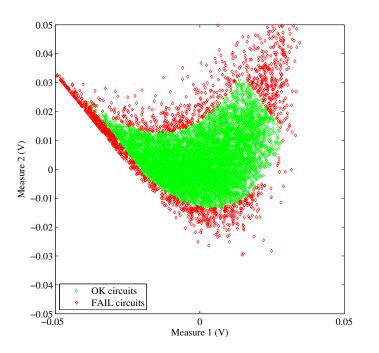

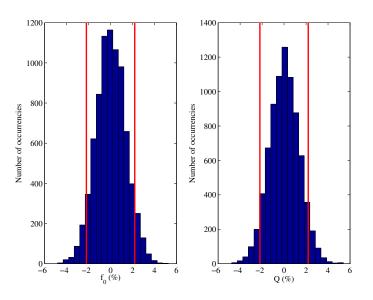

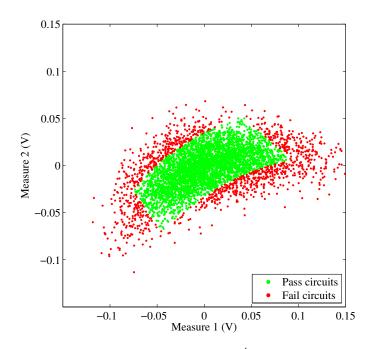

| 3.12 | Band-pass Biquad filter samples in the measure space $\ldots$                                                        | 35 |

| 3.13 | Filter's functional specifications distributions                                                                     | 35 |

| 3.14 | Resulting octree after the training phase for the circuit shown in Figure 3.12                                       | 36 |

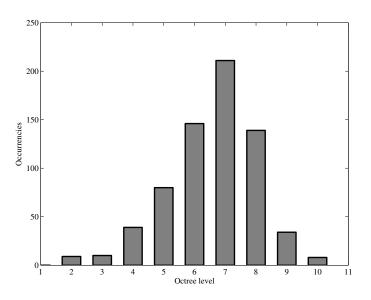

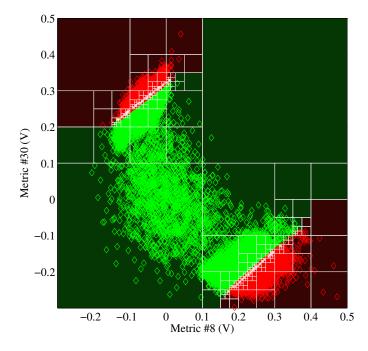

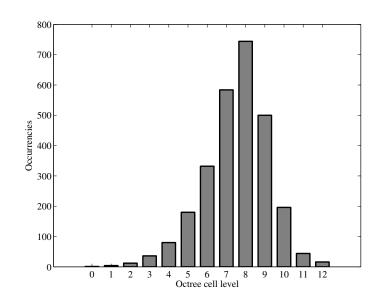

| 3.15 | Octree levels distribution of the octree shown in Figure 3.14                                                        | 37 |

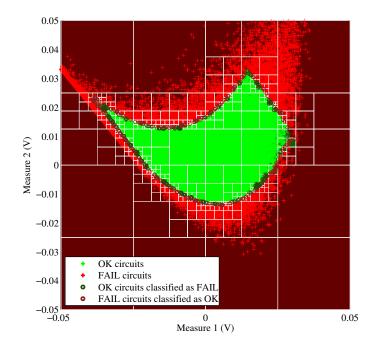

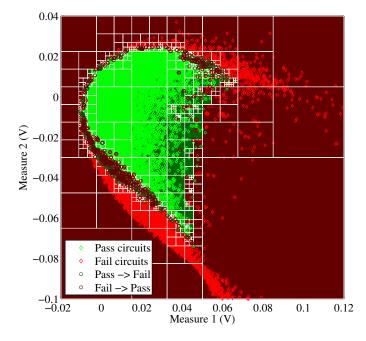

| 3.16 | Testing phase results using $50 \times 10^3$ Monte Carlo samples $\ldots \ldots \ldots$                              | 38 |

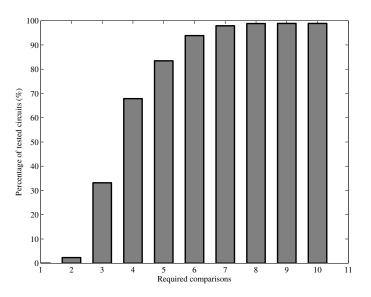

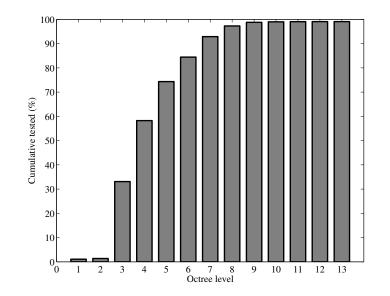

| 3.17 | Cumulative required comparisons distribution for the testing phase using octrees                                     | 39 |

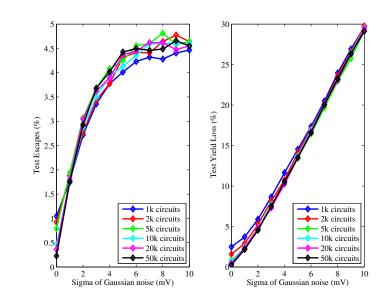

| 3.18 | Analog test metrics as a function of noise levels                                                                    | 40 |

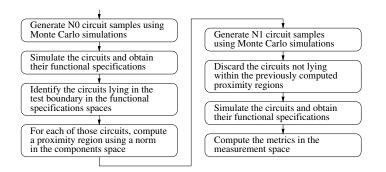

| 3.19 | Densification algorithm to increase the number of circuits near the test decision boundary                           | 41 |

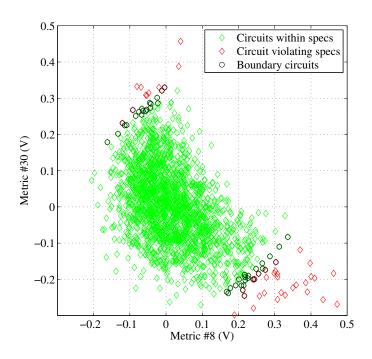

| 3.20 | Monte Carlo simulations of the Biquad filter depicted in Figure 3.23 $$ .                                            | 42 |

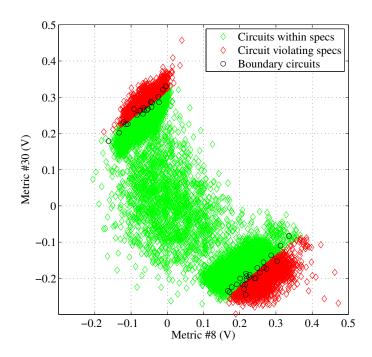

| 3.21 | Monte Carlo samples of the Biquad filter after the application of the densification procedure                        | 43 |

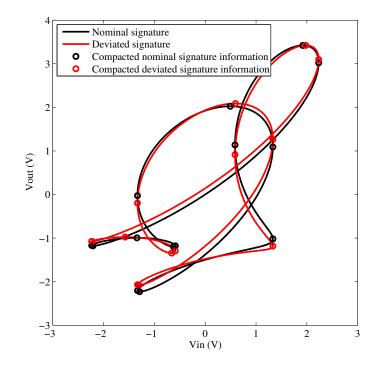

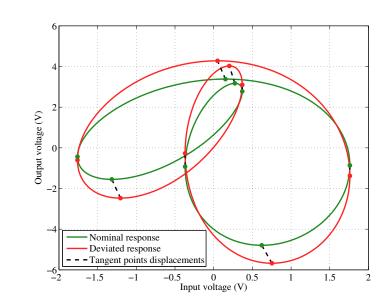

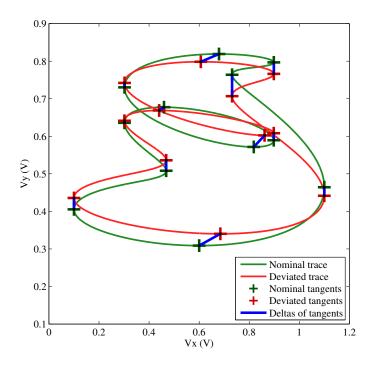

| 3.22 | Lissajous compositions of the nominal and deviated responses when a multitone signal is applied to a low-pass filter | 44 |

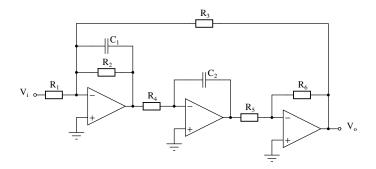

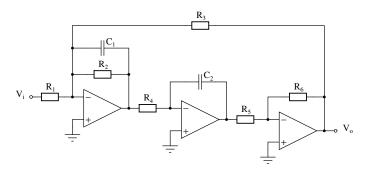

| 3.23 | Schematic of the low-pass state variable filter used as case study $\ . \ . \ .$                                     | 45 |

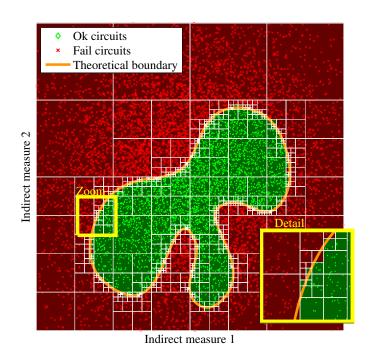

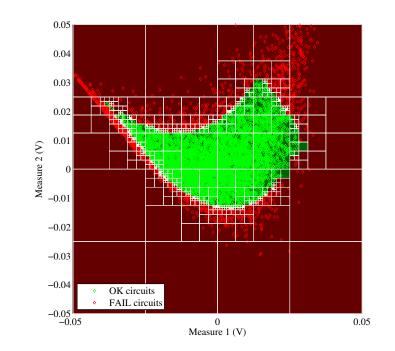

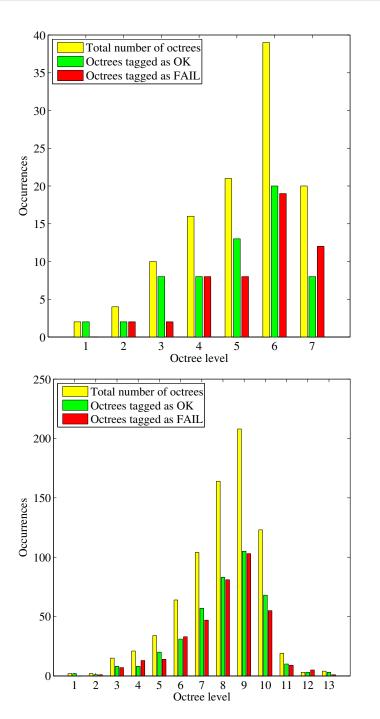

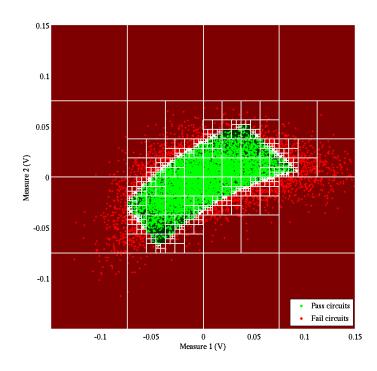

| 3.24 | Quadtree encoding the test acceptance and rejection regions                                                          | 46 |

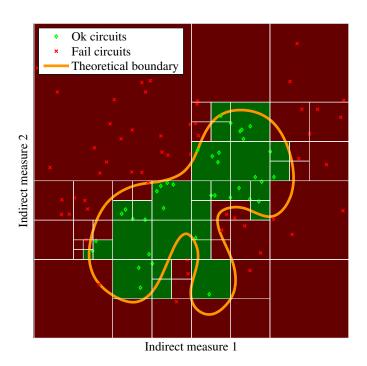

| 3.25 | Resulting octree including the circuit samples generated with the boundary densification algorithm                   | 47 |

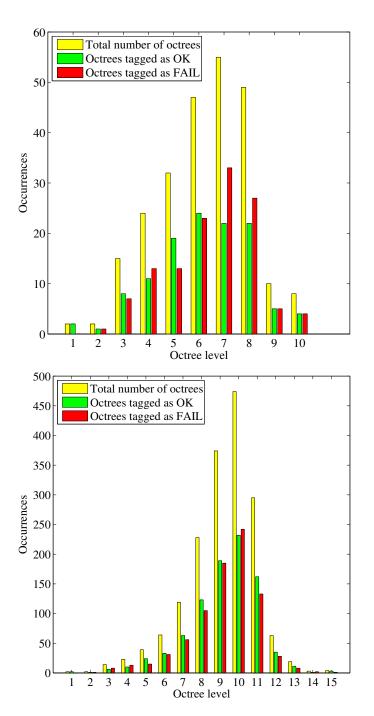

| 3.26 | Octree levels distribution as a function of the Monte Carlo samples<br>used with $N_1/N_0 = 100$                     | 49 |

| 3.27 | Octree levels distribution as a function of the Monte Carlo samples used with $N_1/N_0 = 500$                        | 50 |

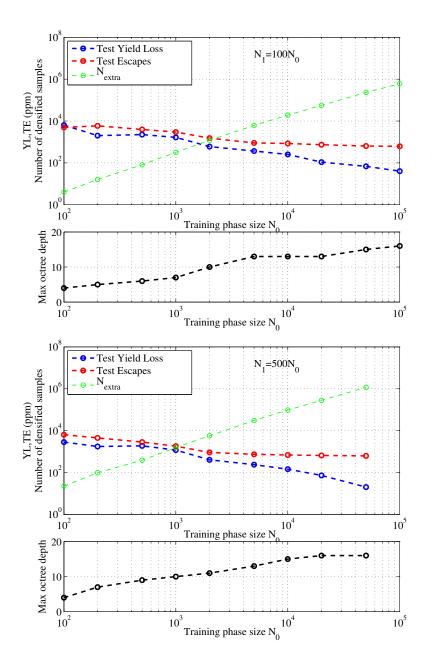

| 3.28 | Analog test metrics for the two densification scenarios of $N_1/N_0 = 100$<br>and $N_1/N_0 = 500$                    | 52 |

| 3.29 | Sketch of the components, specifications, and alternate measurements spaces                                          | 53 |

| 3.30 | Graph representation of the quadtree depicted in Figure 3.31 $\ldots$ .                                              | 54 |

| 3.31 | Example of a quadtree generated using 100 bivariate Gaussian samples and three bins                                  | 55 |

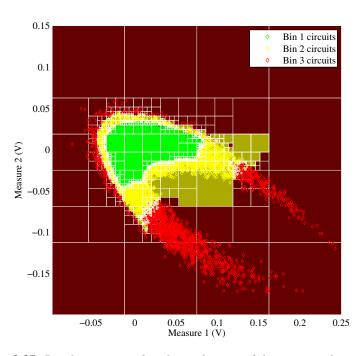

| 3.32 | Monte Carlo samples of a 4th order band-pass Butterworth filter                                                      | 56 |

viii

| 3.33 | Schematic of the 4th order band-pass Butterworth filter used as case study                                                                          | 58 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.34 | Input-output composition when a 3 tone signal is applied to the band-<br>pass Butterworth filter                                                    | 60 |

| 3.35 | Kendall's Tau rank correlation coefficients between all the possible pairs of candidate alternate measurements                                      | 61 |

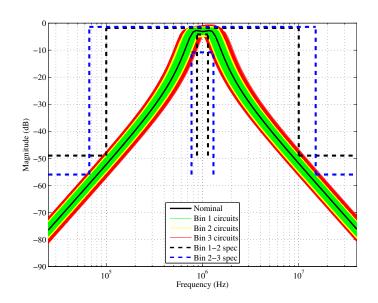

| 3.36 | Magnitude Bode plots of the band-pass Butterworth filter $\ldots$ .                                                                                 | 62 |

| 3.37 | Octree encoding of the alternate measurements space shown in Figure 3.32                                                                            | 63 |

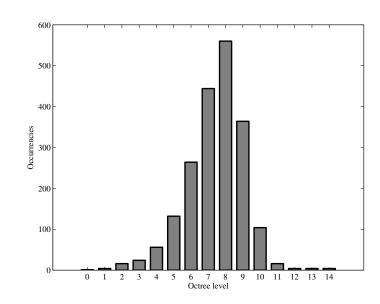

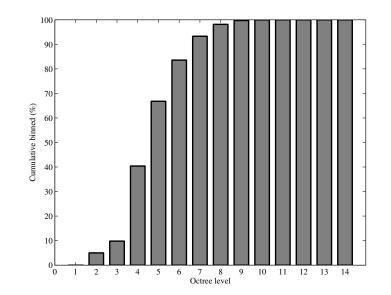

| 3.38 | Octree levels distribution for the encoding shown in Figure 3.37                                                                                    | 64 |

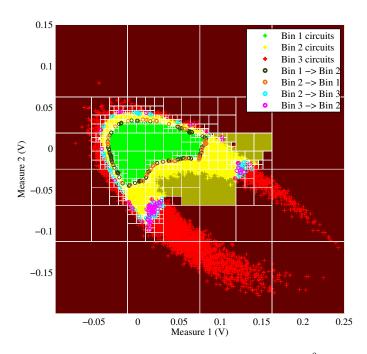

| 3.39 | Binning phase results using a set of $50\times 10^3$ Monte Carlo circuit samples                                                                    | 65 |

| 3.40 | Cumulative percentage of binned circuits as a function of the achieved octree level                                                                 | 66 |

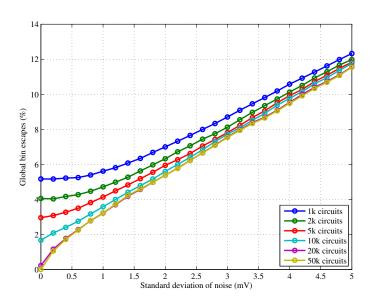

| 3.41 | Global bin escapes as a function of the number of circuit samples used<br>in the training phase and the noise present in the alternate measurements | 67 |

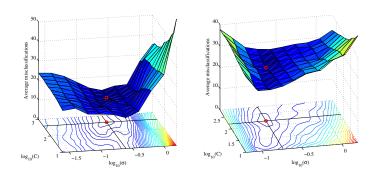

| 3.42 | Grid search results for the comparison with support vector machines $% \mathcal{A}^{(n)}$ .                                                         | 68 |

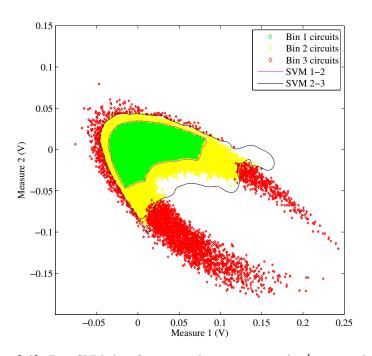

| 3.43 | Best SVM classifiers using the training set shown in Figure 3.32                                                                                    | 69 |

| 4.1  | Stages of the acceleration to voltage transduction chain for integrated capacitive MEMS accelerometers                                              | 72 |

| 4.2  | Sketch of capacitive accelerometer inertial mass and comb fingers                                                                                   | 73 |

| 4.3  | Sketch of a dual axis accelerometer mounted in a vertical spinning wheel and the accelerations involved                                             | 75 |

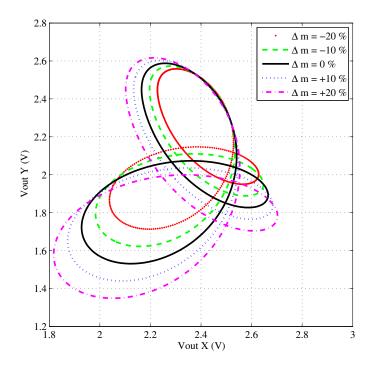

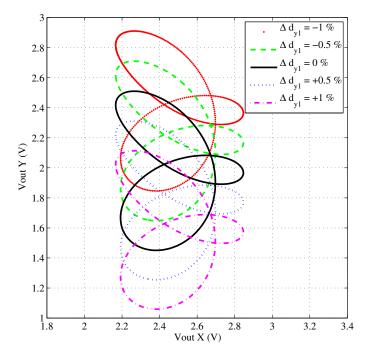

| 4.4  | Simulated Lissajous compositions of a dual axis IC accelerometer for different defect levels in the inertial mass                                   | 77 |

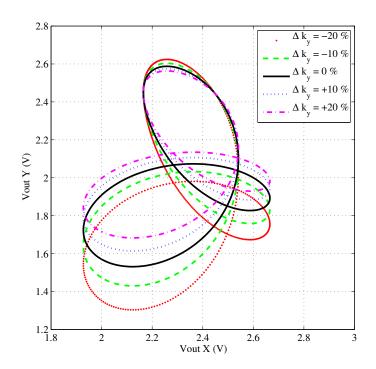

| 4.5  | Simulated Lissajous compositions of a dual axis IC accelerometer for different defect levels in the spring constant                                 | 78 |

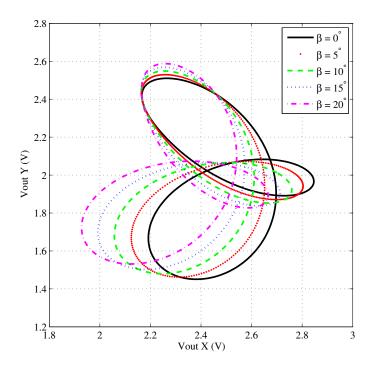

| 4.6  | Simulated Lissajous compositions of a dual axis IC accelerometer for different defect levels in axes misalignment                                   | 79 |

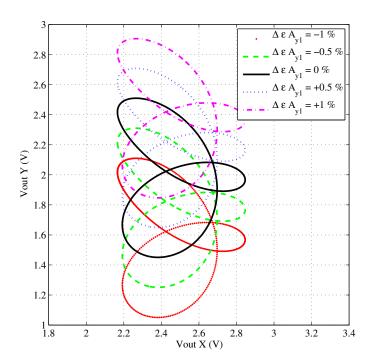

| 4.7  | Simulated Lissajous compositions of a dual axis IC accelerometer for different defect levels in the medium permittivity or plate area               | 80 |

| 4.8  | Simulated Lissajous compositions of a dual axis IC accelerometer for different defect levels in the rest distance between plates                    | 81 |

| 4.9  | Flow diagram showing an overview of the steps that characterize the training and testing phases                                                     | 84 |

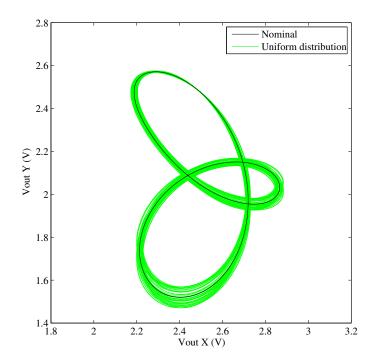

| 4.10 | Set of 50 Lissajous compositions generated with devices which sensitivities have been drawn from non correlated uniform distributions                        | 85  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

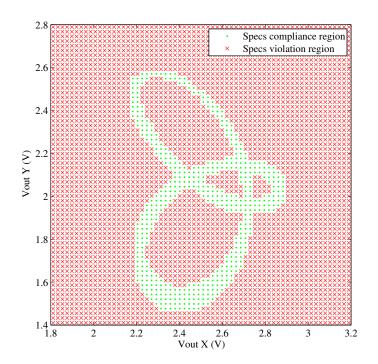

| 4.11 | Resulting specifications compliance and violation regions after digi-<br>tizing the analog information of the Lissajous compositions shown in<br>Figure 4.10 | 86  |

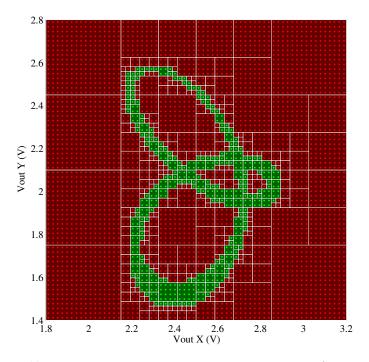

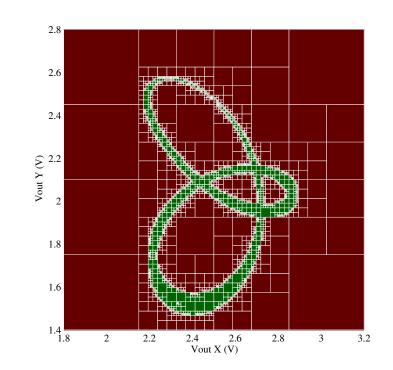

| 4.12 | Octree encoding of the specifications compliance/violation regions for the case study presented in Figure 4.11                                               | 87  |

| 4.13 | Octree encoding of the specifications compliance/violation regions for the case study presented in Figure 4.12                                               | 88  |

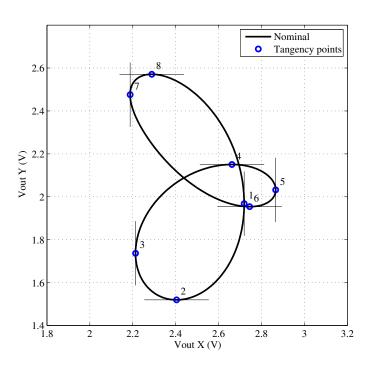

| 4.14 | Lissajous trace information is replaced by its points of tangency with vertical and horizontal tangent lines                                                 | 89  |

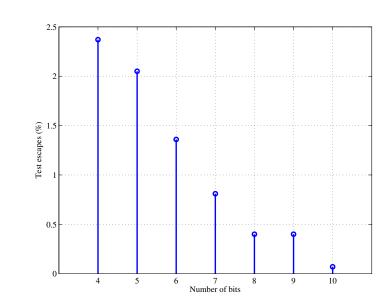

| 4.15 | Test escapes as a function of the number of bits used to encode the octree data structure                                                                    | 90  |

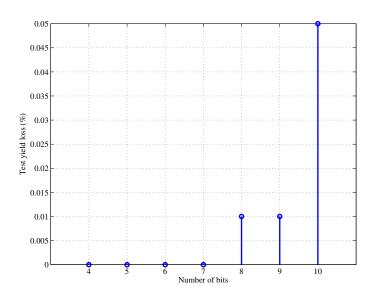

| 4.16 | Test yield loss as a function of the number of bits used to encode the octree data structure                                                                 | 91  |

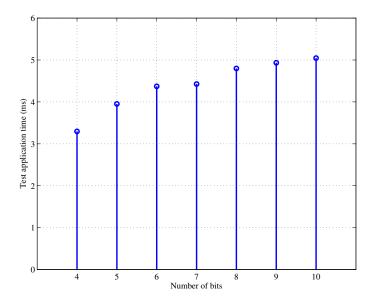

| 4.17 | Test application time as a function of the number of bits used to encode the octree data structure                                                           | 91  |

| 4.18 | Lissajous trace compaction using the points of tangency with vertical and horizontal tangent lines                                                           | 93  |

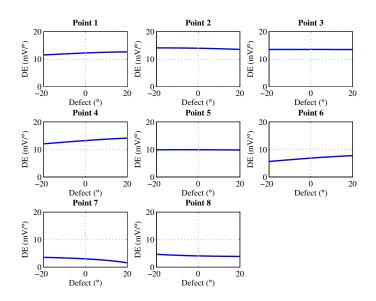

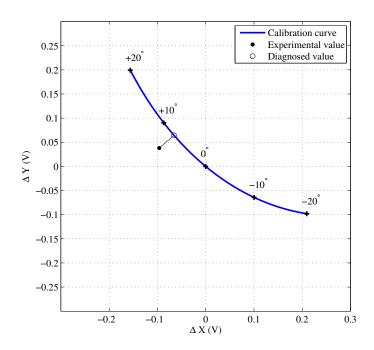

| 4.19 | Calibration curves for $\beta$ angle ranging from $-20^{\circ}$ to $+20^{\circ}$                                                                             | 94  |

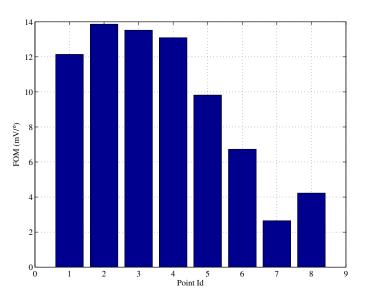

| 4.20 | Diagnosis efficiency for each of the tangent points as a function of misalignment level                                                                      | 94  |

| 4.21 | Diagnosis efficiency FOMs for each of the tangent points identified in the Lissajous curve                                                                   | 95  |

| 4.22 | Photography of the experimental setup where the device is mounted $\ .$                                                                                      | 96  |

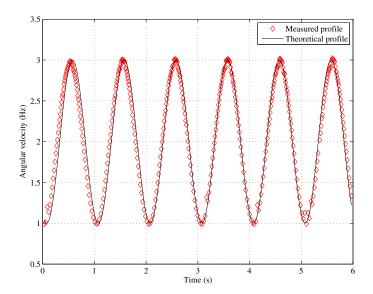

| 4.23 | Simulated and measured angular velocity profiles at the motor shaft $\ .$                                                                                    | 96  |

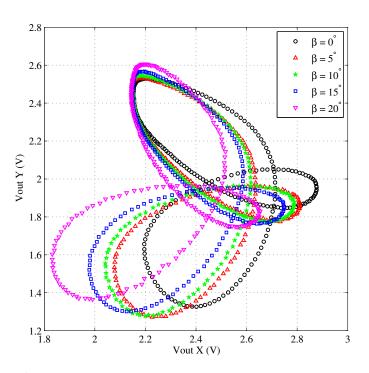

| 4.24 | Experimental Lissajous compositions of a dual axis IC accelerometer for $\{0, 5, 10, 15, 20\}^{\circ}$ misalignment angles                                   | 97  |

| 4.25 | Detail on how the experimental diagnosis procedure is carried out for tangency point 1                                                                       | 98  |

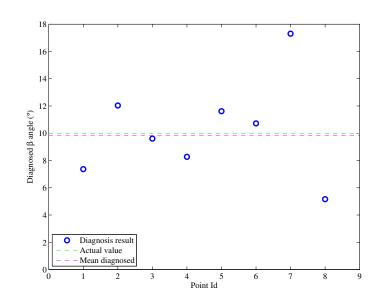

| 4.26 | Diagnosed misalignments for each of the Lissajous tangency points and the weighted averaged diagnosis result                                                 | 100 |

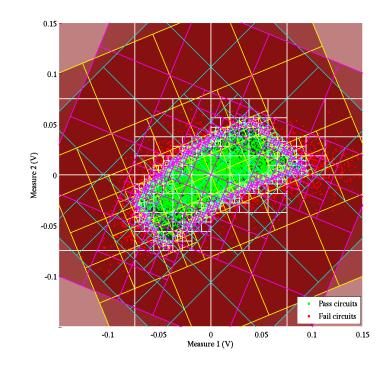

| 5.1  | Example of a synthetic training set of indirect measurements and the corresponding octree encodings when $N_{\text{octrees}} = 3 \dots \dots \dots$          | 105 |

| 5.2  | Detail of the three rotated octrees depicted in Figure 5.1                                                                                                   | 106 |

|      |                                                                                                                                                              |     |

х

#### LIST OF FIGURES

| 5.3  | Example of multi-directional tessellation with $N_{\rm octrees} = 1$ (left) and $N_{\rm octrees} = 5$ (right) using the synthetic data set shown in Figure 5.1 . 106                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

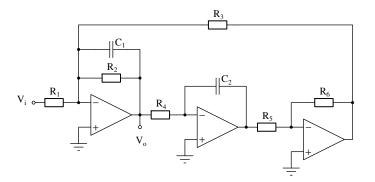

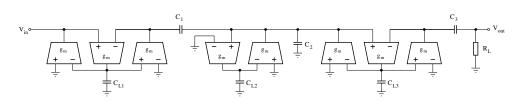

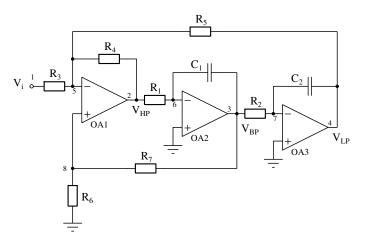

| 5.4  | Schematic of the Tow-Thomas Biquad filter used as case study $\ . \ . \ . \ 107$                                                                                                            |

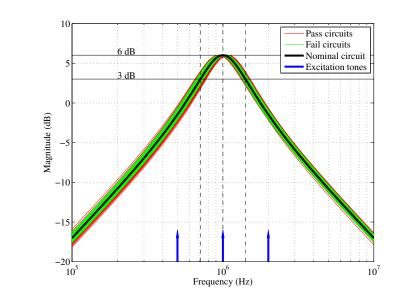

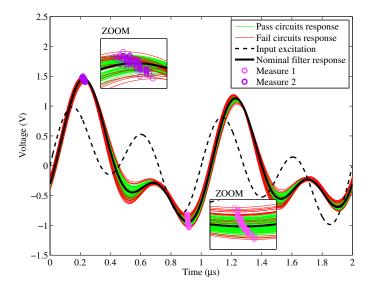

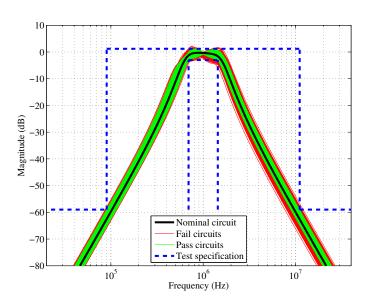

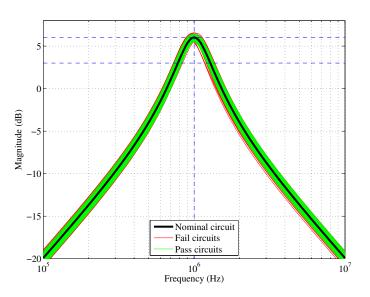

| 5.5  | Magnitude Bode diagrams of the band-pass Biquad filter used as case<br>study                                                                                                                |

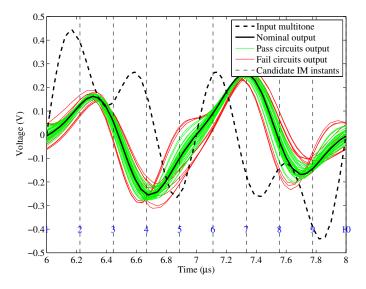

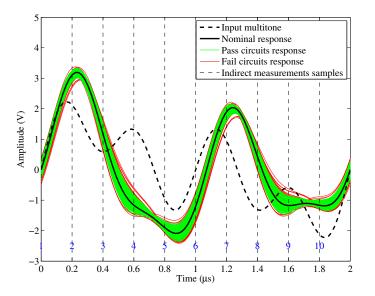

| 5.6  | Response of the band-pass Biquad filter when is excited with a multi-<br>tone signal                                                                                                        |

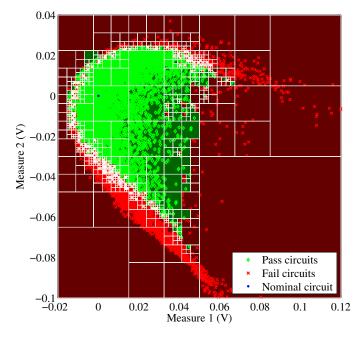

| 5.7  | Indirect measure space showing $10^4$ Monte Carlo circuit samples before applying the proposed multi-directional octree encoding technique $~$ . $~$ 110                                    |

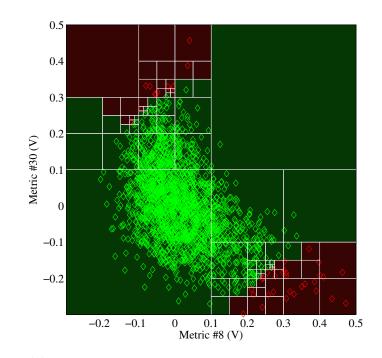

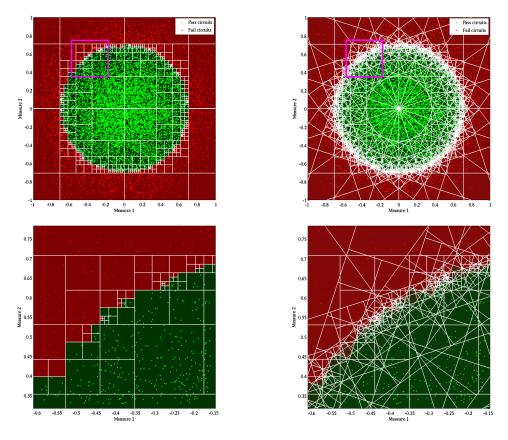

| 5.8  | Indirect measure space encoded using a single octree                                                                                                                                        |

| 5.9  | Indirect measure space encoded using 4 octrees                                                                                                                                              |

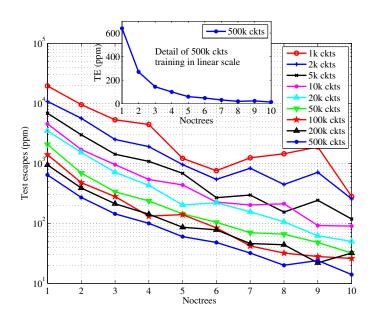

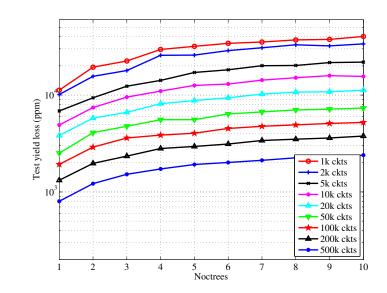

| 5.10 | Incurred test escapes metric resulting from the application of the pro-<br>posed multi-directional tessellation technique                                                                   |

| 5.11 | Incurred test yield loss metric resulting from the application of the proposed multi-directional tessellation technique                                                                     |

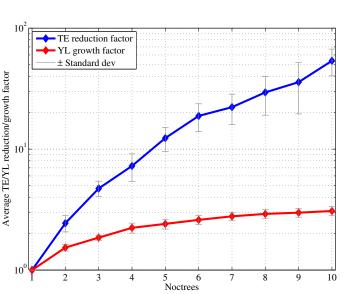

| 5.12 | Average reduction and growth factors for the incurred false positive<br>and false negatives test outcomes with respect to a single octree encoding115                                       |

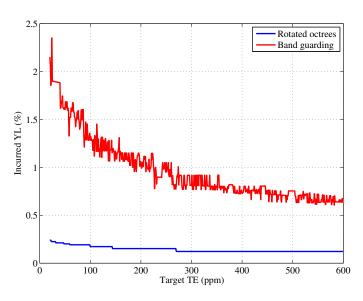

| 5.13 | Incurred test yield loss metric as a function of a given test escape target $117$                                                                                                           |

| 5.14 | Example of multiple specification band guarding in the specifications space                                                                                                                 |

| 5.15 | Schematic of the 6th order band-pass Butterworth filter used as a case study                                                                                                                |

| 5.16 | Magnitude Bode diagrams obtained by Monte Carlo simulations using technology statistical corner                                                                                             |

| 5.17 | Response of the Butterworth filter when it is excited with a multitone signal                                                                                                               |

| 5.18 | Resulting octree after the application of the training phase to the set of $10^4$ Butterworth circuit samples shown in Figure ??                                                            |

| 5.19 | Levels distribution for the octree shown in Figure 5.18 $\ldots \ldots \ldots 124$                                                                                                          |

| 5.20 | Testing phase results using the octree shown in Figure 5.18 with band guarding factors of $r_1 = r_2 = 1$                                                                                   |

| 5.21 | Cumulative percentage of tested circuits as a function of the achieved octree level for the testing phase                                                                                   |

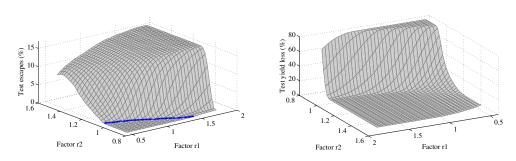

| 5.22 | Test escapes (left) and test yield loss (right) metrics as a function of the band guarding factors $r_1$ and $r_2$                                                                          |

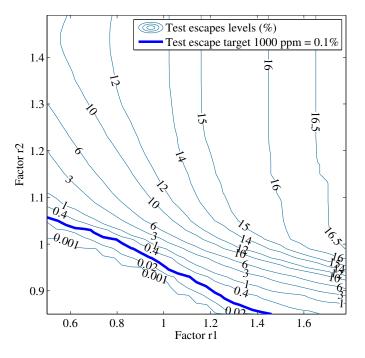

| 5.23 | Test escapes contour levels in the $r_1 - r_2$ plane $\ldots \ldots \ldots$ |

#### LIST OF FIGURES

| 5.24 | Test yield loss contour levels in the $r_1 - r_2$ plane together with the resulting 1000 ppm test escape level from Figure 5.23                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1  | Algorithm to select a subset of indirect measurements for mixed-signal testing                                                                               |

| 6.2  | Schematic of the KHN Biquad filter used in the case study $~~\ldots~$ . 138                                                                                  |

| 6.3  | Steady state transient response of the Biquad filter when it is excited with a multitone signal                                                              |

| 6.4  | Filter's frequency response obtained by Monte Carlo simulation 141                                                                                           |

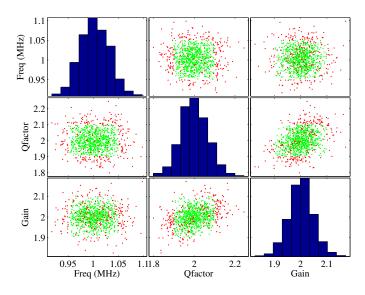

| 6.5  | Pairwise scatter plots and distributions of filter performances obtained<br>by Monte Carlo simulation                                                        |

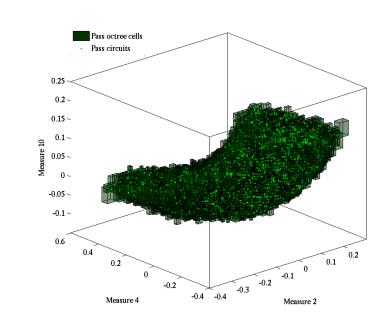

| 6.6  | Octree generated in the training phase encoding pass/fail circuits $144$                                                                                     |

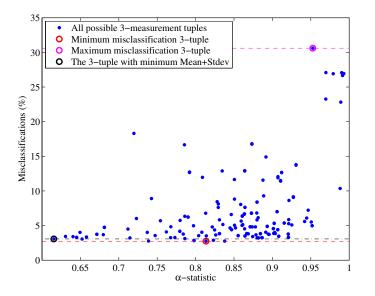

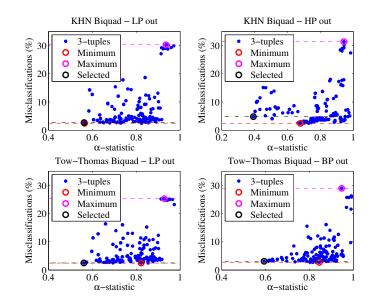

| 6.7  | Scatter plot of test misclassifications as a function of the selection statistic                                                                             |

| 6.8  | Scatter plot of test misclassifications as a function of the selection statistic for several Biquad topologies and filter outputs $\ldots \ldots \ldots 146$ |

| 6.9  | Nominal and deviated analog signatures resulting from an XY signal composition                                                                               |

| 6.10 | Integrated analog signal monitoring and digital signature generation $% \left( {{{\mathbf{r}}_{0}},{\mathbf{r}}_{0}} \right)$ . 148                          |

| 6.11 | Composition of two analog signals and four possible observation windows $148$                                                                                |

| 6.12 | Basic architecture of the signature generator system $\hfill \ldots \hfill 149$                                                                              |

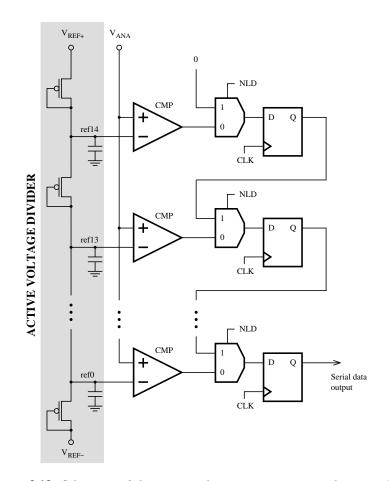

| 6.13 | Schematic of the integrated signature generator subsystem 150                                                                                                |

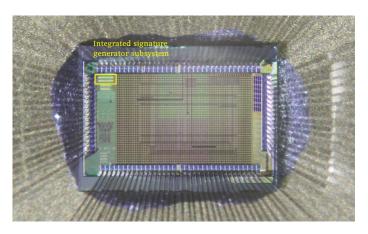

| 6.14 | Layout of the integrated signature generator subsystem $\ \ .$                                                                                               |

| 6.15 | Photograph of the integrated signature generator subsystem fabricated<br>in an industrial 65 nm CMOS technology                                              |

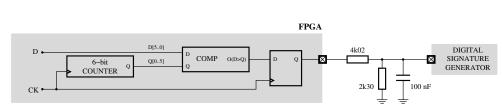

| 6.16 | Architecture of the 6-bit DAC based on an IWOC digital pattern generator                                                                                     |

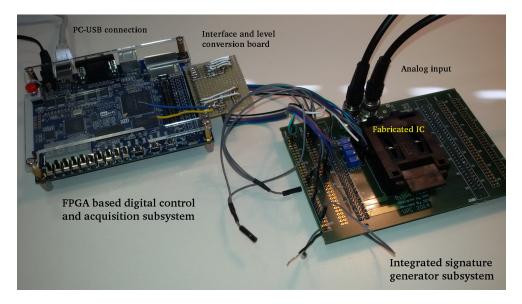

| 6.17 | Photograph of the experimental setup $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 153$                                                    |

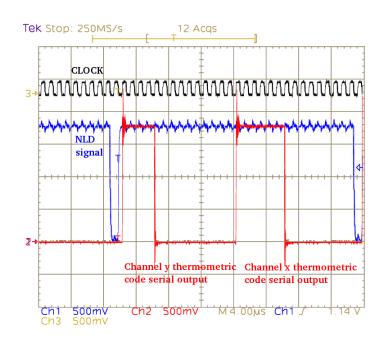

| 6.18 | Oscilloscope chronograms of the signals involved in the serial trans-<br>mission of the signature information                                                |

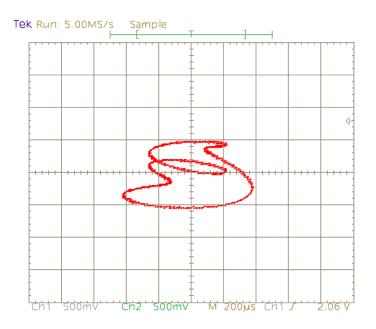

| 6.19 | Measured Lissajous composition of the input/output signals when a multitone is applied to a low-pass Biquad filter $\hdots$                                  |

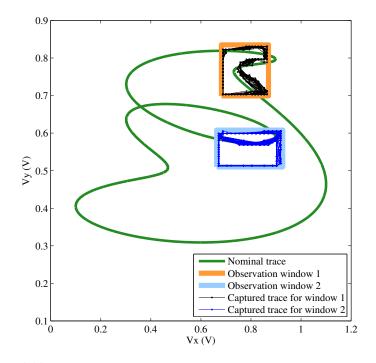

| 6.20 | Simulated XY composition and the digitized experimental trace within the two observation windows considered in this case study 156                           |

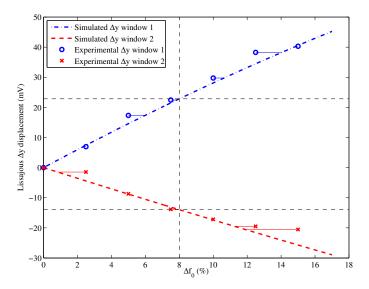

| 6.21 | Simulated and experimental data of the $\Delta y$ displacements of the two tangency points                                                                   |

xii

# List of Tables

| 3.1                                                       | Band-pass Biquad filter test limits                                                                                                                                                                                                                                                       | 32                            |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| 3.2                                                       | Analog test metrics as a function of the number of Monte Carlo samples                                                                                                                                                                                                                    | 37                            |

| 3.3                                                       | Biquad filter functional specifications.                                                                                                                                                                                                                                                  | 45                            |

| 3.4                                                       | Biquad filter testing simulation results                                                                                                                                                                                                                                                  | 48                            |

| 3.5                                                       | Butterworth filter design specifications.                                                                                                                                                                                                                                                 | 58                            |

| 3.6                                                       | Butterworth filter bin limits.                                                                                                                                                                                                                                                            | 59                            |

| 3.7                                                       | Bin escapes matrix for octrees based binning $(\%)$                                                                                                                                                                                                                                       | 62                            |

| 3.8                                                       | SVM classifiers training information                                                                                                                                                                                                                                                      | 68                            |

| 3.9                                                       | Comparison between octrees and support vector machines                                                                                                                                                                                                                                    | 70                            |

| 3.10                                                      | Bin escapes matrix for SVM classifier (%)                                                                                                                                                                                                                                                 | 70                            |

|                                                           |                                                                                                                                                                                                                                                                                           |                               |

|                                                           |                                                                                                                                                                                                                                                                                           |                               |

| 4.1                                                       | Metrics for $10^{\circ}$ misalignment                                                                                                                                                                                                                                                     | 92                            |

| 4.1<br>4.2                                                | Metrics for 10° misalignment                                                                                                                                                                                                                                                              | 92<br>93                      |

|                                                           | FOMs for diagnosis efficiency functions considering different misalign-                                                                                                                                                                                                                   |                               |

| 4.2                                                       | FOMs for diagnosis efficiency functions considering different misalignment levels.                                                                                                                                                                                                        | 93                            |

| 4.2                                                       | FOMs for diagnosis efficiency functions considering different misalignment levels.                                                                                                                                                                                                        | 93<br>99                      |

| 4.2<br>4.3                                                | FOMs for diagnosis efficiency functions considering different misalignment levels.                                                                                                                                                                                                        | 93<br>99                      |

| <ul><li>4.2</li><li>4.3</li><li>5.1</li></ul>             | FOMs for diagnosis efficiency functions considering different misalignment levels.         Experimental diagnosis results and discrepancies.         Band-pass Biquad filter specifications and test limits.                                                                              | 93<br>99<br>107<br>116        |

| <ul><li>4.2</li><li>4.3</li><li>5.1</li><li>5.2</li></ul> | FOMs for diagnosis efficiency functions considering different misalignment levels.       .         Experimental diagnosis results and discrepancies.       .         Band-pass Biquad filter specifications and test limits.       .         Performance and overhead evaluation.       . | 93<br>99<br>107<br>116<br>119 |

| 5.6 | Kendall's Tau rank correlation coefficient between candidate indirect measurement pairs                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------|

| 5.7 | Multiple specification band guarding results                                                                            |

| 5.8 | Multiple specification band guarding results when Gaussian noise is added to the indirect measurements                  |

| 6.1 | Band-pass Biquad filter specifications                                                                                  |

| 6.2 | Kendall's Tau rank correlation coefficients between candidate indirect measurements for the band-pass KHN Biquad filter |

| 6.3 | Measured observation windows limits                                                                                     |

| 6.4 | Measured $\Delta y$ displacements for several $\Delta f_0$ deviation levels and diagnosis and test results              |

Chapter

## Introduction

Society is continuously experiencing the advancements in electrical engineering as well as in computer technology. We all use electronics in a daily basis, consciously or unconsciously. Desktop computers, embedded systems, sensors, and actuators have become common elements in our everyday lifestyle. We all use them and we all expect these devices to function properly in developing the task they are supposed to. Hence, the following question arises: *Who is taking care all these elements function under the required specifications?* Well, test technology comes to the rescue. Every single device or subsystem within an electronic system has been tested, at least, at production stage and probably, if its functionality is critical within the system, it will be periodically tested until the end of its service life. In other words, none of us want the airbag in our car not to deploy in a collision because the embedded accelerometer did not function as expected. This probably gives us an idea of the important and crucial role of testing in the electronic industry.

This thesis is about electronic mixed-signal testing. As mentioned earlier, computers rule the XXI century world, but real world is still analog. Computers are constantly interacting with analog sensors, so there must be some piece of electronics linking these two worlds. This is the mixed-signal domain. For instance, the analog signals provided by sensors need to be filtered, boosted, clipped, or conditioned in any other form. Also, these signals will be digitized in order to allow the interaction with a computer, so an analog to digital conversion will be probably required too. These analog processing steps, amongst others, exemplify the kind of tasks carried out within the mixed-signal realm. At this point, it seems quite reasonable to highlight the importance and crucial role of testing the analog and mixed-signal circuitry within any electronic system. This field, as opposed to the digital domain, entails a considerable number of challenges and open problems with no systematic solutions and therefore, an amazing scenario to dive into.

This chapter serves as a motivation and introduction to the existing challenges in

analog and mixed-signal testing and more specifically, in *alternate* analog and mixedsignal testing. Some of these challenges are briefly exposed and discussed in order to motivate the pursued research of this thesis. The succinct motivation presented in this chapter will be later extended by the state of the art in Chapter 2. The general and specific objectives pursued in this thesis are listed and commented. The thesis organization is then described by providing a summary of each of the chapters and by framing them within the thesis roadmap as well as with the published results in referred journals and conferences.

#### 1.1 Motivation

The extreme scalability in current VLSI circuits represents a remarkable challenge in nowadays microelectronics, both in the fields of design and test. New circuits are able to integrate in the same chip a growing number of devices which perform many different functions (digital processing, analog and mixed-signal processing, signal conditioning, data storage, sensing,...). Because of this miniaturization, process variability, temperature, voltage and aging can make the circuit not to fulfill the set of functional specifications. These facts cause new failures to appear and therefore classic test and diagnosis methods based on specifications are becoming even more challenging.

Process variability is responsible of a large percentage of failures in VLSI circuits. Technological difficulties in the fabrication processes together with the hard to predict variability become the main concern in analog and mixed-signal circuits. As circuits scale down, the use of statistical methods in design, testing and diagnosis has grown considerably, what make classical approaches not that efficient. This calls for the need of new strategies to be used in robust designs, test and diagnosis of mixed-signal and heterogeneous circuits.

Classical CMOS processes represent a mature technology which requires advanced methods for testing, diagnosis and robustness as the reduction in size continues according to Moore's Law predictions, but there also exist emerging technologies which require novel paradigms to cope with the arising problems they present. Nevertheless, as it occurs in classical CMOS processes, variability plays a crucial role which has to be taken in special consideration.

Semiconductor industry is heavily demanding close to zero defect levels, specially for those safety critical applications seen in a wide variety of industries, such as automobile or aeronautics. The ever increasing device verification costs, together with the challenges encountered in analog and mixed-signal testing makes it an important focus of research. The cost impact of classic analog test techniques is not acceptable in high volume mixed-signal productions. The aforementioned scenario brings a set of challenges in the field of alternate test of analog and mixed-signal circuits and justifies the need of doing research in order to cope with all these demands and challenges.

### 1.2 Objectives

The objective of this dissertation is to propose methodologies to improve the alternate test and binning of analog and mixed-signal circuits as well as heterogeneous systems under the challenging scenario previously introduced. The forthcoming paragraphs focus on the specific objectives targeted in this thesis.

The efficiency in testing VLSI circuits is usually evaluated in terms of test escapes and test yield loss metrics. Such metrics are considered critical because of the high amount of incurred costs if faulty chips reach the market (test escapes) or non faulty chips are tagged as faulty (test yield loss). The key point to overcome these problems is to develop effective testing and quality binning techniques for analog and mixed-signal circuits to allow the reduction of these analog metrics. The capability of controlling and leveraging these two metrics becomes also a critical step in any production test program therefore allowing a proper adaption to the specified test target.

Heterogeneous systems testing comprise an extra dose of challenge. They include all the difficulties encountered in classical analog and mixed-signal testing plus the ones found due to their inherently non electrical nature depending on the transduction principle they exploit. This dissertation targets the proposal of novel alternate test strategies for testing MEMS accelerometers capable to overcome the existing challenges in dealing with such kind of devices.

Test application time plays a crucial role in analog and mixed-signal test technology and is one of the main objectives pursued in this dissertation. Test application time, together with test efficiency and the required resources conform a set of key aspects to decide whether or not adopting an alternate test technique over a classical specification based test approach. For that reason, the proposal of time efficient alternate testing methodologies for analog and mixed-signal circuits becomes an imperative goal in this thesis.

In an alternate testing scenario, there exist multiple susceptible measurements to perform and use within the testing procedure, albeit not all the measurements serve with the same efficiency to such endeavor. The selection of alternate measurements plays an important role in alternate testing since they must provide, at least, all the information provided by the classical specification based testing method yet keeping their easy to obtain quality. This dissertation targets the proposal of selection algorithms to achieve a suitable subset of alternate measurements for analog and mixed-signal testing.

## 1.3 Thesis Organization and Contributions

The dissertation is organized in seven chapters as sketched in the thesis roadmap shown in Figure 1.1 and Figure 1.2. The diagrams also contain the published results contributing to each of the chapters. The keys used in the references refer to those listed in Appendix A, page 165. The following paragraphs describe the structure of the dissertation and provide a peek on the contents of each chapter. For easy reference, each chapter contents are described based on the two most significant published results in which it is based.

**Chapter 2** presents the challenges in alternate test and binning of mixed-signal circuits. Special care is taken in framing the thesis in the context of the issues derived from process variations due to the extreme miniaturization. Considerable emphasis is devoted to the existing alternate test methods, specially taking care of the challenges encountered when indirect measurements are used to take the test decision. The chapter focuses on the most commonly used regression and classification techniques in the field. As will be shown later, one of the most challenging issues in alternate mixed-signal testing is the encoding of the test acceptance/rejection regions. This makes circuit classification techniques of relevant importance in this thesis.

**Chapter 3** introduces a novel methodology to encode the test acceptance/rejection regions in the alternate measurement space. The proposed technique relies on tessellating the space using  $2^n$ -ary trees. Such binary tessellation is convenient because of its simplicity and straightforward digital implementation. Also, it has the great advantage of being able to encode the space very fast since the tree resolution is increased just where it is needed, i.e. in the surroundings of the test decision boundary. The tree data structure is also advantageous for high volume production testing since the test decision is achieved within a few comparisons due to the fast traversal of the resulting sparse tree. The published results in which Chapter 3 is based on are listed on the roadmap shown in Figure 1.1.

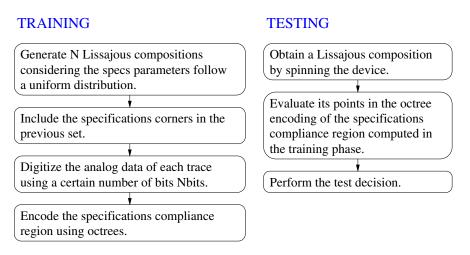

The application of octree data structures to encode the test acceptance/rejection regions was proposed in the paper M-S Test Based on Specification Validation Using Octrees in the Measure Space presented at the European Test Symposium in May 2013. The publication corresponds to reference [C11] in the list shown on page 165. The paper introduces the octree encoding methodology and applies it to test a second order filter affected by parametric variations. The method comprises two phases, namely, training and testing phases. In the former phase, circuit samples are generated based on Monte Carlo simulations, mathematical models or actual production data. The acceptance/rejection region is then encoded using octrees. The latter phase corresponds to the actual high volume production test using the previously encoded octree data structure. The benefits of the methods are discussed based on test escapes and test yield loss metrics as well as the test application time.

The proposed methodology of using octrees to encode the test acceptance/rejection regions can be extended to the more general concept of quality binning of analog and mixed-signal circuits. After volume production, fabricated circuits may present several levels of specification compliance. The manufacturer can take advantage of such levels by selling the fabricated ICs at different price rates according to their respective specification compliance levels. It turns out that octree based space tessellation becomes extremely adequate in such task since just a single tree is able to manage an arbitrary number of disjoint bins with exactly the same advantages shown for the test application.

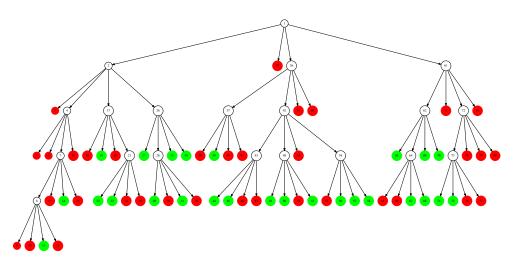

**Figure 1.1:** Thesis roadmap together with the published results contributing to chapters 3 and 4. Refer to Appendix A in page 165 for a complete list of publications.

**Figure 1.2:** Thesis roadmap together with the published results contributing to chapters 5 and 6. Refer to Appendix A in page 165 for a complete list of publications.

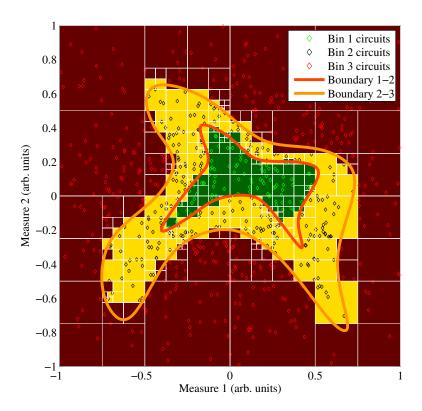

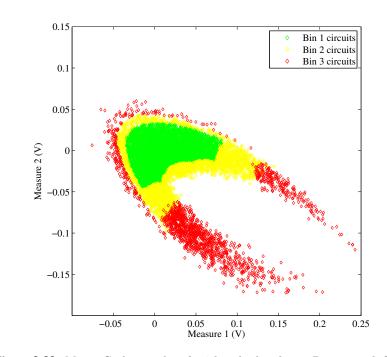

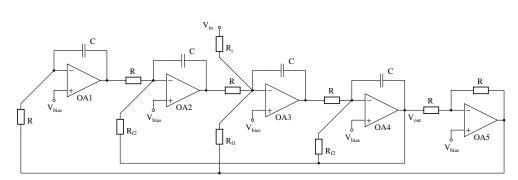

High volume production binning of mixed-signal circuits using octrees was proposed in the article Efficient Production Binning Using Octree Tessellation in the Alternate Measurements Space published in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, volume 35, issue 8, in 2016. The publication corresponds to reference [J03] in the list shown on page 165. The method relies on the same principles mentioned earlier but considering and arbitrary number of bins, which are encoded accordingly, using an octree data structure. In order to illustrate the proposal, the method has been applied to a band-pass Butterworth filter considering three specification bins as a proof of concept. Successful simulation results are reported showing considerable advantages as compared to a SVM based classifier. Similar bin misclassifications are obtained with both methods while the binning time is 5 times faster when using octrees than when using the SVM based classifier.

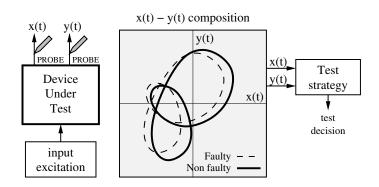

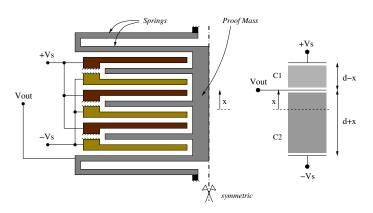

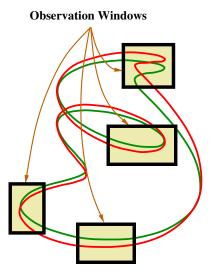

**Chapter 4** is devoted to test heterogeneous systems, and more concisely, to MEMS accelerometers testing. As previously mentioned, testing heterogeneous systems is even more challenging than testing classical mixed-signal circuits due to their inherently non electrical nature. For the case of MEMS accelerometers, their mechanical subsystem must be mechanically excited in order to emulate the actual device operating conditions. Chapter 4 presents a novel methodology for testing MEMS accelerometers by using a vertical spinning wheel setup. This provides a rich kinematic excitation to the DUT as well as being able to capture parametric and catastrophic defects via the orthogonal composition of device outputs. Such composition conforms the alternate measurement space which is then tessellated using the octree encoding technique introduced in Chapter 3. Alternatively, the analog signature can be processed and compacted to extract the necessary information which allows the testing of the device. The published results in which Chapter 4 is based on are listed on the roadmap shown in Figure 1.1.

Testing MEMS accelerometers using octree tessellation was proposed in the paper Test of Dual Axis Accelerometers Based on Specifications Compliance presented at the Design of Circuits and Integrated Systems Conference in November 2013. The publication corresponds to reference [C12] in the list of publications shown on page 165. The paper uses the aforementioned kinematic excitation and encodes the Lissajous alternate space using octrees following the methodology presented in Chapter 3.

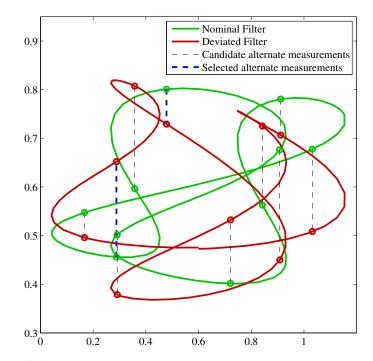

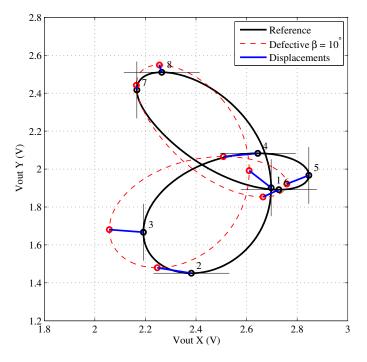

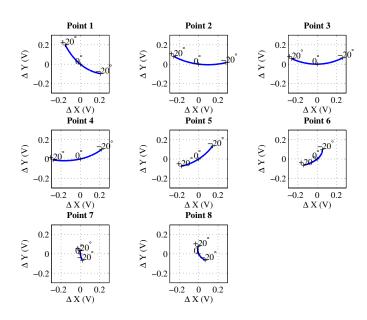

The vertical spinning wheel excitation comprises three different accelerations which are sensed by the DUT, namely, gravity, tangential, and centripetal accelerations. Such complex kinematic excitation makes the test setup undoubtedly sensitive to parametric deviations within the subsystems conforming the device. The inspection of the Lissajous patterns generated by the DUT and its test setup can then be used to identify the deviated parameter if a defect catalog is available. Although the whole Lissajous picture comes in handy when identifying a deviation by simple inspection, it is not that useful if the deviation level needs to be quantified. For that reason, a method for compacting the trace into a representative finite set of points is proposed as well as a metric to rate the sensitivity or diagnosis efficiency of each of the selected trace points. Using this information, the deviation level can be inferred and therefore the test decision taken. The proposed vertical spinning wheel excitation, together with the signature compaction and metric efficiency evaluation has been experimentally applied to test a MEMS accelerometer.

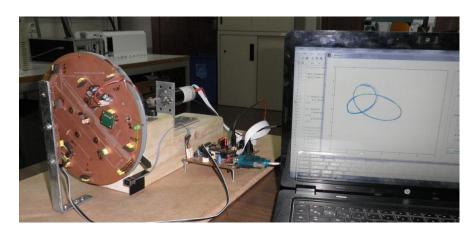

The vertical spinning wheel test and diagnosis methodology was proposed in the article Diagnosis of Parametric Defects in Dual Axis IC Accelerometers published in Microsystem Technologies Journal, volume 21, issue 9, in 2015. The publication corresponds to reference [J02] in the list shown on page 165. Several device parameters have been studied and characterized under different deviation levels. The definition of a metric and the evaluation of its diagnosis efficiency is used to optimize the diagnosis procedure against noisy measurements. The method has been experimentally applied to diagnose the misalignment degree in a commercial dual axis accelerometer. The Lissajous characterization of the defect is illustrated and experimental results are reported. Misalignment diagnosis results show the viability of the proposal.

**Chapter 5** focuses on two major improvements that have been developed in the frame of the proposed octree encoding strategy presented in Chapter 3. A test strategy efficiency is usually evaluated in terms of false positives and false negatives test outcomes, which directly impact the costs of the whole test procedure as well as the final product. Depending on the actual IC, fab or customer requirements, these analog test metrics are usually bounded or restricted in some sense. Because of that reason, two major octree tessellation improvements have been proposed, namely, an ensemble of rotated octrees and a guard banding strategy. The former developed improvement is based on encoding different octrees at different angles and combine their individual information to yield to better misclassification levels. The latter technique corresponds to a multiple specification guard banding methodology implemented with octrees in order to balance the test yield loss and test escapes as desired. The leverage of analog test metrics becomes a useful feature in mixed-signal testing since it allows the accommodation to fab and customer requirements. The published results in which Chapter 5 is based on are listed on the roadmap shown in Figure 1.2.

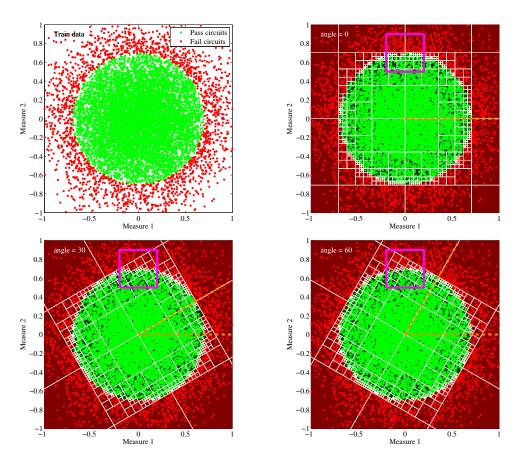

The multi-directional tessellation based on an octree ensemble was proposed in the paper Improving Indirect Test Efficiency Using Multi-Directional Tessellations in the Measure Space presented at the International Mixed-Signal Testing Workshop in July 2016. An enhanced version of the work was published in the article Multi-Directional Space Tessellation to Improve the Decision Boundary in Indirect Mixed-Signal Testing. in Journal of Electronic Testing in February 2017. The publications correspond to references [C24] and [J05], respectively, in the list shown on page 165. The work in [C24] was honored with the **Best PhD Student Paper Award** distinction at the conference.

The articles prospect the possibilities of using space tessellations along multiple directions in order to improve the test decision boundary definition in the alternate measure space. The proposed method is able to reduce false positive test outcomes, with acceptable penalty in test yield loss metric, or vice-versa. The key idea presented in this work is to use an ensemble of octrees, each of them tessellating the plane along different directions. Such tessellations create a refinement in the non linear test decision boundaries without the need of including extra circuit samples. The tree ensemble, together with a strict test decision criterion, serve as a classifier during the production testing phase. The proposed multi-directional ensemble tessellation strategy has been applied to test a band-pass Biquad filter affected by parametric variations. The proposed method has shown to be effective in lowering the test escapes metric as compared to a single octree classifier. The computational overhead of evaluating several octrees is insignificant since  $2^n$ -ary tree data structures can be efficiently traversed to yield a test decision. The octree ensemble technique has also been compared against a classic specification guard-banding technique reporting better test yield loss metrics for the same test escape target.

The multiple specification guard banding methodology using octrees was proposed in the paper Mixed-Signal Test Band Guarding Using Digitally Coded Indirect Measurements presented at the International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design in September 2015. An enhanced version of the work can be found in Indirect Test of M-S Circuits Using Multiple Specification Band Guarding published in Integration, the VLSI Journal in September 2016. The publications correspond to references [C21] and [J04], respectively, in the list shown on page 165.

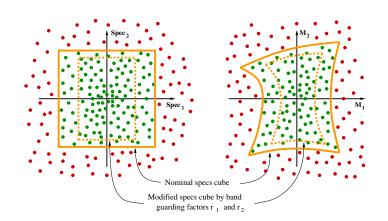

The papers propose a multiple specification band guarding technique as a method to achieve a test target of misclassified circuits. The acceptance/rejection test regions are encoded using octrees in the measurement space, where the band guarding factors precisely tune the test decision boundary according to the required analog test metrics targets. The generated octree data structure serves to cluster the forthcoming circuits in the production testing phase by solely relying on indirect measurements. The combined use of octree based encoding and multiple specification band guarding makes the testing procedure fast, efficient and highly tunable. The proposed band guarding methodology has been applied to test a band-pass Butterworth filter under parametric variations. Simulation results are reported showing noteworthy improvements when the multiple specification band guarding criterion is used.

**Chapter 6** focuses on a topic of major concern in the field of alternate testing, selection and acquisition of indirect measurements. Special care is devoted to an adequate selection of indirect measurements using statistical methods that yield to better and less costly test results. Throughout the chapter, the details of the design and application of an adaptive test system for mixed-signal circuits are presented as well the experimental results derived from its application to an analog system. The published results in which Chapter 6 is based on are listed on the roadmap shown in Figure 1.2.

An algorithm for selecting a subset of alternate measurements was proposed in *Criteria for Selecting a Subset of Indirect Measurements for Analog Testing* presented at the *Design of Circuits and Integrated Systems Conference* in November 2016. The publication corresponds to reference [C25] in the list of publications shown on page 165.

The work proposes a criterion to select a subset of indirect measurements avoiding

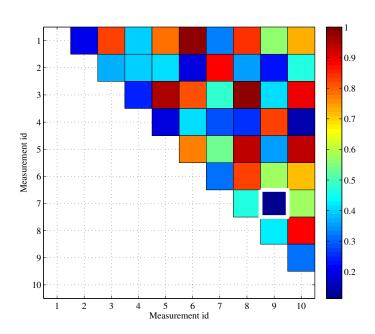

redundant information. The key idea of the proposal is to reduce the actual number of measurements to be performed to those strictly providing relevant information to the testing procedure, therefore keeping the incurred test misclassifications at acceptable levels. The method selects the measurements presenting minimum mean and spread of the correlations between all the possible pairs formed by the measurements within the target subset. In order to show the viability of the proposal, the method has been applied to select a subset of indirect measurements in several analog filters being affected by parametric variations. The obtained misclassification levels using the subset of measurements indicated by the proposed method are considerably low, therefore highlighting the benefits of the proposed selection methodology.

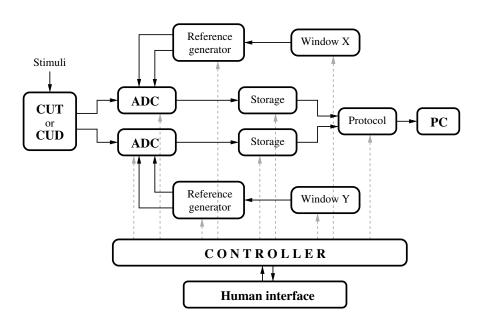

A system for acquiring analog signatures was proposed in the paper Adaptive Test System Applied to the Generation of Mixed-Signal Signatures presented at the Design of Circuits and Integrated Systems Conference in November 2015, honored with the **Best Paper Award** distinction at the conference. The publication corresponds to reference [C22] in the list of publications shown on page 165.

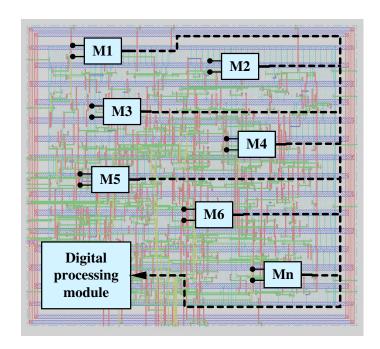

The work proposes an adaptive test system to measure and generate indirect digital signatures. The system is composed by an integrated digital signature generator and a digital control and acquisition subsystem. The signature generator is based on a converter architecture in which the analog range can be adapted. Also, the internal references are implemented using an active voltage divider, what yields to a compact and adaptive design since the actual resolution is increased as the signal range to be converted is reduced. The digital subsystem controls the proposed architecture as well as captures and stores the digital codes sent by the digital signature generator. The digital signature generator has been designed and fabricated in an industrial 65 nm CMOS technology while the digital control and acquisition subsystem has been implemented in an FPGA. The whole system has been applied to test a Biquad filter affected by parametric shifts. Results are reported showing the capabilities of the proposed adaptive test system.

Finally, **Chapter 7** is devoted to summarize the conclusions and contributions of the dissertation as well give some future research guidelines.

## State of the Art

In this chapter, the state of the art in alternate test and binning of mixed-signal circuits is reviewed. One of the main challenges in alternate analog and mixed-signal testing is the representation or encoding of the test acceptance/rejection regions in order to take the test decision in a high volume production test program. This thesis is framed within the aforementioned challenging scenario, so special emphasis is devoted to focus this chapter in such particular issue and the related methods found in the literature of the field.

Chapter 2 is organized as follows. First, a general view of the challenges existing in alternate analog and mixed-signal testing is given with special emphasis in showing how such indirect procedures serve as a promising solution to battle against the ever increasing analog and mixed-signal testing costs [1]. Then, some of the methods found in the literature to overcome these challenges are briefly reviewed and explained. Basically, two different techniques can be distinguished, namely, regressors and classifiers. Amongst the first group, multi-adaptive regression splines (MARS) plays an important role in the field, while artificial intelligence (AI) techniques dominate the methods within the second group [2]. Subsequently, the challenges and advancements in alternate test of heterogeneous systems with particular attention to MEMS systems are reviewed. Then, the concept of quality binning for analog and mixed-signal is introduced and the benefits it may provide are highlighted [3]. Some works making usage of mixed-signal quality binning are commented. Finally, the chapter closes with an overview of the guidelines proposed in the literature to overcome the problem of selecting an adequate subset of alternate measurements for analog and mixed-signal testin.

## 2.1 Alternate Test of Mixed-Signal Circuits

Production testing of analog and mixed-signal circuits is an increasingly challenging task due to the presence of statistical variations related with the manufacturing process which directly affect circuit specifications [1,4]. High amount of resources are solely dedicated to test and diagnose such devices to ensure that only specification compliant circuits are shipped to customers [1,5].

Semiconductor industry is demanding close to zero defect level devices, specially for those applications considered as safety critical, such as automobile and aeronautics [6]. The continuous miniaturization of technology nodes and the ever increasing device verification costs, together with the challenges encountered in analog/RF and mixed-signal testing makes this topic a crucial focus of research [1,7]. The incurred costs in classic specification based test are not acceptable in high volume productions batches. These costs can be reduced when using non specification based procedures, usually referred as alternate or indirect test techniques [8,9]. Instead of directly measuring the functional specification to be validated, alternate test proposes to measure other easy to measure parameters and use them to predict the actual specification and/or to decide whether the circuit is within specifications or not.

When indirect measurements are used to validate circuit performances, lots of factors affect test metrics results. Test yield loss, i.e. good circuits failing the test, and specially test escapes, i.e. bad circuits passing the test, are of major concern for the acceptance of such procedures in a production test program development [7]. The main problem is how to use these alternate data in order to take the test decision without incurring in a prohibited number of misclassified circuits. Regression and machine learning techniques have been widely accepted for such a purpose [10]. For instance, in [7,11] a two tier approach is proposed to retest those circuits with chances of not being correctly classified by the first tier. The work in [12] uses copula theory in order to estimate the tails of distributions and therefore tune the process to achieve the required analog test metrics.

Alternate testing using classifiers implies a clustering process in which the main goal is to obtain a reliable boundary definition to separate circuits fulfilling the specifications from circuits violating them. When such clustering is made with indirect measurements, i.e. different from the actual specifications, getting the correct test decision boundary may become a difficult and challenging task. The benefits of using easy to obtain measures is worth only if the resulting analog test metrics fit the specified test targets [11].

The proposed technique in this thesis relies on tessellating the space using binary trees coming from the field of computer graphics [13] and data clustering [14]. The procedure is referred as  $2^n$ -ary tree space tessellation or in some cases octree tessellation due to its 3D computer graphics connection. In this technique the space is encoded using octrees to determine the test acceptance/rejection regions and such data structre is later used in the actual production testing phase to decide whether a circuit is classified as pass or fail.

### 2.2 State of The Art Methods in Alternate Test

In an alternate test program, once the alternate measurements have been performed, the test decision must be taken by solely relying on the set of measurements. Basically, two main approaches can be identified in the literature to such purpose, regression based techniques and classifier based techniques.

- **Regression based approach:** Relies on constructing a mathematical model to map the actual circuit performances to the set of alternate measurements. This way, for every tuple of circuit measurements the functional specifications can be obtained by simple evaluating them in the regressor function that was previously trained, and the test decision is actually taken in the inferred circuit performance space. This approach requires a regressor to be trained for every functional specification that needs to be validated.

- **Classifier based approach:** Uses state of the art data clustering methods to train (using different procedures) a classifier capable of representing the arbitrary test acceptance/rejection regions within the alternate measurements space. The test decision is take by evaluating the set of alternate measurements in the trained classifier. Oppositely to the regression based approach, classifiers directly yield to the test decision in the alternate measurements space.

Each of these two approaches present different particular methods. For the case of regression based approaches, one can identify linear and nonlinear regression techniques. Within the nonlinear regression techniques, MARS regression plays an important role in the field. For the case of classifier based approaches, one can identify a vast variety of methods, most of them within the artificial intelligence domain such as artificial neural networks (ANN) or support vector machines (SVM).

#### 2.2.1 Regression Techniques

The underlying idea using regressions is to find a mapping function (the regressor) able to predict circuit performances as a function of certain set of indirect measurements. To this purpose, a regression function is needed for each functional specification. Once the regressors are trained, the functional specifications are obtained and therefore the test procedure is reduced to a naive specification based test to see whether each of the specs lie in its test acceptance region or not.

A huge variety of regression functions and methods in the statistical literature, but here, just the most commonly extended and used methods in alternate test of mixedsignal circuits are reviewed. The simplest and easy to understand regression method is the classical linear regression in which the independent or explanatory variables are fitted to a linear variety, i.e. straight line, plane, hyperplane, etc..., to construct a linear model for the response variable. Of course, the previous simple approach can be extended to arbitrary nonlinear functions if a certain mapping is known to fit well to a certain nonlinear relationship. The multivariate adaptive regression splines (MARS) approach has been extensively used in alternate test of mixed-signal circuits. The MARS model is constructed similarly to linear regression but using what are called "basis functions", which can be linear or nonlinear, and their interactions. The subsequent sections briefly describe all these methods and point to some works that have used them serving to alternate test purposes.

#### Linear Regression

Probably, linear regression is the most naive form of regression but still serves as a suitable tool for mapping the indirect measurements to functional specifications in the frame of alternate test. In this section, the term linear regression refers to multivariate linear regression. There are situations in which the indirect measurements clearly present a linear relationship between each of the functional specifications to validate. In such scenarios, linear regressions play a crucial role in inferring the desired circuit specifications. It is worth to mention that a proper statistical analysis of the residues is needed in order to assess the correctness of the linear regression. If the residuals do not present a normal distribution, then a more advanced regression technique must be used such as MARS regression or any other nonlinear regression model.

The way of tackling the general problem of multivariate linear regression is a well known method in statistics which relies on the solution of the so called *normal equations*. The *normal equations* derive from the concept of *leasts squares* fitting. These equations relate the response variable with the explanatory variables through the regression model parameters. The well established linear algebra methods allow a fast solution to the problem.