ADVERTIMENT. L'accés als continguts d'aquesta tesi queda condicionat a l'acceptació de les condicions d'ús establertes per la següent llicència Creative Commons:

ADVERTENCIA. El acceso a los contenidos de esta tesis queda condicionado a la aceptación de las condiciones de uso establecidas por la siguiente licencia Creative Commons:

**WARNING.** The access to the contents of this doctoral thesis it is limited to the acceptance of the use conditions set by the following Creative Commons license: https://creativecommons.org/licenses/?lang=en

Departament de Microelectrònica i Sistemes Electrònics

## AUTOMATIC SOURCE CODE ADAPTATION FOR HETEROGENEOUS PLATFORMS

Albert Saà-Garriga

Memòria de Tesi presentada per optar al títol de

Doctor en Informàtica

September 2016

Dr. Jordi Carrabina, Professor Titular del Departament de Microelectrònica i Sistemes Electrònics, Dr. David Castells-Rufas, Professor Associat del Departament de Microelectrònica i Sistemes Electrònics

## Certifiquen

que la Memòria de Tesi Automatic Source Code Adaptation for Heterogeneous Platforms presentada per Albert Saà-Garriga per optar al títol de Doctor en Informàtica s'ha realitzat sota la seva direcció i ha estat tutoritzada en el Departament de Microelectrònica i Sistemes Electrònics de la Universitat Autònoma de Barcelona.

Dr. Jordi Carrabina ..... Dr. David Castells-Rufas ....

©2016 Albert Saà Garriga Some Rights Reserved. This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

Never send a human to do a machine's job. Agent Smith

vii

### Resum

La fi de l'increment de la freqüència de rellotge com a forma més fàcil de millorar el rendiment dels sistemes de computació, junt amb una creixent escletxa entre la velocitat d'accés a CPU i la memòria, així com l'increment en la intensitat aritmètica dels problemes que resol lacomunitat de Computació amb Altes Prestacions (HPC), ha donat a llum a una nova gama de arquitectures computacionals heterogènies que pretenen conduir a una important millora del rendiment.

Els processadores amb molts nuclis (many-cores), ja siguin homogenis o heterogenis respecte el sistema central de comput són una de les sol·lucions mes esteses per a intentar arribar a les prestacions requerides. No obstant això, la comple xitat d'aquestes noves arquitectures no es pot ocultar fàcilment al programador, i això dificulta la seva aplicació. En aquesta tesi proposo un conjunt d'eines que busquen facilitar la creació de codi que permeti l'aprofitament de les característiques de les arquitectures paral·leles heterogenies a través de transformacions en el codi font, amb l'objectiu de millorar el rendiment i al mateix temps incrementar l'eficiència energètica de aplicacions originariament descrites amb codi seqüencial.

En aquesta tesis es presenta una metodologia i un entorn d'eines que facilita la portabilitat d'un codi font següencial a la seva descripció en entorns de programació paral·lela, com OpenMP, MPI o HMPP. S'ha demostrat amb èxit que les eines faciliten aquesta tasca mitjançant exemples que posen de relleu com es redueix el temps dedicat per un programador per dur a terme aquesta transformació. Com a primer pas en la paralelització del codi es mostra una eina que ens ajuda a detectar dependències de dades en codi complexe. Un cop es detecta el paralelisme potencial, es pot anotar el codi amb pragmas OpenMP, però l'escalabilitat d'aquesta solució està limitada al nombre de processadors del node de computació. Es presenta l'eina OMP2MPI que mostra com generar automàticament codi MPI a partir de OpenMP per poder escalar fàcilment a un nombre major de processadors. Per altre banda, l'eina OMP2HMPP permet transformar codi OpenMP automàticament a codi HMPP, per a la seva execució en arquitectures GPU. A partir d'exemples concrets, es pot veure com el sistema permet transformar un codi sequencial en OpenMP primer, i posteriorment MPI per obtenir una acceleració de  $60 \times$  respecte el codi seqüencial. De manera semblant es demostra com es pot transformar automaticament un codi sequencial a OpenMP primer, i posteriorment en HMPP per obtenir una acceleració de  $31 \times$  respecte al codi seqüencial i alhora augmentar l'eficiència energètica en un factor  $5,86 \times$ .

## Abstract

The demise of frequency scaling, which is the easiest way to improve computing performance, in addition to the growing gap between CPU and memory speeds and the increase in arithmetic intensity in current problems, has given rise to a new range of devices created to improve performance. Heterogeneous Computing (HC), and many-cores are examples of this new range of devices. However, the complexity of these new hardware architectures is not easily hidden from the programmer. In this thesis, I propose a set of tools that seek to exploit (through source-to-source (S2S) compilers) the capabilities and peculiarities of parallel computing and HC to speed up and increase the energy efficiency of originally sequential source code.

The proposed modular programs are implemented as a set of tools that help port sequential source code to OpenMP, MPI, and HMPP, demonstrating how the input code can effectively automatically be translated. Through a real-life example, I show how the proposed dependency analysis tool trivializes the task of parallelizing sequential code, breaking the first performance barrier. The OMP2MPI experiments generate code that is more than  $60 \times$  faster than its sequential version and also faster than its original OpenMP code. The OMP2HMPP experiments obtain an average speedup of  $31 \times$  and average increase in energy efficiency of  $5.86 \times$ . Both tools were tested with OpenMP, obtaining successful results that demonstrate the feasibility of using this set of tools for exploring HC.

## Acknowledgements

I am grateful to David Castells-Rufas and Jordi Carrabina for the care with which they reviewed this thesis as well as for conversations that clarified my thoughts on this and other matters. Their friendship and professional collaboration has meant a great deal to me. Thank you to all my family, specially to my parents because I am you. Toño, I know that you walk beside me every day and, Neus, thank you for being my compass and the spiritual support at critical and opportune times. To Marta, because you are my peace and my smile, you are the song that I want to hear every day, for all the time spent helping me yet being my sunshine. To Arturo, Cesc, Toni, and Miguel for all the shared lunches which gave me the energy to follow my research, the reviews of the final thesis proposal, and also for the comments that encouraged me to revise and improve it.

# Contents |

| 1        | Intr | roduction                                                                                     | 1  |

|----------|------|-----------------------------------------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                                                    | 8  |

|          | 1.2  | Objectives                                                                                    | 9  |

|          | 1.3  | State-of-the-Art Technologies                                                                 | 11 |

|          |      | 1.3.1 Compilers                                                                               | 11 |

|          |      | 1.3.2 Transformations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 13 |

|          |      |                                                                                               |    |

| <b>2</b> | Visi | ualizing Data Access Patterns                                                                 | 17 |

|          | 2.1  | Automatic Instrumentation                                                                     | 19 |

|          |      | 2.1.1 Results                                                                                 | 20 |

|          | 2.2  | Execution                                                                                     | 21 |

|          | 2.3  | Data Analysis                                                                                 | 21 |

|          | 2.4  | Visualization                                                                                 | 23 |

|          | 2.5  | Case Study: Triangular Matrix–Matrix Multiplication $\ . \ . \ . \ .$                         | 23 |

|          | 2.6  | Concluding Remarks                                                                            | 26 |

| 3 | Ope  | enMP to HMPP (OMP2HMPP)                                 | <b>29</b> |

|---|------|---------------------------------------------------------|-----------|

|   | 3.1  | Hybrid Multicore Parallel Programming (HMPP) Directives | 31        |

|   | 3.2  | Source-to-Source Compiler (S2S) Transformations         | 32        |

|   |      | 3.2.1 Outline Phase                                     | 32        |

|   |      | 3.2.2 Inline Phase                                      | 41        |

|   | 3.3  | Results                                                 | 42        |

|   | 3.4  | Concluding Remarks                                      | 47        |

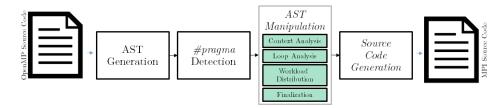

| 4 | Ope  | enMP to MPI (OMP2MPI)                                   | 63        |

|   | 4.1  | Abstract Syntax Tree (AST) Manipulation                 | 64        |

|   |      | 4.1.1 Task Distribution                                 | 68        |

|   |      | 4.1.2 Context Analysis                                  | 68        |

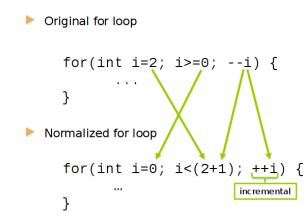

|   |      | 4.1.3 Loop Analysis                                     | 69        |

|   |      | 4.1.4 Workload Distribution                             | 72        |

|   | 4.2  | Results                                                 | 76        |

|   | 4.3  | Concluding Remarks                                      | 78        |

| 5 | Inte | egrated Modular System                                  | 91        |

| 6 | Cor  | iclusions                                               | 97        |

|   | 6.1  | Open Research                                           | 98        |

# List of Figures

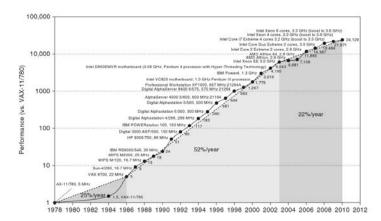

| 1.1 | Growth in processor performance since the late 1970s. Source: $\left[1\right]$                                                                                                                                        | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

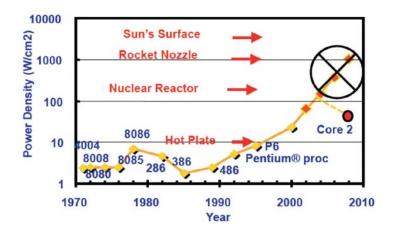

| 1.2 | Power density wall. Source: S. Borkar (Intel)                                                                                                                                                                         | 3  |

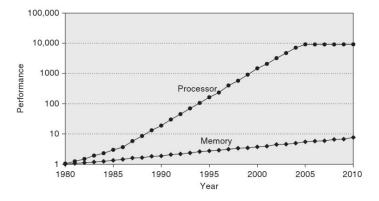

| 1.3 | Performance gap, measured as the difference in time between processor memory request (for a single processor or core) and the latency of the DRAM access, over time using 1980 performance as a baseline. Source: [1] | 3  |

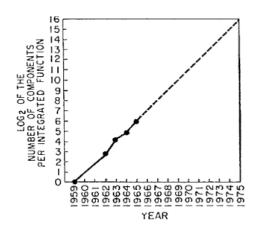

| 1.4 | Moore's 1965 prediction that the number of "minimum cost" com-<br>ponents on a chip would double each year, based on historical data<br>and extrapolated to 1975. Source [2]                                          | 4  |

| 1.5 | Paralleled tasks using OpenMP blocks. Source: [3]                                                                                                                                                                     | 5  |

| 1.6 | Paralleled task using distributed memory architecture. Source: $\left[3\right]$ .                                                                                                                                     | 6  |

| 1.7 | List of objectives for each of the three S2S compilers (Access Pattern, OMP2MPI, and OMP2HMPP)                                                                                                                        | 10 |

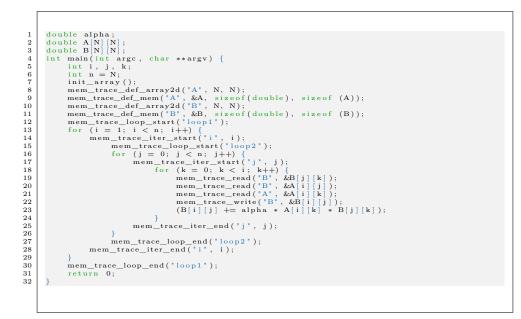

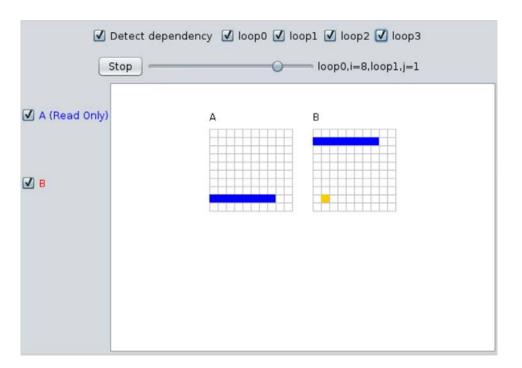

| 2.1 | Caption for LOF1                                                                                                                                                                                                      | 24 |

| 2.2 | Caption for LOF2                                                                                                                                                                                                      | 25 |

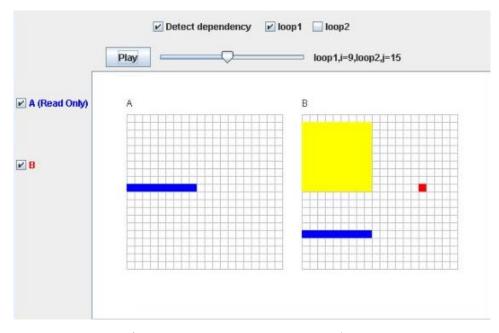

| 2.3 | Caption for LOF3                                                                                                                                                                                                      | 27 |

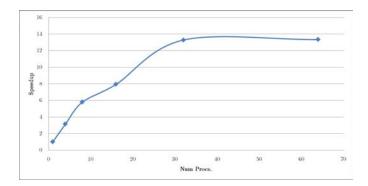

| 2.4 | TRMM problem speedup                                                                                                                                                                                                  | 27 |

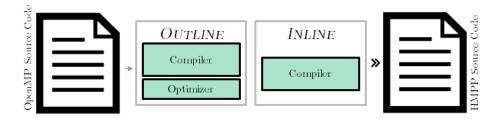

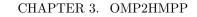

| 3.1 S2S transformation process                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 S2S transformation workflow                                                                                                              |

| 3.3 Example of the location and explanation of new directives 35                                                                             |

| 3.4 FIXED directive flags explanation                                                                                                        |

| 3.5 Context example                                                                                                                          |

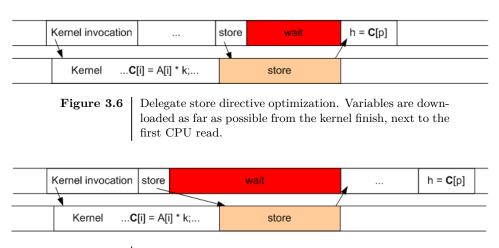

| 3.6 Delegate store directive optimization. Variables are downloaded as far as possible from the kernel finish, next to the first CPU read 38 |

| 3.7 Delegate store directive optimization. Variables are downloaded<br>when the kernel finishes                                              |

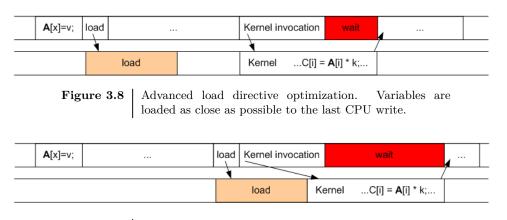

| 3.8 Advanced load directive optimization. Variables are loaded as close<br>as possible to the last CPU write                                 |

| 3.9 Advanced load directive optimization. Variables are loaded when<br>the kernel is invoked                                                 |

| 3.10 Example of data transfer in loops                                                                                                       |

| 3.11 Example of data transfer in loops $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 41$                                                 |

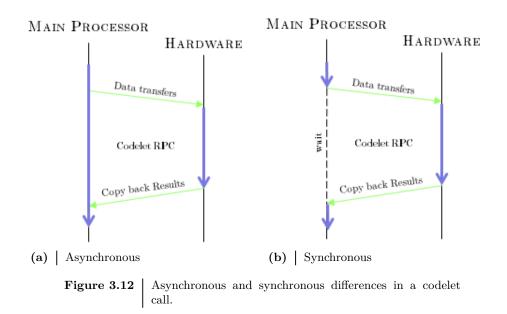

| 3.12 Asynchronous and synchronous differences in a codelet call 42                                                                           |

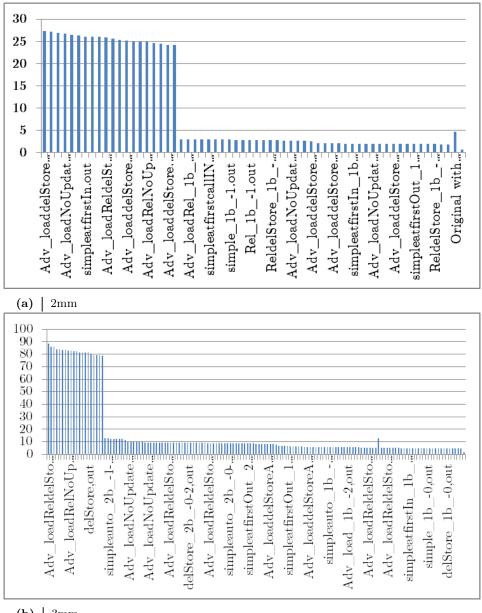

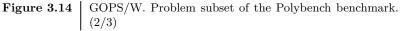

| 3.13 GOPS/W. Problem subset of the Polybench benchmark. $(1/3)$ $\ldots$ 43                                                                  |

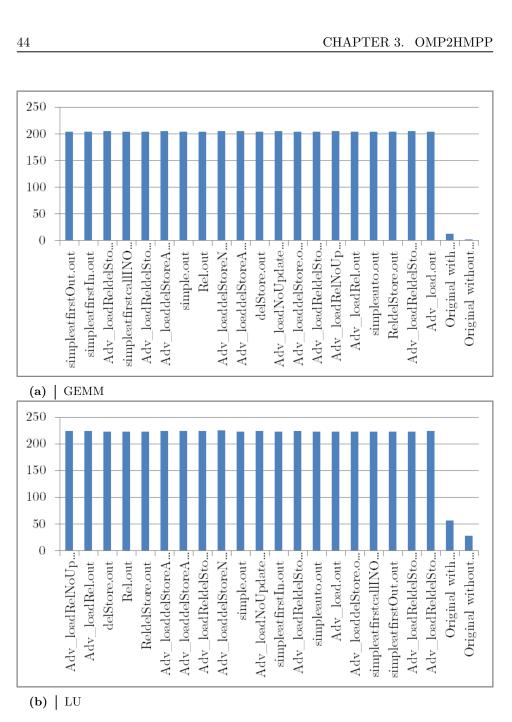

| 3.14 GOPS/W. Problem subset of the Polybench benchmark. $(2/3)$ $\ .$ 44                                                                     |

| 3.15 GOPS/W. Problem subset of the Polybench benchmark. $(3/3)$ $\ .$ 45                                                                     |

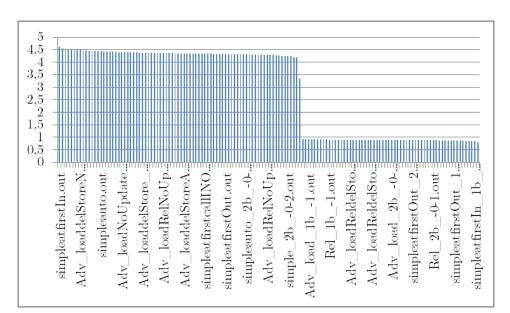

| 3.16 Speedup Comparison. Problem subset of the Polybench benchmark. $$ 47 $$                                                                 |

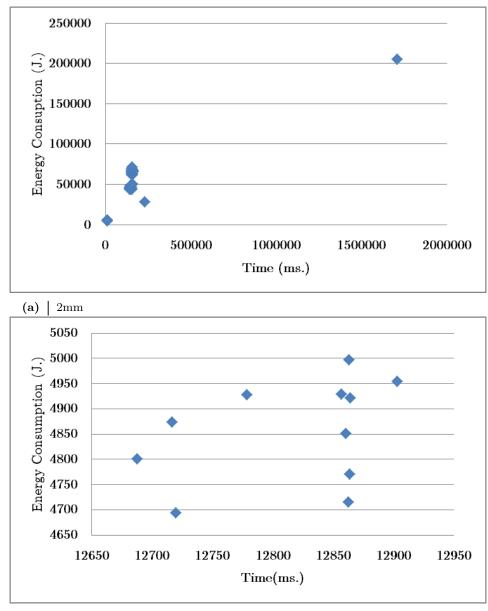

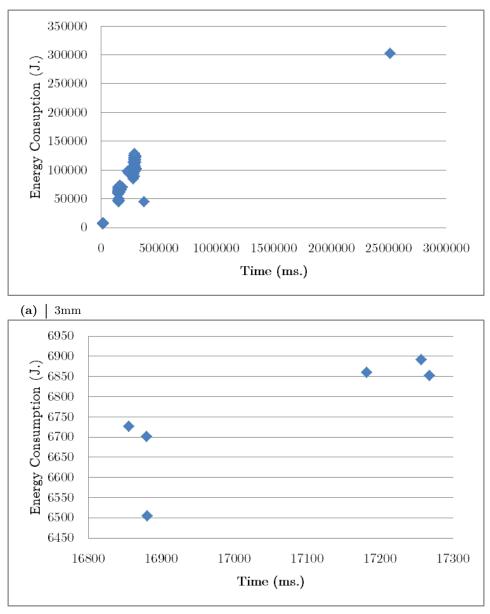

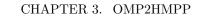

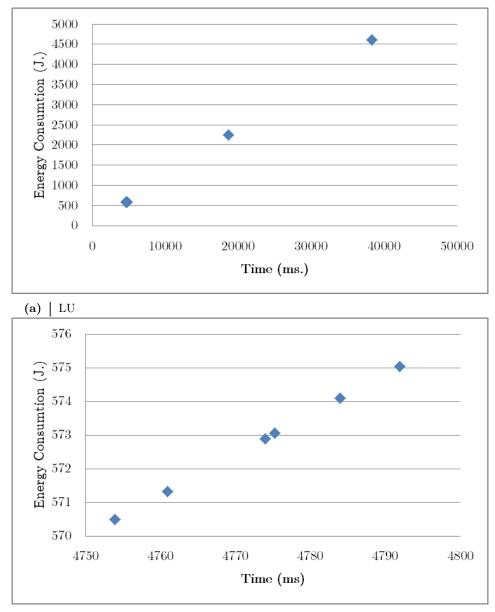

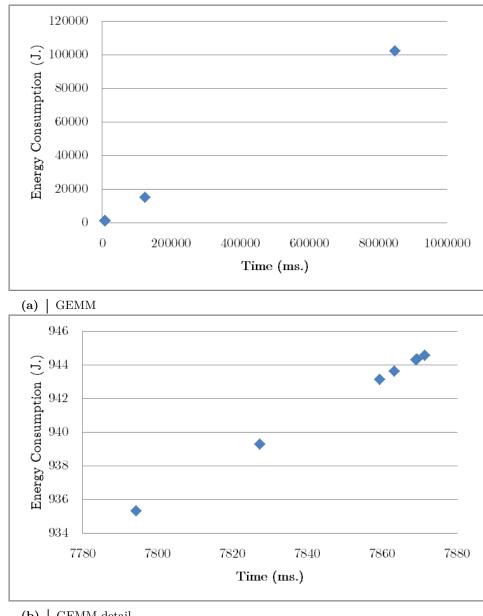

| 3.17 Energy/Time trade-off. Problem subset of the Polybench bench-<br>mark. (1/5)                                                            |

| 3.18 Energy/Time trade-off. Problem subset of the Polybench bench-<br>mark. (2/5)                                                            |

| 3.19 Energy/Time trade-off. Problem subset of the Polybench bench-<br>mark. (3/5)                                                            |

| 3.20 Energy/Time trade-off. Problem subset of the Polybench bench-<br>mark. (4/5)                                                            |

| 3.21 Energy/Time trade-off. Problem subset of the Polybench bench-<br>mark. (5/5)                                                            |

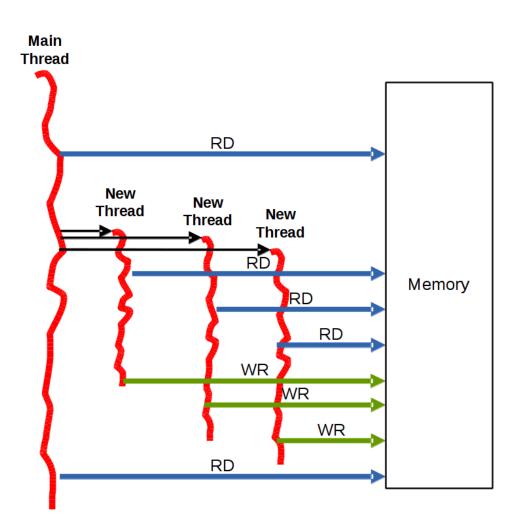

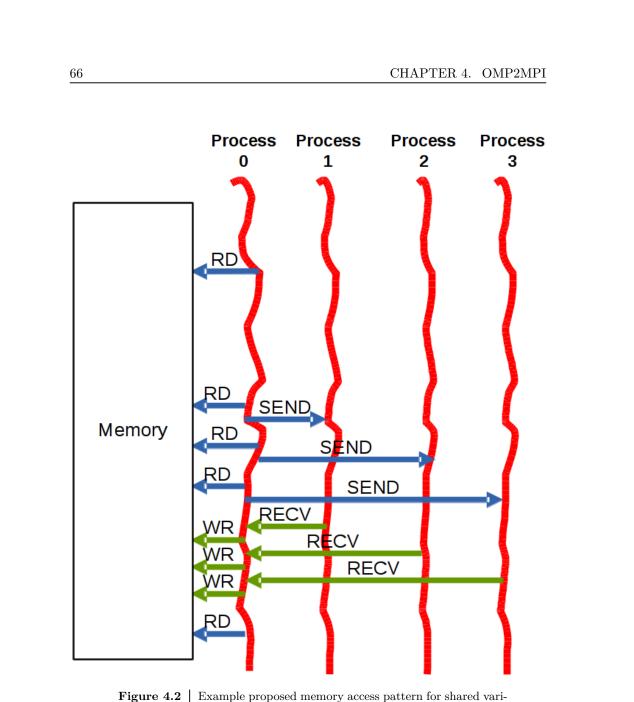

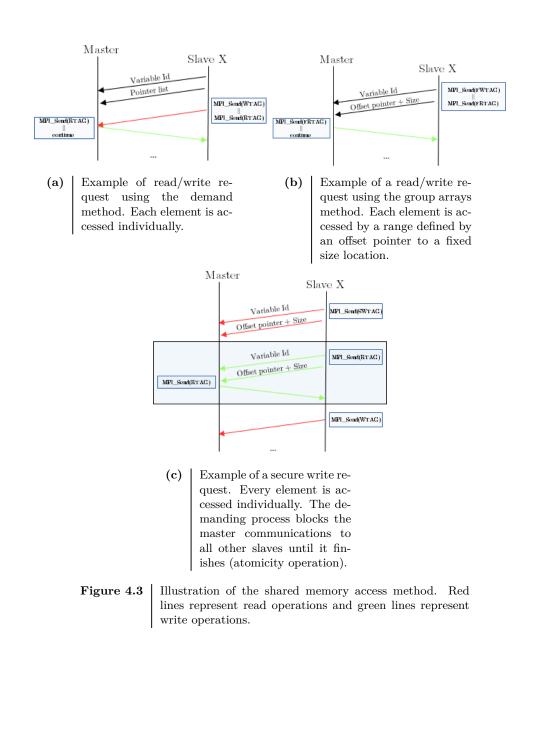

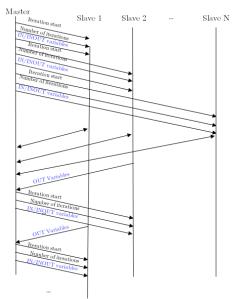

| sent read opera-                                                                                          | 65                                                                               |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| red variables in<br>s is managed by<br>nunicate with it<br>ns, and red lines                              | 66                                                                               |

| d lines represent<br>rations                                                                              | 67                                                                               |

| PI (grey boxes)<br>(grey boxes)                                                                           | 68                                                                               |

|                                                                                                           | 72                                                                               |

|                                                                                                           | 73                                                                               |

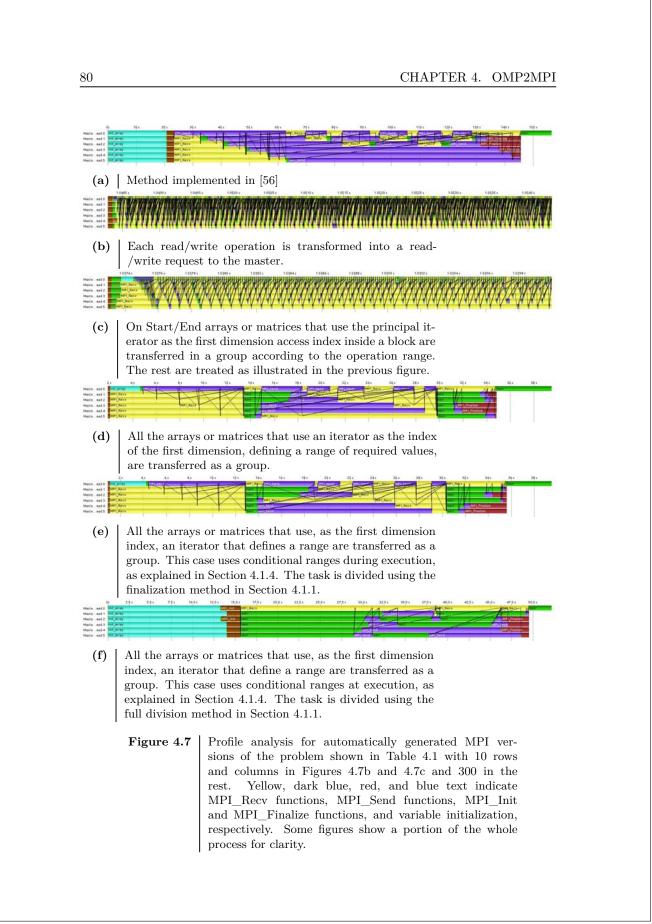

| versions of the<br>s in Figures 4.7b<br>d, and blue text<br>s, MPI_Init and<br>respectively. Some<br>ity. | 80                                                                               |

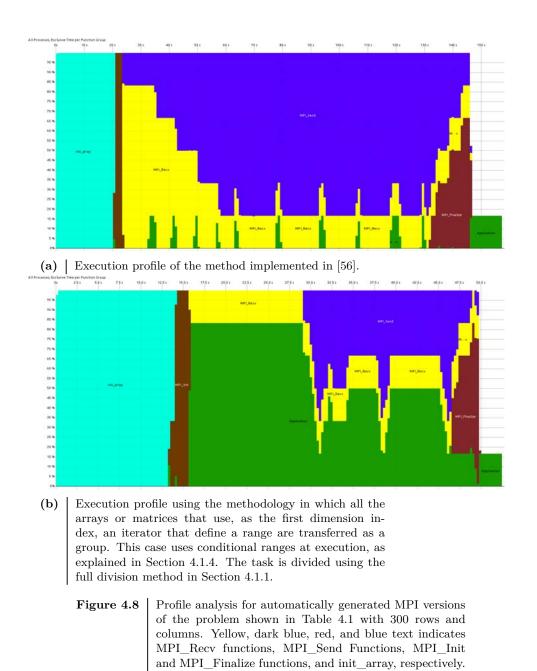

| versions of the<br>ns. Yellow, dark<br>ons, MPI_Send<br>and init_array,                                   | 81                                                                               |

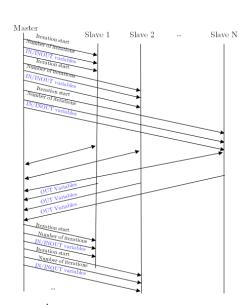

|                                                                                                           | 82                                                                               |

| using 16, 32, and<br>eedup, and blue<br>resents the same<br>d 4, respectively                             | 83                                                                               |

| using 16, 32, and<br>eedup, and blue<br>ne same problem<br>e processors but                               | 84                                                                               |

|                                                                                                           | red variables in<br>s is managed by<br>nunicate with it<br>as, and red lines<br> |

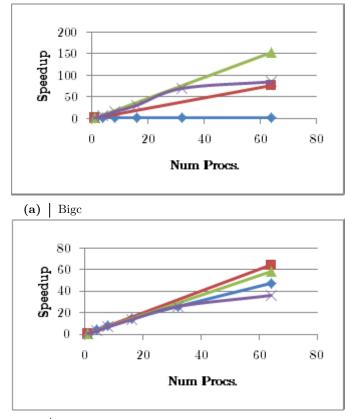

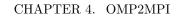

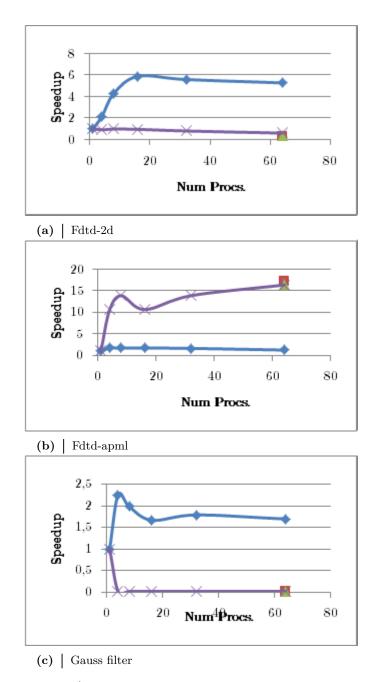

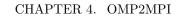

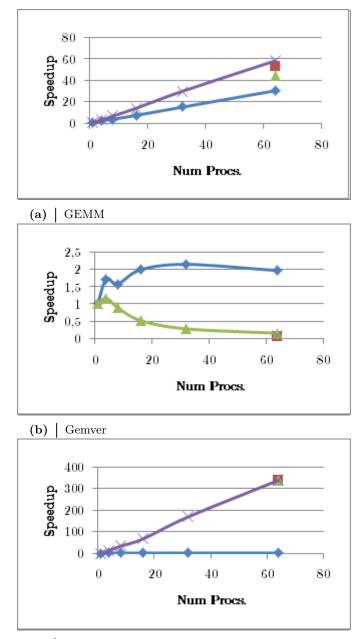

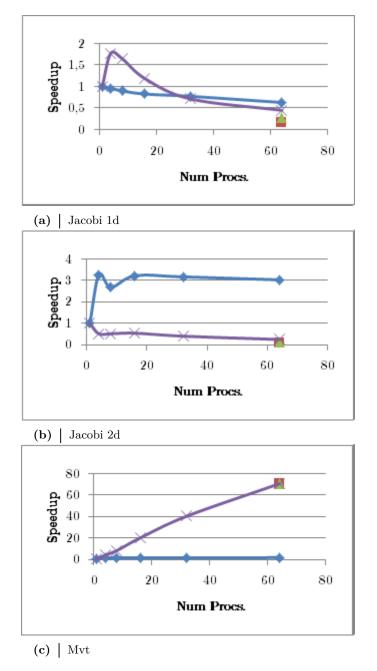

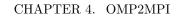

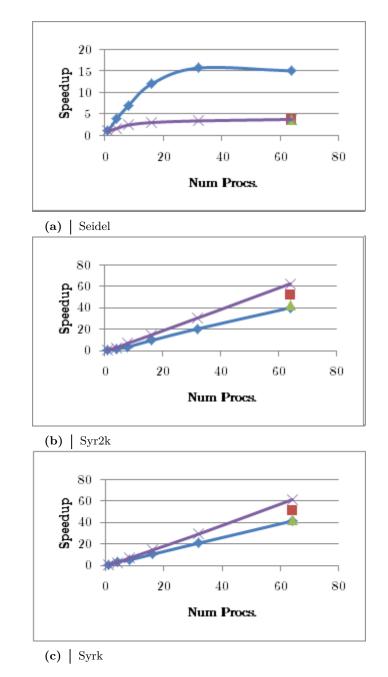

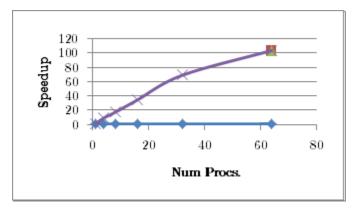

| 4.12 | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. Purple lines represent OpenMP speedup, and blue lines show MPI speedup. Green and red lines show the same problem executed using the maximum number of available processors but different slave block sizes. $(2/6) \ldots \ldots \ldots \ldots \ldots \ldots$ | 85 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.13 | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. Purple lines represent OpenMP speedup, and blue lines show MPI speedup. Green and red lines show the same problem executed using the maximum number of available processors but different slave block sizes. $(3/6) \ldots \ldots \ldots \ldots \ldots \ldots$ | 86 |

| 4.14 | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. Purple lines represent OpenMP speedup, and blue lines show MPI speedup. Green and red lines show the same problem executed using the maximum number of available processors but different slave block sizes. $(4/6) \ldots \ldots \ldots \ldots \ldots \ldots$ | 87 |

| 4.15 | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. Purple lines represent OpenMP speedup, and blue lines show MPI speedup. Green and red lines show the same problem executed using the maximum number of available processors but different slave block sizes. $(5/6) \ldots \ldots \ldots \ldots \ldots \ldots$ | 88 |

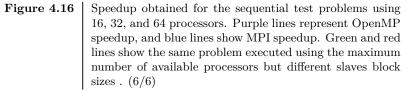

| 4.16 | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. Purple lines represent OpenMP speedup, and blue lines show MPI speedup. Green and red lines show the same problem executed using the maximum number of available processors but different slaves block sizes . $(6/6)$                                         | 89 |

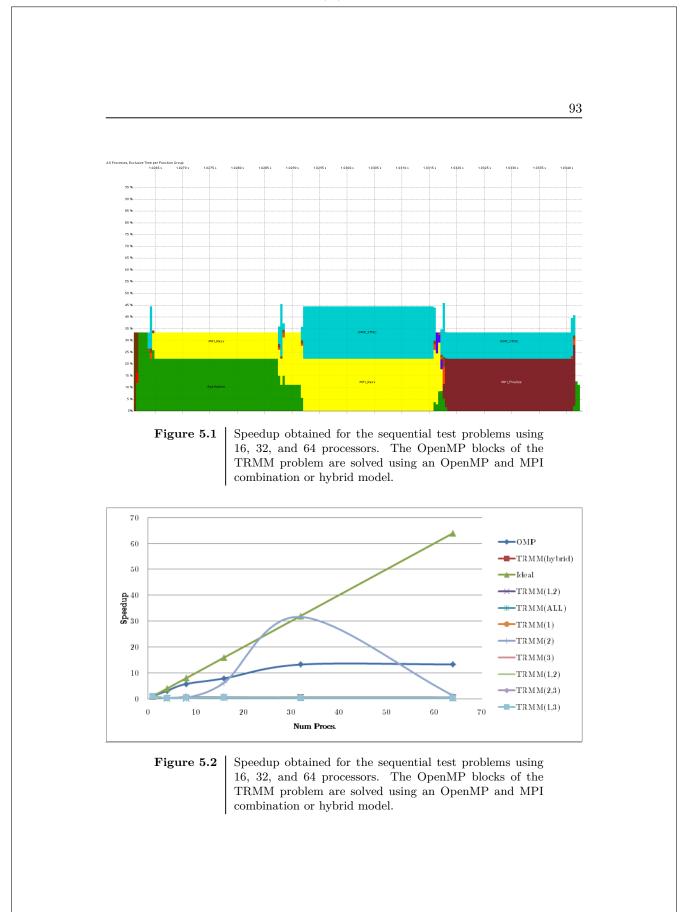

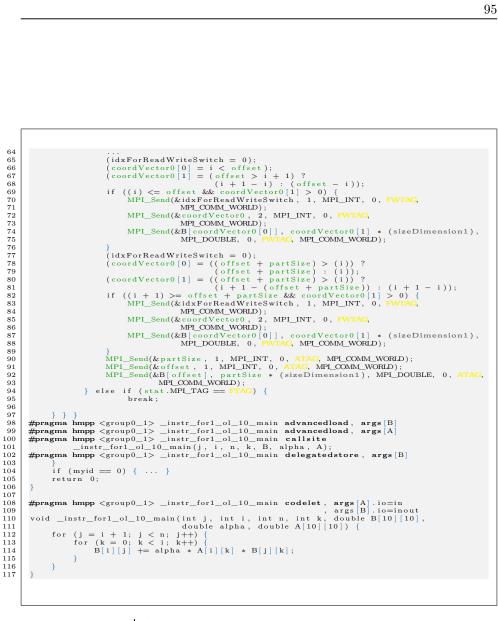

| 5.1  | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. The OpenMP blocks of the TRMM problem are solved using an OpenMP and MPI combination or hybrid model                                                                                                                                                           | 93 |

| 5.2  | Speedup obtained for the sequential test problems using 16, 32, and 64 processors. The OpenMP blocks of the TRMM problem are solved using an OpenMP and MPI combination or hybrid model                                                                                                                                                           | 93 |

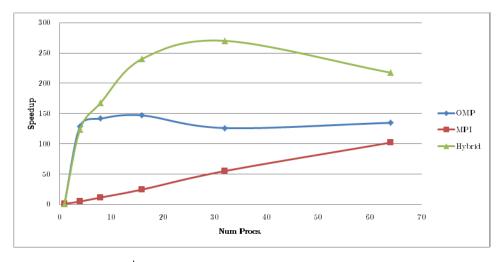

| 5.3  | Speedup obtained for the sequential test problems and the hybrid model of the same problem using 16, 32, and 64 processors                                                                                                                                                                                                                        | 96 |

# List of Tables

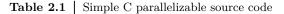

| 2.1 | Simple C parallelizable source code                                                                                                                                                          | 18 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Simple C non-parallelizable source code                                                                                                                                                      | 18 |

| 2.3 | Input code                                                                                                                                                                                   | 21 |

| 2.4 | Transformed code                                                                                                                                                                             | 22 |

| 2.5 | TRMM original code                                                                                                                                                                           | 26 |

| 2.6 | TRMM rectified source code                                                                                                                                                                   | 26 |

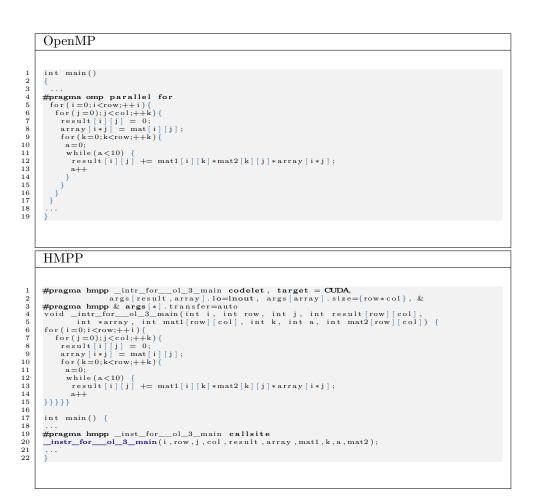

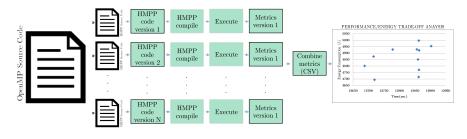

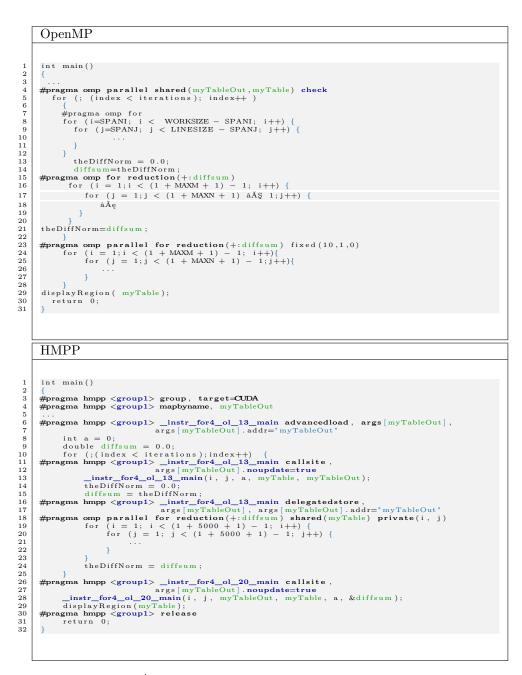

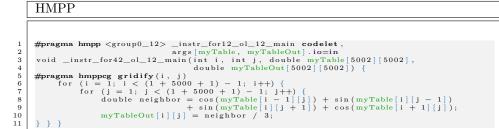

| 3.1 | Example of an OMP2HMPP S2S transformation process using a simple code as input                                                                                                               | 33 |

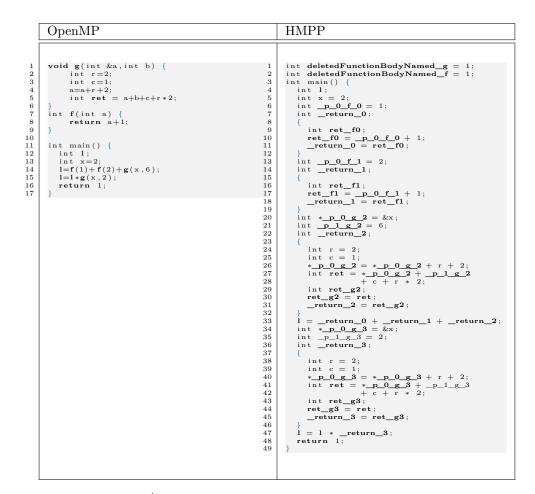

| 3.2 | Different OMP2HMPP transformations on each of the OpenMP par-<br>allel for pragmas inside an OpenMP parallel block                                                                           | 52 |

| 3.3 | Example of variable access inside the kernel, as distinguished by OMP2HMPP, which determines if these variables are read or modified inside it.                                              | 53 |

| 3.4 | Example of grid division, as determined by OMP2HMPP using the <i>hmppcg gridify</i> directive. This example transformation shows an OpenMP block that contains an OpenMP reduction directive | 54 |

| 3.5 | Example of OMP2HMPP use of contextual analysis                                                                                                                                               | 55 |

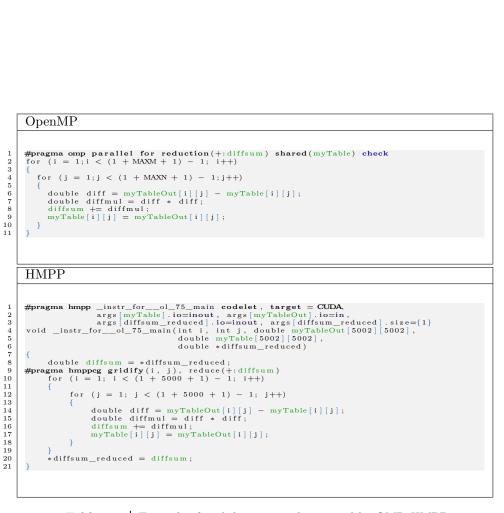

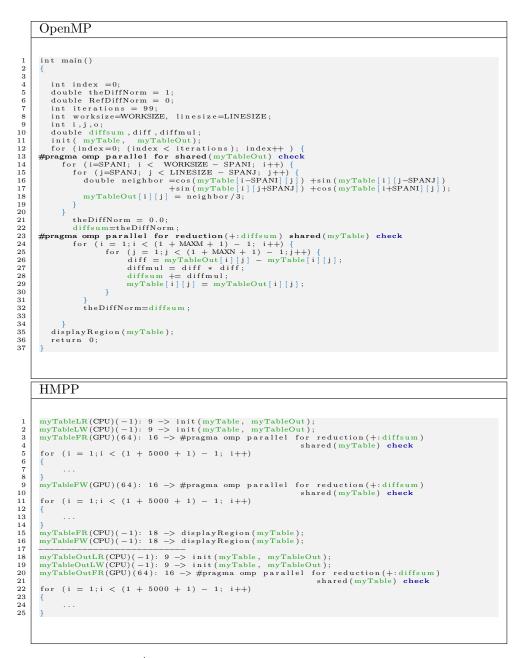

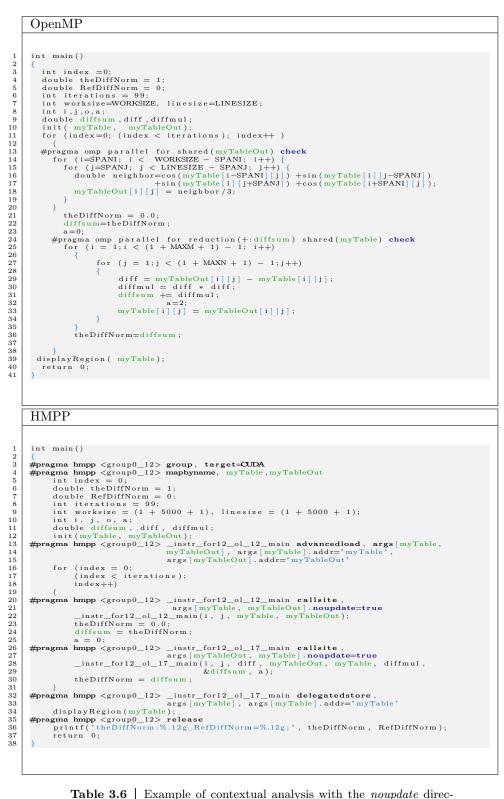

| 3.6 | Example of contextual analysis with the <i>noupdate</i> directive                                                                                                                                           | 56 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7 | OMP2HMPP transformation. Data transfer between the GPU and CPU is decreased by using the HMPP <i>noupdate</i> directive                                                                                     | 57 |

| 3.8 | Inline transformation                                                                                                                                                                                       | 58 |

| 3.9 | Example OMP2HMPP CSV spreadsheet output for Jacobi implementation.                                                                                                                                          | 61 |

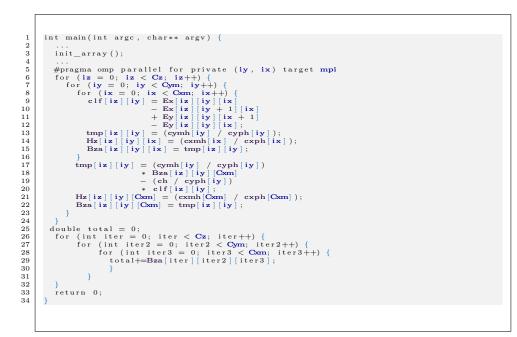

| 4.1 | OpenMP block source code example using the created $target$ clause.                                                                                                                                         | 64 |

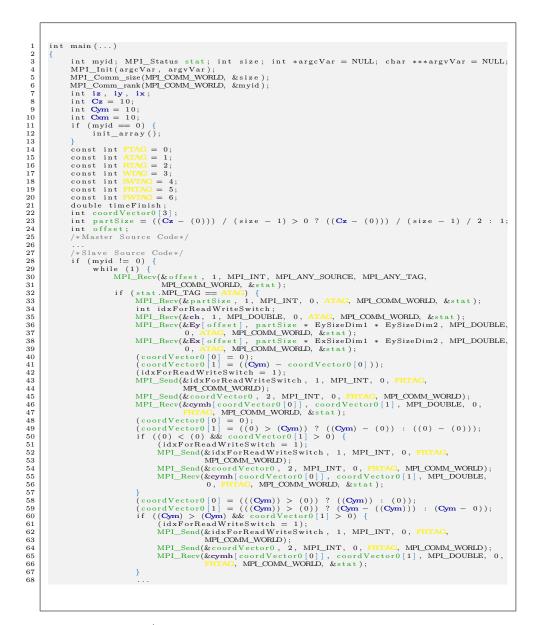

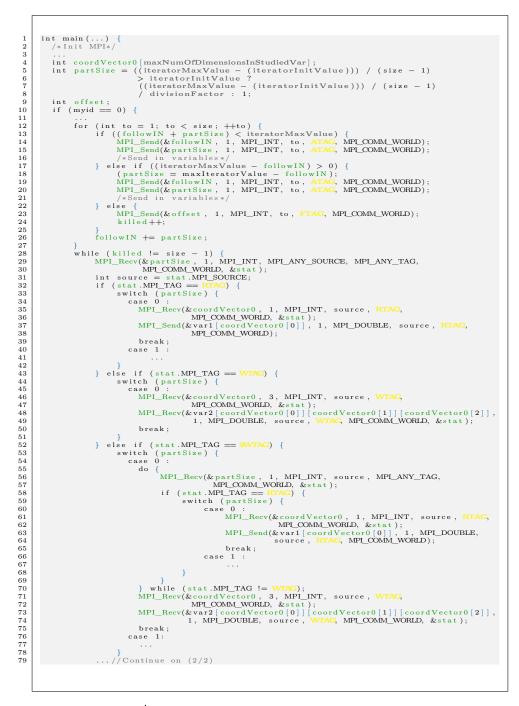

| 4.2 | Automatically generated Message Passing Interface (MPI) source<br>code with expanded slave code. OMP2MPI automatically groups<br>accesses into read/write requests with conditional range updates.<br>(1/2) | 70 |

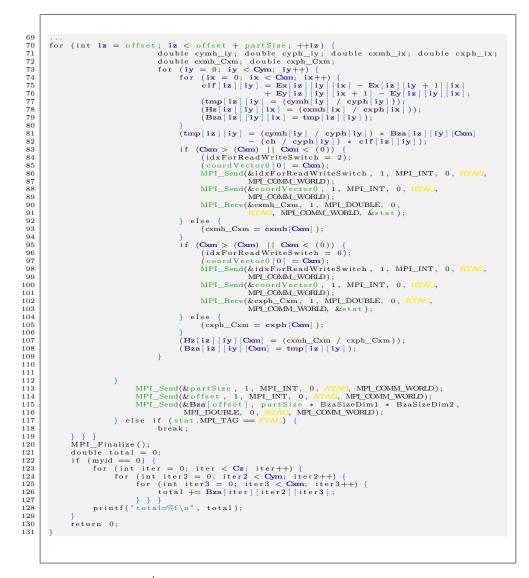

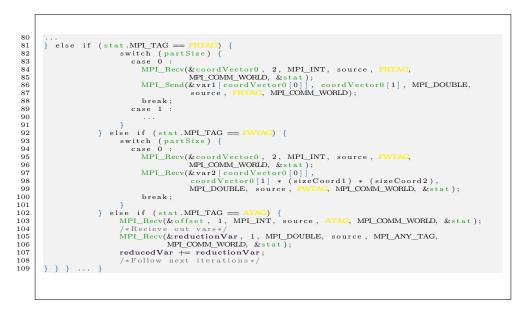

| 4.3 | Automatically generated MPI source code with expanded slave code. OMP2MPI automatically groups accesses into read/write requests with conditional range updates. $(2/2)$                                    | 71 |

| 4.4 | Automatically generated MPI source code with expanded master code. $(1/2)$                                                                                                                                  | 75 |

| 4.5 | Automatically generated MPI source code with expanded master code. $(2/2)$                                                                                                                                  | 76 |

| 4.6 | Automatically generated MPI source code with expanded slave code. Each access to a variable implies a request to the master process                                                                         | 77 |

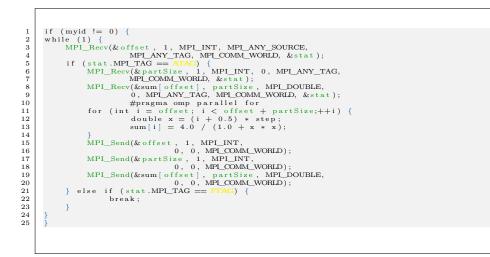

| 5.1 | Slave source code. Hybrid MPI + OpenMP $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                 | 92 |

| 5.2 | Automatically generated OpenMP + MPI source code with HMPP kernels using the proposed tools. $(1/2)$                                                                                                        | 94 |

| 5.3 | Automatically generated OpenMP + MPI source code with HMPP kernels using the proposed tools. $(2/2)$                                                                                                        | 95 |

# List of Acronyms

| <b>HPC</b> High-Performance Computing1                          |

|-----------------------------------------------------------------|

| <b>GPGPU</b> General Propose Units for Graphic Processing Unit7 |

| <b>GPU</b> Graphic Processing Unit                              |

| <b>MPI</b> Message Passing Interface xx                         |

| <b>OpenMP</b> Open Multi-Processing                             |

| CUDA Compute Unified Device Architecture                        |

| <b>OMP2MPI</b> OpenMP to MPIxiv                                 |

| <b>OMP2HMPP</b> OpenMP to HMPPxiv                               |

| <b>HMPP</b> Hybrid Multicore Parallel Programmingxiv            |

| <b>NoC</b> Network on Chip                                   |

|--------------------------------------------------------------|

| MPSoC Multi-Processor System on Chip7                        |

| <b>CPU</b> Central Processing Unit                           |

| <b>FPGA</b> Field Programmable Gate Array                    |

| <b>LLVM</b> Low Level Virtual Machine                        |

| <b>SDSM</b> Software Distributed Shared Memory Architectures |

| AST Abstract Syntax Tree xiv                                 |

| S2S Source-to-Source Compiler xiv                            |

| <b>RPC</b> Remote Procedure Call                             |

| <b>GOPS</b> Giga Operations per Second                       |

| <b>TRMM</b> Triangular Matrix Multiplication                 |

| WTAG Write Tag                                               |

| SWTAG Secure Write Tag                                       |

| RTAG Read Tag                                                |

| <b>FWTAG</b> Full Write Tag74                                |

| <b>FRTAG</b> Full Read Tag                                   |

| IN Input Variables                                          |

|-------------------------------------------------------------|

| <b>OUT</b> Output Variables                                 |

| <b>INOUT</b> Input Output Variables                         |

| <b>DSIP</b> Domain Specific Instruction-Set Processors      |

| <b>ASIP</b> Application Specific Instruction-Set Processors |

| MCAPI Multicore Communications API8                         |

| ${\bf HC}$ Heterogeneous Computingix                        |

| <b>CSV</b> Comma-Separated Values                           |

| <b>OpenCL</b> Open Computing Language                       |

| <b>OpenACC</b> Open Accelerators7                           |

| <b>CTM</b> Close To Metal                                   |

| <b>API</b> Application Programming Interfaces               |

| HWA Hardware Accelerator                                    |

| <b>COBOL</b> Common Business-Oriented Language              |

| <b>CST</b> Concrete Syntax Tree12                           |

| SIMD Single Instruction Multiple Data                       |

## Introduction | 1

Over the years, the High-Performance Computing (HPC) community has tried to increase computer performance and overcome all the problems found in the computing process (Figure 1.1).

Some years ago, digital microelectronics circuits reached the frequency scaling limit. An increment in frequency leads to an increment in power density (in  $W/cm^2$  according to Equation 1.1) that, in the early 2000s, reached a limit equivalent to the power density found in a nuclear reactor. This power dissipation problem made it impossible to continue to increment the frequency and limited computing performance, as shown in Figure 1.2.

$$P = C \times V^2 \times F. \tag{1.1}$$

Another problem is the continuously growing gap between Central Processing Unit (CPU) and memory speeds, as illustrated in Figure 1.3. This has been an important disadvantage for overall computer performance, as sometimes a processor is forced to stall while waiting for a memory operation to complete.

Finally, another important performance hurdle is the continuous increment in arithmetic intensity. Arithmetic intensity is defined as the number of floating-point operations needed to run a program divided by the number of bytes accessed in main memory [4]. Arithmetic intensity is found in recently proposed problems, which are more complex than old ones, but can be introduced into old problems by scaling the problem size.

The HPC community is attempting to overcome these problems by implementing new strategies that increase performance. At the same time, they continue to keep Moore's Law [5] relevant by proposing new architectures that are able to surpass the limitations of conventional systems. Moore's law is a self-fulfilling

#### CHAPTER 1. INTRODUCTION

Figure 1.1 Growth in processor performance since the late 1970s. Source: [1]

prophecy that states that, over the history of computing hardware, the number of transistors in a dense integrated circuit doubles approximately every two years, as illustrated in Figure 1.4. Initially, it was proposed in the form of an observation and forecast. Since it has become widely accepted, it has been converted into a goal for the entire industry. Moore's Law, even with some pessimistic predictions, is still relevant. The aforementioned issues do not affect it, and the number of transistors is still doubled every 18 to 24 months.

Nonetheless, the HPC community has noted that with the end of frequency scaling, these transistors can no longer be used to increase frequency scaling, but can be used to add extra hardware, such as additional cores, to facilitate parallel computing. The clock frequencies of leading processors are now saturated, and architectural innovations are expected to keep raising the overall performance, such as via multi-core processing, which uses various cores to provide performance gains. This allows computing density to continue to double while reducing per-processor power consumption and heat.

In this context, parallel programming has become a necessary tool provided by the HPC community. However, parallel programming is complex for a variety of reasons. Applications are now no longer sequentially executed but divided into a more complex map composed of parallelizations. Further, parallel programs need to communicate among processors in order to coordinate certain tasks.

Parallel applications can be written using a variety of parallel programming paradigms, i.e., message passing, shared memory, parallel data, bulk synchronous parallel data, and mixed-modes. There are two de-facto standards for programing parallel code.

Figure 1.2 | Power density wall. Source: S. Borkar (Intel)

Figure 1.3 Performance gap, measured as the difference in time between processor memory request (for a single processor or core) and the latency of the DRAM access, over time using 1980 performance as a baseline. Source: [1]

#### CHAPTER 1. INTRODUCTION

Figure 1.4 Moore's 1965 prediction that the number of "minimum cost" components on a chip would double each year, based on historical data and extrapolated to 1975. Source [2]

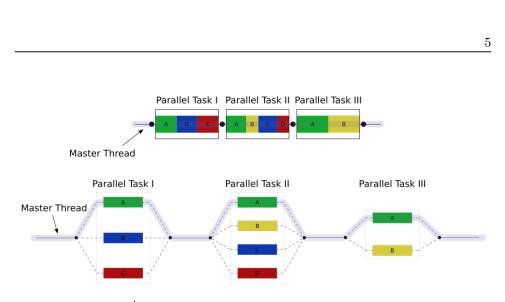

The first, MPI, advocates explicitly embedding communication primitives in the source code, making it difficult to read and maintain. The other, Open Multi-Processing (OpenMP), advocates a pragma-based approach that makes the compiler responsible for the efficient parallelism of the application through the use of a set of task division directives, as illustrated in Figure 1.5.

OpenMP version 2.0 primarily specifies ways to parallelize highly regular loops by using directives (shuch as parallel, do, section) that allow defining the blocks that have to be parallelized as well as the scope of the variables (either private or shared) of the variables inside these blocks. The standard offers other directives to define synchronization in a finer grain (such as critical, atomic) and includes some run-time functions that help implementing the necessary control of typical parallel program (like omp\_set\_num\_threads, omp\_get\_threads\_num).

Version 3.0 included more control with new directives, including the concept of tasks and task constructs. Version 4.0 includes support for accelerators, atomics, error handling, thread affinity, tasking extensions, user defined reduction, and Single Instruction Multiple Data (SIMD) support. One of the strengths of the OpenMP paradigm is the simplicity of its programming model. In this paradigm, the invocation of communication primitives are hidden from the programmer, as they are implicitly introduced by compilation directives working in conjunction with OpenMP at run-time. However, its use is usually limited to shared memory systems. Large HPC systems (such as the ones in the top 500 list) are often created by replicating nodes that contain some memory and a number of sockets

Figure 1.5 | Paralleled tasks using OpenMP blocks. Source: [3]

with multi-core processors or accelerators that can access that memory. Memory on remote nodes is not usually visible in the address space of applications running on one node. This makes OpenMP limited to the node domain. Thus, OpenMP applications are difficult to scale to a larger number of nodes (and cores) without introducing other paradigms such as MPI.

There are run-times that can overcome this limitation, usually by implementing software distributed shared memory (SDSM). They are also transparent to the programmer and, consequently, do not allow any fine tuning that could be needed to better adapt to the potential to different contexts. Moreover, they cannot be generally applied to all distributed memory platforms.

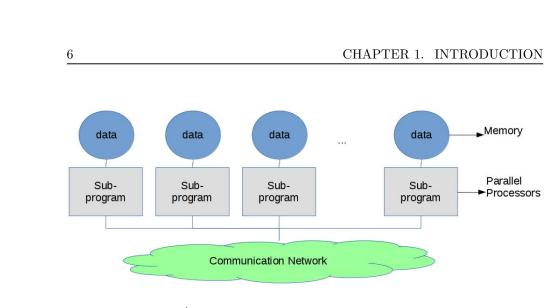

In contrast, MPI is a de-facto standard commonly used for large HPC applications. In this paradigm, the communication primitives must be explicitly coded. Introducing the communication primitives to implement the cooperation patterns makes the code larger and more difficult to read and understand. Obviously, it is more complex to learn because there are many functions, including point-to-point communication primitives as well as collective communication primitives. This coding effort is justified if it is needed for the execution of thousands of cores. MPI allows cores on different nodes to communicate. One might think that this introduces more performance overheads at the node level than OpenMP. However, this is a controversial issue with no clear answer, as shown in [6, 7]. Several versions have been presented since it was first published. Version 1.3 (commonly referred to as MPI-1) emphasizes message passing and has a static runtime environment. The following version, MPI-2.2 (MPI-2), includes new features such as parallel I/O, dynamic process management, and remote memory operations. The most recent

Figure 1.6 | Paralleled task using distributed memory architecture. Source: [3]

version, MPI-3.1 (MPI-3), includes extensions to the collective operations with nonblocking versions and extensions to one-sided operations<sup>1</sup>. Adoption of MPI-1.2 has been more extended during last years, essentially in HPC, but MPI-2.1 have been less repercusion and acceptance. We can see that many of the applications implemented using MPI-1.2 are using just a small subset of that standard, which has mean that there has been notreal need to add MPI-2 functionalities. The basic MPI functions (the complete set of functions can be found in [8]) and subroutines needed to divide tasks as illustrated in Figure 1.6. These can be divided in 4 main subsets: 1) Initialization and finalization functions to control the program flow, 2) Functions that define or report the logical topology of the distributed system (number of available slaves and execution IDs), 3) Data transference functions, dedicated to distribute data necessary for computation among the different nodes either synchronously or asynchronously . 4) Functions that control the communication process, to support, for instance the asynchronous operations (wait, test).

Another option that the HPC community uses to overcome frequency scaling, memory gap, and arithmetic complexity growth problems is to specialize processors for particular tasks, thus creating HC architectures. In those, specialized processors and conventional multi-cores will work together. Heterogeneous architectures have been presented as an architectural solution to all possible scenarios, and highperformance computers are increasingly based on HC architectures. The specialization of computational units and the adoption of different models of computation in various nodes increase system performance and energy efficiency.

$<sup>{}^{1}</sup>Summary \ extracted \ from: \texttt{https://en.wikipedia.org/wiki/Message_Passing_Interface}.$

One example of these target architectures is the General Propose Units for Graphic Processing Unit (GPGPU). GPGPUs were proposed as promising vehicles for general purpose HPC and have become a popular part of such HC architectures because they obtain better speedup than parallel CPU versions in many cases. Accelerators such as NVIDIA Graphic Processing Unit (GPU) and Intel Xeon Phi are gaining market share: a 2013 survey found that 26% of systems have one or more accelerators installed [9].

HC allows a huge range of processing elements to be deployed in a single workflow and, at the same time, the platform that best fits each combination of elements can be selected. HC is different from network computing or high-performance distributed computing. However, even when MPI-based network computing is considered in order to exploit non-shared memory architectures such as distributed computing clusters, network computing can also be applied to HC because it can contain structures such as Network on Chip (NoC)-based or Multi-Processor System on Chip (MPSoC), as demonstrated in [10].

The OpenMP and MPI paradigms for parallel computing significantly increase the performance of a sequential application. The use of specialized processors on GPGPUs has been shown to achieve speedups of up to  $100 \times$  those of conventional microprocessor architectures. Nevertheless, not all problems achieve the same performance increase, because any specific processor solution will be optimal for all kinds of computations.

There are two main barriers to HC use that might affect its wider adoption. First, the programming complexity required to distribute workloads across multiple processors is even more complex than in parallel computing. For example, for GPGPUs, a user must choose from a large number of alternatives proposed by the community, i.e., Compute Unified Device Architecture (CUDA) [11], HMPP [12, 13], RapidMind [14], Open Accelerators (OpenACC) [15], PeakStream [16], and Close To Metal (CTM) [17]. Even with these resources, programming a GPGPU is still complex compared to programming general-purpose CPUs, even when parallel programming models such as OpenMP [3] are used. This hurdle is combined with the additional effort needed to combine different kinds of processors. Neither issue is negligible. The potential advantages that an HC or parallel computing approach can provide have to be weighed against the cost and resources required to overcome them.

These complex and diverse scenarios open the door to new programming strategies that address them and ease the programming of emerging HC systems for nonexperts. These new strategies will also be useful for expert programmers to reduce the time needed for testing and selecting the best method for performance and thus fully exploiting the capabilities of HC architectures. It is therefore essential for

#### CHAPTER 1. INTRODUCTION

computer system researchers to facilitate these tasks. Researchers must offer new programming methods and tools to tightly integrate disparate computing elements on a platform with specialized processors while providing a programming path that does not require fundamental changes for software developers[18].

### 1.1 Motivation

Now that frequency scaling is no longer an easy way to improve computing performance, a new range of devices that exploit parallelism to drive performance have emerged. GPGPUs, and Many-Cores are examples of this new range of devices. However, the complexity of these new hardware architectures is not easily hidden from the programmer. To overcome this situation, many alternatives have been proposed, such as concurrent programming languages (e.g., Cilk and OCCAM), or extensions to existing languages (e.g., OpenMP [3], MPI [19], CUDA, Multicore Communications API (MCAPI), and [20]).

Parallel programming is not new. The HPC community has been active for a long time and usually works with a couple de-facto standards: MPI and OpenMP. The learning curve for new languages is usually steep, and it is desirable for legacy code to be executed on new platforms to take advantage of new capabilities.

The main motivation of this thesis is to ease the learning curve of parallel programming and HC architectures for the programmer. My strategy consists of letting users program in high-level C source code and provide some tools to refactor (or translate) the code into another form so that it can benefit from the specifics of the target architectures. The proposed tools fall into the category of S2S transformations, and are hence only a part of the compilation chain. Hence, they are complemented by standard front-end and back-end compilation tools. The expected benefits from these transformations are (1) better performance and (2) lower energy consumption.

Different types of parallelism can be exploited by this method depending on the targeted hardware architecture. For GPGPUs, source code transformations generally create kernels that have to be executed on the graphics accelerator. For homogeneous many-core accelerators (such as the Intel Xeon-Phi), we can combine different programming languages, models, and tools supporting Intel Architecture such as OpenMP, MPI, MCAPI, Open Computing Language (OpenCL), and Cilk. We also consider Application Specific Instruction-Set Processors (ASIP) or Domain Specific Instruction-Set Processors (DSIP). Related transformations can detect the instruction patterns for which the processors have been optimized and ensure that they are used. For devices such as Field Programmable Gate Array (FPGA) we

#### 1.2. OBJECTIVES

consider HC that combines soft-core processors and custom logic so that the transformation uses custom logic as much as possible.

### 1.2 Objectives

The HPC community is addressing the abovementioned needs by creating new strategies to increase performance using HPC architectures that can work around the limitations of conventional systems. This thesis reviews the proposed methods and focuses on facilitating the task to fully exploit the capabilities of HC architecture and parallel computation paradigms.

The main objective of this thesis is to efficiently orchestrate the distribution of computing tasks and loads on accelerator and HC platforms by providing a diverse suite of tools. These tools allow solutions to be obtained with close-to-optimal performance for certain tasks, such as diverse algebraic level-3 applications, even when they are inherently different.

Because the current number of available target platforms is large, the scope of this research is limited to a representative subset: (1) parallel programming on shared memory architectures using OpenMP, (2) distributed memory architectures using MPI, and (3) HC using both CPUs and GPGPUs. A modular approach is used to build each of these three platforms. This modularity provides better adaptability to future input/output programming languages in a domain that is not yet stable.

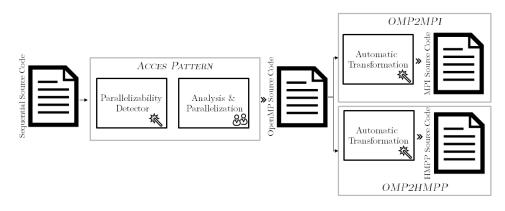

The main idea is to build a set of tools that demonstrates the viability of automatically refactoring high-level C source code into the target programming languages. The proposed workflow is described in Figure 1.7.

OpenMP is defined as the common factor for all transformations because I consider it to be the simplest way to describe a parallel program while maintaining the structure of the sequential source code. OpenMP allows OMP2MPI and OMP2HMPP tools to work with the same input code. These tools generate new code that can be analyzed by time or an energy/time trade-off, if the target system is able to measure it. The code generated by these compilers for any selected architecture leads to more efficient implementations on heterogeneous platforms.

To reach this goal, the first step is to understand the differences between sequential and parallel code, especially to detect which parts of a sequential program can be parallelized without modifying the final result. These parts are mainly loops because the instructions inside them are repeated as sequential executions and therefore are fair candidates for large performance gains when distributed.

It is easier to determine whether simple (that is easy to understand) code can

10

#### CHAPTER 1. INTRODUCTION

Figure 1.7 List of objectives for each of the three S2S compilers (Access Pattern, OMP2MPI, and OMP2HMPP)

be safely parallelized. However, determining this for more complex code that can include conditional clauses and function calls is not as easy. One of the fundamental roadblocks to parallelization is data dependency. When an operation depends on data that has to be previously computed, the execution of the operation has to be delayed until operands are available. Inter-dependencies between variables are very common in procedural programming languages, which were conceived for sequential execution such as C/C++, Java, and many others. The proposed tool facilitates the detection these data dependencies and illustrates them in order to clarify how the initial source code can be parallelized.

Once we have parallel code written in OpenMP, I offer two different tools that generate code able to fully exploit the capabilities of HC architecture, including parallel computation. The first focuses on GPGPUs. This new tool(OMP2HMPP) helps generate code for GPGPUs and combine it with CPU parallel code written using OpenMP.

In contrast, I also extend the use of parallel programming to distributed memory architectures through the use of MPI. I offer a tool that transforms OpenMP source code into MPI source code. The resulting code is able to execute in different kinds of DM systems, such as large HPC clusters or experimental distributed memory processors such as Intel Polaris, Ambric, or experimental FPGA based multi-softcores (such as [21]). Another potential use is to check if there is any performance gain when using MPI for coding a given application on the same shared memory platform or when combining it with OpenMP.

### **1.3 State-of-the-Art Technologies**

As described in Section 1.2, this thesis proposes a new tool chain composed of three different modules. These modules are implemented as S2S compilers that transform sequential C/C++ source code so that it works in a different programming paradigm, i.e., parallel programming either on shared memory architectures, distributed memory architectures, or heterogeneous architectures that include GPGPUs.

#### 1.3.1 Compilers

For many years, assembly code was the way to program code for computers. Each program was specific to a determined task and dependent on the kind of CPU used. With the invention of compilers, programmers where allowed to reuse their software on a variety of CPUs. These compilers became essentials in the process of software implementation. Hopper developed the first compiler, which was devoted to the A-0 programming language, in 1952. With that machine-independent programming languages adoption was extended, leading to the birth of Common Business-Oriented Language (COBOL), which is considered one of the first high-level programming languages.

However, although the most common reasons for compilers since then is to transform source code into a binary form to create an executable program or generate assembly language or machine code to produce a binary form, this thesis is mainly based on compilers that are not dedicated to this task. The extended meaning of compilers as used in the proposed tools is as a specific type of translator. This meaning encompasses the meaning of the original compilers as well.

There are six main extended operations in a compilation procedure: lexical analysis, preprocessing, parsing, semantic analysis (syntax-directed translation), code generation, and code optimization. More abstractly, compilation occurs in two phases. The first one (front-end), is dedicated to analyzing the correctness of the input code by breaking it into abstract symbols that represent lexical units (tokens). Analyzing these tokens, which must be ordered as the compiler expects, follows the description of the form that is defined for all corresponding different sequences of characters. This defines the nodes and allows semantic analysis. There are different intermediate representations of code: semantic graphs, control flow graphs, or the AST. The AST has control of the symbol table, which defines where any symbol in the source code is mapped including contextual information as the type, scope or location. The next step, the semantic analysis, is by definition more complex since it took the tokens as a group, generating sentences that have to

## CHAPTER 1. INTRODUCTION

mean together, it is normally hand written, even that in some cases can be partially or fully automated by the definition of productors of attribute grammars that encapsulate the possible group formations. We can subdivide the explained phases in subgroups: 1) lexing, that will allow scan and evaluation, 2) parsing, generate the Concrete Syntax Tree (CST), that are concrete being easy to generate and represent the input as a tree but are difficult to analyse, and 3) transforming, that translate it to an AST, more abstract, represents in a hierarchical data structure all the syntactic clutter, allowing more easy understanding for further analysis and translation stages.

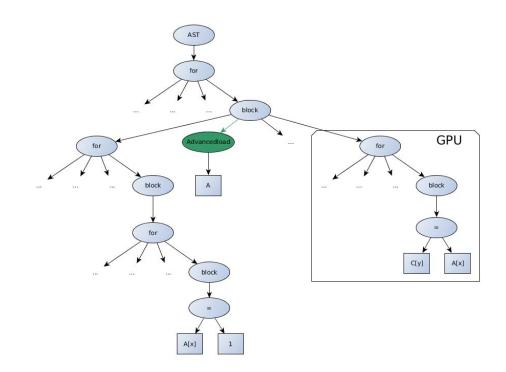

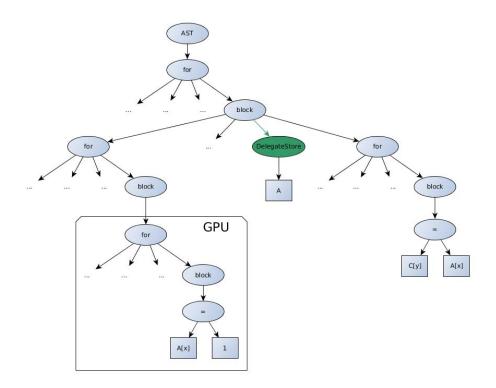

This thesis focuses on understanding and modifying the AST. The AST represents the source code hierarchically as a tree of nodes that includes constants or variables (leaves) and operators or statements (inner nodes). A simple representation of a structure of the AST is shown in Figure 3.11. The AST is often used to generate the intermediate representation, also called an intermediate language, for the code generation. These intermediate languages enable the second phase of a compiler, the optimizations. We can describe many kinds of optimizations at this point, removal of useless or unreachable code, localization and propagation of constant values, relocation of computation to a less frequently executed place (e.g., out of a loop), or specialization of computation based on the context, are part of these. Finally, the code generation is optimized for a target system.

The number of phases used in a certain compiler allows us to classify them in different categories. We can think then, in different front ends for different languages combined back ends oriented to various CPUs, thanks to the separation of these phases. The extended GNU Compiler Collection, or the more new Low Level Virtual Machine (LLVM), are an example in which we can find this combinations. Those compilers combine multiple front-ends and multiple back-ends but they share analysis stage.

We jump over the complexity of parsing the syntaxes and semantics of the input source code and focuses on the S2S compilers or transcompilers. In this kind of compiler, either the input or output will be a high-level language. For S2S compiler infrastructure, there are many possible solutions, such as LLVM [22], PIPS [23], Cetus [24], ROSE [25], and Mercurium [26]. Mercurium supports C/C++source code, which is the main reason it was chosen. As stated in [27], which describes most problems that can be found when parsing C++, this is not an easy task. Using the Mercurium infrastructure allows focus to remain on the creation of the S2S compilers by offering a friendly abstract representation through its intermediate representation (AST). AST provides easy access to the source code structure representation, the table of symbols, and the context of their context using a well-documented API that allows it to be further extended.

#### 1.3. STATE-OF-THE-ART TECHNOLOGIES

With access to the AST, implemented S2S compilers are able to modify it by adding new semantically correct trees while maintaining tree consistency. Our compilers are based on the premise of find and replace or reformulation. The compilers are able to find patterns, understand how they are used, and then generate code that works in the target architecture. One of the earliest S2S compilers was by Digital Research XLT86 in 1981. In this case, the compiler was able to transform .ASM code originally designed for the Intel 8080 processor into .A86 source code for the Intel 8086. There are other actual target-specific examples, such as CFRONT (C++ to C) and HIPHOP for PHP (PHP to C++), and others that are able to transform code to more than one target, such as LLVM [22], which can translate any language sported by gcc 4.2.1 to ADA, C, C++, Fortran, Java, Objective-C or Objective-C++, or from clang to C, C++, or MSIL.

The proposed S2S compilers are a part of the second subset running on top of the Mercurium platform. As explained in [28], this platform has been mainly used in the Nanos environment to implement OpenMP, but because it is quite extensible, it has also been used to implement other programming models or compiler transformations. Extending Mercurium is done using a plugin architecture, where plugins represent several phases of the compiler. These plugins are written in C++ and dynamically loaded by the compiler according to the selected configuration. Code transformations are implemented on the source code so that there is no need to know or modify the internal syntactic representation of the compiler.

## 1.3.2 Transformations

As was explained in [29], to fully utilize the power of heterogeneous machines or parallel programming paradigms, programmers must efficiently parallelize and map their applications. This task is far from trivial, leading to the need to automate this process. Automatically transforming sequential code into parallelized code is more feasible on a shared memory architecture. This process could be either partially addressed by tools that analyze the code to exploit parallelism or a fully automated process. Most of the proposed tools are of the first type, in which techniques are built-in in some parallelizing compilers, but the user needs to identify parallelizable code and mark it with special language constructs. This is also the case for the tool proposed in this thesis. The compiler identifies these language constructs and analyzes the marked code for parallelization. These parts tend to be loops.

## CHAPTER 1. INTRODUCTION

#### From sequential to parallel code (parallelizing compiler)

Most compilers built for automatic parallelization research consider Fortran programs [30, 31, 24, 32]. Fortran cannot produce aliasing when identifying data dependency, in contrast to languages such as C and C++. Aliasing occurs when a data location in memory can be accessed through different symbolic names in the program. Thus, modifying the data through one name implicitly modifies the values associated with all aliased names, which may not be expected by the programmer. As a result, aliasing makes it particularly difficult to determine the data dependencies of a program. Aliasing analyzers try to compute information that is useful for understanding aliasing in programs. Therefore, C/C++ is generally difficult to analyze when pointers are involved. If there are further dependencies in the identified code sections, the possibilities for parallelization decrease. Nevertheless, a few compilers take C as input source code and transform these to OpenMP. One example is [33], which uses the parallelization methodology explained in [32] and applies it to C source code or PLUTO [34]. In both cases, the user has to use a set of new pragma directives defining the scope and mark the blocks of code that should be analyzed for parallelization. That tool generates a naive OpenMP version of the sequential source code when it detects loops that can be parallelized without modifying their form. Nonetheless, it has the drawback that it only transforms originally written C source code.

An experimental comparison using some of the tools mentioned above is presented in [35]. The automation of the parallelization process is neither optimal nor ready to become a widely adopted in practice, even for commercial compilers [36, 37], because of the complexity of changing from sequential to parallel code. Most cases require a more exhaustive analysis of the parts of the code with data dependencies and their adaptations to the parallel programming paradigms. Further work is needed to provide tools to programmers for the parallelization of sequential code. These tools demonstrate the variable access patterns and theory of data dependencies. Various examples are [38], [39], [40], and [41]. Examples of more complex representation are those proposed in [22] or the polyhedral model that produces graphics showing the dependency between iterations [42]. The main characteristic of our tool is that it tries to keep the visualization simple and at the same time analyze complex AST structures that could contain function calls that result in context switching.

## From shared to distributed memory

The second tool of this proposal is dedicated to generating parallel code for distributed memory architectures using MPI. This tool uses generated code to gen-

## 1.3. STATE-OF-THE-ART TECHNOLOGIES

erate solutions that can be executed using distribute memory architectures. Code can come from the access pattern and data dependency analysis extracted by the previous tool or from the code of existing OpenMP implementations that will be reused. Most projects that use OpenMP code for distributed memory architecture rely on the use of a software layer to manage data placements on the nodes ( Software Distributed Shared Memory Architectures (SDSM) architectures). OMNI OpenMP [43] and its optimization (proposed in [44, 45]) are examples of alternatives to support OpenMP in a distributed memory environment using SDSM as an underlying run-time system. Cluster-enabled OMNI OpenMP on SCASH is an implementation of the OMNI OpenMP compiler for SDSM system SCASH running under score cluster system software. Another important software system is Cluster OpenMP, proposed by Intel [46] (although it was discontinued few years ago). All these solutions, based on the software layer, can be used on distributed architecture without using MPI but need some kind of run-time. In contrast, OMP2MPI shows the generated solution that will be executed on the cluster to the programmer. This solution can be further optimized if needed by an expert, thus offering more flexibility about how the code is executed in the cluster.

Other similar ways to port OpenMP programs to clusters were proposed in Pa-RADE [47], which is based on the OMNI compiler, or included in Polaris as [48]. Both combine the data management software layer with MPI primitives.

In [49–51], the authors proposed extending OpenMP with additional clauses for streamization, as I do. Nonetheless, the most similar tools to the ones proposed in this thesis were proposed in [52, 44] and [53]. The first is based on Cetus [24] and the second on PIPS [23].

## Transforming for GPU use

I also explore the use of GPGPUs to increase performance in HC systems. The dominant GPU programming models have traditionally been CUDA [11] and OpenCL [54]). In recent years, many S2S alternatives have been proposed to overcome GPGPU programming complexity. Some of them are similar to the tool proposed in this thesis. In contrast to OMP2HMPP, their methods transform code to the CUDA language, not to HMPP, which means that CUDA programming complexity is directly exposed to the final user.

Some of the proposals extend, in one way or another, the current standards such as C/C++ and OpenMP to trivialize the programming task [55], [56]. In contrast, there are proposals that do not require any language extension to transform the source code directly from CPUs to GPUs.

## CHAPTER 1. INTRODUCTION

One example that includes language extensions is proposed in [15]. CAPS, CRAY, Nvidia, and PGI (members of the OpenMP Language Committee) published OpenACC in November 2011. OpenACC has been proposed as the standard for directive-based standard programming, as it contributes to the specification of OpenMP for accelerators. In the same way, but not with the same consensus, a programming interface called OpenMPC was presented in [57]. This paper analyzes extensively the actual state-of-the-art OpenMP for CUDA S2S and CUDA optimizers. OpenMPC provides an abstraction of the complexity of the CUDA programming model and increases its automation though user-assistance tuning systems. It takes time to understand the newly proposed directives for both OpenMPC and OpenACC and to manually optimize the data transfer between the CPU and GPU. In contrast, OMP2HMPP adds just two new OpenMP directives, and the programmer does not need to deal with new languages and their underlying optimization. Another option, as explained in [57], is the hiCUDA directive-based language [58], which is a set of directives for CUDA computation and data attributes in a sequential program. However, hiCUDA has the same programming paradigm as CUDA. Even though it hides the CUDA language syntax, the complexity of the CUDA programming and memory model is directly exposed to programmers. Moreover, in contrast to OMP2HMPP, hiCUDA does not provide any transfer optimization. Finally [59] and [60] proposed an OpenMP compiler for hybrid CPU/GPU computing architecture. In these papers, the authors propose adding a directive to OpenMP in order to choose where the OpenMP block must be executed (CPU or GPU). The process is fully hidden from the programmer and is a direct translation of CUDA. Again, it does not provide any transfer optimization.

There are fewer proposals that try to directly transform C/C++ code into CUDA without the need for any new language extension. Ref. [61] presents a tool that uses unimodular loop transformation theory to analyze the loops that could be transformed to work in parallel kernels (either OpenMP or CUDA) through the ROSE compiler [25]. Par4All [33] transforms code originally written in C or Fortran to OpenMP, CUDA, or OpenCL. Par4All uses a polyhedral model to analyze and transform C/C++ source code. It also adds OpenMP directives where it thinks this would be useful. This transformation allows the re-factorization of the newly created OpenMP blocks into GPGPUs kernels by moving OpenMP directives into the CUDA language. However, this transformation does not take into account the kernel data-flow context and this leads to non-optimal data transfer results. Regardless, both tools, as well as the tools that transform sequential code to OpenMP, could be useful for generating input code for the proposed OMP2HMPP tool. All that is required is the substitution of the code generated after the access pattern study. This is because of the inherent modular work-flow of the tools proposed in this thesis.

# Visualizing Data Access Patterns in Loops to Identify Potential Parallelism

2

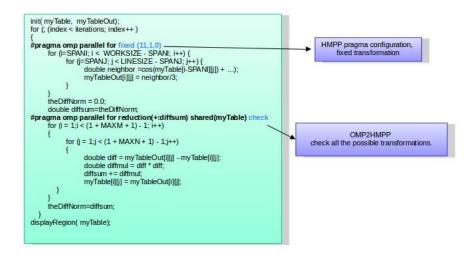

The objective of the first S2S process in the chain (and its related tool) is to provide a way to refactor an input C/C++ source code into another form so it can benefit from the advantages of parallel computing on shared memory architectures using OpenMP, as illustrated in Figure 1.7. This process cannot be fully automated in most cases because of the task complexity, but the tool facilitates this task by providing essential information to the user. The tool detects parts of a sequential code that can be parallelized without modifying the final result obtained by the execution of the initial application.

Simple code can be easy to understand and determine if it can be safely parallelized; however, more complex code, which can include conditional clauses and function calls, is not so easy. The proposed tool is mainly devoted to detecting data dependencies in applications that can make the parallelization of the original source code prohibitive. Inter-dependencies between variables are terribly common in procedural programming languages that were conceived for sequential execution such as C/C++, Java, and many others. When an operation depends on data that has to be previously computed, its execution has to be delayed until all operands are available.

The proposed tool, introduced in [62], mainly focuses on loops, since the instructions inside them will be repeated in sequential execution and are fair candidates for obtaining large performance gains when distributed. Taking as an example a

18

Table 2.2

Simple C non-parallelizable source code

simple C input source code, it is easy to see that some such loops can be easily executed in parallel if they do not exhibit dependency, as illustrated in Table 2.1, where all ten iterations could be executed simultaneously without any problem. Every iteration is independent because the index of access for variables A and B is the actual value of the iterator used in the loop.

Changing the problem by adding an index access with a different value than the variable iterated, as illustrated in Table 2.2, shows iterations that should be executed sequentially. In this case, iteration i needs data from a former iteration. Note that in this case, the subtraction operation is irrelevant; any operation would produce the same data dependency. Such a data dependency could mean that this piece of code cannot be parallelized. Although in the proposed problems in Tables 2.1 and 2.2, the data dependency is easy to see, there are plenty of more complex problems for which it would be necessary to perform a more exhaustive analysis.

To trivialize the parallelization task, the proposed tool provides a trace log of all the variables accessed inside any marked loop of interest and provides a tool to visualize data dependencies in an easy way.

To do this, the implemented procedure is divided into three stages: (1) instrumentation by manually introducing some pragmas in the code to identify the section to be analyzed and using a S2S compiler to complete the instrumentation, (2) execution to create a memory access trace, and (3) visualization to view the data accesses pattern in the loops of the application to detect if there are dependencies that prevent them from being unrolled.

## 2.1. AUTOMATIC INSTRUMENTATION

## 2.1 Automatic Instrumentation

To automatically introduce a log-in function into an input source code, the implemented tool requires source code to be marked using a new pragma directive. This new directive describes the information that needs to be analyzed inside the marked block.

The created directive is *analyze\_access\_pattern*, and it can be completed using two clauses: *var* and *iter*. Table2.3 shows an example of the use of this new directive using both clauses. The *var* clause determines the target variables in which data dependency could appear (marked red), and the *iter* clause determines the iterators targeted in the access log (marked blue).

Having defined the variables of interest (using the *var* clause) and the iterators (using the *iter* clause) in a loop that the programmer wants to analyze, the S2S compiler traverses the AST, detecting memory accesses and including the proper log functions in the detected points.

To generate a well-formed trace log, a set of log functions are defined. These functions are introduced automatically by a new S2S compiler inside the original source code. Later execution of the generated code provides a complete trace log that has the information required to detect all the possible access patterns and related data dependencies.

The set of proposed functions is divided by its functionality: (1) to understand the context, (2) to describe the variables of interest in that context, and (3) to identify how these variables are used.

Within a loop context, the user is interested in knowing how that loop is constructed. Analysis of the AST allows us to detect the desired loop structure. Hence, the following functions are provided:

```

void mem_trace_loop_start(char* var);

void mem_trace_loop_end(char* var);

void mem_trace_iter_start(char* var, int v);

void mem_trace_iter_end(char* var, int v);

```

These functions allow which accesses are done in which operation of which loop to be identified. Every loop that the user wants to analyze during the program is uniquely identified by a name. Iterations are identified by the iteration variable and its value. The first two functions are located before and after the loop of interest. The last ones are located inside the loop body, defining the context of every iteration.

To analyze the use of the variables and their access, we need first to define them by describing their dimensions and the place they occupy in memory. By knowing the

## CHAPTER 2. VISUALIZING DATA ACCESS PATTERNS

size (number of dimensions and size of each), the base memory position, and the type size of variables, we can exactly track which variable elements are accessed. The proposed tool focuses on arrays because the access pointers to them could be more difficult to follow. Finding declarations is usually a difficult task, but, by exploring the AST context, we can detect global or local variables as well as dynamic pointers and their size at a certain point in the code. To describe this variable information, the following list of four functions is defined:

```

void mem_trace_def_array1d(char* v, int d1);

void mem_trace_def_array2d(char* v, int d1, int d2);

void mem_trace_def_array3d(char* v, int d1, int d2, int d3);

void mem_trace_def_mem(char* var, void* ptr, int typeSize,

int varSize);

```

The first three functions are dedicated to determining the size of each of the dimensions for each array of interest (there is a limit to the number of dimensions that define a variable, but this value could be extended in future implementations). In contrast, the last trace function is used to provide memory information.

Finally, two functions are defined to log memory accesses. These functions distinguish two kind of accesses (read or write), and are inserted before any variable calculation expression. Read operations are placed first, followed by write operations. Expressions are usually the last node in an AST. To determine if a symbol is read or written, we analyze two factors in the considered expression. The symbols contained in the second operand of the expression are always considered read access. The first operand is determined by analyzing the operation of the assignment, since some cases can also contain a mathematical expression such as addition, subtraction, multiplication, or division. There is a particular case in which the compiler finds a function call with parameters for analysis for which the type of access cannot be determined at that point. In order to solve this issue, we inline the function, following the methodology explained in Section3.2.2. In order to add the analyzed information, the following set of functions are used for labeling the expressions:

## 2.1.1 Results

Table 2.3 illustrates an example of some input code and Table 2.4 shows the source code generated automatically by the proposed S2S tool.

void mem\_trace\_read(char\* v, void\* idx); void mem\_trace\_write(char\* v, void\* idx);

Just the variable name and pointer are used. In fact, the variable name is redundant, since it could be derived from pointer information.

## 2.2. EXECUTION

```

1 double alpha;

2 double A[N] [N];

3 double B[N] [N];

4

5 int main(int argc, char** argv) {

6 int i, j, k;

7 int n = N;

8 init_array();

9 #pragma analyze_access_pattern var(A,B) iter(i,j)

10 for (i = 1; i < n; i++)

11 for (j = 0; j < n; j++)

12 for (k = 0; k < i; k++)

13 B[i][j] += alpha * A[i][k] * B[j][k];

14 return 0;

15 }

```

Table 2.3Input code

## 2.2 Execution

This is the simplest stage of the proposed work-flow. The automatically generated source code, explained on Section 2.1, is executed. The execution extracts the log of memory accesses.

We encourage working with smaller workloads and thus with higher productivity. The execution process produces a memory overhead and a large demand for memory when visualizing the accesses. Nonetheless, the nature of the data access pattern algorithm is usually independent of the size of the data. For instance, in order to capture and analyze the data access pattern of a matrix multiplication that uses  $1,000 \times 1,000$  matrices, it is sufficient to analyze the  $10 \times 10$  case. This simpler case can provide the information required to discover the related effective parallelization strategy.

## 2.3 Data Analysis

The main principle is that all memory accesses should be aggregated in the same iteration. It makes no sense to look at individual read and write operations. What it is needed is understanding of how different iterations access different memory positions. Furthermore, before visualizing any data, collected information is aggregated so that it can be usefully presented.

Data analysis basically consists of collecting information about when read or write operations happen for each variable. In the case of arrays, this information has to be obtained for every element of the array.

## CHAPTER 2. VISUALIZING DATA ACCESS PATTERNS

Table 2.4

Transformed code

Using the tracing functions added by our S2S compiler, it is possible to automatically track every iteration thanks to an added keyword. This keyword is composed of the name of the loop and the value of the iteration index. If a hierarchy of loops is analyzed, the keywords are formed by the combination of each iteration identifier.

The data analysis step demands a large amount of memory because it needs as many versions of the data access information as iterations (or iteration combinations) that occur at run time.