#### Wideband pulse amplifiers for the integrated cameras of the Cherenkov Telescope Array

Andreu Sanuy Charles

**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (**www.tdx.cat**) i a través del Dipòsit Digital de la UB (**diposit.ub.edu**) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX ni al Dipòsit Digital de la UB. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX o al Dipòsit Digital de la UB (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (**www.tdx.cat**) y a través del Repositorio Digital de la UB (**diposit.ub.edu**) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR o al Repositorio Digital de la UB. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR o al Repositorio Digital de la UB (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (**www.tdx.cat**) service and by the UB Digital Repository (**diposit.ub.edu**) has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized nor its spreading and availability from a site foreign to the TDX service or to the UB Digital Repository. Introducing its content in a window or frame foreign to the TDX service or to the UB Digital Repository is not authorized (framing). Those rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author.

## Wideband pulse amplifiers for the integrated cameras of the Cherenkov Telescope Array

Memòria per optar al títol de doctor per la Universitat de Barcelona en Enginyeria i Tecnologies Avançades

#### Andreu Sanuy Charles

Director: David Gascón Fora

Tutor: Pere Miribel Català

Departament d'Electrònica Facultat de Física Universitat de Barcelona

#### Wideband pulse amplifiers for the integrated cameras of the Cherenkov Telescope Array

This thesis was submitted to the Faculty of Physics, University of Barcelona (UB), as a fulfillment of the requirements to obtain the PhD degree. The work presented was carried out in the years 2010-2015 in the Department of Electronics at UB with the help of my advisor David Gascón.

**Short abstract:** This thesis is focused on novel design circuitry for the channel signal path of a Cherenkov Telescope camera. The amplification is divided into gain stages in order to achieve the requirements of the design. The first stage, presents an innovative low noise wideband pre-amplifier design whereas, the second amplification stage proposes a novel gain circuitry design, being impossible with the classic schemes at the required technology. This second stage also derives and adapts the signal to the following parts of the read-out system of the Cherenkov Telescope camera.

An innovative design that achieves all the restrictions with very low power consumption fulfills the requirements for the first pre-amplification stage. The solution selected is based on a novel current mode circuit to create multiple gain paths at the very front end of the input stage of the readout electronics, simultaneously achieving high dynamic range, low noise, low input impedance, low voltage and low power performances.

The pre-amplification stage also comprises a closed loop transimpedance amplifier with a novel class AB output stage designed with a  $0.35\mu m$  SiGe technology, allowing the design to drive a cable or a transmission line (typ.  $50\Omega$  load) while preserving high bandwidth with moderate power consumption.

This thesis presents an alternative method to implement fully differential wideband pulse amplifiers. The required gain can be reached, while preserving also the bandwidth. Linearity for fast pulses is at the level of solutions based on feedback OTA, limited by slew rate and other transient issues. The design exhibits a large degree of tuneability. An amplifier in a  $0.35\mu m$  CMOS technology implements and validates the GBW product of 8 GHz. This design also incorporates a closed loop transimpedance amplifier with a novel class AB output stage based on the design of the first amplification stage, but designed in a  $0.35\mu m$  CMOS technology which is more difficult to achieve.

**Keywords:** Microelectronics design, silicon technology microelectronics, integrated circuits, telescopes.

### Contents

| Lis | t of I                                                                           | Figures                                                                                                                                                                                                                                                                                                                                            | ix                                                                                                                                                                                       |

|-----|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lis | List of Tables xi                                                                |                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                          |

| Ac  | know                                                                             | ledgements                                                                                                                                                                                                                                                                                                                                         | xiii                                                                                                                                                                                     |

| Re  | sum                                                                              |                                                                                                                                                                                                                                                                                                                                                    | xv                                                                                                                                                                                       |

| Ab  | ostrac                                                                           | t                                                                                                                                                                                                                                                                                                                                                  | xix                                                                                                                                                                                      |

| 1.  | Intro                                                                            | oduction                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                        |

| 2.  | <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> <li>2.5.</li> </ol> | Amplifier for the CTA cameras (PACTA)Design of PACTA2.1.1. Input stage2.1.2. Current readout stage2.1.3. Transimpedance stage2.1.4. Class AB output stage2.1.5. Small signal analysis2.1.6. Noise analysisPreAmplifier for CTA (PACTA) prototypesLayout details2.4.1. Package & usage2.4.2. Measurement resultsOther applicationsPACTA Conclusions | $     \begin{array}{r}       14 \\       14 \\       16 \\       16 \\       18 \\       22 \\       23 \\       27 \\       34 \\       34 \\       38 \\       51 \\     \end{array} $ |

| 3.  | -                                                                                | Differ for the CTA cameras (ACTA)         Design ACTA         3.1.1. Linearized HF Transconductor         3.1.2. Large Swing Current-to-Voltage Conversion         3.1.3. Output Buffer         Amplifier for CTA (ACTA) prototypes         Layout details         Results ACTA         3.4.1. Package & usage         3.4.2. Measurement results  | 62<br>64<br>65<br>66<br>74<br>78<br>78                                                                                                                                                   |

| 4.  | <b>Con</b><br>4.1.<br>4.2.                                                       | ACTA Conclusions                                                                                                                                                                                                                                                                                                                                   | 99<br><b>101</b><br>102<br>103<br>103                                                                                                                                                    |

|               | Journal papers    104      Conference papers    104 |   |

|---------------|-----------------------------------------------------|---|

| Bibliography  | 10                                                  | 7 |

| A. Appendix F | PACTA Datasheet 11                                  | 1 |

| B. Appendix A | ACTA Datasheet 13                                   | 7 |

## LIST OF FIGURES

| 1.1.         | Schematic of detecting gamma rays with Cherenkov telescopes. The Cherenkov light is beamed in the air shower and can be collected with optical detector. | 0               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|              | Referred to [1]                                                                                                                                          | 2               |

| 1.2.         | Scheme of stereoscopic observation with an array of IACTs [2]                                                                                            | 2               |

| 1.3.         | IACTs developed in the last 25 years                                                                                                                     | 4               |

| 1.4.         | Illustrative description of the CTA Medium-Sized Telescope (MST) design<br>with the main assemblies and components [3]                                   | 5               |

| 1.5.         | CTA will consist of three types of telescopes with different mirror sizes in order to cover the full energy range.                                       | 5               |

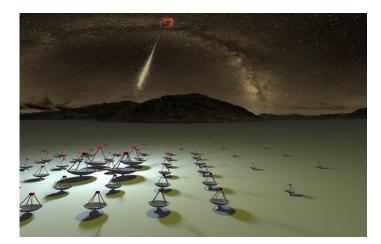

| 1.6.         | Artist's impression of telescope network for the CTA concept [4]                                                                                         | $\overline{7}$  |

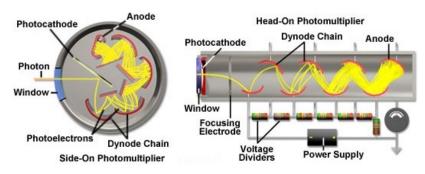

| 1.7.         | Photomultiplier vacuum tube cross-section with the common dynode chain configuration.                                                                    | 7               |

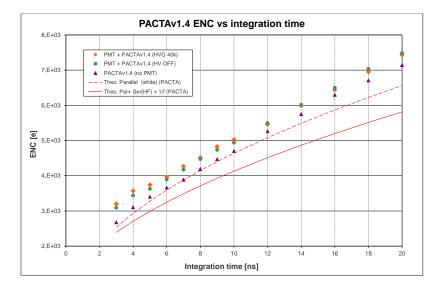

| 10           | Photomultiplier tube selected for the CTA consortium. The right one, shows                                                                               | '               |

| 1.8.         |                                                                                                                                                          | 8               |

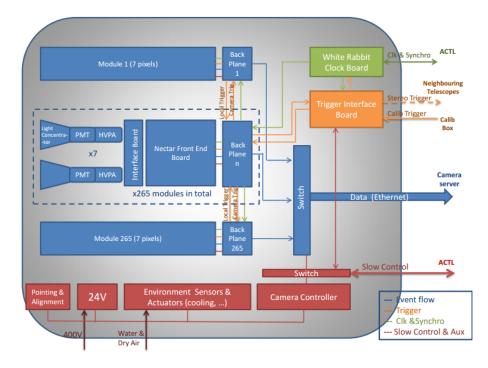

| 1.9.         | the dynodes structure and the left one is covered by mu-metal foil Global architecture of NectarCAM, with the analogue trigger implementation [3].       | 8<br>9          |

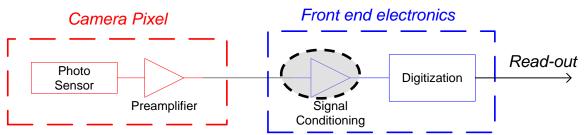

| 2.1.         | Block diagram of the CTA camera electronics.                                                                                                             | 11              |

| 2.2.         | Parallel noise requirement as function of integration time T, for different S/N                                                                          |                 |

|              | in the SPE spectrum.                                                                                                                                     | 12              |

| 2.3.         | Pre-amplifier block diagram of the current mode input stage and the low                                                                                  | 10              |

| 0.4          | impedance output buffer in differential mode                                                                                                             | 13              |

| 2.4.<br>2.5. | Block diagram of the current mode circuit                                                                                                                | 13              |

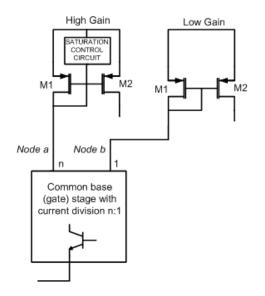

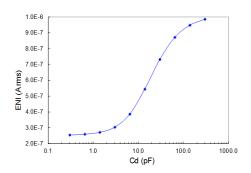

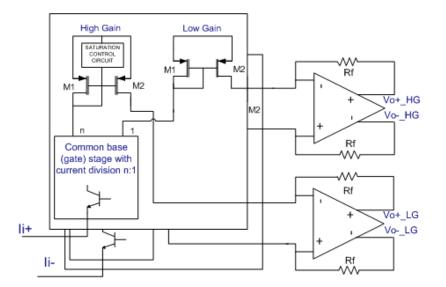

|              | division) of the PACTA chip                                                                                                                              | 14              |

| 2.6.         | Simplified schematic of the current mirrors of the PACTA chip. HG mirror                                                                                 |                 |

|              | incorporates a saturation control circuit                                                                                                                | 15              |

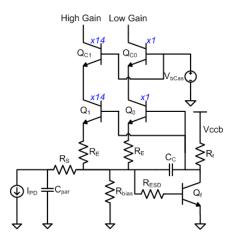

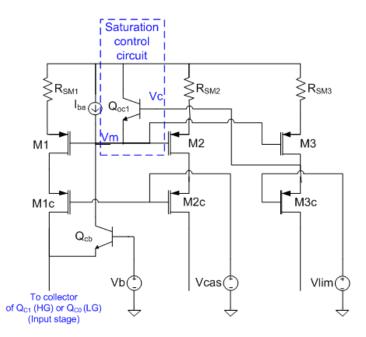

| 2.7.         | Simplified schematic of the fully differential operational amplifier of the PACTA                                                                        |                 |

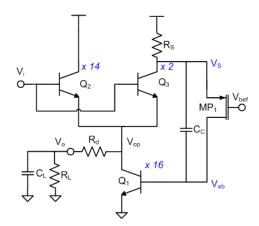

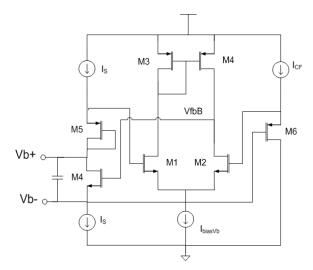

|              | chip                                                                                                                                                     | 16              |

| 2.8.         | Simplified schematic of the class AB output stage of the PACTA chip.                                                                                     | 17              |

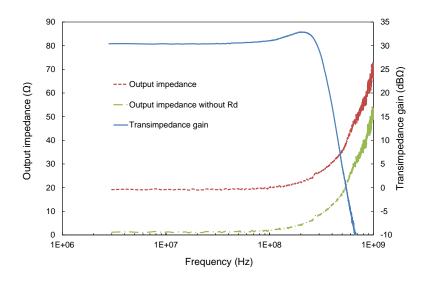

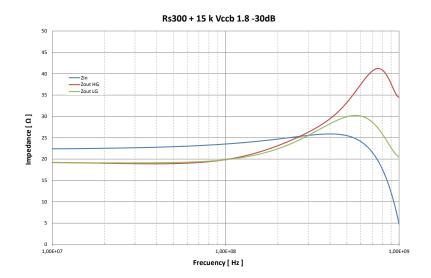

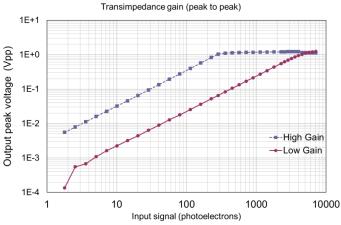

| 2.9.         | PACTAv1.4 Measurement results of the TIA output impedance and tran-                                                                                      |                 |

|              | simple gain for $V_{CC} = 3.3V$ , $R_L = 50\Omega$ , $C_L = 10pF$ , $R_d = 18\Omega$ .                                                                   | 17              |

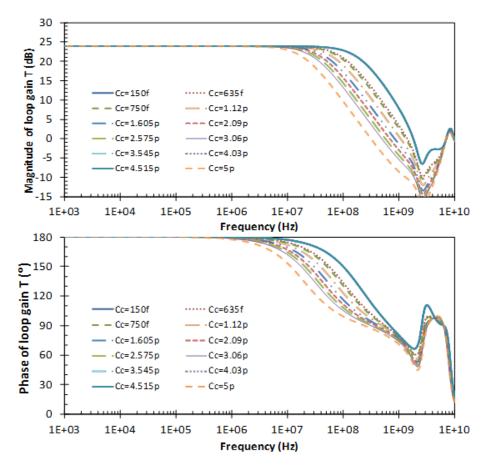

| 2.10.        | Loop gain $T(f)$ for different $C_C$ : magnitude (top) and phase (bootom).                                                                               |                 |

|              | Inductance of the bonding wires is considered                                                                                                            | 19              |

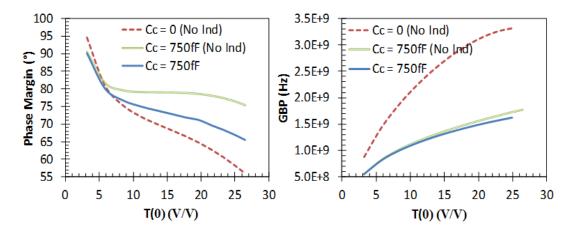

| 2.11.        | Loop gain T(f) phase margin (left) and GBP (right) as function of loop gain,                                                                             |                 |

|              | with an without $C_C$ . The effect of the inductance of the bonding wires is studied for $C_C = 750 fF$                                                  | 20              |

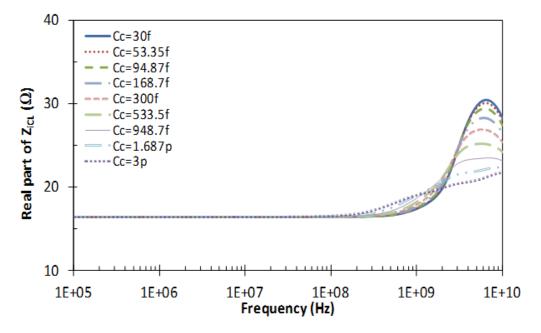

| 9 1 9        | Magnitude of the input impedance for different $C_C$ .                                                                                                   | 20<br>21        |

|              | Magnitude of the input impedance for different loop gain.                                                                                                | 21<br>21        |

|              | Series and parallel noise. Spectre simulation.                                                                                                           | $\frac{21}{22}$ |

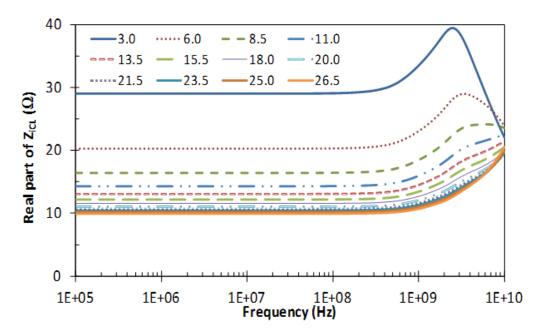

|              | Simulation of the ENI as function of detector capacitance (Cd)                                                                                           | $\frac{22}{23}$ |

|              | Reduced block diagram of the PACTA chip                                                                                                                  | 23<br>24        |

|              |                                                                                                                                                          |                 |

| 2.1(.        | Functional block diagram of the PACTA chip for the differential configuration                                                                            | $\mathbf{Z4}$   |

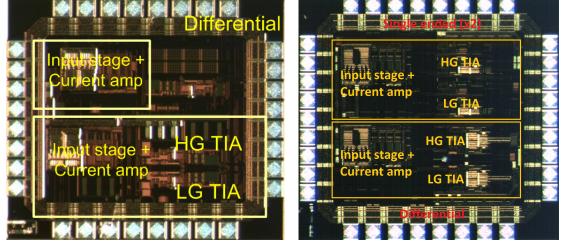

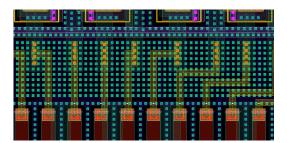

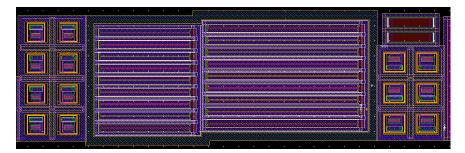

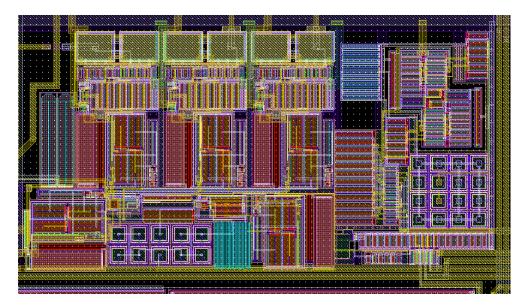

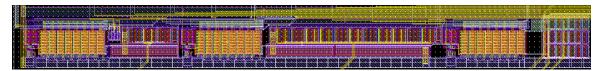

| 2.18.    | Micro photography of the different PACTA ASIC prototypes developed:<br>PACTAv1.1, PACTAv1.2, PACTAv1.2b and PACTAv1.4. | 26       |

|----------|------------------------------------------------------------------------------------------------------------------------|----------|

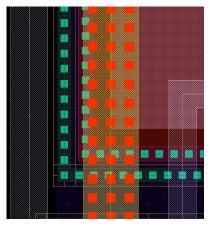

| 9 10     | Design For Manufacturing (DFM) guideline application layout examples.                                                  | 20<br>27 |

|          | Diode layout to solve the antenna violations.                                                                          | 21       |

|          | Common centroid application technique.                                                                                 | 28<br>28 |

|          | Guard ring sample layout of an array of PMOS transistors isolated from the                                             | 20       |

| 2.22.    | N-substrate                                                                                                            | 29       |

| <u> </u> | PMOS transistors array sample layout with dummy devices located at the                                                 | 29       |

| 2.20.    |                                                                                                                        | 29       |

| 0.04     | top and bottom of the structure                                                                                        | 29       |

| 2.24.    | Sample layout of two different resistor types in common centroid configuration                                         | 20       |

| 0.05     | but in separated structures for each resistor type                                                                     | 29<br>20 |

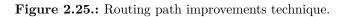

|          | Routing path improvements technique.                                                                                   | 30       |

| 2.20.    | BiasCurrents layout that generates all the required currents with the temper-                                          | 01       |

| 0.07     | ature compensated current reference circuit al the right                                                               | 31       |

| 2.2(.    | BiasIntV layout that generates all the required bias voltages for the PACTA                                            | 01       |

| 0.00     | preamplifier                                                                                                           | 31       |

| 2.28.    | OPdifAB layout block that corresponds to the low impedance output buffer                                               | 01       |

| 0.00     | for the PACTA preamplifier                                                                                             | 31       |

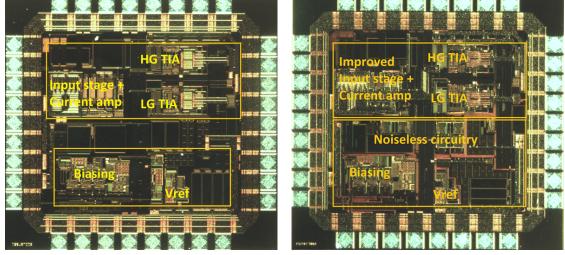

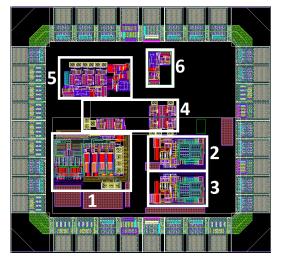

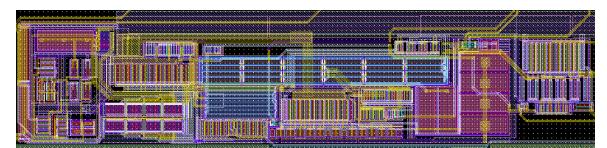

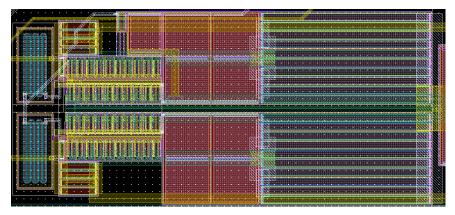

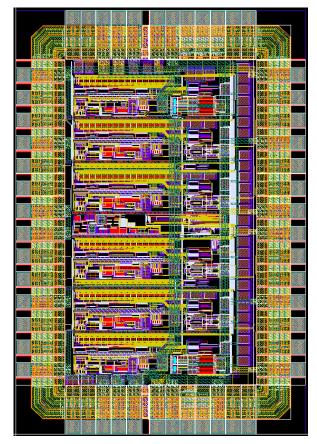

| 2.29.    | PACTAv1.4 Layout design on the left and the floor-planning of the different                                            | 20       |

| 0.00     | blocs at the right.                                                                                                    | 32       |

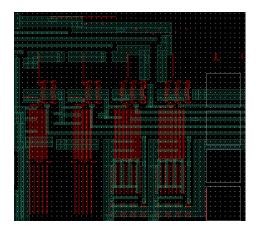

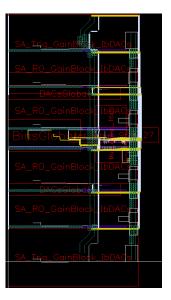

|          | Floor-planning of the gain stage of the PACTAv1.4 ASIC design.                                                         | 32       |

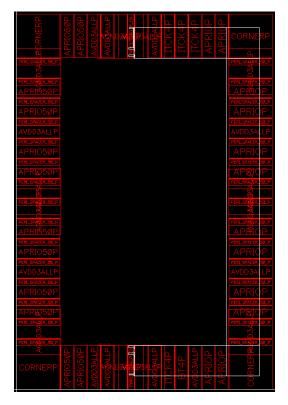

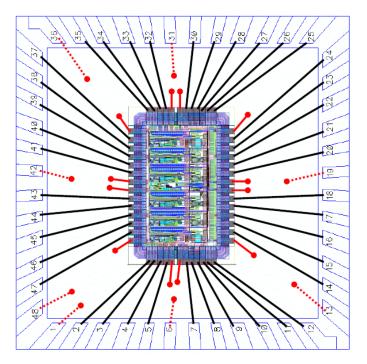

|          | Pad ring floor-planning of the PACTAv1.4 ASIC design.                                                                  | 33       |

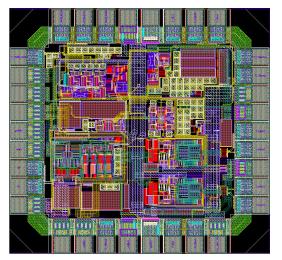

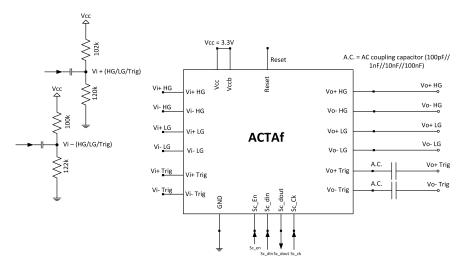

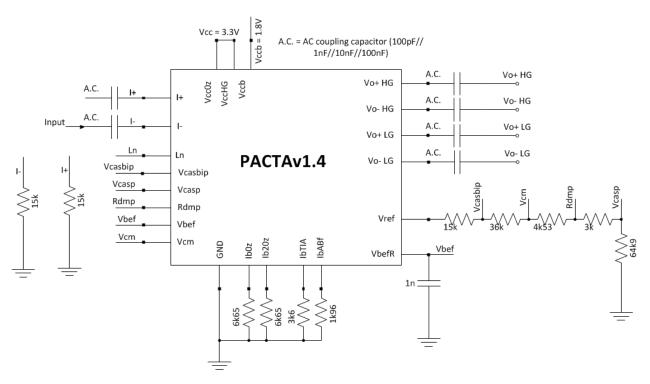

|          | PACTAv1.4 Typical application circuit.                                                                                 | 34       |

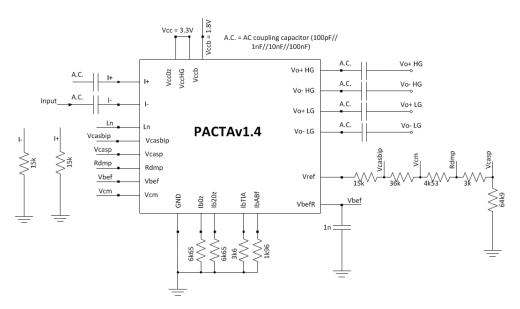

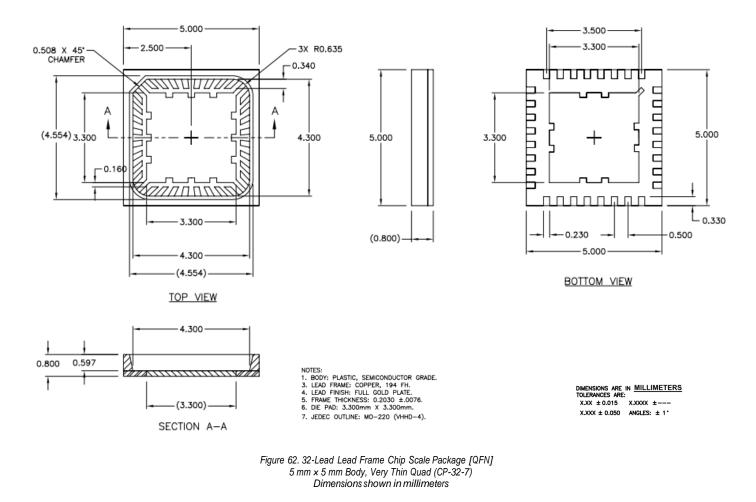

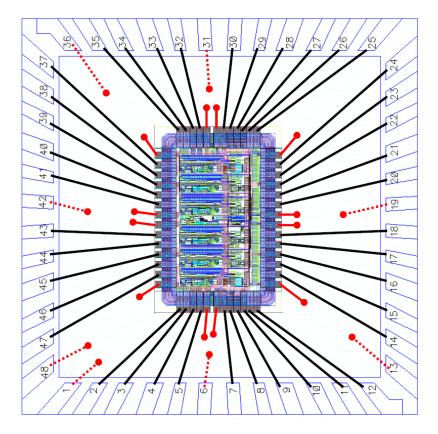

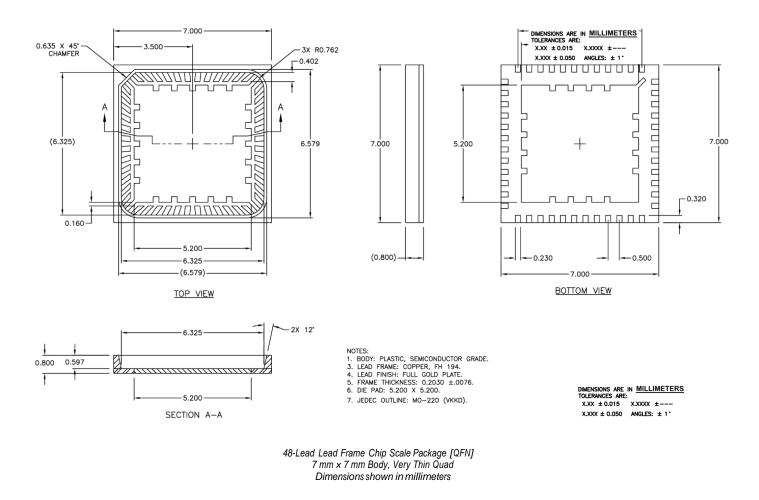

|          | PACTAv1.4 Package details.                                                                                             | 35       |

| 2.34.    | PACTAv1.4 Bonding Diagram with the DIE ground pads connected to the                                                    | 05       |

| 0.05     | central package pad.                                                                                                   | 35       |

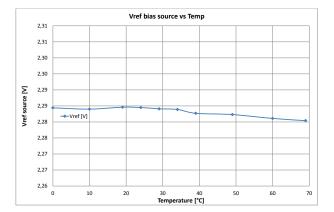

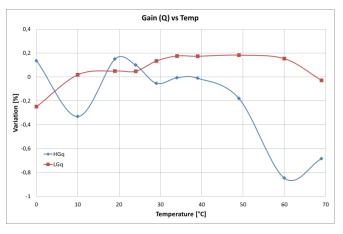

| 2.35.    | PACTAv1.4 $V_{ref}$ bias voltage source reference vs Temperature variation with                                        | 20       |

| 0.00     | $15k\Omega$ at $R_{in}$ and Ln On                                                                                      | 36       |

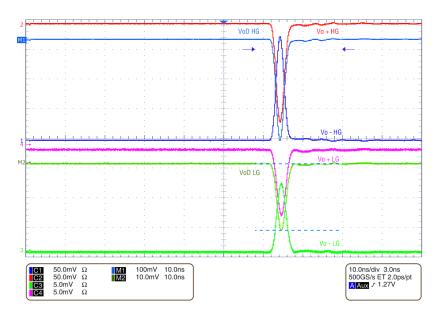

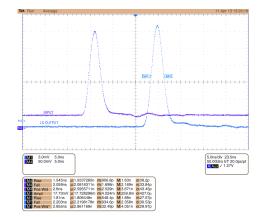

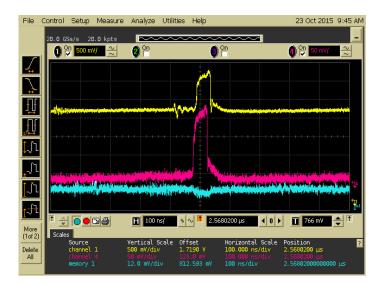

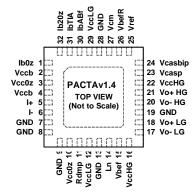

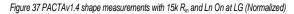

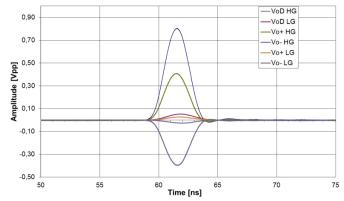

| 2.36.    | PACTAv1.4 shape measurements with a negative pulse at the I $-$ input. VoD                                             |          |

| 0.07     | is obtained by $(Vo+) - (Vo-)$ .                                                                                       | 38       |

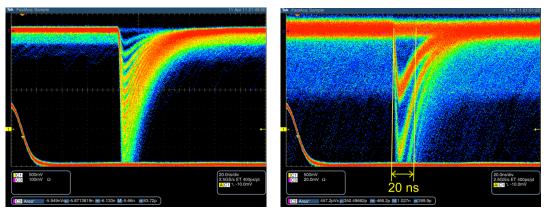

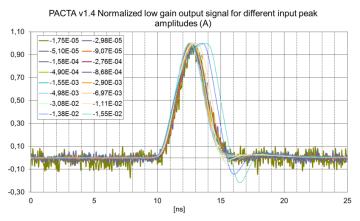

| 2.37.    | PACTAv1.4 shape measurements with a negative pulse at the I- input. $V_O D$                                            |          |

|          | is obtained by $(Vo-) - (Vo+)$ . Input signal is depicted inverted in order to                                         | 20       |

| 0.00     | maintain the picture polarity                                                                                          | 39       |

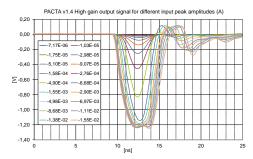

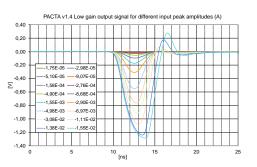

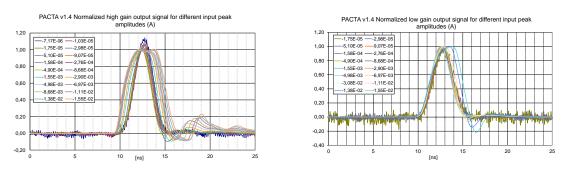

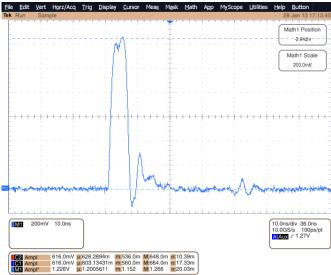

| 2.38.    | PACTAv1.4 Differential output for different input pulse amplitudes with                                                |          |

|          | typical SPE pulse with $15k\Omega R_{in}$ and Ln On: HG (top left) and LG (top                                         | 20       |

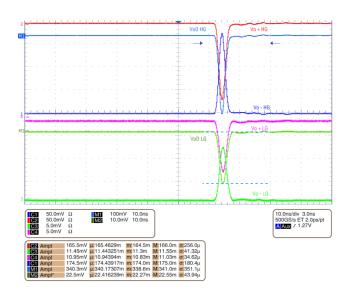

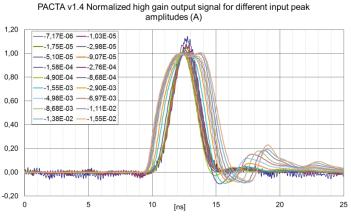

| 0.00     | right). Normalized shape is shown for both at the bottom                                                               | 39       |

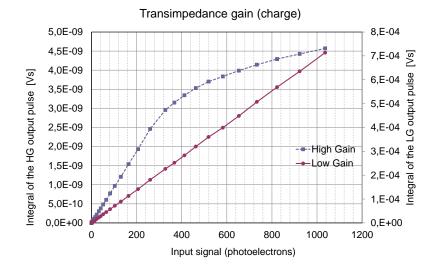

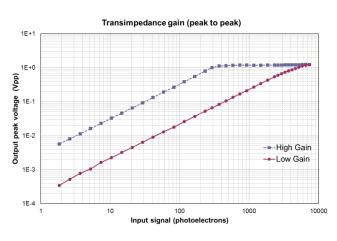

| 2.39.    | Integral of the HG and LG differential outputs as function of input peak                                               | 10       |

| 0.40     | current for typical SPE pulse shape: linear and logarithmic scale                                                      | 40       |

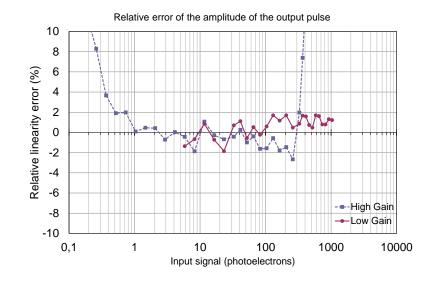

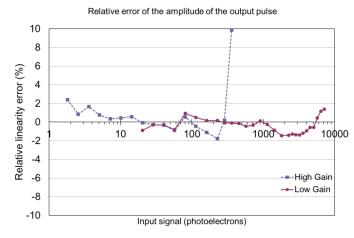

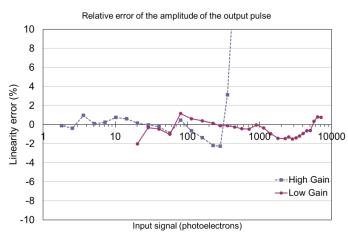

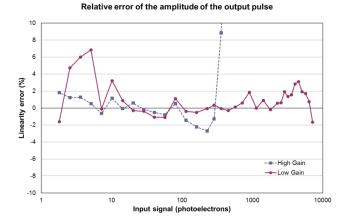

| 2.40.    | HG and LG linearity error for charge measurement versus input peak current                                             | 4.1      |

| 0.41     | (typ. SPE pulse)                                                                                                       | 41       |

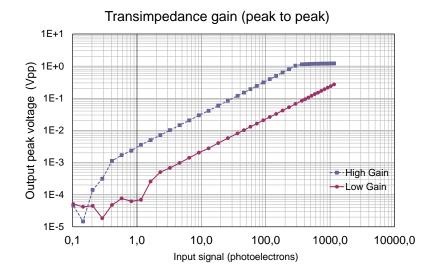

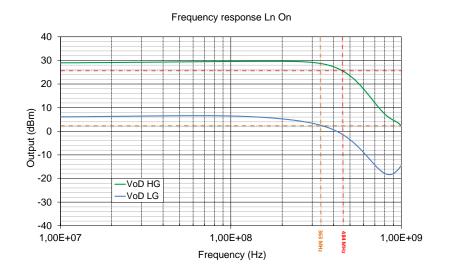

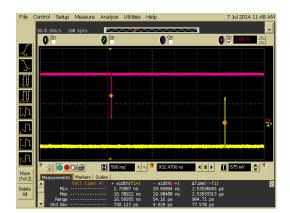

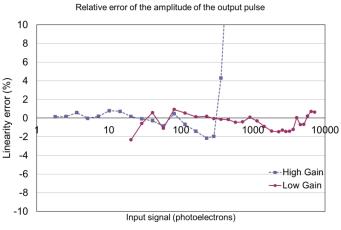

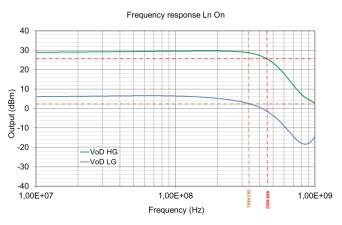

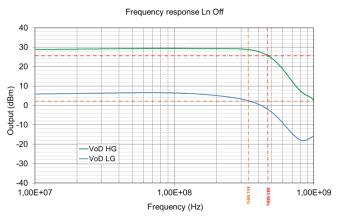

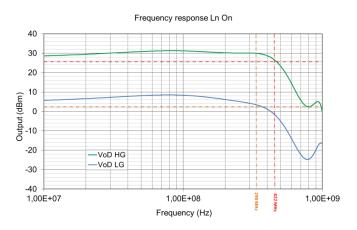

|          | PACTAV1.4 frequency response test with $R_{in}10k\Omega$ and Ln On                                                     | 42       |

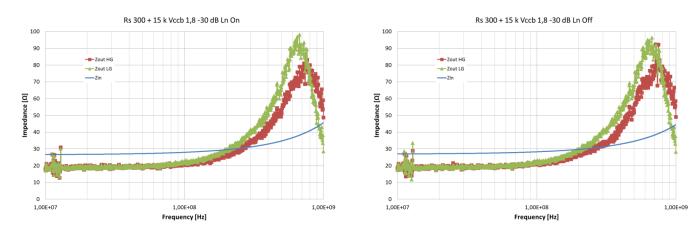

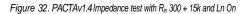

|          | PACTAv1.4 Impedance test with $R_{in}$ 300 and $15k\Omega$ and Ln On                                                   | 42       |

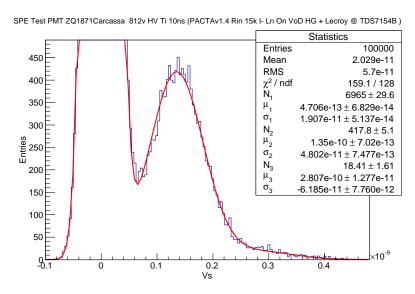

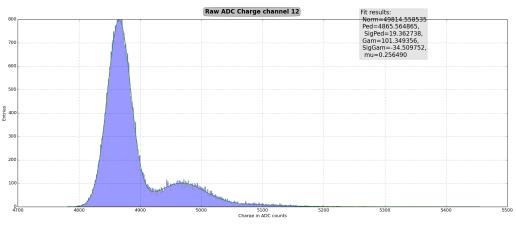

| 2.43.    | SPE spectrum with PMT at nominal gain (40K) by using PACTA with a                                                      |          |

|          | DPO scope (for 10 ns integration time) and NECTAR front end electronics                                                | 10       |

| 0.4.4    | (for 16 ns integration time)                                                                                           | 43       |

| 2.44.    | ENC vs integration time, for calculations at different measurement conditions.                                         | 44       |

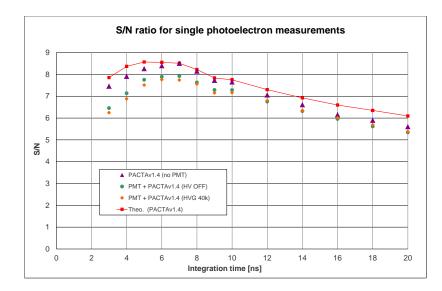

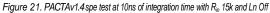

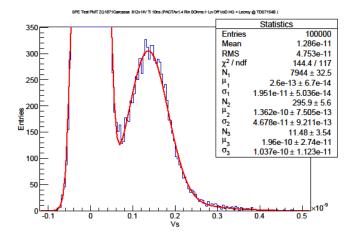

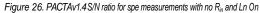

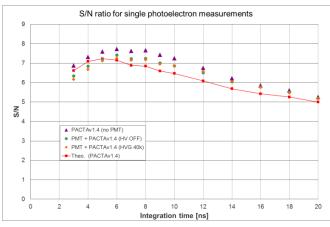

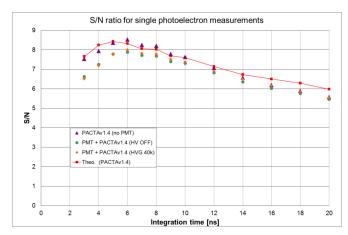

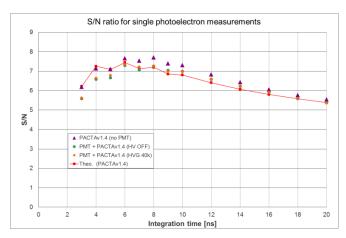

| 2       | .45.       | PSCTAv1.4 S/N ratio for SPE measurements with $R_{in}15k\Omega$ and Ln On                                                            | 45       |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|

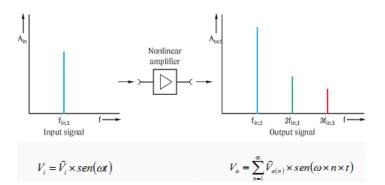

| 2       | .46.       | Total Harmonic Distorsion (THD) definition for a Nonlinear amplifier [40]                                                            | 45       |

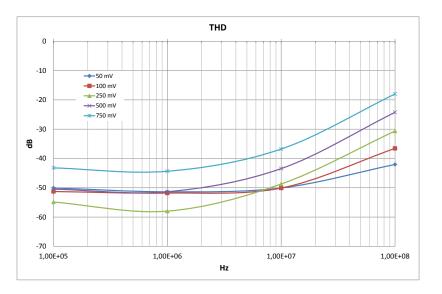

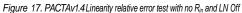

| 2       | .47.       | PACTAv1.4 Total Harmonic Distorsion (THD) test with $R_{in}$ 3k3 at different                                                        |          |

|         |            | output signal amplitudes.                                                                                                            | 46       |

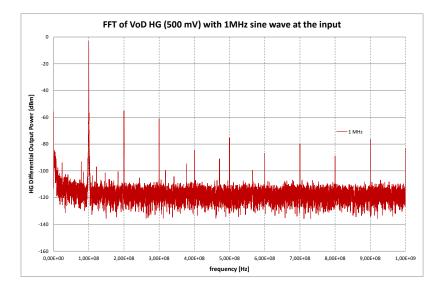

| 2       | .48.       | PACTAv1.4 Frequency domain response of the differential output signal (HG)                                                           |          |

|         |            | with a 500mV amplitude for a 1MHz input signal with $R_{in}$ 3k3                                                                     | 46       |

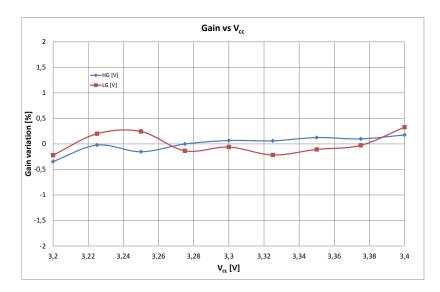

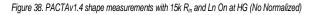

| 2       | .49.       | PACTAv1.4 Gain variation as a function of Power supply ( $V_{CC}$ with 15k $R_{in}$                                                  |          |

|         |            | and $L_n$ On at HG                                                                                                                   | 47       |

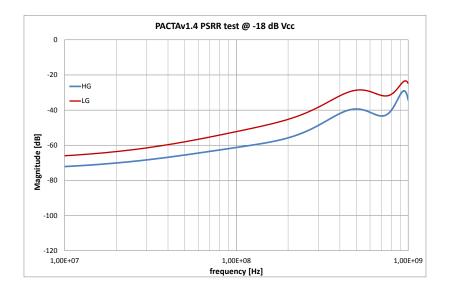

| 2       | .50.       | PACTAv1.4 PACTAv1.4 PSRR measurements with 15k $R_{in}$ and $L_n$ On at Vcc of -18 dB                                                | 48       |

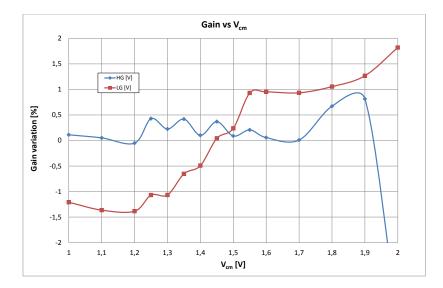

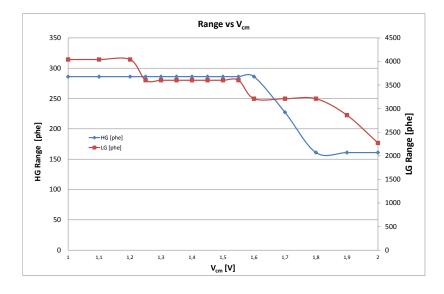

| 2       | 51         | PACTAv1.4 Common Mode variation vs Gain with 15k $R_{in}$ and $L_n$ On at HG.                                                        | 48       |

|         |            |                                                                                                                                      | 49       |

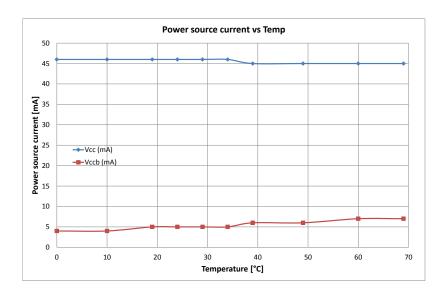

|         |            | PACTAV1.4 Power source current required as a function of the ambient                                                                 | ч5       |

| 2.      | .00.       | temperature.                                                                                                                         | 49       |

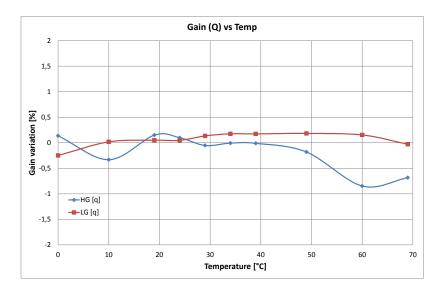

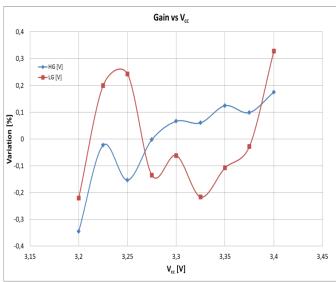

| 2       | 54         | PACTAv1.4 Charge Gain variation as a function of the ambient temperature.                                                            | 50       |

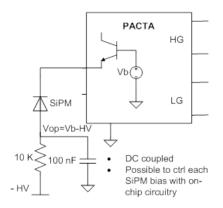

|         |            | Schematic diagram to use the PACTA pre-amplifier with SiPM sensors                                                                   | 51       |

|         |            | SPE spectrum with SiPM by using PACTA with a fast acquisition option of a                                                            | 01       |

|         | .00.       | DPO scope                                                                                                                            | 51       |

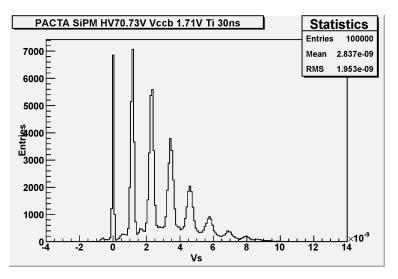

| 2       | .57.       | SPE charge spectrum of the PACTA output with a SiPM input signal                                                                     | 52       |

|         |            | Bi-Gain PACTA output signal with SiPM signal input.                                                                                  | 52       |

|         |            | Scheme of the HESS array trigger [44]                                                                                                | 53       |

|         |            | Emitter part of an SFP, transceiver, AC coupled                                                                                      | 54       |

|         |            | Emitter part of an SFP, transceiver, AC coupled                                                                                      | 55       |

|         |            | Two optical fibers of 2 and 500 m length by using the PACTA pre-amplifier                                                            | 00       |

|         |            | at the receiver link stage.                                                                                                          | 55       |

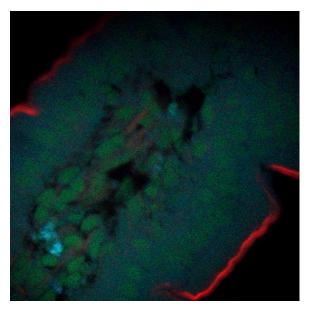

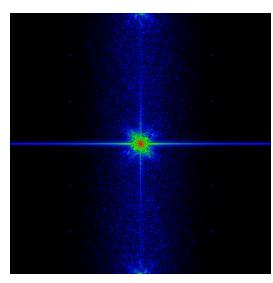

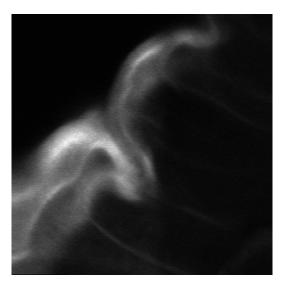

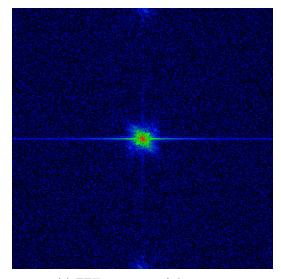

| 2       | .63.       | Mouse intestine section image $(100\mu m \times 100\mu m \text{ observation area})$ with Alexia                                      |          |

|         |            | Fluor 350 WGA, Alexa Fluor 568 phalloidin SYTOX Green observed with a                                                                |          |

|         |            | confocal LSM with pulses of 150 fs FWHM <sup>i</sup> at 76MHz in a Ti-sapphire laser                                                 |          |

|         |            | at 810 nm wavelength of about 30 mW of average light power                                                                           | 56       |

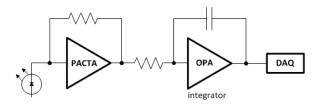

| 2       | .64.       | Simplified block diagram of the schematic used to send the data coming form                                                          |          |

|         |            | the PMT of the confocal LSM to the DAQ by using the PACTA pre-amplifier.                                                             | 57       |

| 2       | .65.       | Images analysis comparison with a commercial pre-amplifier (Hamamatsu                                                                |          |

|         |            | C-7319) and PACTA                                                                                                                    | 58       |

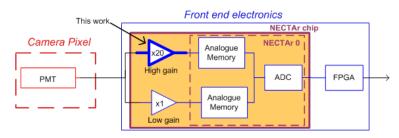

| 9       | 1          | Plack diagram of the front and electronics proposed by NECTA, project                                                                | 61       |

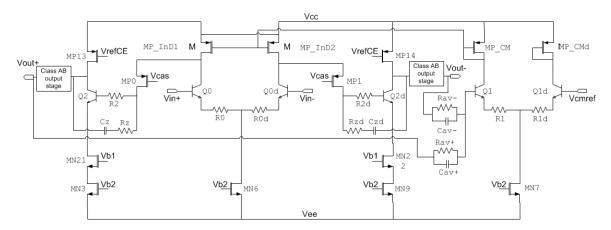

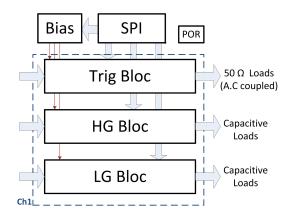

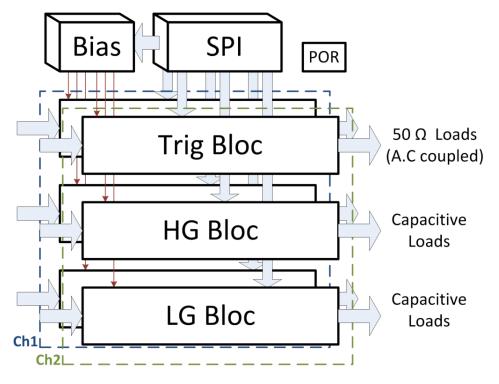

|         | .1.<br>2   | Block diagram of the front end electronics proposed by NECTAr project<br>Block diagram of the proposed amplifier                     | 61<br>62 |

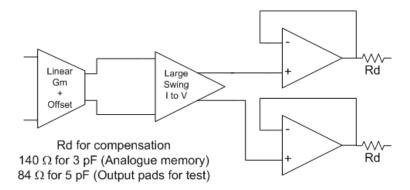

|         | .2.        |                                                                                                                                      | 63       |

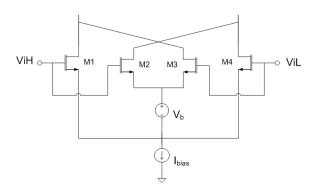

|         | .3.        | Cross coupled transistor pairs with bias offset                                                                                      | 03<br>63 |

|         | .4.<br>E   | Floating voltage source $V_b$                                                                                                        |          |

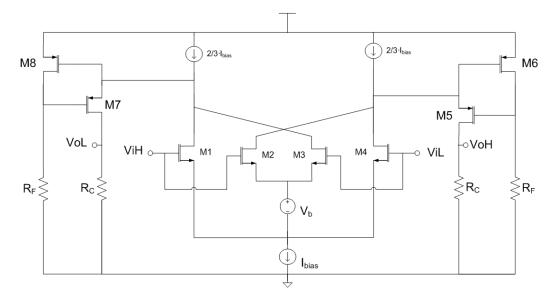

|         | .5.<br>6   | Simplified schematic of the amplifier, without output buffers                                                                        | 65<br>66 |

|         | .6.        | Output buffer scheme.                                                                                                                | 66       |

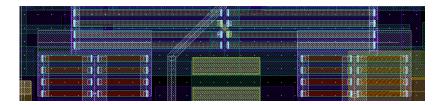

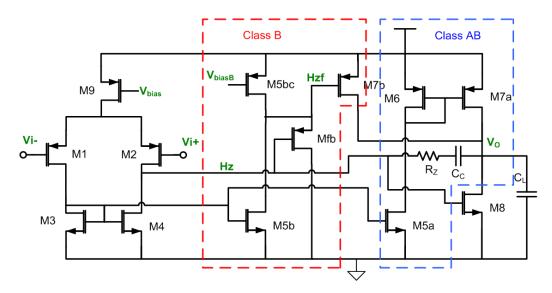

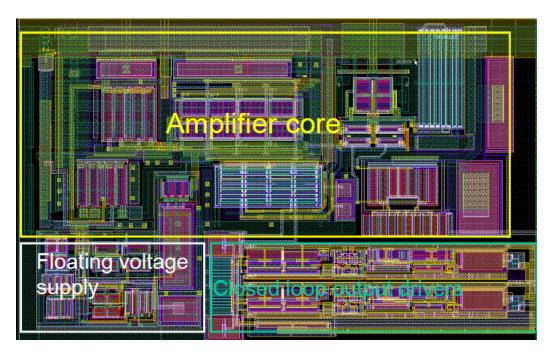

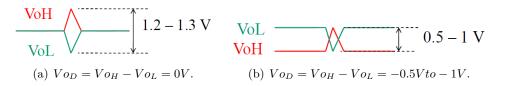

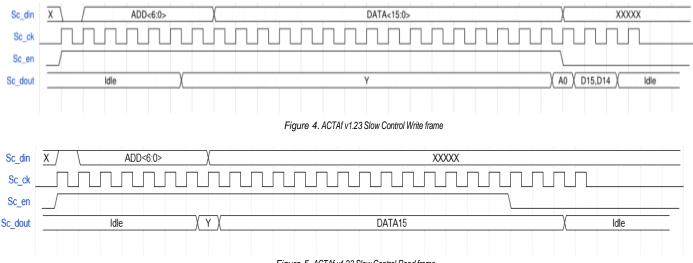

|         | .7.<br>.8. | Full path block diagram of the NECTAr camera proposal Layout of the clossed-loop buffer for the digitizer ASIC of the NECTAr camera. | 67       |

|         |            | NECTAr0 chip with the dedicated input buffers with a new high slew-rate                                                              | 07       |

| ე.<br>ე | .9.        | power efficient class AB structure.                                                                                                  | 68       |

| 3       | 10         | Analogue memory DC input voltage levels of the digitizer ASIC.                                                                       |          |

| 0       |            | THOUSE HOMOLY DO HEPRI VOIDAGE INVESTIGATION HEREINDE HEREIN,                                                                        | 00       |

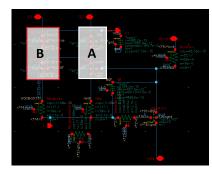

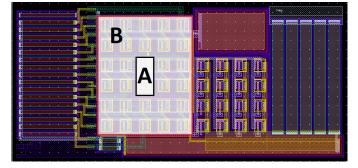

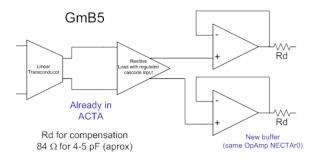

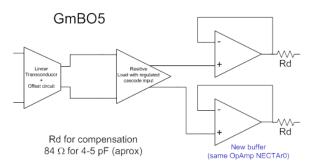

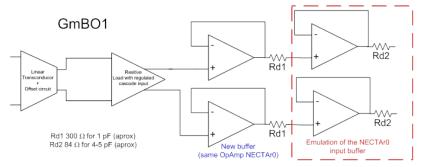

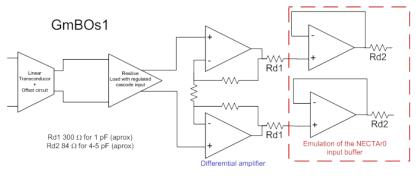

|       | Block diagram differences of the different ACTA ASIC configuration developed:<br>B5, BO5, BO1 and BOs1.                     | 70       |

|-------|-----------------------------------------------------------------------------------------------------------------------------|----------|

|       | Functional block diagram of the ACTAf 1Ch chip with the three amplification                                                 |          |

|       | stages and the slow control by using a dedicated SPI interface.                                                             | 71       |

| 3.13. | Functional block diagram of the ACTAf 2Ch chip with the three amplification                                                 |          |

|       | stages at each channel branch and the shared slow control by using a dedicated                                              |          |

|       | SPI interface                                                                                                               | 71       |

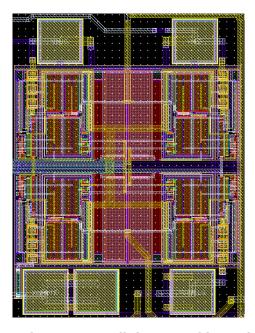

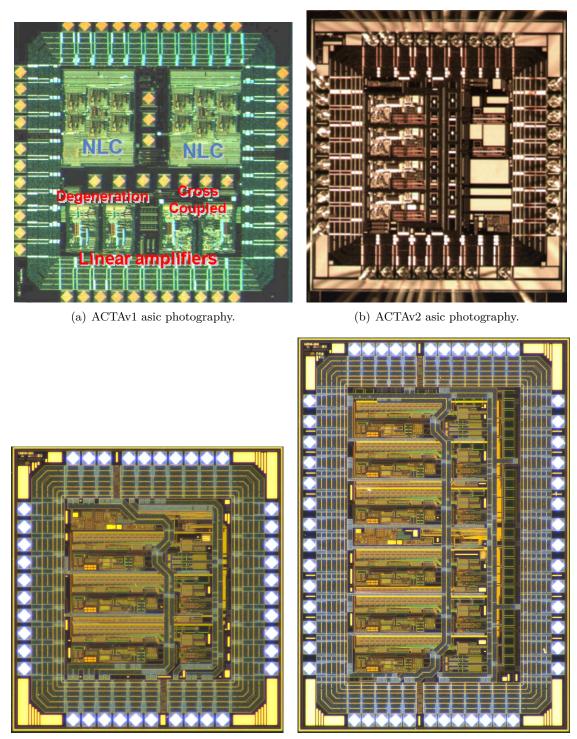

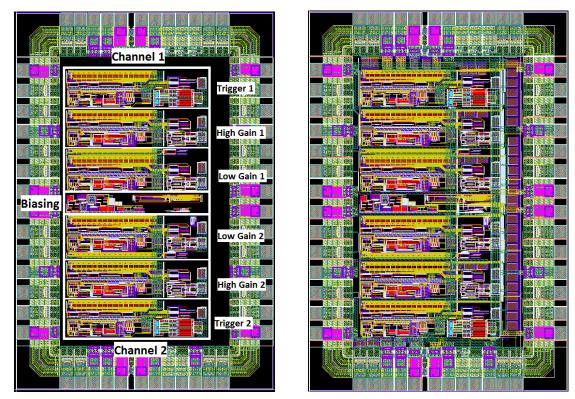

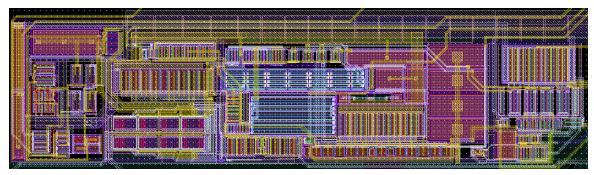

| 3.14. | Micro photography of the different ACTA ASIC prototypes developed: AC-                                                      |          |

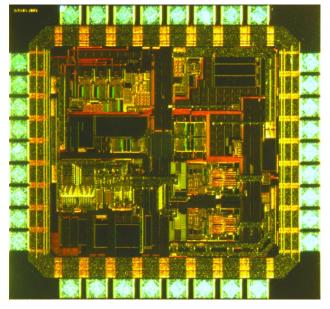

|       | TAv1, ACTAv2, ACTAf 1Ch and ACTAf 2Ch                                                                                       | 72       |

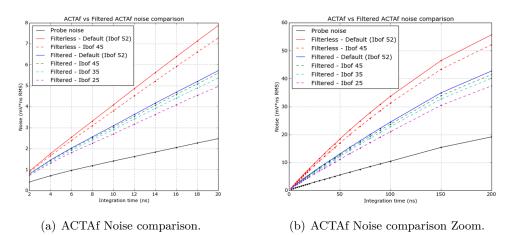

| 3.15. | ACTAf Noise comparision with different charge integration time                                                              | 73       |

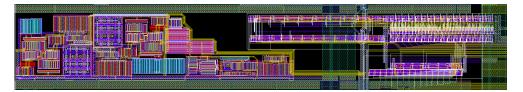

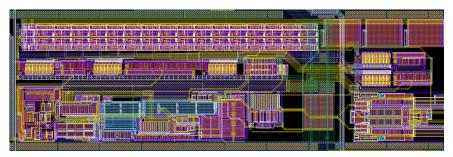

| 3.16. | Bias Circuits layout that generates all the required currents                                                               | 74       |

| 3.17. | Floor-planning of the gain branches and the biasing circuits for the ACTA                                                   |          |

|       | amplifier                                                                                                                   | 74       |

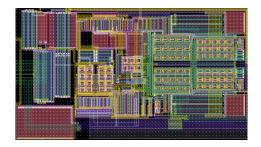

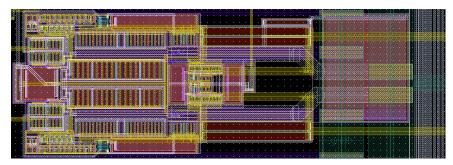

| 3.18. | ACTAf 2Ch Layout design on the left and the floor-planning of the different                                                 |          |

|       | blocs at the right                                                                                                          | 75       |

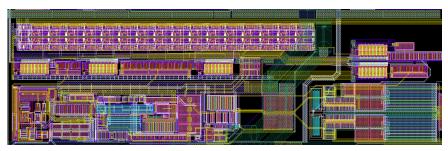

| 3.19. | ACTAf 2Ch Layout design on the two different kind of gain branches                                                          | 76       |

| 3.20. | Digital to Analog Converters local biasing blocks of the ACTAf 2Ch ASIC                                                     |          |

|       | design                                                                                                                      | 76       |

| 3.21. | ACTAf 2Ch Layout design on the two different kind of gain branches with a                                                   |          |

|       | detailed view at the input stage part                                                                                       | 76       |

| 3.22. | ACTAf 2Ch Output buffer layout design on the two different kind of gain                                                     |          |

|       | branches                                                                                                                    | 77       |

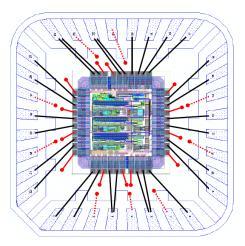

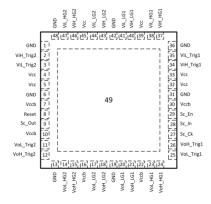

| 3.23. | Pad ring floor-planning of the ACTAf 2Ch ASIC design                                                                        | 77       |

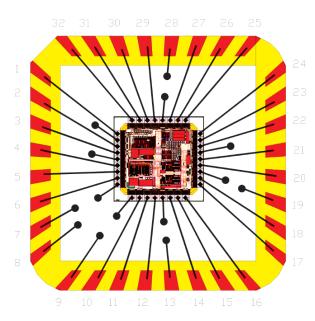

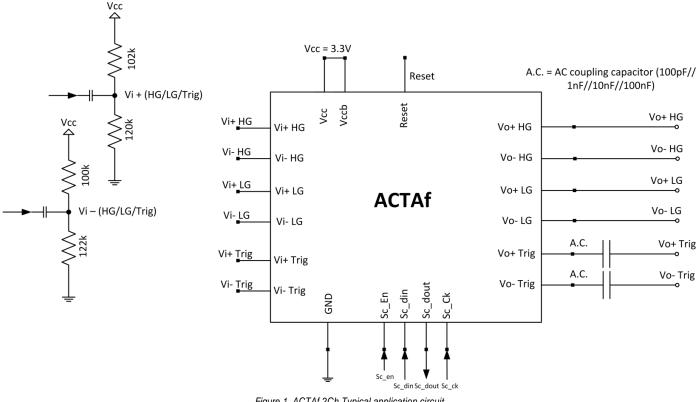

| 3.24. | ACTAf Typical application circuit.                                                                                          | 78       |

|       | ACTAf Bonding Diagram with the DIE ground pads connected to the central                                                     |          |

|       | package pad.                                                                                                                | 79       |

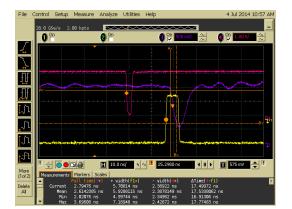

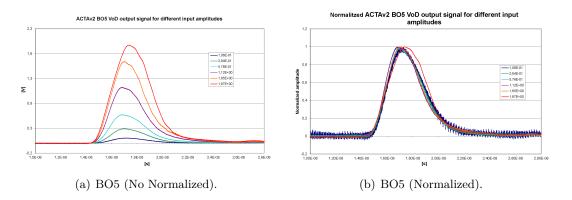

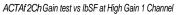

|       | ACTAv2 BO5 Differential output for different input pulse amplitudes with                                                    |          |

|       | typical focal plane instrumentation signals (top). Normalized shape is shown                                                |          |

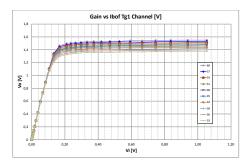

|       | at the bottom                                                                                                               | 80       |

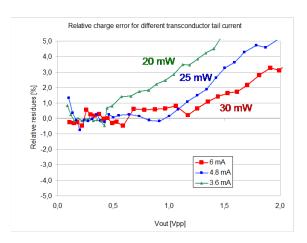

|       | Relative linearity (INL) error for different values of the transconductor tail                                              |          |

|       |                                                                                                                             | 80       |

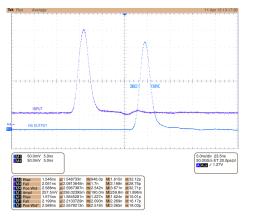

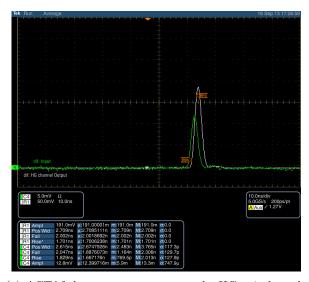

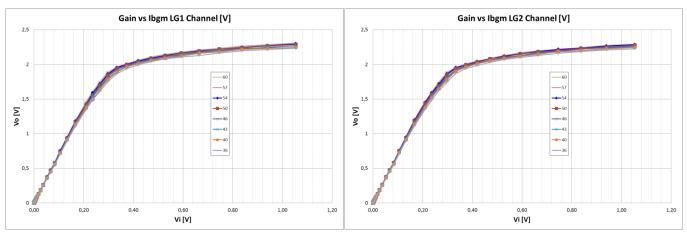

|       | ACTAf shape measurements with an input pulse in the linear region at the                                                    | ~ .      |

|       | different gain branches.                                                                                                    | 81       |

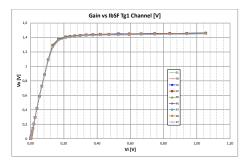

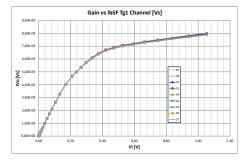

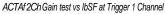

|       | ACTAf measurement results of the integral for the HG, LG and Tg differential                                                |          |

|       | outputs as function of input peak current for typical SPE pulse shape and                                                   | 00       |

|       | the linearity error. Detailed view of the HG and Tg linear range                                                            | 82       |

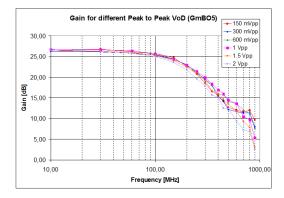

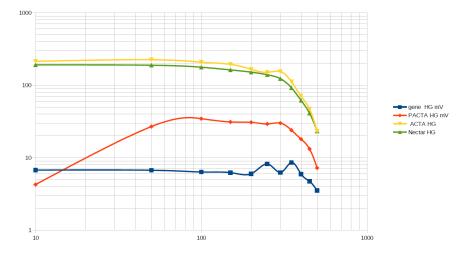

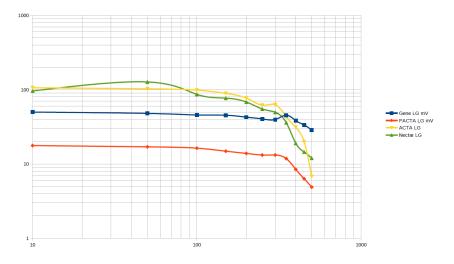

|       | Frequency response of the amplifier for different output levels with different                                              | 0.0      |

|       | amplifier configurations.                                                                                                   | 83       |

|       | Amplitude in mV of the injected sine wave as a function of its frequency, for                                               | 0.4      |

|       | high gain (top) and low gain (bottom)                                                                                       | 84       |

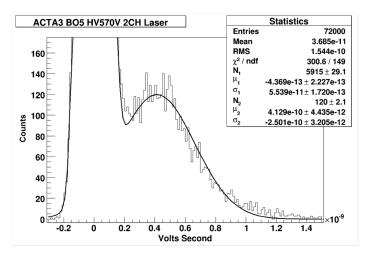

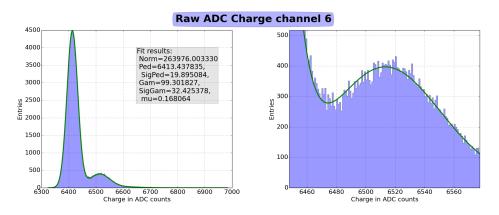

|       | Single photoelectron spectra at the nominal PMT gain (integration time is 10                                                | 05       |

|       | ns)                                                                                                                         | 85<br>85 |

|       | Typical s.p.e. spectrum fitted with a function including 0 to 9 s.p.e contributions                                         | 85       |

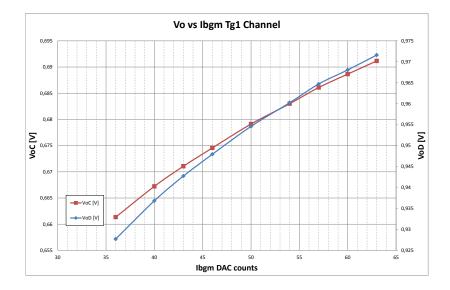

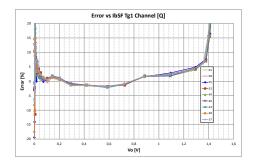

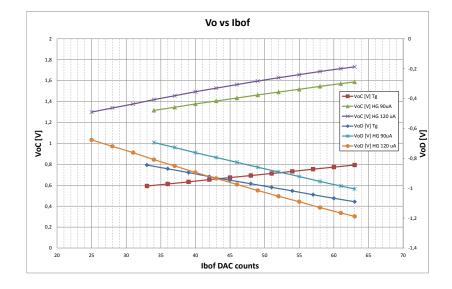

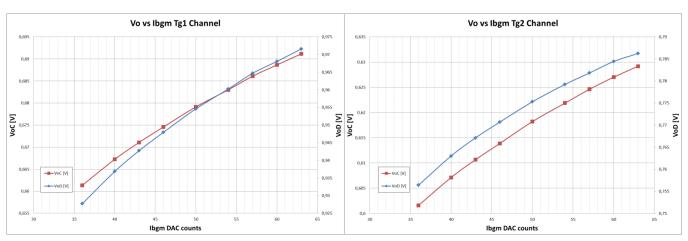

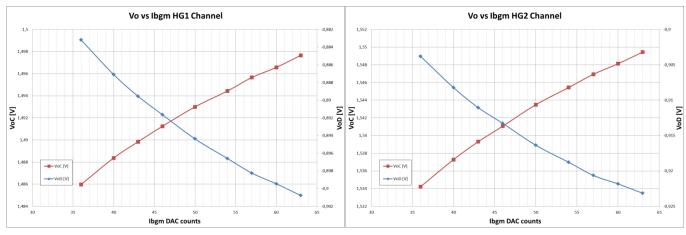

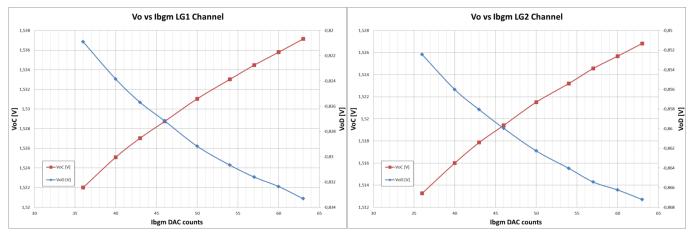

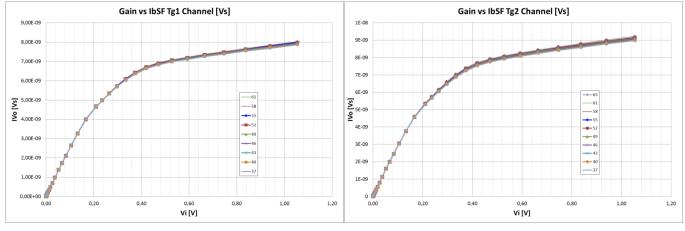

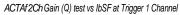

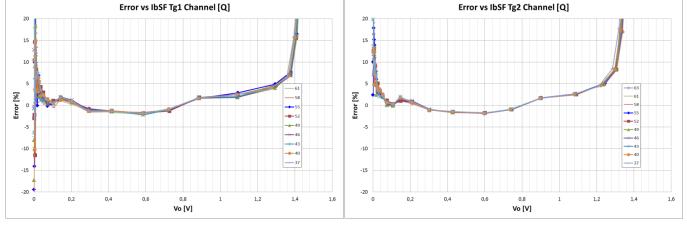

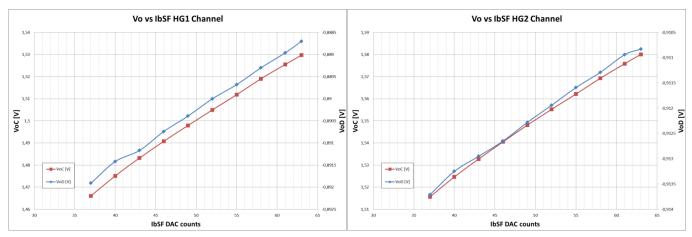

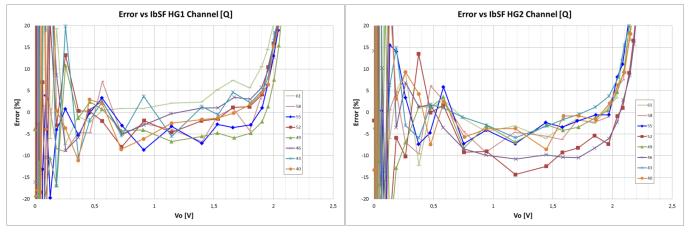

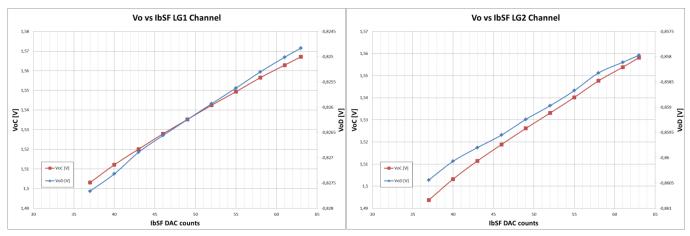

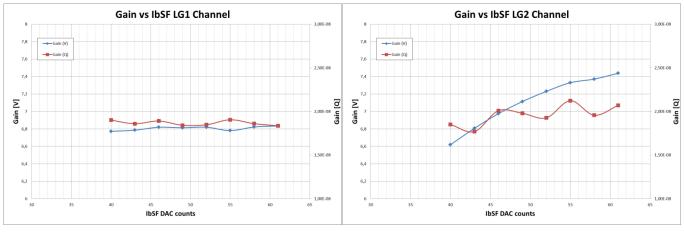

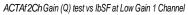

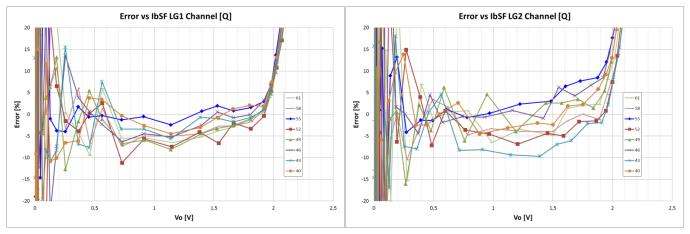

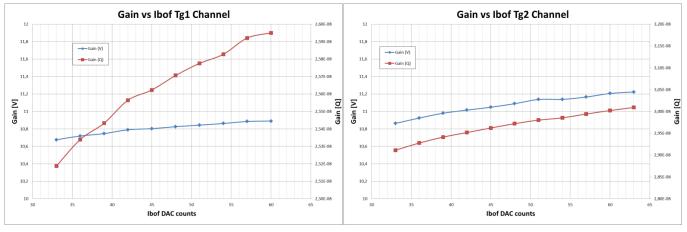

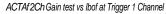

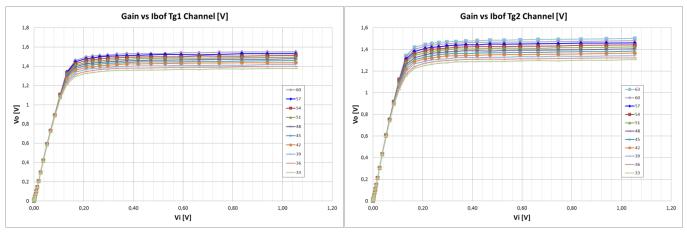

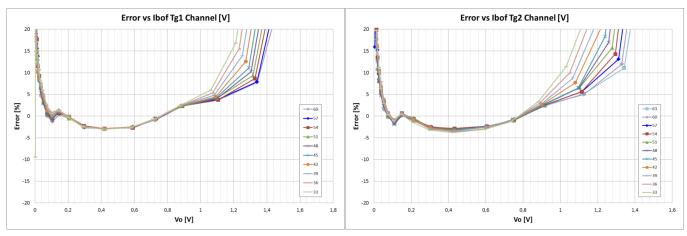

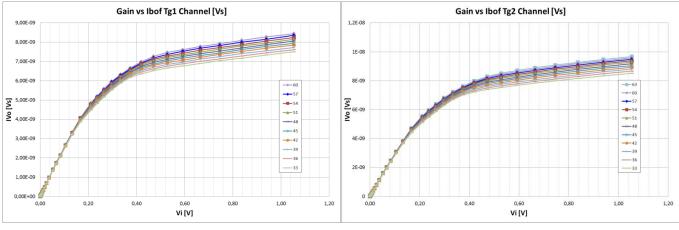

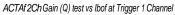

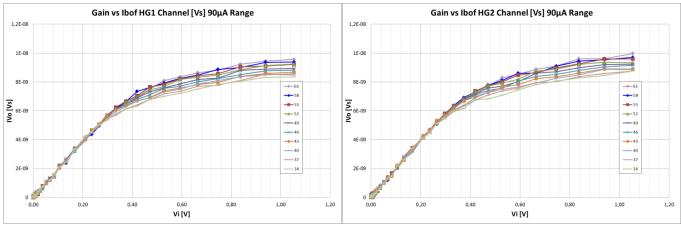

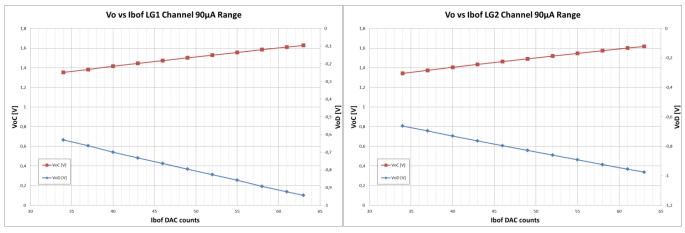

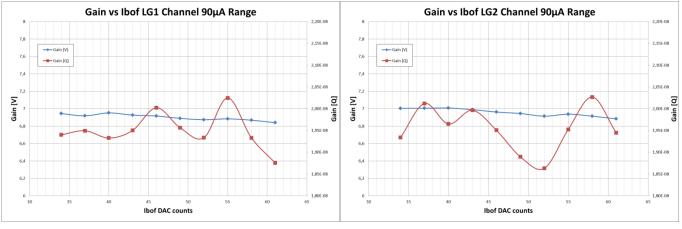

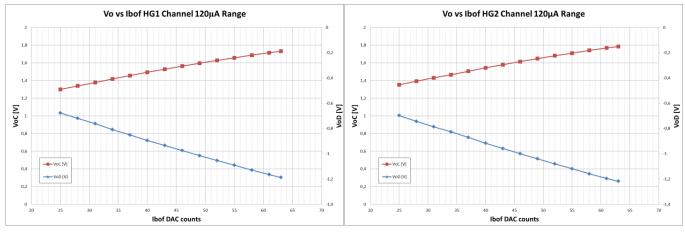

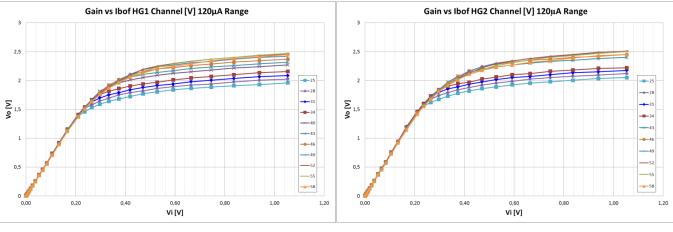

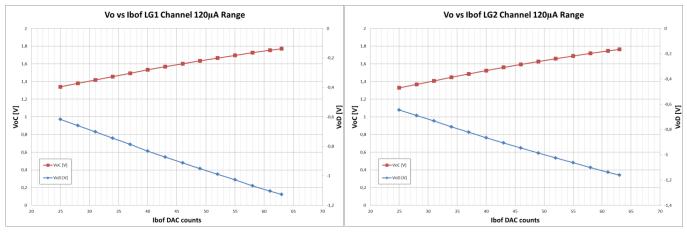

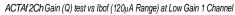

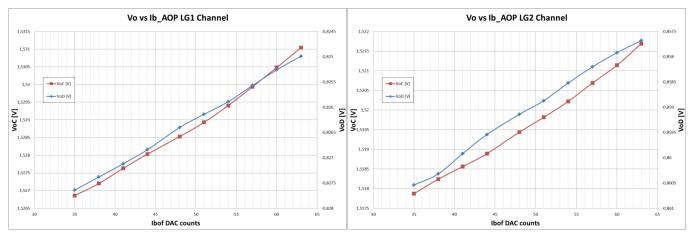

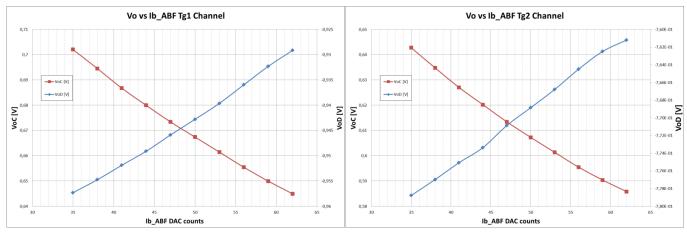

|       | ACTAf 2Ch output voltages in common mode and differential mode variations $a_{i}$ a function of the $L$ bias summer sources | 07       |

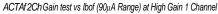

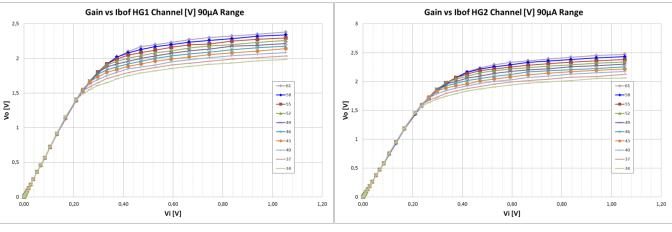

|       | as a function of the $I_{bgm}$ bias current source. $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                      | ðí       |

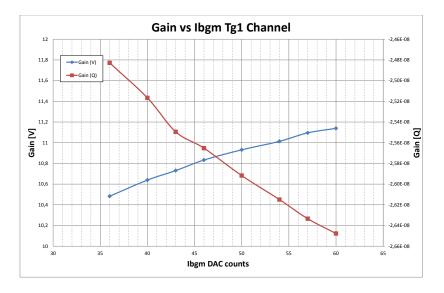

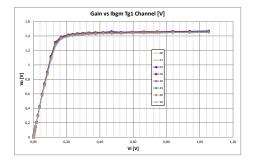

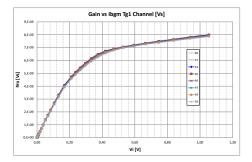

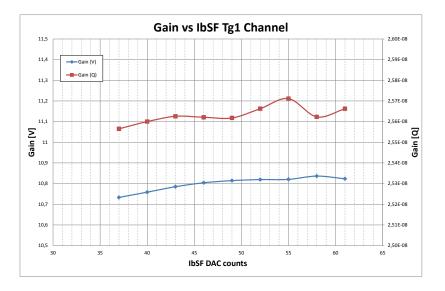

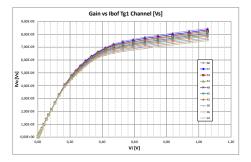

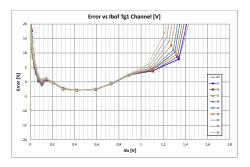

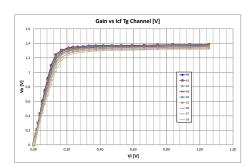

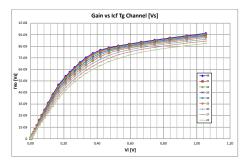

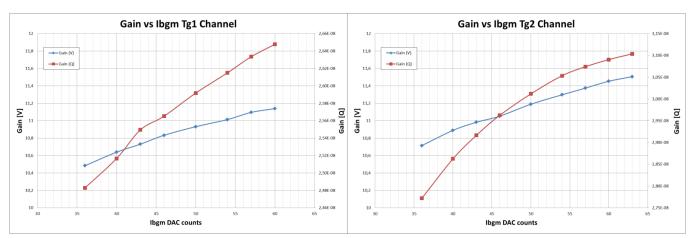

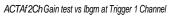

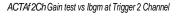

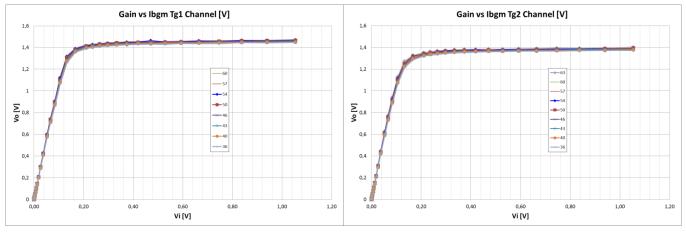

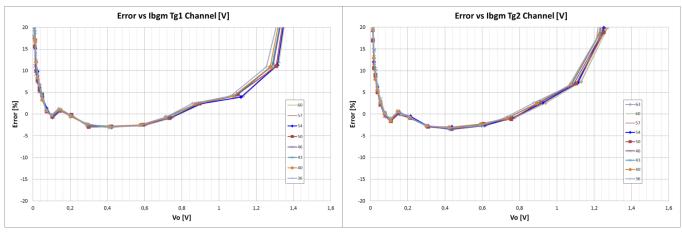

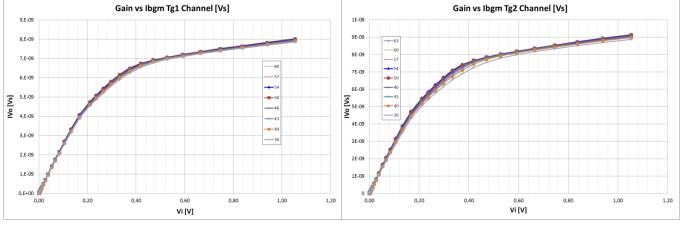

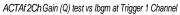

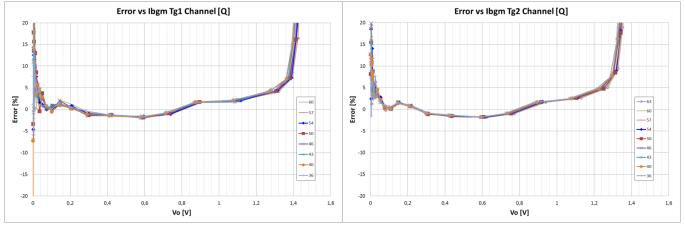

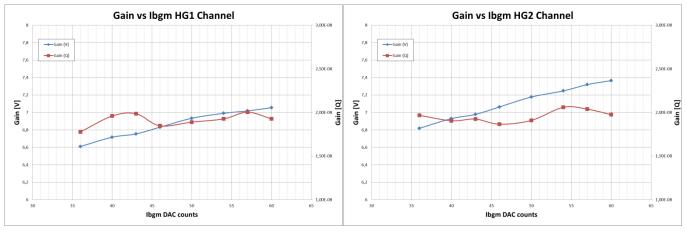

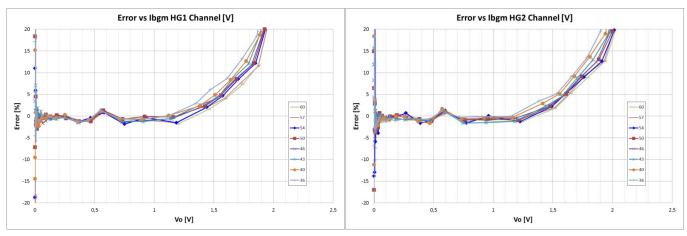

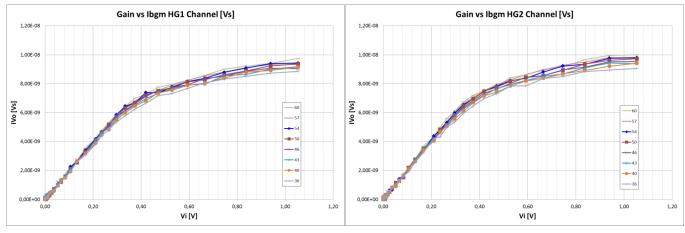

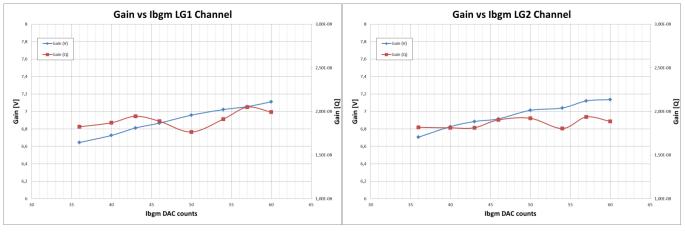

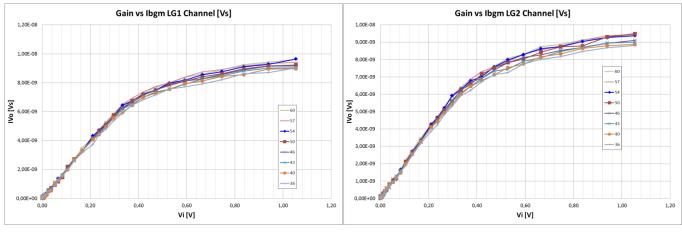

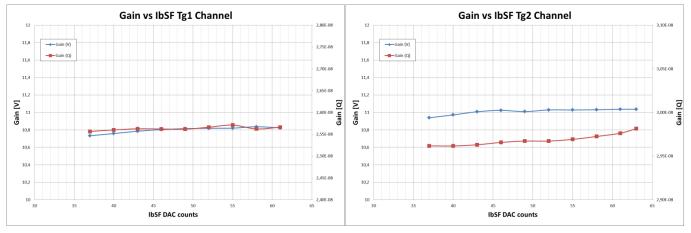

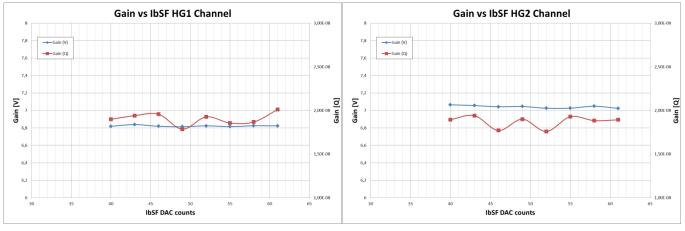

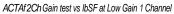

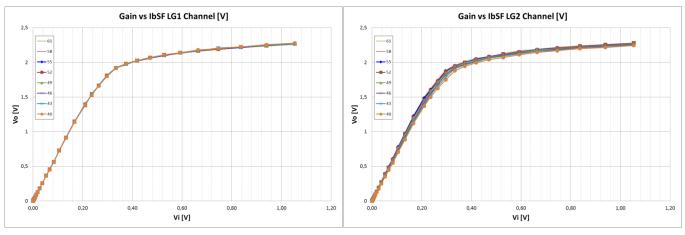

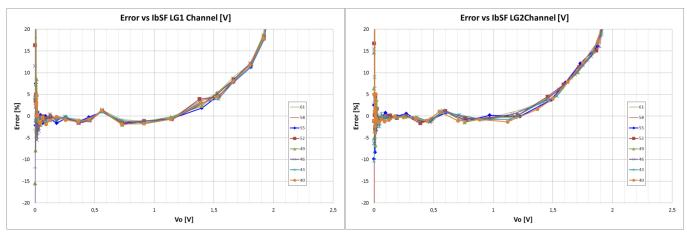

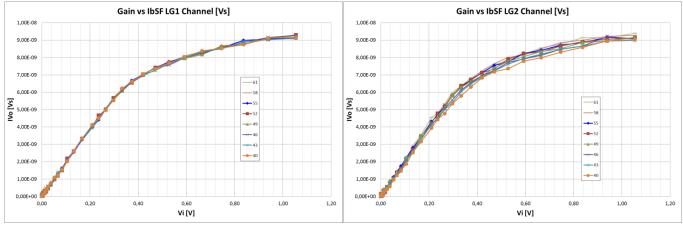

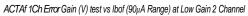

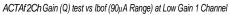

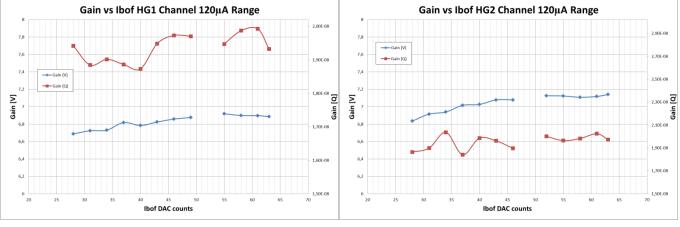

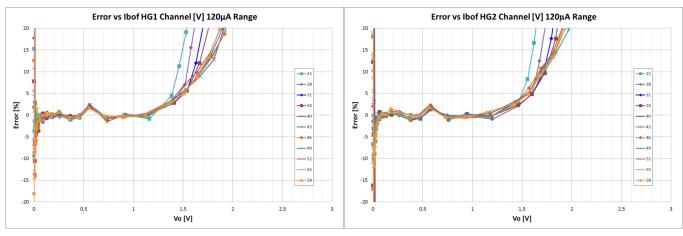

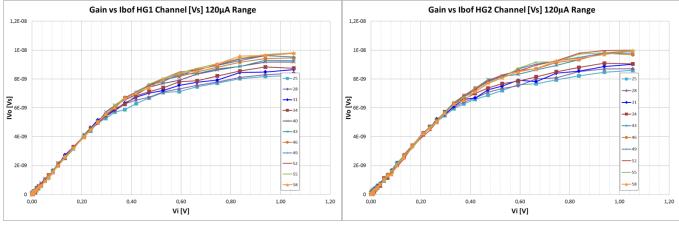

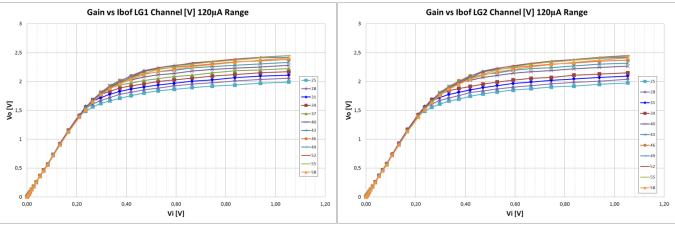

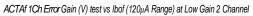

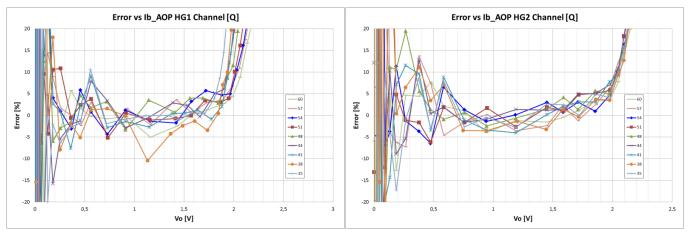

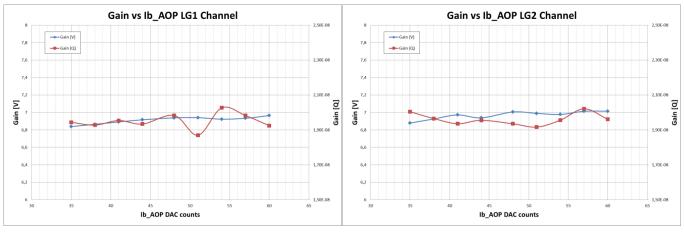

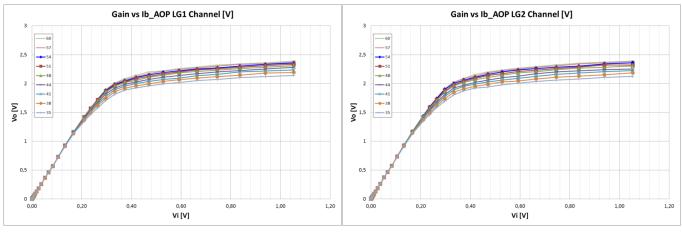

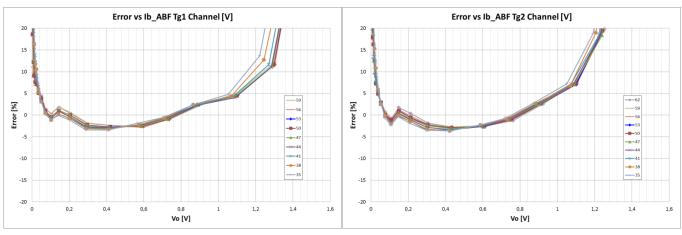

| 3.35. | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

|-------|--------------------------------------------------------------------------------------------|----|

|       | integrated charge variations as a function of the $I_{bqm}$ bias current source            | 88 |

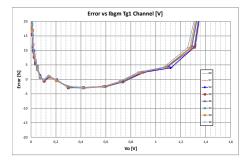

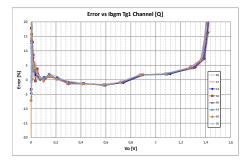

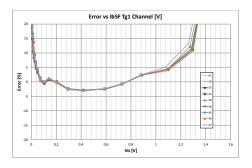

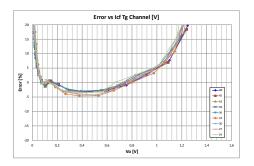

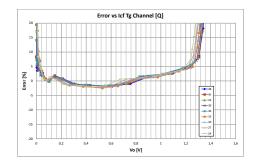

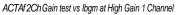

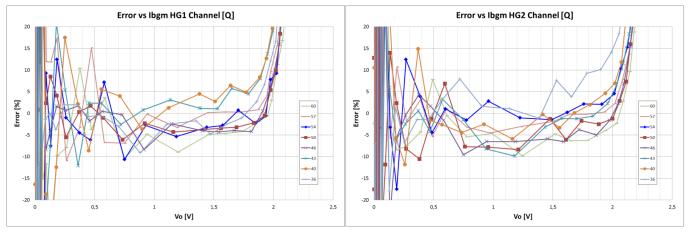

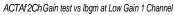

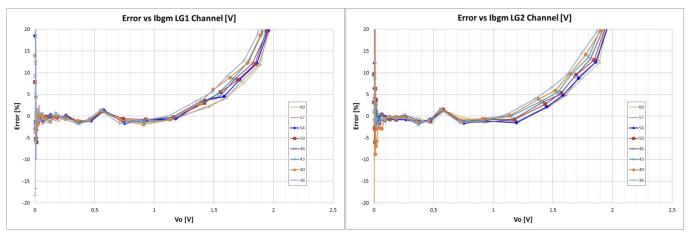

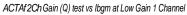

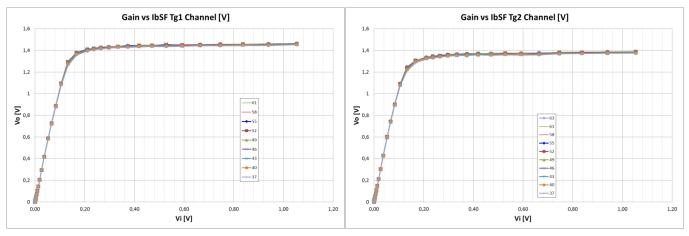

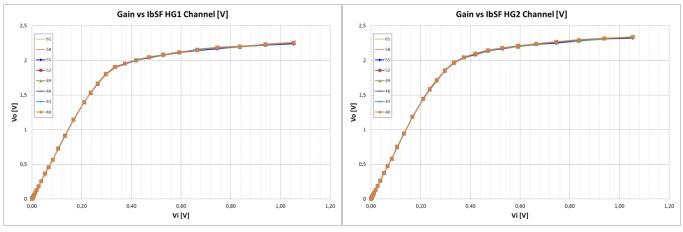

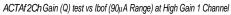

| 3.36. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{bgm}$ bias current source                    | 89 |

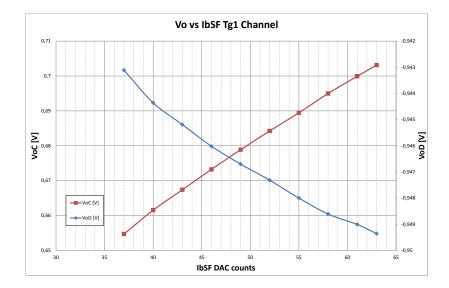

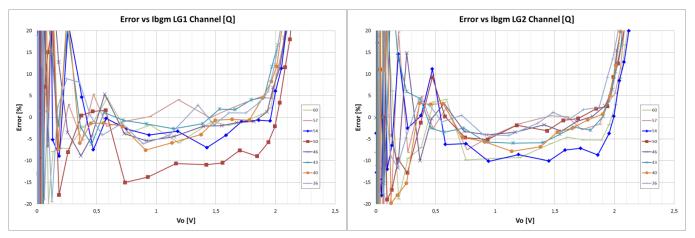

|       | ACTAf 2Ch output voltages in common mode and differential mode variations                  |    |

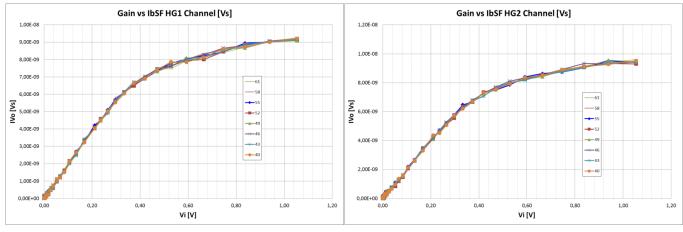

|       | as a function of the $I_{bSF}$ bias current source                                         | 89 |

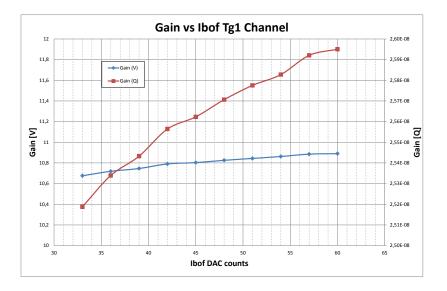

|       | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

|       | integrated charge variations as a function of the $I_{bSF}$ bias current source            | 90 |

| 3.39. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{bSF}$ bias current source                    | 90 |

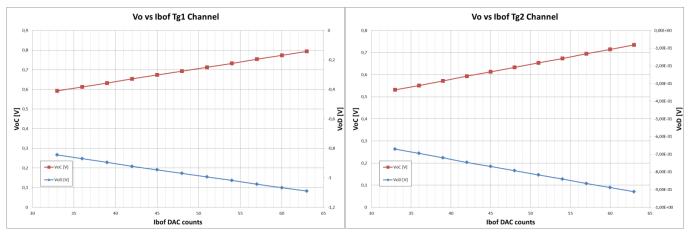

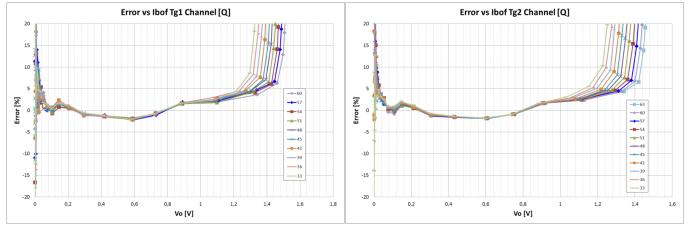

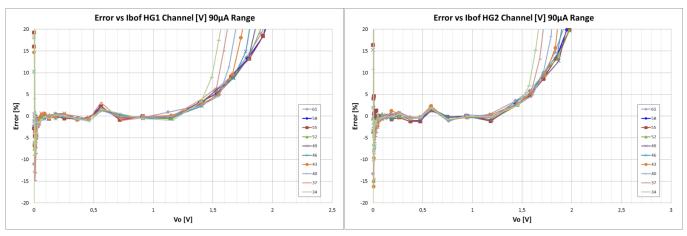

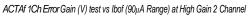

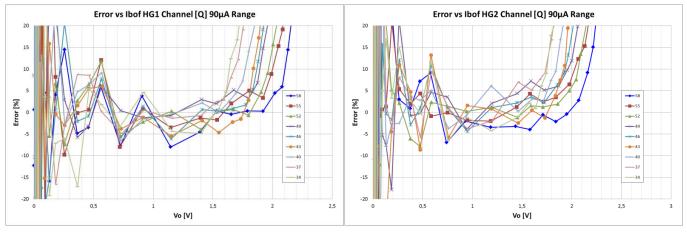

| 3.40. | ACTAf 2Ch output voltages in common mode and differential mode variations                  |    |

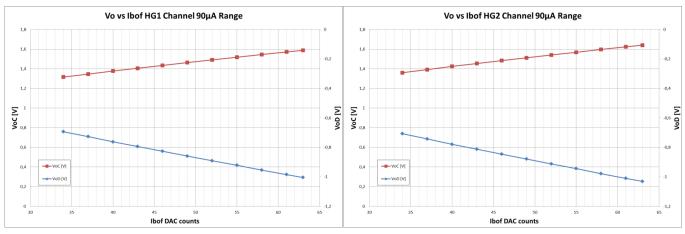

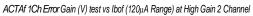

|       | as a function of the $I_{bof}$ bias current source                                         | 91 |

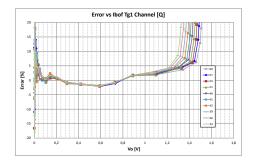

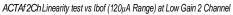

|       | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

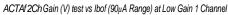

|       | integrated charge variations as a function of the $I_{bof}$ bias current source            | 92 |

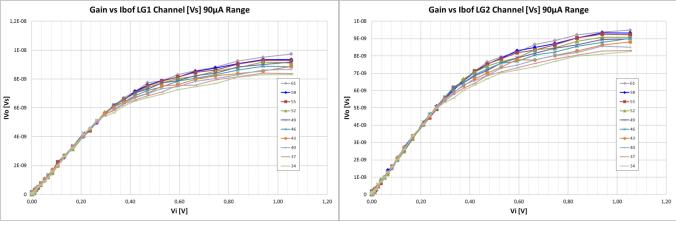

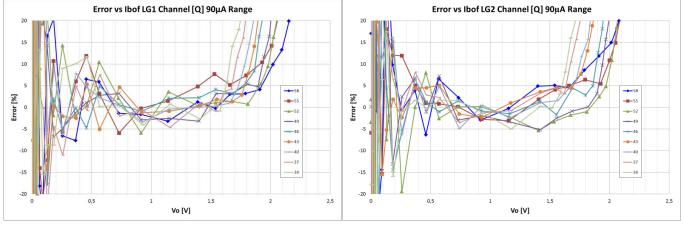

| 3.42. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{bof}$ bias current source                    | 92 |

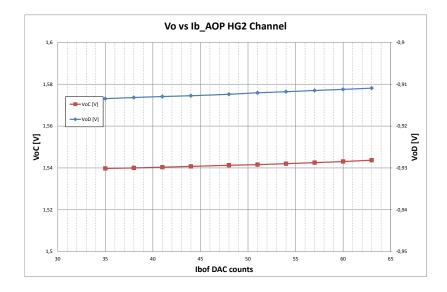

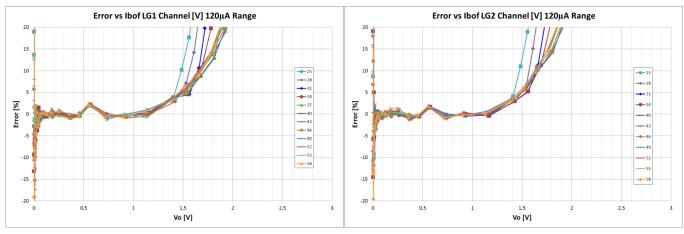

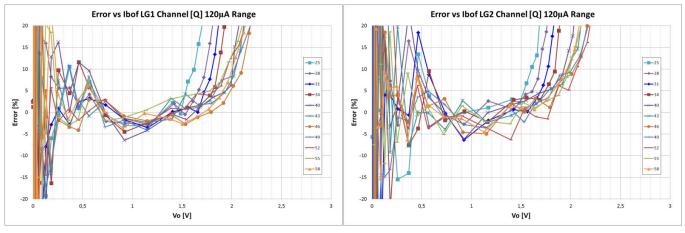

| 3.43. | ACTAf 2Ch output voltages in common mode and differential mode variations                  |    |

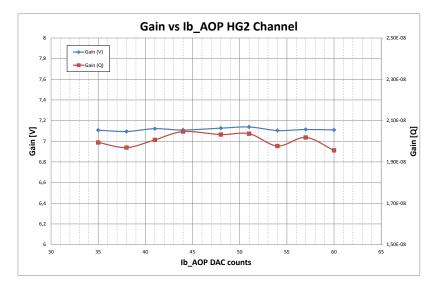

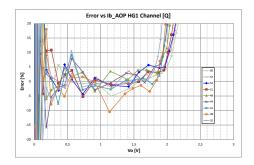

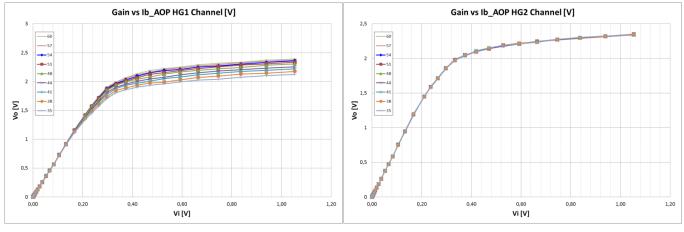

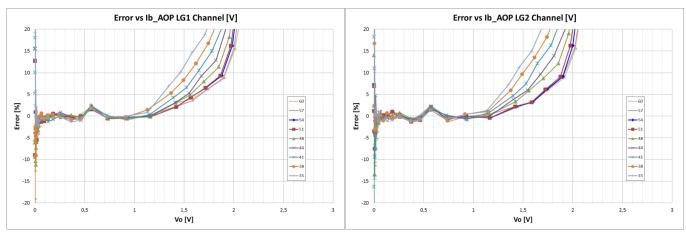

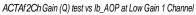

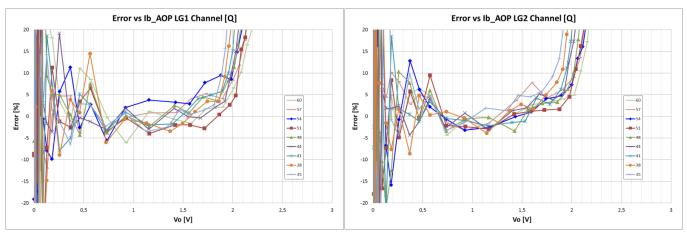

|       | as a function of the $I_{b_{AOP}}$ bias current source                                     | 93 |

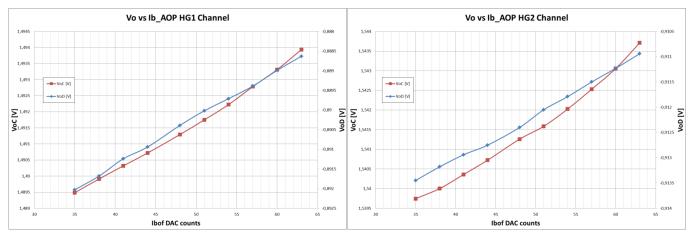

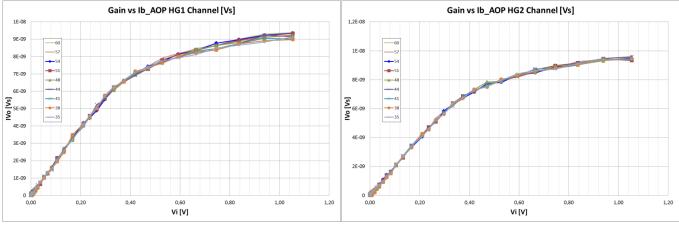

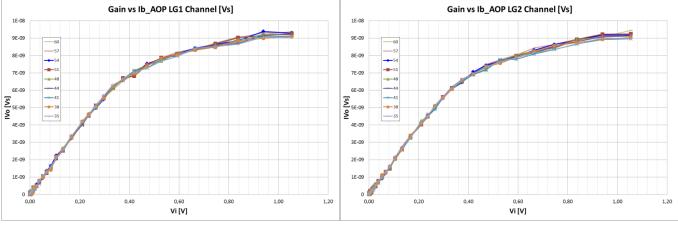

| 3.44. | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

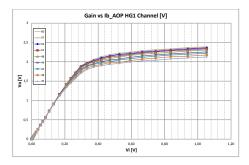

|       | integrated charge variations as a function of the ${\cal I}_{b_{AOP}}$ bias current source | 94 |

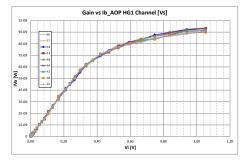

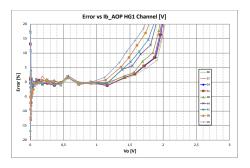

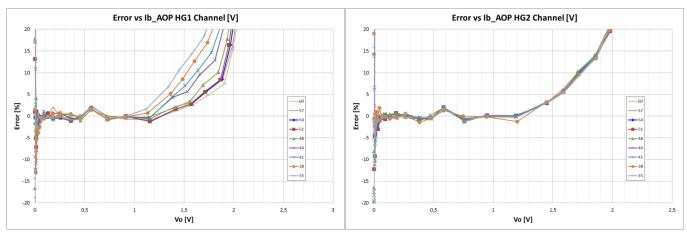

| 3.45. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{b_{AOP}}$ bias current source                | 94 |

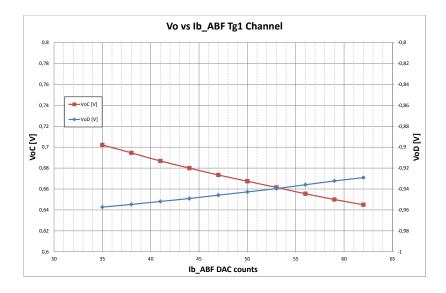

| 3.46. | ACTAf 2Ch output voltages in common mode and differential mode variations                  |    |

|       | as a function of the $I_{b_{ABF}}$ bias current source                                     | 95 |

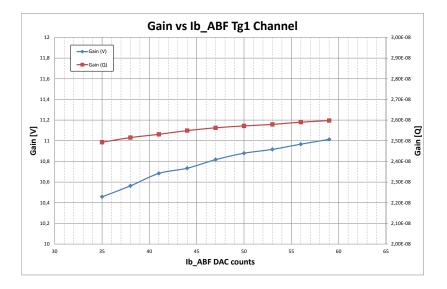

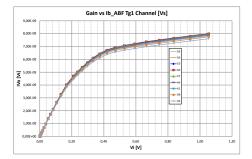

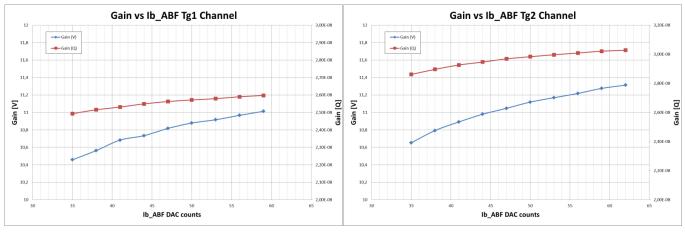

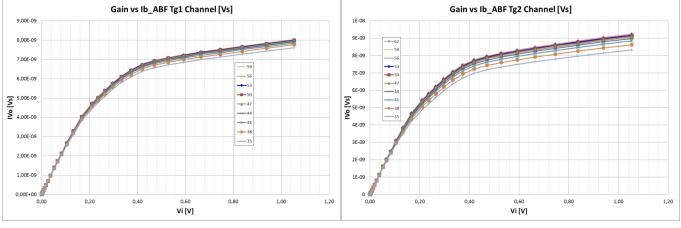

| 3.47. | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

|       | integrated charge variations as a function of the ${\cal I}_{b_{ABF}}$ bias current source | 95 |

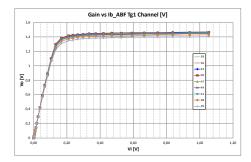

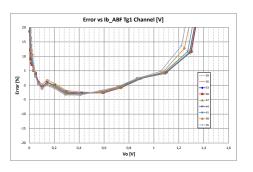

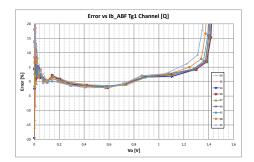

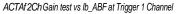

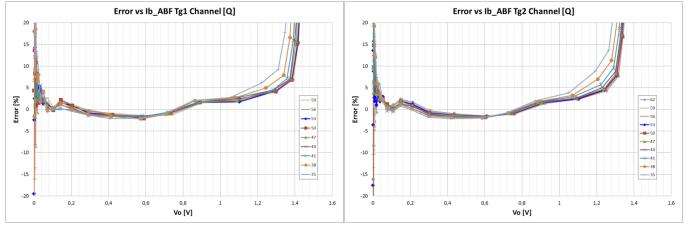

| 3.48. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{b_{ABF}}$ bias current source. $\ . \ . \ .$ | 96 |

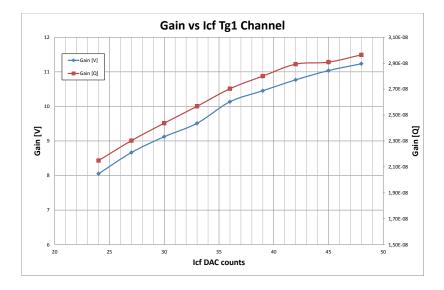

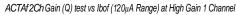

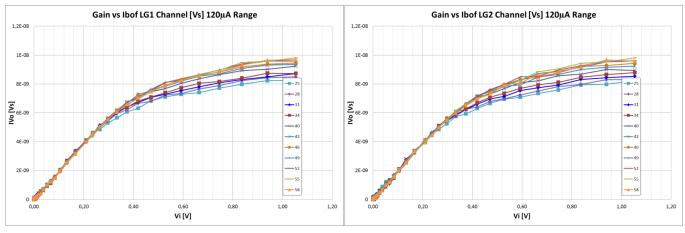

| 3.49. | ACTAf 2Ch gain variations measured at the differential voltage output and                  |    |

|       | integrated charge variations as a function of the ${\cal I}_{bcf}$ bias current source     | 97 |

| 3.50. | Linearity range and the relative error, for differential output voltage (top)              |    |

|       | and charge (bottom) as a influence of the $I_{bcf}$ bias current source                    | 98 |

|       |                                                                                            |    |

#### LIST OF TABLES

| 2.1. | Preamplifier requirements                                                   |

|------|-----------------------------------------------------------------------------|

| 2.2. | PACTA prototype versions comparative                                        |

| 2.3. | PACTAv1.4 Voltage biasing values (typ.)                                     |

| 2.4. | PACTAv1.4 Current biasing values (typ.)                                     |

| 2.5. | Preamplifier requirements                                                   |

| 3.1. | ACTA prototype versions comparative                                         |

| 3.2. | Step function method to calculate the full channel bandwidth with the ACTAf |

|      | amplifier                                                                   |

| 3.3. | Main measured performances of the amplifier                                 |

## Agraïments

Voldria agrair en primer lloc al meu director de tesi, David Gascón, per haver-me donat la oportunitat de treballar en el grup de recerca de física d'altes energies (HEP) de la Facultat de Física da la Universitat de Barcelona i mes concretament, poder participar en la contribució del grup de recerca en el projecte CTA i poder dur a terme la recerca festa en aquesta tesi. Vull destacar també que sense ell, aquesta tesi no hagués tingut sentit. Gracies per guiar-me en el disseny dels layouts, en entendre els resultats, en ajudar-me en buscar la millor solució a cada un dels problemes que ens hem anat trobant al llarg d'aquests anys. Però gracies sobretot, per ensenyar-me els valors de la recerca.

Durant aquests anys, he tingut el privilegi de compartir infinitat d'hores amb molts companys de feina. Gracies Adri per que sempre treus temps per solucionar tota mena de problemes amb els ordenadors, però sobretot, pels consells ni que sigui a canvi del teu "vale por un Adri". Gracies Edu, per totes les hores que hem compartit. Gracies Joan, per que sempre tens una solució. Gracies Sergio, per tota la ajuda en l'escriptura. És molt difícil no deixar-se ningú i demano disculpes per que segurament em deixaré de nombrar algú, però vull donar les gracies especialment a en Ricardo i en Lluis, per que m'ha ajudat en veure el significat de moltes de les mesures. Moltes gracies Javier, pel munt d'hores que m'has ajudat amb el anàlisis de RF i a entendre i utilitzar un munt d'aparells. Moltes gracies als amics que m'heu fet costat aquests anys i que també m'heu empès fins al final. Gracies Chemita, Nectarina, Culu per entendrem en els moments de dificultat que he tingut a l'escriure aquesta tesis.

Vull donar les gracies a tota la meva família, padrins, cosins, tiets, sogres i cunyat. Per que vosaltres ja fa molts mes anys que m'ajudeu a arribar fins aquí. Gracies Tata, per fer-me constat tant incondicionalment i confiar sempre amb mi. Gracies Mama, per que vostè m'heu ensenyat i guiat a ser la persona que soc, i que amb esforç, un pot aconseguir tot el que es proposi.

Finalment, et vull donar les gracies a tu Carol. Per la infinita paciència que has tingut amb mi. Pels moments bons i dolents que hem compartit. Per entendrem en les moltes hores que no hem pogut estar junts. Per ajudar a aixecar-me en els moments difícils. Per ajudar-me a gaudir de les fites que he aconseguit. Però sobretot, gracies per saber-me escoltar.

Els raig còsmics son bàsicament radiacions d'alta energia principalment originats fora del Sistema Solar. Aquestes fonts còsmiques poden causar emissions de raig  $\gamma$  mitjançant diferents mecanismes d'acceleració astronòmica com ara el sincrotró entre d'altres [5].

Actualment existeixen dues tècniques per observar els raig  $\gamma$  procedents de l'espai exterior: l'observació directa mitjançant detectors de partícules a bord dels satèl·lits, i la detecció indirecta per mitjà de detectors terrestres que utilitzen la tècnica Cherenkov.

L'atmosfera absorbeix la major part de la radiació gamma. Per tant, es fa impossible la detecció directa de raigs  $\gamma$  a la superfície de la terra. No obstant això, és possible detectar l'efecte dels raigs  $\gamma$  en l'atmosfera. Quan un raigs  $\gamma$  primari interactua inicialment amb una molècula de l'atmosfera, aquest genera un parell electró-positró. D'aquesta manera es crea una dutxa d'aire estès (EAS), que origina l'emissió de fotons Cherenkov.

La detecció de la llum Cherenkov corresponent a una dutxa generada per uns raigs  $\gamma$  a l'atmosfera no és una tasca fàcil. L'àrea que cobreix la dutxa de llum Cherenkov és molt tènue, amb imatges de no més d'uns pocs milers de fotons, i de durada molt curta entre 2,5 i diverses desenes de nano segons. Això fa necessari l'ús de fotodetectors molt sensibles i ràpids, així com electrònica de baix soroll i també ràpida, capaç de detectar i guardar les imatges rellevants. Aquestes deteccions es realitzen mitjançant l'ús de telescopis d'imatges Cherenkov atmosfèriques (IACTs).

Observar la dutxa de raigs  $\gamma$  amb més d'un IACT al mateix temps permet l'ús de la estereoscopia amb la finalitat de poder reconstruir la dutxa en imatges de 3 dimensions [6], [7].

El següent pas de la comunitat internacional d'astronomia de raigs  $\gamma$  consisteix en la construcció d'un gran conjunt amb molts IACTs, utilitzant l'última tecnologia puntera per construir els millors telescopis fins a l'actualitat, i per tant cobrir tot l'espectre dels raigs  $\gamma$  de totes les fonts en existent en el cel. Aquest és l'objectiu del consorci Cherenkov Telescope Array (CTA) citeCTAweb.

Els telescopis IACTs es basen típicament en una estructura mecànica amb un sistema de mirall reflector que recull els fotons de les dutxes i les reflecteix cap a la càmera.

Com que les dutxes Cherenkov duren només uns pocs nano segons, és important assegurar-se que, d'una banda, els fotons capturats en els IACTs que s'han generat al mateix temps, arriben a la càmera en el mateix intent de temps. Això requereix l'ús de reflectors parabòlics tessel·lats formant una parabòlica, de manera que la longitud dels camins que els fotons han de viatjar sigui la mateixa. D'altra banda, els fotodetectors utilitzats en les càmeres IACT han de ser molt sensibles per tal de poder detectar la major proporció possible dels fotons que entrin mitjançant una alta eficiència de detecció de fotons (PDE). Aquests fotons detectats generalment s'anomenen electrons de fotos (PE).

Es pretén construir tres tipus de telescopis (els anomenats telescopis de mida petita (TSM), els telescopis de mida mitjana (MST) i els telescopis de mida gran (LSTs)) amb diferents mides dels seus miralls reflectors, optimitzats per cobrir els diferents règims d'espectre d'energia [8].

Un dels tipus de detectors de fotons és el tub fotomultiplicador (PMT), i correspon al més utilitzats en els IACTs. Un PMT té un càtode fotoelèctric que absorbeix la llum i emet un electró. Un PMT també conté altres elèctrodes de forma consecutiva anomenats dinodes. Cada dinode es manté a un voltatge positiu més alt que el seu predecessor. Els electrons són atrets per cada dinode successivament, i al impactar-hi es desprenen diversos electrons addicionals per a cada impacte. Com el corrent d'electrons es desplaça de dinode en dinode, es genera finalment una cascada electrons.

Els PMTs aconsegueixen sensibilitats prou bones com per a poder mesurar fotons individualment. Tenen poc soroll en la foscor, però de vegades generen fotons sense haver rebut cap tipus de llum a causa del corrent de foscor, o generen més d'un impuls per a un mateix fotó després d'una cascada d'electrons. Funcionen amb rangs de longituds d'ona sensibles en l'ultraviolat (UV) i l'infraroig (IR) que corresponen amb les dutxes de llum Cherenkov. També tenen una resposta molt ràpida al nivell de nano segons, per contra, els electrons no es generen en tots els dinodes al mateix temps, sinó que es generen amb una certa dispersió en el temps que depèn del nombre de dinodes, l'alta tensió aplicada i altres paràmetres.

Els polsos generats pels fotosensors (normalment PMTs) son molt estrets i han de poder-se mostrejar d'una forma molt ràpida per tal de ser capaços de determinar amb una alta precisió instant d'arribada, i poder integrar la seva càrrega en una finestra de temps prou estreta que permeti reduir la contribució induïda pel soroll de fons degut a la llum cel durant la nit (NSB). Una amplada típica de l'impuls d'un PMT de 2.5 ns necessita mostrejar-se a 800 MHz d'acord amb el teorema de Nyquist, obtenint una freqüència de mostreig de 1 Gs/s. Tenint en compte que una càmera IACT pot tenir al voltant de 1.000 píxels i 8 nivells de quantificació, enregistrar de forma contínua els senyals de tots els píxels d'una càmera significaria una taxa de dades d'1 TB/s, el qual resultaria immanejable. En lloc d'això, els IACTs actuals únicament enregistren de forma contínua quan es detecta un esdeveniment interessant. Per tal d'aconseguir fer això, s'utilitza un sistema d'adquisició de dades basat en memòries analògiques juntament amb un complex sistema de desencadenament.

Aquest memòries analògiques mostregen els senyals d'entrada a una alta freqüència de mostreig, però amb petits acumuladors muntats en una determinada configuració d'anell. L'opció de l'electrònica de part davantera (FE) en la col·laboració NECTAr (Nova Electrònica per al conjunt CTA) per a les càmeres de CTA (que és on està centrada aquesta tesi) està realitzat en un xip de mostreig de 16 bits d'entre 1 i 3 GS/s i que es basa en memòries analògiques, incloent-hi la major part de les funcions de lectura [9].

El sistema de desencadenament analitza cada pols i decideix si el senyal correspon a un esdeveniment de Cherenkov vàlid per a ser emmagatzemada o no. L'estratègia bàsica del complex sistema de desencadenament és, en un primer nivell, activar inicialment un grup de píxels veïns (disparador de nivell 0 o L0) i després fer-ho a nivell de la càmera sencera (nivell 1 o L1 i possiblement nivell 2 o L2). La decisió final és pren pel sistema disparador a nivell de matriu de telescopis [10].

Com que els polsos ràpids procedents d'un PMT requereixen una sistema de lectura ràpid [11] aquests es llegeixen mitjançant un preamplificador amb un gran ample de banda (BW), un alt rang dinàmic (DR) i de baix soroll. El preamplificador ha d'estar a prop del fotosensor connectat amb un cable o una línia de transmissió a l'electrònica FE. D'acord amb simulacions de Monte Carlo [12] el BW analògic del sistema complet ha de ser d'almenys 300 MHz, per la qual cosa el BW del preamplificador ha de ser d'aproximadament 500 MHz. Es requereix un DR de 16 bits d'una banda per a poder mesurar el senyal d'un sol foto-electró (SPE) amb finalitats de calibratge, i d'altra banda per a poder mesurar polsos més alts de llum de fins a 5000 PE. Atès que el PMT ha de funcionar a un guany baix (40 K) per tal d'evitar problemes d'envelliment, aconseguir una bona resolució en la mesura del SPE imposa requisits de baix soroll. El soroll de càrrega equivalent de (ENC) < 4Ke significa que la densitat espectral de potència (PSD) del soroll de corrent referenciat a l'entrada ha de ser menor de  $10pA/\sqrt{Hz}$  per a una lectura en mode corrent. Per a la implementació integrada del preamplificador es necessari una impedància d'entrada baixa i un punt d'operació de voltatge baix per tal d'aconseguir un gran BW.

D'acord amb els requisits del consorci CTA, les especificacions de la càmera per als diferents telescopis necessiten circuits electrònics dedicats fora de les especificacions dels components comercials que hi ha disponibles en el mercat. Per motius d'efectivitat en el cost i la innovació tècnica en l'estat de l'art, s'han desenvolupat diversos circuits integrats d'aplicació específica (ASICs) completament personalitzats. L'objectiu d'aquesta tesi és el desenvolupament d'un canal d'amplificació complert per poder injectar els polsos ràpids procedents dels sensors de la càmera cap les memòries analògiques del circuit digitalitzador. En base a les grans restriccions del canal d'amplificació per al projecte CTA, s'han aplicat noves tecnologies per tal de cobrir per una banda, el BW requerit pel baix nivell de soroll que es necessita i d'altra banda disminuir el consum d'energia necessari tant com sigui possible.

Aquesta tesi es centra en el disseny de l'etapa amplificadora per als telescopis LST i MST en la primera etapa d'amplificació (preamplificador), i també en una segona etapa d'amplificació i condicionament de la senyal per als telescopis MST.

La primera etapa d'amplificació es basa en un preamplificador en mode corrent de banda ampla amb 16 bits de DR. En aquesta tesi es proposa un nou circuit en mode corrent per tal de superar la limitació del senyal màxim mitjançant la creació de diversos camins de guany en la primera part de l'etapa d'entrada. El corrent d'entrada es divideix en l'etapa d'entrada en base comuna en dues (o més) corrents de sortida escalades. Després, cada corrent es llegeix en un mirall de corrent dedicat que pot ser optimitzat per a diferents situacions. El mirall de corrent de guany alt requereix circuits específics de control de saturació per tal d'assegurar que la divisió de corrent segueix sent prou precisa fins i tot si aquest mirall de corrent es satura. Finalment, el senyal de corrent es converteix en voltatge mitjançant un amplificador de transimpedància de llaç tancat.

El xip pre-amplificador per CTA (PACTA) compleix els requisits generals del projecte CTA en base a un disseny innovador que aconseguir superar totes les restriccions amb un molt baix consum d'energia. S'han dissenyats i provats versions tant de composició única com diferencials. El consum d'energia de les solucions alternatives basades en components comercials COTS que es van provar per als prototips de les càmeres dels telescopis de CTA es van descartar ja que tenien consums de com a mínim 4 vegades més gran.

La col·laboració nèctar [13] té la intenció de construir un nou circuit integrat que inclou la major part dels components discrets necessaris fins ara i correspon a una de les opcions de FE considerades per a les càmeres CTA [11]. Una millora en els costos, la fiabilitat i les prestacions de la càmera s'aconsegueix mitjançant la maximització en la integració de la electrònica de FE en un ASIC, en un sol xip de mostreig a GHz.

Una solució de llaç totalment tancat basat en amplificadors de tensió en realimentació (OTA o OpAmp) no és factible ja que es requereix un producte de guany per ample de banda (GBW) de més de 8 GHz, mentre que el producte GBW màxim que es pot aconseguir en tecnologia CMOS de 0,35  $\mu m$  està molt per sota d'1 GHz ([14], [15]). En aquesta tesi s'explora un enfocament alternatiu basat en transconductors d'alta freqüència (HF) linealitzats, els quals inclouen un circuit dedicat per ajustar l'offset de DC per tal d'estar acoblat correctament en DC al ADC NECTAr0, i seguit a continuació per un convertidor de corrent a tensió de gran marge, i finalment un acumulador de bucle tancat i baixa impedància de sortida serveix per accionar les càrrega capacitives de l'entrada de les memòries analògiques.

#### Abstract

Two techniques are currently available to observe the  $\gamma$ -rays coming from outer space: the direct observation by particle detectors on board of satellites, and the indirect detection by ground-based detectors using the Cherenkov technique. The atmosphere absorbs the most of the gamma radiation so, the direct detection of  $\gamma$ -rays at ground level becomes impossible. However, it is possible to detect the effect of  $\gamma$ -rays in the atmosphere. When a primary  $\gamma$ -ray first interacts with a molecule of the atmosphere it generates an electron-positron pair. In this way an Extended Air Shower (EAS) is created, originating the Cherenkov photon emission. Detecting the Cherenkov light corresponding to an air shower generated by a  $\gamma$ -ray is not an easy task. Cherenkov light pool is very faint, having Cherenkov images at the camera with no more than a few thousand photons, and the duration is very short, between 2.5 and several tens of nanoseconds. This makes necessary the use of very sensitive and fast photo detectors, as well as fast and low noise electronics, capable to detect and save the interesting images. These detections are performed by using Imaging Atmospheric Cherenkov Telescopes (IACTs).

One type of photon detector is the photomultiplier tube (or PMT), most commonly used in IACTs. A PMT has a photoelectric cathode that absorbs light and emits an electron. A PMT also contains other electrodes in sequence called dynodes. Each dynode is kept at a higher positive voltage than the preceding one. Electrons are attracted to each successive dynode, and upon striking the dynode they knock off several additional electrons from the dynode. As the electron stream travels from dynode to dynode, more and more electrons are emitted as part of a cascade.

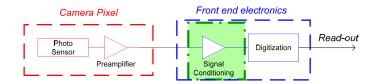

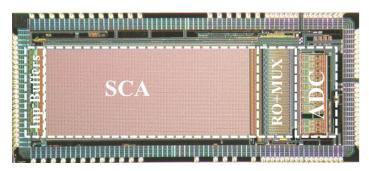

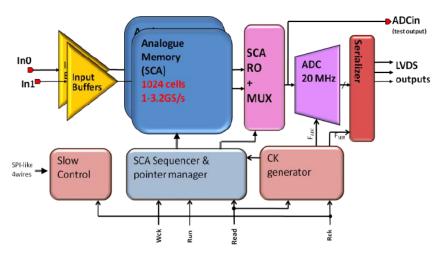

The pulses generated by the photo sensors (typically PMTs), being very narrow, need to be sampled very fast in order to determine with high precision its arrival time, and to integrate its charge in a narrow window which allows to reduce the noise contribution induced by night sky background (NSB). A typical 2.5 ns width pulse from a PMT needs to be sampled at 800 MHz to recover at least the first lobe according to Nyquist theorem, being 1 Gs/s a typical sampling frequency. Considering that an IACT camera can have around 1000 pixels and 8 quantization levels, a continuous recording of the signals from all the pixels in a camera would mean a data rate of 1 TB/s, which is unmanageable. Instead of that, current IACTs only records continuously when an interesting event is detected. In order to do that, they uses a complex data acquisition system based on analogue memories with a complex trigger system. This analogue memories sample the input signals at high sample rate, but with small buffers mounted in a dedicated ring configuration. The NECTAr (New Electronics for the CTA array) collaboration's front end (FE) option for the camera of the CTA (which is this thesis focused) is a 16 bits and 1-3 GS/s sampling chip based on analogue memories including most of the readout functions [9]. The trigger system, analyzes each pulse, and decides if the signal corresponds to a valid Cherenkov event to be stored or not [10].

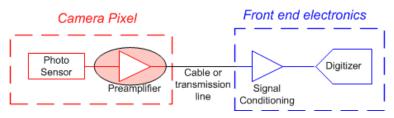

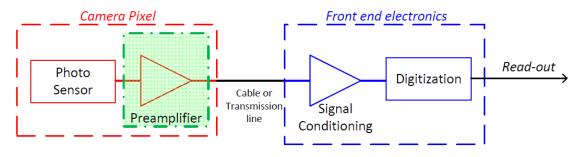

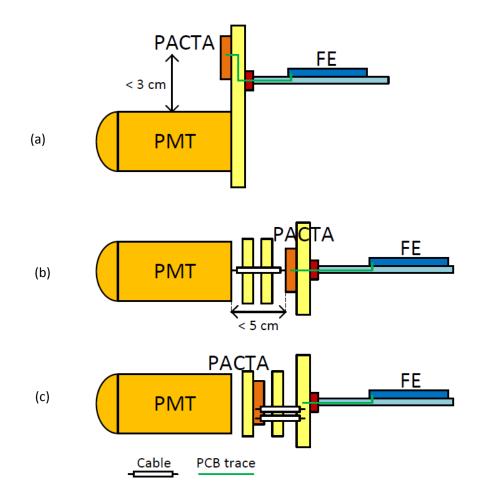

The fast pulses coming from the PMT requires a fast readout option [11] with a wideband, high dynamic range and low noise pre-amplifier. The pre-amplifier is attached to the photo sensor and it is connected by a cable or transmission line to the front end electronics, which is placed in the camera. According to Monte Carlo simulations [12] the analogue bandwidth (BW) of the full system must be at least 300 MHz, and so the pre-amplifier BW about 500

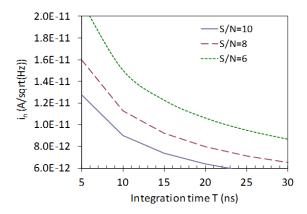

MHz. A 16 bit dynamic range (DR) is required on one side by the measurement of the single photo-electron signal (SPE) for calibration purposes, and on the other side by the highest light pulse (5000 PE). Since the PMT operates at low gain (40 K) to avoid ageing problems, achieving a good SPE resolution imposes low noise requirements, Equivalent Noise Charge (ENC) < 4Ke which means that the input referred current noise power spectral density (PSD) should be smaller than  $10pA/\sqrt{Hz}$  for a current mode readout. Low input impedance and low voltage operation are required for integrated implementation and to achieve large BW.

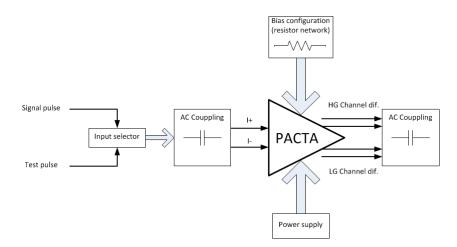

According to the CTA consortium requirements, the camera specifications for the different telescopes needs dedicated electronic circuits, since these specifications can not be achieved with current commercial components in the market. Due to cost effective and state of the art innovation, some full custom ASICs have been developed. The aim of this thesis is to develop a full amplification channel path to inject the fast pulses coming from the camera sensors to the analogue memories of the digitizer circuitry. Based on the hard constrains of the amplification channel path for the CTA project, new technologies are applied to cover on one hand, the required wideband at the low noise level and, on the other hand decrease the power consumption required as much as possible.

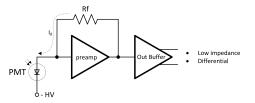

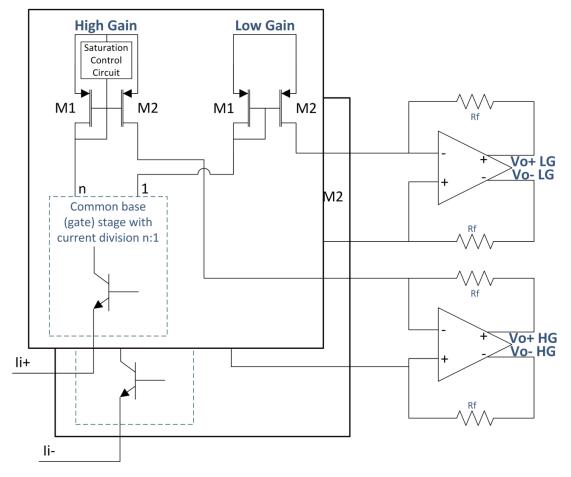

This thesis is focused in the design of the amplifier path stage of the CTA cameras at the first amplification stage (pre-amplifier) and also, at a second amplification stage and signal conditioning. The first amplification stage is based on a wideband current mode preamplifier with 16 bits DR. We propose a novel current mode circuit to overcome the maximum signal limitation by creating multiple gain paths at the very front end of the input stage. The input current is split in the common base input stage into two (or more) output scaled currents. Then each current is readout with a dedicated current mirror. The high gain current mirror requires dedicated saturation control circuitry in order to assure that current division is still accurate even if this mirror saturates. Finally, the current signal is converted to voltage by a closed loop transimpedance amplifier. The pre-amplifier for CTA (PACTA) chip fulfills the CTA general requirements based on an innovative design that achieve all the restrictions with very low power consumption. The power consumption of the alternative solutions based on COTS components which were tested for CTA camera prototypes but discarded is at least 4 times higher.

The NECTAr collaboration [13] intends to build a new integrated circuit including most of the discrete components needed so far. It is one of the front end electronics options considered for the CTA cameras [11]. A gain in cost, reliability and camera performances can be achieved by maximizing the integration of the front-end electronics in an ASIC, a single GHz sampling chip. A fully closed loop solution based on voltage feedback amplifiers (OTA or OpAmp) is not feasible because a Gain-bandwidth (GBW) product of more than 8 GHz is required, and the maximum GBW product that can be achieved in a  $0.35\mu m$  CMOS technology is well below 1 GHz ([14], [15]). An alternative approach based on linearised high frequency (HF) transconductors is explored, which includes dedicated circuitry to adjust the DC offset in order to be properly DC coupled to the NECTAr0 ADC, and is followed by a high swing current to voltage conversion, and finally a low output impedance closed loop buffer is used to drive a capacitive load.

#### ACRONYMS

- **AC** Alternating Current

- **ACTA** Amplifier for CTA

- **ADC** Analog-to-digital converter

- **APD** Avalanche Photo Diode

- **ASIC** application-specific integrated circuit

- **BW** Bandwidth

- CM Common Mode

- **CMOS** Complementary Metal–Oxide–Semiconductor

- **COTS** Commercial Off-The-Shelf

- CTA Cherenkov Telescope Array

- **DAC** Digital-to-Analogue Converter

- **DAQ** Data acquisition

- **DC** Direct Current

- **DFM** Design For Manufacturing

- **DPO** Digital Phosphor Oscilloscope

- **DR** Dynamic Range

- DRC Design Rule Check

- **EAS** Extended Air Shower

- **ENC** Equivalent Noise Charge

- **ENI** Equivalent Noise Current

- **FE** Front End

- FWHM Full Width at Half Maximum

- **GBP** gain bandwidth product

- **HF** High Frequency

- **HG** High Gain

- **IACT** Imaging Atmospheric Cherenkov Telescope

- **INL** Integral Non-Linearity

- IR Infra Red

- **LF** Low Frequency

- LG Low Gain

- LSB Least Significant Bit LSM Laser Scanning Microscopy LST Large-Sized Telescope **LVDS** Low-voltage Differential Signaling **LVPECL** Low-Voltage Positive/pseudo Emitter-Coupled Logic **MSB** Most Significant Bits **MST** Medium-Sized Telescope **NECTAr** New Electronics for the CTA array **NSB** Night Sky Background **OPAMP** Operational Amplifier **OTA** Operational Transconductance Amplifier **PACTA** PreAmplifier for CTA PCB Printed Circuit Board PΜ Phase Margin **PDE** Photon Detection Efficiency **PMT** Photo Multiplier Tube **PoR** Power-on Reset **PSD** Power Spectral Density **PSRR** Power Supply Rejection Ratio **QFN** Quad Flat No-leads **SAM** Sampling Analogue Memory SC Slow Control SE Single Ended **SFP** Small Form Factor Pluggable SiPM Silicon Photomultiplier SiGe Silicon Germanium **SPE** Single Photo-Electron SPI Serial Peripheral Interface SS Slave Select **SST** Small-Sized Telescope **S/R** Signal-to-noise Ratio

- $\textbf{TC} \quad \text{Temperature Coefficient} \quad$

- $\ensuremath{\mathsf{THD}}$  Total Harmonic Distortion

- **TIA** Transimpedance Amplifier

- **TIB** Trigger Interface Board

- **UB** University of Barcelona

- **UV** Ultra Violet

- $\label{eq:VCSEL} Vertical\mbox{-}Cavity \mbox{ surface-}Emitting \mbox{ Laser}$

Pels qui ens agradaria que hi fóssin, preò no hi són.

# 1

#### INTRODUCTION

Cosmic rays are immensely high-energy radiation, mainly originating outside the Solar System. A significant fraction of primary cosmic rays are originated from the supernovae of massive stars, pulsars and active galactic nuclei, quasars, gamma-ray bursts and dark matter annihilation studies. These cosmic sources can cause  $\gamma$ -ray emissions by different astronomical accelerating mechanisms like synchrotron, curvature radiation, inverse Compton effect, neutral pion decay and other accelerating mechanisms [5].

Two techniques are currently available to observe the  $\gamma$ -rays coming from outer space: the direct observation by particle detectors on board of satellites, and the indirect detection by ground-based detectors using the Cherenkov technique. Direct detection by on-board satellite detectors is the most direct solution to detect cosmic  $\gamma$ -rays by measuring them where they have not been absorbed out of the atmosphere yet. However, this thesis is based on the ground-based detectors.

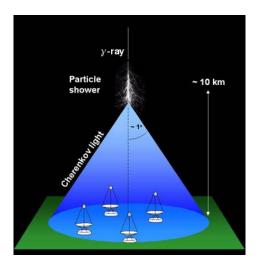

The atmosphere absorbs the most of the gamma radiation so, the direct detection of  $\gamma$ -rays at ground level becomes impossible. However, it is possible to detect the effect of  $\gamma$ -ray interacting in the atmosphere. When a primary  $\gamma$ -ray first interacts with a molecule of the atmosphere it generates an electron-positron pair. These two particles will further interact with other atmosphere molecules, loosing a fraction of their energy by the bremsstrahlung effect, and thus emitting a lower energy  $\gamma$ -ray. The new  $\gamma$ -rays create more electron-positron pairs that generate even lower energy  $\gamma$ -rays and the process repeats until the produced  $\gamma$ -rays have so low energy that they cannot produce new electron-positron pairs. In this way an Extended Air Shower (EAS) is created, originating the Cherenkov photon emission. The Cherenkov photons are emitted in a cone characterized by a certain angle  $\theta$ , known as Cherenkov angle. Nevertheless, the higher the shower occurs, the more space the cone has to spread and, at the end, the Cherenkov photons cast on a circle of roughly 120 m radius, whatever the height at which the EAS happened (typically at 10 Km high) [2]. Figure 1.1, illustrates a detecting gamma rays schematic, with Cherenkov telescopes.

Detecting the Cherenkov light corresponding to an air shower generated by a  $\gamma$ -ray is not an easy task. Cherenkov light pool is very faint, having Cherenkov images at the camera with no more than a few thousand photons in the best cases, and the duration is very short, between 2.5 and several tens of nanoseconds. This makes necessary the use of very sensitive and fast photo detectors, as well as fast and low noise electronics, capable to detect, identify and save the interesting images. These detections are performed by using Imaging Atmospheric Cherenkov Telescopes (IACTs). Analysing the images obtained by the IACTs, it is possible to calculate the so-called Hillas parameters [16], which are directly related with the meaningful physical parameters of the original  $\gamma$ -rays which generated the showers, such as their energies and incoming directions.

Figure 1.1.: Schematic of detecting gamma rays with Cherenkov telescopes. The Cherenkov light is beamed in the air shower and can be collected with optical detector. Referred to [1].

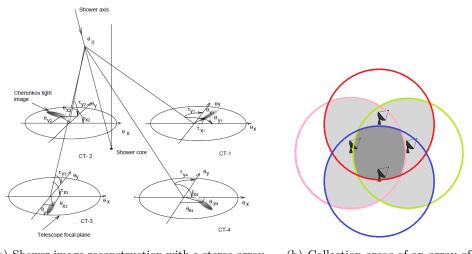

Observing a  $\gamma$ -ray shower with more than one IACT at the same time allows using stereoscopy to reconstruct the shower in 3 dimensions [6], [7]. Compared to the monoscopic observations, stereoscopic data recording allows a precise three-dimensional determination of the shower maximum position and impact parameter, an effective Hillas parameter [16] extrapolation, a better energy resolution and a more stringent rejection of muons, hadrons and Night Sky Background (NSB). Moreover, it also improves the angular resolution, making possible to distinguish sources which are very close. Figure 1.2, shows an image reconstruction scheme with a stereo array of 4 IACTs and their effective collection area.

(a) Shower image reconstruction with a stereo array of 4 IACTs.

(b) Collection areas of an array of 4 IACTs.

Figure 1.2.: Scheme of stereoscopic observation with an array of IACTs [2].

Direct detection is preferable for low energies, where the size of the Cherenkov showers is small, with not many Cherenkov photons, making these showers, difficult to distinguish from the night sky background photons. While the Cherenkov technique is more effective for high energies, that will scape undetected quite frequently in direct techniques. The IACTs developed in the last 25 years are ground-based detectors. The first one was Whipple, which in 1989 detected a TeV emission from the Crab Nebulae for first time [18]. After Whipple, other IACTs were built like HEGRA [19], which stands for High-Energy-Gamma-Ray Astronomy. HEGRA took data between 1987 and 2002, at which point it was dismantled in order to build its successor, MAGIC, at Roque de los Muchachos Observatory on La Palma. MAGIC, Major Atmospheric Gamma Imaging Cherenkov Telescopes, was built in 2003 with a diameter of 17 meters for the reflecting surface. A second MAGIC telescope (MAGIC-II), at a distance of 85 m from the first one, started taking data in July 2009. Together they integrate the MAGIC telescope stereoscopic system [20]. Other IACTs like CANGAROO, an acronym for Collaboration of Australia and Nippon (Japan) for a GAmma Ray Observatory in the Outback located near Woomera, South Australia operates since 1992. Since 1999 CANGAROO-II, an evolution of CANGAROO was built with a bigger diameter dish (7m and expanded to 10m in the year 2000 to increase the light collection). CANGAROO-III, is not a telescope itself, but an array of four CANGAROO-II expanded telescopes. The full array operates since 2004 [21]. The largest Cherenkov telescope in the world is HESS, stands for High Energy Stereoscopic System in Namibia. HESS is a stereoscopic telescope system, where four telescopes view the same air shower and it was operational by late summer 2001. In 2012 the phase II of the HESS project was completed, obtaining an array of five telescopes were the last one (HESS-II) is a 28-meter-sized mirror [22]. The last observatory that built a Cherenkov telescope is VERITAS, Very Energetic Radiation Imaging Telescope Array System [23] in Arizona; an array of four 12m telescopes that was completed in 2007.

The next step of the the international  $\gamma$  ray astronomy community consists of building a large array with many IACTs, using the latest high technology to build the best telescopes ever, and thus covering all the  $\gamma$  ray spectrum from all the sources in all the sky. This is the target of the Cherenkov Telescope Array (CTA) consortium [17].

The IACTs telescopes are commonly based on a mechanical structure with a reflector mirror system to collect the photons of the showers and reflects them into the camera.

This mechanical structure should allow at the camera, to move in azimuth<sup>i</sup> and also elevation. The reflector is not made by a single mirror due to the price and to the complexity of developing a mirror of about 28 m diameter. Instead of that, many individual tesselated<sup>ii</sup> spherical mirrors which can be reoriented by individual actuators in order to compensate possible deformations of the structure due to gravity, wind or even earthquakes.

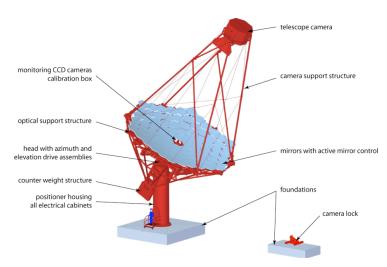

As the Cherenkov showers last only few nanoseconds, it is important to ensure that, on the one hand, the photons collected in the IACTs, which were generated at the same time, arrive to the camera at the same time. This requires the use of tesselated parabolic reflectors with overall parabolic shape, so the length of the paths that the photons have to travel is the same (figure 1.4). On the other hand, the photo detectors used in IACT cameras must be very sensitive to detect the largest possible proportion of incoming photons, requiring high

<sup>&</sup>lt;sup>i</sup>An azimuth is an angular measurement in a spherical coordinate system. The vector from an observer (origin) to a point of interest is projected perpendicularly onto a reference plane; the angle between the projected vector and a reference vector on the reference plane is called the azimuth.

<sup>&</sup>lt;sup>ii</sup>A tessellation of a flat surface is the tiling of a plane using one or more geometric shapes, called tiles, with no overlaps and no gaps.

(a) CANGAROO-I.

(b) CANGAROO-II.

(c) HEGRA.

(d) MAGIC.

(e) VERITAS.

(f) HESS.

Figure 1.3.: IACTs developed in the last 25 years.

Photon Detection Efficiency (PDE)<sup>iii</sup>. These detected photons are usually known as photo electrons (PE).

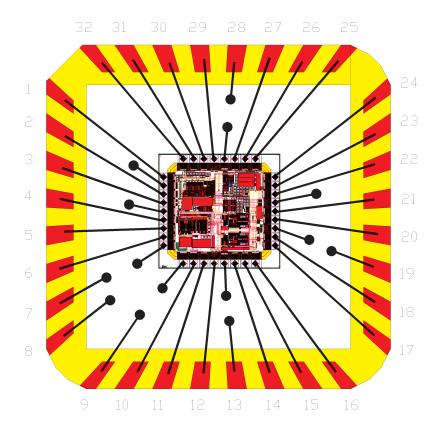

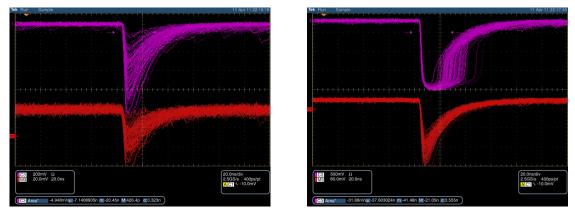

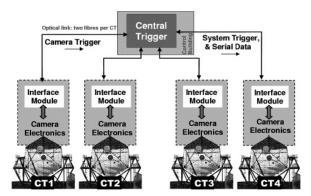

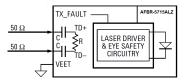

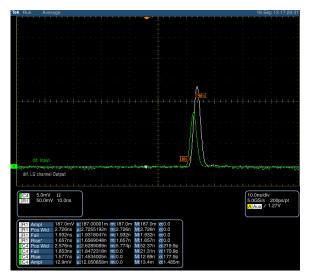

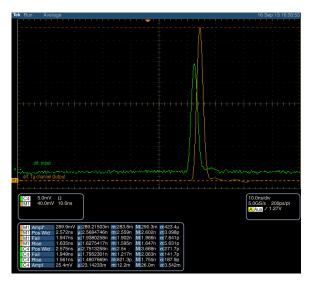

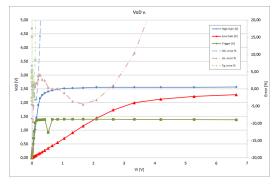

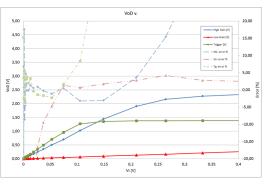

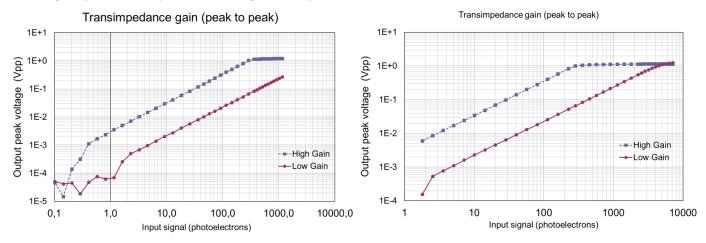

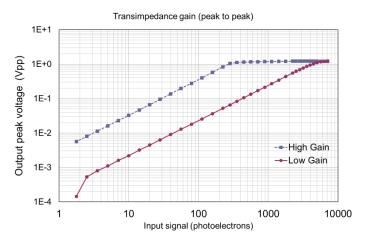

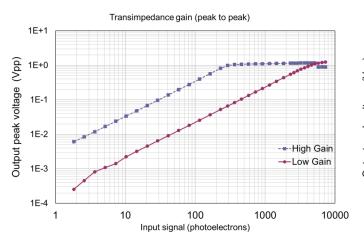

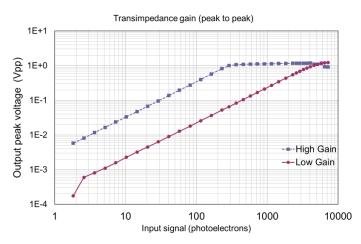

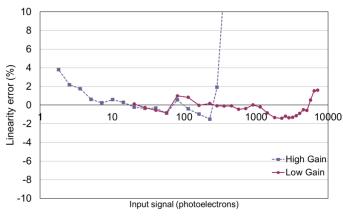

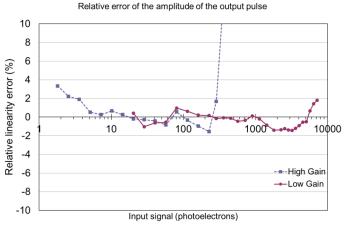

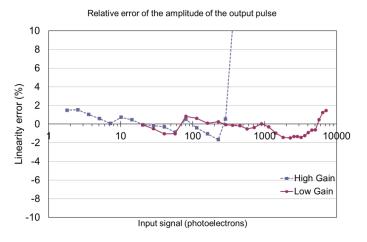

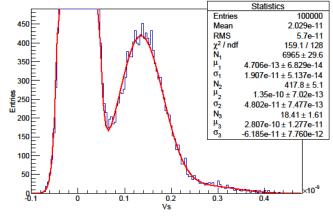

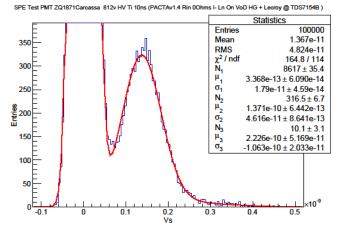

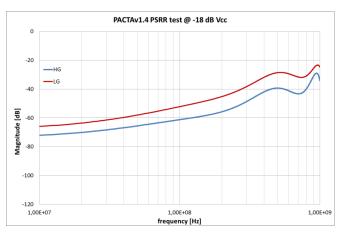

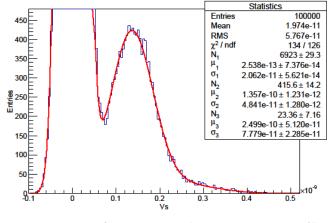

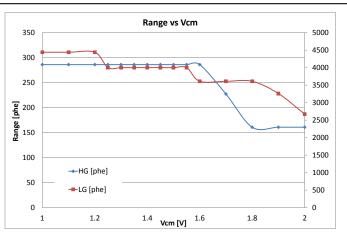

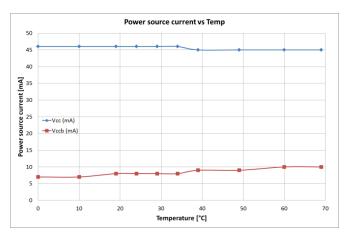

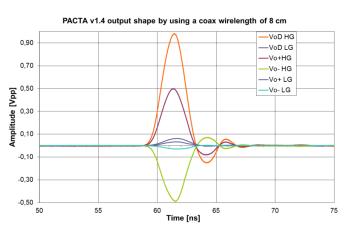

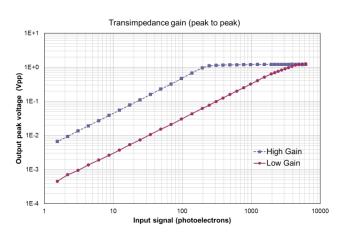

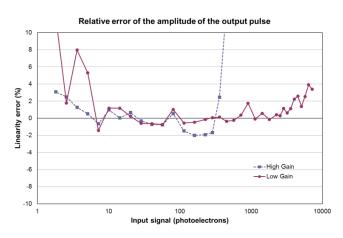

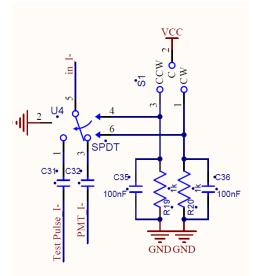

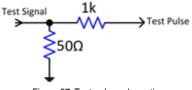

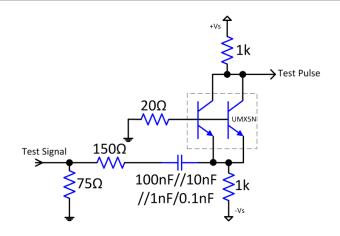

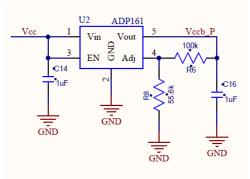

Figure 1.4.: Illustrative description of the CTA Medium-Sized Telescope (MST) design with the main assemblies and components [3].