# Circuit Designs for Increasing Reliability and Reducing Energy

Azamolsadat Seyedi Department of Computer Architecture Universitat Politècnica de Catalunya

A dissertation submitted in fulfillment of the requirements for the degree of Doctor of Philosophy / Doctor per la UPC

October 2015

Advisors: Osman Unsal, Adrian Cristal

| Acta de calificación de tes                 |                             | Curso académico:         |                                           |  |

|---------------------------------------------|-----------------------------|--------------------------|-------------------------------------------|--|

| Nombre y apellidos                          |                             |                          |                                           |  |

| Programa de doctorado                       |                             |                          |                                           |  |

| Unidad estructural responsable del programa |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| Resolución del Tribunal                     |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| Reunido el Tribunal designado a tal e       | efecto, el doctorand        | lo / la doctorand        | a expone el tema de la su tesis doctoral  |  |

| titulada                                    |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| Acabada la lectura y después de d           | ar respuesta a las          | cuestiones for           | muladas por los miembros titulares del    |  |

| tribunal, éste otorga la calificación:      |                             |                          |                                           |  |

|                                             | -                           |                          |                                           |  |

|                                             | PROBADO                     | NOTABLE                  | SOBRESALIENTE                             |  |

|                                             |                             |                          |                                           |  |

| (Nombre, apellidos y firma)                 |                             | (Nombre, apellidos y fir | ma)                                       |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| Presidente/a                                | 1                           | Secretario/a             |                                           |  |

| (Nombre, apellidos y firma)                 | (Nombre, apellidos y firma) |                          | (Nombre, apellidos y firma)               |  |

|                                             |                             |                          |                                           |  |

| Vocal                                       | Vocal                       |                          | Vocal                                     |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| ,                                           | de                          | de                       |                                           |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| El resultado del escrutinio de los voto     | os emitidos por los         | miembros titular         | es del tribunal, efectuado por la Escuela |  |

| de Doctorado, a instancia de la Comis       | -                           |                          |                                           |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

|                                             |                             |                          |                                           |  |

| (Nombre, apellidos y firma)                 |                             | (Nombre enellidee) (fr   |                                           |  |

| (Nombre, apendos y inma)                    |                             | (Nombre, apellidos y fir | na)                                       |  |

Presidente de la Comisión Permanente de la Escuela de Doctorado Secretario de la Comisión Permanente de la Escuela de Doctorado

Barcelona a \_\_\_\_\_\_ de \_\_\_\_\_\_ de \_\_\_\_\_\_

#### ABSTRACT

Computing technology has witnessed an inimitable progress in the last decades which is the result of CMOS technology scaling commensurate with Moore's law. Transistor feature sizes have shrunk to half at each generation, and consequently the number of transistors per chip has doubled each two years. However, power-density problems and the difficulty of eking out more performance from complex out of order single core architectures forced the processor manufacturers to introduce chip multiprocessors (CMP) as a solution. Each processor core in these CMPs was relatively simpler, and the increased number of cores provided increased total performance with decreased powerdensity. However, the same problems of energy-efficiency wall and performance wall have resurfaced with further scaling; exacerbate by the problem of reliability. This motivates researchers to find effective solutions on a wide variety of aspects such as architecture and circuit levels to mitigate these problems. In this thesis, we cope with these issues and concern about unwelcome problems and struggle with them in circuit level.

To satisfy the power consumption problem, computer architects have focused on designs that integrate several processing cores on a single chip but at the cost of more complexity in programming applications in a parallel fashion. This motivates us in this thesis to concern about hardware transactional memory, one of the state of the art mechanisms which provide acceptable parallel performance and simple parallel code. We propose a circuit solution of such hardware mechanism which attempts to simplify data versioning management, one of the key aspects in hardware transactional memory, and improves the performance considerably.

In this thesis, we also deal with the power consumption in cache memories. Cache memories are known as critical components in nowadays processors especially from the energy consumption point of view. We propose two circuit designs which aim to reduce the power consumption of cache lines during cache access.

Furthermore, we investigate another power reduction method which is very attractive in reducing the energy consumption: supply voltage scaling. However, in spite of its

popularity, it increases the number of memory cell failures. Therefore, in this thesis we propose a cache memory design which is equipped with an effective circuit mechanism in order to be resilient to a large number of cell failures. Our proposed cache configures itself for different supply voltages from the nominal to the near threshold voltage levels and duplicates or triplicates each data line whenever higher reliability is required.

In this thesis, we also attend to one of the emerging technologies called NEMs (Nano-Electro-Mechanical) switches and design a CAM (Content Addressable Memory) cell based on both NEM and CMOS technologies. As a use case, we leverage our proposed cell to design one of the most frequently accessed components of a microprocessor, first-level TLBs (Translation Lookaside Buffers) in order to extremely reduce the energy consumption per search/write operation, standby mode and also usage area.

#### ACKNOWLEDGMENT

First of all, I would like to express my sincere gratitude to my advisors Adrian Cristal and Osman Unsal for the continuous support of my PhD study and related research, for their patience, motivation, and immense knowledge. I learned a lot from my advisors. Thanks Osman and Adrian. Your guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor for my PhD study. I would also like to acknowledge Ibrahim Hur for his impressive support during the initial phase of my PhD. I also thank Mateo Valero for his dedication and continuous effort in making the Barcelona Supercomputing Center such a great platform for research.

I am thankful to my PhD committee members: Wolfgang Karl, Oguz Ergin, Oscar Palomar, Ramon Canal and Santhosh Rethinagiri, for reviewing my thesis and providing me with valuable comments and constructive feedback.

My sincere thanks also go to Stefan Cosemans, who accepted me very warmly and provided me an opportunity to join IMEC as an intern student. I had a great and productive time in Belgium thanks to Stefan's positive attitude and enthusiasm. Without his precious support it would not be possible to conduct the last step of this research.

I would like to express my thanks to my former supervisor during my studies at the University of Tehran, Ali Afzali-Kusha, for his endless support and kindness and also his help for preparing necessary documents of my PhD thesis deposit.

I would also like to acknowledge all my friends and colleagues from the office that helped me throughout my PhD; for their insights and expertise in technical matters, and for their unconditional support that has been crucial to keep me sane. Many thanks go to Adria Armejach, Ruben Titos, Vasilis Karakostas, Vesna Smiljković, Vladimir Gajinov, Daniel Nemirovsky, Oriol Arcas, Mario Nemirovsky, Gina Alioto, Nehir Sonmez, Behzad Salami, Srđan Stipić, Gulay Yalcin, Oscar Palomar, Omer Subaci, Nikola Marković, Chinmay Kulkarni, Cristian Perfumo, Timothy Hayes, Paul Carpenter, Francesco Ciaccia, Damian Roca, Cagri Eryilmaz, Saša Tomic, Ivan Ratkovic, Javier Arias, Milan Stanic, Milovan Djuric, Tassadaq Hussain, Ferad Zyulkyarov, and many others. I sincerely thank you all for your help and all the great moments we have had together.

Finally I would like to express my warmest thanks to my family for supporting me during this endeavor. I would like to extend my deepest gratitude to my beloved uncle and aunt for their never ending concern and enthusiastic support especially during our stay in Belgium. I wish you health, happiness and all the bests you deserve. I especially thank my mom and dad. My hard-working parents have sacrificed their lives for us and provided unconditional love and care. I certainly would not reach this point without their constant supports and encouragements. I love them so much, and I take the chance here to thank them from the bottom of my heart. My special thanks go to my brother and sister, my best friends in all my life. I love them dearly and thank them for all their invaluable support and inspiration. I am always grateful to my beloved husband. He has been a true and great supporter and has unconditionally loved me during all my good and bad moments. This dissertation would have not been possible without him. By all mean this acknowledgement would not be complete without thanking my little son for all happiness he has created in our life and also for his patience during completing this thesis. Thank you my sweet love. I would like to dedicate my dissertation work to my family.

Azam Seyedi Barcelona, October 2015

| AF | BSTR  | АСТ     | iv                                                                          |

|----|-------|---------|-----------------------------------------------------------------------------|

| A  | CKNC  | WLEI    | DGMENT vi                                                                   |

| CC | ONTE  | NTS     | viii                                                                        |

| LI | ST OF | F TABL  | ESxii                                                                       |

| LI | ST OF | F FIGUI | RES xiii                                                                    |

| 1. | Intro | duction |                                                                             |

|    | 1.1   | Overv   | iew2                                                                        |

|    | 1.2   | Proble  | m Statement and Thesis Contribution                                         |

|    |       | 1.2.1   | Circuit Design of a New L1 Data Cache to Improve Version<br>Management      |

|    |       | 1.2.2   | Two Circuit Power Management Solution to Improve Low Power<br>Cache Designs |

|    |       | 1.2.3   | <b>Circuit Design of a New L1 Data Cache to Improve Reliability</b> 6       |

|    |       | 1.2.4   | NEM Based CAM Cell Designed for Highly Efficient TLBs7                      |

|    | 1.3   | Thesis  | Outline                                                                     |

| 2. |       |         | ESIGN OF A DUAL-VERSIONING L1 DATA CACHE FOR OPTIMISTIC                     |

|    | 2.1   | Introd  | uction 10                                                                   |

|    | 2.2   | dvSRA   | AM design details11                                                         |

|    |       | 2.2.1   | Dual-versioning cell design                                                 |

|    |       | 2.2.2   | dvSRAM array structure design                                               |

|    |       |         | 2.2.2.1 Brief description of the whole array structure                      |

|    |       |         | 2.2.2.2 Middle part of the array 16                                         |

|    |       |         | 2.2.2.3 Sub-array structure description                                     |

|    |       |         | 2.2.2.4 Data and address signals distribution                               |

|    |       | 2.2.3   | Design methodology and analysis                                             |

|    |       | 2.2.4   | Reconfigurability: RDC execution modes                                      |

## CONTENTS

|    |       |          | 2.2.4.1    | General purpose mode (64KB)                           | 29 |

|----|-------|----------|------------|-------------------------------------------------------|----|

|    |       |          | 2.2.4.2    | TM mode (32KB)                                        | 30 |

|    | 2.3   | Use ca   | ises       |                                                       | 33 |

|    |       | 2.3.1    | Specula    | tive multithreading (SpMT)                            | 33 |

|    |       | 2.3.2    | Specula    | tive lock elision (SLE)                               | 33 |

|    |       | 2.3.3    | Transac    | tional memory (TM)                                    | 33 |

|    |       | 2.3.4    | Results:   | transactional memory                                  | 34 |

|    | 2.4   | Relate   | d work     |                                                       | 35 |

|    | 2.5   | Summ     | ary        |                                                       | 37 |

| 3. | Nov   | el SRA   | M BIAS     | CONTROL CIRCUITS FOR A LOW POWER L1 DATA CACHE.       | 39 |

|    | 3.1   | Introd   | uction     |                                                       | 39 |

|    | 3.2   | Backg    | round: av  | vailable techniques to reduce cache power consumption | 40 |

|    | 3.3   | The pr   | oposed b   | ias control circuits                                  | 42 |

|    |       | 3.3.1    | DB-Cor     | ntrol Circuit                                         | 42 |

|    |       | 3.3.2    | SAB-Co     | ontrol Circuit                                        | 44 |

|    | 3.4   | Analy    | sis of the | DVSRAM L1 data cache                                  | 44 |

|    |       | 3.4.1    | Profiling  | g dvSRAM Components Activation                        | 44 |

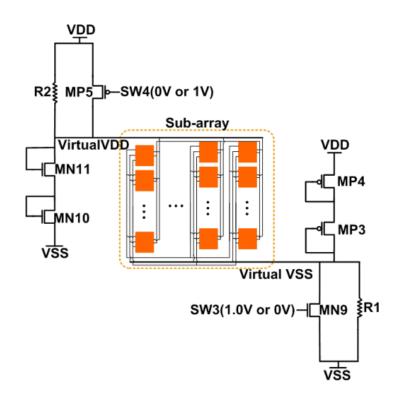

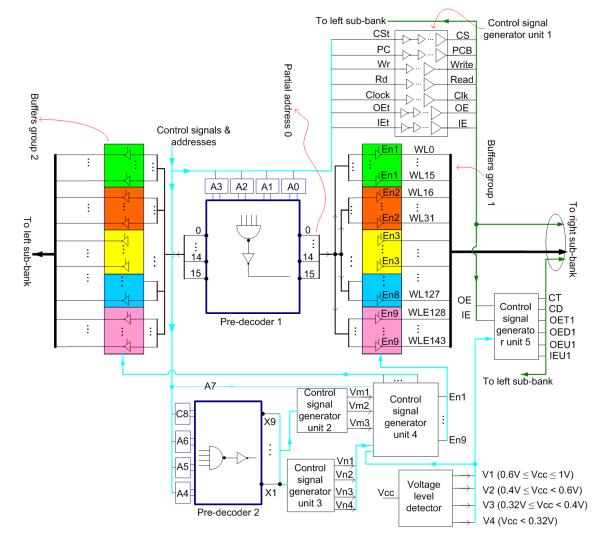

|    | 3.5   | DVSR     | AM-D a     | rray structure design                                 | 47 |

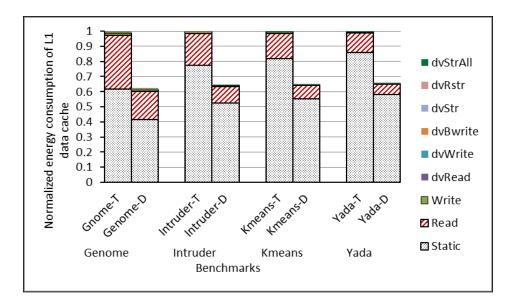

|    | 3.6   | Evalua   | ation      |                                                       | 48 |

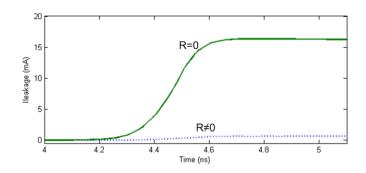

|    | 3.7   | Instab   | ility prob | lems of un-accessed cells                             | 51 |

|    | 3.8   | Summ     | ary        |                                                       | 52 |

| 4. | Circu | iit Desi | gn of a N  | ovel Adaptable and Reliable L1 Data Cache             | 54 |

|    | 4.1   | Introd   | uction     |                                                       | 54 |

|    | 4.2   | Backg    | round and  | d Related Work                                        | 56 |

|    |       | 4.2.1    | Memory     | y Failures                                            | 57 |

|    |       |          | 4.2.1.1    | Persistent Failures                                   | 57 |

|    |       |          | 4.2.1.2    | Non-Persistent Failures                               | 58 |

|    |     | 4.2.2  | Related Work                                                       | 58 |

|----|-----|--------|--------------------------------------------------------------------|----|

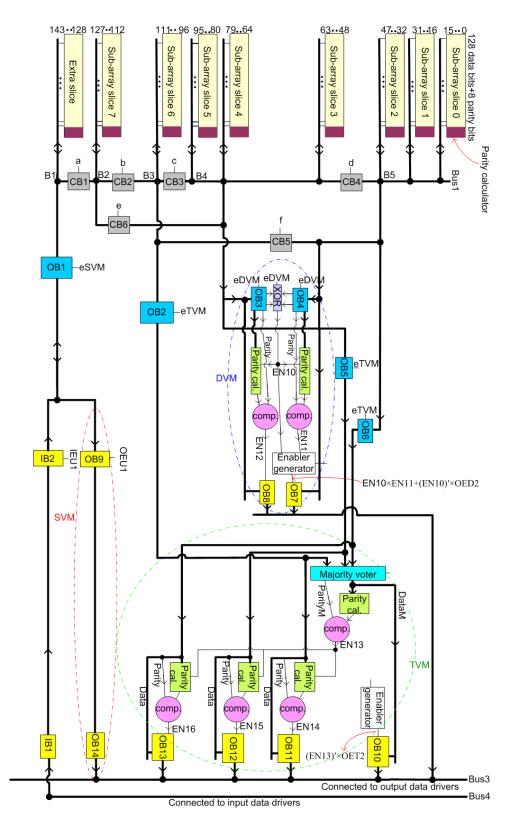

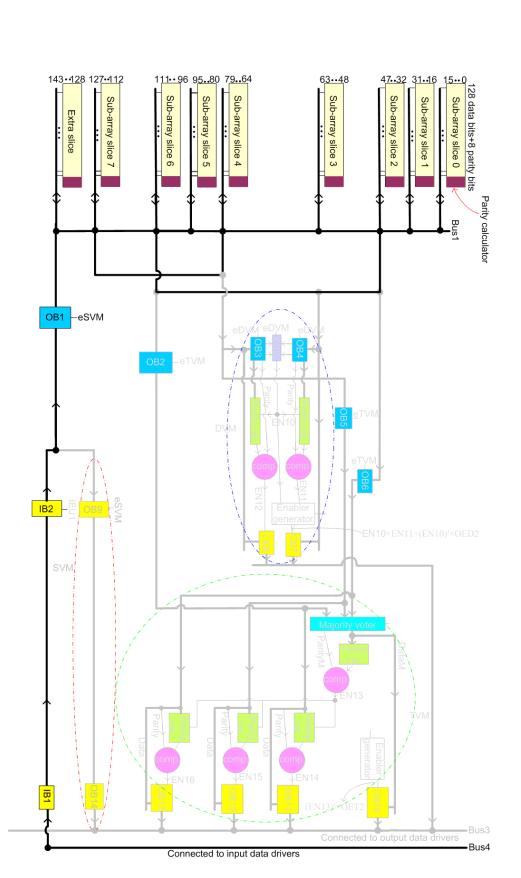

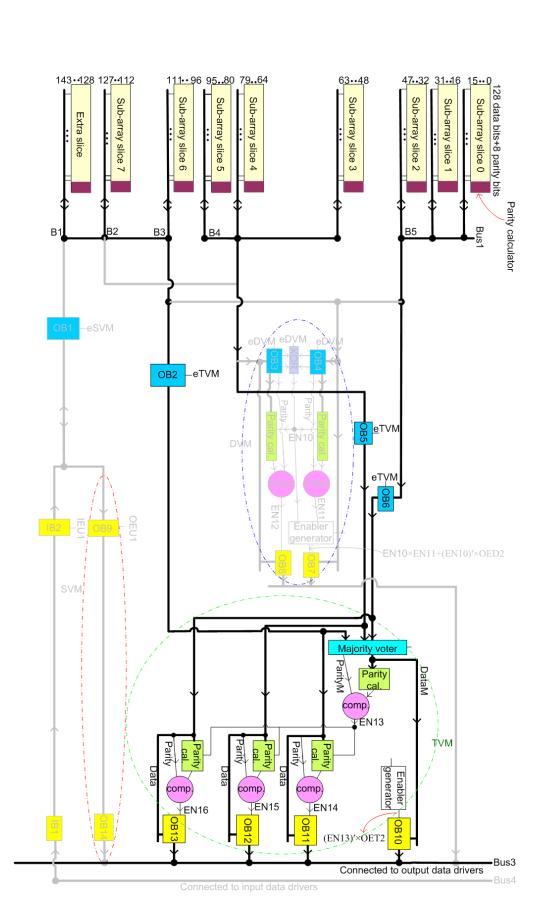

|    | 4.3 | Archit | ecture of Flexicache                                               | 60 |

|    | 4.4 | Circui | t Design of Flexicache                                             | 63 |

|    |     | 4.4.1  | Block Diagram of Flexicache                                        | 63 |

|    |     | 4.4.2  | Circuit Details of Each Flexicache Sub-Array                       | 65 |

|    |     | 4.4.3  | Circuit Details in SVM                                             | 68 |

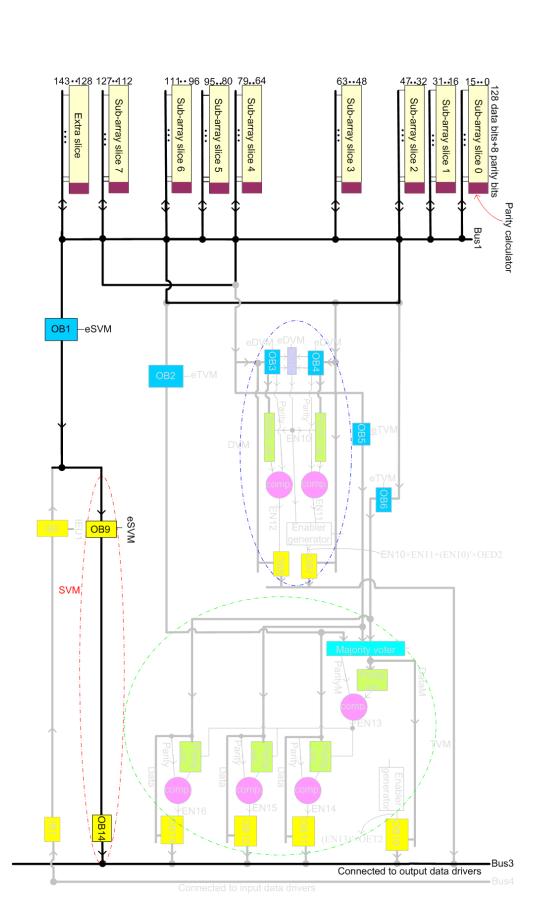

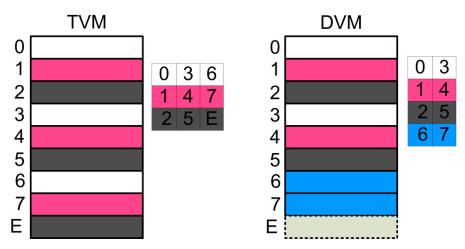

|    |     | 4.4.4  | Circuit Details in DVM                                             | 71 |

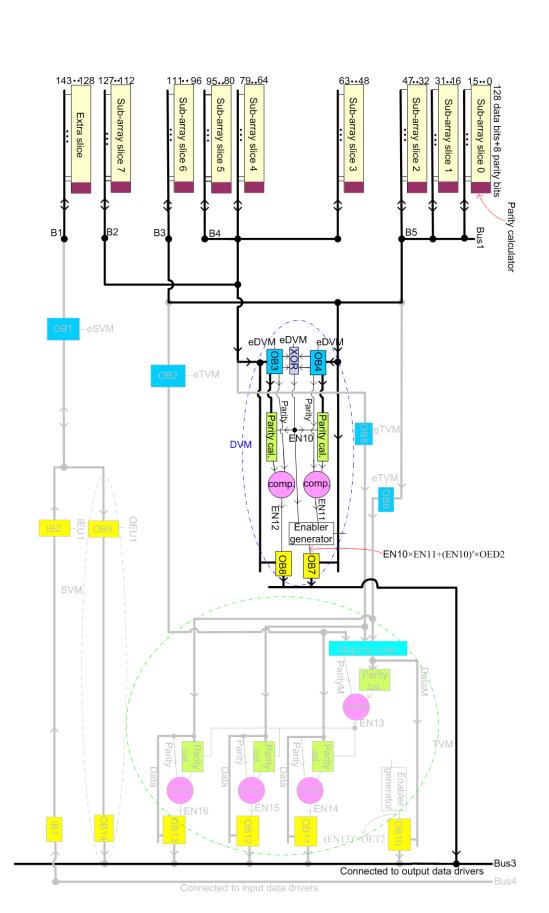

|    |     | 4.4.5  | Circuit Details in TVM                                             | 73 |

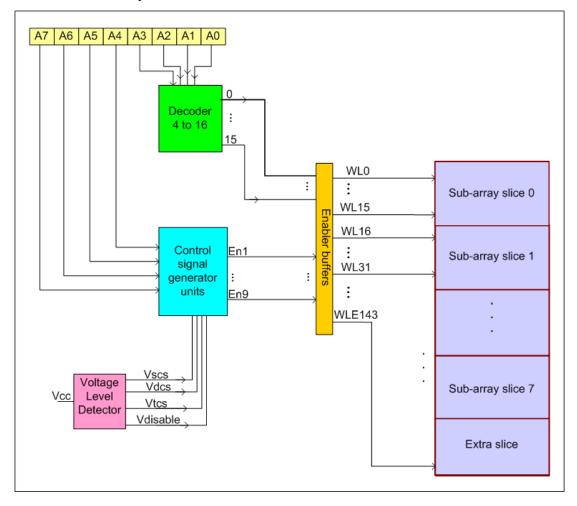

|    | 4.5 | Addre  | ss Decoder Circuits of Flexicache                                  | 76 |

|    |     | 4.5.1  | Abstract View of the Address Decoder                               | 76 |

|    |     | 4.5.2  | Details of the Decoder Circuits of Flexicache                      | 77 |

|    | 4.6 | Switch | ning Between Modes                                                 | 81 |

|    | 4.7 | Metho  | dology and Evaluation                                              | 82 |

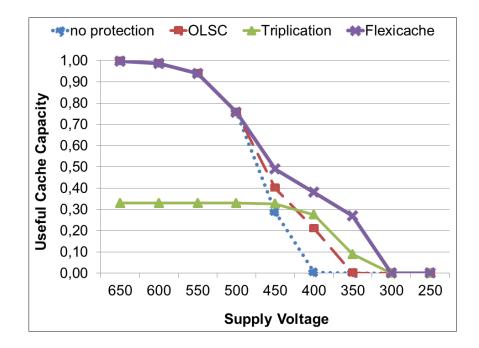

|    |     | 4.7.1  | Useful Cache Capacity                                              | 83 |

|    |     | 4.7.2  | Error Correction Latency                                           | 84 |

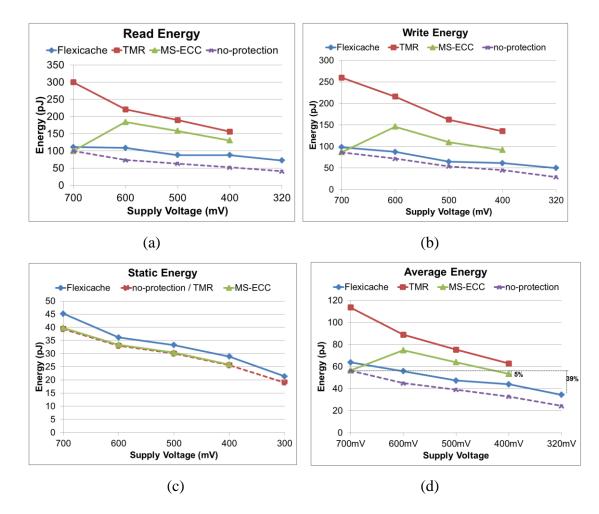

|    |     | 4.7.3  | Energy Reduction                                                   | 85 |

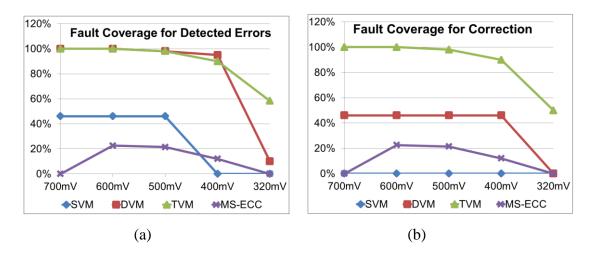

|    |     | 4.7.4  | Reliability Against Particle Strike                                | 87 |

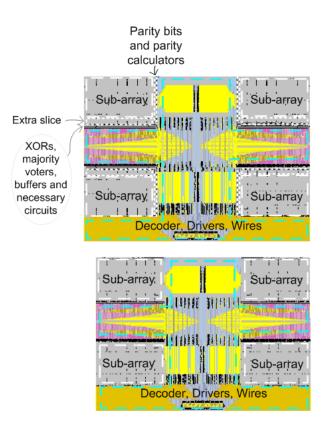

|    |     | 4.7.5  | Area Overhead                                                      | 88 |

|    | 4.8 | Conclu | usion                                                              | 89 |

| 5. |     |        | Cell based on Nano-Electro-Mechanical Switch and CMOS for Hi<br>Bs |    |

|    | 5.1 | Introd | uction                                                             | 91 |

|    | 5.2 | Backg  | round                                                              | 93 |

|    |     | 5.2.1  | Emerging technologies                                              | 93 |

|    |     | 5.2.2  | NEM Switches                                                       | 95 |

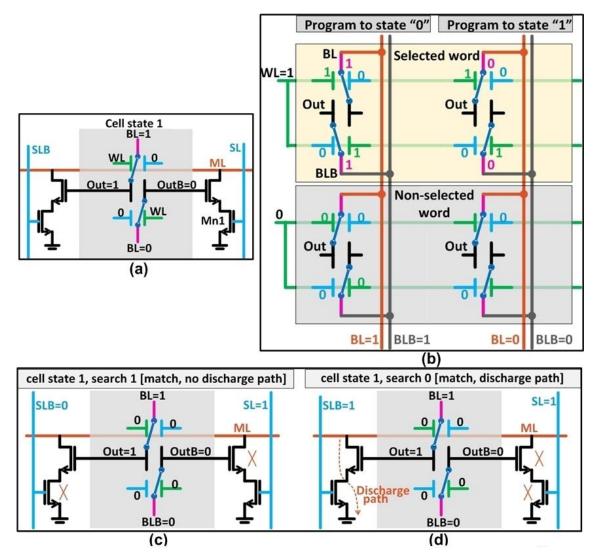

|    |     | 5.2.3  | Non-volatile NEM switches                                          | 98 |

|    |     | 5.2.4  | Memory arrays based on NEM switches                                | 98 |

|    |     | 5.2.5  | Configuration elements based on NEM switches                       | 98 |

|    |     |        |                                                                    |    |

|    |        | 5.2.6    | Content    | Addressable Memory                  | 98  |

|----|--------|----------|------------|-------------------------------------|-----|

|    |        | 5.2.7    | Translat   | ion Lookaside Buffer                | 100 |

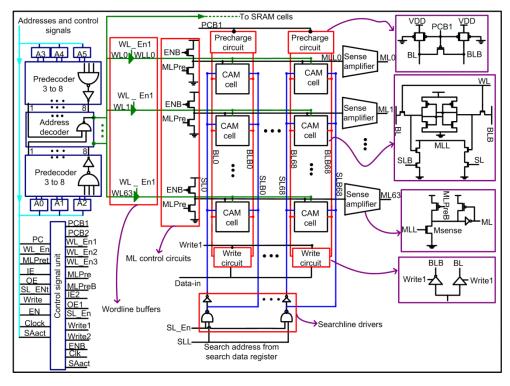

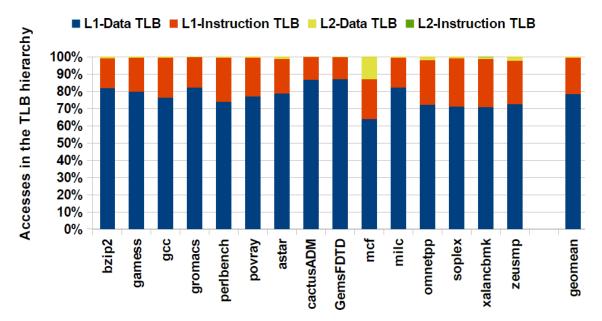

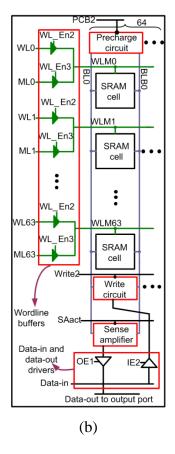

|    |        |          | 5.2.7.1    | The Circuit Design of CMOS-only TLB | 102 |

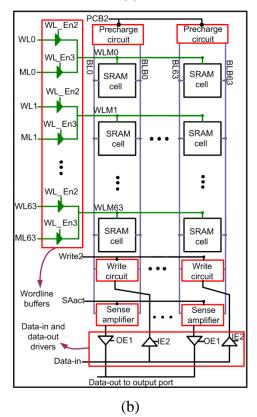

|    | 5.3    | Design   | n of NEM   | IsCAM Cell                          | 102 |

|    |        | 5.3.1    | Circuit    | Operations                          | 104 |

|    |        |          | 5.3.1.1    | Write Biasing Scheme                | 104 |

|    |        |          | 5.3.1.2    | Search operation                    | 104 |

|    |        | 5.3.2    | Cell Are   | chitecture                          | 105 |

|    | 5.4    | A Use    | Case for   | NEMsCAM: TLB                        | 106 |

|    |        | 5.4.1    | Motivat    | ion                                 | 106 |

|    |        | 5.4.2    | Design     |                                     | 108 |

|    |        |          | 5.4.2.1    | Search Operation                    | 109 |

|    |        |          | 5.4.2.2    | Write Operation                     | 110 |

|    | 5.5    | Experi   | imental E  | valuation                           | 110 |

|    |        | 5.5.1    | Method     | ology                               | 110 |

|    |        | 5.5.2    | Results    |                                     | 111 |

|    |        |          | 5.5.2.1    | Energy & Area                       | 111 |

|    |        |          | 5.5.2.2    | Latency                             | 112 |

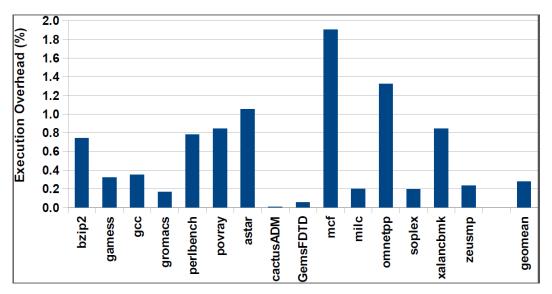

|    |        |          | 5.5.2.3    | System                              | 113 |

|    | 5.6    | Relate   | d Work .   |                                     | 114 |

|    | 5.7    | Summ     | ary        |                                     | 115 |

| 6. | Conc   | lusion   | and futur  | e work                              | 117 |

|    | 6.1    | Conclu   | usion      |                                     | 117 |

|    | 6.2    | Future   | Work       |                                     | 119 |

| Th | e cont | ent of t | his thesis | led to following publications:      | 122 |

| 7. | Refe   | rences:  | ••••••     |                                     | 123 |

## LIST OF TABLES

| Table 2.1: Brief description of the dvSRAM cell operations.    13                         |

|-------------------------------------------------------------------------------------------|

| Table 2.2: Typical SRAM and dvSRAM energy consumption and access time per                 |

| operation for VDD=1V and T=25°                                                            |

| Table 2.3: The average number of each operation for all tested applications of the        |

| STAMP benchmark suite (gnome, intruder, kmeans and yada)                                  |

| Table 3.1: Number of each dvSRAM operation for tested applications of STAMP               |

| benchmark suite (Genome, Intruder, Kmeans, Yada) for one core                             |

| Table 3.2: Activated parts of a dvSRAM cell for each operation                            |

| Table 3.3: The probability of access to each part of dvSRAM cells for tested applications |

| of the STAMP benchmark suite at each execution time                                       |

| Table 3.4: Energy consumption per operation for dvSRAM-T & dvSRAM-D                       |

| Table 4.1: Comparison of Flexicache with Architecture Based Error Correction Schemes      |

| for Scaling Vcc (Bold is better)                                                          |

| Table 4.2: Logical truth tables to generate word-line addresses and enablers              |

| Table 4.3: The area overhead and latency presented by encoders and decoders in            |

| Flexicache and OLSC                                                                       |

| Table 5.1: Traditional and emerging memory technologies characteristics [106], [95]94     |

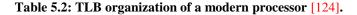

| Table 5.2: TLB organization of a modern processor [124].    107                           |

| Table 5.3: Energy consumption for search, write operations and standby mode and           |

| normalized area footprint111                                                              |

## LIST OF FIGURES

| Figure 2.1: Circuit schematic of the proposed dvSRAM cell: a main cell with a               |

|---------------------------------------------------------------------------------------------|

| secondary cell and exchange circuits                                                        |

| Figure 2.2: dvSRAM array with two sub-banks, one mat in each of them with four              |

| identical sub-arrays. Decoder and control signal generator units are in the middle          |

| part14                                                                                      |

| Figure 2.3: A view of one dvSRAM sub-bank and the middle part of array: four identical      |

| sub-arrays, each with 64 rows and 128 columns                                               |

| Figure 2.4: Middle part of dvSRAM array: address decoders, control signal units, and        |

| tri-state buffers. Boolean functions: $dvStr = abc$ , $dvRstr = abc$ , $WL\_En1 = abc + bc$ |

| $\mathbf{abc}$ , WL_En2 = $\mathbf{abc}$ + $\mathbf{abc}$ , dvStrAll = $\mathbf{abc}$       |

| Figure 2.5: The structure of one sub-array                                                  |

| Figure 2.6: The distribution of address and data drivers in a sub-array. The equivalent     |

| resistance and capacitance of each wire is shown in lumped model. Each triangle in          |

| the driver groups is representing eight drivers (two series inverters)                      |

| Figure 2.7: Normalized dvSRAM energy consumption per operation for three supply             |

| voltages, 1V, 0.9V and 0.8V and T=110°C (Normalized based on maximum value,                 |

| i.e., energy consumption for strAll when VDD=1V)                                            |

| Figure 2.8: Normalized dvSRAM access time per operation for three supply voltages,          |

| 1V, 0.9V and 0.8V and T=110°C (Normalized based on maximum value, i.e.,                     |

| access time for strAll when Vdd=0.8V)                                                       |

| Figure 2.9: Normalized dvSRAM energy consumption per operation for all process              |

| corners and T=110°C (Normalized based on maximum value, i.e., energy                        |

| consumption for strAll in FF process corner)                                                |

| Figure 2.10: Normalized dvSRAM access time per operation for all process corners and        |

| T=110°C (Normalized based on maximum value, i.e., access time for strAll in FS              |

| process corner)                                                                             |

| Figure 2.11: Typical SRAM (top) and dvSRAM (bottom) layouts. Showing one sub-               |

| bank and address decoders                                                                   |

| Figure 3.6: The leakage current passes through the transistors MNS1 and MNS2 when              |

|------------------------------------------------------------------------------------------------|

| exchange circuits are un-accessed for R1=0 and R1 $\neq$ 0                                     |

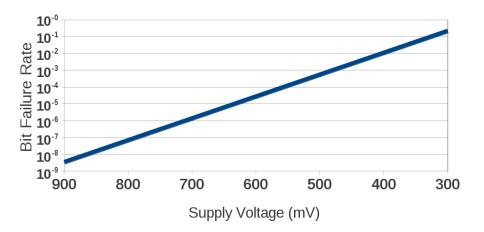

| Figure 4.1: Bit Failure Rate vs Supply Voltage                                                 |

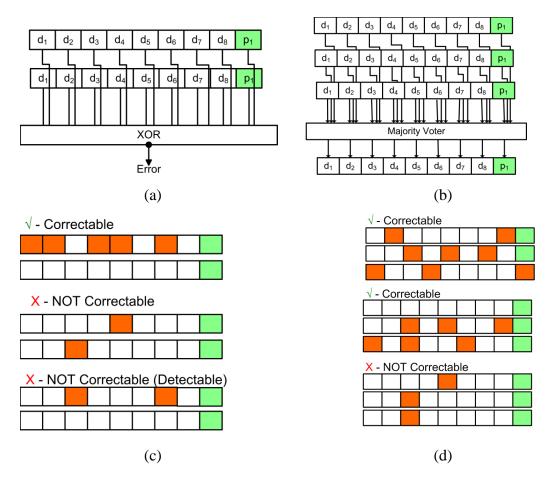

| Figure 4.2: The figure presents the behavior of Flexicache for DVM (a), and TVM (b)            |

| for 8-bit partitions. Also, it presents examples for correctable and non-correctable           |

| faults (c and d)                                                                               |

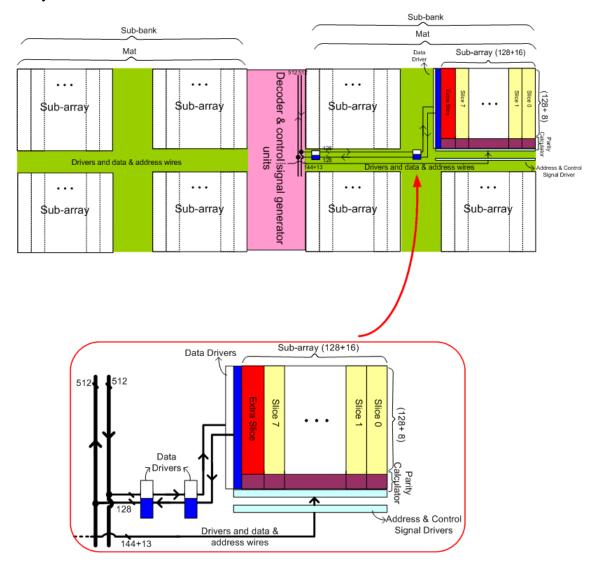

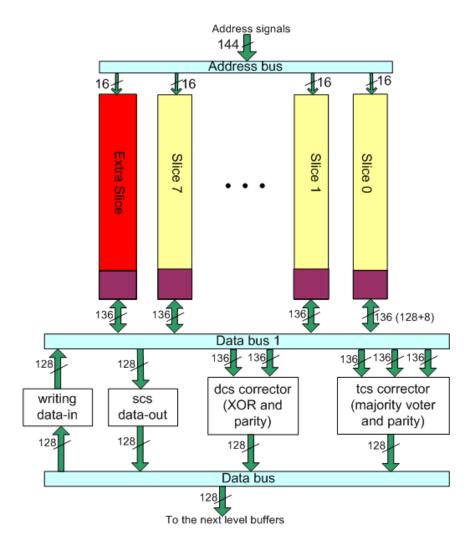

| Figure 4.3: Flexicache block diagram                                                           |

| Figure 4.4: The figure presents the main components of Flexicache such as buses and            |

| decoder                                                                                        |

| Figure 4.5: Sub-array block diagram; sub-arrays are much bigger but for clarity we show        |

| like that                                                                                      |

| Figure 4.6: Sub-array block diagram during a write access in SVM mode                          |

| Figure 4.7: Sub-array block diagram during a read access in SVM mode70                         |

| Figure 4.8: Sub-array block diagram in DVM mode72                                              |

| Figure 4.9: Sub-array block diagram in TVM mode75                                              |

| Figure 4.10: Abstract view of the address decoder of Flexicache76                              |

| Figure 4.11: Necessary decoders and control signal generators78                                |

| Figure 4.12: Related equations which are necessary to generate word-line addresses and         |

| enablers                                                                                       |

| Figure 4.13: Slices activated at a time in DVM and TVM                                         |

| Figure 4.14: Useful cache capacity provided by Flexicache after disabling uncorrectable        |

| lines under this bit failure rate                                                              |

| Figure 4.15: Energy reduction in cache operations                                              |

| Figure 4.16: Non-persistent fault injection                                                    |

| Figure 4.17: The figure shows the layout of a sub-bank and address decoder of                  |

| Flexicache (top) and a typical cache (down)                                                    |

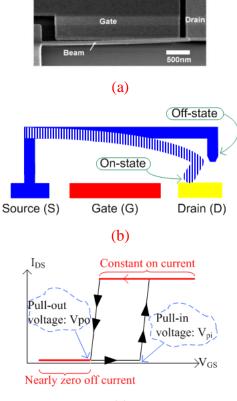

| Figure 5.1: (a) SEM image of three-terminal NEM relay [110]. (b) Schematic of a 3T             |

| NEM relay consisting of source, gate, and drain; a cantilever beam connected to the            |

| source. The beam collapses to the drain when $V_{GS} \ge V_{pi}$ and is released when $V_{GS}$ |

| <v<sub>po (c) Typical I<sub>DS</sub>-V<sub>GS</sub> characteristics of 3T NEM array96</v<sub>  |

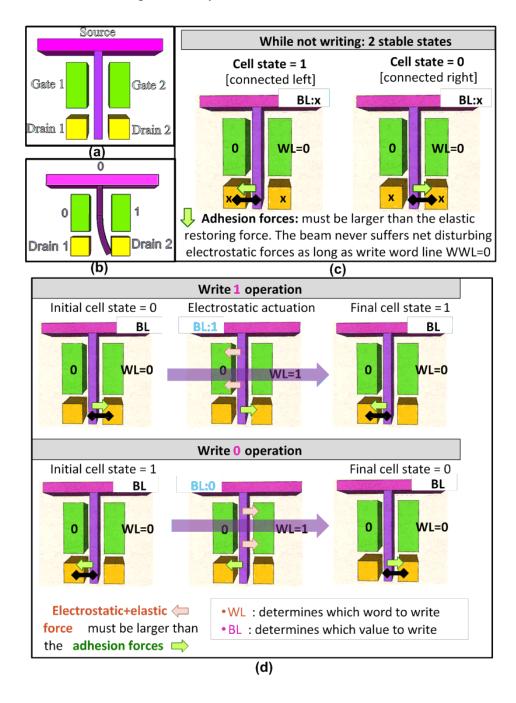

| Figure 5.2: (a) Schematic of a 5T NEM switch. (b) VGS1 (VGate1- VSource) is 0 and        |

|------------------------------------------------------------------------------------------|

| VGS2 is 1, so the beam collapses to Drain2. (c) The non-volatile NEM assumed in          |

| this work has two stable states. (d) Biasing scheme used for writing the non-volatile    |

| NEM switching. WL selects the cells for writing, while the BL determines the value       |

| that will be written                                                                     |

| Figure 5.3: (a) Typical 10-T NOR type CAM cell, (b) Typical 9T NAND type CAM             |

| [94]                                                                                     |

| Figure 5.4: Simplified view of a full associative translation look aside buffer 100      |

| Figure 5.5: The circuit details of a typical (a) CAM and (b) RAM architecture in a TLB   |

| structure                                                                                |

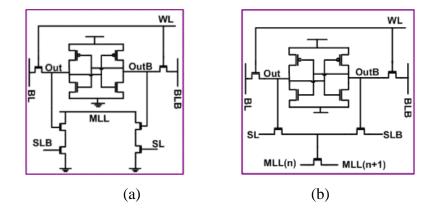

| Figure 5.6: (a) Schematic of the proposed NEMsCAM cell. (b) NEMsCAM storage              |

| array organization and writing scheme. (c) When the NEMsCAM cell content                 |

| matches the value being searched, there is no discharge path through the cell. (d) In    |

| case of a mismatch, the cell tries to discharge the match line ML 103                    |

| Figure 5.7: (a) Schematic of our NEM memory cell. (b) Simplified switch model of         |

| NEM memory cell (c) A simple NEM Verilog-A model between BL (source), Out                |

| (drain) and WL nodes [93] 104                                                            |

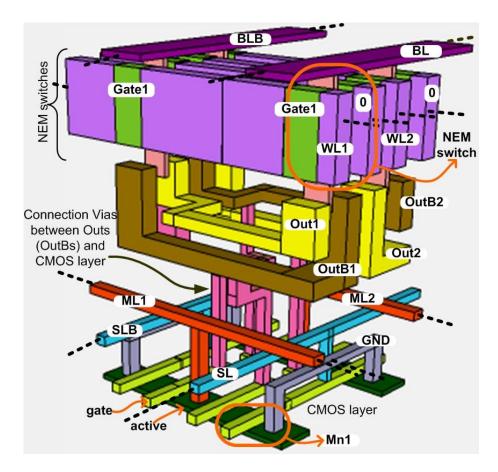

| Figure 5.8: Three-dimensional view of two adjacent NEMsCAM cells in a CAM array.         |

|                                                                                          |

| Figure 5.9: Breakdown of accesses in the TLB hierarchy                                   |

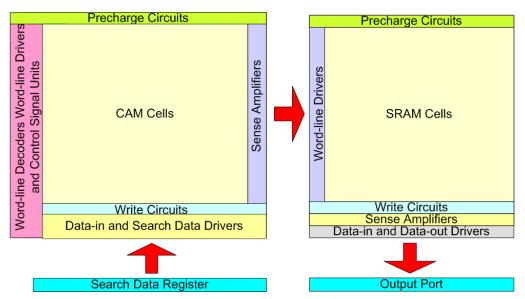

| Figure 5.10 (a)                                                                          |

| Figure 5.11: The circuit detail of (a) the proposed NEM-CMOS CAM and (b) a typical       |

| SRAM architecture in the proposed TLB structure                                          |

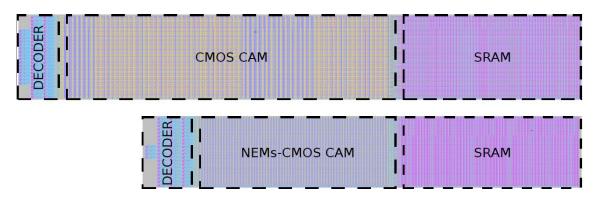

| Figure 5.12: Layout of the DTLB implemented with CMOS-only CAM cells (top), and          |

| NEM-based CAM cells (bottom)112                                                          |

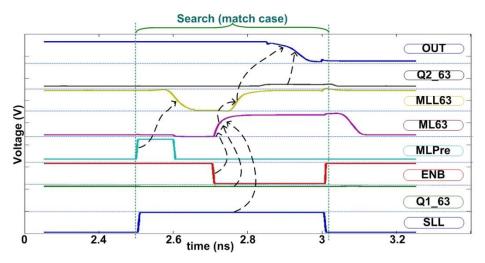

| Figure 5.13: Simulation waveform of matching state for the first cell at the last row of |

| the NEMsCAM DTLB 112                                                                     |

| Figure 5.14: Dynamic energy consumption of the CMOS-only and the NEMsCAM                 |

| DTLB and ITLB 113                                                                        |

| Figure 5.15: Execution time overhead due to NEMsCAM TLBs                                 |

**CHAPTER 1**

**INTRODUCTION**

#### 1.1 Overview

Increasing the number of transistors over the last decades has led to a considerable performance improvement especially for monolithic single-core processors [1]. This was primarily achieved by aggressive technology scaling resulting in doubling of device density and performance doubling every 18 months commensurate with Moore's law [2]. However in the late 1990's, power-density problems [3] and the difficulty of eking out more performance from complex out of order single core architectures forced the processor manufacturers to do a right-hand turn and introduce chip multiprocessors (CMP) as a solution. Each processor core in these CMPs was relatively simpler, and the increased number of cores provided increased total performance with decreased powerdensity. However, the same problems of energy-efficiency wall and performance wall have resurfaced with further scaling; exacerbate by the problem of reliability. Hence, industry has been forced to look for novel solutions on a wide variety of aspects from architecture to circuit levels targeting higher performance and efficiency. Motivated by these efforts we try to hit the walls in this thesis and propose some novel circuit designs based on the state of the art techniques to improve the performance, reliability and reduce the energy consumption.

Among computer components we concentrate on the design of two critical structures, cache memories and TLBs. Cache memories improve the processor performance by reducing the average time to access to the main memory. Caches are usually organized as a hierarchy of different levels (level-one, level-two, etc.), and whenever the processor requests the access to the main memory, they are first checked to see whether a copy of that data is there. If so, the processor directly writes to or reads from the cache, which is much faster than accessing to the main memory. If the memory location is not found in the cache, the cache allocates a new entry and copies data from the main memory. Then the processor request is executed. Based on these observations, caches especially first-level ones are activated at each main memory request so considering cache structure in power consumption, reliability and speed point of view are critical for designing future microprocessors. TLBs are also one of our research directions in this thesis. Translation

Lookaside Buffer (TLB) is a cache that is employed to accelerate virtual-to-physical address translation [4]. The processor searches the TLB on every memory operation using the virtual page number. Hence, The TLB is a crucial component for the performance and power consumption of the computers [4]. Based on mentioned discussion, we investigate on these two important components and propose improved level-one caches and TLBs in this thesis:

1- To satisfy the power consumption problem, computer architects have focused on designs that integrate several processing cores on a single chip. However, there are new challenges for designers to design parallel programing methodologies and tackle with multi-core hardware architecture which motivate us in this thesis for considering one of the state of the art mechanisms, transactional memory, in circuit level to greatly improve the performance. Transactional Memory (TM) [5], [6] has been introduced as a promising paradigm to provide acceptable parallel performance and simple parallel code. TM system tackles with two important key aspects: version management and conflict detection. Version management schemes try to apply the mechanisms in which the system can read and modify both old and new version of same logical data during transactional execution. In this thesis, we introduce the circuit design of such hardware mechanism which simplifies data versioning management and improves the performance considerably.

2- In this thesis, we also pay attention to power consumption increase in cache memories when they become bigger and more complicated. Cache optimization is vital from two points of view: first, nowadays caches occupy a major part of each core; therefore, cache memory optimization techniques are necessary to increase the performance and reduce the total power consumption [7]. Second, during each cache access only few lines are active and other lines only consume energy to keep the stored data which causes extra energy consumption. Therefore, in this thesis we propose some power management methods to manage the energy consumption during each cache access.

3- Beside power and performance issues which we investigate in this thesis, reliability is the other design constraint which we concern. Reducing the supply voltage in microarchitectures and caches is an effective technique for reducing the overall power consumption but at the cost of performance. However, the reliability of this technique is limited by a considerable increase in the number of cell failures especially in on-chip memories [8], [9]. In this thesis, we propose an effective mechanism for level-one caches which provides the highest reliability during the supply voltage reduction.

4- Scaling of available technologies challenges with serious problems that occur due to leakage currents and reliability issues [10], and prevents manufacturers from fabricating smaller devices. In order to maintain the ability to scale circuits, various non-CMOS technologies (emerging technologies) have been employed and become a good replacement for volatile and non-volatile memories. In this thesis, we focus on one of those emerging technologies called NEMs (Nano-Electro-Mechanical switches). We design a CAM (Content Addressable Memory) cell based on NEM and CMOS technologies and employ it to design a power hungry component like TLBs (Translation Lookaside Buffers).

#### **1.2 Problem Statement and Thesis Contribution**

#### **1.2.1** Circuit Design of a New L1 Data Cache to Improve Version Management

Transactional Memory (TM) [5] potentially simplifies parallel programming by providing atomicity and isolation for executed transactions. In this thesis, we focus on Hardware TM (HTM) implementations [11], [12], where version management implementation is a key aspect to obtain good performance. Traditional version management schemes, eager or lazy, fail to efficiently handle two versions, old and new, of the same logical data. An efficient version management scheme should be able to read and modify both versions during transactional execution using a fast hardware mechanism. Furthermore, this hardware mechanism should be flexible enough to work with two versions of the same logical data efficiently. We introduce the circuit design of such a hardware mechanism.

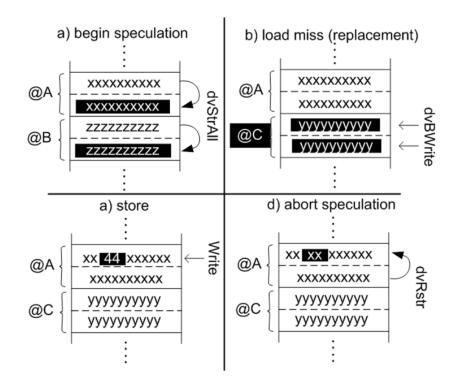

<u>In the second chapter of this thesis</u>, we propose a novel L1 data cache design with dual versioning SRAM cells (dvSRAM) for chip multi-processors (CMP) that implements optimistic concurrency proposals. In this new cache architecture, each dvSRAM cell has

two cells, a main cell and a secondary cell, which keep two versions of the same data, the new value and the old value. These values can be accessed, modified, moved back and forth between the main and secondary cells within the access time of the cache using special operations supported by the cell.

We design and simulate a dual-versioning L1 data cache, which we describe in detail as well as the supported operations that allow to efficiently solving existing version management problems. We also introduce three well-known use cases that make use of optimistic concurrency execution and that can benefit from our proposed design. Our experiments show that large speedups can be achieved with acceptable overall energy dissipation.

Also, we introduce a reconfigurable L1 data cache architecture that has two execution modes: a general purpose mode and a TM mode that is able to manage efficiently two versions of the same logical data. The latter allows handling old and new transactional values within the cache simultaneously when executing transactional workloads. We explain in detail the architectural design of this Reconfigurable Data Cache (RDC), as well as the supported operations that allow to efficiently solving existing version management problems. We also evaluate the area and energy effects of our proposal, and we find that RDC designs are more energy-delay efficient compared to baseline HTM systems, with negligible area impact on modern processors.

## **1.2.2** Two Circuit Power Management Solution to Improve Low Power Cache Designs

On-die caches already occupy more than 50% of the total chip area in recent designs and it will continue to grow as technology scales [7]. Since the leakage current depends on the total number of the on-chip transistors, the proportion of caches in the overall leakage current is large and will continue to do so in future designs. Therefore, leakage current management is an unavoidable approach in total power consumption control in nowadays microprocessors [13].

During each cache access only few cache lines become active and other unselected ones consume energy to retain their data properly. To alleviate this problem, some techniques

have been proposed to put infrequently accessed cache lines into low power standby mode. Besides that, a technique has been broadly called drowsy mode technique put the inactive cache lines into a low leakage state while retain their data properly [14], [15].

In the third chapter of this thesis, we propose two novel circuits to manage the power consumption of inactive cache cells in data retention mode. Both circuits have lower power consumption and area overheads when compared to previous proposals. The first proposed circuit (Dynamic Bias Control circuit or DB-Control circuit) dynamically tracks the reference current and sets the bias voltage of cells, while the second (Self-Adjust Bias Control circuit or SAB-Control circuit) has a self-adjust property to set the bias voltages and also alleviates the instability problems that appear due to noise injection.

Although any SRAM array can benefit from these circuits, to show their usefulness, we frame the study on our dvSRAM cache where leakage current has more effect on power dissipation and circuit instability. Therefore, we add the proposed bias control circuits to a dvSRAM cache and simulate and optimize the entire cache. The simulations demonstrate the effectiveness of our proposed circuits to considerably reduce the energy consumption of dvSRAM L1 data cache compared to the typical dvSRAM cache. This is achieved with a negligible area increase per sub-array and negligible delay overhead. We also show that instability problems are alleviated by using our second proposed circuit.

#### **1.2.3** Circuit Design of a New L1 Data Cache to Improve Reliability

A very effective approach in reducing the energy consumption is to reduce the supply voltage (Vcc) close to the transistor's threshold. However, the energy reduction in the low-power mode comes with a drastic increase in the number of memory cell failures especially in large memory structures such as on-chip SRAM memories (such as L1 and L2 caches) [8], [9]. This motivates us to design a cache which is resilient to large number of cell failures and operates at lower supply voltages.

In the fourth chapter of this thesis, we propose a flexible and reliable L1 data cache design (Flexicache) with the unique capability of automatically adapting itself for different supply voltage levels and providing the highest reliability. Depending on the

supply voltage level, Flexicache defines three operating modes: (1) Single Version Mode (SVM), (2) Double Version Mode (DVM) or (3) Triple Version Mode (TVM). In high supply voltages, Flexicache operates in SVM and provides reliability through single-bit parity. In middle range of supply voltages DVM is used: Flexicache writes data to two separate cache-lines simultaneously in order to use one line for error recovery when the other line is faulty. In near threshold supply voltages, Flexicache operates in TVM and writes data to three separate cache-lines simultaneously in order to our experimental results, the energy is reduced and latency as well as cache capacity usage is improved compared to typical previous proposals: Triple Modular Redundancy (TMR) (conventional triplication) and OLSC [16], [17].

#### 1.2.4 NEM Based CAM Cell Designed for Highly Efficient TLBs

Among emerging technologies, Nano-electro-mechanical (NEM) switches have been considered as a promising memory technology providing some very appealing characteristics, such as near-zero leakage current and infinite subthreshold slope and non-volatility. However, in spite of their specific characteristics, they have an important constraint: finite write endurance. Therefore, we get benefits from NEM technologies whenever endurance is not a critical issue, e.g. for processor structures that are mostly read-only.

In the fifth chapter of this thesis, we propose a novel Content Addressable Memory (CAM) cell, NEMsCAM, based on both NEMs and CMOS technologies, to employ in processor structures where writes are relatively infrequent, for example the Translation Look-aside Buffers (TLB). The memory component of the proposed CAM cell is designed with two complementary non-volatile NEM switches (two 5-Terminal NEMs) and located on top of the CMOS-based comparison component. As a use case of the NEMsCAM cell, we design and simulate level-one data and instruction TLBs. The simulations show that the NEMsCAM TLB considerably reduces the energy consumption per search operation, write operation and standby mode and the area usage compared to a CMOS-only TLB with minimal performance overhead.

#### **1.3 Thesis Outline**

Chapter 2 introduces a level-one dvSRAM data cache as well as its design details, simulation results and evaluation. Also, the design details of the other version of our proposed L1 data cache, Reconfigurable Data Cache (RDC) will be presented in this chapter. Chapter 3 depicts the design details as well as simulation results of two novel circuits which have the ability to manage the power consumption of unselected cache lines in drowsy mode. Chapter 4 presents the circuit design and the evaluation results of a L1 cache design (Flexicache) which can automatically adapt itself for different supply voltage levels to provide the highest possible reliability. Chapter 5 introduces a novel 3-Dimensional Content Addressable Memory cell (NEMsCAM) designed based on both NEMs and CMOS technologies which is used in processor structures like TLBs where writes are relatively infrequent. Finally, chapter 6 concludes this dissertation.

**CHAPTER 2**

CIRCUIT DESIGN OF A DUAL VERSIONING L1 DATA CACHE FOR OPTIMISTIC CONCURRENCY PROPOSALS

#### **2.1 Introduction**

In recent decades, industry has benefited immensely from remarkable progress in chip multiprocessor designs to mitigate power consumption issues. Furthermore, various novel architecture implementations such as speculative multithreading [18], lock elision [19], and hardware transactional memory [6] have been proposed to get more performance offered by these multi-core chips. All of these proposals leverage optimistic concurrency, by assuming that conflicting data accesses will not occur; in case a conflict occurs, all tentative data updates have to be undone. Thus, multiple versions of the same data have to be maintained by the L1 data cache. However, the circuit design of such a cache which supports all these different proposals had not been proposed. In this thesis chapter, we propose a cache, called dual-versioning L1 data cache (dvSRAM) which keeps multiple versions of the same data and supports all mentioned proposals [20], [21].

The main characteristic of the dvSRAM cache is the inclusion of two cells in each dvSRAM cell, main cell and secondary cell, which keep two versions of the same data. These two values can be accessed separately or simultaneously, modified and exchanged within the cache access time using defined operations supported by the cache. Exchange circuits are introduced to connect main cell and secondary cell to each other. When the exchange circuits are inactive, the main cell and secondary cell are isolated from each other.

In Section 2.2 we explain a detailed circuit design of a 32KB dual-versioning SRAM (dvSRAM) L1 data cache, a four-way set associative cache, with 64B data lines, two clock cycles access time and 45nm Predictive Technology Model [22] at 2GHz processor frequency. We propose a complete description of the internal structure of each array and details of all its components, such as address decoders, control signal generator units, data and word-line buffers, sub-array cells, and necessary peripheral circuitries. We simulate both the dvSRAM and a typical SRAM array with HSPICE 2003.03, design the layouts [23], and calculate dynamic and static energy consumptions and access times

for all the operations and all process corners. Also we show that with a few modifications, the dvSRAM array can be presented as a Reconfigurable Data Cache (RDC) which provides two execution modes, a general purpose mode and optimistic concurrency mode.

In Section 2.3 we discuss how the aforementioned optimistic concurrency based systems can benefit from the efficient dual-versioning provided by dvSRAM. Moreover, we evaluate one of the systems using state-of-the-art baseline and benchmarking suite and show that significant speedups are achieved with acceptable overall energy consumption overhead. In Section 2.4 we discuss the related works, and finally we summarize the chapter in Section 2.5.

#### 2.2 dvSRAM design details

In this section, we start with dvSRAM cell design. We describe the cell circuit, and we introduce the available operations of the dvSRAM array structure. Then we describe the different blocks that form the dvSRAM array structure in detail.

#### 2.2.1 Dual-versioning cell design

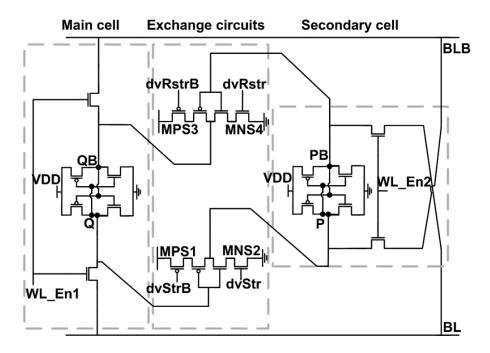

Figure 2.1 depicts the structure of our proposed dvSRAM cell, which is composed of two typical 6T SRAM cells [24]: the main cell and the secondary cell. These two cells are connected via two tri-state inverters [24]; we call them exchange circuits which are two inverters coupled with two pairs of nMOS and pMOS transistors. The main and secondary cells of one dvSRAM cell keep different versions of the same data. The only time they are not isolated is when the exchange circuits are active, and the data of the main cell is stored to the secondary cell, or the data of the secondary cell is restored to the main cell. When the signals dvRstr and dvStr are low, and the exchange circuits are not active, there is more than one off transistor in the nMOS or pMOS stacks in the exchange circuits, which leads to a significant reduction in the subthershold leakage current that flows through them (stacking effect [25], [26], [27]).

In Table 2.1, we briefly explain dvSRAM cell operations. Read and Write act like read and write operations in a typical SRAM cell. Other operations are created based on our

Figure 2.1: Circuit schematic of the proposed dvSRAM cell: a main cell with a secondary cell and exchange circuits.

goal in this chapter. When dvStr is high, transistors MPS1 and MNS2 are turned on, and the exchange circuit acts as an inverter by inverting Q to P. The secondary cell which is formed by two back to back inverters keeps the value of P when dvStr is low, and it inverts P to PB, so that PB has the same value as Q. Similarly, when dvRstr is high, PB in the secondary cell is inverted to QB and converted to Q, so that previously saved data in the secondary cell can be recovered. Note that dvStr operation acts just for a line; when we need to store all the cells to their secondary cells simultaneously, we use dvStrAll operation. We use dvRead to read the data from the secondary cell and dvWrite to write to the secondary cell. Finally, we use dvBWrite to write to both main and secondary cells simultaneously. In Section 2.2.2.2, we describe how these signals are generated.

Main and secondary cells have similar sizes for each dvSRAM cell; BL is connected to Q and PB and BLB is connected to QB and P via pass gate transistors for symmetric behavior. Transistor sizing is an important point in dvSRAM cell design because two SRAM cells retain two different data values. An update to one of the cells should not lead to any changes in the preserved data value of the other cell, so the leakage current

| Operation | Description                                                                              |

|-----------|------------------------------------------------------------------------------------------|

| Write     | Writing to a main cell by activating WL_En1                                              |

| Read      | Reading from a main cell by activating WL_En1                                            |

| dvWrite   | Writing to the secondary cell by activating WL_En2                                       |

| dvRead    | Reading from the secondary cell by activating WL_En2                                     |

| dvStr     | ~Q $\rightarrow$ P: Storing the main cell to the secondary cell by activating dvStr      |

| dvRstr    | ~PB $\rightarrow$ QB: Restoring the secondary cell to the main cell by activating dvRstr |

| dvBWrite  | Writing to both cells simultaneously by activating WL_En1 and WL_En2                     |

| dvStrAll  | Storing all main cells to their secondary cells simultaneously                           |

#### Table 2.1: Brief description of the dvSRAM cell operations.

of the exchange circuits should be as low as possible in order to avoid data values to change due to leakage current (We describe a new design in the next chapter to reduce the leakage current and the instability problem).

#### 2.2.2 dvSRAM array structure design

In this subsection, we describe the high-level organization of the dvSRAM array, considering each part of its structure.

#### **2.2.2.1** Brief description of the whole array structure

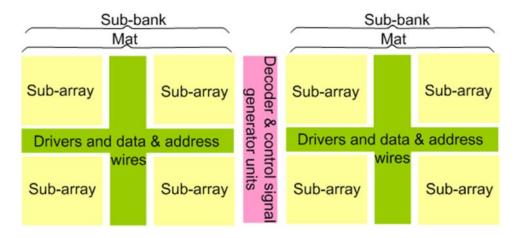

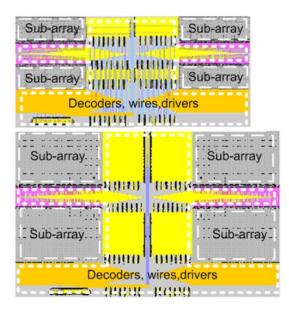

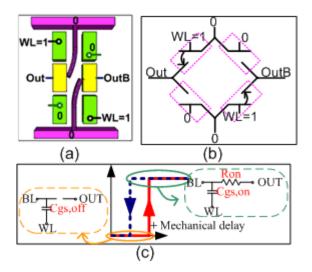

An appropriate cache modeling tool that chooses the optimal number of sub-banks, size and orientation is Cacti [28]. We use Cacti to determine the optimal number and size of dvSRAM array components and find the cache architecture with optimal access time and power consumption. For the L1 data cache configuration we assume 32KB, four way, 64 byte lines, two clock cycles access time; and we use the 45nm Predictive Technology Model [22]. For one bank array, Cacti suggests two identical sub-banks, one mat for each sub-bank and four identical sub-arrays in each mat as can be seen in Figure 2.2

Figure 2.2: dvSRAM array with two sub-banks, one mat in each of them with four identical subarrays. Decoder and control signal generator units are in the middle part.

[29]. The number of sub-banks and mats in each sub-bank are the most important results we exploit from the Cacti suggestions ( $N_{sub-banks} = \frac{N_{db1}}{2}$ ,  $N_{mats-in-sub-banks} = \frac{N_{dw1}}{2}$  [28]). The address decoder and control signal generator units are placed in the middle part of the array and necessary drivers and data and address wires in middle part of each sub-bank.

Figure 2.3 shows the complete description of one sub-bank of the dvSRAM array and the middle part, decoder and control signal generator units. Our sub-bank design is based on Cacti suggestions and SRAM configurations that Wang et al. [30] proposed. dvSRAM array parts names come from Cacti suggested names for more clarity and simplicity.

Considering the cache structure of our system, i.e., 32KB size, 64B lines and four-way set associativity, we need seven address bits to address a line in the array, so these seven bits and the necessary control signal bits which we describe later, enter to the left side of Figure 2.3 where the control signal generator units and address decoders can be seen. A complete description of middle part of the array is presented later in Section 2.2.2.2.

During an access, only one of the two sub-banks is activated; hence the numbers of bits that deal with decoder and produce word-line addresses are six; so 64 word-line

Figure 2.3: A view of one dvSRAM sub-bank and the middle part of array: four identical subarrays, each with 64 rows and 128 columns.

addresses and 12 control signals for both sub-banks are generated there in middle part of the array and enter to the sub-bank from the left side as can be seen in Figure 2.3. 512 data-in and 512 data-out bits are routed from the up side of the sub-bank.

As mentioned before, each mat has 4 identical sub-arrays; all of them are activated during an access; therefore each sub-array holds a part of the cache line, so 128 of the 512 data bits (64B) are distributed to each sub-array. The bottom sub-arrays are mirror

images of the top sub-arrays and the left hand side sub-arrays are mirror images of the right hand side ones. The word-line address signals enter the upper sub-arrays through their lower sides and the lower sub-arrays through their upper sides. The data-in and data-out signals enter to the left side of the right sub-arrays and right side of the left sub-arrays. Each sub-array is composed of data-in, data-out and word-line address buffers, a 2D matrix of memory cells and associated peripheral circuitry as explained in Section 2.2.2.3.

We put necessary optimized drivers (chain of two series inverters) in paths to reach their related loads in the sub-arrays. 512 data-in wires enter to up side of each sub-bank. They are divided into four groups of 128 data-in wires, each for one sub-array. For the 128 data-in wires of each sub-array, there are three levels of stage drivers in the path to reach their related sub-array; two stage drivers are in the path and the last one is connected to the sub-array. Each wire and its related drivers have the same color in Figure 2.3. The same method is used for data-out wires as can be seen in Figure 2.3. The upper part and lower part of the sub-array are symmetric.

64 address wires re-drive twice with two levels of stage drivers in their paths to reach each sub-array as can be seen in Figure 2.3. They re-drive with the first stage drivers and reach the second stage which is connected to each sub-array. The driver sizes are optimized to ensure that the access time for all sub-arrays is as equal as possible. As can be seen in Figure 2.3, we put necessary drivers for the 12 control signals as well, using the same method employed for the address wires.

There are two important points to consider when designing the dvSRAM array. First, the wire lengths for both data and addresses from the array edge to each sub-array should be as short as possible; and second, these wire lengths for all sub-arrays of each sub-bank should be as close as possible to each other.

#### 2.2.2.2 Middle part of the array

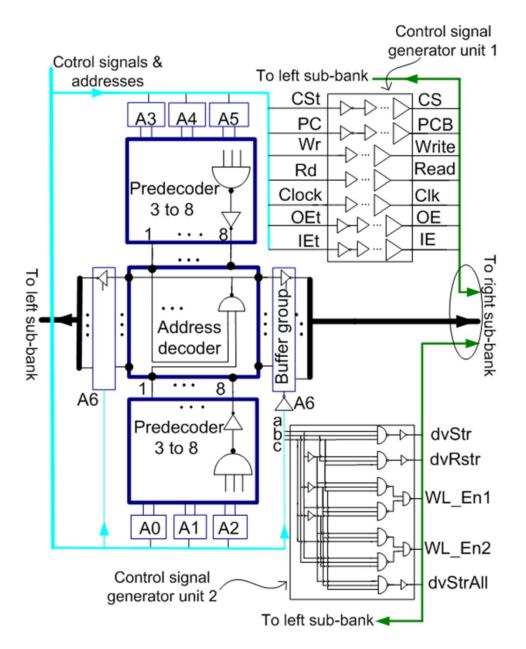

Figure 2.4 depicts the address decoder, control signal units, and tri-state buffers that reside in the center of the dvSRAM array. To generate 64 word-line addresses from six address bits, A0...A5, we design a two-level decoder similar to the design of Amrutur

[31]. Two 3-to-8 pre-decoders produce partially decoded products, and the main decoder generates 64 word-line addresses from their outputs. 64 word-line addresses are connected to both sub-banks via two tri-state buffer groups with enable signals. We use the highest value bit, A6 bit, as an enable signal to select the sub-bank which is activated during the access time; so when A6 is equal to 1, the left sub-bank is activated and when A6 is equal to 0 the right one is activated.

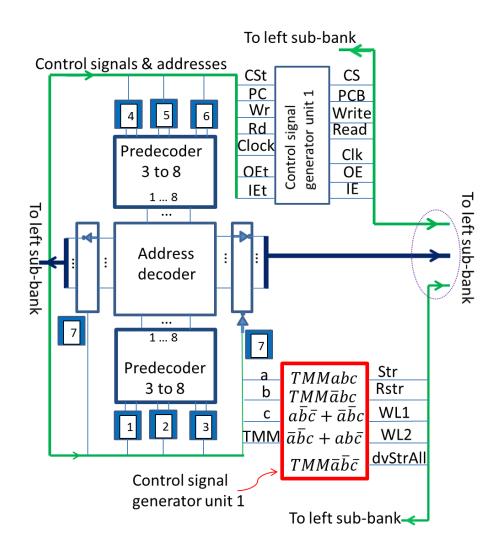

Figure 2.4: Middle part of dvSRAM array: address decoders, control signal units, and tri-state buffers. Boolean functions: dvStr = abc, dvRstr =  $\bar{a}bc$ , WL\_En1 =  $\bar{a}bc$ , WL\_En2 =  $\bar{a}bc$  + abc, dvStrAll =  $\bar{a}bc$ .

Control signal units are responsible to generate the necessary signals for executing the proposed operations and have a synchronous flow-thru SRAM. They use one external clock to time the operations of the dvSRAM array [32]. Control signal generator unit 1 consists of some optimized inverter chains that regulate the signals to control the

dvSRAM sub-array circuits such that main cell operations, typical read and write can be operated correctly. Control signal generator unit 2 is a 3-to-8 decoder, generating the necessary signals for optimistic concurrency proposals: dvStr, dvRstr, WL\_En1, WL\_En2 and dvStrAll according to its input signal levels, a, b and c.

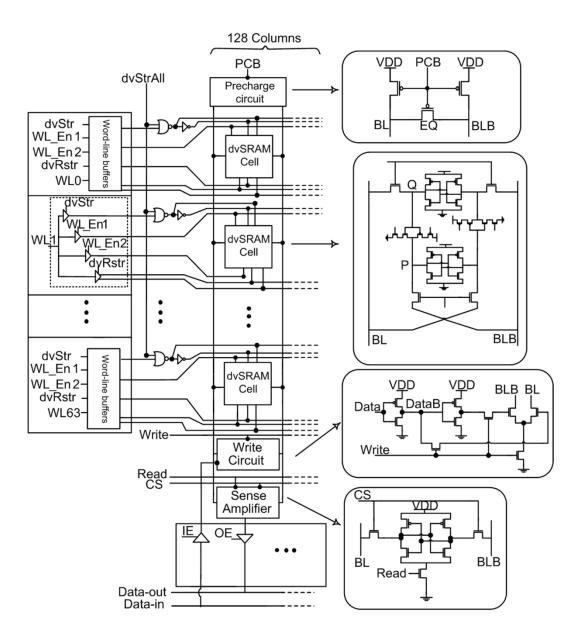

#### 2.2.2.3 Sub-array structure description

Figure 2.5 shows the structure of one sub-array that consists of 2D matrix of memory cells, data-in, data-out, word-line address buffers, and associated peripheral circuitry. On the left side of Figure 2.5, we can see the word-line address buffers and a set of NOR and inverter gates. As explained before, control signal generator unit 2 generates signals dvStr, WL\_En1, WL\_En2, and dvRstr to enable word-line address buffers. Each word-line address enters to its corresponding line via one of four buffers. For example, if we want to store the main cells of cache line 1 to their secondary cells, signals dvStr and WL1 are prepared in the control signal unit 2 and decoder and then the related buffer is activated. Control signal generator unit 2 also generates dvStrAll. When dvStrAll is activated, all the main cells of whole sub-array are stored to their secondary cells simultaneously. Data-in, data-out buffers are in the bottom part of the figure. They are typical data buffers that isolate a sub-array with interconnected wires and reduce injected noise effects.

We use typical precharge [33], [24], write circuits [34], and sense amplifiers [33], [24], [34]; the control signal generator unit 1 generates signals to control these circuits. Each column is connected to an individual sense amplifier. The precharge circuit keeps the bit-lines (BL and BLB) high when PCB is low. Both Read and dvRead are like read operation in typical SRAM arrays. After preparing the appropriate word-line address in decoder and the signal Read or dvRead in control signal generator units 1 and 2, the desired word-line is raised, turning on the pass transistors of related dvSRAM cells. Then, the bit-lines relative to the cell nodes that contain the value '0' begin discharging. At this time CS should be high and activates the related pass transistors to connect the sense amplifiers to the bit-lines. The sense amplifiers detect which of the bit-lines are discharging and hence read the stored values [34]. The outputs of sense amplifiers are

# Figure 2.5: The structure of one sub-array.

connected to their related output buffers. When OE is low, the data outputs are always tri-stated. When OE is high, they are active and the data can appear at the outputs.

Similar to a read operation, a write cycle is initiated by asserting WL. At this moment the IE is high and the data inputs can be transferred by the data input buffers to the write circuits. The write circuit is a differential stage which is driven by two Data and Write signals. The Data and DataB signals are passed through write buffers and feed the differential inputs. Two pass transistors and the current source for the differential amplifier is controlled by the Write signal. Then, the final values and their complements are loaded onto BL and BLB [34]. The circuit behavior for Write and dvWrite is similar. Two signals WL\_En1 and WL\_En2 are activated simultaneously for the dvBWrite operation and Data is stored to both main and secondary cells at the same time.

Similar to Thoziyoor et al.'s [28] implementation, a layer of multiplexing can be added, before output buffers, at the outputs of sense amplifiers to select the correct way in this 4-way set associative cache; but, for simplicity, we waive this option, and the signal CS (from control signal generator unit 1, from Figure 2.4) in the sense amplifiers selects the correct cache set. We show the simulation waveform of dvSRAM for all operations in Section 2.2.3.

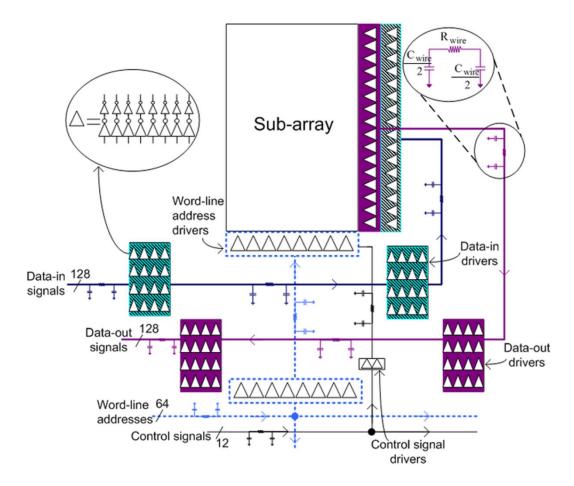

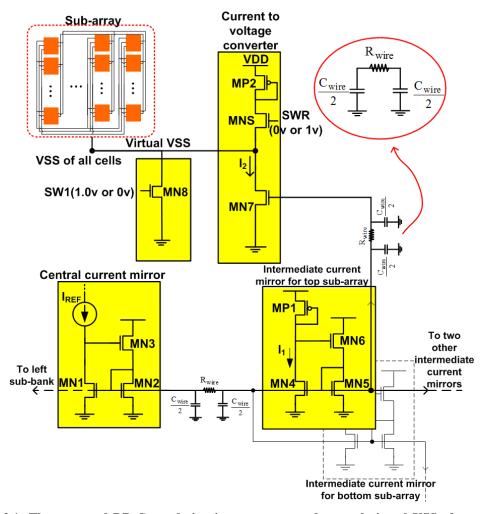

### 2.2.2.4 Data and address signals distribution

Figure 2.6 shows the distribution of address, data and control signals, the equivalent wire resistance and capacitance and necessary optimized drivers for one sub-array. As seen before, 64 lines of word-line addresses, 128 data-in, 128 data-out, and 12 control signal wires are routed to the sub-array from the left side of the figure. These are long wires with considerable RC delay constant and big propagation delay. For compensating the voltage drop, reflection effect and for driving big word-line capacitances, we divide the wires to shorter length and put drivers (two series inverters) at the end of each piece of wire.

As explained in Figure 2.3, for each 512 data-in (data-out) wires, we put two stages of drivers in the path to reach each sub-array and one driver just in the sub-array and for the 64 word-line addresses and 12 control signal wires, we put one stage of drivers in the path to reach each sub-array and one another driver just in the sub-array. We optimize the sizes of these drivers by considering resistance and capacitance of wire sections and sub-array circuit sizes.

Figure 2.6: The distribution of address and data drivers in a sub-array. The equivalent resistance and capacitance of each wire is shown in lumped model. Each triangle in the driver groups is representing eight drivers (two series inverters).

We can place the drivers of each stage in one line as Cacti suggests [28] but it leads to high area and un-optimized area floor-plan so we use an optimal allocation of each stage drivers that we explain as follows for both data-in and data-out wires: Instead of locating all the drivers (512 drivers) of one stage in one line, we divide them into four groups of 128 drivers (each group for one sub-array) and then we put these 128 drivers in four lines and rotate them 90 degree anti-clockwise as shown in Figure 2.6. Setting word-line address and control signal drivers is easier and we locate them in one line at each stage. In the figure, for simplicity, all related drivers and wires have same color.

## 2.2.3 Design methodology and analysis

We construct, for one array of dvSRAM and one array of a typical SRAM, HSPICE transistor level net-lists that include the complete decoder, control signal units, and two sub-banks with necessary drivers and equivalent capacitances and resistances of wires. The high level structure of a typical SRAM array is the same as of a dvSRAM array, but with 6T typical SRAM cells, related word-line address buffers and control signal generator units.

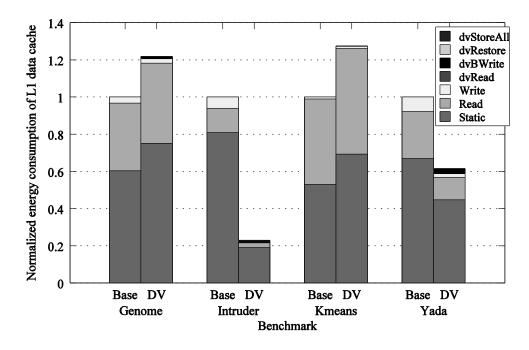

We simulate and optimize both the dvSRAM and typical SRAM array with HSPICE using 45nm Predictive Technology Model (High Performance) for VDD=1V, 2GHz processor clock frequency. We calculate the access time, dynamic energy and static energy per access for all operations in dvSRAM and SRAM and present them in Table 2.2. Our analysis indicates that our dvSRAM design meets, as the typical SRAM, the target access time requirement of two clock cycles and acceptable power and area increase. The energy consumption of dvStrAll is much higher than others but as we explain in Section 2.3.4, its effect in total energy consumption is negligible.

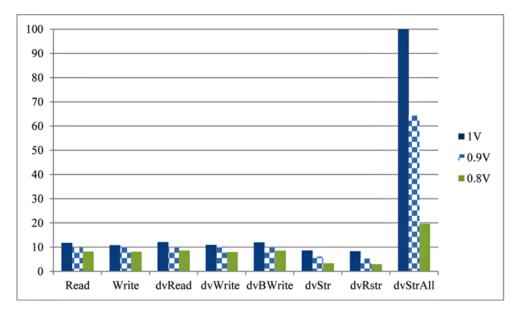

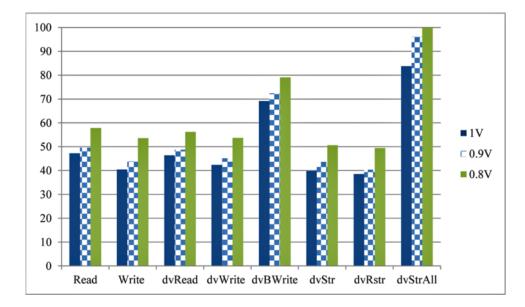

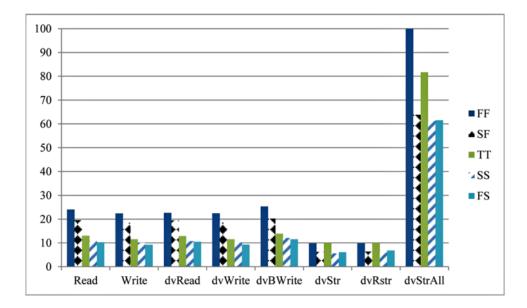

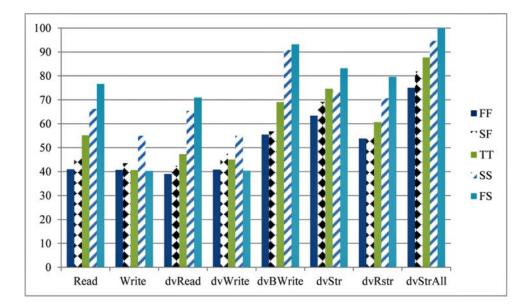

Moreover, we calculate dvSRAM energy consumption and access time per operation for three supply voltages, 1V, 0.9V and 0.8V for 45nm Predictive Technology Model and T=110°C and show the results in Figure 2.7 and Figure 2.8. In addition, we calculate dvSRAM energy consumption and access time per operation for all process corners using the 45nm Predictive Technology Model and T=110°C as can be seen in Figure 2.9 and Figure 2.10.

|           | Ener | ·gy (pJ) | Time (ps) |        |  |

|-----------|------|----------|-----------|--------|--|

| Operation | SRAM | dvSRAM   | SRAM      | dvSRAM |  |

| Read      | 90.4 | 112.4    | 496       | 604    |  |

| Write     | 80.2 | 99.3     | 736       | 838    |  |

| dvRead    | -    | 114.4    | -         | 576    |  |

| dvWrite   | -    | 101.1    | -         | 845    |  |

| dvBWrite  | -    | 122.6    | -         | 870    |  |

| dvStr     | -    | 114.9    | -         | 599    |  |

| dvRstr    | -    | 112.9    | -         | 545    |  |

| dvStrAll  | -    | 1123.2   | -         | 891    |  |

| Static    | 35.1 | 51.4     | -         | -      |  |

Table 2.2: Typical SRAM and dvSRAM energy consumption and access time per operation for VDD=1V and T= $25^{\circ}$ .

Figure 2.7: Normalized dvSRAM energy consumption per operation for three supply voltages, 1V, 0.9V and 0.8V and T=110°C (Normalized based on maximum value, i.e., energy consumption for strAll when VDD=1V).

Figure 2.8: Normalized dvSRAM access time per operation for three supply voltages, 1V, 0.9V and 0.8V and T=110°C (Normalized based on maximum value, i.e., access time for strAll when Vdd=0.8V).

Figure 2.9: Normalized dvSRAM energy consumption per operation for all process corners and T=110°C (Normalized based on maximum value, i.e., energy consumption for strAll in FF process corner).

Figure 2.10: Normalized dvSRAM access time per operation for all process corners and  $T=110^{\circ}C$  (Normalized based on maximum value, i.e., access time for strAll in FS process corner).

Figure 2.11 shows the layouts [23] of one sub-bank for both 32KB dvSRAM and the typical 32KB SRAM arrays. They include one sub-bank, address decoders, address and data wires, and the control signals. After adding PADs and I/O interfaces [35], the area increase of the dvSRAM compared to the typical SRAM is 46%. The area devoted to L1Ds in state-of-the-art CMPs is small compared to the entire die, for example, in Power7 [36] it is less than 1%, therefore the dvSRAM area overhead in die size is modest. With a few modifications, we present the dvSRAM array as a reconfigurable array which provides two execution modes, a general purpose mode and optimistic concurrency mode [37]. The general purpose mode allows for a 64KB cache and the optimistic concurrency mode for a 32KB cache with dual-versioning support. By using this technique, the area increase when comparing to a typical SRAM array of 64KB is 15.2%. We explain the design details in Section 2.2.4.

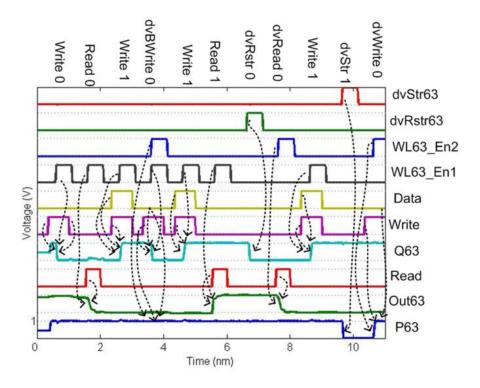

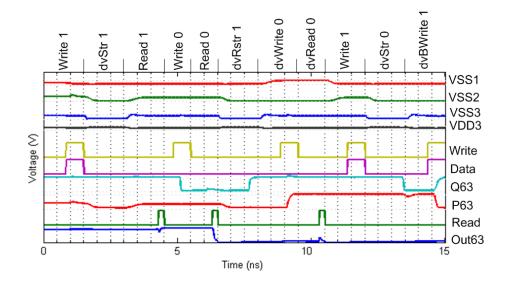

Figure 2.12 shows the simulation waveform for a sequence of eleven operations that take 11ns for the first cell at the last row of one sub-array. Q63, P63 and Out63 are internal nodes and dvStr63, dvRstr63, WL63\_En1 and WL63\_En2 are the outputs of the last

word-line address buffers. Signals PC, CS, CLK, OE, IE, a, b, c are omitted because their behaviors are similar to the related signals in a typical SRAM array [24].

Figure 2.11: Typical SRAM (top) and dvSRAM (bottom) layouts. Showing one sub-bank and address decoders.

Figure 2.12: The simulation waveform of dvSRAM array for a sequence of eleven operations for the first cell of the last row of one sub-array. The operations are shown on top.

### 2.2.4 Reconfigurability: RDC execution modes

As mentioned before, with a few modifications, we present the dvSRAM array as a Reconfigurable Data Cache (RDC) which provides two execution modes, a general purpose mode and an optimistic concurrency mode. We explain this structure in this section.

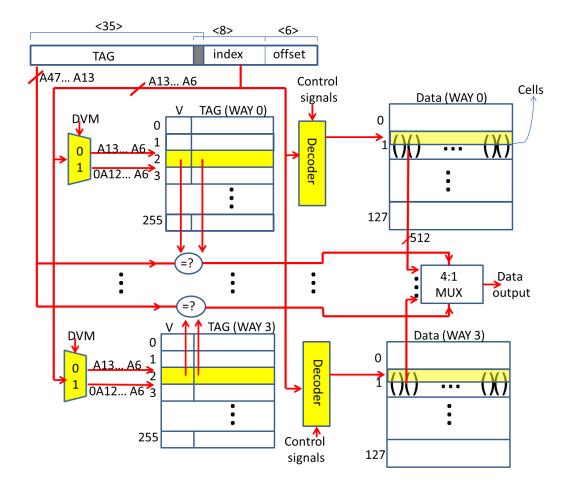

The reconfigurable L1 data cache provides two different execution modes. The execution mode is indicated by a signal named Transactional Memory Mode (TMM). If the TMM signal is not set, the cache behaves as a 64KB general purpose L1D cache; if the signal is set, it behaves as a 32KB cache with the capabilities to manage two versions of the same logical data. Figure 2.13 and Figure 2.14 show an architectural diagram of RDC, the decoder details and its associated signals, which change depending on the execution mode; the design assumes 48-bit addresses and a 4-way organization with 64-byte cache lines.

### 2.2.4.1 General purpose mode (64KB)

In this mode, the upper and lower bit-cells inside of a cell contain data from different cache lines. Therefore, a cache line stored in the upper cells belongs to cache set i in way j, while a cache line stored in the corresponding lower cells belongs to set i+1 in way j (i.e., consecutive sets in the same way). This mode uses the first four operations described in Table 2.1, to perform typical read and write operations as in any general purpose cache. Figure 2.13 shows an architectural diagram of the RDC. As can be seen in the figure, the most significant bit of the index is also used in the tags to support the 32KB TM mode with minimal architectural changes, so tags have fixed size for both modes (35 bits). The eight index bits (A13...A6) are used to access the tags (since TMM is not set) and also sent to the decoder. In Figure 2.14 it can be seen how the seven most significant bits of the index are used to address the cache entry while the least significant bit (A6) determines if the cache line is located in the upper or the lower cells, by activating WL1 or WL2 respectively.

### 2.2.4.2 TM mode (32KB)

In this mode, each data bit has two versions: old and new. Old values are kept in the lower cells and new values are kept in the upper cells. These values can be accessed, modified, and moved back and forth between the upper and lower cells within the access time of the cache using the operations in Table 2.1. To address 32KB of data, only half of the tag entries that are present in each way are necessary. For this reason, as can be seen in Figure 2.13, the most significant bit of the index is set to '0' when the TMM signal is active. So, only the top-half tag entries are used in this mode. Regarding the decoder (Figure 2.14), in this mode, the most significant bit of the index is discarded, and the rest of the bits are used to find the cache entry, while the signals a, b, and c select the appropriate signal(s) depending on the operation needed.

Figure 2.13: RDC architectural diagram: considering a 4-way RDC, with 64B cache-lines and 48b addresses.

|         | <u>۱</u> |

|---------|----------|

| 19      | ۱.       |

| ۱a      | ,        |

| · · · · | /        |

|                      | Address bits and control signals |    |    |     |     |     |     |   |    |   |     |

|----------------------|----------------------------------|----|----|-----|-----|-----|-----|---|----|---|-----|

| Execution Mode       | 1                                | 2  | 3  | 4   | 5   | 6   | 7   | а | b  | с | тмм |

| 64KB general purpose | A7                               | A8 | A9 | A10 | A11 | A12 | A13 | 1 | A6 | 0 | 0   |

| 32KB dual-versioning | A6                               | A7 | A8 | A9  | A10 | A11 | A12 | Х | Х  | Х | 1   |

(b)

Figure 2.14: (a) Decoder details and associated signals used for each execution mode. (b) Depending on the TMM signal, address bits and control signals for an execution mode are generated and passed to the decoder.

# 2.3 Use cases

In this section we discuss several use cases for the proposed dvSRAM. Moreover, a short evaluation for one of the use cases follows to show the impact of the dvSRAM.

### 2.3.1 Speculative multithreading (SpMT)