# Optimizing SIMD Execution in HW/SW Co-designed Processors

**Rakesh Kumar**

Department of Computer Architecture Universitat Politècnica de Catalunya

Advisors:

Alejandro Martínez Intel Barcelona Research Center Antonio González Intel Barcelona Research Center Universitat Politècnica de Catalunya

A thesis submitted in fulfillment of the requirements for the degree of

Doctor of Philosophy / Doctor per la UPC

#### ABSTRACT

SIMD accelerators are ubiquitous in microprocessors from different computing domains. Their high compute power and hardware simplicity improve overall performance in an energy efficient manner. Moreover, their replicated functional units and simple control mechanism make them amenable to scaling to higher vector lengths. However, code generation for these accelerators has been a challenge from the days of their inception. Compilers generate vector code conservatively to ensure correctness. As a result they lose significant vectorization opportunities and fail to extract maximum benefits out of SIMD accelerators.

This thesis proposes to vectorize the program binary at runtime in a speculative manner, in addition to the compile time static vectorization. There are different environments that support runtime profiling and optimization support required for dynamic vectorization, one of most prominent ones being: 1) Dynamic Binary Translators and Optimizers (DBTO) and 2) Hardware/Software (HW/SW) Co-designed Processors. HW/SW co-designed environment provides several advantages over DBTOs like transparent incorporations of new hardware features, binary compatibility, etc. Therefore, we use HW/SW co-designed environment to assess the potential of speculative dynamic vectorization.

Furthermore, we analyze vector code generation for wider vector units and find out that even though SIMD accelerators are amenable to scaling from hardware point of view, vector code generation at higher vector length is even more challenging. The two major factors impeding vectorization for wider SIMD units are: 1) Reduced dynamic instruction stream coverage for vectorization and 2) Large number of permutation instructions. To solve the first problem we propose Variable Length Vectorization that iteratively vectorizes for multiple vector lengths to improve dynamic instruction stream coverage. Secondly, to reduce the number of permutation instructions we propose Selective Writing that selectively writes to different parts of a vector register and avoids permutations.

Finally, we tackle the problem of leakage energy in SIMD accelerators. Since SIMD accelerators consume significant amount of real estate on the chip, they become the principle source of leakage if not utilized judiciously. Power gating is one of the most widely used techniques to reduce leakage energy of functional units. However, power gating has its own energy and performance overhead associated with it. We propose to selectively devectorize the vector code when higher SIMD lanes are used intermittently. This selective devectorization keeps the higher SIMD lanes idle and power gated for maximum duration. Therefore, resulting in overall leakage energy reduction. **Table of Contents**

| Abstra  | act                                                                                                                                                                                       | i      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| List of | f Figures                                                                                                                                                                                 | vii    |

| List of | f Tables                                                                                                                                                                                  | xi     |

| List of | f Algorithms                                                                                                                                                                              | xiii   |

| 1. Int  | troduction                                                                                                                                                                                | 1      |

|         | 1.1 SIMD Execution Model                                                                                                                                                                  | 2      |

|         | <ul> <li>1.2 Challenges in SIMD Execution</li></ul>                                                                                                                                       |        |

|         | <ul> <li>1.3 Contributions</li> <li>1.3.1 Speculative Dynamic Vectorization</li> <li>1.3.2 Vectorizing for Wider Vector Units</li> <li>1.3.3 Dynamic Selective Devectorization</li> </ul> | 5<br>6 |

|         | 1.4 HW/SW Co-designed Processors                                                                                                                                                          | 7      |

|         | 1.5 Why HW/SW Co-designed Environment                                                                                                                                                     | 7      |

|         | 1.6 Thesis Organization                                                                                                                                                                   | 8      |

| 2. Ba   | ckground                                                                                                                                                                                  |        |

|         | <ul> <li>2.1 Microarchitectural Innovations to Exploit Parallelism</li></ul>                                                                                                              |        |

|    | 2.2.3 ARM Neon                                                                                                                                                                                                                                                                                                                                                                                                              |                |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|    | 2.3 Code Generation for SIMD Accelerators<br>2.3.1 Traditional Compiler Vectorization                                                                                                                                                                                                                                                                                                                                       |                |

|    | 2.3.2 Superword Level Parallelism                                                                                                                                                                                                                                                                                                                                                                                           |                |

|    | 2.3.3 SLP in Presence of Control Flow                                                                                                                                                                                                                                                                                                                                                                                       |                |

|    | 2.3.4 Speculative Dynamic Vectorization                                                                                                                                                                                                                                                                                                                                                                                     | 24             |

|    | 2.3.5 Liquid SIMD                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|    | 2.3.6 Vapor SIMD                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|    | 2.4 Code Optimizations                                                                                                                                                                                                                                                                                                                                                                                                      |                |

|    | 2.4.1 Static Compiler Optimizations                                                                                                                                                                                                                                                                                                                                                                                         |                |

|    | 2.4.2 Dynamic Binary Optimizations                                                                                                                                                                                                                                                                                                                                                                                          |                |

|    | 2.4 Hardware/Software Co-designed Processors                                                                                                                                                                                                                                                                                                                                                                                |                |

|    | 2.4.1 Memory System in HW/SW Co-designed Processors                                                                                                                                                                                                                                                                                                                                                                         | 29             |

|    | 2.4.2 TOL translator/optimizer                                                                                                                                                                                                                                                                                                                                                                                              |                |

|    | 2.4.3 Hardware Support in HW/SW Co-designed Processors                                                                                                                                                                                                                                                                                                                                                                      |                |

|    | 2.4.4 Salient features of HW/SW Co-designed Processors                                                                                                                                                                                                                                                                                                                                                                      | 33             |

| 3. | Experimental Framework                                                                                                                                                                                                                                                                                                                                                                                                      | 35             |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

|    | 3.1 Main Components                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|    | <ul><li>3.1 Main Components</li><li>3.2 Execution Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                            |                |

|    | -                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

|    | 3.2 Execution Flow                                                                                                                                                                                                                                                                                                                                                                                                          | 37<br>39       |

|    | <ul><li>3.2 Execution Flow</li><li>3.3 Translation Optimization Layer</li></ul>                                                                                                                                                                                                                                                                                                                                             | 37<br>39<br>39 |

|    | <ul> <li>3.2 Execution Flow</li> <li>3.3 Translation Optimization Layer</li></ul>                                                                                                                                                                                                                                                                                                                                           |                |

|    | <ul> <li>3.2 Execution Flow</li> <li>3.3 Translation Optimization Layer</li></ul>                                                                                                                                                                                                                                                                                                                                           |                |

|    | <ul> <li>3.2 Execution Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       |                |

|    | <ul> <li>3.2 Execution Flow</li> <li>3.3 Translation Optimization Layer</li> <li>3.3.1 Interpretation</li> <li>3.3.2 Basic Block Translation</li> <li>3.3.3 Superblocks and Optimizations</li> <li>3.4 Speculation and Recovery</li> </ul>                                                                                                                                                                                  |                |

|    | <ul> <li>3.2 Execution Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       |                |

|    | <ul> <li>3.2 Execution Flow</li> <li>3.3 Translation Optimization Layer</li> <li>3.3.1 Interpretation</li> <li>3.3.2 Basic Block Translation</li> <li>3.3.3 Superblocks and Optimizations</li> <li>3.4 Speculation and Recovery</li> <li>3.5 The Timing Model</li> <li>3.6 TOL Configuration</li> <li>3.6.1 Optimal Promotion Threshold</li> <li>3.6.2 Optimized Code Distribution</li> <li>3.6.3 Emulation Cost</li> </ul> |                |

|    | <ul> <li>3.2 Execution Flow</li></ul>                                                                                                                                                                                                                                                                                                                                                                                       |                |

|    | 3.8.1 Power Modeling                                    | 57 |

|----|---------------------------------------------------------|----|

| 4. | Speculative Dynamic Vectorization                       | 59 |

|    | 4.1 Introduction                                        | 59 |

|    | 4.2 Motivation                                          | 61 |

|    | 4.3 Dynamic Vectorization Algorithm                     |    |

|    | 4.3.1 The Vectorizer                                    |    |

|    | 4.3.2 Avoiding Cyclic Dependences                       |    |

|    | 4.3.3 Static vs Dynamic Vectorization                   |    |

|    | 4.3.4 Working through an Example                        |    |

|    | 4.4 Performance Evaluation                              | 72 |

|    | 4.4.1 FP Dynamic Instruction Elimination                |    |

|    | 4.4.2 Dynamic FP Instruction Stream Distribution        | 74 |

|    | 4.4.3 Vectorization Overhead                            | 76 |

|    | 4.4.4 Effectiveness of Memory Speculation               |    |

|    | 4.4.5 Performance                                       | 77 |

|    | 4.5 Related Work                                        | 79 |

|    | 4.6 Conclusion                                          |    |

| 5. | Vectorizing for Wider Vector Units                      |    |

|    | 5.1 Introduction                                        | 81 |

|    | 5.2 Motivation                                          |    |

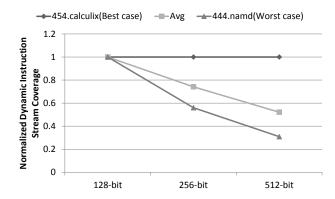

|    | 5.2.1 Reduced Dynamic Instruction Stream Coverage       |    |

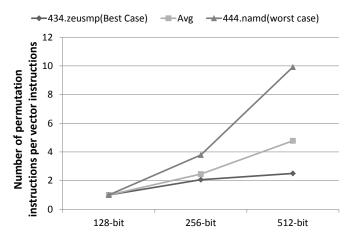

|    | 5.2.2 Number of Permutation Instructions                |    |

|    | 5.3 Variable Length Vectorization                       |    |

|    | 5.3.1 Code Generation                                   |    |

|    | 5.3.2 Hardware Requirements                             | 86 |

|    | 5.4 Selective Writing                                   |    |

|    | 5.4.1 Eliminating Permutation using Selective Writing   |    |

|    | 5.4.2 Reducing Permutation Instruction to Pack N Values |    |

|    | 5.5 Performance Evaluation                              |    |

|    | 5.5.1 Dynamic Instruction Stream Coverage               |    |

|    | 5.5.2 Permutation Reduction                             |    |

|    | 5.5.3 Putting Everything Together                       |    |

|    | 5.5.4 Performance                                       |    |

|    | 5.6 Related Work                           |

|----|--------------------------------------------|

|    | 5.7 Conclusion                             |

| 6. | Dynamic Selective Devectorization          |

|    | 6.1 Introduction                           |

|    | 6.2 Background and Related Work            |

|    | 6.3 Motivation                             |

|    | 6.4 Profiling and Devectorization104       |

|    | 6.4.1 Profiling                            |

|    | 6.4.2 Devectorization                      |

|    | 6.4.3 Reducing Devectorization Slowdown108 |

|    | 6.5 Performance Evaluation                 |

|    | 6.5.1 Baseline                             |

|    | 6.5.2 Models and Parameters                |

|    | 6.5.3 Higher SIMD Lane Usage Profile111    |

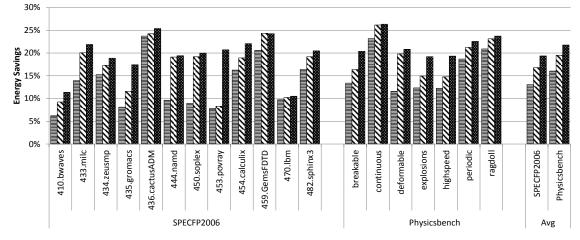

|    | 6.5.4 SIMD Accelerator Energy Savings      |

|    | 6.5.5 Overall Energy Savings               |

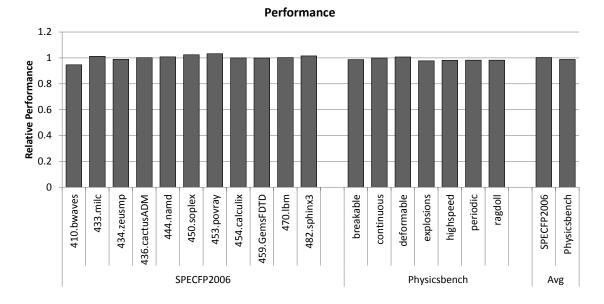

|    | 6.5.6 Performance                          |

|    | 6.5.7 Sensitivity Analysis118              |

|    | 6.6 Conclusion                             |

| 7. | Conclusions 123                            |

|    | 7.1 Conclusions                            |

|    | 7.2 Future Work                            |

| 8. | References                                 |

# List of Figures

| 2.1  | SIMD Execution Model                                                                     | 17 |

|------|------------------------------------------------------------------------------------------|----|

| 2.2  | HW/SW interface in processors                                                            | 28 |

| 2.3  | Memory system in a HW/SW co-designed processor                                           | 30 |

| 2.4  | Typical two stage TOL control flow                                                       | 31 |

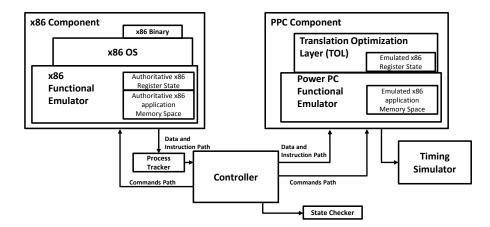

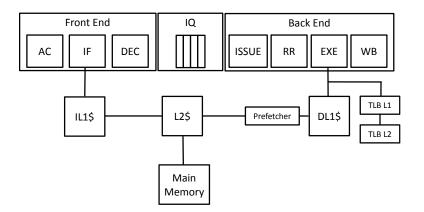

| 3.1  | DARCO Main components                                                                    | 36 |

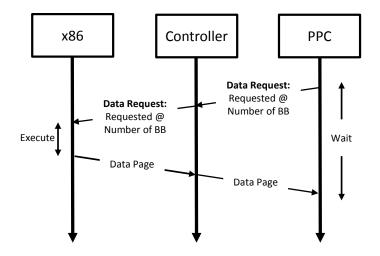

| 3.2  | Data page request from the PPC component, enforcing the synchronization phase            | 38 |

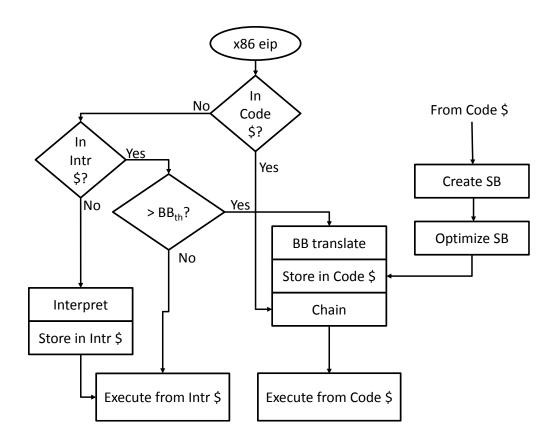

| 3.3  | Translation Optimization Layer execution flow                                            | 40 |

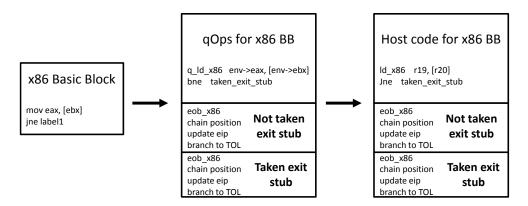

| 3.4  | Abstract translation of an x86 basic blaock to host ISA                                  | 41 |

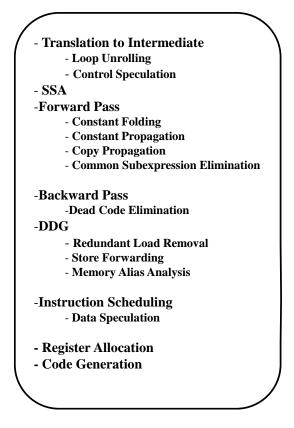

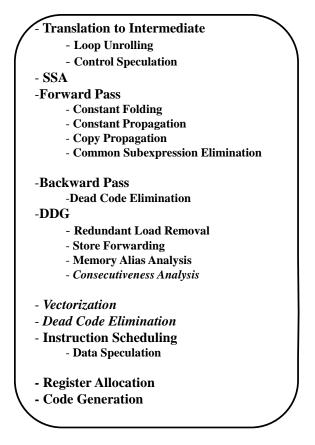

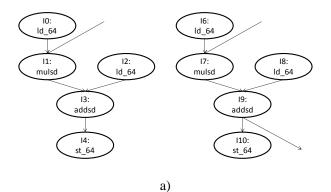

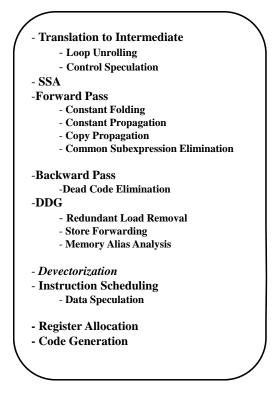

| 3.5  | Optimizations flow in Superblocks                                                        | 44 |

| 3.6  | Speculation Failure Detection Example                                                    | 46 |

| 3.7  | Host Processor Pipeline                                                                  | 47 |

| 3.8  | Effect of Threshold Variation on the Number of host instructions                         | 50 |

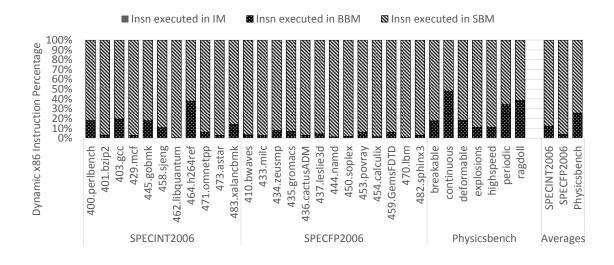

| 3.9  | Dynamic x86 instruction distribution in IM, BBM and SBM                                  | 51 |

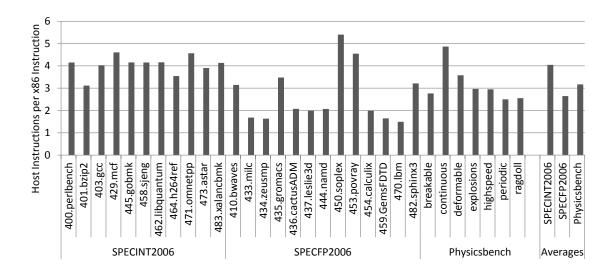

| 3.10 | Host instructions per x86 instruction in SBM                                             | 52 |

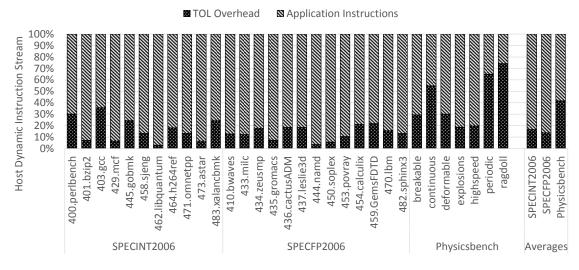

| 3.11 | Overall Host Dynamic Instruction Distribution                                            | 53 |

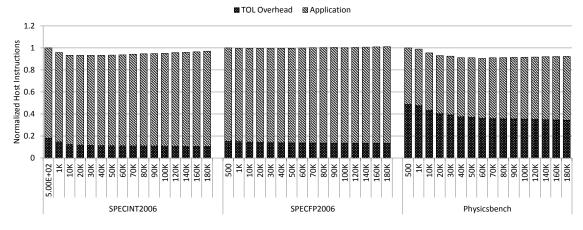

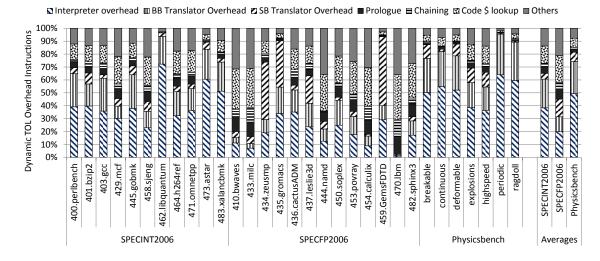

| 3.12 | Dynamic TOL Overhead Distribution                                                        | 53 |

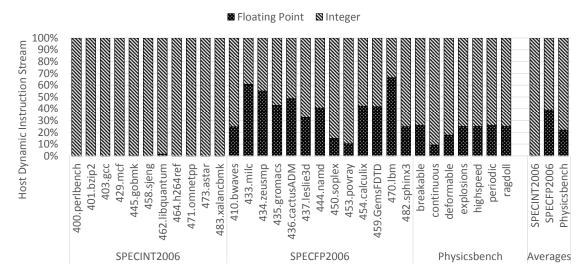

| 3.13 | Floating Point and Integer instruction distribution in host dynamic instruction stream.  | 54 |

| 4.1  | An Example Loop with pointer arithmetic                                                  | 62 |

| 4.2  | Optimization Sequence in Superblocks for Vectorization Support                           | 64 |

| 4.3  | Additional Dependence after vectorization                                                | 69 |

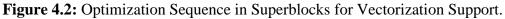

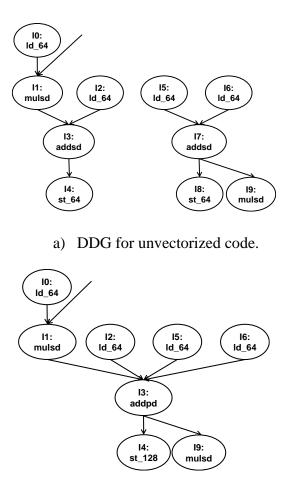

| 4.4  | Speculative Dynamic Vectorization Example                                                | 71 |

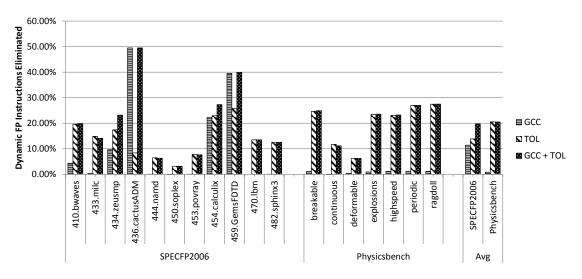

| 4.5  | Percentage of Dynamic Instructions eliminated by GCC, TOL and GCC+TOL vectorizations     | 73 |

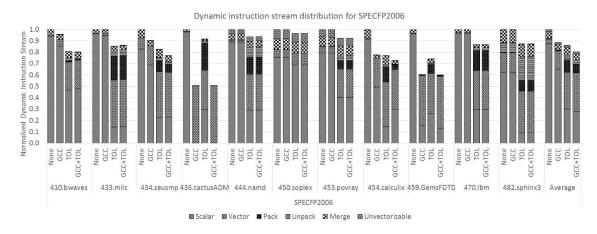

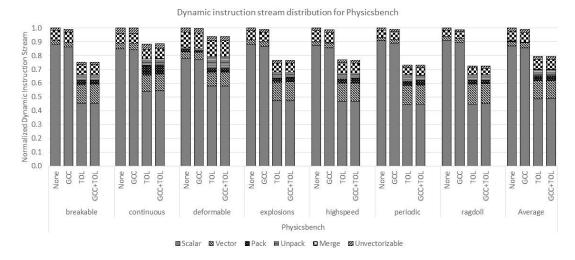

| 4.6  | Dynamic FP instruction stream distribution for SPECFP2006                                | 75 |

| 4.7  | Dynamic FP instruction stream distribution for Physicsbench                              | 75 |

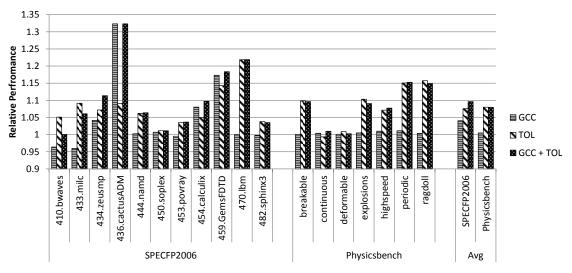

| 4.8  | Execution speed for GCC, TOL and GCC + TOL vectorized code relative to unvectorized code |    |

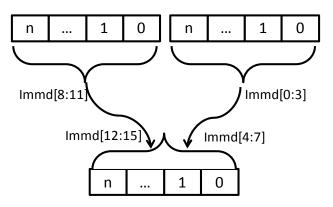

| 5.1  | Dynamic FP Instruction Stream Coverage for vectorization at 128, 256 and 512 bit vector lengths normalized to 128-bit case        | 83  |

|------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

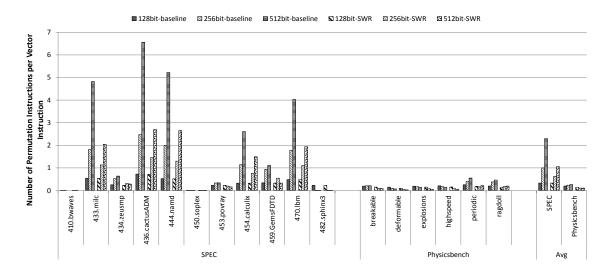

| 5.2  | Number of permutation instructions generated per vector instruction at 128, 256 and 512 vector lengths normalized to 128-bit case | 84  |

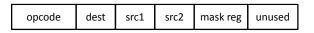

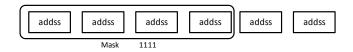

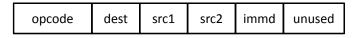

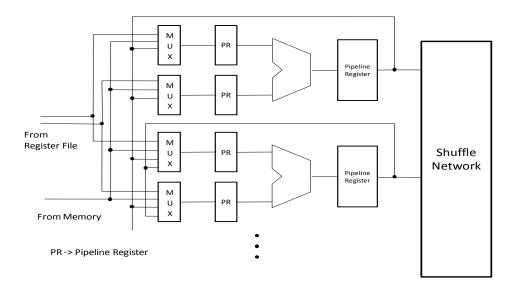

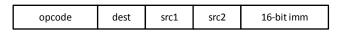

| 5.3  | Instruction format for masked vector instructions                                                                                 | 85  |

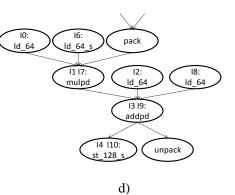

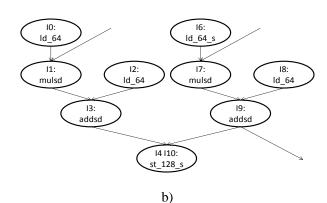

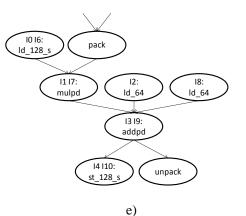

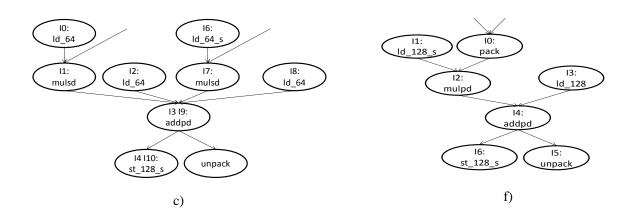

| 5.4  | Variable Length Vectorization Example                                                                                             | 86  |

| 5.5  | Masked Vector Instruction Execution                                                                                               | 86  |

| 5.6  | Packing scalar instruction results for feeding a vector instruction                                                               | 88  |

| 5.7  | Proposed instruction format for scalar instructions                                                                               | 88  |

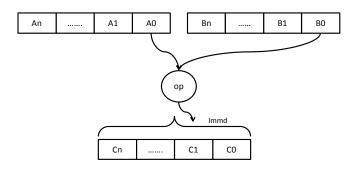

| 5.8  | Functionality of the proposed arithmetic scalar instructions                                                                      | 89  |

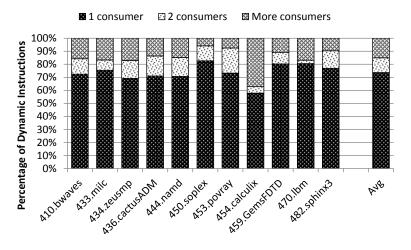

| 5.9  | Percentage of Dynamic Instructions with one, two and more number of consumers                                                     | 89  |

| 5.10 | Operand Forwarding before shuffle                                                                                                 | 90  |

| 5.11 | Instruction sequence for packing 4 values from different registers into a single register                                         | 91  |

| 5.12 | Instruction format for the proposed permutation instruction                                                                       | 91  |

| 5.13 | Functionality of the proposed Pack instruction                                                                                    | 91  |

| 5.14 | Dynamic Instructions stream coverage at three vector lengths, baseline and with VLV                                               | 93  |

| 5.15 | Number of Permutation Instructions per vector instruction, baseline and with SWR                                                  | 94  |

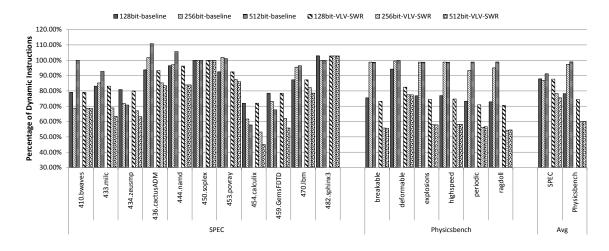

| 5.16 | Dynamic Instruction Percentage after baseline and VLV-SWR vectorizations.                                                         | 95  |

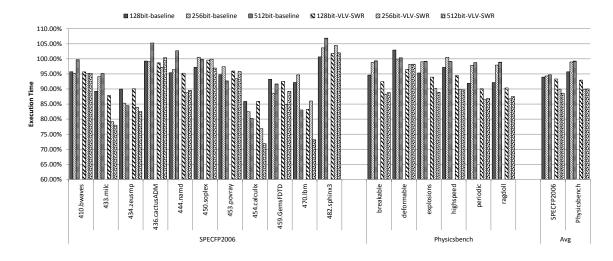

| 5.17 | Execution time for baseline and VLV-SWR vectorizations normalized to unvectorized code execution time                             | 96  |

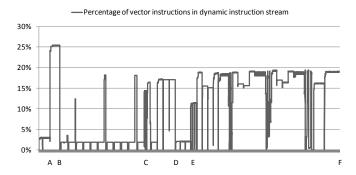

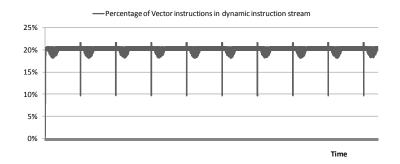

| 6.1  | Percentage of vector instruction (excluding memory instructions) in the dynamic instruction stream over the time                  | 104 |

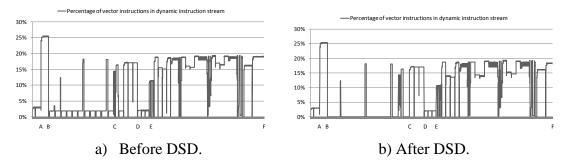

| 6.2  | Optimization sequence in superblocks for devectorization support                                                                  | 105 |

| 6.3  | Percentage of vector instruction in the dynamic instruction stream after dynamic selective devectorization for 434.zesump         | 111 |

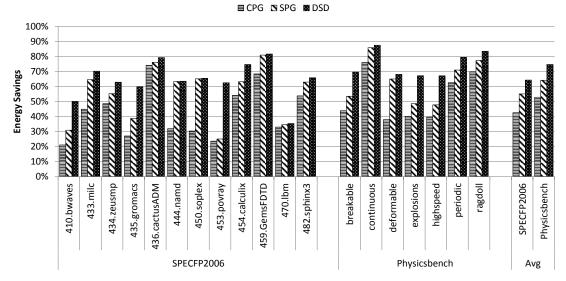

| 6.4  | SIMD accelerator energy savings for CPG, SPG and DSD normalized to no power gating without including DSD energy overhead          | 113 |

| 6.5  | SIMD accelerator energy savings for CPG, SPG and DSD normalized to no power gating including DSD energy overhead                  | 113 |

| 6.6  | Percentage of vector instruction (excluding memory instructions) in the dynamic instruction stream for 470.lbm                    | 114 |

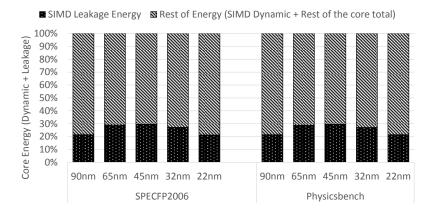

| 6.7  | Core overall energy distribution at different technologies                                                                                                                                                                                                  | 115 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

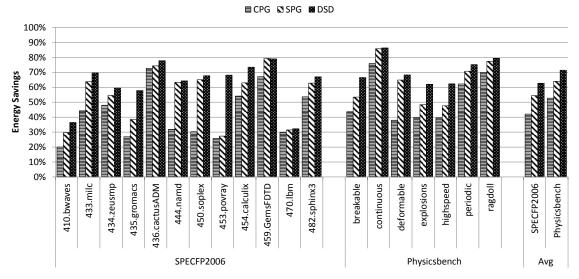

| 6.8  | Core energy consumptions for CPG, SPG and DSD normalized to no power gating                                                                                                                                                                                 | 116 |

| 6.9  | Overall Performance after DSD normalized to SPG                                                                                                                                                                                                             | 117 |

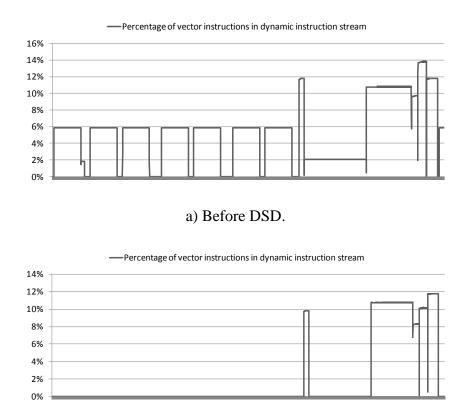

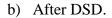

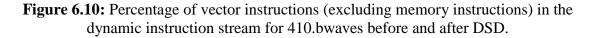

| 6.10 | Percentage of vector instructions (excluding memory instructions) in the dynamic instruction stream for 410.bwaves before and after DSD                                                                                                                     | 118 |

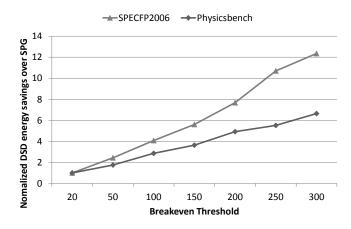

| 6.11 | Effect of breakeven threshold variation on DSD overall (dynamic + leakage) energy savings over SPG with a fixed wakeup latency of 10 cycles                                                                                                                 | 119 |

| 6.12 | Effect of breakeven threshold variation on DSD overall (dynamic + leakage)<br>energy savings over SPG normalized to breakeven threshold of 20 cycles,<br>with a fixed wakeup latency of 10 cycles (no success monitors, no dynamic<br>idle detect interval) | 119 |

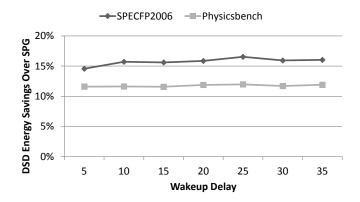

| 6.13 | Effect of wakeup delay variation on DSD overall (dynamic + leakage)<br>energy savings over SPG with a fixed breakeven threshold of 150 cycles                                                                                                               |     |

х

## List of Tables

| 3.1 | Host Processor Microarchitectural Parameters                                                                      | 47   |

|-----|-------------------------------------------------------------------------------------------------------------------|------|

| 3.2 | TOL configuration parameters                                                                                      | 48   |

| 4.1 | Percentage of Dynamic Instructions eliminated by GCC, TOL and GCC+TOL vectorizations                              | 74   |

| 4.2 | Execution speed for GCC, TOL and GCC + TOL vectorized code relative to unvectorized code                          | 78   |

| 5.1 | Percentage of permutations requiring N, N-1 and N-2 input registers to pack N values, for 256 and 512-bit vectors | 92   |

| 6.1 | McPAT Parameters                                                                                                  | .110 |

## List of Algorithms

| 4.1 | Speculative Dynamic Vectorization Algorithm | 67  |

|-----|---------------------------------------------|-----|

| 6.1 | Dynamic Selective Devectorization Algorithm | 108 |

# Chapter 1

## Introduction

Microprocessor design has traditionally been driven by higher performance requirements. Several microarchitectural techniques have been used to extract different kinds of parallelism from the applications. Starting with the introduction of pipeline, processor microarchitecture has gone through numerous improvements like superscalar and VLIW execution, out-of-order execution, speculative execution, multithreaded architectures, application specific accelerators, etc. Different microarchitectural extensions target different kinds of parallelism available in the applications in order to boost performance. Broadly, the parallelism available in an application falls under one or more of the following categories.

- 1) Instruction Level Parallelism (ILP)

- 2) Data Level Parallelism (DLP)

- 3) Thread Level Parallelism (TLP)

Microarchitectural techniques like instruction pipelining, superscalar and VLIW execution, out-of-order execution, register renaming, branch prediction, etc. are all used to exploit ILP. Single Instruction Multiple Data (SIMD) accelerators and vector processors are specifically designed to extract DLP from data parallel applications. Finally, techniques like multithreading and architectures like chip multiprocessors (CMP) target TLP. This thesis focuses on extracting data level parallelism through SIMD accelerators.

SIMD accelerators are one of the most widely used microarchitectural extensions because these are particularly effective in exploiting DLP. Applications from multimedia, scientific, and throughput computing domains are the main targets of these accelerators since they provide significant amount of DLP. Data parallel applications perform the same operation on multiple pieces of data. As a result, SIMD accelerators just need to have duplicated functional units with a very simple control mechanism. The performance boosting ability of SIMD accelerators and their relatively low complexity has led to their incorporation in processors from all the computing domains: general purpose processors, digital signal processors, gaming consoles, as well as embedded architectures. Intel's MMX, SSE and AVX extensions, AMD's 3DNow!, PowerPC's Altivec, and ARM Neon are prominent examples of SIMD extensions.

Apart from microarchitectural innovations, code optimizations have played an important role in boosting performance. Significant amount of work has been done in compiler optimizations to generate optimized binaries. Traditional compiler optimizations like constant propagation, copy propagation, common sub-expression elimination, loopinvariant code motion, redundant load elimination, store forwarding, dead code elimination, software pipelining, etc. have been successfully used to achieve significant performance improvements. Last decade has also seen the emergence of dynamic optimizations that are performed at runtime. These optimizations benefit from the availability of runtime information that is not available at compile time.

Performance has traditionally been the main focus of computer architects. However, power consumption of the microprocessors and battery life requirements of portable devices have made power/energy consumption an equally important factor. Therefore, computer architects now have to achieve a balance between performance and energy consumption. To address the problem, computer architects have turned their focus on designing simple cores by eliminating power hungry components of a complex core. Since simple cores provide lower performance than complex cores, several proposals have been made to improve overall throughput. For instance, Hardware/Software (HW/SW) Codesigned processors employ dynamic optimizations and speculative execution to improve the overall performance. Chip multiprocessors (CMP) have multiple simple cores on the same die and by simultaneously executing several threads on different cores, the overall throughput is increased.

Since HW/SW co-designed processors provide an opportunity to optimize the applications dynamically using the information about runtime behavior of the application, this thesis focuses on efficient code generation for SIMD accelerators in a HW/SW co-designed environment.

## **1.1 SIMD Execution Model**

SIMD execution, as the name suggests, consists of operating on multiple data elements in parallel using a single instruction. Therefore, the first step to enable SIMD execution is to encode multiple data elements that can be operated on in parallel, in a single instruction. This step is called vectorization. In general, vectorization is done at compile time by a vectorizing complier. Compilers do program analysis to find independent scalar instructions performing the same operation. Several of these instructions, depending on the data type of instructions and the SIMD accelerator width, are packed together in a single instruction, called a vector/SIMD instruction. Vectorized instructions are then executed on the SIMD accelerator. SIMD execution has several advantages over scalar execution. Some of them are described below:

- 1) Since SIMD accelerators perform multiple scalar operations encoded in a single vector instruction in parallel, they improve the overall performance.

- 2) Since a single vector instruction encode multiple operations, the total number of instructions to execute an application reduces. This results in lower instruction cache size requirements. Alternatively, it results in improved instruction cache hit rate and improved performance.

- 3) Having fewer instructions also reduces the amount of work the processor front-end needs to do. It needs to fetch, decode, and schedule less instructions. Also, the back-end needs to retire fewer instructions. This translates to better energy efficiency.

- 4) Having multiple operations encoded in an instruction allows a high number of effective operations in the instruction window. This leads to better instructions scheduling.

- 5) Vector memory instructions lead to fewer memory accesses and better utilization of available memory bandwidth.

## **1.2 Challenges in SIMD Execution**

Even though SIMD accelerators are very simple from the hardware perspective, code generation for them has always been a challenge. Static compile time vectorization loses significant vectorization opportunities due to conservative memory disambiguation analysis. The problem further deepens at higher vector lengths because it becomes difficult to find enough independent instructions, performing the same operation, to fill the wider vector/SIMD paths. Furthermore, SIMD accelerators without any leakage control mechanism might become a major source of leakage energy if not utilized judiciously.

#### **1.2.1 Static Vectorization Limitations**

The Instruction Set Architecture (ISA) of microprocessors contains special instructions that are executed over SIMD accelerators. However, in the early days, compilers were not smart enough to generate these instructions automatically. Therefore, programmers used to target these extensions mainly using in-line assembly or specialized

library calls. Later, automatic generation of SIMD instructions (auto-vectorization) was introduced in compilers, which borrowed their methodology from vector compilers.

A recent evaluation of vectorizing compilers by S. Maleki et al. [74] shows that the modern compilers including GNU GCC, IBM XLC, and Intel ICC are limited in extracting available vectorization opportunities from the vectorizable applications. One of the main problems in static compiling that they discovered is compilers inability to do accurate interprocedural pointer disambiguation and interprocedural array dependence analysis. Furthermore, J. Holewinski et. al. [45] showed that static vectorization fails to extract significant vectorization opportunities especially in pointer-based applications. They vectorize array- and pointer-based version of Digital Signal Processing (DSP) kernels from UTDSP benchmark suit [13]. Their results show that the compiler is able to extract significant parallelism from array based version of the kernels, whereas for pointer based version it fails to extract any vectorization opportunity.

#### **1.2.2 Wider Vector Units**

Due to their hardware simplicity SIMD accelerators are relatively easy to scale to higher vector lengths. As a result, SIMD accelerators grow in size with each new generation. For example, Intel's MMX [4] had vector length of 64-bits, which was increased to 128-bits in SSE [4] extensions. Intel's recent SIMD extensions AVX [4] and AVX2 [4] support 256-bit wide vectors. Furthermore, Intel Xeon Phi [12] and its visual computing architecture Larrabee [93] perform 512-bit wide vector operations.

Although SIMD accelerators are amenable to scaling from the hardware point of view, generating efficient code for higher vector lengths is not straightforward. The problem lies in the fact that different applications have different natural vector length. The applications with low natural vector length cannot benefit from wider vector units. There are applications for which compilers just need to unroll loops with a higher unroll factor to fill the wider vector paths. However, there is another category of applications that does not have enough parallelism for vectorization at higher vector lengths. Generating code for these applications for wider vector units becomes a challenge.

We discover that there are two key factors that thwart the performance at higher vector lengths: 1) Reduced dynamic instruction stream coverage for vectorization and 2) Huge number of permutation instructions.

#### **1.2.3 Leakage in SIMD accelerators**

Leakage energy is the static energy consumption of a circuit when it is idle. Functional units of microprocessors are responsible for a major fraction of leakage energy. Even though SIMD accelerators are an energy efficient way of improving performance, they become the main source of leakage energy due to their wider datapaths, for the applications lacking DLP, in the absence of leakage control mechanism. Therefore, it is of prime importance to shrink the leakage energy of SIMD accelerators when they cannot be utilized efficiently due to lack of DLP.

Many leakage control techniques have been studied [46][96][116], power gating [46] being one of the most prominent ones. Power gating cuts the supply voltage to the idle functional units, resulting in leakage energy savings. However, power gating has an energy and performance overhead associated with it. The energy and performance penalty has to be paid every time a power gated function unit is awakened to perform some operation. This overhead is unjustifiable especially if a functional unit like SIMD accelerator is needed to be awakened only for few cycles.

## **1.3 Contributions**

This thesis focuses on optimizing SIMD execution in HW/SW co-designed processors including efficient code generation and reducing leakage energy of SIMD accelerators.

### **1.3.1 Speculative Dynamic Vectorization**

We propose to complement the static vectorization with a speculative dynamic vectorizer. Static vectorization applies several complex and time consuming loop transformations to make a loop vectorizable. However, due to conservative memory disambiguation analysis it loses significant vectorization opportunities, especially in pointer rich applications. We propose to have a speculative dynamic vectorizer to handle these cases. The proposed dynamic vectorizer speculatively assumes that a pair of ambiguous memory accesses will never alias. This speculative assumption gives more freedom in instructions reordering and hence the dynamic vectorizer is able to discover more vectorization opportunities. During execution, the hardware checks for any memory dependence violations caused by the speculative vectorization. If any violation is detected, the hardware rolls back to a previously saved check-point and executes a non-speculative version of the code.

This work has been published in the Proceedings of 20th International Conference on High Performance Computing (HiPC 2013) [61] as a full length technical paper and in the Proceedings of the 21st International Conference on Parallel Architectures and Compilation Techniques (PACT 2012) [65] as a short paper. Furthermore, we also presented this work at Hipeac Compiler, Architecture and Tools Conference at Haifa, Israel in November 2013 [62].

## **1.3.2 Vectorizing for Wider Vector Units**

We discovered two major problems in generating code for wider vector units: 1) Reduced dynamic instruction stream coverage for vectorization and 2) Huge number of permutation instructions.

We propose Variable Length Vectorization (VLV) to increase the dynamic instruction stream coverage. Compilers generate vectorized code only when it is possible to fill the entire vector path, or in other words when there are enough independent scalar operations to occupy all the vector lanes. If this condition is not met, all the instructions are left in the scalar form. VLV, on the other hand, packs maximum number of scalar instructions together, even if the number is less than the number of vector lanes available. Therefore, the dynamic instruction stream coverage for vectorization increases and the dynamic instruction count decreases.

To tackle the problem of permutation instructions, we propose Selective Writing. Permutation instructions are needed when the input operands of a vector instruction are not available in a single vector register or are not in the correct order. Selective Writing consists of two techniques. The first technique eliminates permutation instructions altogether if the result of a scalar instruction is read only by one scalar instruction. The other technique reduces the number of instructions required to pack N values from N-1 to N/2.

This work resulted in a publication in the Proceedings of 15th International Conference on High Performance Computing and Communications (HPCC 2013) [63].

#### **1.3.3 Dynamic Selective Devectorization**

Dynamic Selective Devectorization (DSD) is a technique to efficiently power gate higher SIMD lanes. It helps reducing the leakage energy of higher vector lanes and, as a result, of whole SIMD accelerator and the core. Power gating [46] is a widely used technique to reduce leakage energy consumption of functional units. Power gating cuts the supply voltage to the idle functional units, sending it to sleep state, resulting in leakage energy savings. DSD dynamically profiles the applications to find higher lanes usage pattern. If a period of low activity, when the higher lanes are used scarcely, is detected, DSD devectorizes the corresponding piece of code. As a result, the higher lanes can be power gated for longer time intervals without intermittent awakening. Therefore, DSD enables power gating to save more leakage energy.

This work has been published in the Proceedings of the 25th International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD 2013) [64].

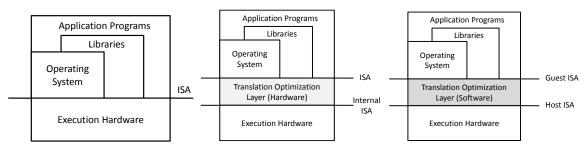

## 1.4 HW/SW Co-designed Processors

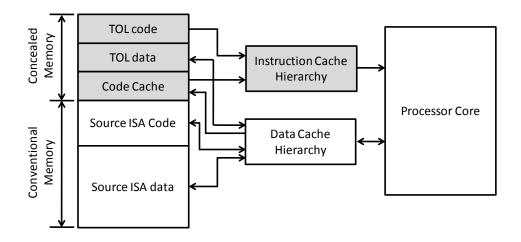

HW/SW Co-designed processors [36][39][91] have enticed researchers for more than a decade. Moreover, there is a renewed interest in them in both industry and academia [5][28][29][73][79][87][113]. These processors employ a software layer that resides between the hardware and the operating system. This software layer allows host and guest ISAs to be completely different, by translating the guest ISA instructions to the host ISA dynamically. The host ISA is the ISA which is implemented in the hardware, whereas, guest ISA is the one for which applications are compiled. The basic idea behind these processors is to have a simple host ISA to reduce power consumption and complexity.

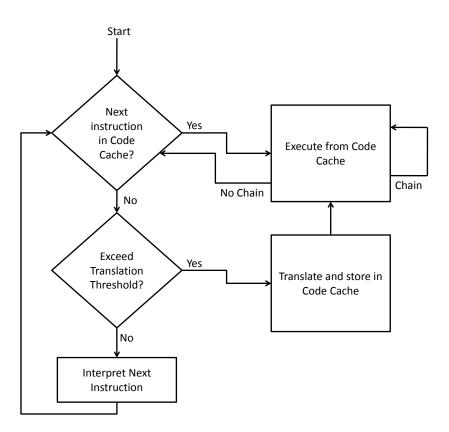

The software layer translates the guest ISA instructions to the host ISA in multiple phases. Generally, in the first phase, guest ISA instructions are interpreted. In the rest of the phases, guest code in translated and stored in a code cache, after applying several dynamic optimizations, for faster execution. The number of translation phases and optimizations in each phase are implementation dependent.

## 1.5 Why HW/SW Co-designed Environment

HW/SW co-designed processors provide some unique features that enable optimized vector code generation. Some of these features include:

**Support for Speculation and Recovery:** HW/SW co-designed processors provide efficient speculation and recovery support. It enables them to apply aggressive and speculative runtime optimizations. We speculatively vectorize the code when dependence between the two memory references is unknown. The hardware support is then leveraged to recover from any speculation failure caused due to speculative vectorization.

**Bigger Optimization Regions:** Compilers, in general, vectorize at basic block level in the absence loops. On the other hand, runtime optimizations in HW/SW co-designed processors are applied on bigger optimization regions called superblocks. Superblocks include multiple basic blocks following the biased direction of branches. Applying vectorization at superblocks increases the scope of vectorization and hence, available opportunities.

**Decoupled ISA and Hardware:** HW/SW Co-designed processors decouple the ISA from hardware implementation by means of a software layer. This decoupling allows to modify the hardware transparently to the software stack. As a results, different SIMD accelerators can be targeted without recompiling the code.

**Dynamic Optimizations:** HW/SW co-designed processors dynamically optimize the program binary at runtime. Therefore, vectorizing the program binary, instead of source code, allows legacy code vectorization.

**Online Profiling:** HW/SW co-designed processors employ online profiling to discover runtime application behavior. This information about runtime behavior of applications allows more specialized optimizations. For example, runtime application behavior can be used to decide which portions of application can be devectorized for efficient power gating of higher vector lanes without affecting performance.

## **1.6 Thesis Organization**

The rest of the thesis is organized as follows:

Chapter 2 provides the necessary background for the work presented. First we present an historical evolution of microprocessors and SIMD accelerators, followed by a description of different vectorization techniques. Then, we introduce dynamic optimization and different environments where they are applied. Finally, we present an overview of HW/SW co-designed processors and the features they offer.

Chapter 3 provides the details of our simulation environment. First, we present our simulation infrastructure, DARCO that is an in house development in collaboration with other members of the research group. Then, we describe benchmarks used for the evaluation of our proposals. Afterwards, we present the vector instruction set of the host ISA.

The next three chapters illustrate our proposals in detail. Each chapter starts with an introduction and motivation for the work presented. It is then followed by a description of the proposed algorithms or techniques. Thereafter, we present the experimental evaluation results. Finally, we compare out proposals with the related work in the corresponding area.

Chapter 4 explains our proposal of Speculative Dynamic Vectorization to vectorize application at runtime and extract vectorization opportunities missed by compilers due to conservative memory disambiguation analysis. Chapter 5 discusses problems in vectorization at higher vector lengths and provides details of our proposals: Variable Length Vectorization and Selective Writing. Chapter 6 presents the proposed Dynamic Selective Devectorization technique and how it improves power gating efficiency in saving leakage energy in SIMD accelerators. Finally, Chapter 7 concludes the thesis and outlines the future work.

# Chapter 2

## Background

High computational power requirements have always driven the microprocessor design. The high performance demands have been met through technology scaling and microarchitectural innovations to extract different kind of parallelism from the applications. Parallelism can broadly be divided into the following categories:

#### **Instruction Level Parallelism:**

Instruction level parallelism (ILP) takes advantage of sequences of instructions that require different functional units (such as the load unit, ALU, FP multiplier, etc.) for execution. Different architectures approach this in different ways, but the idea is to have these non-dependent instructions executing simultaneously to keep the functional units busy as often as possible.

#### **Thread Level Parallelism:**

Thread level parallelism (TLP) is extracted by running multiple flows of execution of a single application simultaneously. TLP is most often found in applications that need to run independent, unrelated tasks (such as computing, memory accesses, and IO) simultaneously. These types of applications are often found on machines that have a high workload, such as web servers. TLP is gaining importance due to the rising popularity of multi-core and multi-processor systems, which allow for different threads to truly execute in parallel.

#### **Data Level Parallelism:**

Data level parallelism (DLP) is more of a special case than instruction level parallelism. DLP appears due to the need of performing the same operation on multiple data items simultaneously. A classic example of DLP is performing an operation on an image in which processing each pixel is independent from the ones around it (such as brightening). Other types of operations that allow the exploitation of DLP are matrix, array, and vector processing.

## 2.1 Microarchitectural Innovations to Exploit Parallelism

A whole body of microarchitectural innovations exists to exploit different kind of parallelisms. Most prominent of these techniques are given below:

#### **2.1.1 Extracting Instruction Level Parallelism**

Arguably, the maximum number of microarchitectural innovations have been focused on extracting ILP, especially in general purpose computation domain. These include:

**Instruction Pipelining:** Instruction pipelining is a technique to overlap the execution of different instructions at the same time [26][31]. An instruction goes through different processor stages during its execution: fetch, decode, register read, execute, memory access, and write back are the most basic stages. The insight behind pipelining is that any given instruction is only in one of these processor stages during its execution while the rests of the stages are idle. Instead of waiting for one instruction to finish its execution and then initiating the next instruction, pipelining initiates next instruction as soon as first instruction leaves the first stage. In other words, pipelining thrives by keeping all the processor stages busy. Hence, pipelining extract parallelism among different phases of instructions by executing them in parallel and boosts overall throughput.

**Dynamic Instruction Scheduling and Out-of-Order Execution:** Dynamic instruction scheduling decides the order of instruction execution at runtime. It enables instructions bypassing each other during execution, i.e. out-of-order execution, instead of following the strict order in which they are stored in memory. In the absence of dynamic instruction scheduling, the whole pipeline is stalled if an instruction cannot be executed due to any reason like dependence, cache miss, etc. However, dynamic instruction scheduling allows later instructions to bypass the stalled instruction and continue their execution. Scoreboard in CDC 6600 [105] and Tomasulo's algorithm [108] are two earliest example of dynamic instruction scheduling. Executing instructions in out-of-order fashion increases resource utilization and hence improves performance. However, complex hardware structures are maintained to allow the instructions to execute out of the original program order and track dependencies. This increases hardware complexity and increase power consumption.

**Superscalar Processors:** These processors consist of multiple pipelines all operating in parallel [16][20]. Having multiple pipelines allow superscalar processors to issue and commit (complete) multiple independent instructions per cycle. These processors incorporate sophisticated hardware to dynamically check dependences among instructions

at runtime. This hardware sophistication results in chip complexity and power dissipation, which have become a major problem in modern superscalar processors. Even though superscalar processors incorporate multiple pipelines, the effective use of these pipelines depend on available ILP in the applications. Data dependency among consecutive instructions limits the amount of ILP that can be extracted by superscalar processors. Nonetheless, superscalar processors have been used successfully to extract ILP by executing multiple instructions in parallel.

**VLIW Processors:** Very Long Instruction Word (VLIW) processors [33][40][76][94] are similar to superscalar processors in the sense that they also incorporate multiple pipelines. However, VLIW processors do not have dynamic instruction scheduling, as do superscalars. Compiler is responsible for scheduling instructions to be executed in different pipelines. This reduces the complexity and high power consumption problems of superscalar processors. However, compiler needs to be aware of microarchitectural details in order to do efficient scheduling and extract ILP. The dependence of VLIW processors on the compiler support makes them a less attractive option. This is one of the reasons behind superscalars being more popular than VLIWs.

Register renaming, branch prediction [38][49][51][84][97][118][119], and speculative execution [48][50][100][101][102] are some of the other well-known microarchitectural techniques to extract more ILP. Register renaming is a technique used to avoid false (anti and output) dependence among instructions. Removing false dependences exposes more ILP. Branch predictor, as the name suggests, predicts outcome of a branch before it is executed so that the control dependent instructions can start their execution without waiting for the outcome of the branch. If the prediction is incorrect, however, there is a penalty to be paid. Speculative execution refers to performing a task before knowing whether it is to be performed or not. Brach prediction is an example of speculative execution. All these techniques focus on boosting performance by exploiting ILP.

#### 2.1.2 Extracting Thread Level Parallelism

Exploiting ILP has driven the microprocessor design for several decades. However, diminishing returns on ILP has led architects to consider exploiting other kinds of parallelism to meet performance requirements. TLP has been targeted in the applications that perform several independent tasks. Microarchitectural supports for extracting TLP can be summarized as:

**Multithreading:** The basic idea behind multithreading is to execute multiple threads (workloads) on a processor simultaneously. In a multithreaded processor, the hardware resources are shared among a set of threads. However, it requires duplication of some of the resources like registers and program counter, to maintain the thread state. The three main approaches to multithreading are:

*Fine-grained Multithreading:* This technique issues instructions from a different thread on each clock cycle, skipping the stalled threads [44][53][67]. Since the threads are switched every clock cycle, throughput loss even for short stalls in one thread can be efficiently hidden by executed instructions from the other threads. The flip side of fine-grained multithreading is that it slows down the execution of an individual thread even if does not suffer any stalls. Nonetheless, the technique is effective for improving system throughput.

*Coarse-grained Multithreading:* Where fine-grained multithreading switches between threads on every clock cycle, coarse-grained multithreading switched them only for costly stalls, like L2 or L3 cache misses [14]. Therefore, slowdown in individual threads is going to be less, if they do not have costly stalls. However, thread switching only for costly stalls prevents coarse-grained multithreading to compensate for throughput loss due to short stalls.

*Simultaneous Multithreading:* Simultaneous multithreading technique [75][111] is a special case of fine-grained multithreading implemented in multiple issue, dynamically scheduled superscalar processors. Fine- and coarse-grained multithreading, even though switch threads, issue instructions from a single thread in one cycle. As a result, some of the issue slots may remain empty due to lack of ILP. Simultaneous multithreading solves the problem by issuing instructions from multiple threads in the same cycle. Therefore, the number of empty slots reduces and system throughput increases.

**Multiprocessor:** Multiprocessors [42] consist of a set processors sharing memory and peripherals. TLP is extracted by executing independent threads on different processors. Comparing to a single multithreaded processor, multiprocessors duplicate the entire processor, whereas multithreading requires duplication of only the private state such as the registers and program counter. Moreover, each processor within the multiprocessor can also support multithreading, thereby, increasing the total number of threads that can be executed on the multiprocessor. If all the processors in a multiprocessor are on the same chip, it is called chip multiprocessor or CMP. Depending upon the memory organization,

multiprocessors can be categorized as either shared memory multiprocessors or distributed memory multiprocessors.

*Centralized Shared-Memory Multiprocessors* typically consist of small number of processors sharing a centralized memory. Since the memory is centralized, all the processors have uniform memory access latency, therefore, this configuration is called Uniform Memory Access (UMA) multiprocessors as well. UMA is suitable only for multiprocessors with few cores because it is not practical for a centralized memory to support the bandwidth requirements of large number of cores.

*Distributed Shared-Memory Multiprocessors* can support larger processor count, since the memory is physically distributed among the processors. The memory bandwidth increases as a result of distributed memory, however, it also means that the memory access latency is not uniform, rather depends on the location of the processor that has the requested data. Therefore, these multiprocessors are also called Non Uniform Memory Access (NUMA) Multiprocessors.

## 2.1.3 Extracting Data Level Parallelism

A set of architectural extensions exists to specifically extract data level parallelism from applications from different computing domains like multimedia applications, scientific computing, etc. These extensions include vector processors, graphics processing units (GPU), and SIMD accelerators. The basic idea behind all of these extensions is to perform the same operation on multiple data elements by a single instruction. In addition to the performance benefits, this also results in energy efficiency because the front-end of the microprocessor has to handle less instructions.

**Vector Processors:** Vector processors [43][114] are especially designed to efficiently execute data parallel applications. These processors work with long vectors, a typical example is 64 element vectors. The elements in a vector are processed in a pipelined manner, including memory load/store. These pipelined load/stores help vector processors in hiding memory latency. However, these architectures are expensive mainly because of high memory bandwidth requirements.

**Graphics Processing Unit (GPU):** The last decade saw the appearance of GPUs [2][6][7] as high performance graphics accelerators. However, due to their high throughput they are gaining popularity in general purpose computing domain as well. GPUs consist of highly parallel hardware that support single instruction multiple data execution model. They also support huge number of threads executing in parallel. These architectures sometimes are

referred to as heterogeneous architectures because they have a system processor and system memory in addition to the GPU itself. The main challenge in GPUs is optimizing the communication between system memory and GPU.

**SIMD Accelerators:** In the mid-90's SIMD accelerators [4][23][37] [68] emerged mainly to accelerate multimedia applications on general purpose processors. Like vector processors, SIMD accelerators perform the same operation on multiple pieces of data using one instruction. However, the vector length of SIMD accelerators is typically much smaller than the maximum vector length of vector processors. Furthermore, some of the fundamental features of vector processors like variable vector length, strided memory access, gather-scatter, and mask registers are generally omitted in SIMD accelerators to simplify the design. This, however, makes it difficult for compilers to generate code for them. Therefore, some of the latest SIMD accelerators have started to incorporate these features in their ISA gradually with each new generation.

Due to their simplicity, performance boosting ability, and energy efficiency SIMD accelerators form an integral part of processors from different computing domains. Even though GPUs have greater compute potential, they work as a coprocessor, whereas SIMD accelerators form part of processor's pipeline. This fact allows them to speed up the execution of more general purpose applications. GPUs and vector processors, on the other hand, target a specific kind of applications that have significant amount of explicit DLP. Moreover, GPUs have specific programming language requirements and require programmers to explicitly expose DLP through programming language notations. Whereas, SIMD accelerators do not have any such requirements. Therefore, this thesis focuses on extracting DLP through SIMD accelerators instead of GPUs or vector processors.

## 2.2 SIMD ISA Extensions

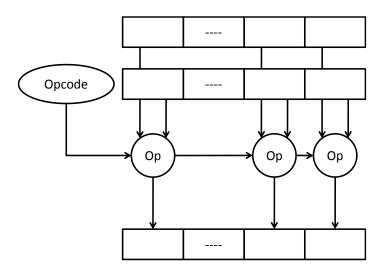

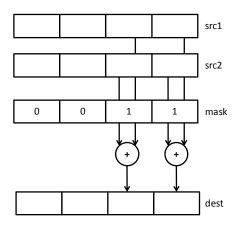

SIMD accelerators [4][35][23][37][52][68][103][109] are ubiquitous in microprocessors from different domains ranging from supercomputers to smart phones. These accelerators are specially designed to target computation intensive scientific applications, multimedia applications like image processing, signal processing, graphics, audio and video encoding, etc. These applications consists of compute intensive data parallel kernels where each element can be processed in parallel. For example, in image processing, properties of individual pixels can be modified in parallel. To efficiently execute these kernels, SIMD accelerators provide multiple functional units all performing the same operation as shown in Figure 2.1.

Figure 2.1: SIMD execution model.

Microprocessors have special extensions to their Instruction Set Architecture (ISA) and hardware state (e.g. new registers) to support SIMD execution. Following are some of the representative SIMD extensions in current microprocessors.

### 2.2.1 Intel's SIMD Extensions

Intel's SIMD extensions [4] have gone through major transformations since they were first introduced in 1996. Intel introduced MMX as 64-bit wide multimedia extensions for their Pentium processors. MMX supports 8-bit, 16-bit, and 32-bit vectors. This means that the 64-bit wide vector path can perform eight 8-bit, four 16-bit or two 32-bit operations in parallel. Following the IA-32 semantics, MMX implements two-operand destructive instruction encoding, where one of the source registers is also the destination register. However, MMX does not include floating-point vector instructions.

MMX defines eight 64-bit vector registers named MM0-MM7. However, these registers are mapped to x87 floating-point registers to avoid saving extra state on context switches. Therefore, this register aliasing prohibits MMX and x87 code intermixing. The register values need to be saved and retrieved before switching between MMX and x87 code.

**Streaming SIMD Extensions (SSE):** Intel introduced SSE [4] in 1999 in Pentium III to overcome the limitations of MMX. The vector length was increased to 128-bits from 64-bit of MMX to boost performance. SSE introduced 70 new instructions to perform single-precision floating-point arithmetic operations, memory load/store, comparison, data shuffling, and data type conversion between integer and floating-point. Moreover, SSE

introduced special instructions for cacheability control, prefetch, and memory ordering. The vector single-precision floating-point instructions of SSE perform four single-precision floating-point operations in parallel, whereas the scalar floating-point instructions perform only one operation. Therefore, the scalar instructions in SSE provide an option to avoid the complex x87 Floating Point Unit (FPU) to execute floating-point code even without vectorization. The cacheability control instructions provide a fine control over when and what data to bring to caches.

SSE also introduced a separate vector register file with eight 128-bit vector registers (XMM0 – XMM7) and a 32-bit status and control register MXCSR. Having a separate register file resolves the register aliasing problem of MMX. The ability to intermix SSE and MMX code provides greater flexibility and throughput for applications operating on large arrays of floating-point and integer data.

**SSE2:** SSE2 [4] was introduced in 2001 with Intel Pentium IV processors. SSE2 improved on existing MMX and SSE extensions by adding 144 new instructions. SSE2 extensions featured two major enhancements: 1) Double-precision floating-point instructions and 2) 128-bit SIMD integer instructions. MMX and SSE both lacked double-precision floating-point support. Its inclusion in SSE2 enabled high precision computations in SIMD unit and as a result, better performance for scientific and engineering applications. MMX had 64-bit vector integer instructions and even though SSE supports 128-bit wider vectors, it does it only for floating-point instructions. SSE2 extended 128-bit vector support for integer instructions as well. Furthermore, SSE2 improved upon the cacheability control and prefetching support introduced in earlier SSE extensions.

**SSE3/SSSE3/SSE4:** SSE3 [4] was introduced in 2004 with Pentium IV processor with Hyper Threading (HT) technology. SSE3 introduced 13 new instructions in different categories. It included floating point instructions that support packed addition/subtraction and horizontal addition/subtraction. The packed addition/subtraction instructions perform addition on one element of the vector register and subtraction on the other element. The horizontal addition/subtraction instructions perform the operation on the different elements of the same source register instead of performing it on the corresponding elements of different source registers. Furthermore, two thread synchronization and one integer unaligned load instruction was also introduced in SSE3.

Supplement Streaming SIMD Extensions (SSSE3) was introduced in 2006 with Intel Core 2 processor family. It introduced 32 new instructions mainly to accelerate multimedia and signal processing applications with integer data. It extended the horizontal addition/subtraction support of SSE3 to integers as well. Further, SSSE3 introduced new instructions like absolute value evaluation, multiply and add for dot products, negating packed integers, etc.

SSE4 consists of two extensions: SSE4.1 and SSE4.2. The 47 new instructions of SSE4.1 are targeted at improving the performance of media, imaging, and 3D applications whereas SSE4.2 focuses on string and text processing.

Advanced Vector Extensions (AVX): AVX [4] is Intel's 256-bit SIMD extension supported by Sandy Bridge architecture. A major difference between AVX and earlier SIMD extensions, apart from the vector length, is the instruction encoding. AVX uses a three operand non-destructive instruction encoding. It helps in reducing the number of register-register copy operations.

Further, AVX enhances the 128-bit floating point instructions to operate on 256bits. However, vector integer instructions do not have a 256-bit version. Apart from enhancing existing instructions to 256-bits, AVX offers several new instructions for nonunit-stride fetching of data, intra-register manipulation of data, etc. AVX also introduces a new register file consisting of eight 256-bit registers YMM0–YMM7. However, the lower 128-bits of the YMM registers are mapped on to XMM registers.

**FMA and AVX2 Extensions:** Fused-Multiply-Add (FMA) [4] extensions include various combinations of fused instructions to further improve the performance. The instructions in this extension includes fused multiply-add, fused multiply-subtract, fused multiply add/subtract interleave, and signed-reversed multiply on fused multiply-add and multiply-subtract. All these instructions can operate on single-precision and double-precision floating-point data. Moreover, scalar and vector (packed) version of all these fused operations are available except for fused multiply add/subtract interleave that has only the vector version.

Advanced Vector Extensions 2 (AVX2) [4] promotes the majority of integer instructions to support 256-bit vector operations, whereas AVX supports 256-bit vector operations only on floating-point data. Moreover, AVX2 provides gather support to fetch data from non-contiguous memory locations. It also includes vector shift instructions with per element shift count. Furthermore, it improves the broadcast and permutation functionality of AVX instructions.

**Intel's 512-bit Vector Extensions:** Intel's Many Integrated Core (MIC) architecture and products based on it, like Xeon Phi [12], support 512-bit wide vector instructions. Apart

from wider vectors, this architecture supports masked vector execution that enables vectorizing short conditional branches. This improves overall efficiency of vector processing unit. Furthermore, MIC supports gather and scatter instructions to access non-unit stride memory accesses. Vectorizing irregular memory access patterns helps extracting additional vectorization opportunities and improves overall performance.

#### 2.2.2 PowerPC Altivec

Altivec [37] SIMD extensions were the result of a joint effort from Apple, IBM, and Motorola in late 90's. The name Altivec, however, comes from Motorola. IBM called these extensions VMX, whereas Apple referred to them as Velocity Engine. Like SSE, Altivec supports a vector length of 128-bits, thought it was launched before SSE. It included a rich set of both integer and floating-point vector instructions; however, support for double-precision floating-point is absent. Furthermore, Altivec implements non-destructive instruction encoding.

Altivec has a vector register file with thirty-two 128-bit registers compared to eight 128-bit registers of SSE (though x86-64 has sixteen 128-bit registers). A notable difference between Altivec and SSE is that Altivec does not have scalar floating-point instructions like SSE. Scalar code has to be executed on a separate floating-point unit (FPU). Furthermore, there is no instruction for moving data between vector and floating-point register files.

Altivec provides some very flexible data permutation instructions like *vperm*. It allows each byte of a resulting vector to be taken from any byte of either of two other vectors, parameterized by yet another vector. *vsel* is another permutation instruction that operates at bit level. In addition, Altivec offers vector compare instructions and select mechanism to allow control flow in the vectorized code. Like SSE, Altivec also provides instructions for cacheability control to avoid polluting the cache with non-temporal data.

### 2.2.3 ARM Neon

Neon is 128-bit (or alternatively 64-bit) wide SIMD extension for ARM processors. Neon provides a rich set of integer and floating-point vector instructions. It supports scalar single-precision and double-precision computations. However, only single-precision floating-point instructions have vector equivalents. Neon also provides scalar and vector half-precision conversions instructions. Like Altivec, it uses a non-destructive instruction encoding for most of the instructions. Neon has a vector register file that can be viewed as: 1) Thirty-two 64-bit registers D0-D31 or 2) Sixteen 128-bit register Q0-Q15. In other words, each D register is one half, either lower or higher, of a Q register. Alternatively, a Q register is composed to two D registers. For example Q0 is the same register as D0 and D1 combined. This dual view of registers allows to promote/demote the elements within a single operation. A "promotion" doubles the precision of the elements, for example instructions like VMULL, VADDL, etc. promotes elements from 16-bits to 32-bits. These instructions read the source operands from D registers and place the results in the destination Q register. Similarly, a "demotion" reduces the precision by reading input operands from Q registers and placing the result in D register, e.g. VADDHN. Furthermore, there are instructions that promote only the second operand like VADD, VSUB, etc.