## **UNIVERSIDAD DE MURCIA**

# FACULTAD DE INFORMÁTICA

Improving the Energy-Efficiency of Cache-Coherent Multi-Cores.

Técnicas para Mejorar la Eficiencia Energética de los CMPs con Coherencia de Caché.

**D. Antonio García Guirado** 2013

UNIVERSIDAD DE MURCIA Departamento de Ingeniería y Tecnología de Computadores

# Improving the Energy-Efficiency of Cache-Coherent Multi-Cores

A dissertation submitted in fulfillment of the requirements for the degree of

Doctor en Informática

By Antonio García Guirado

Advised by José Manuel García Carrasco Ricardo Fernández Pascual

Murcia, September 2013

### Abstract

With the end of the energy benefits of classical transistor scaling, energy-efficiency became the driving factor of microprocessor design. The energy costs of increasing operating frequencies and using more aggressive microarchitectures to improve performance can no longer be compensated by transistor technology advances at the same rate as in the past. Now more than ever, computer architects are left in charge of providing the expected growth of microprocessor performance by means of more energy-efficient designs, in order to make cost-effective use of the ever-increasing transistor density in chips within a limited power budget. Otherwise, microprocessor evolution would be doomed to hit a *power wall*.

Some years back, chip multiprocessors (CMPs) containing relatively simple cores were deemed a suitable architecture in the search for energy-efficiency and went mainstream. However, CMPs pose particular challenges in their design. In this thesis we tackle two paramount issues with growing importance as we scale out CMPs, namely network-on-chip power consumption and cache coherence scalability, and we propose mechanisms to alleviate their impact on the energyefficiency of CMPs.

Cache coherence information may eventually account for most storage area on chip if we fail to provide scalable and energy-efficient coherence schemes. To address this challenge, we propose a new coherence scheme based on a chip divided in linked areas that noticeably reduces the size of the storage used to maintain sharing information. Then, we propose a unified cache organization that eliminates the overhead and complexity of directory storage structures by leveraging shared cache resources to alternately store data or directory information at a cache entry granularity. This organization makes efficient use of storage resources as just the required (small) number of entries are allocated for directory information in the unified cache.

#### Abstract

The second CMP design challenge tackled by this thesis is that, as the core count increases, current trends indicate that networks-on-chip (NoCs) would end up taking up most of the chip energy budget unless measures are taken to prevent it. These measures include the development of techniques to increase the proximity of data to cores at the architecture level and the use of disruptive low-power transmission technologies such as silicon photonics. For increasing data proximity, in this thesis we propose a mechanism that retrieves data from a close provider in the area in which the core requesting the data is located, working at the cache coherence protocol level. At the cache organization level, we propose a new organization that aims at minimizing the average distance to access the last level cache, reducing the energy required to feed the cores with data. To enable the exploitation of photonics, we open the field of dynamic policies for arbitrating hybrid photonic-electronic NoCs, making energy-efficient use of the particular properties of both technologies at a fine message granularity, resulting in important benefits in throughput, energy and latency.

We expect that the mechanisms described in this thesis will help scale-out CMPs in the current scenario of energy-constrained transistor miniaturization, in order to achieve the ever-increasing performance demanded of computing systems.

### **Acknowledgments**

I would like to start by thanking my advisors, Ricardo and Jose Manuel. First they gave me the chance to start researching in the field I liked since I started my undergraduate studies, and then they were by my side throughout all these years, making this such an enriching experience. As a preparatory stage to performing research, I dare say that they made my doctorate years successful.

I also want to thank all my laboratory mates: Rubén, Dani, Ginés, Chema, Juanma, as well as those in the laboratory next door: Dani, Epi, José Luis, Antonio, Ana, and other colleagues: Alberto, Varadan, for sharing these years with me and helping me in everything I needed. I want to express my gratitude to my host at the Università degli Studi di Siena, Sandro Bartolini, for making me feel at home for almost five months and supporting me ever since. Also, thanks to Pierfrancesco Foglia and Sylvain Collange for taking on the extensive task of reviewing my thesis. I must remark and thank the support I received from my friends in Murcia and as well as in Siena; they are too many to be listed here. Still, Ángel, Cai, Fernando, José David, Josipa, Rafah and Stefania have to appear by name. Last, but most important, I thank my family for everything.

# Contents

| Abstra  | ct                                                        | 5  |

|---------|-----------------------------------------------------------|----|

| Ackno   | wledgments                                                | 7  |

| Conte   | nts                                                       | 9  |

| Table   | of Contents in Spanish                                    | 13 |

| List of | Figures                                                   | 15 |

| List of | Tables                                                    | 19 |

| Extend  | led Abstract in Spanish                                   | 21 |

| 1 Int   | roduction                                                 | 31 |

| 1.1     | The Power Wall and the Shift to Multi-Core                | 33 |

| 1.2     | Shared Memory and Cache Coherence                         | 37 |

| 1.3     | Networks-on-Chip and Cache Organizations                  | 41 |

| 1.4     | Cache-Coherent Tiled CMPs                                 | 44 |

| 1.5     | Motivation                                                | 45 |

| 1.6     | Thesis Contributions                                      | 47 |

|         | 1.6.1 Multiple-Area Cache Coherence Protocols             | 47 |

|         | 1.6.2 Distance-Aware Partially Shared Cache Organizations | 47 |

|         | 1.6.3 In-Cache Coherence Information                      | 48 |

|         | 1.6.4 Management Policies for Exploiting Hybrid Photonic- |    |

|         | Electronic Networks                                       | 48 |

| 1.7     | Publications                                              | 49 |

| 1.8     | Thesis Organization                                       | 50 |

|         |                                                           |    |

#### Contents

| 2 | <b>Bacl</b><br>2.1<br>2.2 |         | d 53<br>e Coherence Basics                           |

|---|---------------------------|---------|------------------------------------------------------|

| 3 | Mul                       | tiple-A | Area Cache Coherence Protocols 65                    |

|   | 3.1                       | -       | round                                                |

|   |                           | 3.1.1   | Base Architecture                                    |

|   |                           | 3.1.2   | Direct Coherence                                     |

|   | 3.2                       | Multi   | ple-Area Coherence Protocols                         |

|   |                           | 3.2.1   | DiCo-Providers                                       |

|   |                           | 3.2.2   | DiCo-Arin                                            |

|   | 3.3                       | Detail  | ed Operation of the Protocols                        |

|   |                           | 3.3.1   | DiCo-Providers                                       |

|   |                           | 3.3.2   | DiCo-Arin                                            |

|   | 3.4                       | Evalu   | ation                                                |

|   |                           | 3.4.1   | Methodology                                          |

|   |                           | 3.4.2   | Static Power Consumption                             |

|   |                           | 3.4.3   | Dynamic Power Consumption                            |

|   |                           | 3.4.4   | Performance Results                                  |

|   | 3.5                       | Relate  | ed Work                                              |

|   | 3.6                       | Concl   | usions                                               |

|   |                           |         |                                                      |

| 4 |                           |         | ware Partially Shared Cache Organizations 99         |

|   | 4.1                       | 0       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|   |                           | 4.1.1   | Base Architecture                                    |

|   |                           | 4.1.2   | Coherence Issues                                     |

|   | 4.0                       | 4.1.3   | Block Mapping and Distance to Access the LLC 106     |

|   | 4.2                       |         | nce-Aware Partially Shared Cache Organizations       |

|   |                           | 4.2.1   | Exploring the DAPSCO Search Space                    |

|   |                           | 4.2.2   | Tori and Sliding Patterns                            |

|   |                           | 4.2.3   | Implementation Details                               |

|   | 4.3                       |         | ation                                                |

|   |                           | 4.3.1   | Effectiveness of DAPSCO 119                          |

|   |                           | 4.3.2   | Simulation Methodology                               |

|   |                           | 4.3.3   | Results and Discussion                               |

|   |                           | 4.3.4   | Orthogonality of DAPSCO: Reactive NUCA               |

|   | 4.4                       |         | ed Work                                              |

|   | 4.5                       | Concl   | usions                                               |

| 5 | In-C                                                                        | Cache O                                                                                                                                       | Coherence Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 133                                                                                            |

|---|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 5.1                                                                         | Backg                                                                                                                                         | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 134                                                                                            |

|   |                                                                             | 5.1.1                                                                                                                                         | CMP Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140                                                                                            |

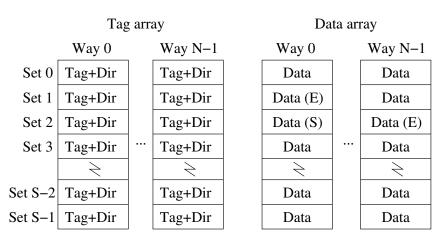

|   |                                                                             | 5.1.2                                                                                                                                         | Inclusive Cache with Tag-Embedded Sharing Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 140                                                                                            |

|   |                                                                             | 5.1.3                                                                                                                                         | Sparse Directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 141                                                                                            |

|   |                                                                             | 5.1.4                                                                                                                                         | Scalable Coherence Directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 143                                                                                            |

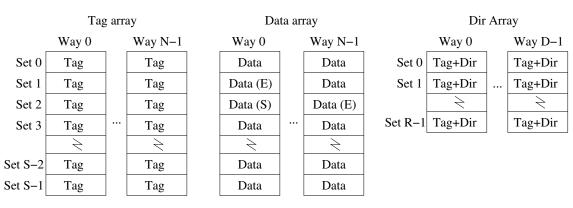

|   | 5.2                                                                         | ICCI:                                                                                                                                         | In-Cache Coherence Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                |

|   |                                                                             | 5.2.1                                                                                                                                         | ICCI LLC Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 147                                                                                            |

|   |                                                                             | 5.2.2                                                                                                                                         | Storage Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149                                                                                            |

|   |                                                                             | 5.2.3                                                                                                                                         | Contextualizing ICCI's Directory Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 149                                                                                            |

|   |                                                                             | 5.2.4                                                                                                                                         | Contextualizing ICCI's Cache Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 151                                                                                            |

|   | 5.3                                                                         | Evalu                                                                                                                                         | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 152                                                                                            |

|   |                                                                             | 5.3.1                                                                                                                                         | Parameter Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 152                                                                                            |

|   |                                                                             | 5.3.2                                                                                                                                         | Results for $8 \times S/P$ Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                |

|   |                                                                             | 5.3.3                                                                                                                                         | Results for Lower S/P Ratios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                |

|   |                                                                             | 5.3.4                                                                                                                                         | Exploratory Analysis of ICCI's Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 164                                                                                            |

|   | 5.4                                                                         | Relate                                                                                                                                        | ed Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                |

|   | 5.5                                                                         | Concl                                                                                                                                         | usions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 182                                                                                            |

|   |                                                                             |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                |

| 6 | Dvr                                                                         | namic I                                                                                                                                       | Policies for Hybrid Photonic-Electronic NoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 185                                                                                            |

| 6 | -                                                                           |                                                                                                                                               | Policies for Hybrid Photonic-Electronic NoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>185</b><br>186                                                                              |

| 6 | <b>Dyr</b><br>6.1                                                           | Backg                                                                                                                                         | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 186                                                                                            |

| 6 | -                                                                           | Backg<br>6.1.1                                                                                                                                | Ring-based Photonic Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 186<br>188                                                                                     |

| 6 | -                                                                           | Backg<br>6.1.1<br>6.1.2                                                                                                                       | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 186<br>188<br>189                                                                              |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3                                                                                                              | ground          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 186<br>188<br>189<br>191                                                                       |

| 6 | -                                                                           | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna                                                                                                      | ground          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 186<br>188<br>189<br>191<br>192                                                                |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1                                                                                             | ground          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 186<br>188<br>189<br>191<br>192<br>192                                                         |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1<br>6.2.2                                                                                    | ground          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size          AVAIL: Ring Availability                                                                                                                                                                                                                                                                                                                                                                                                                      | 186<br>188<br>189<br>191<br>192<br>192<br>194                                                  |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dynat<br>6.2.1<br>6.2.2<br>6.2.3                                                                          | ground          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size          AVAIL: Ring Availability                                                                                                                                                                                                                                                                                                                                                                                                                      | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195                                           |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                  | ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199                                    |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dynat<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu                                                        | ground       Ring-based Photonic Networks       Ring-based Photonic Networks         Case Study Photonic Networks       Ring-based Photonic Networks         Arbitration and Pipelined Transmission       Ring Arbitration         mic Management Policies for Hybrid NoCs       Ring Availability         SIZE: Message Size       Ring Availability         Distance Dependent Availability       Ring Availability         Photonic-Electronic Interface       Ring Availability                                                                                                                                                                                    | 186<br>188<br>189<br>191<br>192<br>192<br>192<br>194<br>195<br>199                             |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1                                                | round          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size          AVAIL: Ring Availability          Distance Dependent Availability          Photonic-Electronic Interface          ation          Evaluation Methodology for 16-Endpoint NoCs                                                                                                                                                                                                                                                                   | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199<br>199<br>200                      |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dynat<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1<br>6.3.2                                      | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 186<br>188<br>189<br>191<br>192<br>192<br>192<br>194<br>195<br>199<br>199<br>200<br>203        |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1<br>6.3.2<br>6.3.3                              | round          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size          AVAIL: Ring Availability          Distance Dependent Availability          Photonic-Electronic Interface          ation          Evaluation Methodology for 16-Endpoint NoCs          Results for 16-Endpoint Hybrid NoCs                                                                                                                                                                                                                      | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199<br>200<br>203<br>205               |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dynat<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                    | round                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199<br>200<br>203<br>205<br>213        |

| 6 | 6.1                                                                         | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dyna<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>Relate           | round          Ring-based Photonic Networks          Case Study Photonic Networks          Arbitration and Pipelined Transmission          mic Management Policies for Hybrid NoCs          SIZE: Message Size          AVAIL: Ring Availability          Distance Dependent Availability          Photonic-Electronic Interface          ation          Evaluation Methodology for 16-Endpoint NoCs          Results for 16-Endpoint Hybrid NoCs                                                                                                                                                                                                                      | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199<br>200<br>203<br>205<br>213<br>218 |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Backg<br>6.1.1<br>6.1.2<br>6.1.3<br>Dynat<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Evalu<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>Relate<br>Concl | round       Ring-based Photonic Networks         Case Study Photonic Networks       Case Study Photonic Networks         Arbitration and Pipelined Transmission       Size         mic Management Policies for Hybrid NoCs       Size         SIZE: Message Size       Size         AVAIL: Ring Availability       Size         Distance Dependent Availability       Size         Photonic-Electronic Interface       Size         ation       Size         Evaluation Methodology for 16-Endpoint NoCs       Size         Results for 16-Endpoint Hybrid NoCs       Size         Results for 64-Endpoint Hybrid NoCs       Size         Availability NoCs       Size | 186<br>188<br>189<br>191<br>192<br>192<br>194<br>195<br>199<br>200<br>203<br>205<br>213<br>218 |

### Bibliography

229

# Índice

| Ín | dice                                                                         | 13  |

|----|------------------------------------------------------------------------------|-----|

| Li | sta de Figuras                                                               | 15  |

| Li | sta de Tablas                                                                | 19  |

| Re | esumen en Español                                                            | 21  |

| 1  | Introducción                                                                 | 31  |

| 2  | Conceptos Básicos                                                            | 53  |

| 3  | Protocolos de Coherencia Basados en Múltiples Areas                          | 65  |

| 4  | Organización de Caché Parcialmente Compartida Basada en Distan-<br>cia       | 99  |

| 5  | Información de Coherencia Almacenada en Caché                                | 133 |

| 6  | Políticas de Gestión Dinámica para Redes Híbridas Fotónicas-<br>Electrónicas | 185 |

| 7  | Conclusiones y Vías Futuras                                                  | 221 |

| Bi | bliografía                                                                   | 229 |

# **List of Figures**

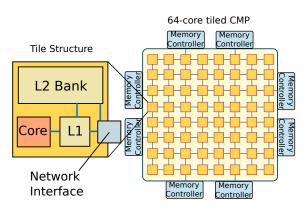

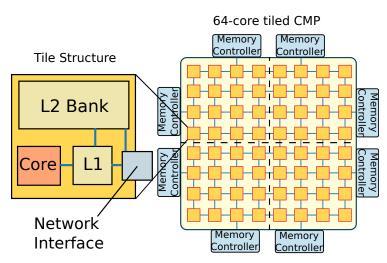

| 1.1  | Diagram of a 64-core tiled CMP                                         |

|------|------------------------------------------------------------------------|

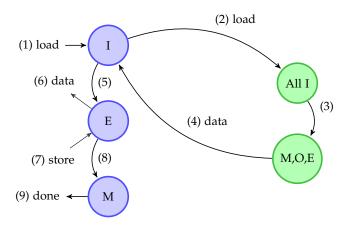

| 2.1  | Resolution of consecutive load and store operations                    |

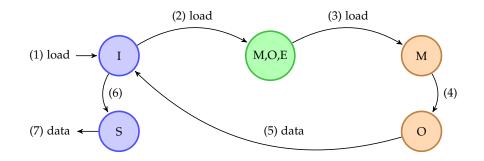

| 2.2  | Resolution of a load miss for which an owner private cache exists 60   |

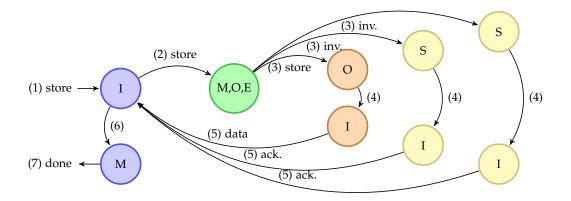

| 2.3  | Resolution of a store miss to a block for which an owner private cache |

|      | and sharers exist                                                      |

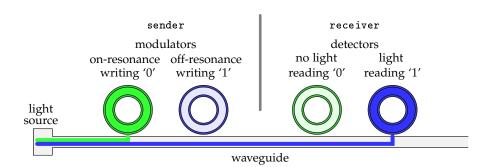

| 2.4  | Basics of photonic data transmission                                   |

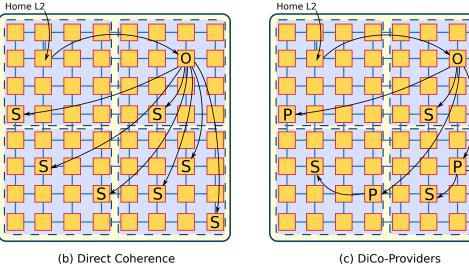

| 3.1  | Read request to deduplicated block                                     |

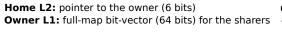

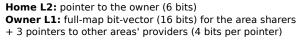

| 3.2  | Coherence information                                                  |

| 3.3  | Write request                                                          |

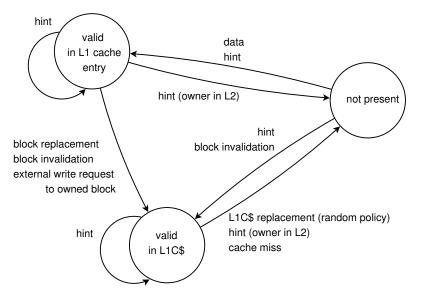

| 3.4  | Prediction state diagram                                               |

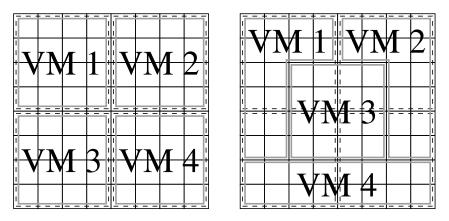

| 3.5  | VM configurations 86                                                   |

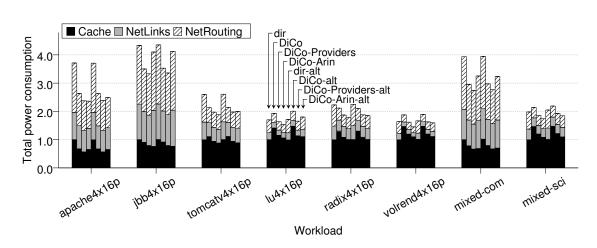

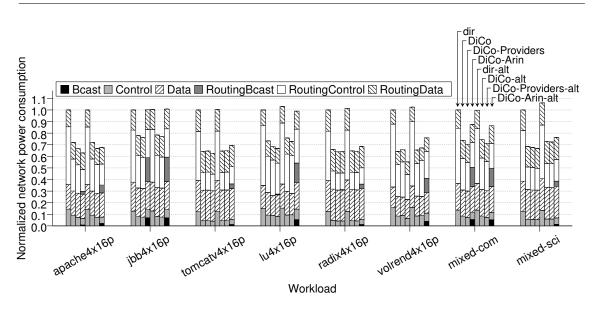

| 3.6  | Dynamic power consumption                                              |

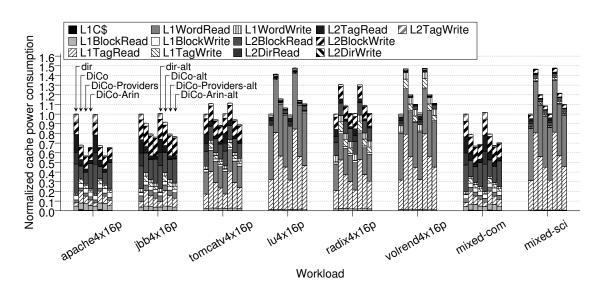

| 3.7  | Breakdown of cache dynamic power consumption 91                        |

| 3.8  | Breakdown of NoC dynamic power consumption                             |

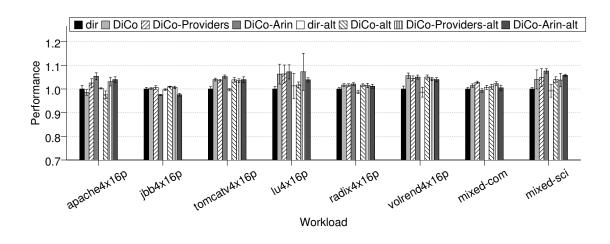

| 3.9  | Performance                                                            |

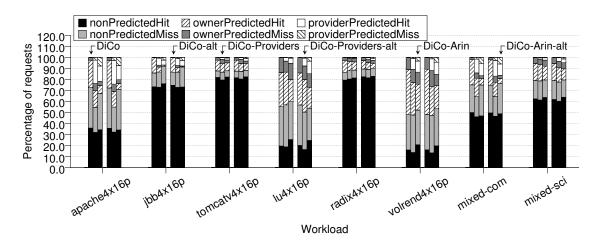

| 3.10 | Prediction accuracy                                                    |

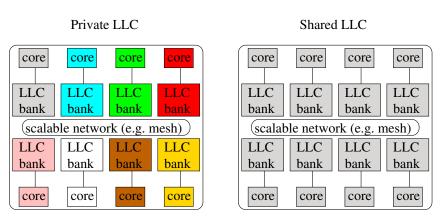

| 4.1  | Examples of private and shared last-level caches                       |

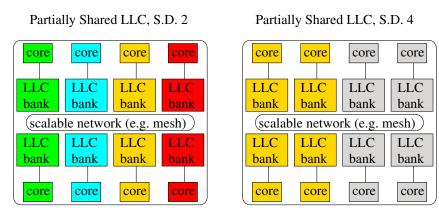

| 4.2  | Examples of partially-shared last-level caches                         |

| 4.3  | Diagram of a 64-core tiled CMP with a sharing degree of 16 103         |

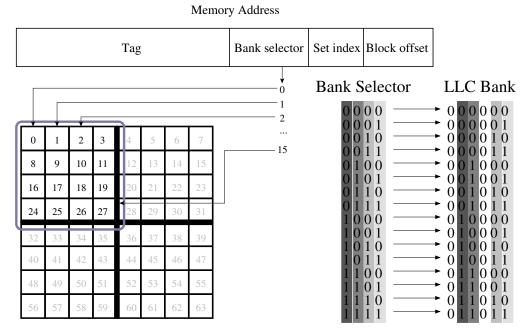

| 4.4  | Bank selection in a partially shared LLC                               |

| 4.5  | Cache miss breakdown                                                   |

| 4.6  | Average distance from cores to LLC banks                               |

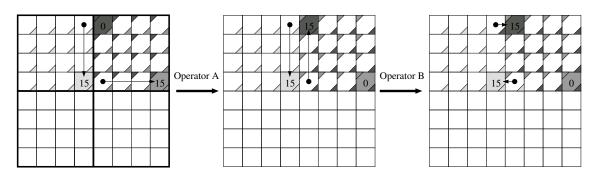

| 4.7  | DAPSCO search example                                                  |

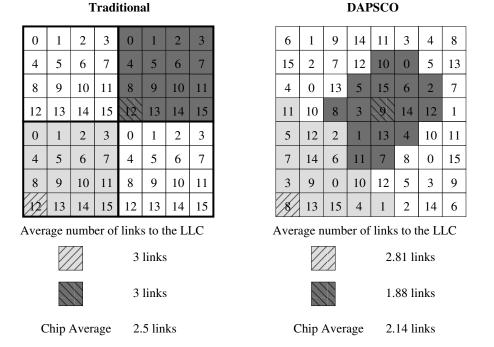

| 4.8  | DAPSCO and traditional partially shared caches with a sharing degree   |

|      | of 8                                                                   |

#### List of Figures

| 4.9   | DAPSCO and traditional partially shared caches with a sharing degree of 16        |

|-------|-----------------------------------------------------------------------------------|

| 1 10  |                                                                                   |

| 4.10  | DAPSCO and traditional partially shared caches with a sharing degree              |

|       | of 32                                                                             |

|       | Tessellations (solid lines) and label assignations to LLC banks 116               |

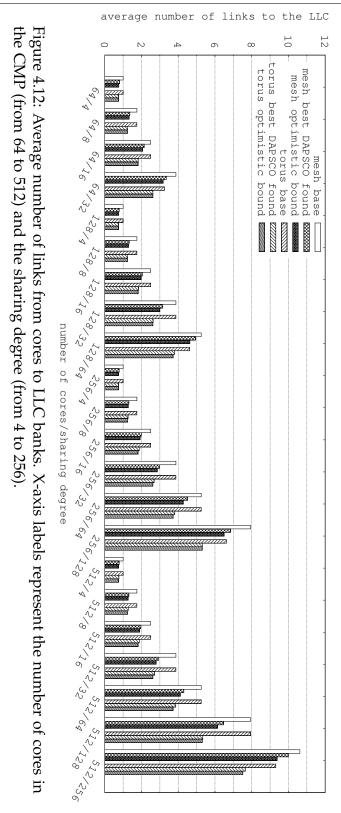

| 4.12  | Average distances from cores to LLCs in DAPSCO and traditional                    |

|       | from 64 to 512 cores                                                              |

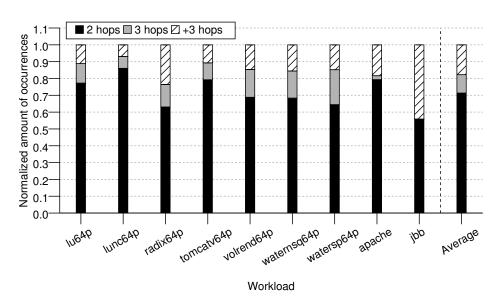

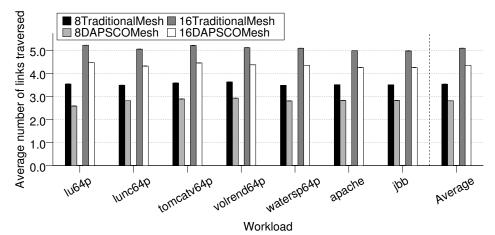

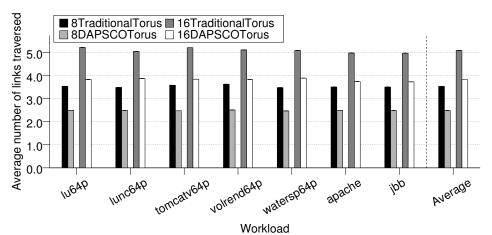

|       | Average number of links in 2-hop misses in the mesh                               |

| 4.14  | Average number of links in 2-hop misses in the torus                              |

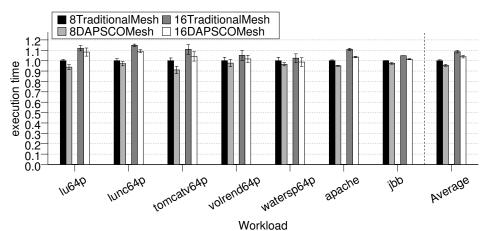

| 4.15  | Normalized execution time in the mesh                                             |

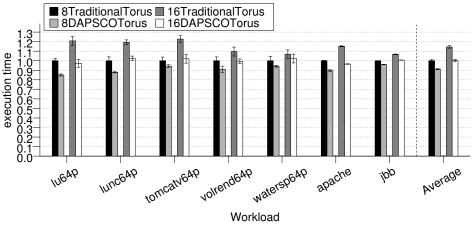

| 4.16  | Normalized execution time in the torus                                            |

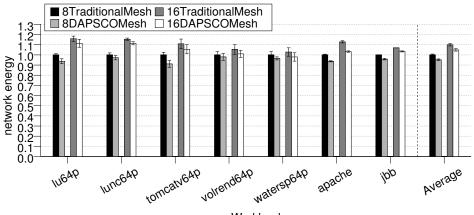

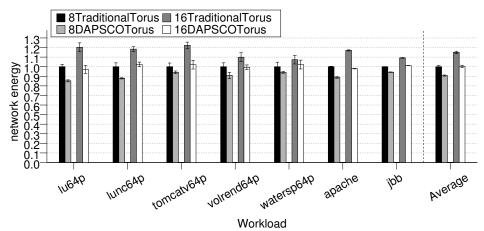

| 4.17  | Normalized energy consumption of the mesh interconnection network.126             |

| 4.18  | Normalized energy consumption of the torus interconnection network. 127           |

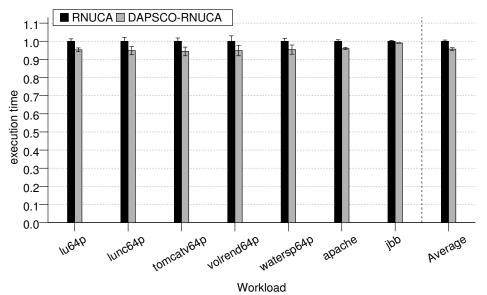

|       | Execution time of Reactive NUCA without and with DAPSCO 128                       |

|       |                                                                                   |

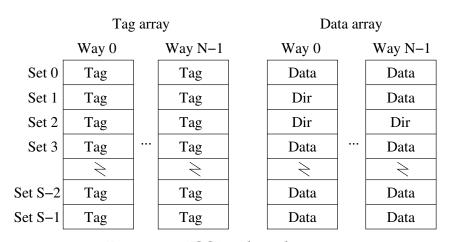

| 5.1   | Tag-embedded sharing information                                                  |

| 5.2   | Sparse directory                                                                  |

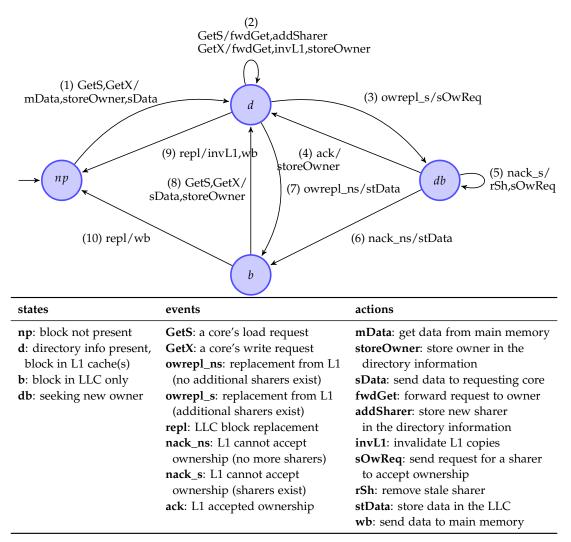

| 5.3   | ICCI cache coherence                                                              |

| 5.4   | ICCI's state diagram for the LLC                                                  |

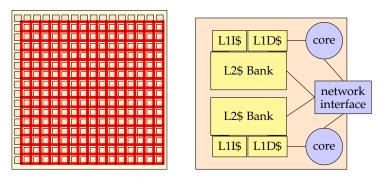

| 5.5   | 512-core CMP. Two tiles (each containing a core, private L1 caches and            |

|       | a shared L2 cache bank) share each router of the $16 \times 16$ mesh network. 153 |

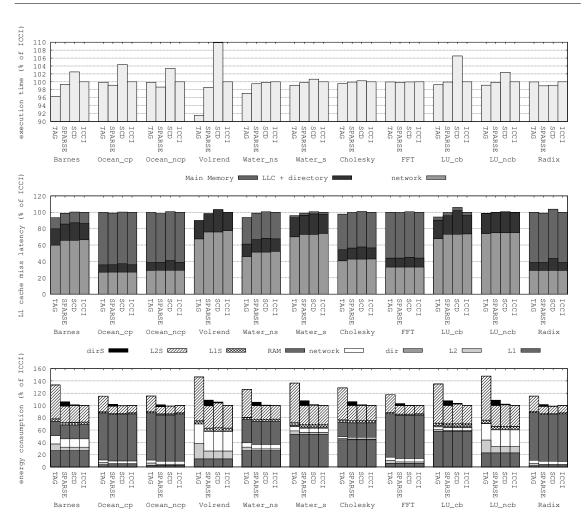

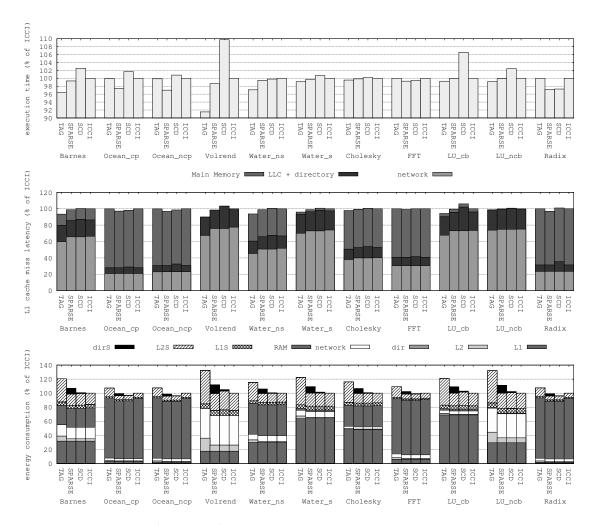

| 5.6   | Results for $8 \times S/P$ ratio. From top to bottom: execution time, average     |

|       | memory access time and energy consumption                                         |

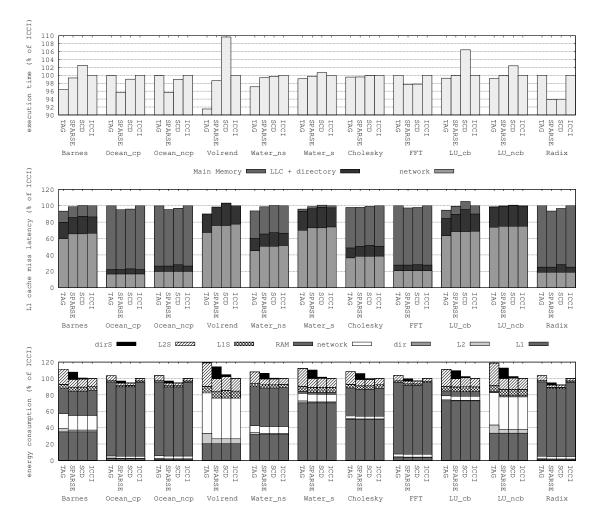

| 5.7   | Results for $4 \times S/P$ ratio. From top to bottom: execution time, average     |

|       | memory access time and energy consumption                                         |

| 5.8   | Results for $2 \times S/P$ ratio. From top to bottom: execution time, average     |

|       | memory access time and energy consumption                                         |

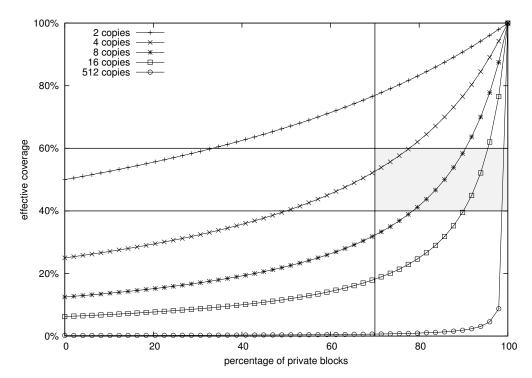

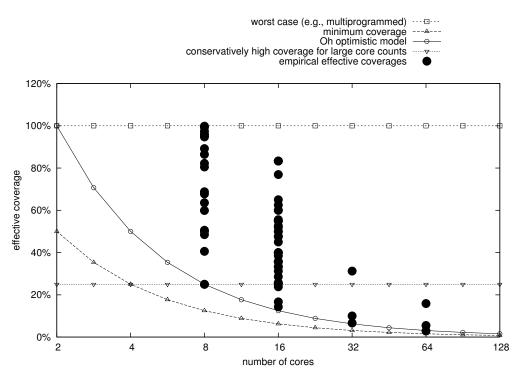

| 5.9   | Effective coverage depending on memory block sharing characteristics 167          |

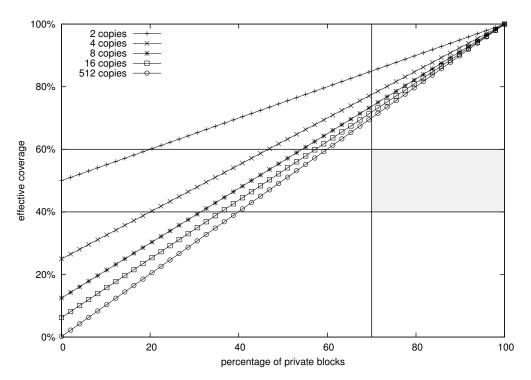

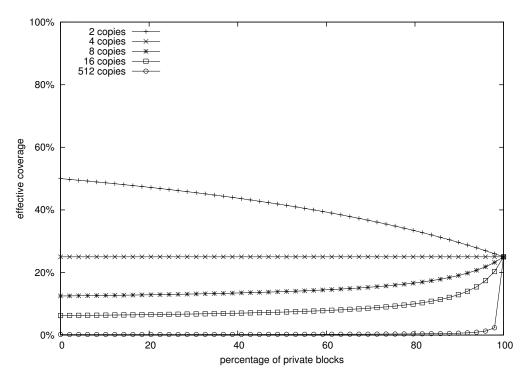

|       | Effective coverage depending on private-cache block sharing charac-               |

| 0.10  | teristics                                                                         |

| 5 11  | Survey of effective coverages                                                     |

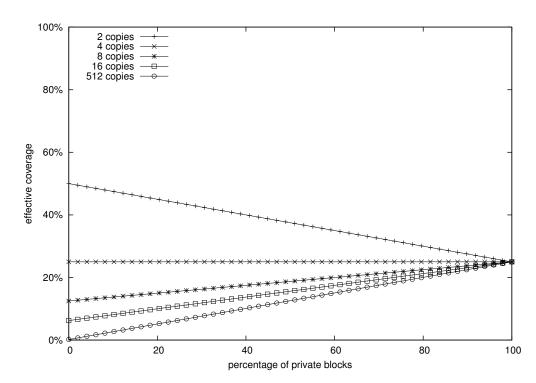

|       | Effective coverages with 75%-effectiveness private-block coherence                |

| 5.12  | deactivation.                                                                     |

| 5 1 2 | Effective coverages with 75%-effectiveness private-block coherence                |

| 5.15  | deactivation                                                                      |

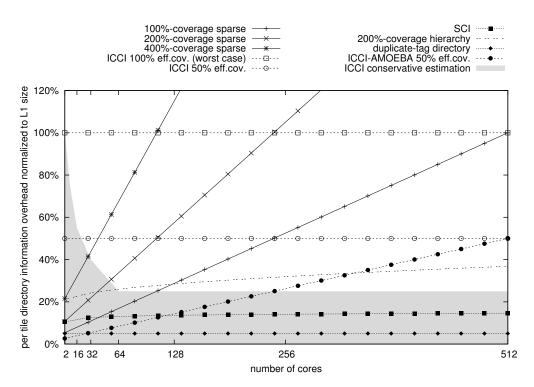

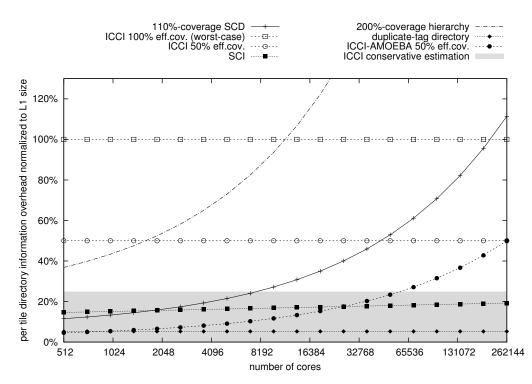

| 511   | Cache coherence storage overhead from 2 to 512 cores                              |

|       | -                                                                                 |

| Э.15  | Cache coherence storage overhead from 512 to 256 K cores 179                      |

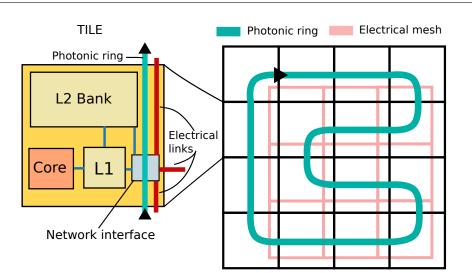

| 6.1 | Hybrid photonic-electronic NoC on a 16-core tiled CMP. Every tile can   |

|-----|-------------------------------------------------------------------------|

|     | read from or write in the photonic ring                                 |

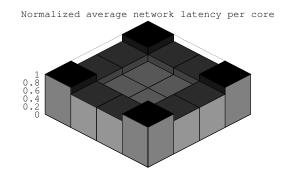

| 6.2 | Average network latency perceived by cores depending on their posi-     |

|     | tion in a 16-core CMP. Cores in the corners suffer 50% longer latencies |

|     | than cores in the center                                                |

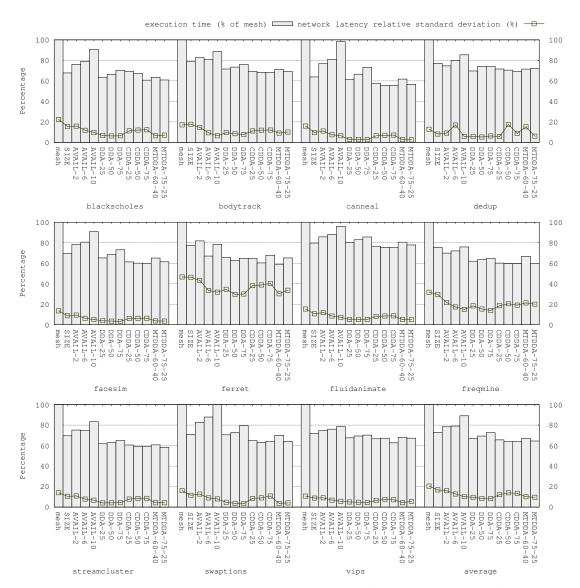

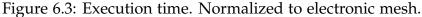

| 6.3 | Execution time. Normalized to electronic mesh                           |

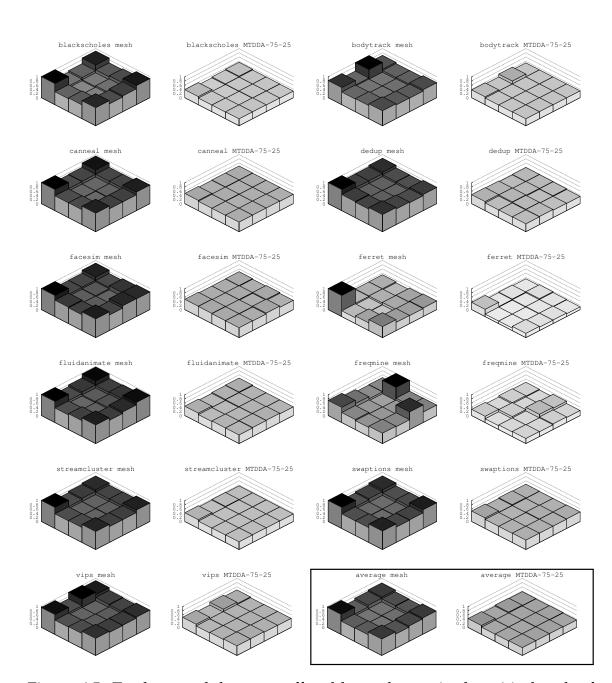

| 6.4 | Network latency. Normalized to electronic mesh                          |

| 6.5 | Total network latency suffered by each core in the critical path of L1  |

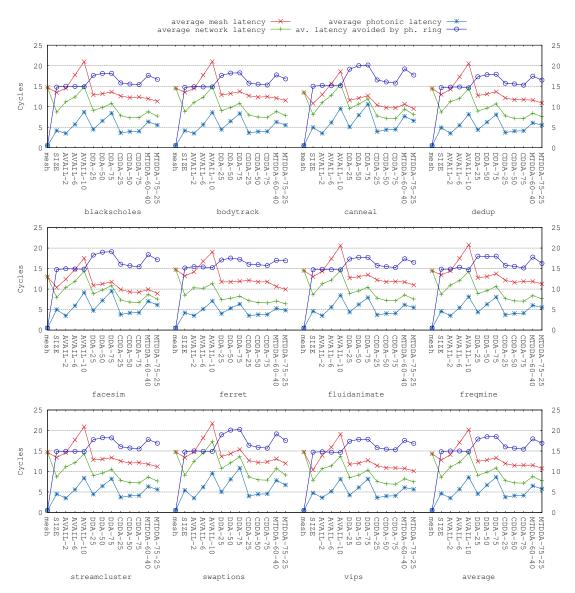

|     | cache misses                                                            |

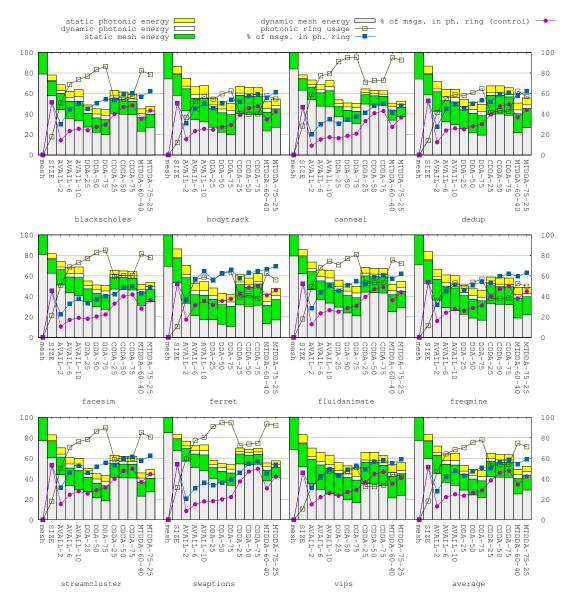

| 6.6 | Network energy consumption (normalized to electronic mesh) and          |

|     | photonic ring usage                                                     |

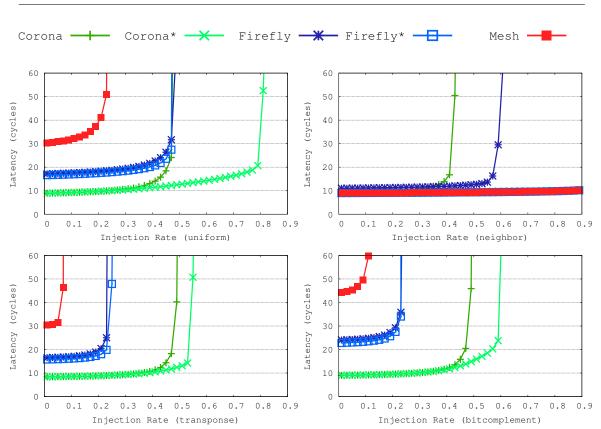

| 6.7 | Load latency curves for uniform, neighbor, transpose and bitcomp        |

|     | traffic. 256-bit photonic datapath width                                |

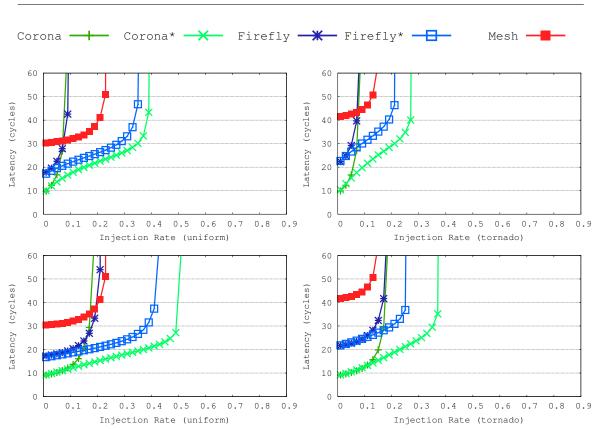

| 6.8 | Load latency curves for uniform and tornado traffic, using 32-bit (top) |

|     | and 64-bit (bottom) photonic datapath width                             |

# **List of Tables**

| 2.1 | Allowed combinations of states in the private caches for a memory block | 55  |

|-----|-------------------------------------------------------------------------|-----|

| 2.2 | Request messages sent to the home node upon events in the requestor     | 57  |

| 2.3 | State transitions and actions upon the reception of requests in the     |     |

|     | home node                                                               | 58  |

| 2.4 | State transitions in the private caches                                 | 58  |

| 3.1 | Actions performed in DiCo-Providers upon the reception of a request     | 78  |

| 3.2 | Actions taken by DiCo-Providers upon a block replacement from L1        | 80  |

| 3.3 | System configuration.                                                   | 84  |

| 3.4 | Benchmark configurations                                                | 85  |

| 3.5 | Coherence memory overhead                                               | 87  |

| 3.6 | Leakage power of the caches per tile                                    | 88  |

| 3.7 | Storage overhead of the protocols depending on the number of cores      |     |

|     | and number of areas of the chip with respect to the tag and data arrays |     |

|     | of the caches                                                           | 89  |

| 3.8 | Links traversed per miss for misses solved on a remote L1 cache         |     |

|     | depending on the number of cores and number of areas of the chip        |     |

|     | for each protocol.                                                      | 95  |

| 4.1 | Sharing information overhead of partially shared caches on the total    |     |

| 1.1 | cache capacity of the chip                                              | 106 |

| 4.2 | DAPSCO circuits characteristics                                         |     |

| 4.3 | System characteristics.                                                 |     |

| 4.4 | Benchmark configurations                                                |     |

| 4.5 | Average distance from cores to LLC banks.                               |     |

| 1.0 |                                                                         | 120 |

| 5.1 | Comparative of directory schemes                                        | 150 |

| 5.2 | ICCI and other cache hierarchies                                        | 152 |

#### LIST OF TABLES

| 5.3                             | Simulated machine                                                                                              |

|---------------------------------|----------------------------------------------------------------------------------------------------------------|

| 5.4                             | Directory size requirements for the schemes tested. Size is given as a                                         |

|                                 | percentage of the aggregate capacity of the tracked caches, assuming                                           |

|                                 | a 512-core CMP and 64-byte lines                                                                               |

| 5.5                             | SPLASH-2 program sizes                                                                                         |

| 5.6                             | LLC miss rate for $8 \times \text{S/P}$ ratio                                                                  |

| 5.7                             | 3-hop misses as a percentage of all L1 cache misses                                                            |

| 5.8                             | Data writebacks (as a percentage of L1 writebacks)                                                             |

| 5.9                             | LLC miss rate for $4 \times$ S/P ratio                                                                         |

| 5.10                            | LLC miss rate for $2 \times S/P$ ratio                                                                         |

|                                 |                                                                                                                |

| 6.1                             | Feature comparison between case study NoCs. Values with (*) are                                                |

| 6.1                             | Feature comparison between case study NoCs. Values with (*) are estimations based on the available information |

| 6.1<br>6.2                      | · · · · · · · · · · · · · · · · · · ·                                                                          |

|                                 | estimations based on the available information                                                                 |

| 6.2                             | estimations based on the available information                                                                 |

| 6.2<br>6.3                      | estimations based on the available information                                                                 |

| 6.2<br>6.3<br>6.4               | estimations based on the available information                                                                 |

| 6.2<br>6.3<br>6.4<br>6.5        | estimations based on the available information                                                                 |

| 6.2<br>6.3<br>6.4<br>6.5<br>6.6 | estimations based on the available information                                                                 |

### Resumen

#### Introducción y Motivación

En las últimas décadas, la computación moderna ha proporcionado constantes progresos en todas las áreas de nuestras vidas. Esto ha sido posible gracias a un continuo crecimiento exponencial del rendimiento de los microprocesadores. Desafortunadamente, la informática se enfrenta a un enorme reto a día de hoy debido a limitaciones físicas de la tecnología actual que suponen una barrera al incremento de rendimiento al que nos hemos acostumbrado.

Durante la mayor parte de la evolución de los microprocesadores desde que el primero fuera fabricado en 1971 (el Intel 4004), su rendimiento ha mejorado mediante el uso de frecuencias de reloj más altas y diseños de arquitectura más complejos, posibilitados por el continuo desarrollo de transistores más pequeños y más rápidos. En cada nueva generación, los procesadores eran capaces de explotar más paralelismo a nivel de instrucción (ILP) de manera dinámica y de hacerlo a una frecuencia de operación mayor, doblando su rendimiento cada dos años aproximadamente.

Este crecimiento exponencial de rendimiento fue posible gracias a que el escalado clásico de los transistores asociaba a la reducción de tamaño una reducción exponencial del consumo energético. Esto mantenía la densidad de potencia disipada en los nuevos chips dentro de unos límites manejables a pesar del aumento de frecuencia y de complejidad en la circuitería, permitiendo siempre reducir la energía disipada por operación ejecutada. Esta constante reducción de la energía por operación ha sido la piedra angular sobre la que se ha sustentado la evolución de la informática. Si la miniaturización no hubiese llevado asociada tal mejora energética en los transistores, la potencia necesaria para alimentar servidores como los de hoy en día sería inaceptable, los dispositivos móviles modernos vaciarían rápidamente sus baterías, y además ningún medio de refrigeración

#### Resumen

razonable sería capaz de evitar que estos chips ardiesen literalmente, haciendo imposible su existencia.

Desafortunadamente, aunque aún somos capaces de integrar el doble de transistores en el mismo área cada 18–24 meses, en cierto momento (alrededor de 2004, con el paso de un tamaño de transistor de 65 nm a uno de 45 nm) cuestiones físicas nos hicieron incapaces de seguir escalando las características energéticas de los transistores de la manera clásica, perdiendo gran parte de los beneficios asociados. Esta incapacidad puso y sigue poniendo en riesgo futuras reducciones de la energía consumida por operación, y por tanto futuros avances en el rendimiento de los procesadores.

Para continuar mejorando el rendimiento con estas restricciones energéticas no podemos seguir confiando en la miniaturización de los transistores como antes, pues ésta ya no puede contrarrestar los costes energéticos de incrementar la frecuencia y usar simultáneamente más transistores en diseños más complejos. Por tanto, ahora es el propio diseño de los chips el que debe tener como objetivo la eficiencia energética, para así seguir reduciendo la energía consumida por operación y poder proporcionar más rendimiento sin elevar el consumo energético. Es por ello que los multiprocesadores en un chip (CMPs), que integran varios cores relativamente simples, fueron adoptados como una alternativa más eficiente energéticamente que los procesadores que integran un único núcleo más complejo. La idea detrás de este cambio radica en que aumentar la complejidad del diseño de un core incrementa su rendimiento de manera proporcional a la raíz cuadrada del incremento en el número de transistores empleados, y a la vez la mayor complejidad de los circuitos resultantes, necesaria para poder identificar y ejecutar un mayor número de operaciones en paralelo, aumenta el factor de actividad de los transistores (es decir, el número de transistores que se activan simultáneamente para poder realizar cada operación). Mayor número de transistores y mayor factor de actividad significan un crecimiento insostenible del consumo energético por operación. En comparación, replicar el diseño del mismo core colocando varios cores adyacentes puede aumentar el rendimiento de manera proporcional al número de transistores empleados y sin aumentar el factor de actividad de los transistores. Si queremos hacer realidad este ideal de crecimiento de rendimiento proporcional al área y al consumo energético, lo que permitiría mejorar el rendimiento con avances en la tecnología de fabricación más modestos, debemos superar los retos que plantea la existencia de un número cada vez mayor de cores en el chip.

En particular, explotar el paralelismo a nivel de hilo (TLP) proporcionado por números de cores cada vez mayores requiere aplicaciones paralelas que son difíciles de programar. No es ninguna sorpresa que el modelo de programación paralela más extendido sea a la vez el más simple: memoria compartida. Los modelos de memoria compartida son normalmente implementados sobre un protocolo de coherencia de caché, que es necesario para realizar el manejo implícito de las memorias caché privadas que ocultan la mayor parte de la diferencia de velocidad entre los cores y la lenta memoria DRAM principal. Esto crea la necesidad de luchar contra los problemas de escalabilidad de los mecanismos de coherencia de caché para no crear otra barrera a la eficiencia energética. En particular, el porcentaje de área ocupada por los mecanismos de coherencia número de cores.

Un segundo problema particular de los CMPs es que los multiprocesadores son especialmente propensos a movimientos de datos entre distintas partes del chip, lo que a su vez puede reducir la eficiencia energética, llegando a consumir la mayor parte de la energía en transmisión de datos. Si no se explota adecuadamente la localidad de datos, y si no se adoptan nuevas tecnologías de transmisión más eficientes, el consumo energético de la comunicación on-chip puede convertirse en un serio problema para la evolución de la informática.

En esta tesis hemos abordado estos dos retos específicos de los multicores, la escalabilidad del protocolo de coherencia y el consumo energético de la red de interconexión. Como modelo de estudio hemos usado un diseño tiled-CMP en el que el rendimiento aumenta mediante replicación de *tiles*, bloques básicos que contienen un core, recursos de caché y una interfaz de red para comunicarse mediante una red escalable como una malla. En particular, las siguientes oportunidades motivan esta tesis:

- El protocolo de coherencia de caché coordina la comunicación en el chip y puede optimizarse para mejorar la proximidad de los datos, también permitiendo un tamaño reducido para códigos de compartición exactos para mejorar la escalabilidad del mecanismo de coherencia.

- Las organizaciones de caché se pueden optimizar para mejorar la proximidad de los datos reorganizando los mapeos que determinan qué cores acceden a qué bancos de caché, reduciendo la distancia y el número de retransmisiones en la red.

- Los recursos compartidos de la caché pueden usarse más eficientemente para almacenar datos e información de compartición, mejorando la escalabilidad de la coherencia de caché.

Las tecnologías fotónica y electrónica pueden combinarse para explotar las mejores características de cada una de ellas, aumentando la eficiencia de la red con respecto a usar tan sólo una de estas tecnologías, y se necesitan políticas de gestión adecuadas para hacerlo eficientemente.

Como resultado de la investigación realizada proponemos mecanismos para reducir el impacto de la coherencia de caché y el consumo de la red de interconexión. Las contribuciones de esta tesis se resumen en los siguientes apartados.

### Protocolos de Coherencia con Multiples Areas

Proponemos una familia de protocolos de coherencia que dividen el chip en áreas estáticamente para reducir la sobrecarga de almacenamiento y mejorar la proximidad entre los datos y los cores, consiguiendo reducir el consumo energético y acelerar la operación del chip. Estos protocolos mantienen información de coherencia por área y utilizan punteros que enlazan las áreas para mantener un único dominio de coherencia en todo el chip. Este esquema de almacenamiento proporciona una reducción de espacio de almacenamiento que es especialmente significativa para grandes números de cores (e.g., 93 % de reducción comparado con un directorio de vector de bits full-map para 1024 cores y usando tan solo 4 áreas).

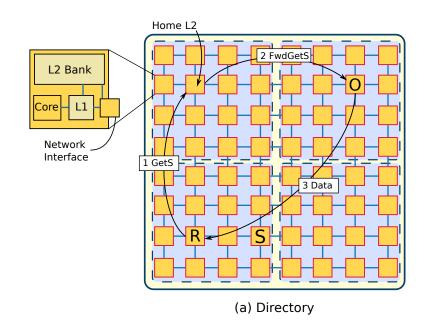

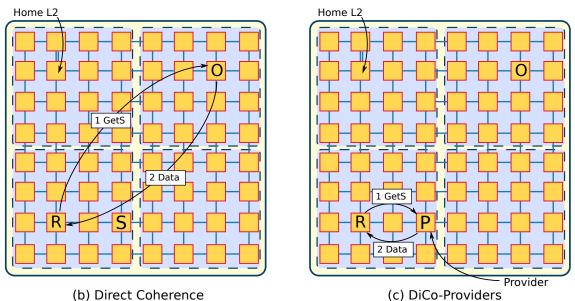

Además, el protocolo de coherencia selecciona dinámicamente un nodo por área para actuar como proveedor de los datos para los fallos de caché que se produzcan en su área. Los cores usan un mecanismo de predicción para alcanzar al proveedor del área para cada bloque, evitando la indirección típica del directorio y reduciendo la latencia media de los fallos de caché y el tráfico de red.

Comparado con un directorio de vector de bits full-map, estos protocolos reducen el consumo estático del directorio un 54 % y el consumo dinámico de las cachés y la red hasta un 38 % en un multiprocesador de 64 cores con cuatro áreas, sin mostrar degradación del rendimiento, y hasta mejorándolo un 6 % en el servidor web apache. Estos protocolos fueron propuestos en el contexto de la consolidación de servidores por medio de virtualización, pero son igualmente aplicables a cargas multiprogramadas y aplicaciones paralelas.

### Organización de Caché Parcialmente Compartidas Basada en Distancia (DAPSCO)

Cuanto mayor sea el número de cores en un chip, más interesantes resultan los diseños parcialmente compartidos para el último nivel de caché (LLC). En una caché parcialmente compartida tradicional los cores comparten sus bancos de LLC en grupos, resultando en un diseño que causa menos accesos a memoria que una LLC totalmente privada por core y menos tráfico de red y menor latencia que una LLC totalmente compartida entre todos los cores. En una organización de caché parcialmente compartida el número de cores que forman cada grupo y comparten sus bancos de LLC es conocido como el *grado de compartición* de la caché.

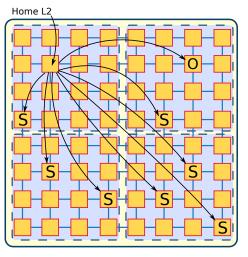

En este contexto, nosotros proponemos DAPSCO como una optimización a las cachés parcialmente compartidas tradicionales, basándonos en la observación de que agrupar los bancos de LLC y cores en grupos no es la organización de caché más eficiente. Para ilustrar las ineficiencias del esquema tradicional, basta con observar que un core situado en la esquina de un grupo se encuentra de media notablemente más lejos de los bancos de LLC del grupo que un core situado en el centro. DAPSCO usa un mapeo entre cores y bancos de LLC más eficiente en el que no existen grupos y cada core accede a los bancos de LLC que le rodean, minimizando así la distancia media a la LLC.

El mapeo de DAPSCO mantiene las mismas propiedades deseables de las organizaciones tradicionales: los bancos de LLC almacenan subconjuntos del espacio de memoria y cada core accede a un banco por cada subconjunto para alcanzar el espacio de memoria completo.

Hemos generado y evaluado configuraciones de DAPSCO para números de cores desde 64 hasta 512 con distintos grados de compartición y topologías de red. Por ejemplo, DAPSCO reduce el número medio de enlaces para alcanzar la LLC un 33% en un CMP de 512 cores con un grado de compartición de 128, reduciendo la latencia de los accesos LLC y el uso de energía de manera similar.

DAPSCO fue evaluado mediante simulación detallada en un CMP de 64 cores para confirmar sus ventajas teóricas. Además, DAPSCO casi no introduce sobrecarga, ya que tan sólo requiere cambios menores en algunos circuitos combinacionales ya presentes en el chip.

# Información de Coherencia Almacenada en Caché (ICCI)

ICCI es una nueva organización de caché que hace que la sobrecarga de almacenamiento asociada a mantener un directorio sea escalable. ICCI se basa en almacenar entradas de directorio en los recursos de caché compartidos ya existentes en el chip, proporcionando coherencia de caché hardware económica para gran número de cores (e.g., 512). ICCI consigue tiempos de ejecución cercanos a un directorio no escalable y reduce a la vez el consumo de energía del sistema de memoria notablemente. La idea detrás de ICCI es que conforme aumenta el número de cores y el grado de compartición de los datos también lo hace, menos entradas de directorio por core son necesarias, ya que cada entrada mantiene la información de compartición del mismo bloque en más cachés privadas.

ICCI hace un uso más eficiente de los recursos de caché permitiendo de manera dinámica que las entradas del último nivel de caché almacenen bloques o códigos de compartición de manera alternativa, resultando en un diseño más compacto, sencillo y eficiente que si se usa una estructura dedicada para bloques y otra para información de directorio. Mediante el aprovechamiento dinámico de entradas de la LLC para almacenar información de directorio, solo el número de entradas realmente necesarias para información de compartición son reservadas en cada momento, dejando el resto de entradas libres para almacenar datos.

Hemos evaluado analíticamente que el uso de recursos de ICCI para información de directorio es asumible para grandes números de cores. Con grados de compartición encontrados en la literatura ICCI usa incluso menos espacio que alternativas escalables en términos de área (pero no de rendimiento o consumo energético) como SCI o tags duplicados. De hecho, contrariamente a otros esquemas, ICCI usa menos espacio para almacenar información de directorio conforme aumenta el número de cores, debido a la mayor compartición y al tamaño fijo de las entradas usadas (el tamaño de una entrada de la LLC).

En caso de no existir compartición de datos, el uso de mecanismos ya propuestos para mantener el estado privado de las páginas en la tabla de páginas hace que ICCI no use ningún espacio en LLC para información de directorio para las páginas privadas, lo cual es una característica única hasta el momento. Otra ventaja de ICCI es su simplicidad: cambios muy sencillos en el sistema con respecto a un directorio tradicional de vector de bits son suficientes para implementar ICCI, lo que contrasta con la complejidad de otras propuestas. Además, el diseño de ICCI garantiza que se producirá una cantidad despreciable de invalidaciones de bloques activos causadas por reemplazos de directorio comparado con el gran volumen de éstas que pueden producirse potencialmente en los esquemas tradicionales. Los resultados para un CMP de 512 cores muestran que ICCI reduce el consumo de energía del sistema de memoria en hasta un 48 % comparado con un directorio embebido en los tags, y de un 8 % comparado con el recientemente propuesto Directorio de Coherencia Escalable (Scalable Coherence Directory, SCD), al que ICCI también mejora en tiempo de ejecución de las aplicaciones y área utilizada, resultando en un efecto multiplicativo en la mejora en eficiencia energética con respecto a SCD. Además, ICCI puede usarse en combinación con códigos de compartición más elaborados para aplicarlo a números de cores extremadamente altos (e.g., 1 millón).

### Políticas Dinámicas de Gestión para Redes Híbridas Fotónicas-Electrónicas