**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<a href="www.tesisenred.net">www.tesisenred.net</a>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<a href="www.tesisenxarxa.net">www.tesisenxarxa.net</a>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

## **PhD Thesis**

## Common-mode Voltage Cancellation in Single-and Three-Phase Transformerless PV Power Converters

Gerardo Vázquez Guzmán

Barcelona, September 2012

## Common-mode Voltage Cancellation in Single-and Three-Phase Transformerless PV Power Converters

## Gerardo Vázquez Guzmán

Dissertation submitted to the PhD Doctorate

Office of the Universitat Politècnica de

Catalunya in partial fulfillment of the

requirements for the degree of Doctor of

Philosophy by the

# UNIVERSITAT POLITÈCNICA DE CATALUNYA

Electrical Engineering Department Research Center on Renewable Electrical Energy Systems

SEPTEMBER 2012

Common-mode Voltage Cancellation in Single- and Three-Phase Transformer-less PV Power Converters.

Research Projects:

ENE2011-29041-C02-01

Printed in Catalonia by the DEE-UPC

September 2012

UNIVERSITAT POLITÈCNICA DE CATALUNYA (UPC) Electrical Engineering Department (DEE) Research Center on Renewable Electrical Energy Systems (REES)

Colom, 1 08222 Terrassa-Barcelona, Spain Telephone: 0034-93 739 8156 Fax: 0034-93739 8236

Web: http://www.dee.upc.edu

## Acknowdledgements

This thesis was carried out under the supervision of Dr. Pedro Rodríguez who is a titular professor at Technical University of Catalonia, my sincere gratefulness for all his time, technical support and advices during the elaboration of the work done in this thesis. Without his help, this thesis would not have been possible.

I would like to express my sincere thanks to all my colleagues at Technical University of Catalonia: Álvaro Luna, Iñaki Candela, Daniel Aguilar, Joan Rocabert, Raúl Santiago Muñoz, Emiliano Aldabas, Juan Ramon Hermoso, Gustavo M. S. Azevedo, Hernan Miranda and Hector Beltrán, thanks for your friendly companionship, technical support and advices during my stay in Terrassa.

I want to express specially thank to Dr. Remus Teodorescu and Dr. Tamás Kerekes for their support in all aspects during my stay as a visiting student at Institute of Energy Technology in Aalborg, Denmark. Thanks for share with me your knowledge and time.

Thanks also for all institutions that provide me their financial support to carry out this thesis project specially to CONACYT (Consejo Nacional de Ciencia y Tecnología en México), UPC (Universitat Politècnica de Catalunya en España) and MCYT (Ministerio de Ciencia y Tecnología en España).

And last but not least; mi más profundo agradecimiento a mis padres; María de los Ángeles Guzmán y José Luis Vázquez por educarme y enseñarme a vivir. Gracias a mis hermanos, Olga, Luis, Ernesto, Ángeles y Vane por darme todo su apoyo durante estos duros y largos cinco años, de corazón muchas gracias, sin su apoyo esto no hubiera sido posible. Mi especial gratitud para ti Daly por todo tu amor y por darme ese apoyo tan necesario en los momentos difíciles.

### Resumen

La generación de energía eléctrica es una causa de gran preocupación alrededor del mundo. Se han hecho una gran cantidad de esfuerzos en este sentido para intentar cubrir la creciente demanda de energía eléctrica. Además del aumento en la demanda de energía eléctrica se requiere que sea renovable. Debido a esto, muchos países están haciendo grandes inversiones en sistemas de generación de energía eléctrica a partir de fuentes renovables como la energía del viento y la energía solar.

Los sistemas que generan energía eléctrica a partir de energía solar actualmente proporcionan un alto porcentaje del total de energía producida. De acuerdo con el último reporte de la agencia internacional de energía (IEA por sus siglas en inglés) en referencia al programa de sistemas de potencia fotovoltaica (PVPS por sus siglas en inglés), el total de potencia fotovoltaica instalada en el mundo hasta finales de 2009 fue de alrededor de 20.3 GW de los cuales 6.188 GW fueron instalados en 2009. Del total de potencia fotovoltaica instalada en 2009, 6.113 GW corresponden a sistemas conectados a la red eléctrica. El crecimiento de este tipo de sistemas se debe a la introducción de nuevas tecnologías y desarrollos que han permitido reducir los costes de diseño, manufactura e instalación de una planta solar.

Dado que el mayor porcentaje del total de la energía fotovoltaica instalada proviene de sistemas conectados a la red eléctrica, este trabajo de tesis está enfocado al análisis y a la presentación de soluciones en sistemas fotovoltaicos conectados a la red eléctrica sin transformador, los cuales pueden proporcionar eficiencias más altas que aquellos que usan transformador. Cuando no existe transformador entre el convertidor de potencia y la red eléctrica, corrientes parásitas pueden circular a través de los condensadores parásitos y causar serios problemas para los usuarios.

iv Resumen

La principal tarea de este trabajo de tesis ha sido analizar y evaluar la operación de diferentes topologías sin transformador que han sido encontradas en la bibliografía y de esta forma proponer algunas soluciones para minimizar o eliminar las corrientes parásitas que pueden presentarse debido a las características del panel fotovoltaico y de las condiciones de operación generales del sistema.

Este trabajo de tesis está dividido en 6 capítulos. En el primer capítulo se expone el estado del arte en el cual se analizan las principales topologías usadas en aplicaciones de sistemas fotovoltaicos. En este análisis general se incluyen topologías tanto de sistemas monofásicos como de sistemas trifásicos. Se exponen las ventajas y desventajas principales para cada caso.

El segundo capítulo proporciona un análisis detallado de las principales topologías sin transformador en sistemas monofásicos. Las topologías con mayor eficiencia han sido estudiadas y se propone una nueva estructura de convertidor que presenta la característica de reducir a valores cercanos a cero la corriente parásita. Se presentan resultados tanto de simulación como experimentales para justificar las características de la topología propuesta.

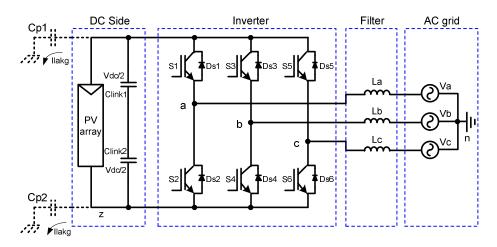

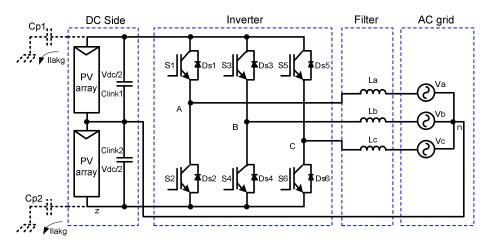

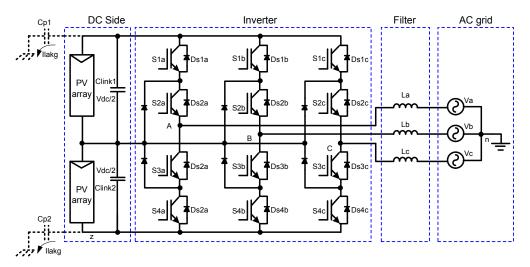

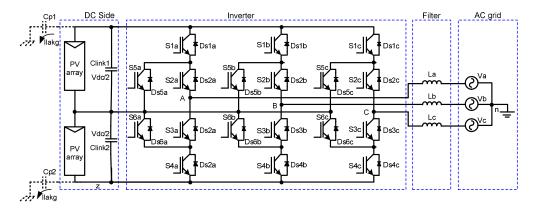

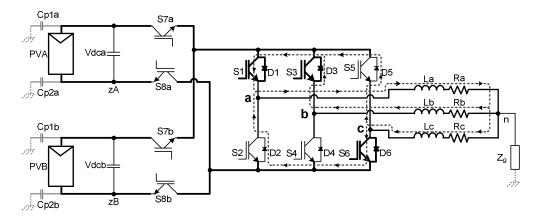

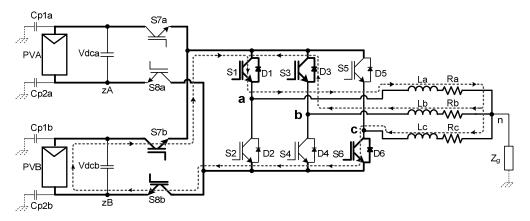

En el tercer capítulo se introduce el problema de las corrientes parásitas en los sistemas trifásicos empleando un modelo de tensión de modo común del sistema. Una vez hecho este análisis, se presenta una nueva topología que ha sido llamada FB10 y que resuelve el problema de las corrientes parásitas. La topología consiste básicamente de dos buses de corriente continua y de un inversor trifásico en puente completo. Se presenta también para el FB10 un modelo de modo común basado en el modelo convencional. Se proporcionan detalles de la estrategia de modulación empleada para controlar el convertidor y un análisis de pérdidas para cada semiconductor usando PSIM® (Power Simulator) como herramienta de simulación. En este caso también se han realizado las correspondientes simulaciones, asimismo se proporcionan resultados experimentales para justificar la topología.

En el capítulo cuatro se presentan cuatro diferentes estrategias de modulación diseñadas para controlar el convertidor FB10. Cada estrategia de modulación presenta un comportamiento distinto tanto en pérdidas de potencia como en distorsión harmónica y generación de corrientes parásitas. Por esta razón se ha desarrollado un análisis completo de estos parámetros. Se presentan resultados de simulación y experimentales que proporcionan los detalles de operación de las cuatro estrategias de modulación.

Dado que los paneles fotovoltaicos no son fuentes constantes de tensión, en el capítulo cinco se proponen dos estrategias que permiten compensar el sistema tanto en tensión como en potencia. Un breve análisis muestra cómo funciona cada una de ellas. Se presentan resultados de simulación y experimentales de las estrategias propuestas.

### **Abstract**

Covering the energy demand is an issue that is continuously cause of concern around the world. In the case of electrical energy many efforts have been lately addressed to cover the continuously growing electrical energy demand by means of using energy sources, different from those based on fossil fuels. In this sense, many countries have made a very strong bet on energy generation systems based on renewable sources, mainly wind and solar energy, something that has contributed to develop a solid and promising industry around these technologies.

At the present time, solar energy systems provide a significant percentage of the total energy production. According to the latest report of the International Energy Agency (IEA) regarding Photovoltaic Power System Program (PVPS), the cumulative installed PV power at the end of 2009 was around 20.3 GW out of which 6.188 MW were installed in 2009. From the total PV power installed in 2009, 6.113 MW were grid connected systems. The growth in the installed PV power is mainly due to the new technologies and developments that have permitted to reduce costs in the design and installation of PV systems.

As the major percentage of the total PV energy installed belongs to grid connected systems, this PhD deals with the analysis and proposals of transformerless grid-connected PV systems which, can provide higher efficiencies than PV systems with transformers. However, the lack of transformer between the electrical grid and the power converter generates serious problems regarding the appearance of leakage ground currents. This issue associated to these transformerless topologies, as well as the proposal of solutions oriented to overcome this drawback, is one of the main goals of this thesis work.

The main research task in this thesis work is to analyze and evaluate the operation of the different transformerless topologies presented in the bibliography and to provide some

Vİ Abstract

solutions to minimize the leakage ground current phenomenon in order to comply with the standard requirements.

This dissertation is divided in 6 chapters. The first chapter deals with the state of the art, in which the main topologies used in PV applications are analyzed. This analysis considers not only single-phase structures but also three-phase topologies.

The second chapter provides an analysis of single-phase transformerless topologies. The most efficient topologies are studied and a new topology is proposed. Simulations and experimental results are provided in order to endorse the proposed topology.

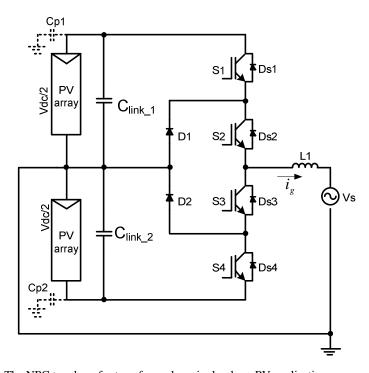

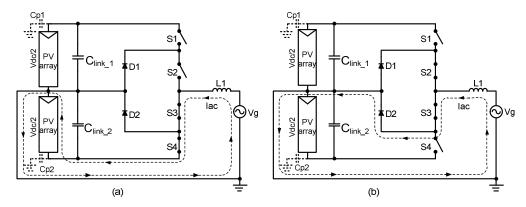

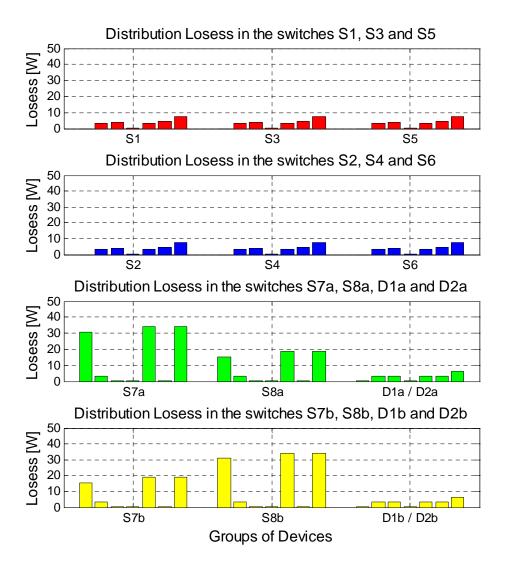

The third chapter introduces the three-phase systems and the leakage ground current problem. A general common mode model for the conventional three-phase system is showed. Then a three-phase transformerless topology namely FB10 (Full-Bridge 10) is presented. As it will be further discussed this topology consists basically on two DC independent sources and a conventional three-phase inverter. A common mode model for the proposed topology, as well as a modulation strategy are explained in this chapter. In the framework of this study an analysis of the distribution losses, based on simulation, was also performed and presented in this work.

The fourth chapter deals with four different modulation strategies designed to control the FB10 topology. The modulation strategies have different performance in both power quality and efficiency. Therefore a complete analysis regarding losses, power quality and leakage ground current was performed introducing the IGBT model to measure the losses in each semiconductor. In this chapter experimental results are also shown for each case.

As the PV panels are not constant DC sources, the fifth chapter gives two proposals; one to control the power converter under voltage unbalances in the DC sources and the second one is a proposal to control the power injected from the PV panels. Also in this case, simulations and experimental results are provided.

In the last chapter the general conclusions and the future works of this PhD thesis are given.

## **Contents**

|               | ements                                             |     |

|---------------|----------------------------------------------------|-----|

| Resumen       |                                                    | iii |

| Abstract      |                                                    | v   |

| Contents      |                                                    | vii |

| Figures       |                                                    | xi  |

| Tables        |                                                    | xix |

| 1. Introducti | ion                                                | 1   |

| 1.1. Back     | ground and Motivation                              | 2   |

| 1.2. Obje     | ctives                                             | 3   |

| 1.3. Thes     | is Scope and limitations                           | 4   |

| 1.4. Cont     | ributions                                          | 4   |

|               | of the art                                         |     |

| 1.5.1.        | General PV system layout                           | 5   |

| 1.5.2.        | PV inverters classification                        | 6   |

| 1.5.3.        | PV Inverters with transformer on the AC side (LF)  | 7   |

| 1.5.4.        | PV Inverters with transformer on the DC side (HF)  | 8   |

|               | PV Inverters without transformer (transformerless) |     |

| 1.5.6.        | Current controllers for PV systems                 | 27  |

| 1.5.7.        | Grid integration of PV systems                     | 32  |

| 1.5.8.        | Codes for grid connection of PV systems            | 33  |

| 1.6. Outli    | ne of the thesis                                   | 35  |

viii Contents

| 1.7. Lis   | st of publications                                 | 36  |

|------------|----------------------------------------------------|-----|

| Reference  | es                                                 | 39  |

| 2. Single- | phase transformerless PV power converters          | 43  |

| 2.1. Co    | mmon mode model                                    | 43  |

| 2.2. An    | alysis of the H5 and HERIC topologies              | 45  |

|            | e HB-ZVR topology                                  |     |

|            | perimental results                                 |     |

| 2.5. Co    | mparative analysis                                 | 51  |

| 2.6. Co    | nclusions                                          | 52  |

| Reference  | es                                                 | 54  |

| 3. Three-I | Phase transformerless PV power converters          | 55  |

| 3.1. Le    | akage ground current model                         | 56  |

| 3.2. Th    | e FB10 topology                                    | 61  |

| 3.3. Co    | mmon mode model of the proposed topology           | 63  |

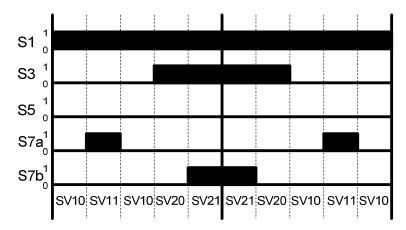

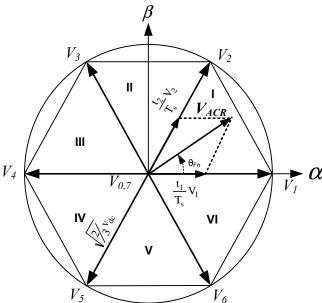

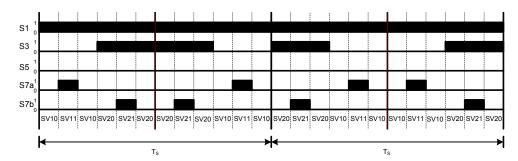

| 3.4. Mo    | odulation strategy                                 | 69  |

| 3.5. Co    | nclusions                                          | 82  |

| Reference  | es                                                 | 83  |

| 4. Modula  | ation strategies for FB10 topology                 | 85  |

| 4.1. Un    | symmetrical Zero Placement SVM (UZP-SVM)           |     |

| 4.1.1.     | 6,                                                 |     |

| 4.1.2.     |                                                    |     |

| 4.1.3.     | Efficiency and power quality                       |     |

| 4.2. Sy    | mmetrical Zero Placement SVM (SZP-SVM)             |     |

| 4.2.1.     | Description of SZP-SVM strategy                    | 92  |

| 4.2.2.     | Losses analysis                                    | 96  |

| 4.2.3.     | Efficiency and power quality                       |     |

| 4.3. Co    | mbine Zero Placement SVM (CZP-SVM)                 |     |

| 4.3.1.     | Description of the CZP-SVM strategy                | 98  |

| 4.3.2.     | <i>3</i>                                           |     |

| 4.3.3.     | Efficiency and power quality                       |     |

| 4.4. Co    | mbined Double Zero Placement SVM (CDZP-SVM)        | 102 |

| 4.4.1.     | Description of CDZ-SVM strategy                    |     |

| 4.4.2.     | Losses analysis                                    | 106 |

| 4.4.3.     | Efficiency                                         |     |

|            | mmary of the analysis of the modulation strategies |     |

|            | sses optimization                                  |     |

|            | nclusions                                          |     |

| Reference  | es                                                 | 110 |

Contents

| 5. FB | 10 topology DC bus management                       | 111     |

|-------|-----------------------------------------------------|---------|

|       | Operation of the FB10 topology under DC bus voltage |         |

| 5.2.  | Power sharing between the two DC buses of the FB1   | 0 power |

|       | converter                                           | 120     |

| 5.3.  | Conclusions                                         | 131     |

| Refe  | ences                                               | 132     |

| 6. Co | nclusions and future works                          | 133     |

| 6.1.  | Summary                                             | 133     |

| 6.2.  | Main contributions                                  | 135     |

| 63    | Future work                                         | 136     |

# Figures

| Figure 1.1.  | Evolution of the PV market during the last ten years2    |

|--------------|----------------------------------------------------------|

| Figure 1.2.  | General layout of a PV system connected to the           |

|              | electrical grid6                                         |

| Figure 1.3.  | General classification of the PV inverters6              |

| Figure 1.4.  | Full-bridge PV inverter with low frequency transformer8  |

| Figure 1.5.  | Full-bridge PV inverter with low-frequency transformer   |

|              | and DC-DC boost converter8                               |

| Figure 1.6.  | Full-bridge PV inverter with high-frequency              |

|              | transformer9                                             |

| Figure 1.7.  | Full-bridge PV inverter with push-pull converter and     |

|              | high-frequency transformer9                              |

| Figure 1.8.  | Leakage capacitances in a PV system10                    |

| Figure 1.9.  | Single-phase H5 PV topology (SMA technologies)11         |

| Figure 1.10. | Modulation states during positive half cycle; (a) Active |

|              | state, (b) Null state                                    |

| Figure 1.11. | Modulation states during negative half cycle; (a) Active |

|              | state, (b) Null state                                    |

| Figure 1.12. | Single-phase transformerless HERIC topology [1.12]13     |

xii Figures

| Figure 1.13.  | Modulation states during positive half cycle; (a) Active state, (b) Null state. | 13  |

|---------------|---------------------------------------------------------------------------------|-----|

| Figure 1.14.  | Modulation states during negative half cycle; (a) Active                        | 13  |

| 11gare 1.11.  |                                                                                 | 14  |

| Figure 1.15.  | The NPC topology for transformerless single-phase PV                            | 1   |

| 11gare 1.13.  | applications                                                                    | 15  |

| Figure 1.16.  | Modulation states in the NPC topology during positive                           | 13  |

| riguic 1.10.  | half cycle; (a) Active state, (b) Null state                                    | 16  |

| Figure 1.17.  | Modulation states in the NPC topology during negative                           | 10  |

| riguic 1.17.  | half cycle; (a) Active state, (b) Null state                                    | 17  |

| Figure 1.18.  | Full-bridge inverter with DC by-pass                                            |     |

| Figure 1.19.  | Modulation states in the full-bridge inverter with DC                           | 1 / |

| riguic 1.17.  | bypass during the positive half cycle; (a) Active state                         |     |

|               | and (b) Null state.                                                             | 18  |

| Figure 1.20.  | Modulation states in the full-bridge inverter with DC by-                       | 10  |

| 1 1guic 1.20. | pass during the negative half cycle; (a) Active state, (b)                      |     |

|               | Null state.                                                                     | 19  |

| Figure 1.21.  | Three-phase two-level transformerless inverter.                                 |     |

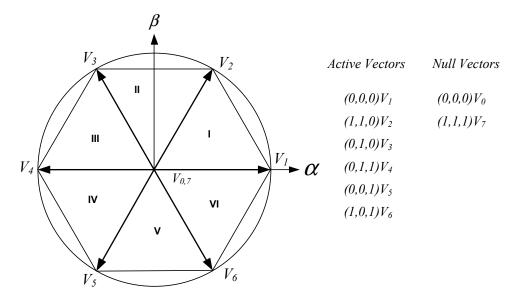

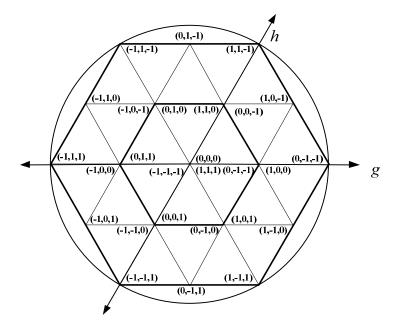

| Figure 1.22.  | General SVM for three-phase inverters.                                          |     |

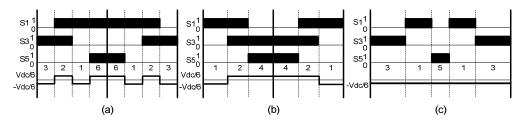

| Figure 1.23.  | Reduced CMV space vector modulations, (a)                                       | 21  |

| 1 1guic 1.23. | AZSPWM1, (b) AZSPWM2, (c) RSPWM3 [1.22]                                         | 22  |

| Figure 1.24.  | Three-phase two-level converter with the neutral point                          |     |

| C             | clamped to the middle point of the DC bus                                       | 22  |

| Figure 1.25.  | Three-phase three-level NPC converter                                           |     |

| Figure 1.26.  | Switching states for the three-level NPC converter                              |     |

| •             | Three-phase ANPC multi-level converter                                          |     |

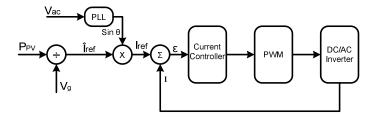

| Figure 1.28.  | General scheme of the current controller in a single-                           |     |

| C             | phase PV system                                                                 | 28  |

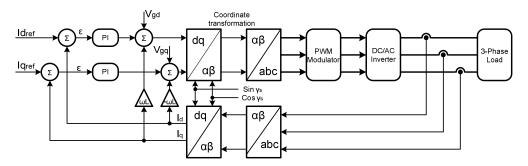

| Figure 1.29.  | Current controller for a three-phase PV system using PI                         |     |

| C             | controllers in the current loop.                                                | 29  |

| Figure 1.30.  | Proportional resonant current controller for a three-phase                      |     |

| C             | and single-phase systems.                                                       | 30  |

| Figure 1.31.  | Proportional resonant current controller and low-order                          |     |

| J             | harmonic compensator.                                                           | 30  |

| Figure 1.32.  | Basic hysteresis current controller                                             |     |

| -             | -                                                                               |     |

Figures xiii

| Figure 1.33. | Output current in an inverter using a conventional hysteresis current controller.                                                                                                                                                                                    | 32 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

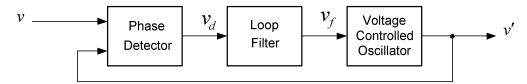

| Figure 1.34. | Block diagram of the basic Phase Locked Loop (PLL) system.                                                                                                                                                                                                           |    |

| Figure 2.1.  | General single-phase PV system with low-frequency transformer.                                                                                                                                                                                                       |    |

| Figure 2.2.  | Final common mode model of the single-phase PV power converter.                                                                                                                                                                                                      |    |

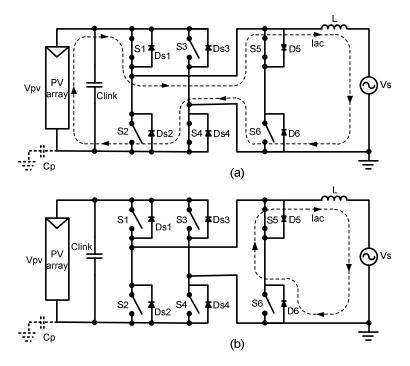

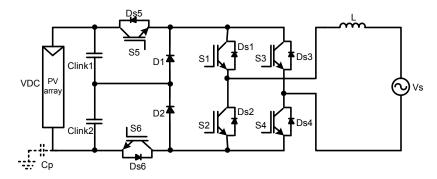

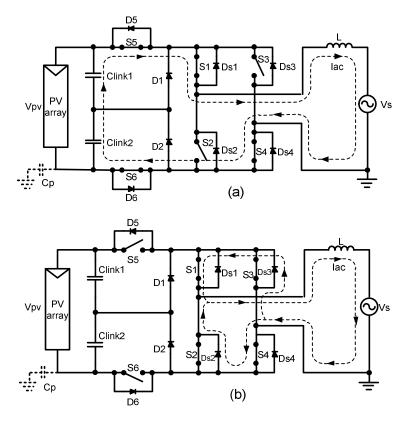

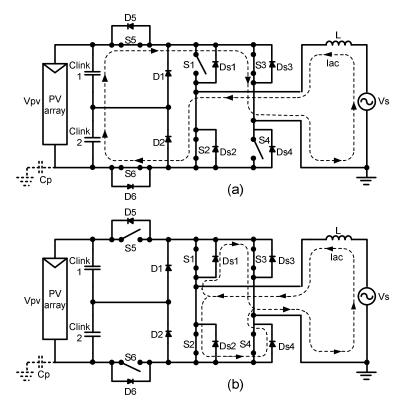

| Figure 2.3.  | Popular single-phase transformerless PV systems; (a) H5 and (b) HERIC.                                                                                                                                                                                               |    |

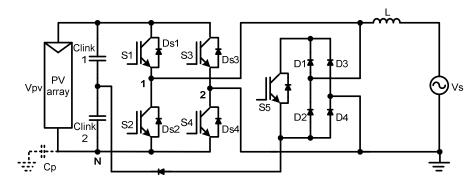

| Figure 2.4.  | Proposed HB-ZVR transformerless topology                                                                                                                                                                                                                             |    |

| Figure 2.5.  | a) Positive active state condition and b) Dead-time state after turn-OFF S1-S4 in the HB-ZVR topology                                                                                                                                                                |    |

| Figure 2.6.  | Null state during the positive half cycle in the HB-ZVR topology.                                                                                                                                                                                                    |    |

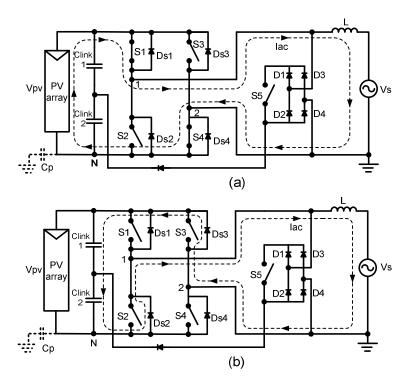

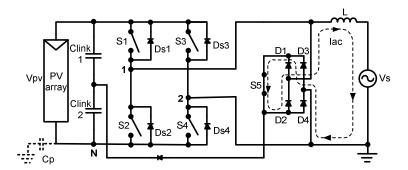

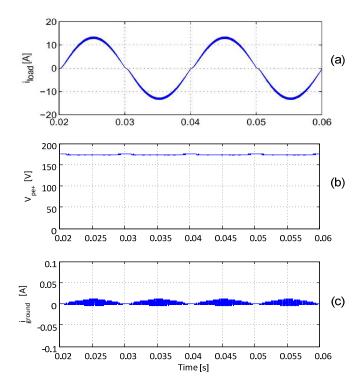

| Figure 2.7.  | Simulation results of: (a) Load current, (b) DC+ terminal voltage respect to ground and (c) Leakage ground                                                                                                                                                           | 48 |

| Figure 2.8.  | Modular experimental setup to test the single-phase transformerless PV inverters.                                                                                                                                                                                    |    |

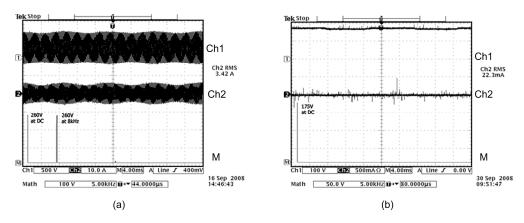

| Figure 2.9.  | Experimental results for: (a) Full-bridge inverter (with unipolar modulation strategy), Ch1 shows the voltage to ground of the DC+ terminal, Ch2 is the leakage ground current and M is the FFT of Ch1 and (b) HERIC topology (same channel distribution than "(a)") |    |

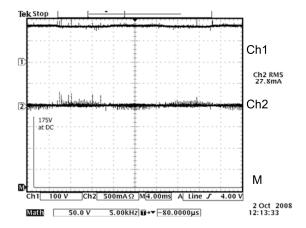

| Figure 2.10. | Experimental results for the proposed HB-ZVR topology, Ch1 shows the voltage to ground of the DC+ terminal, Ch2 is the leakage ground current and M is the                                                                                                           | 51 |

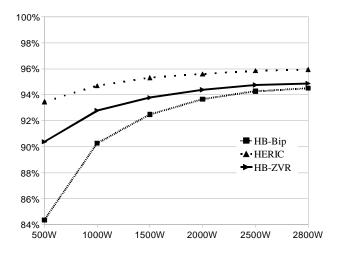

| Figure 2.11. | Efficiency comparison between the three topologies under test.                                                                                                                                                                                                       | 52 |

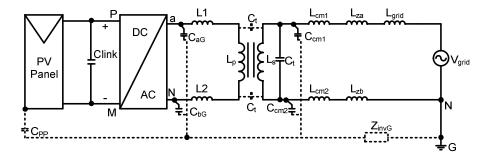

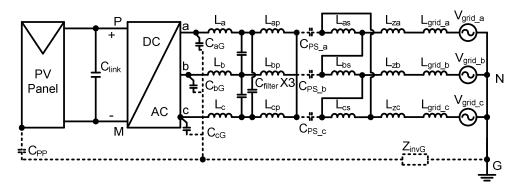

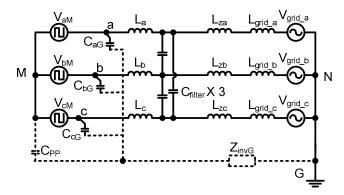

| Figure 3.1.  | General three-phase PV system.                                                                                                                                                                                                                                       |    |

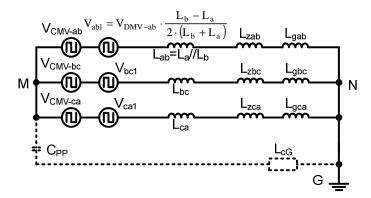

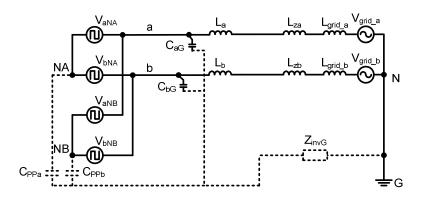

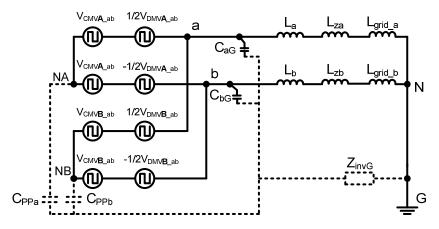

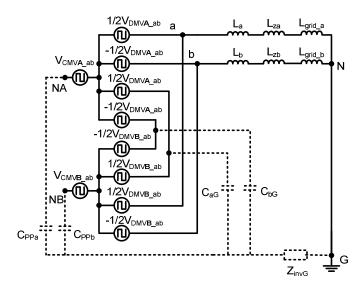

| Figure 3.1.  | Three-phase PV system model with transformer                                                                                                                                                                                                                         |    |

| _            | considering the parasitic elements in the system.                                                                                                                                                                                                                    | 57 |

<u>XiV</u> Figures

| Figure 3.3.   | Three-phase transformerless inverter with the controlled |

|---------------|----------------------------------------------------------|

|               | voltage sources                                          |

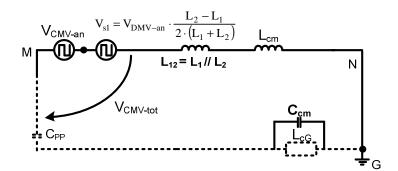

| Figure 3.4.   | Common mode and differential mode voltages in a          |

|               | transformerless three-phase inverter 59                  |

| Figure 3.5.   | Simplified model of the three-phase inverter using two   |

|               | legs 59                                                  |

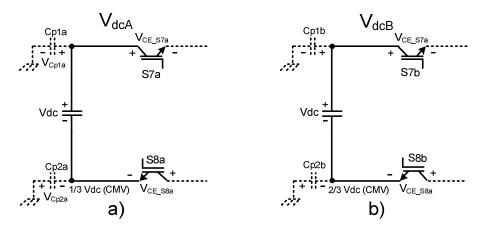

| Figure 3.6.   | Simplified model for the two legs of the inverter; a)    |

| _             | Considering the unbalance impedances and b) Final        |

|               | simplified common mode model                             |

| Figure 3.7.   | Final simplified model for the three-phase system        |

| C             | including the CMV voltage sources                        |

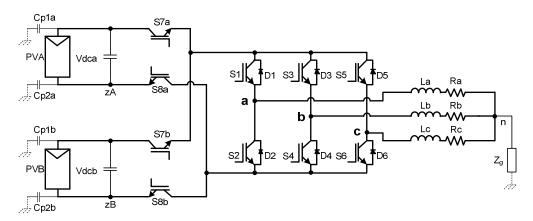

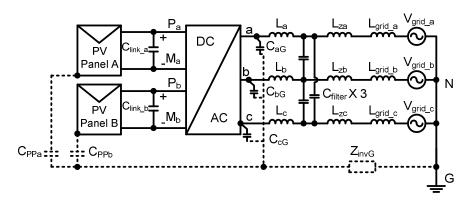

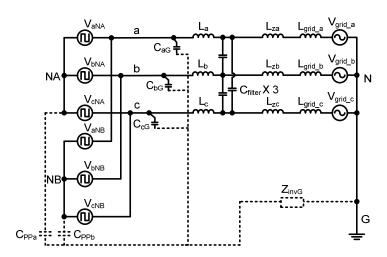

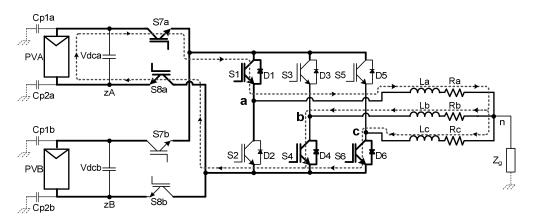

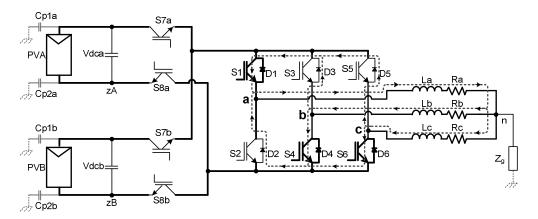

| Figure 3.8.   | Proposed FB10 transformerless three-phase PV             |

| 8             | topology62                                               |

| Figure 3.9.   | Proposed FB10 transformerless topology scheme            |

| 8             | considering its stray elements                           |

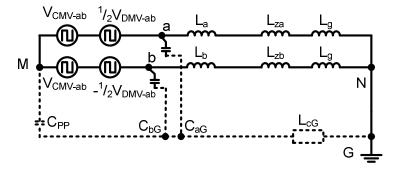

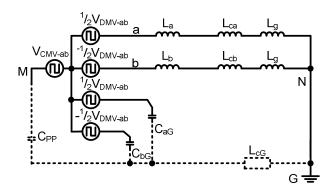

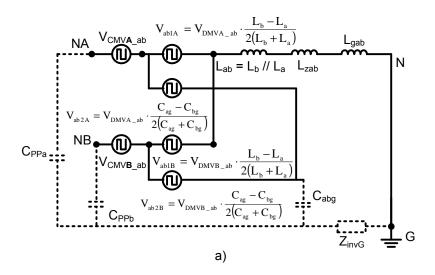

| Figure 3.10.  | Initial common mode model proposed for the FB10          |

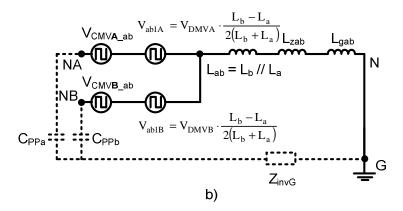

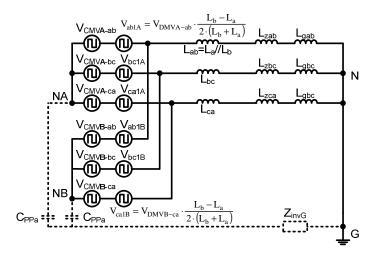

| 118010 2.10.  | transformerless topology                                 |

| Figure 3.11.  | Common mode model proposed for the FB10                  |

| 1 1guic 5.11. | transformerless topology (using just two phases)         |

| Figure 3.12.  | Common mode model for the FB10 transformerless           |

| 1 iguic 3.12. | topology using the equations (3.15) to (3.18)            |

| Figure 3.13.  | Simplified common mode model for the FB10                |

| 1 iguic 5.15. | transformerless topology following the equations (3.15)  |

|               | to (3.18)                                                |

| Figure 3.14.  | Simplified common mode model; a) Considering the         |

| 11guie 3.14.  | unbalanced impedances and b) Final simplified common     |

|               | mode model                                               |

| Figure 3.15.  | Final simplified common mode model for the FB10          |

| rigule 3.13.  | transformerless topology                                 |

| Eiguro 2 16   | FB10 topology configured with an odd active vector       |

| Figure 3.16.  | 1 00                                                     |

| Eigung 2 17   | (V1)                                                     |

| Figure 3.17.  | FB10 topology configured with a null vector (V1 is       |

| Eigen 2 10    | configured in the full-bridge circuit)                   |

| Figure 3.18.  | FB10 topology configured with a null vector (V2 is       |

|               | configured in the full-bridge circuit)71                 |

Figures XV

| Figure 3.19.  | FB10 topology configured with an even active vector (V2)                               | 72  |

|---------------|----------------------------------------------------------------------------------------|-----|

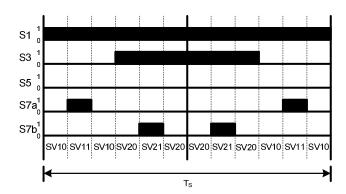

| Figure 3.20.  | Initial modulation strategy proposed to control the FB10 PV inverter topology          |     |

| Figure 3.21.  | SVM represented in the $\alpha$ - $\beta$ plane.                                       |     |

| Figure 3.22.  | Simulation results with the initial modulation strategy to                             | , 5 |

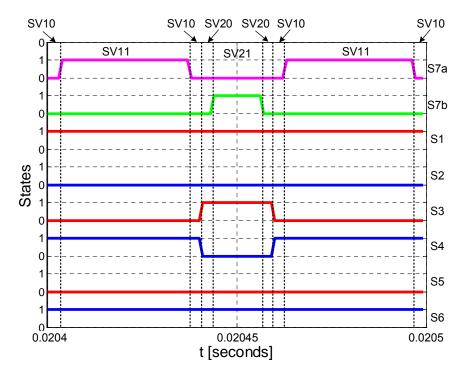

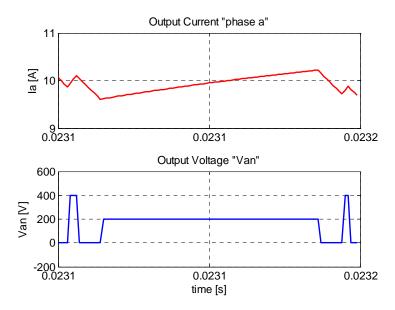

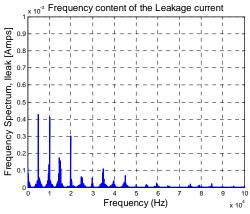

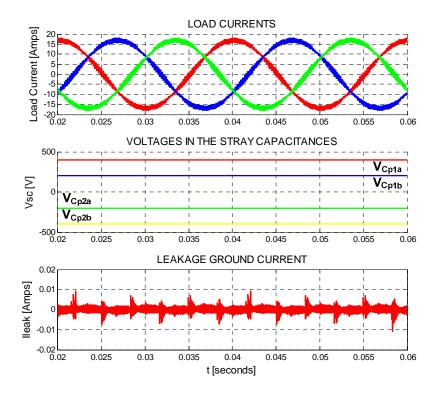

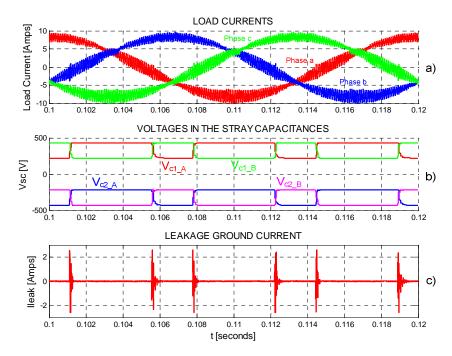

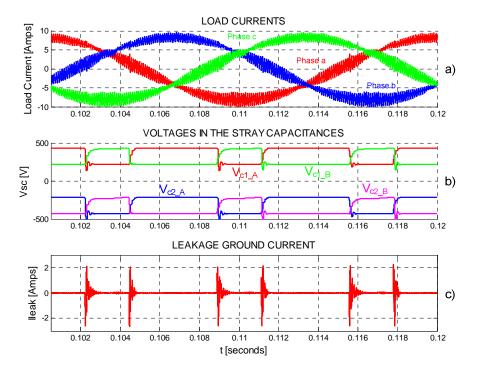

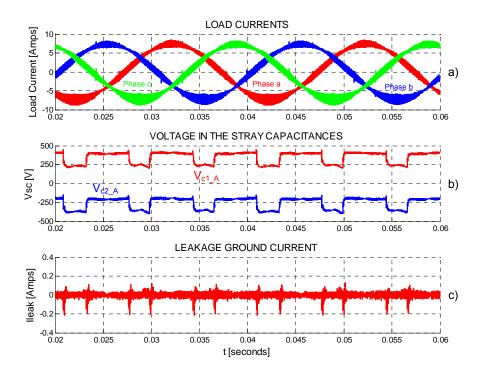

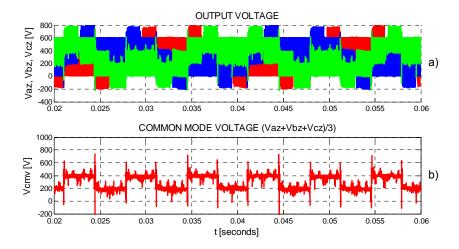

| 1 18010 3.22. | control the FB10 PV inverter topology                                                  | 75  |

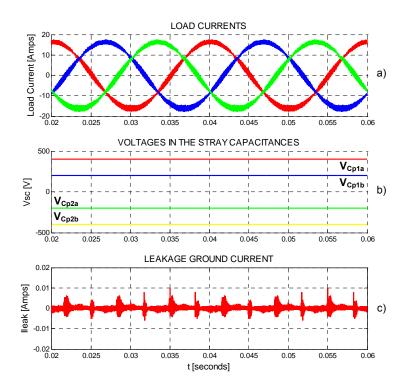

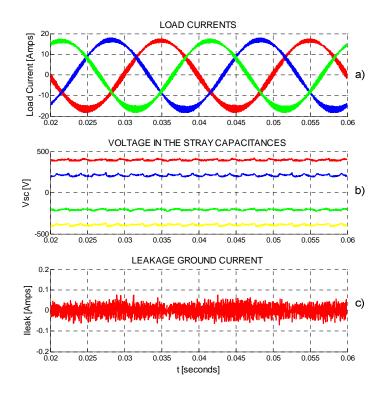

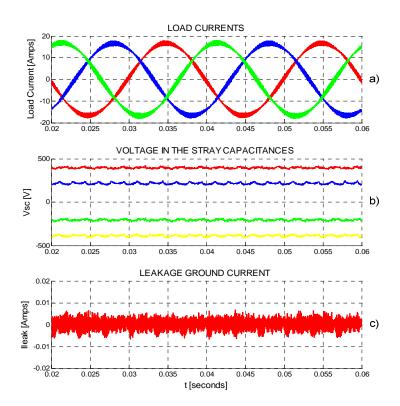

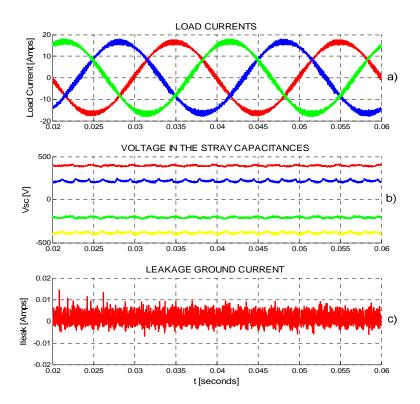

| Figure 3.23.  | Simulation results for the FB10 topology, a) Load                                      |     |

| 8             | currents, b) Voltages across the stray capacitances ( $C_{p1a}$ ,                      |     |

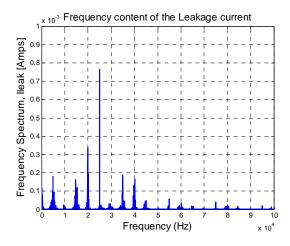

|               | $C_{p2a}$ , $C_{p1b}$ and $C_{p2b}$ ), c) Leakage ground current.                      | 77  |

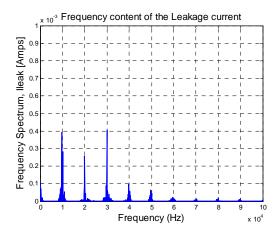

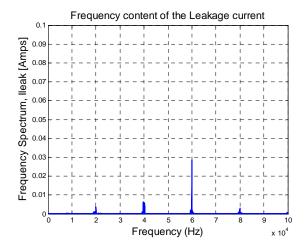

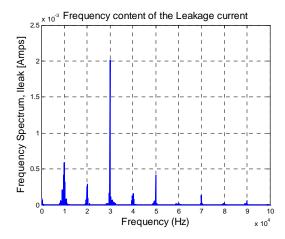

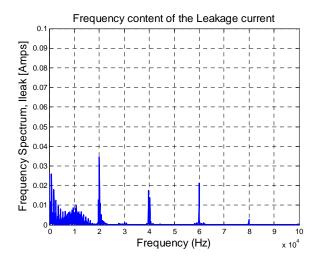

| Figure 3.24.  | Frequency spectrum of the leakage ground current                                       |     |

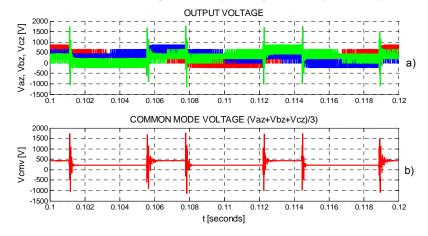

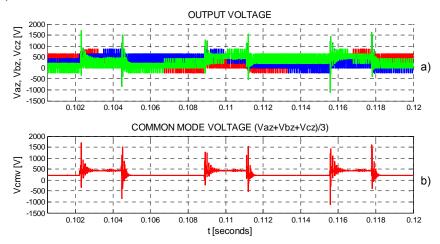

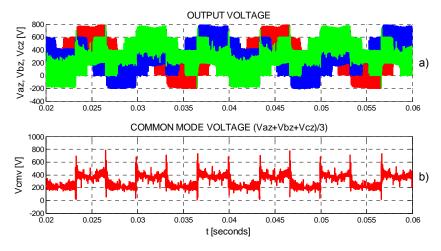

| Figure 3.25.  | CMV in the FB10 topology; Case 1: a) Output voltage                                    |     |

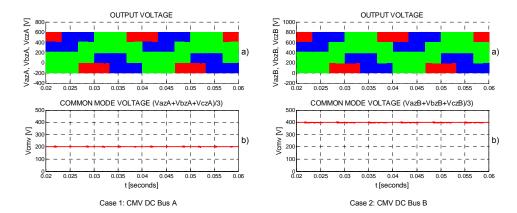

| C             | respect to a common point "zA" (zA is the negative                                     |     |

|               | terminal of the V <sub>dcA</sub> ), b) CMV measured using equation                     |     |

|               | (3.19). Case 2: a) Output voltage respect to a common                                  |     |

|               | point "zB" (zB is the negative terminal of the V <sub>dcB</sub> ), b)                  |     |

|               | CMV measured using equation (3.20).                                                    | 78  |

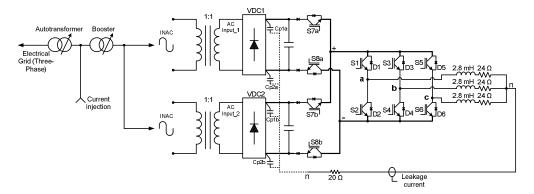

| Figure 3.26.  | Scheme of the experimental setup of the FB10 topology                                  | 79  |

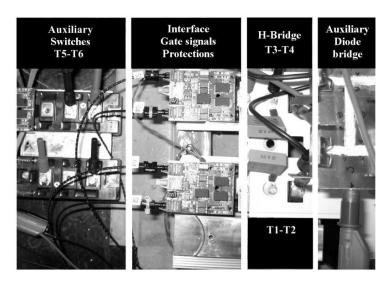

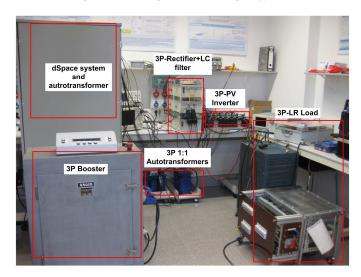

| Figure 3.27.  | Experimental setup of the FB10 topology.                                               | 79  |

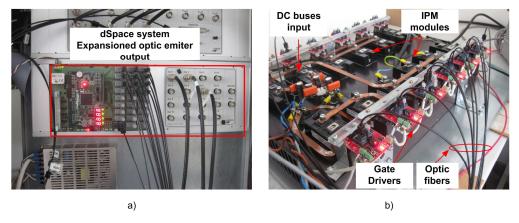

| Figure 3.28.  | Detail of the three-phase transformerless FB10 inverter                                | 80  |

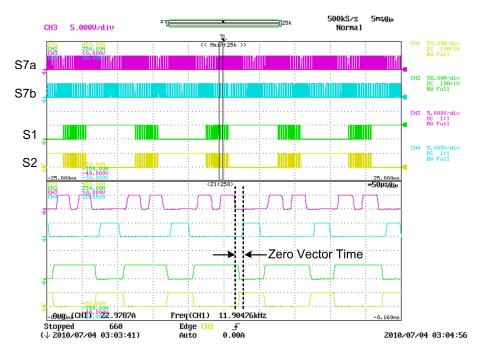

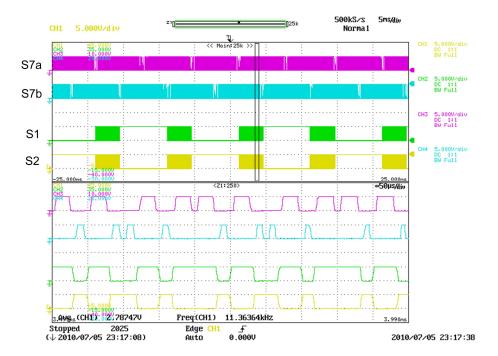

| Figure 3.29.  | Experimental results of the FB10 topology                                              | 81  |

| Figure 3.30.  | Experimental frequency spectrum of the leakage current                                 | 81  |

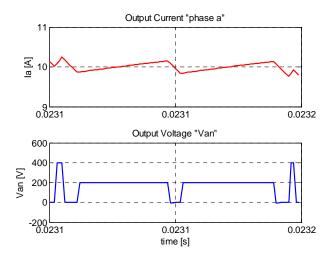

| Figure 4.1.   | Ripple details for the UZP-SVM technique                                               | 86  |

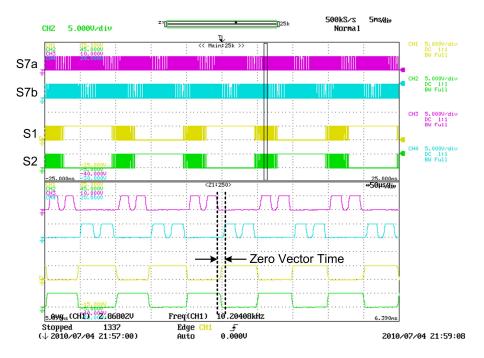

| Figure 4.2.   | Experimental results of the UZP-SVM strategy                                           | 87  |

| Figure 4.3.   | Equivalent circuits on the DC side when a null vector is                               |     |

|               | applied to the load.                                                                   | 88  |

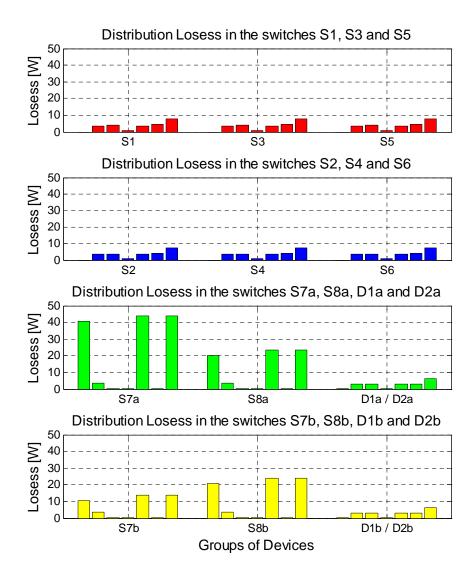

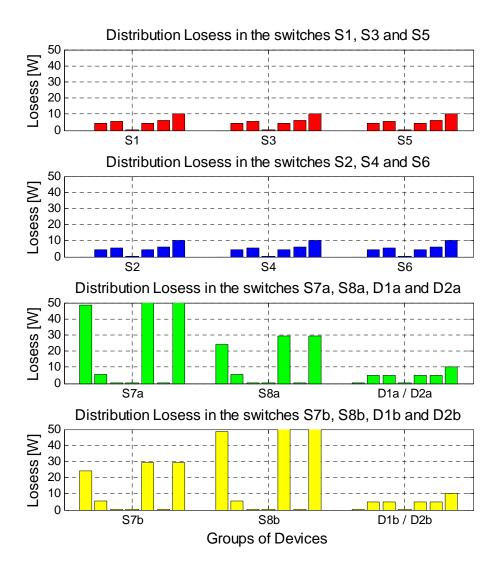

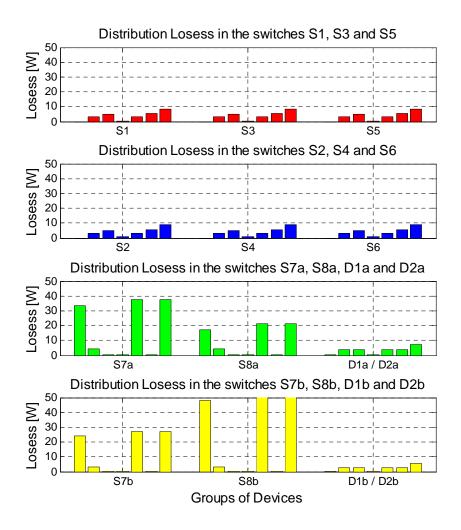

| Figure 4.4.   | Distribution losses in the FB10 topology using UZP-                                    |     |

|               | SVM strategy.                                                                          | 90  |

| Figure 4.5.   | Modulation signals for SZP-SVM strategy                                                | 92  |

| Figure 4.6.   | Current ripple for the SZP-SVM strategy                                                | 93  |

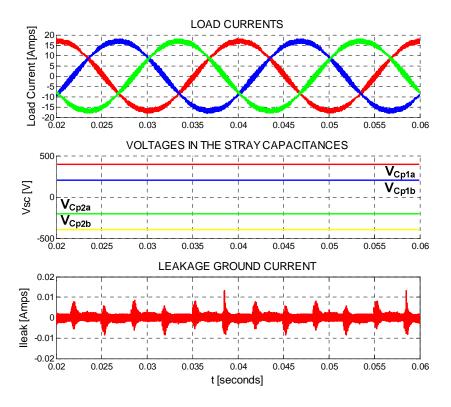

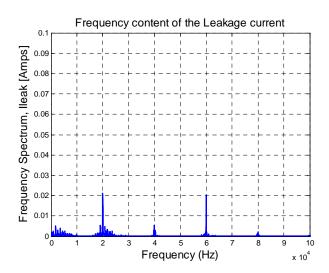

| Figure 4.7.   | Simulation results for the FB10 topology, a) Load                                      |     |

|               | currents, b) Voltages across the stray capacitances ( $C_{p1a}$ ,                      |     |

|               | C <sub>p2a</sub> , C <sub>p1b</sub> and C <sub>p2b</sub> ), c) Leakage ground current. | 93  |

| Figure 4.8.   | Experimental results of the SZP-SVM strategy:                                          |     |

|               | Modulation signals                                                                     | 94  |

XVI Figures

| Figure 4.9.  | Experimental results of the SZP-SVM strategy: a) Load currents, b) Voltage in the stray capacitances and c) |      |

|--------------|-------------------------------------------------------------------------------------------------------------|------|

|              | Leakage ground current                                                                                      | . 95 |

| Figure 4.10. | Experimental frequency spectrum of the leakage ground                                                       |      |

| J            | current for SZP-SVM strategy.                                                                               | . 95 |

| Figure 4.11. | Distribution losses in the case of the SZP-SVM strategy                                                     |      |

| Figure 4.12. | Modulation signals of the CZP-SVM strategy                                                                  |      |

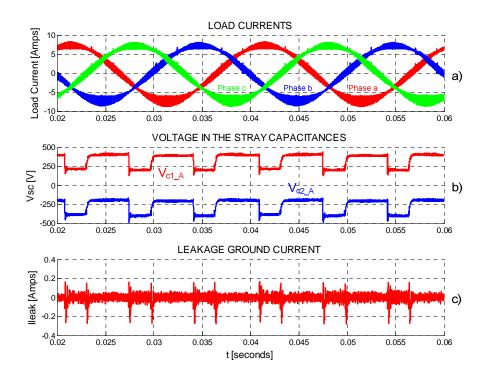

| Figure 4.13. | Simulation results for the FB10 topology, a) Load                                                           |      |

|              | currents, b) Voltages across the stray capacitances (C <sub>p1a</sub> ,                                     |      |

|              | C <sub>p2a</sub> , C <sub>p1b</sub> and C <sub>p2b</sub> ), c) Leakage ground current                       | . 99 |

| Figure 4.14. | Experimental results of the CZP-SVM strategy:                                                               |      |

|              | Modulation signals.                                                                                         | . 99 |

| Figure 4.15. | Experimental results of the CZP-SVM strategy: a) Load                                                       |      |

|              | currents, b) Voltage in the stray capacitances and c)                                                       |      |

|              | leakage ground current.                                                                                     | 100  |

| Figure 4.16. | Experimental frequency spectrum of the leakage ground                                                       |      |

|              | current for CZP-SVM strategy.                                                                               |      |

| Figure 4.17. | Distribution losses in the case of CZP-SVM strategy                                                         | 101  |

| Figure 4.18. | Vectors sequence of the CDZP-SVM strategy                                                                   | 103  |

| Figure 4.19. | Simulation results for the FB10 topology, a) Load                                                           |      |

|              | currents, b) Voltages across the stray capacitances (C <sub>p1a</sub> ,                                     |      |

|              | $C_{p2a}$ , $C_{p1b}$ and $C_{p2b}$ ), c) Leakage ground current                                            | 103  |

| Figure 4.20. | Experimental results of the CDZP-SVM strategy:                                                              |      |

|              | Modulation signals.                                                                                         | 104  |

| Figure 4.21. | Experimental results of the CDZP-SVM strategy: a)                                                           |      |

|              | Load currents, b) Voltage in the stray capacitances and                                                     |      |

|              | c) Leakage ground current                                                                                   | 105  |

| Figure 4.22. | Experimental frequency spectrum of the leakage ground                                                       |      |

|              | current for CDZP-SVM strategy                                                                               |      |

| Figure 4.23. | Distribution power losses in the case of CDZP-SVM                                                           | 106  |

| Figure 5.1.  | Active voltage modification under unbalance DC bus                                                          |      |

|              | conditions in the FB10 three-phase PV converter                                                             | 112  |

| Figure 5.2.  | Simulation results when $V_{dcA} = 600V$ and $V_{dcB} = 650V$ ;                                             |      |

|              | a) Without balancing technique and b) With balancing                                                        |      |

|              | technique.                                                                                                  | 114  |

Figures xvii

| Figure 5.3.  | Simulation results when $V_{dcA} = 650V$ and $V_{dcB} = 600V$ ; |      |

|--------------|-----------------------------------------------------------------|------|

|              | a) Without balancing technique and b) With balancing            |      |

|              | technique.                                                      | .116 |

| Figure 5.4.  | Experimental results when $V_{dcA} = 540V$ and $V_{dcB} =$      |      |

|              | 600V; a) Without balancing technique and b) With                |      |

|              | balancing technique.                                            | .117 |

| Figure 5.5.  | Experimental results when $V_{dcA} = 600V$ and $V_{dcB} =$      |      |

|              | 540V; a) Without balancing technique and b) With                |      |

|              | balancing technique.                                            | .118 |

| Figure 5.6.  | Experimental results to show the ripple in the load             |      |

|              | currents and the effect of the DC voltage compensation          |      |

|              | technique when $V_{dcA} > V_{dcB}$                              | .119 |

| Figure 5.7.  | Power sharing under normal operation of FB10                    |      |

|              | converter.                                                      | .120 |

| Figure 5.8.  | DC currents along the Sector I in a symmetrical power           |      |

|              | sharing situation.                                              | .121 |

| Figure 5.9.  | Simulation results for the power sharing technique with         |      |

|              | a regulation angle $\alpha = 20^{\circ}$                        | .123 |

| Figure 5.10. | CMV in the case of power compensation technique                 |      |

|              | using a regulation angle $\alpha = 20^{\circ}$ .                | .123 |

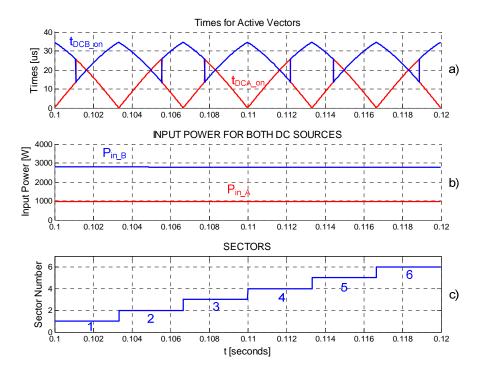

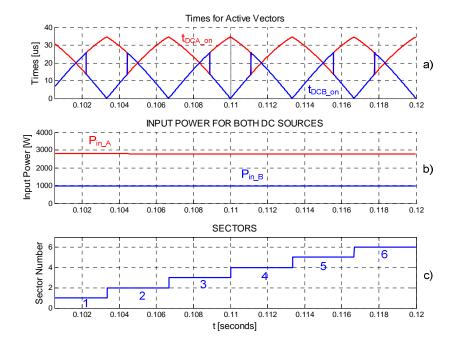

| Figure 5.11. | a) Active times, b) Power measured and c) Sectors, in           |      |

| U            | the case of the power sharing technique using a                 |      |

|              | regulation angle $\alpha = 20^{\circ}$                          | .124 |

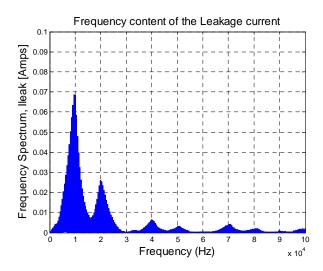

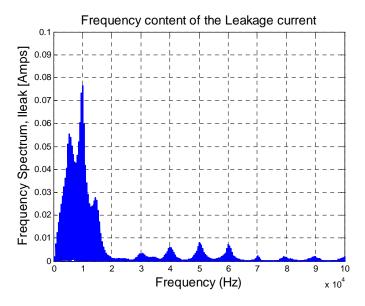

| Figure 5.12. | Frequency spectrum of the leakage ground current when           |      |

|              | the power sharing technique is applied using a regulation       |      |

|              | angle $\alpha = 20^{\circ}$ .                                   | .125 |

| Figure 5.13. | Simulation results for the power sharing technique for a        |      |

|              | regulation angle $\alpha = -20^{\circ}$ .                       | .125 |

| Figure 5.14. | CMV in the case of power sharing technique applied              |      |

|              | when the regulation angle $\alpha = -20^{\circ}$                | .126 |

| Figure 5.15. | a) Active times, b) Power measured and c) Sectors, in           |      |

| C            | the case of the power sharing technique applied using a         |      |

|              | regulation angle $\alpha = -20^{\circ}$ .                       | .126 |

xviii Figures

| Figure 5.16. | Frequency spectrum of the leakage ground current when             |

|--------------|-------------------------------------------------------------------|

|              | the power sharing technique is applied using a regulation         |

|              | angle $\alpha = -20^{\circ}$                                      |

| Figure 5.17. | Experimental results for the power sharing strategy               |

|              | applied when a regulation angle $\alpha = 20^{\circ}$ is applied  |

| Figure 5.18. | Experimental CMV in the case of power sharing                     |

|              | technique applied with a regulation angle $\alpha = 20^{\circ}$   |

| Figure 5.19. | Experimental frequency spectrum of the leakage ground             |

|              | current in the case of Power sharing technique applied            |

|              | with a regulation angle $\alpha = 20^{\circ}$                     |

| Figure 5.20. | Experimental results for the power sharing strategy               |

|              | applied when a regulation angle $\alpha = -20^{\circ}$ is applied |

| Figure 5.21. | Experimental CMV in the case of power sharing                     |

|              | technique applied with a regulation angle $\alpha = -20^{\circ}$  |

| Figure 5.22. | Experimental frequency spectrum of the leakage ground             |

|              | current in the case of Power sharing technique applied            |

|              | with a regulation angle $\alpha = -20^{\circ}$                    |

## **Tables**

| Table 1.1  | CMV generated by two-level FB inverter                   | 21   |

|------------|----------------------------------------------------------|------|

| Table 1.2. | Three-level states and CMV.                              | 26   |

| Table 1.3. | Leakage current jumps and their corresponding            |      |

|            | disconnection time from VDE 0126-1-1                     | 35   |

| Table 2.1. | Efficiency obtained at the different power levels in the |      |

|            | three topologies                                         | 52   |

| Table 4.1. | Comparative analysis regarding efficiency in all four    |      |

|            | modulation strategies.                                   | .107 |

| Table 4.2. | Comparative table regarding waveform quality for the     |      |

|            | proposed modulation strategies                           | .108 |

|            |                                                          |      |

n the last decades, renewable energies have emerged as a reliable solution to classical generation power plants based on fossil fuels, which are finite, nonrenewable and pollutants. Even new developments oriented to enhance the operation, control and performance of renewable energy based generation systems have contributed positively to improve its penetration into the electrical network; however there is still a lot to do in different fields in order to reach a massive integration of such systems. The usage of fossil fuels has contributed to maintain an alarming increase over the last 100 years in the atmospheric pollution level and global warming (which can reach a global average temperature as much as 6 °C during XXIth century) this effect in the climate conditions, as well as the increasing environmental concern, has paved the way for the fast development and installation of renewable energy technologies like wind power (WT) and photovoltaic (PV) systems, whose development has been supported by the local governments, especially in European countries. As an example, WT in the range of several MW as well as PV farms in this power range are currently installed all around the world with great success.

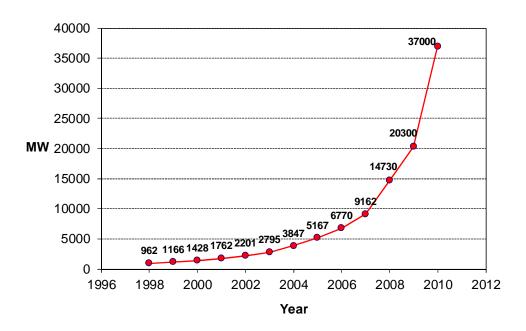

Due to its high potential for producing clean energy among all of the renewable energy sources, solar energy continues to be one of the most attractive choices for investors and manufactures, mainly in grid connected residential applications. According with the European Photovoltaic Industry Association (EPIA) the total PV power installed at 2010 is around 37 GW compare to 20.3 GW in 2009. During 2010 Europe alone added between 11.6 and 13.3 GW of new PV installed capacities. Germany has been the leader in new PV installations in the last two years with around 7 GW (in 2010) followed by Italy, Czech Republic, France and Spain. Out of Europe the PV market is also growing, in 2010 the major markets progressed to reach in total between 2.6 and 3.2 GW of PV power installed, where Japan is the leader with 1 GW followed by USA (~800 MW) and China (~600 MW). In Figure 1.1, it is shown the historical PV global market development, for instance Europe is

the leader in 2010 with at least 13.3 GW representing around 80% of the global cumulative PV installed capacity [1.1].

The expectative for the future in PV energy industry is hopeful. Experts believe that in 2011 the market could reach up to 16 GW in a moderate scenario. The PV industry is hopping markets such as the French, Italian, Spanish, American and Chinese will pull the demand.

## Development of global Cumulative PV power installed

**Figure 1.1.** Evolution of the PV market during the last ten years.

### 1.1. Background and Motivation

The increase in the installation of power plants based on renewable energy sources has been almost exponential during the last years. These technologies are continuously under evolution and relevant efforts are being addressed in different research field in the aim of making these technologies more efficient, reliable and competitive. In this sense based on the research and evaluation performed some solutions and improvements can be provided in order to make a better use of the renewable energy resources.

Among renewable energy sources PV systems are gaining more and more importance in the renewable energy market. The power electronic systems used to convert the solar energy

from the PV panel (DC nonlinear power supply) into electrical energy have a special importance in the design of a PV power system, due to the fact that the PV panels itself have not a very high efficiency, commonly between 15% and 20% in average in commercial products. This means that the electronic power conversion stage must have a very good efficiency in order to make the overall system competitive from a power production point of view. Additionally the system must be reliable in terms of security and life time.

At the beginning, and still today in many applications, PV systems are designed for being connected to the grid through an isolation transformer that can be found in the system as a Low-Frequency Transformer (LFT) on the AC side, or as a High-Frequency Transformer (HFT) on the DC side. The main problem in this concept is that the transformer introduces additional losses in the system and its integration can be somehow difficult, as it is a heavy and bulky component, meanwhile it increases the overall costs. Another alternative to implement the PV system is to take out the isolation transformer and connect the system directly to the electrical grid by means of a filter (i.e. a LCL filter). The new *Transformerless* system can get a better efficiency than the first ones, but the main drawback is that now there is no galvanic isolation. Therefore, and due to the high frequency operation (typically in the range of 2 to 20 kHz) some leakage currents may appear trough the stray capacitance formed between the PV panel frame and the earth. The main motivation to develop this research work is to propose efficient power electronic solutions to solve the leakage current problem in transformerless PV applications.

### 1.2. Objectives

The main objectives of this PhD are focused in the study, analysis, test and proposal of new solutions within the field of PV transformerless inverters in both: single-phase and three-phase systems. In a nutshell, the main goals of this work are listed in the following:

- > To review and evaluate the electrical effects of the leakage ground currents in PV systems.

- > To model and proposed solutions to the leakage ground current problem in the case of PV transformerless topologies in single and three-phase systems.

- To make the proposed solutions compatible with the requirements established by the current standards applicable to PV systems connected to the electrical grid.

- To develop solutions that can be competitive with the commercial PV inverters not only in single-phase topologies but also in three-phase systems in terms of efficiency.

- ➤ To propose specific pulsed width modulation strategies to control the energy transfer in the proposed topologies.

According to the points listed above, the main objective of this thesis is to propose solutions based on hardware and control techniques that give rise to PV power systems able to reduce or eliminate the leakage ground currents, keeping or improving the total efficiency of the PV power conversion system.

### 1.3. Thesis Scope and limitations

This PhD work is focused in the PV power converter, which is the conversion stage responsible of managing the power flow between a DC input, coming from the PV panels, to an AC output, which is the distribution network. The power conversion stage can be implemented in different ways, for instance: three stages systems converter+Inverter+Low-frequency transformer), two stages (Inverter+Low-frequency transformer), etc. This thesis is focused just in single stage DC to AC configurations, where an inverter is connected directly to the grid through a grid connection filter. In this regard both, single-phase and three-phase systems were analyzed and the most interesting topologies were experimentally implemented. The PV array has been implemented using a constant DC source in both simulation and experimental tests.

#### 1.4. Contributions

The contributions of this thesis work are the study about the problem associated to common mode voltage (CMV) and efficiency in the PV transformerless power converters and the proposal of solutions oriented to eliminate or reduce the leakage ground current magnitude.

In the case of single-phase systems a new topology called HB-ZVR topology with high efficiency and constant CMV has been proposed. The analysis and operation of this topology is widely explained in this document. A comparative analysis with the most extended topologies used in single-phase systems regarding the efficiency and leakage ground current was carried out in order to validate the feasibility of the proposed system.

In the case of three-phase systems, a new topology was proposed. The topology is three-phase extension of the H5 topology concept, in this case the CMV is constant and the leakage ground current is close to zero. This new topology is called FB10 topology.

#### 1.5. State of the art

The PV panel technology has undergone a fast evolution in the last decades, improving noticeably their efficiency. Nowadays the commercial PV Silicon (Si) cells convert between 14% and around 22% of the solar radiation into usable electrical energy. Moreover, there are new PV technologies under development which are able to reach efficiencies close to 40.1%, as introduced in [1.2] and [1.3].

In the beginning, the PV modules were connected in series in order to get a higher voltage (each panel producing 40V) without using amplification system. Those arrays were later connected in parallel, so a higher power levels could be reached. These kinds of systems were experiencing some limitations, such as the need of high voltage DC cables, the high power losses, etc. However the main drawback of this configuration was its inadequate design for the massive production [1.4]. To overcome these limitations new structures and control methods have been developed.

Not only the PV technology and the connection configuration have been improved, but also the power electronics devices. The first PV generation plants were controlled using thyristors. As a consequence there were important problems regarding harmonics because they can produce a poor power quality. The modern MOSFET's and IGBT's which today are broadly used have contributed to reduce that problem thanks to their high switching frequency operation, i.e. in the case of MOSFET's. It should be remarked that certain PV systems may require devices that support 1000 V, for instance when series array of PV modules are directly connected to the inverter [1.4]. In order to overcome this limitation multi-string topologies can be implemented. These systems normally consist of a single PV strings connected to a DC-DC converter that is linked finally to a common inverter, responsible of injecting the power to the electrical grid.

At the beginning PV systems were designed for stand-alone operation, in which the grid connection was not required. This kind of applications are used in small camp houses, farms, public lighting systems, etc. (generally low power applications), in these applications single-phase systems are commonly used. At the present time, most PV systems are connected to the electrical grid by means of three-phase PV inverters. In this sense, lot of research has been done in order to overcome all the problems related to the grid connection, performance and security.

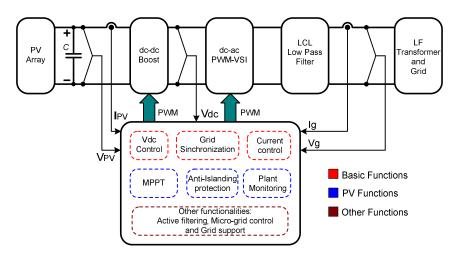

#### 1.5.1. General PV system layout

A PV system consists in a few well defined stages. First stage is the PV panel or PV panel arrays; the PV panels receive and harvest the solar energy in order to transform it into electrical energy. This PV source is a DC nonlinear power supply that delivers its electrical energy to a second stage called DC-DC converter. The second stage can be omitted depending on the application and the PV array. This stage has at least two main functions which are to step-up the DC voltage and to performance the MPPT (Maximum Power Point Tracking) task. Third stage consists of an inverter which is responsible to change the DC voltage into an AC voltage. The AC voltage is then used as an input in a LCL filter which is directly connected to the grid (fourth stage). Finally a very important stage is the control system which has a lot of tasks to do; some of them are listed below:

- ➤ MPPT control

- DC bus control

- Inverter control

- Grid Synchronization

- ➤ Anti-islanding protection

- > Grid support control

As can be seen, the complete system becomes complex when all parts are added. Figure 1.2 shows the different parts of a PV system connected to the electrical grid. The PV system is a single-phase system with a DC-DC boost converter which increases the input voltage to a suitable level. A LCL filter takes out the high frequency component from the output current and finally a low-frequency transformer connects the system to the electrical grid. This

transformer provides galvanic isolation for the PV system. The variables that in general are used to control the system are also shown. Input DC current  $(I_{pv})$  and voltage  $(V_{pv})$  are necessary to implement the MPPT algorithm of the PV panels. On the AC side, the output current  $(I_g)$  and voltage  $(V_g)$  are required to perform functions as: Current control, grid synchronization, etc.

Figure 1.2. General layout of a PV system connected to the electrical grid.

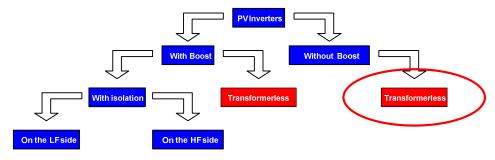

#### 1.5.2. PV inverters classification

There are different power converters topologies for PV systems, as it is reported in [1.4]-[1.5], but within all this variety, it is possible to classify them in two main groups. In one side there are topologies which use a galvanic isolation (transformer) either in the AC side (Low-Frequency) or in the DC side (High-Frequency) and, on the other side, those that do not use transformer (transformerless). In general power converters for PV systems can be classified as show in Figure 1.3.

**Figure 1.3.** General classification of the PV inverters.

Another way to classify PV inverters can be performed considering the PV power plant configuration and the power rate. According to these criteria power plants can be classified as indicated in the following:

- ➤ Centralized PV inverters: This kind of inverters links a large number of PV modules to the grid. The PV modules are connected in series, called *strings* and then connected in parallel through string diodes in order to generate enough DC voltage to inject current to the electrical grid. The drawbacks of this configuration are the long DC cables between the inverter and PV panels, the mismatch losses in the panels and the losses generated by the string diodes [1.4].

- ➤ Modularized inverters: The modularized inverters can be connected with one or several PV modules with a total power below 500W. In this case the PV array voltage is around 30-150 V [1.6]. According with this, it is require to step-up the DC input voltage, as a consequence, a system with several stages can be implemented, including topologies with transformer.

- > String PV inverters: In order to obtain a better performance in a PV system, a new kind of PV plant was proposed. String PV inverters get the best of modularized inverters and centralized inverters. Several PV panels can be set in series reaching DC voltage around 150 to 450 V with power level around 2 kW, a better power range regarding to the above concepts [1.6]. With this power rating it is easy to reduce the cost and increase the efficiency.

- > Multi-string PV inverters: With the need of reducing costs, came up a new approach to configure a PV plant. In this case the idea is to connect in parallel some PV strings with its own MPPT control (boost converter) and then, with a DC bus, link them to the electrical grid with a PWM inverter, which includes all supervisory and protections functions.

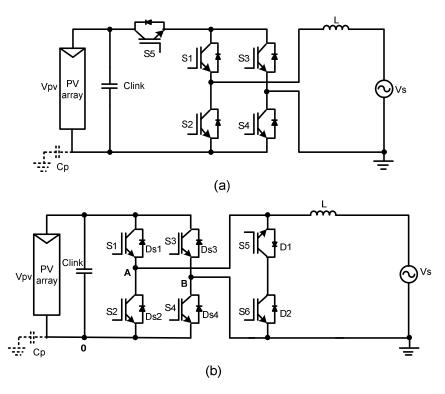

#### 1.5.3. PV Inverters with transformer on the AC side (LF)

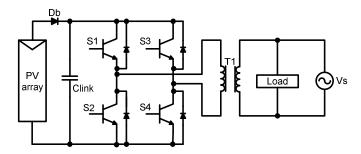

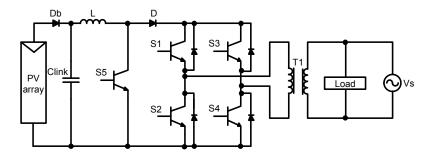

The simplest scheme used in the energy conversion in a PV system is shown in Figure 1.4. This topology use only one conversion stage and a LF transformer. The PV panels deliver a DC voltage to the inverter, with an adequate modulation scheme for S1, S2, S3 and S4 it is possible to obtain a square waveform (with sinusoidal component) at the output of the inverter. The high inductance of the transformer can reduce harmonic distortion meanwhile the transformer provides galvanic isolation. In spite of these good characteristics, the operation frequency of this transformer is around 50-60 Hz, therefore this transformer will be big, bulky and expensive. In addition, another drawback of this topology is that the DC input voltage should be high enough to reach the voltage level of the electrical grid without using a very high turn ratio in the transformer, which would result in very high currents and losses [1.7].

**Figure 1.4.** Full-bridge PV inverter with low frequency transformer.

In order to solve the problem of the low DC voltage at the input, some topologies with DC-DC boost converter have been proposed. This DC-DC converter boost the DC input voltage and follows the maximum power point of the PV panel or array. The Figure 1.5 shows the scheme of this converter.

Figure 1.5. Full-bridge PV inverter with low-frequency transformer and DC-DC boost converter.

In the converter structure of Figure 1.5, there are more components than in the first topology, as a consequence this topology become more expensive and the control could be more complex. In spite of these drawbacks this inverter is on the market with efficiencies between 93% and 95% [1.7].

The low-frequency transformer isolates the circuitry from the grid and minimizes the EMC (Electromagnetic Compatibility) problems even when an asymmetric Pulse Width Modulation (PWM) pattern is used. Moreover, the LF transformer has losses in the core reducing the total efficiency of the system. In general, the LF transformer is a big drawback in PV systems connected to the electrical grid.

#### 1.5.4. PV Inverters with transformer on the DC side (HF)

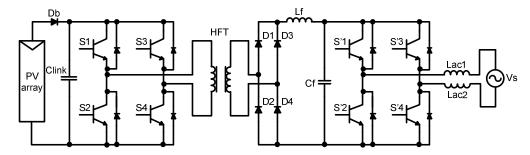

In order to overcome the associated problem with the LF transformer a new configuration was proposed [1.8]. Figure 1.6 shows a full-bridge inverter with a high-frequency

transformer. This converter has some stages which consist of a high frequency inverter, high-frequency transformer, rectifier, filter and finally a low frequency inverter.

Figure 1.6. Full-bridge PV inverter with high-frequency transformer.

The PV panels are still isolated from the grid and the first inverter delivers a high frequency square waveform to the high-frequency transformer. Therefore, the transformer size is reduced. Maximum efficiency of 95% is achievable [1.7]. As can be seen in Figure 1.6, there are eight switches which should be controlled, therefore the control becomes more complex compared to other topologies. An alternative to generate the high frequency square waveform to feed the high-frequency transformer is shown in Figure 1.7.

Figure 1.7. Full-bridge PV inverter with push-pull converter and high-frequency transformer.

As can be seen in the figure above, the total amount of switches is reduced to seven but the losses produced by the transformer still affect the total efficiency. The push-pull converter is used to boost the input voltage in order to reduce the switching losses on the high voltage side. As in the previous case, both converters in series reduce the total efficiency and the control is still complex.

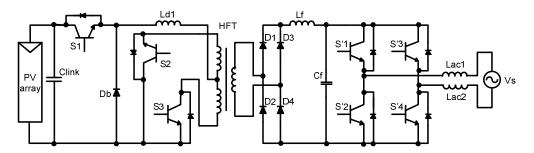

### 1.5.5. PV Inverters without transformer (transformerless)

According with the previous section, the transformer in the PV systems has some critical drawbacks; size, weight, high losses, expensive, etc. In order to avoid the use of transformers, in the last years, some topologies which do not use transformer have been

developed. When a transformer is not used, the inverter is connected directly to the electrical grid through a LCL filter; therefore there is not galvanic isolation between them.

PV panels are typically manufactured in layers involving glass, silicon semiconductor and a backplane. The junction of these layers is covered by a grounded metallic frame. A PV inverter typically operates with a switching frequency in the range of kHz (2-15 kHz depending on the power level), this high frequency can generate leakage currents which flow through the frame and the stray capacitances. These stray capacitances are established between the ground and the metallic frame, in Figure 1.8 the stray capacitances connected to the positive and negative terminals are modeled in the diagram. The stray capacitances are finally an element of a closed circuit which consists on the PV panels, the AC filter elements and the grid impedance. These capacitances provide a full path for the current to flow through ground. The value of these capacitances depends on the weather conditions, PV topology, PWM pattern, the material used in the metallic frame and the values in the passive elements of the converters. Some experiments have been done in order to determine approximately the value of these parasitic elements (under certain conditions) which has been concluded to be around 100nF/kW according with [1.9].

Figure 1.8. Leakage capacitances in a PV system.

The flow of leakage currents through the stray capacitances is not a problem just from the electrical point of view, but it is also a serious problem related to the safeness of the workers. In this sense some standards have been established in Germany by DIN (Deutsches Institut für Normung e.V.). In this standard it is established that the maximum leakage current should be 300 mA [1.10]. Considering this standard, some topologies have been developed to fulfill its requirements. In this section some of the most important transformerless PV inverters able to avoid the appearance of these currents will be explained.

#### Transformerless single-phase PV inverters

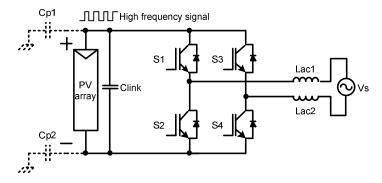

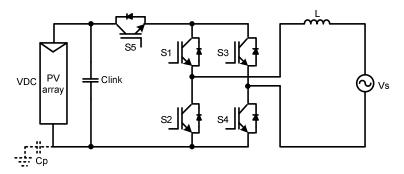

In the case of the single-phase PV systems, one of the most popular topologies is based on the basic full-bridge Inverter and is named H5 [1.11]. In Figure 1.9 the H5 structure is shown.

**Figure 1.9.** Single-phase H5 PV topology (SMA technologies).

The PWM pattern for this topology can be design in order to get constant CMV. The PWM pattern in this case introduces the null state through S5. During the positive half cycle, when switches S5, S1 and S4 are ON and S2 and S3 are OFF, an active state is applied to the output. In this state, the current in the link inductor increases, Figure 1.10 a). In order to apply a null state at the output, S5 and S4 goes OFF and S2 and S3 remain OFF. In this case, the current decreases and flows through S1 and the diode of S4. This means that the S5 and S4 are switching at high frequency, Figure 1.10 b).

Figure 1.10. Modulation states during positive half cycle; (a) Active state, (b) Null state.

On the other hand, during negative half cycle when switches S5, S3 and S2 are ON an active state is applied to the load. This means that the current in the link inductor increases, Figure 1.11 a). The zero voltage state can be applied if S5 and S2 go OFF. In this case, the current decreases and flows through S3 and free-wheeling diode of S1. In this half cycle S5 and S2 are switching at high frequency, this state is shown in Figure 1.11 b).

The pulse width modulation explained above, shows that the  $5^{th}$  switch allows to isolate the PV panels from the electrical grid during zero voltages states and as a consequence constant CMV on the PV converter is obtained and the leakage ground current does not flow through the stray capacitances. As an additional characteristic, the  $5^{th}$  switch avoids reactive power exchange between the  $C_{link}$  and the L filter, reducing the losses in the semiconductors and reactive components.

**Figure 1.11.** Modulation states during negative half cycle; (a) Active state, (b) Null state.

H5 is very suitable for transformerless PV applications due to its good characteristics regarding to EMI (Electromagnetic Interference) components at PV terminals and high efficiency. Actually, H5 is currently commercialized by SMA in the series SunnyBoy 4000/5000 TL with European efficiency higher than 97.7% and maximum efficiency of 98%.

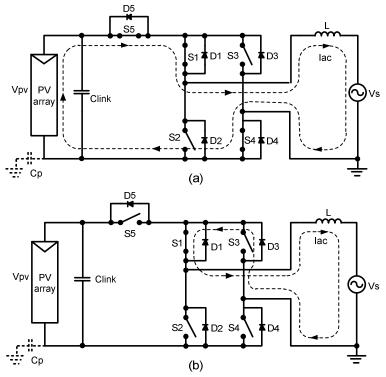

Another transformerless PV topology which is widely used in the PV market is the HERIC (High Efficiency Reliable Inverter Concept) topology. This topology is also based in the conventional single-phase full-bridge inverter and was patented by Sunways in 2006. In this case, this topology generates the null state at the AC side by using extra switches, which allows set all the switches of the full-bridge in OFF during the null state. In this way the PV panels are isolated from the AC side. The scheme of this structure is depicted in Figure 1.12.

**Figure 1.12.** Single-phase transformerless HERIC topology [1.12].

Figure 1.13. Modulation states during positive half cycle; (a) Active state, (b) Null state.

As it can be appreciated in Figure 1.12, there are two additional switches with the collector connected at the same point, forming a bidirectional switch. In Figure 1.13 a), during the positive half cycle, when S1, S4 and S5 are ON (S2, S3 and S6 are OFF), an active state is applied to the output. In this case, the output current increases. In order to apply a null state, S1 and S4 go OFF while S5 remains ON (S2, S3 and S6 are kept OFF). In this case, the output current decreases and flows through the S5 and D2 (free-wheeling situation). This state is shown in Figure 1.13 b). During all positive half cycle S1 and S4 are switched at switching frequency while S5 is switched at the line frequency. On the other hand, during the negative half cycle, when S2, S3 and S6 are ON (S1, S4 and S5 are turned OFF), an active state is applied and then the output current increases, see Figure 1.14 a). The null state is applied by means of turning OFF S2 and S3 while S1, S4 and S5 are kept OFF and then the output current flows through the S6 and D1. In this case, the current decreases. This state is shown in Figure 1.14 b). As in the case of the positive half cycle, S2 and S3 are switched at the switching frequency and S6 is switched at the line frequency.

**Figure 1.14.** Modulation states during negative half cycle; (a) Active state, (b) Null state.

From the modulation explained above, it is possible to see that the two additional switches can avoid the reactive power exchange between the L filter and the  $C_{link}$  capacitance. Moreover these two switches operate as a bidirectional switch and provide a path during zero voltage states. With this solution the voltage across the filter is unipolar, yielding in lower core losses. As a result, considering these two important characteristics, the efficiency in this

topology can be high, around 97%. Moreover, no common mode switching frequency components can appear over the PV panel terminals, therefore there are not leakage ground currents flowing through the stray capacitances.

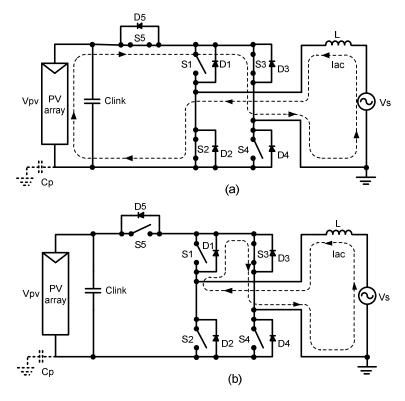

Another promising topology in single-phase PV systems for transformerless applications is the NPC (Neutral Point Clamped) topology. This topology consists in a leg with four transistors in series as shown in Figure 1.15 [1.13].

**Figure 1.15.** The NPC topology for transformerless single-phase PV applications.

The NPC topology is a structure that consists in four switches connected in series which are modulated in order to obtain an AC waveform at the output. This topology is suitable for PV transformerless systems because there are not voltage fluctuations on the DC side since the PV panels are ground clamped. The null state is achieved by connecting (clamping) the output to the grounded middle point of the DC bus using D1 and D2, depending on the sign of the output current.

During the positive half cycle, S2 remains ON while S1 and S3 are switched at switching frequency in a complementary way in order to generate the active and null states. When S1 is ON and S3 is OFF, an active state is applied to the output and the current in the link inductance increases and flows through S1 and S2 toward the output, as is shown in Figure 1.16 a). On the other hand, when S1 goes OFF and S3 comes ON a null state is applied to the output and the output current decreases while flows through S2 and D1, see Figure 1.16 b).

In negative half cycle, shown in Figure 1.17, S3 remains ON along the whole negative half cycle, while S2 and S4 are switched at the switching frequency in a complementary way to provide the active and null states to the output. The active state is applied when S4 comes ON and S2 goes OFF. In this case, the current in the link inductance increases and flows though the switches S3 and S4 see Figure 1.17 a). The null state is applied when S4 goes OFF and S2 comes ON, dealing in a decrease of the output current, which flows through D2 and S3. This state is depicted in Figure 1.17 b).

The NPC topology has the advantage that the voltage across the output filter is unipolar, thus it is possible to obtain low core losses. Moreover, with this configuration there is not power exchange between the  $C_{link}$  and L filter at the output during null states, so the efficiency can be high, around 98%. Another important thing that contributes to improve the efficiency is that S2 and S3 are switched at the grid frequency. Finally, in order to increase the efficiency even more, the voltage rating of the switches S1 and S4 can be reduce to  $V_{dc}/4$ , leading in a switching losses reduction. The most remarkable problems with this topology lays in the fact that there are two additional diodes, requires double voltage input in comparison with the conventional full-bridge inverter and unbalance switching losses may appear because of the different switching frequency in S1 and S4 (high frequency) and S2 and S3 (grid frequency). It is important to mention that due to the way in which the null states are generated there are no voltage fluctuations on the PV terminals and, as a consequence, no leakage current appears [1.14].

**Figure 1.16.** Modulation states in the NPC topology during positive half cycle; (a) Active state, (b) Null state.

This inverter is currently used by *Danfoss Solar inverters* in the *TripleLynx* series (three-phase 10/12.5/15 kW), and it is commercialized with an European Efficiency around 97% and maximum efficiency around 98% [1.15].

**Figure 1.17.** Modulation states in the NPC topology during negative half cycle; (a) Active state, (b)

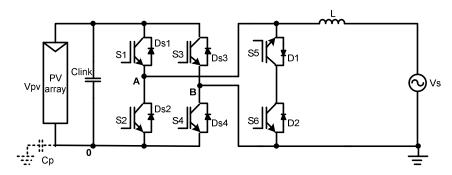

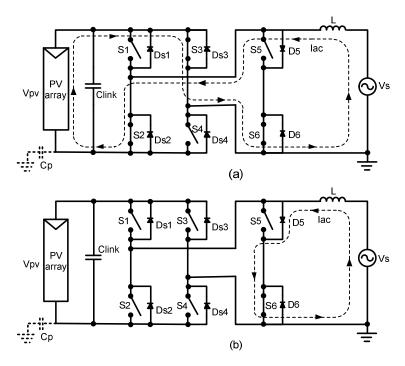

Finally, the last topology included in this summary related to the single-phase transformerless topologies for PV applications is also based on the full-bridge inverter. This topology is a modified H5 topology, the main difference is that in this topology the AC side is not floating, but it is clamped at the middle point of the dc-link capacitors. The scheme of this structure is shown in Figure 1.18 [1.16].

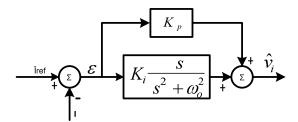

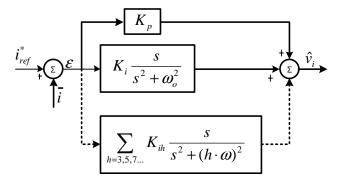

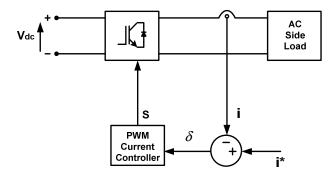

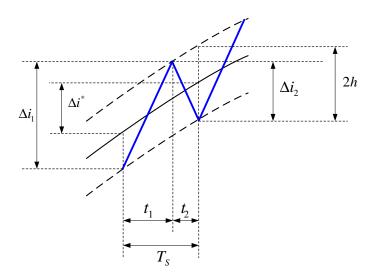

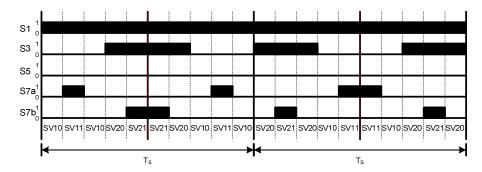

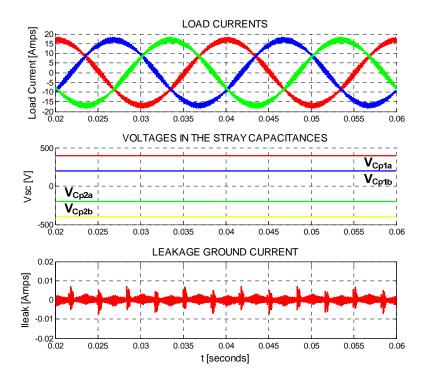

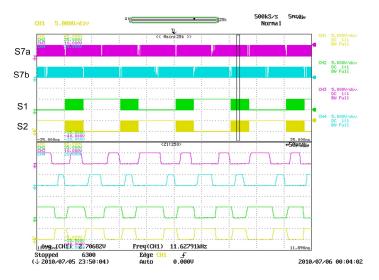

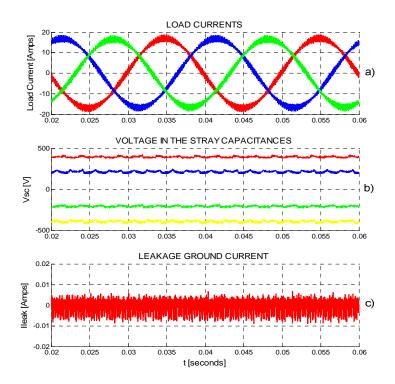

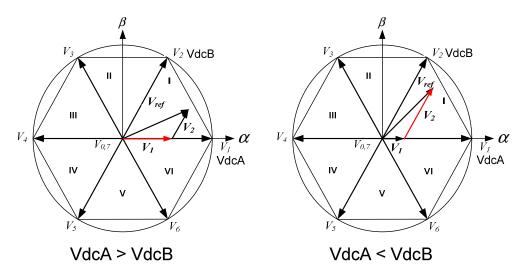

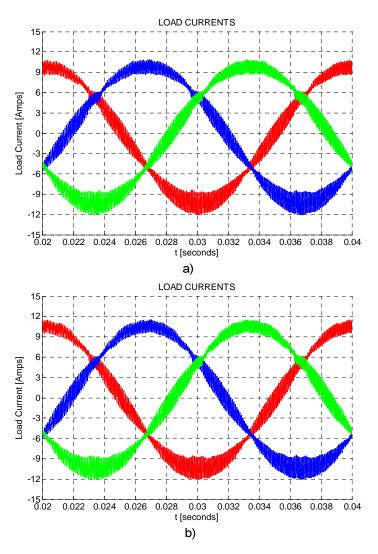

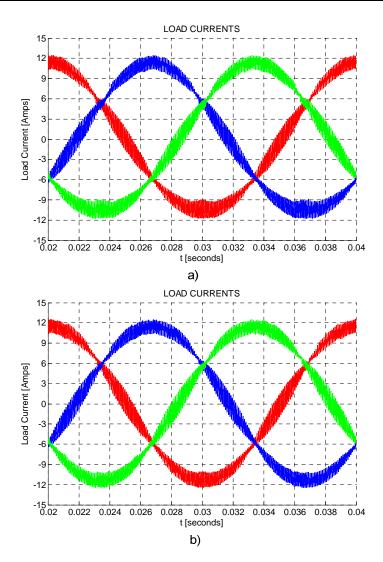

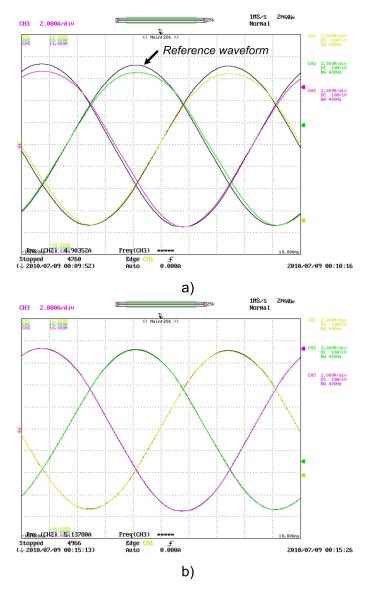

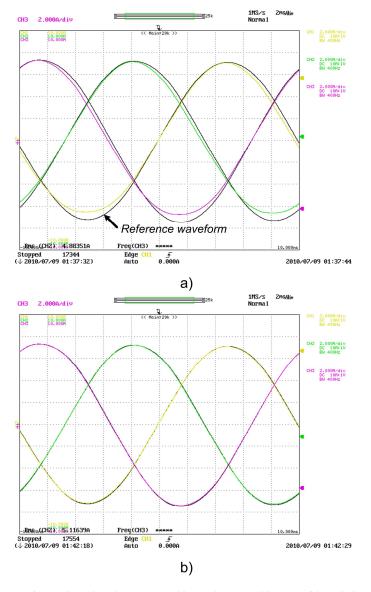

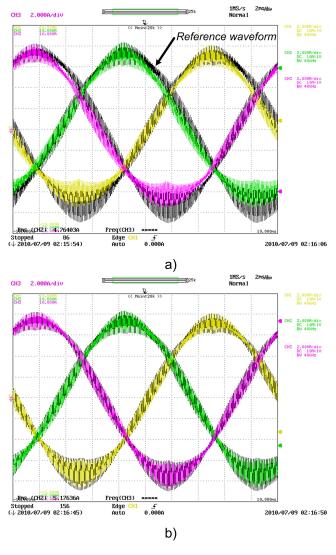

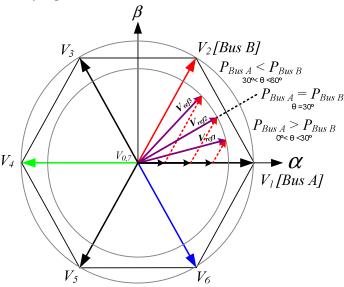

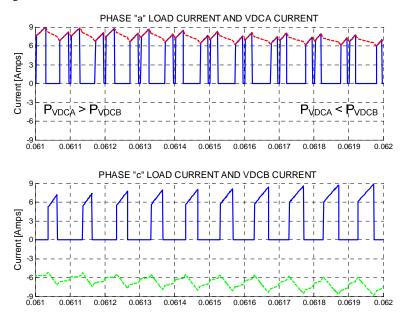

Figure 1.18. Full-bridge inverter with DC by-pass.