#### COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS

#### Muthupandian Cheralathan

Dipòsit Legal: T. 1294-2012

**ADVERTIMENT**. L'accés als continguts d'aquesta tesi doctoral i la seva utilització ha de respectar els drets de la persona autora. Pot ser utilitzada per a consulta o estudi personal, així com en activitats o materials d'investigació i docència en els termes establerts a l'art. 32 del Text Refós de la Llei de Propietat Intel·lectual (RDL 1/1996). Per altres utilitzacions es requereix l'autorització prèvia i expressa de la persona autora. En qualsevol cas, en la utilització dels seus continguts caldrà indicar de forma clara el nom i cognoms de la persona autora i el títol de la tesi doctoral. No s'autoritza la seva reproducció o altres formes d'explotació efectuades amb finalitats de lucre ni la seva comunicació pública des d'un lloc aliè al servei TDX. Tampoc s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant als continguts de la tesi com als seus resums i índexs.

**ADVERTENCIA.** El acceso a los contenidos de esta tesis doctoral y su utilización debe respetar los derechos de la persona autora. Puede ser utilizada para consulta o estudio personal, así como en actividades o materiales de investigación y docencia en los términos establecidos en el art. 32 del Texto Refundido de la Ley de Propiedad Intelectual (RDL 1/1996). Para otros usos se requiere la autorización previa y expresa de la persona autora. En cualquier caso, en la utilización de sus contenidos se deberá indicar de forma clara el nombre y apellidos de la persona autora y el título de la tesis doctoral. No se autoriza su reproducción u otras formas de explotación efectuadas con fines lucrativos ni su comunicación pública desde un sitio ajeno al servicio TDR. Tampoco se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al contenido de la tesis como a sus resúmenes e índices.

**WARNING**. Access to the contents of this doctoral thesis and its use must respect the rights of the author. It can be used for reference or private study, as well as research and learning activities or materials in the terms established by the 32nd article of the Spanish Consolidated Copyright Act (RDL 1/1996). Express and previous authorization of the author is required for any other uses. In any case, when using its content, full name of the author and title of the thesis must be clearly indicated. Reproduction or other forms of for profit use or public communication from outside TDX service is not allowed. Presentation of its content in a window or frame external to TDX (framing) is not authorized either. These rights affect both the content of the thesis and its abstracts and indexes.

### **DOCTORAL THESIS**

### **MUTHUPANDIAN CHERALATHAN**

## COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS

### **UNIVERSITAT ROVIRA I VIRGILI**

Department of Electronic, Electric and Automatic Engineering

### Muthupandian Cheralathan

## COMPACT MODELING FOR MULTI-GATE MOSFETs USING ADVANCED TRANSPORT MODELS

## DOCTORAL THESIS

### Supervised by Prof. Benjamin Iñiguez

Department of Electronic, Electric and Automatic Engineering

**UNIVERSITAT ROVIRA I VIRGILI**

Tarragona 2013

Department of Electronic, Electric and Automatic Engineering (DEEEA) Av. Paisos Catalans 26, Campus Sescelades 43007, Tarragona, Spain Phone: +34 977 558524 Fax: +34 977 559605

I STATE that the present study, entitled "Compact Modeling for Multi-Gate MOSFETs using Advanced Transport models", presented by Muthupandian Cheralathan for the award of the degree of doctor, has been carried out under my supervision at the Department of Electronic, Electric and Automatic Engineering of this university, and that it fulfills all the requirements to be eligible for the European Doctorate Award.

Tarragona, 25<sup>th</sup> February 2013

Doctoral Thesis Supervisor

Professor Benjamin Iñiguez

# Acknowledgments

A great number of wonderful people have made my Universitat Rovira i Virgili career a very rewarding and memorable experience. I would like to have a special thought for those people that in one way or another have contributed to carry out this work.

First and foremost, I would like to express my grateful and sincere thanks to my supervisor Prof. Benjamin Iñiguez, for his guidance and encouragement at all stage of my work at Universitat Rovira i Virgili. I am extremely lucky to have had a supervisor who cared so much about my work, and who responded to my questions and queries so promptly. During the brainstorming sessions, he has helped me develop a clear technical understanding of device physics, TCAD, and technology. Without his kind support this research work would have not been possible. I would specially thank him for giving me the freedom and opportunity to advertise my work at various important conferences.

I would like to give a special thank you to Prof. Antonio Cerdeira, who has always been a source of never ending advice and help, and with whom I have collaborated closely during the years.

My most rewarding experience was the summer I spent at IMEP-MINATEC, Grenoble, France. I would also like to thank

Prof. Sorin Cristoloveanu for giving me the opportunity to participate in his research group.

I would like to thank Dr. Gilles Depeyrot in particular, for allowing me to participate in the world of MEDAL in Dolphin Integration, Grenoble, France.

I would like to especially thank Prof. Jamal Deen, whose help and advice has been well received and put to good use.

I would like to give special thanks to Prof. Lluis Marsal, the head of DEEEA, for giving me the opportunity to come to URV and start this wonderful journey.

My sincere thanks and acknowledgements are due to my wife Seema and my parents. I would like to give thanks to my friends Maria Mendez, Ghader Darbandy, Alexandra, Francois lime, and Mahbub for their moral support. The support of the staff from the Department of Electrical and Electronics Engineering, URV is also greatly appreciated.

# Prologue

The continuous scaling-down process of the channel length over the last four decades is reaching its limits in terms of gate oxide thickness, short channel effects and power consumptions, increased leakage currents. The multiple-gate SOI CMOSFET devices are expected to replace the bulk CMOSFET transistors for a better control of the entire device electrostatics. In today's extremely scaled MOSFETs the channel length is in the order of the carrier mean-free-path ( $\lambda$ ). This means that carriers, when travelling from source towards the drain, experience only few scattering events. This regime is commonly referred to as quasiballistic transport. Quasi-ballistic (QB) effects are expected to occur in bulk MOSFETs as well. It is, however, the multiple gate structure that increases the device's immunity to shortchannel effects, thus allowing a further reduction of the channel length into the order of the carrier mean-free-path, making quasi ballistic transport phenomena even more likely. QB transport is an active area of research since a good understanding of the physics of carrier scattering and the main feature which impact carrier transport, can help improve and optimize the device performance. QB transport models are benchmarked against Monte-Carlo (MC) simulations. The MC approach provides a statistical solution to the Boltzmann Transport equation (BTE). The BTE is a general formulation of the semi-classical carrier

transport problem from which approximate transport models such as the Drift-Diffusion (DD) and hydrodynamic equations are derived.

In this thesis we have developed compact models including hydrodynamic transport model adapted for double-gate (DG) and surrounding-gate (SRG) MOSFETs from a unified charge control and surface potential models respectively which are derived from Poisson's equation. Similar modelling scheme have been used in all these devices. The current and total charges are written in terms of the mobile charge sheet densities at the source and drain ends of the channel. The model show good agreement with the 2D and 3D (SRG) numerical simulations, in all operating regimes. Due to the limitation of available optimized devices for analysis, numerical simulation was used as the main analysis tool. The model developed is very promising to be easily adapted in circuit simulators.

The thesis is outlined as follows: **Chapter 1** presents the state of the art, we dedicate **chapter 2** for the compact modelling of undoped and doped surrounding-gate (SRG) MOSFETs and its adaptation to reproduce advanced transport models. An analytical and continuous compact model for a long-channel cylindrical SRG MOSFETs is developed. The analytical expression for the surface potentials are continuous and explicit function of the applied voltages. The expression obtained for the potentials are used to derive an analytical compact model for the

drain current which is valid from low to high doping. The results are compared with 3D ATLAS device simulator. Further, the compact model is then extended to include the hydrodynamic transport and quantum mechanical effects, and we show that it can reproduce results of 3D numerical simulations using advanced transport models. The final compact model includes mobility degradation, drain-induced barrier lowering, velocity overshoot and quantum effects.

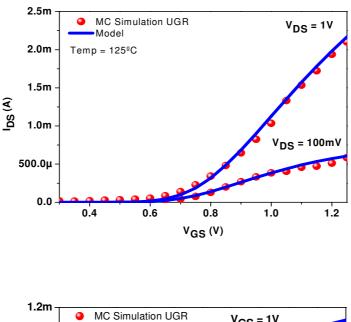

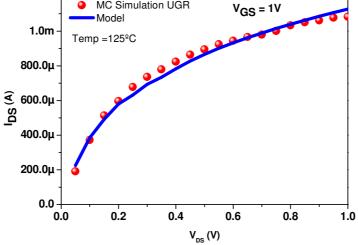

In chapter 3 extension of the compact double-gate (DG) MOSFET model to reproduce advanced transport models, first our compact drain current model for DG MOSFET has been extended to include the hydrodynamic transport and quantum mechanical effects. The final compact model can accurately reproduce simulation results of some of the most advanced transport simulators. The model is based on a compact model for charge quantization within the channel and it includes mobility degradation, channel length modulation, drain-induced barrier lowering, overshoot velocity effects and quantum mechanical effects. The temperature dependency is also accounted in the compact model.

In **chapter 4** implementation of compact model of DG and SRG MOSFETs in circuit simulator specifically in SMASH has been presented. First, the results of the implementation of a nanoscale DG MOSFETs compact model, which includes hydrodynamic transport model, in Verilog-A in order to carry out circuit

simulation are presented. The model is used with SMASH circuit simulator for the analysis of the DC and transient behaviour. A DG CMOS inverter circuit and a five stage ring oscillator circuit have been analysed. Second, compact model of a nanoscale cylindrical surrounding-gate (SRG) MOSFETs which includes hydrodynamic transport model, in Verilog-A implemented in circuit simulation are presented.

Finally in **chapter 5**, we will summarize the main findings of this work and conclude with some directions for future extension of the work addressed in this thesis.

# **List of Symbols**

- $\phi$  Electrostatic potential

- $N_a$  Doping concentration

- $\boldsymbol{\varepsilon}_{si}$  Permittivity of silicon

- *q* Electric charge

- $\Phi_f$  Fermi level

- $\Phi_t$  Thermal voltage

- *C*<sub>ox</sub> Gate capacitance per unit area

- $C_{si}$  Silicon capacitance per unit gate area

- $t_{ox}$  Oxide thickness

- $\boldsymbol{\varepsilon}_{ox}$  Permittivity of oxide

- *R* Radius of the cylindrical silicon body

- $V_{fb}$  Flat band voltage

- *V<sub>ch</sub>* Channel voltage

- $V_{gs}$  Applied to the gate voltage

- $Q_{dep}$  Fixed charge density per unit gate area

- $Q_{in}$  Inversion charge density per unit gate area

- $E_s$  Electric field at the silicon-oxide interface

i

- $\phi_{_{sBT}}$  Surface potential at subthreshold

- $\phi_{_{oBT}}$  Center potential at subthreshold

- LW Lambert function

- $\phi_{sT}$  Surface potential at threshold

- $\phi_{oT}$  Center potential at threshold

- $\phi_s$  Overall surface potential

### $\alpha_{T}$ - Normalized difference between the surface and the

center potential at threshold

- $V_{GM}$  Maximum applicable gate voltage

- $Q_{sem}$  Semiconductor charge per unit gate area

- W Channel width

- *L* Channel length

- $\mu$  Electron mobility

- $V_s$  Source voltage

- $V_D$  Drain voltage

- $V_{dss}$  Effective drain-source voltage

- $C_{ox}^*$  Corrected oxide capacitance

- $V_T$  Threshold voltage

- $\Delta V_T$  Corrected threshold voltage

- $\sigma$  Fitting parameter

- $L_m$  Reference length

- *L<sub>C</sub>* Characteristics length

- $v_{sat}$  Saturation velocity

- *V<sub>sat</sub>* Saturation potential

- $au_w$  Energy relaxation time constant

- $\lambda_{w}$  Energy-relaxation length

- *T* Temperature

- $\mu_o$  Low-field mobility

- $\mu_{eff}$  Effective mobility

- $E_{sat}$  Saturation field

- $L_e$  Effective length

- $\Delta L$  Saturated channel length

- Mobility attenuation coefficients of the first order

- $\theta_2$  Mobility attenuation coefficients of the second order

- $q_s$  Normalized induced charge at the source

- $q_d$  Normalized induced charge at the drain

- *V<sub>bi</sub>* Source and drain junction built-in voltage

- $Q_s$  -Mobile charge densities at the source

- $Q_d$  Mobile charge densities at the drain

$\Delta \phi$  - Work-function difference between the gate electrode and the intrinsic silicon

- $n_i$  Intrinsic concentration

- $C_g$  Effective oxide capacitance

- $C_{gs}$  Gate-source capacitance

- $C_{gd}$  Gate-drain capacitance

- $\hbar$  Reduced Planck constant

- $m_{eff}$  Electron effective mass

- *γ* Fitting parameter

iii

iv

# List of figures

| Figure 1.1 Plot of transistor count against dates of introduction – (Moore's law)                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 Predicted ITRS Roadmap for the next decade4                                                                                                                                                                                                      |

| Figure 1.3 (A) Partially depleted and (B) Fully depleted SOI MOSFETs                                                                                                                                                                                        |

| Figure 1.4 Various structures of multi-gate MOSFETs. (BOX: buried oxide; SOI: silicon-on-insulator)7                                                                                                                                                        |

| Figure 2A.1 Schematic cross-section of an N-channel SRG MOSFET showing the coordinate system and related variables                                                                                                                                          |

| Figure 2A.2 Modeled (circles) and Simulated (triangles) potential at the surface of the Si layer as a function of $N_a$ in the subthreshold regime for $t_{ox}$ =3nm and $R$ =5 nm                                                                          |

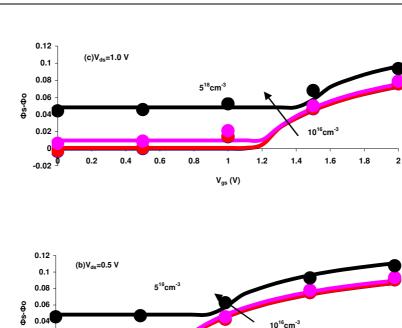

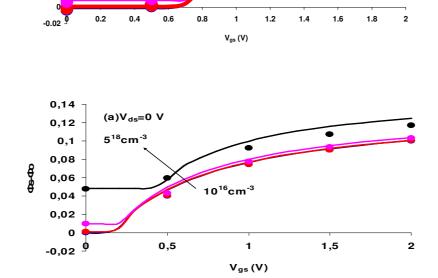

| Figure 2A.3a, b and c. Modeled (solid lines) and numerically simulated (symbols) potential difference $\phi_s - \phi_o$ as a function of gate voltage for different Si layer concentration and V <sub>ds</sub> = 0, 0.5 and 1 V, $t_{ox}$ =3nm and R =5nm32 |

| Figure 2A.4 Modeled (solid lines) and numerically simulated (symbols) surface potential as a function of gate voltage for different Si layer concentrations                                                                                                 |

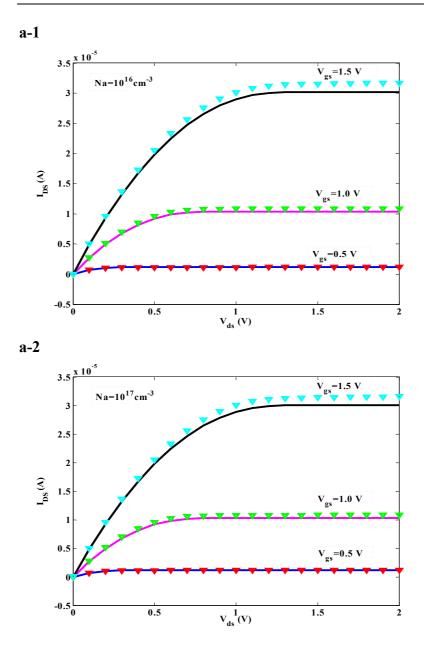

| Figure 2A.5 Output (a1-a2) characteristics. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot                                                                                     |

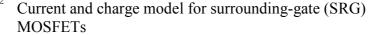

| Figure 2A.5 Output (a3-a4) characteristics. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot                                                                                     |

v

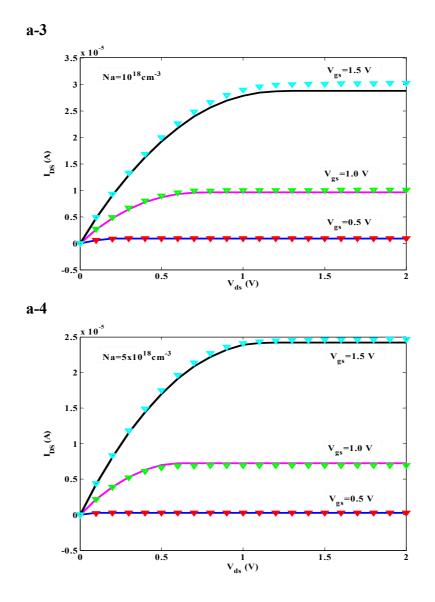

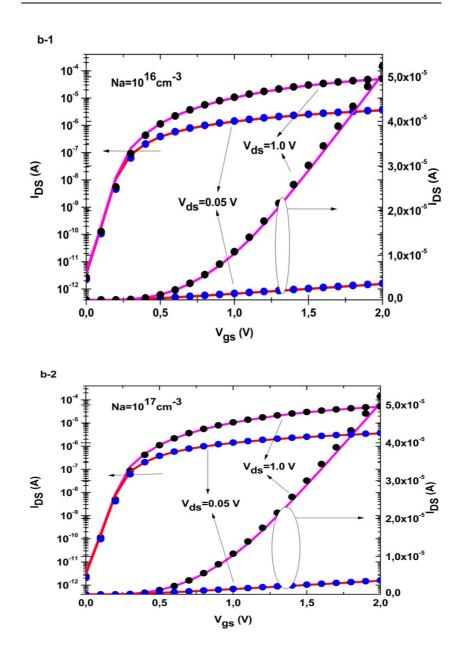

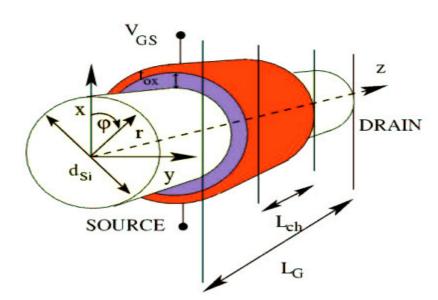

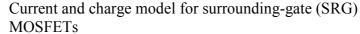

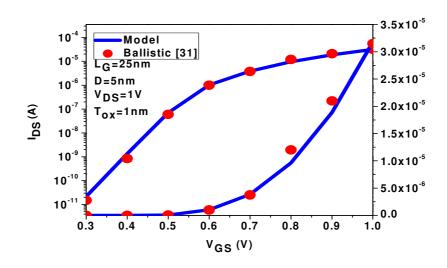

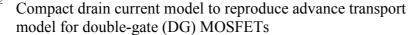

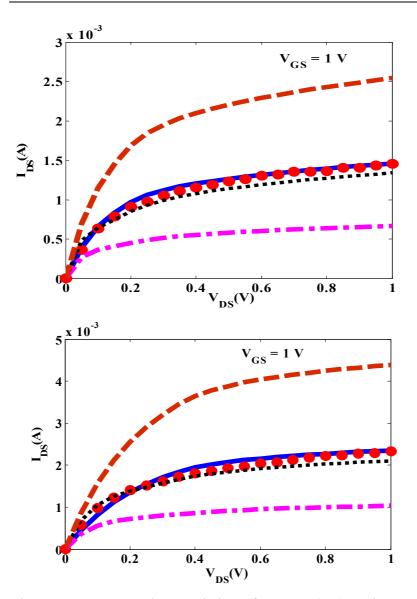

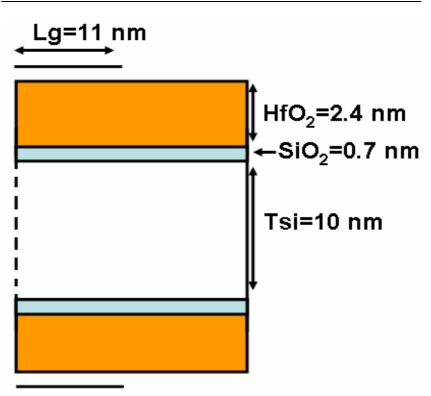

Figure 2B.2 Transfer characteristics of the cylindrical SRG MOSFET (Figure 2B.1) for low (top) and high (bottom)  $V_{DS}$ . 3D numerical simulation data by Synopsys (SNPS) [27], Univ. of Bologna (IUNET-BO) [28]-[29], IMEP [30].....60

Figure 2B.3 Transfer characteristics of a cylindrical SRG MOSFET at high  $V_{DS}$  both in linear and logarithmic scale.....64

Figure 2B.4 Transfer characteristics of a cylindrical SRG MOSFET at high  $V_{DS}$  both in linear and logarithmic scale.....64

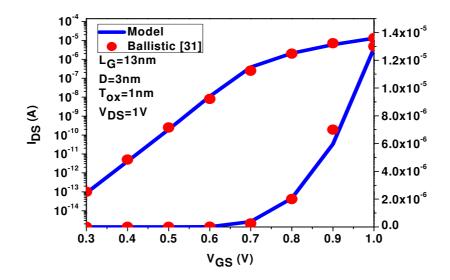

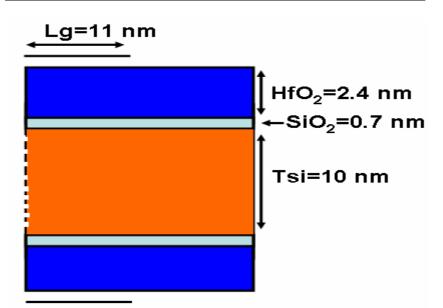

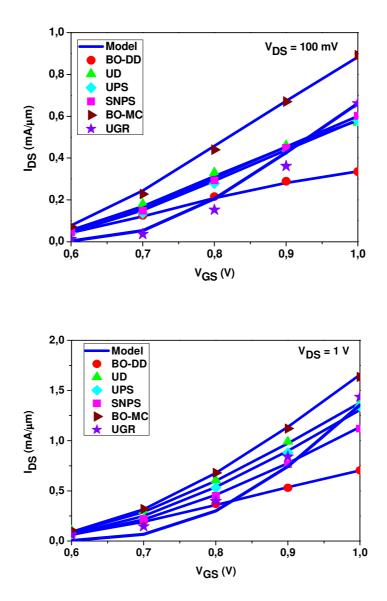

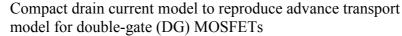

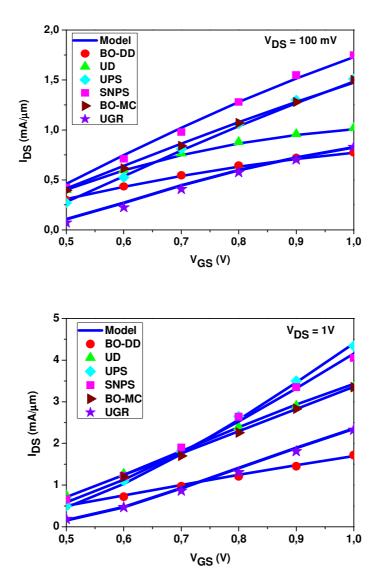

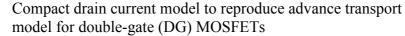

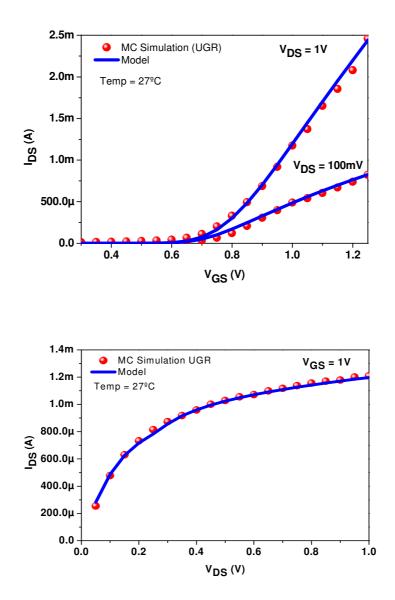

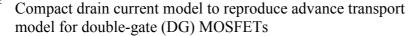

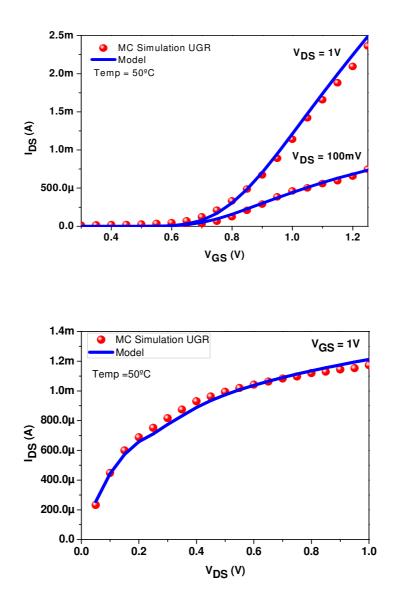

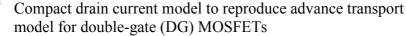

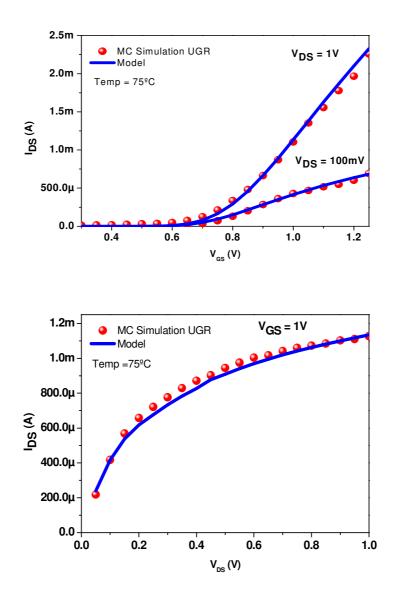

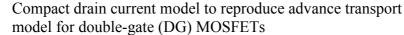

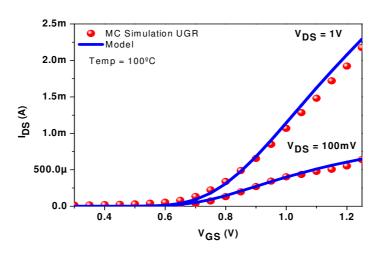

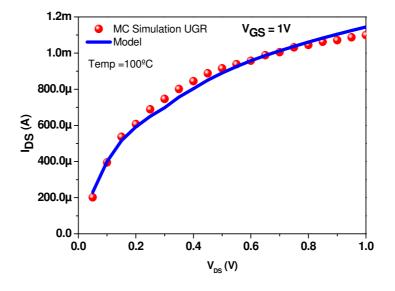

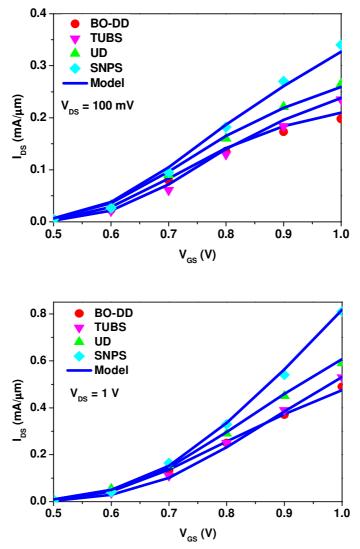

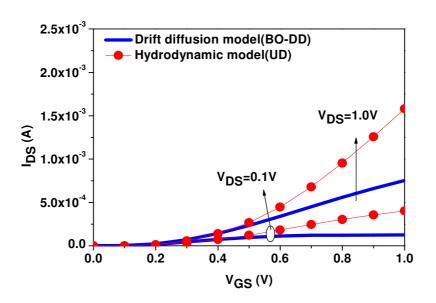

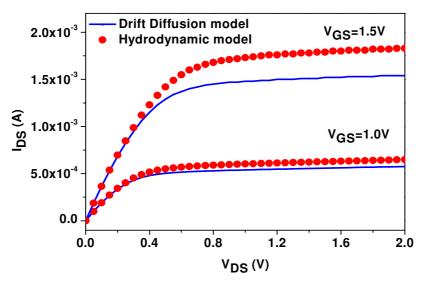

Figure 3.2: Transfer characteristics of 22 nm DG MOSFETs for low (top) and high (bottom)  $V_{DS}$ . 2D numerical simulation data by Univ.of Bologna (BO-DD) [2], Univ.of Udine (UD) [2], Univ.of Paris-Sud (UPS) [2], Synopsys (SNPS) [2], Univ.of Bologna (BO-MC) [2], Univ.of Granada (UGR) [1].......92

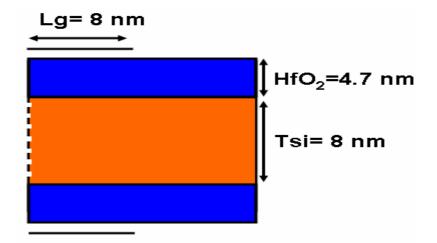

Figure 3.3: Transfer characteristics of 16 nm DG MOSFETs for low (top) and high (bottom)  $V_{DS}$ . 2D numerical simulation data by Univ.of Bologna (BO-DD) [2], Univ.of Udine (UD) [2], Univ.of Paris-Sud (UPS) [2], Synopsys (SNPS) [2], Univ.of Bologna (BO-MC) [2], Univ.of Granada (UGR) [1]......94

vi

vii

| Figure 4A.2: Transfer characteristics of 22 nm DG p-channel MOSFETs for low (top) and high (bottom) V <sub>DS</sub> . 2D numerical simulation data by Univ.of Bologna (BO-DD) [12-13], Tech. Univ. Braunschweig (TUBS) [17-20], Univ.of Udine (UD) [14-15], Synopsys (SNPS) [16] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

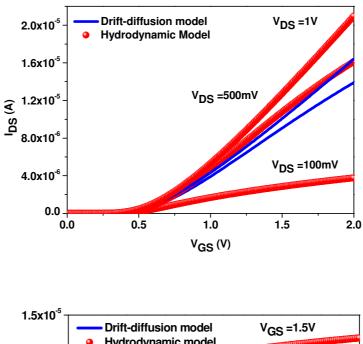

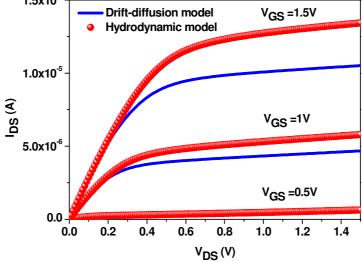

| Figure 4A.4 Transfer characteristics obtained for an n-channel DG MOSFET Lg=22 nm Ts=10 nm and EOT=1.1 nm128                                                                                                                                                                     |

| Figure 4A.5 Output characteristics obtained for an n-channel DG MOSFET Lg=22 nm Ts=10 nm EOT=1.1 nm128                                                                                                                                                                           |

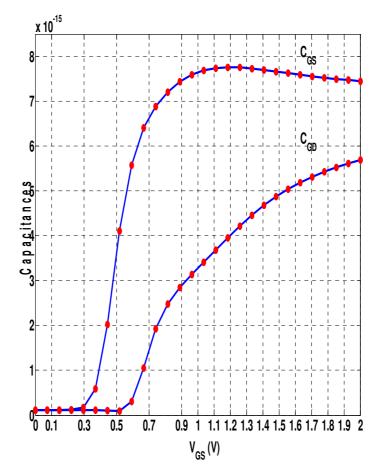

| Figure 4A.6 Gate-to-source capacitance (Cgs) and gate-to-drain capacitance (Cgd), for $V_{DS}$ =0.5V, obtained using the method implemented in Verilog-A with SMASH (Symbols) and the entire capacitance model developed (lines)                                                 |

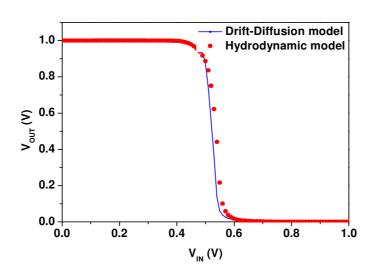

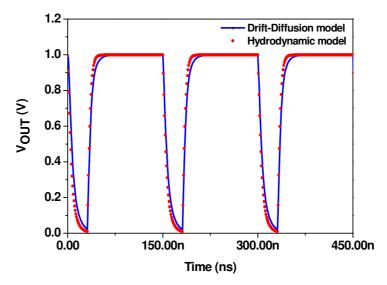

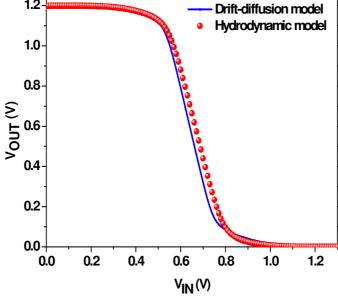

| Figure 4A.7 Voltage transfer characteristics of a 22nm CMOS inverter using the DG MOSFET model in Verilog-A with SMASH                                                                                                                                                           |

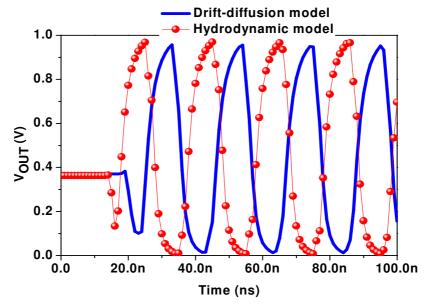

| Figure 4A.8 Transient response of 22nm CMOS inverter using our DG MOSFET model in SMASH by means of Verilog-A.132                                                                                                                                                                |

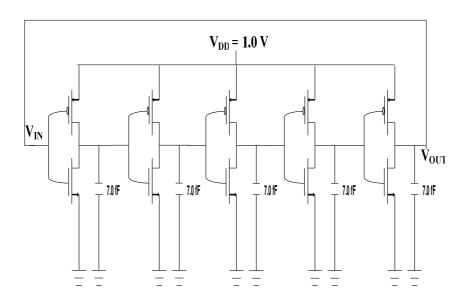

| Figure 4A.9 Five stage Ring oscillator134                                                                                                                                                                                                                                        |

| Figure 4A.10 Transient response of 22nm five stage CMOS ring oscillator using our DG MOSFET model in SMASH by means of Verilog-A                                                                                                                                                 |

| Figure 4B.1 Transfer (top) and output (bottom) characteristics<br>for an n-channel SRG MOSFET Lg=6 nm Ts= 4 nm and EOT=<br>1 nm                                                                                                                                                  |

| Figure 4B.2 Voltage transfer characteristics of a CMOS inverter using SRG MOSFET model in Verilog-A with SMASH <b>140</b>                                                                                                                                                        |

viii

# List of tables

Table 4A.1 Parameters used in the proposed analytical model in order to fit the simulations obtained using different transport models......**125**

Х

# List of Publications Journal papers

**Muthupandian Cheralathan**, Esteban Contreras, Joaquín Alvarado, Antonio Cerdeira, Giuseppe Iannaccone, Enrico Sangiorgi, Benjamin Iñiguez, "Implementation of Nanoscale Double-Gate CMOS circuits using Compact Advanced Transport Models", Microelectronics Journals, Vol. 44, Issue 2, pages 80-85, February 2013, ISSN 0026-2692, 10. 1016/j.mejo. 2012.11.006.

Sung-Jae Chang, **Muthupandian Cheralathan**, Maryline Bawedin, Benjamin Iniguez, Burhan Bayraktaroglu, Jong-Hyun Lee, Jung-Hee Lee, Sorin Cristoloveanu, "Mobility behavior and models for fully depleted Nanocrystalline ZnO thin film transistors", Solid State Electronics EUROSOI' 2012 Special issue, (Under Review).

**M. Cheralathan**, G. Iannaccone, E. Sangiorgi, B. Iñiguez, "Analytical Drain Current Model Reproducing Advanced Transport Models in Nanoscale Cylindrical Surrounding-Gate (SRG) MOSFETs", J. Appl. Phys. 110, 034510(2011) ; doi : 10.1063/1.3618678 (5pages).

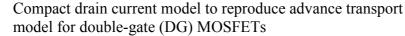

**M. Cheralathan**, C. Sampedro, J. B. Roldán, F. Gámiz, G. Iannaccone, E. Sangiorgi, B. Iñiguez, "Compact Drain Current Model for Reproducing Advanced Transport Models in Nanoscale Double-Gate (DG) MOSFETs", Semicond. Sci. Technol. Volume 26, No. 9 pp: 095015-095021 (7pages), September 2011.

**M. Cheralathan**, A. Cerdaira and B. Iñiguez, "Compact model for long-channel cylindrical surrounding-gate MOSFETs valid from low to high doping concentrations", Solid-State Electronics, Volume 55, Issue 1, January 2011, Pages 13-18.

xi

A. Lázaro, B. Nae, **C. Muthupandian** and B. Iñíguez, "High-frequency compact analytical noise model of gate-all-around MOSFETs", Semiconductor Science and Technology, Volume 25, Issue 3, 035015(10pp), March 2010.

### **International Conferences**

**Cheralathan, Muthupandian**; Contreras, Esteban; Alvarado, Joaquin; Cerdeira, Antonio; Iniguez, Benjamin; , "Simulation study of nanoscale double-gate CMOS circuits using compact advanced transport models," Mixed Design of Integrated Circuits and Systems (MIXDES), 2012 Proceedings of the 19th International Conference , vol., no., pp.74-77, 24-26 May 2012

**M.Cheralathan**, G.Iannaccone, E.Sangiorgi, B.Iñiguez, "Analytical DC Model of Double-Gate (DG) p-channel MOSFETs adapted to Advanced Transport Models", MOS-AK/GSA Workshop, Dresden, Germany, April 26th – 27th , 2012

**Cheralathan, M.**; Chang, S. J.; Bawedin, M.; Bayraktaroglu, B.; Lee, J. H.; Iniguez, B.; Cristoloveanu, S.; , "Mobility models for ZnO TFTs," Devices, Circuits and Systems (ICCDCS), 2012 8th International Caribbean Conference on , vol., no., pp.1-4, 14-17 March 2012, doi: 10.1109/ICCDCS.2012.6188880.

S.-J. Chang, **M. Cheralathan**, M. Bawedin, B. Iniguez, B. Bayraktaroglu, J-H. Lee, S. Cristoloveanu, "Mobility models for Zinc oxide Thin film Transistors", Proc. of EUROSOI2012, Montpellier, France, January 23th -25th, pp 71-72, 2012.

**M.Cheralathan**, G.Iannaccone, E.Sangiorgi, B.Iñiguez, "Compact DC Model of Cylindrical Surrounding-Gate (SRG) MOSFETs adapted to Advanced Transport Models", MOS-AK/GSA Workshop, Paris, France, April 7th – 8th, 2011

xii

S.-J. Chang, **M.Cheralathan**, M. Bawedin, B. Iniguez, B. Bayraktaroglu, J-H. Lee, S. Cristoloveanu, "Mobility behaviour and models for ZnO TFTs," International dvanced Workshop on 'Frontiers in Electronics' (WOFE'11), SanJuan, Puerto Rico (18–21 dec. 2011)

Cheralathan, M.; Sampedro, C.; Roldan, J. B.; Gamiz, F.; Iannaccone, G.; Sangiorgi, E.; Iniguez, B.; "Analytical drain current model reproducing advanced transport models in nanoscale double-gate (DG) MOSFETs," Ultimate Integration on Silicon (ULIS), 2011 12th International Conference on , vol., no., pp.1-4, 14-16 March 2011 doi: 10.1109/ULIS.2011.5757954.

**M. Cheralathan**, C. Sampedro, J. B. Roldán, F. Gámiz, B. Iñiguez, "A Compact Double-Gate MOSFET Model Consistent with a Multi-Subband Ensemble Monte Carlo Model", Proc. of EUROSOI 2011, Granada (Spain), January 17th – 19th , pp. 93-94, 2011.

**M. Cheralathan**, A. Cerdaira and B. Iñiguez, "Compact potential and current model for long-channel doped cylindrical surrounding-gate MOSFETs", Proc. of ULIS 2010, Glasgow (UK), March 18th – 19th, pp. 145-148, 2010.

xiii

xiv

# Contents

### **Chapter 1**

State of the Art and Trends for Multiple-gate MOS devices.....1

| 1.1 Introduction                     | 1  |

|--------------------------------------|----|

| 1.2 Advantages of Multi-gate MOSFETs | 8  |

| 1.3 Compact modeling                 | 9  |

| 1.4 Numerical simulations            |    |

| 1.5 Circuit simulations              | 11 |

| 1.6 References                       | 13 |

### **Chapter 2**

| Current | and | Charge | model | for | Surrounding-gate | (SRG) |

|---------|-----|--------|-------|-----|------------------|-------|

| MOSFE   | Гѕ  |        |       |     |                  | 17    |

| 2A.1 Introduction                             | 18 |

|-----------------------------------------------|----|

| 2A.2 SRG model                                | 20 |

| 2A.3 Calculation of the potentials            | 23 |

| 2A.3.1 Subthreshold regime                    | 23 |

| 2A.3.2 Threshold condition                    | 27 |

| 2A.3.3 Modeling of potentials in all regimes. | 29 |

| 2A.4 Modeling charge carriers and current     | 36 |

| 2A4.1 Charge carrier model                    | 36 |

| 2A.4.2 Current model                          |    |

| 2B.1 Introduction | 44 |

|-------------------|----|

| 2B.2 DC model     | 47 |

XV

| 2B.2.1 Expression for potentials                             | 47     |

|--------------------------------------------------------------|--------|

| 2B.2.2 Mobile charge                                         |        |

| 2B.2.3 DIBL effect                                           |        |

| 2B.2.4 Velocity overshoot                                    |        |

| 2B.2.5 Drain current                                         |        |

| 2B.3 Simulated device                                        |        |

| 2B.4 Simulated approaches                                    |        |

| 2B.4.1 SNPS (Synopsis Switzerland LLC)                       |        |

| 2B.4.2 SNPS with Ion impurities (II)                         |        |

| 2B.4.3 IUNET-BO (Consorzio Nazionale                         |        |

| Interuniversitario per la Nanoelettronica)- University of Bo | ologna |

| (Quantum Ballistic)                                          | 57     |

| 2B.4.4 IUNET-BO (Semiclassical Ballistic)                    | 58     |

| 2B.4.5 IUNET-BO (Acoustic phonon and S                       | urface |

| roughness)                                                   |        |

| 2B.4.6 IMEP (Institut de Microèlectronique                   |        |

| Electromagnètisme et Photonique), Grenoble (France)          |        |

| 2B.5 Results and Discussion                                  |        |

| 2C. Conclusions                                              |        |

| 2D References                                                |        |

|                                                              |        |

## Chapter 3

Compact Drain Current model to reproduce advance transport model for double-gate (DG) MOSFETs......73

| 3.1 Introduction                      | 74 |

|---------------------------------------|----|

| 3.2 DC model                          | 77 |

| 3.2.1 Classical charge control model  | 77 |

| 3.2.2 Velocity overshoot              | 79 |

| 3.2.3 Channel length modulation (CLM) | 81 |

| 3.2.4 DIBL effect                     | 83 |

| 3.2.5 Drain current                   | 84 |

| 3.2.6 Quantum mechanical effects      | 85 |

| 3.3 Simulated devices                 | 86 |

| 3.4 Simulated approaches              | 88 |

| 3.4.1 DD family                       | 89 |

| 3.4.1a BO-DD (Univ. Bologna)          | 89 |

xvi

| 3.4.2 MC family                        | 89  |

|----------------------------------------|-----|

| 3.4.2a BO-MC (Univ. of Bologna)        |     |

| 3.4.2b UD (Univ.of Udine)              | 89  |

| 3.4.2c UPS (Univ. of Paris-Sud)        |     |

| 3.4.2d SNPS (Synopsis switzerland LLC) | 90  |

| 3.4.2e UGR (Univ. of Granada)          | 90  |

| 3.5 Results and Discussion             |     |

| 3.6 Conclusions                        | 106 |

| 3.7 References                         | 107 |

## Chapter 4

| Nanoscale Multi-gate CMOS circuits simulation using compac | t |

|------------------------------------------------------------|---|

| models11                                                   | 3 |

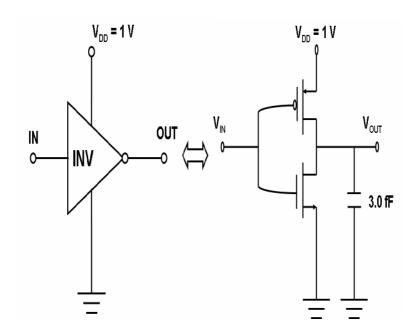

4A. Implementation of nanoscale double-gate (DG) CMOS circuits using compact advanced transport models.....114

| 14  |

|-----|

| 117 |

| 118 |

| 19  |

| 119 |

| 19  |

| 20  |

| 25  |

| 33  |

|     |

4B. Compact advanced transport models for nanoscale surrounding-gate (SRG) MOSFETs......135

| 4B.1 Introduction     | 135 |

|-----------------------|-----|

| 4B.2 Device structure | 137 |

| 4C Conclusions        | 141 |

| 4D References         | 142 |

## Chapter 5

| Conclusions147 | 7 |

|----------------|---|

|----------------|---|

xvii

xviii

# Chapter 1

# State of the Art and Trends for Multiple-gate MOS devices

## **1.1 Introduction**

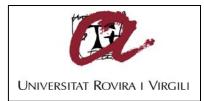

The phenomenal growth of the semiconductor industry is characterised by the remarkable increase of transistor count in integrated circuits (IC), as represented by the well-known Moore's Law [1]. However, this law is a rough prediction of the future of IC expansion. The semiconductor industry has made considerable progress, especially regarding the Metal Oxide Semiconductor Field Effect Transistor (MOSFET). MOSFETs have the remarkable feature that as they become smaller they also become cheaper, consume less power, become faster, and enable more functions per unit area of silicon. As a result, denser silicon integrated circuits can be realized, offering superior performance at reduced cost per function. Figure 1.1 shows the latest update of Moore's law, which sees the introduction of the world's first processor with 2 billion transistors.

#### Microprocessor Transistor Counts 1971-2011 & Moore's Law

Figure 1.1 Plot of transistor count against dates of introduction – following Moore's law.

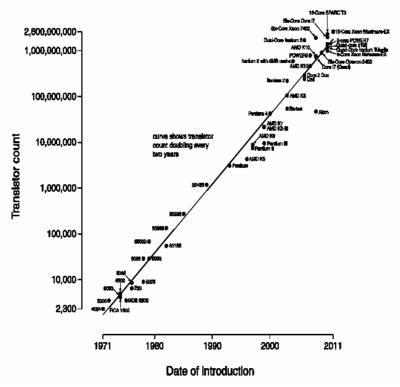

The need of a more accurate estimate defined by the International Technology Roadmap for Semiconductors (ITRS) [2], which has been forecasting and driving the pace of semiconductor technology at the same time. Figure 1.2 shows the evolution of the transistors gate length for the last decades, as well as the ITRS Roadmap predictions made for the next 15 years.

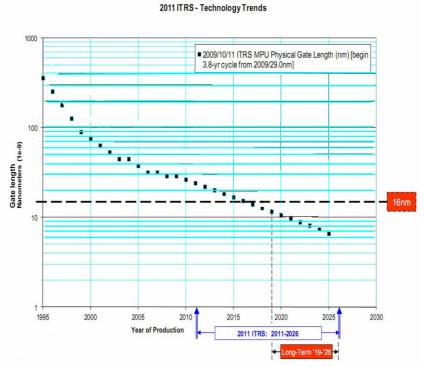

Over the past several decades, the extraordinary evolution of microelectronics has thus been made possible together by continuously shrinking the size of the transistors and also materials used for fabrication that has changed from bulk silicon wafers to Silicon-on-Insulator (SOI) wafers. Within the SOI planar technology, two distinct families of devices are classically considered as shown in Figure 1.3, namely partially-depleted (PD) and fully depleted (FD) MOSFETs. One of the main advantages of this wafer is the drastic reduction of all the parasitic effects from the silicon substrate [3]. In FD MOSFETs, the thickness of the silicon film is reduced in such a way that the depletion region below the inversion channel extends down to the buried oxide. In this case the entire Si film is depleted from free carriers.

When the film is made thicker the depletion region can stop at a certain depth within the silicon film, leaving an un-depleted region above the buried oxide called the body. For this reason such devices are referred to as partially-depleted MOSFETs. The floating potential of the body region in PD MOSFETs is responsible for the floating body effects, which affect the device's electrical behavior. The remarkable feature of the FD MOSFET is that the current drive is higher than in bulk MOSFET and its subthreshold slope is sharper, due to a much smaller body factor [4].

Figure 1.2 Predicted ITRS Roadmap for the next decade.

(B)

Figure 1.3 (A) Partially depleted and (B) Fully depleted SOI MOSFETs.

FD MOSFETs presents nearly an ideal subthreshold slope, lower junction capacitances, enabling the reduction of the threshold voltage and power consumption. For low power analog applications FD technology are much suited [5-6].

In the last decade, we have seen some remarkable technology at work, from just a few devices on a single silicon wafer, to Very-Large-Scale-Integration (VLSI) and in the last few years, this has moved to what is known as Ultra-Large-Scale-Integration (ULSI), in keeping with Moore's Law. The trend in device scaling has almost faithfully followed a universal scaling rule [7] that is derived from the assumption of simple electrostatics and the classical physics of ideal gases for transport. However, with device sizes entering the deep sub-micron (< 0.1 mm gate length) regime, several additional elements of the detailed transport physics have required attention to understand device behavior adequately.

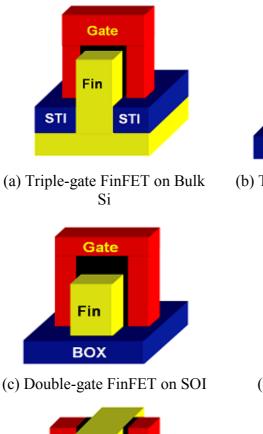

These range from purely classical effects caused by the onset of ballisticity in the transport, such as hot-carrier effects [8], velocity overshoot [9], and impact ionization [10], to purely quantum mechanical effects due to the wave nature of the charge carriers in semiconductors. This constant shrinking, however, has its limits, and we have reached the point where materials and device issues are starting to arise, opening the door for alternative device structures. The most promising SOI devices for the nanoscale range are based on multiple gate structures, such as the double-gate (DG), the triple gate or fin-

shaped field-effect transistor (FinFET), and the surrounding gate (SGT) or gate-all-around (GAA) [11-17. The definition of the various multiple-gate structures can be easily mistaken if not defined properly based on their physical gate dimensions. Figure 1.4 shows some of the multi-gate MOSFETs. The multiple-gate architecture has some interesting characteristics that are presented in the next section.

State of the art and trends for multiple-gate MOS devices

FinFET on SOI

(b) Triple-gate FinFET on SOI

Gate

Fin

вох

(d) Gate-all-around

(e) Independent Double-gate (f) Planar Double-gate on SOI

Figure 1.4 Various structures of multi-gate MOSFETs. (BOX: buried oxide; SOI: silicon-on-insulator).

### **1.2 Advantages of Multi-gate MOSFETs**

One of the most important ones is the gate control over the electrostatic charges. This increased charge control in the channel translates into improved short channel effects [18]. Since the channel (body) is controlled electrostatically by the gate from multiple sides, the channel is better-controlled by the gate than in the conventional transistor structure. Unwanted leakage components are reduced and a small transistor can be used to continue the cost reduction through miniaturization. Improved gate control also provides lower output conductance. This provides greater voltage gain, which is beneficial to analog circuits as well as to the noise tolerance of digital circuits.

Another distinct characteristic of multiple-gate devices is the increased current and therefore faster circuit speed [19]. One of the main advantages of using multiple-gate devices is the highly improved electrical characteristic in the subthreshold regime [20]. The drain induced barrier lowering (DIBL) characteristic of a FD multiple-gate transistor is much improved over a normal SG MOS transistor [4]. The volume inversion is a phenomenon found only in multiple-gate architectures. A device is said to be operating in volume inversion if there is a strong coupling between two conducting channels [21]. In multiple gate devices, the use of a very thin film allows to downscale the devices without the need of using high channel doping densities and

gradients [22-24]. In fact, undoped films can be used: the full depletion of the thin film prevents punch-through from happening. Besides, the absence of dopant atoms in the channel increases the mobility by suppressing impurity scattering [23]. Multiple gate nanoscale devices have many advantages in circuit performance. A very high packaging density is possible because of the small size of these devices, caused by the short channel and the thin film. Because of the higher mobility, transconductance can be higher, which gives more current gain and allows a higher operating frequency. Therefore, multiple gate nanoscale devices have a big potential for RF and microwave applications [25-26]. The analog performance is also very good. Voltage gain is much higher than in conventional bulk MOSFETs, and especially in moderate inversion.

### **1.3 Compact modeling**

Compact Models (CMs) for circuit simulation have been at the heart of CAD tools for circuit design over the past decades, and are playing an ever increasingly important role in the nanometer system-on-chip (SOC) era. Although not highly "visible" to circuit designers and technology developers, a compact model plays the key role in accuracy and efficiency of the circuit simulator being used by designers as well as a bridge to the technology in which the design is to be fabricated. As the mainstream MOS technology is scaled into the nanometer

regime, development of a truly physical and predictive compact model for circuit simulation that covers geometry, bias, temperature, DC, AC, RF, and noise characteristics becomes a major challenge. A physics based device model is understood to be a description of device behavior in terms of analytical, algebraic expressions. This is contrary to device simulations, which are numerical derivations behavior based on complex equations, such as partial differential equations. Furthermore, device models may be characterized as being compact if they are described in terms of analytical, explicit expressions. Compact models can also cover models which involves preprocessing of model expressions by iterative routines that result in parameter lookup-tables for fast retrieval for use in simplified parameterized models. Compact models have the characteristic of being computational efficient in the context of circuit simulations. The demands for advanced models, which can describe nanoscale silicon devices in analog and mixed-signal applications and can account for the physical effects on small geometry devices, have led to enormous research & development (R&D) efforts in the development of advanced physics-based compact models.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 State of the art and trends for multiple-gate MOS devices

### **1.4 Numerical simulations**

Numerical device simulation mostly involves iteration over Poisson's equation in combination with a transport model for a given set of boundary conditions. A common way to solve this problem is to discretise the 2D surface or 3D volume with a grid and iterate over this with a PDE solver. Convergence and accuracy of the solutions depends strongly on the grid distribution and size. In addition, convergence time depends strongly on the solver type, models for carrier statistics, and current continuity. Typically, numerical solvers are not applicable for simulating integrated circuits due to the high computational overhead. In the present work, we have used the device simulator Atlas from Silvaco [27]. Central in this tool is a range of models for physical phenomena behavior such as charge carrier transport models, classical and quantum carrier statistics, material properties, etc. These can be combined in the simulation of specific transistor configurations.

### **1.5 Circuit simulations**

Tools for simulating the behavior of simple circuits began emerging in parallel with the development of integrated circuits. Central elements in circuit simulators are the device models. Different research groups have steadily provided models and modeling approaches to SPICE, adding a wide range of

functionality to the simulator engine. The MOSFET model BSIM by the Berkeley group has been highly successful and was an industry standard for many years. In 2005, for the first time since the seventies, the Compact Model Council, which works for a standardization of compact models and model interfaces, has decided to make the PSP [28] model developed by Philips semiconductors and Pennsylvania State University the industry standard, succeeding the Berkeley groups BSIM3 and BSIM4 [29]. SPICE simulators come with a selection of models for different semiconductors. Choosing the most effective and exact model for the circuit simulation is a difficult task and often leaves the circuit designer with a dilemma, whether to choose a time-consuming precise model or a more simplified and quick model for simulation and parameter extraction. Precise models are often characterized by many parameters that have to be identified empirically by analyzing measurements or TCAD simulations. This may be a quite difficult task considering that some models use several hundred parameters. These parameters cannot always be associated directly with physical mechanisms. However, for a specified technology, this task only has to be performed once by the transistor manufacturer. The numerical tools sometimes come with additional parameter extractors which aid the designer in the process.

State of the art and trends for multiple-gate MOS devices

### **1.6 References**

[1] Gordon E. Moore, "Cramming more components onto integrated circuits", Electronics, vol. 38, no. 8, 1965.

[2] The International Technology Roadmap for Semiconductors, <u>www.itrs.net</u>

[3] Chung Tsung Ming, PhD thesis: "Simulation, Fabrication and Characterization of Advanced MOSFETs: Graded-Channel and Multiple-Gate devices in SOI technology for Analog and RF applications," Université Catholique de Louvain, Belgium, 2007.

[4] J.P. Colinge, C. A. Colinge, "Physics of Semiconductor devices," Springer, 2006.

[5] F. Ichikawa, Y. Nagamoto, Y. Katakura, M. Itoh, S. Itoh, H. Matsuhashi et al, "Fully depleted SOI process and device technology for digital and RF applications", Solid State Electronics, 48, 999-1006 (2004)

[6] G. Baccarani, M.R. Wordeman and R.H. Dennard, "Generalized scaling theory and its application to a <sup>1</sup>/<sub>4</sub> micron MOSFET design", IEEE Trans. Electron Devices, vol. ED-31, pp. 452-462, April 1984.

[7]M. Vanmackelberg, C. Raynaud, O. Faynot, J.-L. Pelloie, C. Tabone, A. Grouilet et al, " $0.25 \mu m$  fully depleted SOI MOSFETs for RF mixed analog-digital circuits, including a comparison with partially depleted devices with relation to high frequency noise parameters", Solid State Electronics, 46, 379-382 (2002)

[8] M. Song, K.P. MacWilliams, and J. C.S. Woo, "Comparison of NMOS and PMOS hot carrier effects from 300 to 77 K", IEEE Trans. Electron Devices, vol.ED-44, no. 2, February 1997.

[9]F. Assederaghi, P.K. Kop and C. Hu, "Observation of velocity overshoot in silicon inversion layers", IEEE Electron. Dev. Letters, vol. 14, Issue 10, pp. 484-486, Oct. 1993.

[10] K. Taniguchi, M. Yamaji, K. Sonoda, T. Kunikiyo, C. Hamaguchi, "Monte Carlo study of impact ionization phenomena in small geometry MOSFETs", IEDM Technical Digest, , pp. 355-358, 11-14, Dec. 1994.

[11] J. P. Colinge, X. Baie, V. Bayot, and E. Grivei, "A siliconon-insulator quantum wire," Solid-State Electron., vol. 39, no. 1, pp. 49–51, 1996.

[12] X. Huang, W. C. Lee, C. Kuo, D. Hisamoto, L. Chang, J. Kedzierski, E. Anderson, H. Takeuchi, Y. K. Choi, K. Asano, V. Subramanian, T. J. King, J. Bokor, and C. Hu, "Sub 50 nm FinFET: PMOS," in IEDM Tech. Dig., 1999, pp. 67–70.

[13]Z. Jiao and C. A. T. Salama, "A fully depleted Π-channel SOI nMOSFET," Proc. Electrochem. Soc. 2001–3, 2001, pp. 403–408.

[14] J. P. Colinge, M. H. Gao, A. Romano-Rodriguez, H. Maes, and C. Claeys, "Silicon-on-insulator gate-all-around device," in IEDM Tech.Dig., 1990, pp. 595–598.

[15] D. Hisamoto, T. Kaga, Y. Kawamoto, and E. Takeda, "A fully depleted lean-channel transist or (DELTA)-a novel vertical

ultra thin SOI MOSFET," in IEDM Tech. Dig., 1989, pp. 833-836.

[16] F.-L. Yang, "25 nm CMOS Omega FETs," in IEDM Dig.,2002, pp. 255–258.

[17] J. T. Park, J. P. Colinge, and C. H. Diaz, "Pi-gate SOI MOSFET," IEEE Electron Device Lett., vol. 22, pp. 405–406, Aug. 2001.

[18] J.P. Colinge, "Multiple-gate SOI MOSFETs", Solid-state electronics, vol. 48, no. 6, pp. 897-905, 2004.

[19] 2003 Spring Meetings Proceedings, editor, "Evolution of SOI MOSFETs: From single-gate to multiple-gates", MRS Proceedings, 765, D1.6 (2003)

[20] J.-P. Colinge, "Silicon-on-insulator technology: Material to VLSI", USA: Springer (2004)

[21] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, T. Elewa, "Double-gate silicon-on-insulator transistor with volume inversion: a new device with greatly enhanced performance", IEEE Electron Device Letters, 8, 410-412 (1987)

[22] Y.K. Choi, K. Asano, N. Lindert, V. Subramarian, T.J. King, J. Bokor, C. Hu, "Ultrathin-body SOI MOSFET for deep subtenth micron era," IEEE Electron device letters, vol. 21 pp. 254-255, 2000

[23] J.H. Choi, Y.J. Park and H.S. Min, "Electron mobility behavior in extremely thin SOI MOSFETs," IEEE Electron device letters, vol. 16, pp. 527-529, 1995

[24] D. Esseni, A. Abramo, L. Selmi, and E. Sangiorgi, "Physcially based modeling of low field electron mobility in ultrathin single- and double-gate n-MOSFETs," IEEE Trans. Electron devices, TED-50, pp. 2445-2454, 2003

[25] D. Lederer, R. Lobet, J.-P. Raskin, "Enhanced high resistivuty SOI wafers for RF applications", Proceedings of IEEE International SOI Conference, 46 (2004)

[26] A. Lázaro, B. Nae, O. Moldovan, and B. Iñiguez, "A compact quantum model of nanoscale double-gate metal-oxide-semiconductor field-effect transistor for high frequency and noise simulations," *Journal of Applied physics*, 100, 084320-12, 2006.

[27] Device simulator ATLAS, Silvaco International; 2007.

[28]Berkeleygroups:<a href="http://www-device.eecs.berkeley.edu/bsim/">http://www-</a>device.eecs.berkeley.edu/bsim/

[29] H. Wang, X. Li, W. Wu, G. Gildenblat, R. Van Langevelde,

G. Smitt, A. Scholten and D. Klaassen, "Unified non-quasistatic mosfet model for large-signal and small-signal simulation," in *Custom Integrated circuits conference*, 2005, *Proceedings of the IEEE 2005*, 2005, pp. 823-826.

Current and charge model for surrounding-gate (SRG) MOSFETs

# Chapter 2

## **Current and Charge model for Surrounding-gate (SRG) MOSFETs**

This chapter is aimed to study the electrostatic potentials and current characteristics of the cylindrical surrounding-gate (SRG) MOSFET.

The chapter is divided into two sections as follows:

In section 2A, an analytical and continuous compact model for a long-channel cylindrical SRG MOSFETs is developed. The analytical expression for the surface potentials are continuous and explicit function of the applied voltages. The expression obtained for the potentials are used to derive an analytical compact model for the drain current which is valid from low to high doping concentrations. The results are compared with 3D ATLAS device simulator.

In section 2B, the compact model is then extended to include the hydrodynamic transport and quantum mechanical effects, and we show that it can reproduce results of 3D numerical simulations using advanced transport models. The final compact model includes mobility degradation, drain-induced barrier lowering, velocity overshoot and quantum effects.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

**MOSFETs**

# 2A. Compact model for long-channel cylindrical surrounding-gate (SRG) MOSFETs valid from low to high doping concentration

### 2A.1. Introduction

The advantages of silicon-on-insulator (SOI) MOSFETs over bulk transistors, such as reduced short channel effects, lower parasitic capacitances and increased circuit speed have made them very attractive for applications in low power and low voltage digital and analog integrated circuits [1]. Among SOI devices, cylindrical surrounding-gate (SRG) MOSFET has become one of the most promising device structures in the technology scaling roadmap [2]. By completely surrounding the channel by the gate, excellent gate control is achieved to reduce short-channel effects. These devices are especially interesting for analog and mixed circuit applications, making the demand of an accurate and CAD compatible compact model for the SRG MOSFETs a really urgent task. To use SRG MOSFETs in circuit design, an analytical model is required [3, 4]. Most of the developed SRG MOSFETs models are only valid for intrinsic channels [5 - 7]. However, doping in SRG MOSFET has been used to adjust the threshold voltage of the device [8]. Besides,

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding as

## Current and charge model for surrounding-gate (SRG) MOSFETs

there is a growing interest in highly doped nanowires working as junctionless transistors [9]. A few models have been presented for the particular case of heavy doping [8]. An compact model valid from low to high doping concentrations is been presented [10], nevertheless it requires iterations to solve for the mobile charge densities. But an explicit compact model for SRG MOSFETs, valid for a broad range of dopings, is needed for the design of circuits using SRG MOSFETs.

In this section, first of all, we present an analytical expression for the electrostatic potentials at the surface and center in the long-channel cylindrical SRG MOSFETs, valid for the practical range of doping concentrations. The expression obtained for the potentials is used to derive an analytical compact model for the drain current of doped long-channel cylindrical SRG MOSFETs. We have considered a long-channel device in order to focus on doping effects and to get rid of short-channel effects. Additionally the quantum effects are not considered for the radial geometry of the device if it is 10nm and above. However, this model can be used as a basis to introduce short-channel effects, like in [11] for double-gate (DG) MOSFETs.

In order to validate our model, calculated potentials and currents are compared with 3D simulations obtained using ATLAS device simulator [12].

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

**MOSFETs**

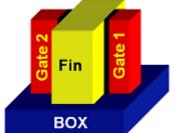

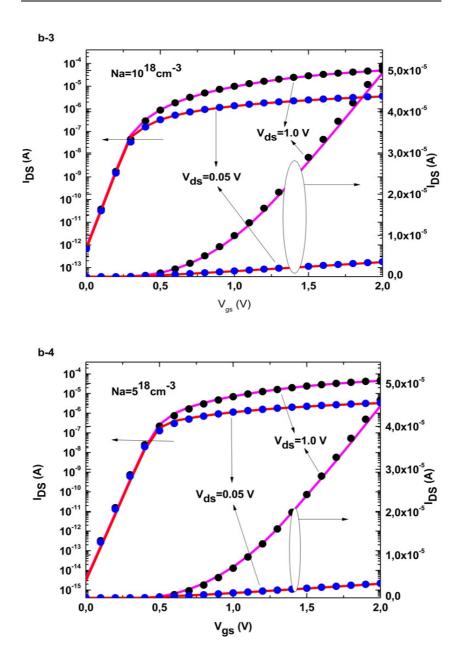

### 2A.2. SRG Model

The schematic cross-section and coordinate system of an Nchannel SRG MOSFET being studied is shown in Figure. 2A.1. *R* is the radius of the cylindrical silicon body and  $V_{gs}$  is applied to the gate voltage [3].

Following the gradual channel approximation (GCA), the electrostatic potential distribution in the silicon channel can be described by Poisson's equation as follows [3]:

$$\frac{1}{r}\frac{d}{dr}\left(r\frac{d\phi}{dr}\right) = \frac{qN_a}{\varepsilon_{si}}\left[e^{\beta}\left(\phi - V_{ch} - 2\phi_F\right) + 1\right]$$

(2A.1)

where  $\phi$  is the electrostatic potential,  $N_a$  is the doping concentration,  $\varepsilon_{si}$  is the permittivity of silicon, q is the electric charge,  $\beta = q/(kT)$  represents the reciprocal of thermal voltage  $\phi_t = \frac{1}{\beta}$ ,  $\phi_F = \beta^{-1} \ln(N_a/n_i)$  is the Fermi potential, and  $V_{ch}$  is

the quasi-Fermi potential along the channel.

Current and charge model for surrounding-gate (SRG) MOSFETs

Figure 2A.1 Schematic cross-section of an N-channel SRG MOSFET showing the coordinate system and related variables.

The boundary conditions of (2A.1) are:

$$C_{ox}(V_{gs} - V_{fb} - \phi_s) = Q_{in} + Q_{dep} = -\varepsilon_{si}E_s$$

(2A.2a)

$$\frac{d\phi}{dr} = 0 \text{ as } r = 0 \tag{2A.2b}$$

where  $C_{ox} = \varepsilon_{ox} / (R \ln(1 + t_{ox} / R))$  is the oxide capacitance per unit gate area in a SRG MOSFET [5],  $t_{ox}$  is the oxide thickness,  $\varepsilon_{ox}$  is the permittivity of oxide,  $V_{fb}$  is the flat band voltage,  $Q_{in}$  is the inversion charge density per unit gate area,

Current and charge model for surrounding-gate (SRG) MOSFETs

$Q_{dep} = qN_aR/2$  is the fixed charge density per unit gate area, and  $E_s$  is the electric field at the silicon-oxide interface.

For the doped case, the full-depletion approximation can be obtained by neglecting the exponential term on the right hand side (RHS) of (2A.1) [3, 4]:

$$\phi(R) = \phi_o + \frac{qN_aR^2}{4\varepsilon_{si}}$$

(2A.3)

Following [3] an expression for the surface electric field  $E_s$  is obtained:

$$E_{s} = -\sqrt{\left[\frac{Q_{dep}}{\varepsilon_{si}} - \frac{2}{\beta R}\left[1 - e^{\beta(\phi_{o} - \phi_{s})}\right]\right]} \frac{4}{\beta R} e^{\beta(\phi_{s} - V_{ch} - 2\phi_{F})} + \left(\frac{Q_{dep}}{\varepsilon_{si}}\right)^{2}$$

(2A.4)

From (2A.4), we get  $E_s$  as a function of the potential at the surface  $\phi_s$ , and at the center of the layer  $\phi_a$ :

$$E_{s} = -\sqrt{\frac{2qN_{a}\phi_{t}}{\varepsilon_{si}}}\sqrt{\frac{\phi_{s}-\phi_{o}}{2\phi_{t}} + \left[1 - \frac{\phi_{t}}{\phi_{s}-\phi_{o}} + \frac{\phi_{t}}{\phi_{s}-\phi_{o}}e^{-(\frac{\phi_{s}-\phi_{o}}{\phi_{t}})}\right]}e^{\left(\frac{\phi_{s}-V_{ch}-2\phi_{F}}{\phi_{t}}\right)}$$

(2A.5)

We can rewrite (2A.5) as:

$$E_{s} = -\sqrt{\frac{4Q_{dep}\phi_{t}}{R\varepsilon_{si}}}\sqrt{\alpha}\sqrt{\frac{1}{2} + \left[\frac{1 - \frac{1}{\alpha} + \frac{1}{\alpha}e^{-\alpha}}{\alpha}\right]}e^{\left(\frac{\phi_{s} - V_{ch} - 2\phi_{F}}{\phi_{t}}\right)}$$

(2A.6)

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding a

## Current and charge model for surrounding-gate (SRG) MOSFETs

where  $\alpha = (\phi_s - \phi_o)/\phi_t$  is the normalized difference of potentials [13].

Substituting (2A.6), in the expression  $V_{gs} - V_{fb} = \phi_s - \varepsilon_{si} E_s / C_{ox}$  (coming from (2A.2a)), the surface

potential  $\phi_s$  is implicitly defined as:

$$V_{gs} = V_{fb} + \phi_s + \frac{1}{C_{ox}} \sqrt{\frac{4Q_{dep}\varepsilon_{si}\phi_t}{R}} \sqrt{\alpha} \sqrt{\frac{1}{2} + \left[\frac{1 - \frac{1}{\alpha} + \frac{1}{\alpha}e^{-\alpha}}{\alpha}\right]} e^{\left(\frac{\phi_s - V_{ch} - 2\phi_F}{\phi_t}\right)}$$

(2A.7)

### 2A.3 Calculation of the potentials

#### 2A.3.1 Subthreshold regime

In the subthreshold regime, the difference between the surface potential and the potential at the center of the Si layer is calculated using the full-depletion approximation which is valid in this regime [3], (2A.3) as:

$$\phi_{dBT} = \phi_{sBT} - \phi_{oBT} = \frac{qN_a R^2}{4\varepsilon_{si}} = \frac{Q_{dep}R}{2\varepsilon_{si}}$$

(2A.8)

where  $\phi_{sBT}$  and  $\phi_{oBT}$  are the values of the surface potential and potential at the center of the Si layer corresponding to the

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding or

Current and charge model for surrounding-gate (SRG) MOSFETs

subthreshold condition. As can be seen,  $\phi_{dBT}$  depends only on the doping concentration  $N_a$  and on the silicon body radius R.

$$\phi_{_{SBT}}$$

is calculated by solving the (2A.7). For the

subthreshold regime, the term

$$\left[\frac{1-\frac{1}{\alpha_{BT}}+\frac{1}{\alpha_{BT}}e^{-\alpha_{BT}}}{\alpha_{BT}}\right] < 1 \text{ and}$$

(2A.7) can be simplified expanding the square root.

After some rearrangements we can obtain:

$$V_{gs} - V_{fb} = \phi_{sBT} + \frac{Q_{dep}}{C_{ox}} \left( 1 + e^{\left(\frac{\phi_{sBT} - V_{ch} - 2\phi_F}{\phi_t}\right)} \right)$$

(2A.9)

Using the principal branch of the Lambert function LW.  $\phi_{sBT}$  is calculated from (2A.9) as:

$$\phi_{sBT} = V_{gs} - V_{fb} - \frac{Q_{dep}}{C_{ox}} - \phi_t LW \left[ \frac{Q_{dep}}{C_{ox}\phi_t} e^{\left(\frac{V_{gs} - V_{fb} - \frac{Q_{dep}}{C_{ox}} - V_{ch} - 2\phi_F}{\phi_t}\right)}\right]$$

(2.4.10)

(2A.10)

## Current and charge model for surrounding-gate (SRG) MOSFETs

$\phi_{oBT}$  is calculated substituting (2A.10) in (2A.8) as:

$$\phi_{oBT} = \phi_{sBT} - \phi_{dBT} \tag{2A.11}$$

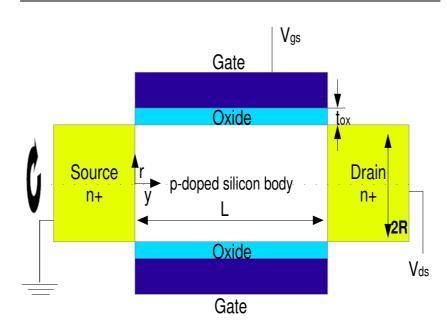

Figure 2A.2 shows the behavior of  $\phi_{sBT}$  (subthreshold) as a function of the doping concentration in the Si layer. Comparison is made between the results obtained by solving (2A.10) and numerical 3D ATLAS simulation. As can be seen, our analytical expression provides a good agreement in all the doping concentrations from  $10^{16}$  to 5 x  $10^{18}$  cm<sup>-3</sup> for  $t_{ox} = 3$  nm and R =5 nm. A gate with a mid-gap work function was considered. The source and drain doping concentration of 10<sup>20</sup> cm<sup>-3</sup> was considered. From the plot, it can be seen that the potential increases doping concentration as increases. When  $N_a = 10^{18}$  cm<sup>-3</sup> the potential has a maximum value, and for further increase of the doping concentration in the Si layer the potential decreases, which is clearly seen from the plot.

From (2A.10) for the surface potential in the deep subthreshold regime (where the Lambert function term is negligible), we observe that the flatband voltage term dominates at low channel dopings over the other terms, leading to an increase of the surface potential with increasing doping. At high channel dopings the term  $Q_{dep}/C_{ox}$  term dominates over the other terms in the expression and hence the surface potential starts to decrease after reaching a peak value as the doping concentration is increased.

# Current and charge model for surrounding-gate (SRG) MOSFETs

Figure 2A.2 Modeled (circles) and Simulated (triangles) potential at the surface of the Si layer as a function of  $N_a$  in the subthreshold regime for  $t_{ox} = 3$  nm and R = 5 nm.

## Current and charge model for surrounding-gate (SRG) MOSFETs

### 2A.3.2 Threshold condition

From numerical calculation using 3D ATLAS simulation, the expression of the difference of potentials at the threshold voltage is found as:

$$\phi_{dT} = \phi_{dBT} + \Delta \phi_{dT} = \frac{Q_{dep}R}{2\varepsilon_{si}} + \frac{5}{8}\phi_t$$

(2A.12)

Extending the threshold voltage expression given in [13] for double-gate (DG) MOSFETs to SRG MOSFETs, the surface potential at threshold condition is given by:

$$\phi_{sT} = 2\phi_F + \phi_t \ln\left[\frac{C_{ox}}{4C_{si}}\left(1 + \frac{\phi_t C_{ox}}{Q_{dep}}\right)\right]$$

(2A.13)

where  $C_{ox}$  is the oxide capacitance of the cylindrical SRG MOSFET, and  $C_{si} = \frac{\varepsilon_{si}}{2R}$  is the silicon capacitance per unit gate area.

while

$$\phi_{oT} = \phi_{sT} - \phi_{dT} \tag{2A.14}$$

The potential at the center of the layer  $\phi_{oT}$ , as a function of the layer concentration  $N_a$  has a maximum value for a doping 27

**MOSFETs**

concentration of  $N_{a \max}$ . The expression of  $N_{a \max}$  is obtained by differentiating (2A.14) with respect to doping and making this derivative equal to zero.

The threshold voltage is calculated substituting (2A.13) in (2A.7):

$$V_{T} = V_{fb} + 2\phi_{F} + \phi_{t} \ln\left[\frac{C_{ox}}{4C_{si}}\left(1 + \frac{\phi_{t}C_{ox}}{Q_{dep}}\right)\right] + \frac{1}{C_{ox}}\sqrt{\frac{4Q_{dep}\varepsilon_{si}\phi_{t}}{R}}\sqrt{\alpha_{T}}\sqrt{\frac{1}{2} + \left[\frac{1 - \frac{1}{\alpha_{T}} + \frac{1}{\alpha_{T}}e^{-\alpha_{T}}}{\alpha_{T}}\right]\left[\frac{C_{ox}}{4C_{si}}\left(1 + \frac{\phi_{t}C_{ox}}{Q_{dep}}\right)\right]}$$

$$(2A.15)$$

where  $\alpha_T$  is the normalized difference between the surface and the center potential at threshold.

# Current and charge model for surrounding-gate (SRG) MOSFETs

### 2A.3.3 Modeling of potentials in all regimes

Using the numerical calculation obtained from (2A.8) and (2A.12) we found that the difference between the surface and center potential can be expressed by empirical analytical expressions in the different conditions, in a similar way as for DG MOSFETs [13].

(a) Subthreshold

$$\phi_{d1} = \phi_{dBT} + \frac{19}{16} \phi_t \left[ \frac{e^{\frac{V_{gs} - V_T - V_{ch}}{\phi_t}}}{\frac{V_{gs} - V_T - V_{ch}}{\phi_t}}}{1 + e^{\frac{V_{gs} - V_T - V_{ch}}{\phi_t}}} \right]$$

(2A.16)

(b) Above threshold for  $N_a < N_{a \max}$

$$\phi_{d2a} = \left(\frac{\phi_{dBT}}{3} + \phi_{dM} - 0.028V\right) - \left(\frac{\phi_{dBT}}{3} + \phi_{dM} - 0.028V - \phi_{dT}\right) \left(\frac{1 - \frac{V_{gs} - V_T - V_{ch}}{V_{GM} - V_T - V_{ch}}}{1 + 1.35(V_{gs} - V_T - V_{ch})}\right)$$

(2A.17)

(c) Above threshold for  $N_a > N_{a \max}$

$$\phi_{d2b} = \left(\frac{\phi_{dBT}}{2} + \phi_{dM} - 0.028V\right) - \left(\frac{\phi_{dBT}}{2} + \phi_{dM} - 0.028V - \phi_{dT}\right) \left(\frac{1 - \frac{V_{gs} - V_T - V_{ch}}{V_{GM} - V_T - V_{ch}}}{1 + 1.35(V_{gs} - V_T - V_{ch})}\right)$$

(2A.18)

MOSFETs

where  $V_{GM}$  is the maximum applicable gate voltage for the device (in our case  $V_{GM} = 2$  V).

The complete expression for the difference of potentials  $\phi_d$  valid from subthreshold to above threshold can be expressed using an interpolation function as in [13] for DG MOSFETs:

$$\phi_{d} = \phi_{d1} \frac{1}{2} \{ 1 - \tanh[50(V_{gs} - V_{T} - V_{ch})] \} + \phi_{d2} \frac{1}{2} \{ 1 + \tanh[50(V_{gs} - V_{T} - V_{ch})] \}$$

(2A.19)

where

$$\phi_{d2} = \phi_{d2a} \frac{1}{2} \{ 1 - \tanh[10(\log(N_a) - \log(N_{a\max}) - 0.5)] \} + \phi_{d2b} \frac{1}{2} \{ 1 + \tanh[10(\log(N_a) - \log(N_{a\max}) - 0.5)] \}$$

(2A.20)

As in [11] an empirical expression was found to describe the behavior of  $\phi_{dM}$  up to  $V_{GM} = 2$  V as a function of gate dielectric and silicon layer thickness.

$$\phi_{dM} = 0.162 - 0.047t_{ox} + 0.0045t_{ox}^2 + 0.00836R - 12 \times 10^{-5} (R)^2$$

(2A.21)

where  $t_{ox}$  and R are written in nm.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

**MOSFETs**

The two empirical parameters have been adjusted to the best possible fit with the TCAD simulations regarding the difference between the surface and center potentials.

Figures 2A.3 (a, b and c), show a good agreement between the potential difference calculated by the model in expression (2A.19) and the 3D ATLAS simulations measured at the center of the channel (Figure 2A.3a) for  $V_{ds}$ = 0, and for  $V_{ds}$ > 0 at a position near the drain end (Figures 2A.3b and 2A.3c) for different doping concentrations and channel voltages.

0.02

Figure 2A.3a, b and c. Modeled (solid lines) and numerically simulated (symbols) potential difference  $\phi_s - \phi_o$  as a function of gate voltage for different Si layer concentration and V<sub>ds</sub>= 0, 0.5 and 1 V,  $t_{ox}$ =3nm and R=5nm.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

MOSFETs

The surface potential above threshold can be calculated from (2A.7) after substituting (2A.19) in  $\alpha$ . The simplified expression for the surface potential above threshold is:

$$\phi_{sAT} = V_{gs} - V_{fb} - 2\phi_t LW \left[ \frac{1}{2C_{ox}\phi_t} \sqrt{\frac{4Q_{dep}\varepsilon_{si}\phi_t}{R}} \sqrt{1 - \frac{1}{\alpha} + \frac{1}{\alpha}e^{-\alpha}} e^{\left(\frac{V_{gs} - V_{fb} - V_{cb} - 2\phi_f}{2\phi_t}\right)} \right]$$

(2A.22)

A complete expression for the surface potential valid from subthreshold to above threshold is obtained using an interpolation function as in [13] for DG MOSFETs:

$$\phi_{s} = \phi_{sBT} \frac{1}{2} \{ 1 - \tanh[10(V_{gs} - V_{T} - V_{ch})] \} + \phi_{sAT} \frac{1}{2} \{ 1 + \tanh[10(V_{gs} - V_{T} - V_{ch})] \}$$

(2A.23)

The potential at the center of the Si layer is calculated as:

$$\phi_o = \phi_s - \phi_d \tag{2A.24}$$

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

MOSFETs

Figure 2A.4 shows a good agreement between the overall surface potential calculated by the model and the one calculated by 3D ATLAS simulations in the subthreshold and near threshold regimes for the different doping concentrations considered. At higher gate voltages, the model potential is slightly higher than the simulation for all the doping concentration considered, but the agreement is acceptable, and as it will be shown, does not cause lack of accuracy in the modeled I-V characteristics.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-ga

# Current and charge model for surrounding-gate (SRG) MOSFETs

Figure 2A.4 Modeled (solid lines) and numerically simulated (symbols) surface potential as a function of gate voltage for different Si layer concentrations.

Current and charge model for surrounding-gate (SRG) MOSFETs

### 2A.4 Modeling charge carrier and current

#### 2A.4.1 Charge carrier model

The charge carrier concentration at a certain position in the channel is determined by the following relation as governed by the Gauss's law at the silicon-oxide interface [10]:

$$-E_{s} = \frac{Q_{sem}}{\varepsilon_{si}} = \frac{C_{ox}\phi_{l}}{\varepsilon_{si}} \left(q_{in} + q_{dep}\right)$$

(2A.25)

where  $Q_{\rm sem}$  is the semiconductor charge per unit gate area ,

$q_{in} = \frac{Q_{in}}{C_{ox}\phi_t}$  is the normalized inversion charges per unit gate

area, and  $q_{dep} = \frac{Q_{dep}}{C_{ox}\phi_t}$  is the normalized fixed charge density per

unit gate area.

Substituting the expression of the electric field from (2A.6) in (2A.25), the normalized charge carrier concentration becomes equal to,

$$q_{in} = \sqrt{\frac{4q_{dep}\varepsilon_{si}}{C_{ox}R}} \sqrt{\alpha} \sqrt{\frac{1}{2} + \left[\frac{1 - \frac{1}{\alpha} + \frac{1}{\alpha}e^{-\alpha}}{\alpha}\right]} e^{\frac{\phi_s - V_{ch} - 2\phi_F}{\phi_i}} - q_{dep}$$

(2A.26)

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

MOSFETs

### 2A.4.2 Current model

Considering a drift-diffusion transport, the transistor current is calculated as [11]:

$$I_{DS} = \frac{W}{L} \mu C_{ox} \phi_t \int_{V_s}^{V_D} q_{in}(V) dV$$

(2A.27)

where W is the channel width ( which for SRG MOSFETs is  $W = 2\pi R$  ), L is the channel length (in our case  $L = 1\mu m$  ),  $V_s$  and  $V_D$  are the channel potential at the source and drain respectively, and  $\mu$  is the electron mobility.

Using (2A.26), the gate voltage  $V_{gs}$  in (2A.7) can be rewritten as

$$V_{gs} = V_{fb} + \phi_s + \phi_t (q_{in} + q_{dep})$$

(2A.28)

Substituting  $\phi_s$  from (2A.23) in (2A.26) and solving for  $V_{gs}$  the following general solution is obtained after neglecting few terms as:

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding a

Current and charge model for surrounding-gate (SRG) MOSFETs

$$V_{gs} - V_{fb} - \phi_t q_{dep} - V_{ch} - 2\phi_F + \phi_t \ln\left[\frac{1 - \frac{1}{\alpha} + \frac{1}{\alpha}e^{-\alpha}}{\alpha}\right]$$

$$= \phi_t q_{in} + \phi_t \ln\left[\left(\frac{2\alpha_{BT}}{\alpha}\right)\left(\frac{q_{in}}{q_{dep}}\left(\frac{q_{in}}{q_{dep}} + 2\right)\right)\right]$$

(2A.29)

The derivative of (2A.29) with respect to  $V_{ch}$  gives

$$-1 + \frac{d}{dV} \left[ \phi_t \ln \left[ \frac{1 - \frac{1}{\alpha} + \frac{1}{\alpha} e^{-\alpha}}{\alpha} \right] \right] = \phi_t \left[ 1 + \frac{1}{q_{in}} + \frac{1}{q_{in} + 2q_{dep}} \right] \frac{dq_{in}}{dV} + \phi_t \frac{d}{dV} \ln \left( \frac{2\alpha_{BT}}{\alpha} \right)$$

$$(2A.30)$$

Neglecting the logarithm terms on both sides, the following expression is obtained:

$$-1 = \phi_t \left[ 1 + \frac{1}{q_{in}} + \frac{1}{q_{in} + 2q_{dep}} \right] \frac{dq_{in}}{dV}$$

(2A.31)

Substituting (2A.31) in (2A.27) and integrating  $q_{in}$  from its value at the source,  $q_s$ , to its value at drain,  $q_d$ , the current is expressed as:

#### Current and charge model for surrounding-gate (SRG) MOSFETs

$$I_{DS} = I_o \left[ 2(q_s - q_d) + \frac{q_s^2 - q_d^2}{2} + 2q_{dep} \ln \left[ \frac{q_d + 2q_{dep}}{q_s + 2q_{dep}} \right] \right],$$

(2A.32)

where

$$I_o = \frac{W}{L} \mu C_{ox} \phi_t^2$$

.

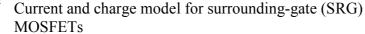

Figure 2A.5 (a1-a4) show a good agreement between output characteristics by the model and the 3D ATLAS simulations by considering constant mobility (1000 cm<sup>2</sup>/Vsec) for doping concentrations from  $10^{16}$  cm<sup>-3</sup> to 5 x  $10^{18}$  cm<sup>-3</sup> at different gate voltages. In Figure 2A.5 (b1-b4) the transfer characteristics calculated between the model and the 3D ATLAS simulation show a good agreement for the doping concentrations from  $10^{16}$  cm<sup>-3</sup> to 5 x  $10^{18}$  cm<sup>-3</sup>.

Figure 2A.5 Output (a1-a2) characteristics. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot.

UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

**MOSFETs**

Figure 2A.5 Output (a3-a4) characteristics. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot.

Figure 2A.5 Transfer (b1-b2) characteristics in logarithmic and linear scale. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot.

Figure 2A.5 Transfer (b3-b4) characteristics in logarithmic and linear scale. Solid lines: compact model. Symbols: 3D numerical simulations with ATLAS. The doping concentration as indicated in the plot.

**MOSFETs**

# 2B. Compact drain current model reproducing advanced transport models in nanoscale cylindrical surroundinggate (SRG) MOSFETs

#### **2B.1 Introduction**

The surrounding-gate (SGT) MOSFET is one of the most promising candidates for the downscale of CMOS technology toward the nanometer-channel-length range since the SGT architecture allows excellent control of the channel charge in the silicon film, reducing short-channel effects (SCE) [14-17]. These devices include important features that permit more aggressive channel length scaling than to their conventional bulk counterparts. In this context, it is important to highlight the efforts currently under way in relation to multigate MOSFETs compact modeling [18-20]. The continuous scaling in the IC industry makes the reduction in the active silicon area in multigate MOSFETs essential in order to keep the short channel

### Current and charge model for surrounding-gate (SRG) MOSFETs

effects (SCE) under control [4]. Therefore, the influence of structural confinement is increasing, which makes the charge distribution in these devices completely different to that found in conventional bulk. Hence, there is a great need for new compact models that accurately describe the physics of these devices [21]. Our starting point, in this section is an analytical expression that models the variation of surface potential as well as the difference of potential at the surface and at the middle of the silicon layer [22]. The expression obtained for the potentials is used to derive an analytical compact model for the drain current of a cylindrical surrounding-gate MOSFETs. This model was derived for doped devices, but it has been demonstrated to be valid in lightly doped devices. We extend the model to include hydrodynamic transport and quantum mechanical effects. As the channel length is reduced 3D effects appear near the source and drain producing the so-called SCE such as drain-induced barrier lowering (DIBL). The DIBL effect is considered through a threshold voltage correction in the compact model. Using the concept of inversion layer centroid, we have introduced a

correction in the oxide capacitance to improve the accuracy in the strong inversion region [21]. Velocity overshoot is modeled through the hydrodynamic transport [23] which is also included in the model. The model takes into account the mobility degradation [24] due to scattering effects. The final compact model for the drain current includes hydrodynamic transport, mobility degradation, short channel effects such as DIBL and quantum effects. Comparisons between the compact model and 3D advanced numerical transport models are shown. UNIVERSITAT ROVIRA I VIRGILI COMPACT MODELING FOR MULTI-GATE MOSFETS USING ADVANCED TRANSPORT MODELS Muthupandian Cheralathan Dipòsit Legal: T. 1294-2012 Current and charge model for surrounding-gate (SRG)

MOSFETs

#### 2B.2 DC model

#### 2B.2.1 Expression for potentials

The potentials at the surface,  $\phi_s$ , and in the center,  $\phi_o$ , of the silicon layer are calculated analytically. The surface potential in the subthreshold  $\phi_{sBT}$  regime are calculated analytically using the Lambert function as [22]:

$$\boldsymbol{\phi}_{SBT} = V_{GS} - V_{fb} - \frac{Q_{dep}}{C_{ox}^*} - \boldsymbol{\phi}_t LW \left[ \frac{Q_{dep}}{C_{ox}^* \boldsymbol{\phi}_t} e^{\left( \frac{V_{GS} - V_{fb} - \frac{Q_{dep}}{C_{ox}^*} - V_{ch} - 2\boldsymbol{\phi}_F}{\boldsymbol{\phi}_t} \right)} \right]$$

(2B.1)

and in the above threshold regime as:

$$\boldsymbol{\phi}_{sAT} = V_{GS} - V_{fb} - 2\boldsymbol{\phi}_t LW \left[ \frac{1}{2C_{ox}^* \boldsymbol{\phi}_t} \sqrt{\frac{4Q_{dep}\boldsymbol{\varepsilon}_{si}\boldsymbol{\phi}_t}{R}} \sqrt{1 - \frac{1}{\boldsymbol{\alpha}} + \frac{1}{\boldsymbol{\alpha}} e^{-\boldsymbol{\alpha}}} e^{\left(\frac{V_{GS} - V_{fb} - V_{ch} - 2\boldsymbol{\phi}_F}{2\boldsymbol{\phi}_t}\right)} \right]$$

(2B.2)

where  $V_{GS}$  is applied to the gate voltage,  $V_{fb}$  is the flat band voltage,  $Q_{dep} = qN_aR/2$  is the fixed charge density per unit gate area,  $N_a$  is the doping concentration, R is the radius of the cylindrical silicon body,  $\phi_t = \frac{kT}{q}$  is the thermal voltage,  $V_{ch}$  is quasi-Fermi the potential along the channel,  $\phi_F = \phi_t \ln(N_a / n_i)$  is the Fermi potential,  $\alpha = (\phi_s - \phi_o) / \phi_t$  is the normalized difference of potentials,  $\mathcal{E}_{si}$  is the permittivity of silicon, q is the electric charge. The inversion centroid is a function of the inversion charge. A simple relationship between inversion centroid and inversion charge obtained by fitting simulation numerical results is given by

$$\frac{1}{z_{I}} = \frac{1}{a + 2bR} + \frac{1}{z_{IO}} \left(\frac{N_{I}}{N_{IO}(R)}\right)^{n}$$

[21] with

a = 0.55 nm, b = 0.198,  $z_{IO} = 5.1$  nm, n = 0.75, and  $N_{IO}(R) = 8.26 \times 10^{12} \text{ cm}^{-2} \cdot 4.9 \times 10^{18} \text{ cm}^{-3} \times R(cm)$ . The classical oxide capacitance  $C_{ox}$  was replaced in our model by another capacitance, corrected oxide capacitance  $(C_{ox}^*)$ , where the

capacitance of the oxide was in series with a centroid capacitance, which is the capacitance of a silicon layer as [21]:

$$\frac{1}{C_{ox}^{*}} = \frac{1}{C_{ox}} + \frac{1}{C_{cen}}$$

(2B.3)

where  $C_{cen} = \frac{\varepsilon_{si}}{(R - z_I) \ln \left(1 + \frac{z_I}{(R - z_I)}\right)}$  and

$C_{ox} = \frac{\varepsilon_{ox}}{R \ln \left(1 + \frac{t_{ox}}{R}\right)}$  is the oxide capacitance per unit gate area in