**ADVERTIMENT**. La consulta d'aquesta tesi queda condicionada a l'acceptació de les següents condicions d'ús: La difusió d'aquesta tesi per mitjà del servei TDX (<u>www.tesisenxarxa.net</u>) ha estat autoritzada pels titulars dels drets de propietat intel·lectual únicament per a usos privats emmarcats en activitats d'investigació i docència. No s'autoritza la seva reproducció amb finalitats de lucre ni la seva difusió i posada a disposició des d'un lloc aliè al servei TDX. No s'autoritza la presentació del seu contingut en una finestra o marc aliè a TDX (framing). Aquesta reserva de drets afecta tant al resum de presentació de la tesi com als seus continguts. En la utilització o cita de parts de la tesi és obligat indicar el nom de la persona autora.

**ADVERTENCIA**. La consulta de esta tesis queda condicionada a la aceptación de las siguientes condiciones de uso: La difusión de esta tesis por medio del servicio TDR (<u>www.tesisenred.net</u>) ha sido autorizada por los titulares de los derechos de propiedad intelectual únicamente para usos privados enmarcados en actividades de investigación y docencia. No se autoriza su reproducción con finalidades de lucro ni su difusión y puesta a disposición desde un sitio ajeno al servicio TDR. No se autoriza la presentación de su contenido en una ventana o marco ajeno a TDR (framing). Esta reserva de derechos afecta tanto al resumen de presentación de la tesis como a sus contenidos. En la utilización o cita de partes de la tesis es obligado indicar el nombre de la persona autora.

**WARNING**. On having consulted this thesis you're accepting the following use conditions: Spreading this thesis by the TDX (<u>www.tesisenxarxa.net</u>) service has been authorized by the titular of the intellectual property rights only for private uses placed in investigation and teaching activities. Reproduction with lucrative aims is not authorized neither its spreading and availability from a site foreign to the TDX service. Introducing its content in a window or frame foreign to the TDX service is not authorized (framing). This rights affect to the presentation summary of the thesis as well as to its contents. In the using or citation of parts of the thesis it's obliged to indicate the name of the author

## Design-oriented model for predicting and controlling fast-scale instabilities in switching converters. Application to advanced power management integrated circuits

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy in Electrical Engineering by:

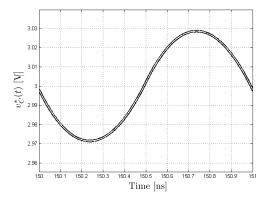

Enric Rodriguez Vilamitjana

PhD Thesis Advisors:

Dr. Eduard Alarcon (UPC-BarcelonaTech) Dr. Abdelali El Aroudi (Universitat Rovira Virgili)

In the graduate division of the UPC-BarcelonaTech University, Barcelona, Spain Winter 2010

Cridem quin som i que tothom ho escolti. I, en acabat, que cadascú es vesteixi com bonament li plagui, i via fora, **que tot està per fer i tot és possible.** *Ara mateix*, Miquel Martí i Pol,

Quan surts per fer el viatge cap a Itaca, has de pregar que **el camí sigui llarg, ple d'aventures, ple de coneixences**. Has de prega que el camí sigui llarg, que siguin moltes les matinades que entraràs en un port que els teus ulls ignoraven, i vagis a ciutats **per aprendre del que saben**. Has d'arribar-hi, és el teu destí, peró no forcis gens la travessia. *Camí d'Itaca*

...a la meva família i a tots els amics, que m'han acompanyat en aquest viatge...

### Acknowledgement, Agraïments

It is a pleasure to thank those who made this thesis possible.

First, I would like to thank my thesis supervisors, not only because of the huge amount of time and energy invested in it, but because all I have learnt during this thesis and the fact that they have given me the opportunity to enjoy the research carried out. I consider that it has been an honor to be able to share these 4 years with them, whom I consider to be exceptional not only as researchers, but also as persons.

I would also like to show my gratitude to the research group members, who have made available their support in a number of ways and have always shown the willingness to share and discuss scientific ideas that facilitated this thesis contributions.

Furthermore, I would like to thank my PhD colleagues at the Electronic Engineering department at UPC BarcelonaTech who supported me during this thesis, sharing experiences and interests and making easier the working days.

This work has been supported by an FPU PhD fellowship granted by the Ministry of Science and Innovation of Spain (MICINN). Partial funding from the project TEC2007-67988-C02-01 from the Spanish MICINN and EU FEDER funds is acknowledged.

Finally, this thesis would not have been possible unless the full support of my family and friends.

Voldria agraïr especialment als meus pares, la meva avia i al Miquel, els quals sense els seu recolzament aquest tesi no hauria estat possible. Per estar sempre disposats a escoltar, per recolzar-me en les meves decisions i per fer més fàcils els moments difícils.

I finalment, donar les gràcies a tots els amics que han fet aquest viatge una mica més agradable:

Als bons amics Marc F., Pablo, Edu, Xavi, Nuria P., Albert, i José per tots els bons moments compartits, i els molts que ens queden. A unes persones molt especials: Mar, Laia, Mariona i Marta M., amb les que sempre he gaudit de la seva companyia. A la gent que està lluny, peró que la sento propera, Lorena, Hans i Annie, amb els que sempre ha estat un plaer retrobar. Als companys de pis, Maria i Albert, per fer el dia a dia un mica més agradable. A la gent de D-Recerca, Eurodoc i FJI per compartir les ganes de canviar una mica el mon, especialment a la Elena P., Noe i Alfredo. A la Laura, per tots els bon moments que hem viscuts. A la Clara, per estar al meu costat i donar-me l'energia per acabar aquesta tesi.

## Contents

| 1        | Intr           | roduction                                                                                                                                                                                       | 1                    |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|          | 1.1            | Key enabling technologies for power management subsystems                                                                                                                                       | 2                    |

|          | 1.2            | Modern power management approaches                                                                                                                                                              | 4                    |

|          |                | 1.2.1 Non-conventional switching power converter topologies                                                                                                                                     | 5                    |

|          |                | 1.2.2 Non-conventional control $\ldots$                                                                                                                                                         | 6                    |

|          |                | 1.2.3 Functionality: from regulation to tracking                                                                                                                                                | 8                    |

|          |                | 1.2.4 $$ Modern power management architectures case examples $$ .                                                                                                                               | 8                    |

|          | 1.3            | Dynamics and stability models of switching power converters $\ .$ .                                                                                                                             | 9                    |

|          |                | 1.3.1 Overview of nonlinear dynamical systems                                                                                                                                                   | 9                    |

|          |                |                                                                                                                                                                                                 | 11                   |

|          |                | 1.3.3 The discrete-time models                                                                                                                                                                  | 13                   |

|          |                | 1.3.4 Design-oriented circuit-based models: The average model                                                                                                                                   | 17                   |

|          | 1.4            | Chaos control methods                                                                                                                                                                           | 19                   |

|          |                | 1.4.1 Via external force                                                                                                                                                                        | 20                   |

|          |                | 1.4.2 Via feedback techniques                                                                                                                                                                   | 20                   |

| <b>2</b> | Cor            | mplex behavior of VMC buck converter: characterization                                                                                                                                          | 22                   |

|          | 2.1            | -                                                                                                                                                                                               | 22                   |

|          | 2.2            | Power-oriented electrical metrics characterization of VMC buck                                                                                                                                  |                      |

|          |                | converter dynamics                                                                                                                                                                              | 31                   |

| 3        | $\mathbf{Des}$ | sign-oriented models for predicting instabilities in a buck                                                                                                                                     |                      |

|          |                |                                                                                                                                                                                                 | 38                   |

|          | 3.1            |                                                                                                                                                                                                 | 39                   |

|          | 3.2            | 0 0                                                                                                                                                                                             | 43                   |

|          |                | 3.2.1 Validation of the ripple-based approach by means of the                                                                                                                                   |                      |

|          |                | switched model                                                                                                                                                                                  | 44                   |

|          |                | 3.2.2 Experimental validation                                                                                                                                                                   | 45                   |

|          | 3.3            | Discrete-time model stability analysis. Relationship with the                                                                                                                                   |                      |

|          |                | ripple-based index                                                                                                                                                                              | 47                   |

|          |                | 3.3.1 The discrete-time model                                                                                                                                                                   | 48                   |

|          |                |                                                                                                                                                                                                 |                      |

|          |                |                                                                                                                                                                                                 | 50                   |

|          |                | 3.3.3 Condition for FSI                                                                                                                                                                         | $50 \\ 51$           |

|          |                |                                                                                                                                                                                                 |                      |

|          | 3.4            | 3.3.4 Stability analysis including the ripple amplitude                                                                                                                                         | 51                   |

|          | 3.4            | 3.3.4 Stability analysis including the ripple amplitude Design-oriented ripple-based index mathematical demonstration .                                                                         | 51<br>52             |

|          | 3.4            | 3.3.4Stability analysis including the ripple amplitudeDesign-oriented ripple-based index mathematical demonstration3.4.1Revisiting the state transition matrices                                | 51<br>52<br>54       |

|          | 3.4            | 3.3.4Stability analysis including the ripple amplitudeDesign-oriented ripple-based index mathematical demonstration3.4.1Revisiting the state transition matrices3.4.2Critical ripple expression | 51<br>52<br>54<br>54 |

|          | 3.5            | A desi   | ign-oriented combined approach for predicting overall sta-      |     |

|----------|----------------|----------|-----------------------------------------------------------------|-----|

|          |                | bility   | boundaries                                                      | 59  |

|          | 3.6            |          | sion to discontinuous conduction mode                           | 60  |

|          | 3.7            | Extens   | sion to full-state-feedback controller                          | 63  |

|          |                | 3.7.1    | Extension to the PID compensator                                | 70  |

|          | 3.8            | A freq   | uency domain model for overall stability boundary               | 73  |

|          |                | 3.8.1    | Discrete-time model: From z-domain to frequency domain          |     |

|          |                |          | representation                                                  | 74  |

|          |                | 3.8.2    | The averaged model and the discrete-time model frequency        |     |

|          |                |          | domain discrepancies                                            | 75  |

|          |                | 3.8.3    | The modulator frequency response                                | 78  |

|          |                | 3.8.4    | Extended discrete-time model                                    | 80  |

|          |                | 3.8.5    | Complete design-oriented frequency domain model                 | 83  |

|          |                | 3.8.6    | Extension to a PI compensator                                   | 84  |

| 4        | Cor            | ntrol of | f fast-scale instabilities in switching power converters        | 88  |

|          | 4.1            | Introd   | uction                                                          | 88  |

|          | 4.2            | Time-    | delay-based chaos controllers                                   | 89  |

|          |                | 4.2.1    | The time-delay feedback controller                              | 90  |

|          |                | 4.2.2    | Extended time-delay feedback controller                         | 92  |

|          | 4.3            | Notch    | -based chaos controllers                                        | 94  |

|          | 4.4            | Repet    | itive chaos controllers                                         | 96  |

|          | 4.5            |          | w band amplifier chaos controller                               | 99  |

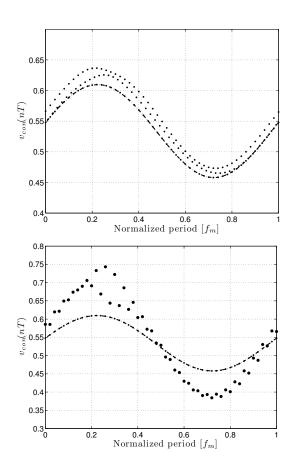

|          | 4.6            | Towar    | ds a low-ripple high-stability regulation: combining chaos      |     |

|          |                | contro   | ller with output ripple reduction                               | 101 |

|          |                | 4.6.1    | The LC divider: combining the low ripple and FSI con-           |     |

|          |                |          | troller                                                         | 105 |

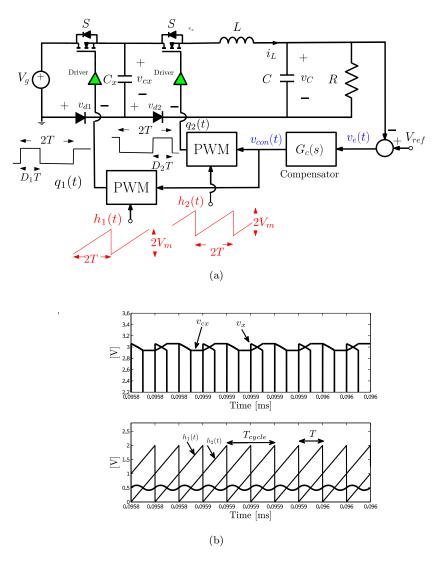

|          |                | 4.6.2    | Application to CMC                                              | 109 |

|          | 4.7            | Stabili  | ity margins and power metrics comparative between con-          |     |

|          |                | troller  | S                                                               | 113 |

| <b>5</b> | $\mathbf{Ext}$ | ension   | to alternative topologies and functionalities aiming            | S   |

|          | pow            |          | 0 0                                                             | 120 |

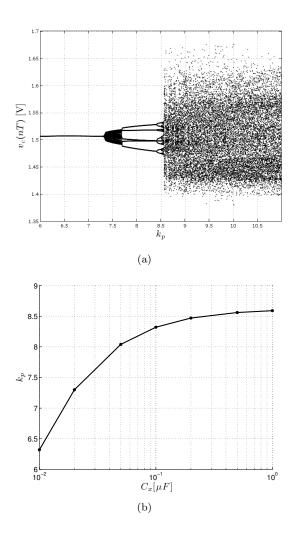

|          | 5.1            |          | nree-level buck-based converter: characterization, modeling     |     |

|          |                |          | rediction of instabilities                                      |     |

|          |                | 5.1.1    | Characterizing instabilities in a three-level buck converter    |     |

|          |                | 5.1.2    | Low capacitance value of the floating capacitor $\ldots \ldots$ |     |

|          | 5.2            | Exper    | imental Results                                                 | 124 |

|          | 5.3            | Three    | -level buck converter discrete-time model for FSI prediction    | 126 |

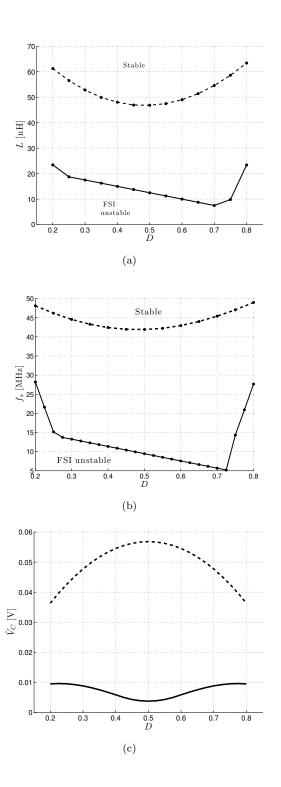

|          | 5.4            |          | e-based design-oriented index for fast-scale instability pre-   |     |

|          |                |          | 1                                                               | 130 |

|          | 5.5            |          | based switching power amplifier: modeling and characteri-       |     |

|          |                |          |                                                                 | 135 |

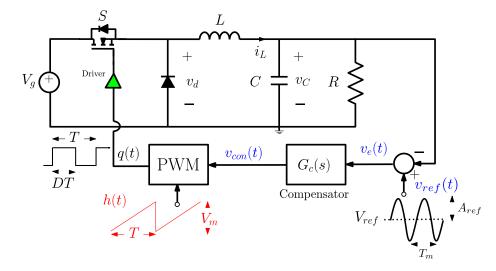

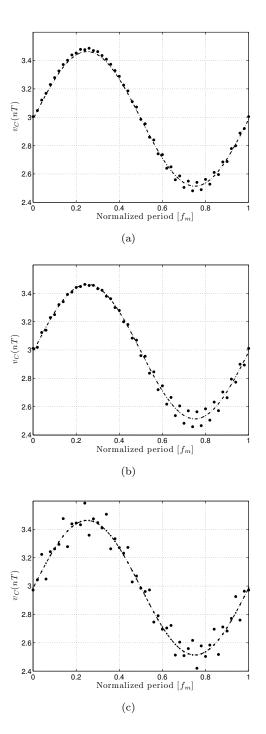

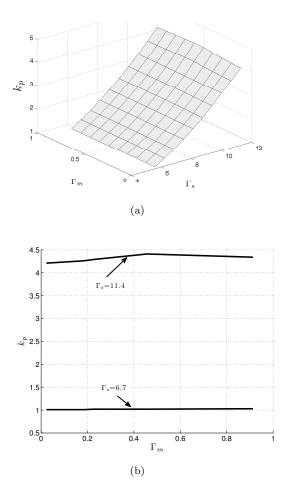

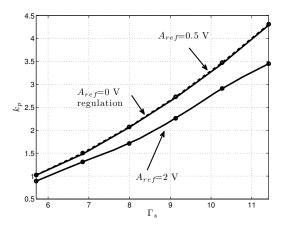

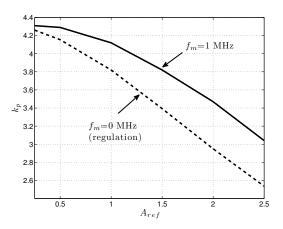

|          |                | 5.5.1    | Buck-based switching power amplifier instabilities: design-     |     |

|          |                |          | space exploration                                               | 136 |

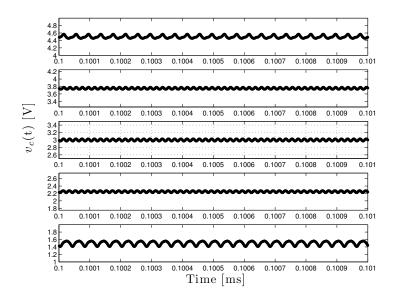

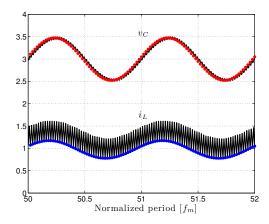

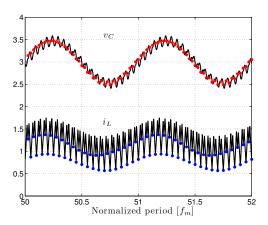

|          |                | 5.5.2    | Qualitative characterization of instabilities in a buck-based   |     |

|          |                |          | power switching amplifier with time-varying sinusoidal ref-     |     |

|          |                |          | erence                                                          |     |

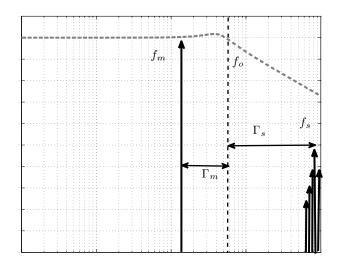

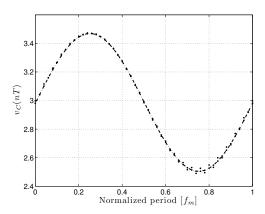

|          |                | 5.5.3    | Description of the switching amplifier dynamics by a discrete   |     |

|          |                |          | time model                                                      | 143 |

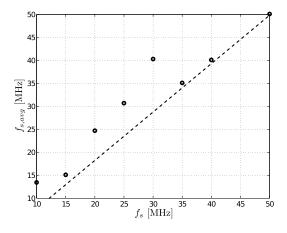

|              |     | 5.5.4   | Characterizing the stability boundary from the discrete time model             | 146 |

|--------------|-----|---------|--------------------------------------------------------------------------------|-----|

| 6            | Cor | clusio  | ns                                                                             | 149 |

| $\mathbf{A}$ | Dev | elopm   | ent of discrete-time map                                                       | 155 |

|              | A.1 | PI cor  | ntroller in a VMC or CMC buck converter                                        | 155 |

|              | A.2 | Realis  | stic PID controller in a VMC buck converter                                    | 156 |

|              | A.3 | DCM     | in a VMC buck converter under PI controller                                    | 156 |

|              | A.4 | Notch   | Amplifer narrow band chaos controller in a VMC buck                            |     |

|              |     | convei  | rter under a PI compensator                                                    | 157 |

|              | A.5 | High i  | impedance output filter and narrow band amplifier FSI con-                     |     |

|              |     | troller | in a VMC buck converter under a PI compensator                                 | 158 |

|              | A.6 | LC di   | vider in a VMC buck converter under a $\overrightarrow{\text{PI}}$ compensator | 159 |

| в            | Equ | ivalen  | ce of dynamics buck switching converters                                       | 160 |

| $\mathbf{C}$ | Rel | ation 1 | Between the time Derivative and the Ripple of the                              | е   |

|              |     | trol S  |                                                                                | 162 |

| D            | Exa | ct Exi  | pression of the Output Voltage Ripple for the Buck                             | ٢   |

|              |     |         | derived from Laplace analysis                                                  | 165 |

# List of Figures

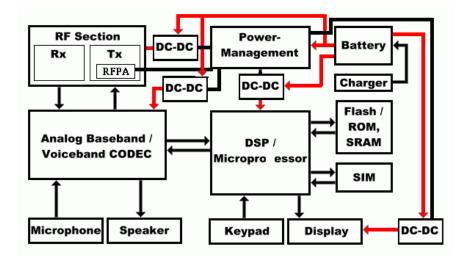

| 1.1        | Architecture of a battery-operated portable device (mobile phone).               | 1        |

|------------|----------------------------------------------------------------------------------|----------|

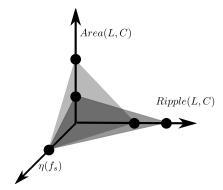

| 1.2        | Design-space of performance metrics limitations for integration:                 |          |

|            | Area, Efficiency $\eta$ and ripple. Two cases are illustrated: low area          |          |

|            | high-ripple and low-ripple high-area by keeping constant switch-                 |          |

|            | ing frequency.                                                                   | 3        |

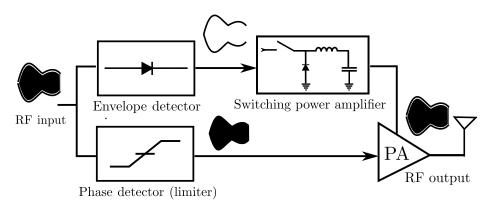

| 1.3        | EER technique including wide band switching power converter                      |          |

|            | as adaptive power supply.                                                        | 4        |

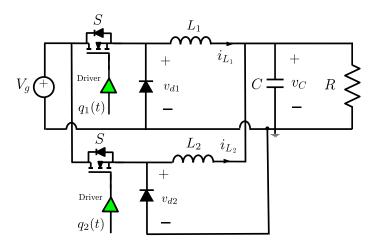

| 1.4        | Parallel connected (interleaving) topology based on buck converter.              | 5        |

| 1.5        | Multilevel (2-cell, 3-levels) topology based on buck converter                   | 6        |

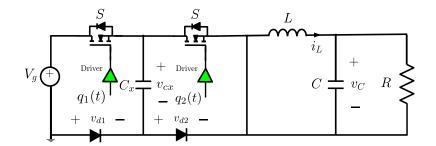

| 1.6        | (a) Conventional PWM modulator scheme (b) VMC and (c) CMC                        | 7        |

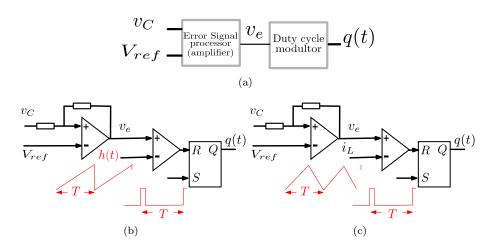

| 1.7        | Block diagram of a digital controller                                            | 7        |

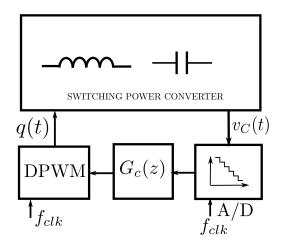

| 1.8        | Trajectories from the Lorenz system $\dot{x} = 10(y-x), \ \dot{y} = x(r-z)$      |          |

|            | and $\dot{z} = xy - 3z$ . (a) Limit cycle in steady-state with $r=160$ (b)       |          |

|            | Chaotic attractor in steady-state with $r=25$ . Initial conditions               |          |

|            |                                                                                  | 10       |

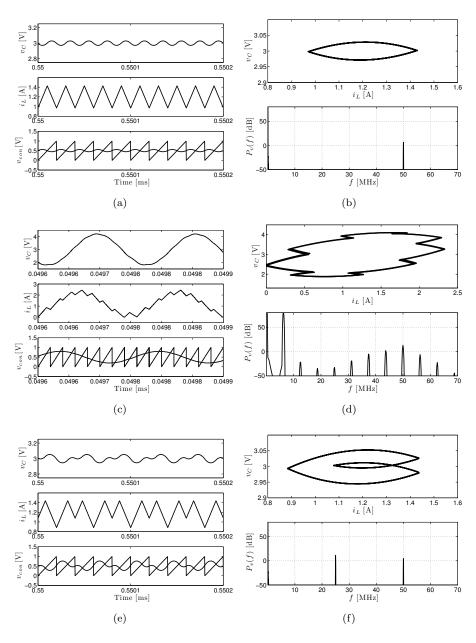

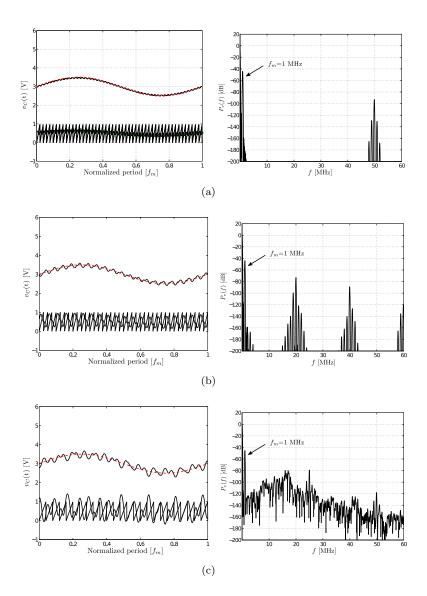

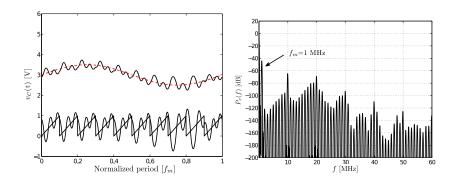

| 1.9        | Capacitor voltage, inductor current and modulator input wave-                    | 10       |

| 1.0        | forms along with phase portrait and frequency domain repre-                      |          |

|            | sentation, being $P_v(f) = 20 \log( V_C(f) )$ , in a VMC buck con-               |          |

|            | verter with PI control for the occurrence of different attractors                |          |

|            | (a) period-one (b) low frequency oscillation (SSI) and (c) period-               |          |

|            |                                                                                  | 12       |

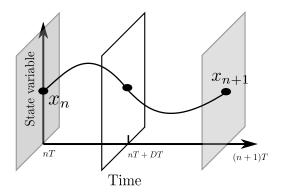

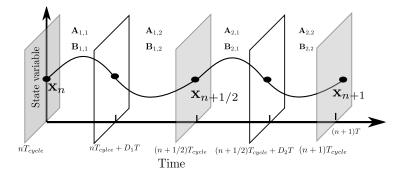

| 1 10       | Discrete time model illustration by sampling a two configuration                 | 12       |

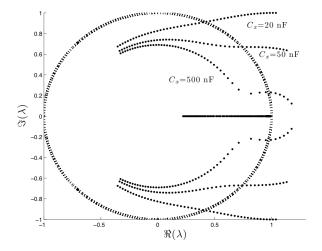

| 1.10       |                                                                                  | 13       |

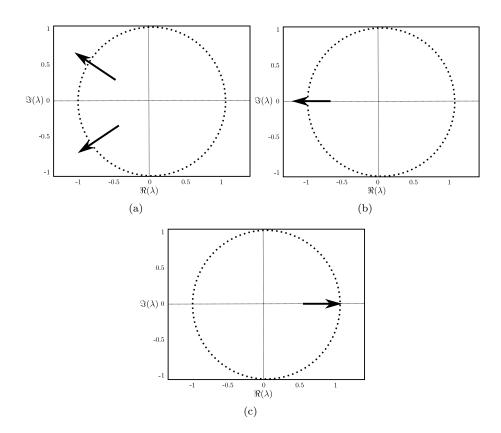

| 1 1 1      | Classification of eigenvalues $(\lambda)$ crossing the unit circle: (a) Neimark- | 10       |

| 1.11       | Sacker bifurcation occurrence (b) period-doubling bifurcation and                |          |

|            |                                                                                  | 14       |

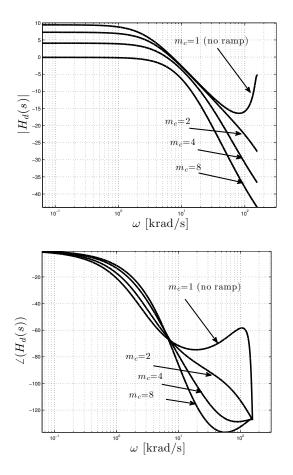

| 1 1 9      | The control-to-output transfer function $H_d(s)$ , in the frequency              | 14       |

| 1.12       | domain, considering the effect of the compensating ramp $m_c$ ob-                |          |

|            | tained from the expression and values proposed in (Ridley, 1989),                |          |

|            | D=0.4545, L=37.5 $\mu$ H, C=400 $\mu$ F, R=1 $\Omega$ and $f_s$ =50 kHz          | 18       |

| 1 1 2      |                                                                                  | 18       |

|            |                                                                                  | 10<br>21 |

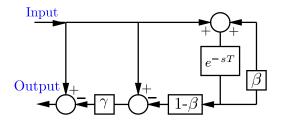

| 1.14       | TDFC ( $\beta = 0$ ) and its extension version (ETDFC) schemes                   | 21       |

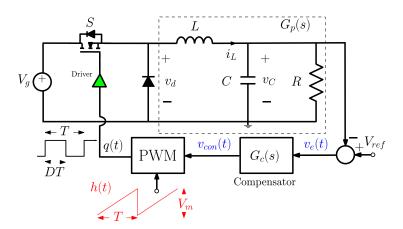

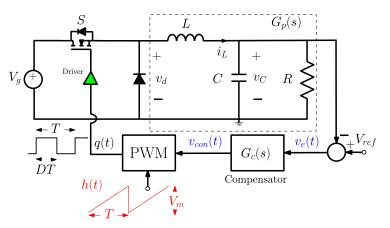

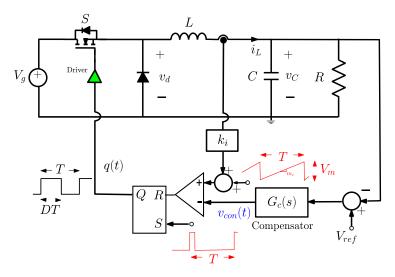

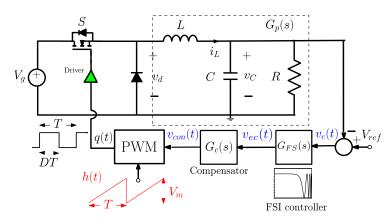

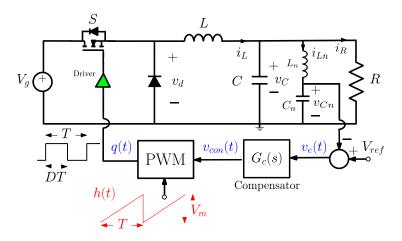

| 2.1        | VMC buck converter with a control $G_c(s)$ and PWM modulator                     |          |

| 2.1        |                                                                                  | 23       |

| 2.2        |                                                                                  | 20       |

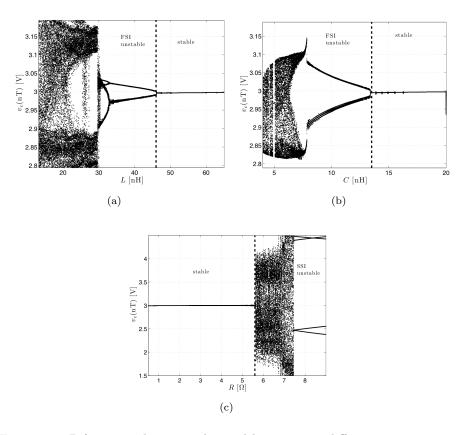

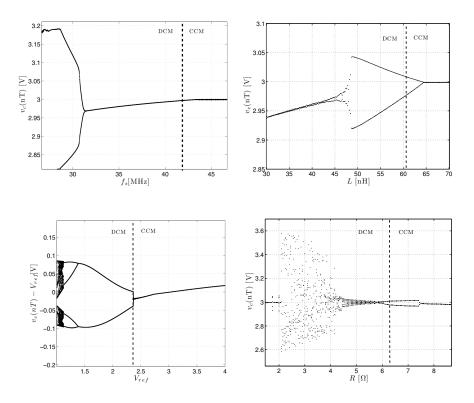

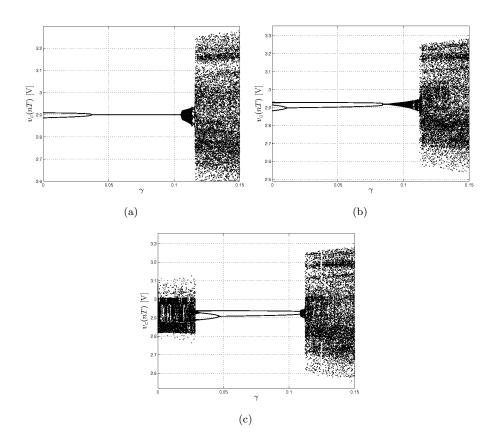

| 2.2<br>2.3 | Bifurcation diagrams obtained by sweeping different converter                    | - r      |

| 2.0        |                                                                                  | 25       |

|            |                                                                                  | -0       |

| 2.4  | Bifurcation diagrams obtained by sweeping the input and the reference voltages $V_q$ and $V_{ref}$ respectively.                                                                                                                                                                                                                                                                                                                                                               | 26       |

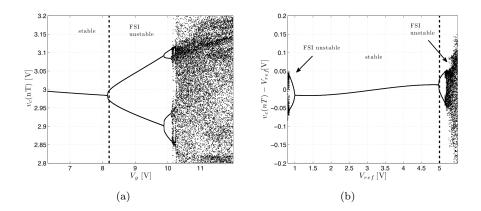

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

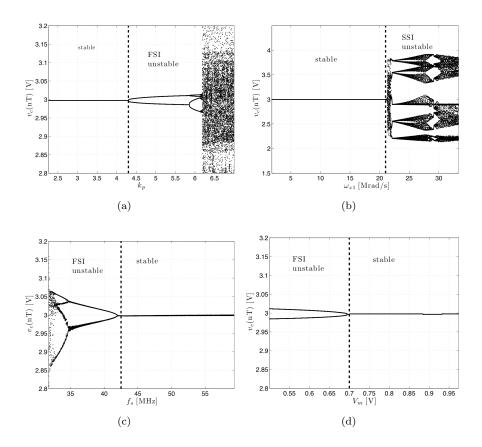

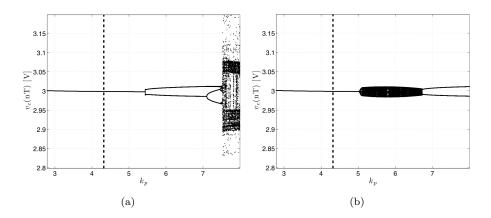

| 2.5  | Bifurcation diagrams obtained by sweeping controller parameters<br>(a) proportional gain $k_p$ (b) PI zero $\omega_{z1}$ and modulator parame-                                                                                                                                                                                                                                                                                                                                 |          |

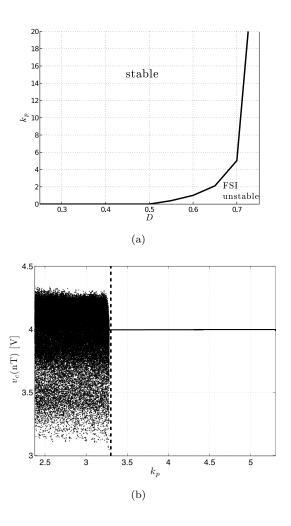

| 2.6  | ters (c) switching frequency $f_s$ and (d) ramp amplitude $V_m$<br>(a) Bifurcation diagram obtained by sweeping proportional gain $k_p$ with $\omega_{z1}=21$ Mrad/s (b) Stability boundary characterization                                                                                                                                                                                                                                                                   | 26       |

| 2.7  | over the space $(k_p, \omega_{z1})$ along with possible routes Route $\vec{v}_{\text{FS},\text{SS}}^{\text{CCM}}$ by plotting the bifurcation diagram as a function of                                                                                                                                                                                                                                                                                                         | 27       |

|      | $y$ . (a) $\mathcal{P}=5$ and (b) $\mathcal{P}=6$ .                                                                                                                                                                                                                                                                                                                                                                                                                            | 28       |

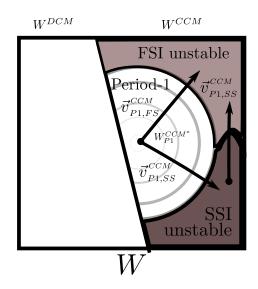

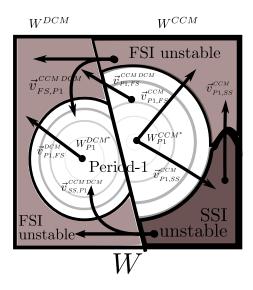

| 2.8  | Descriptive map in DCM and CCM along with routes between<br>modes and behaviors.                                                                                                                                                                                                                                                                                                                                                                                               | 29       |

| 2.9  | Different bifurcation diagrams obtained by crossing from CCM to DCM (a) $\vec{v}_{\text{FS},\text{P1}}^{\text{CCM},\text{DCM}}(f_s)$ as a function of switching frequency $f_s$ (b) $\vec{v}_{\text{FS},\text{P1}}^{\text{CCM},\text{DCM}}(L)$ as a function of inductance $L$ (c) $\vec{v}_{\text{P1},\text{FS}}^{\text{CCM},\text{DCM}}(V_{ref})$ as a function of voltage reference $V_{ref}$ with $k_p = 2$ (d) $\vec{v}_{\text{SS},\text{P1}}^{\text{CCM},\text{DCM}}(R)$ |          |

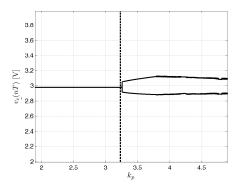

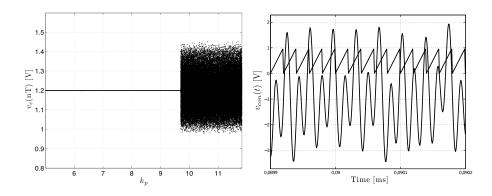

| 210  | as a function of output resistor $R$ and with $\omega_{z1} = 10$ Mrad/s<br>Bifurcation diagram by sweeping the proportional gain $k_p$                                                                                                                                                                                                                                                                                                                                         | 30<br>31 |

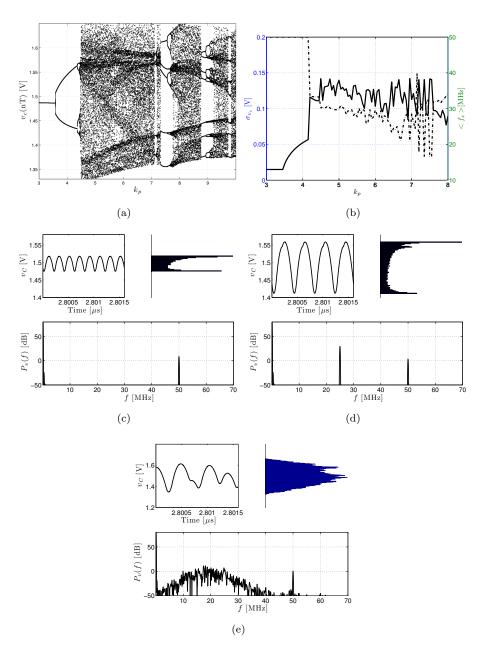

|      | (a) Bifurcation diagram sy sweeping the proportional gain $n_p$ : (a) Bifurcation diagram as function of $k_p$ (b) Standard deviation $\sigma_{v_c}$ (solid) and averaged switching frequency $\langle f_s \rangle$ (dashed). Representative time-domain waveform, histogram and spectrum (calculated within 1000 periods) of the output voltage for (c)                                                                                                                       | 01       |

|      | $k_p=3$ (period-one) (d) $k_p=5$ (period-doubling) and (e) $k_p=7$ (chaotic                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|      | regime) with $D = 0.5$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33       |

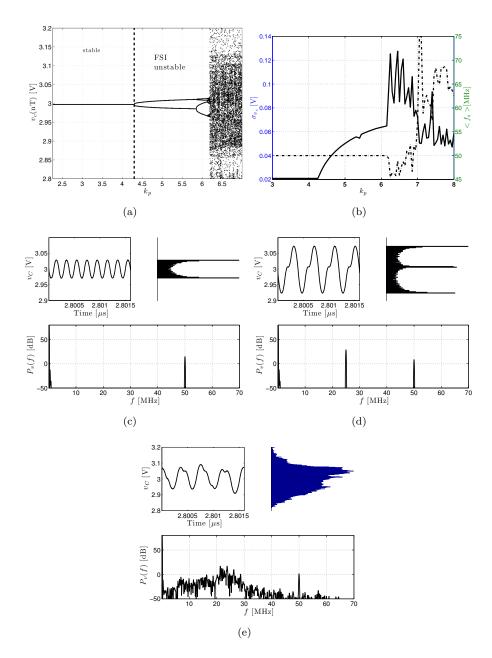

| 2.12 | (a) Bifurcation diagram as function of $\omega_{z1}$ (b) Standard deviation $\sigma_{v_c}$ (solid) and average switching frequency (dashed) $\langle f_s \rangle$ .<br>Representative time-domain waveform, histogram and spectrum (calculated within 1000 periods) of the output voltage for (c) $\omega_{z1}=10$ Mrad/s (period-one) and (d) $\omega_{z1}=25$ Mrad/s (SSI) with $D = 0.5$ .                                                                                  | 34       |

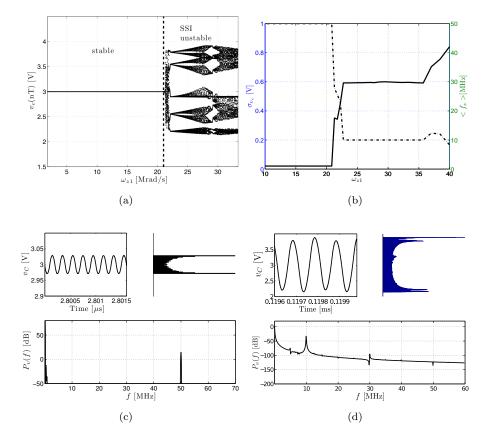

| 2.13 | (a) Bifurcation diagram as a function of $k_p$ (b) Standard deviation $\sigma_{v_c}$ (solid) and average switching frequency $\langle f_s \rangle$ (dashed).<br>Representative time-domain waveform, histogram and spectrum (calculated within 1000 periods) of the output voltage for (c) $k_p = 3$ (period-one) (d) $k_p = 4$ (period-doubling) and (e) $k_p = 7$                                                                                                            | 01       |

|      | (Chaotic behavior) with $D = 0.25$ .                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36       |

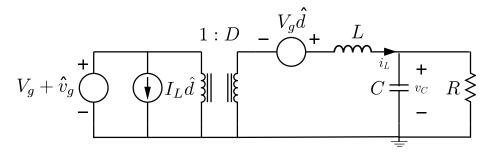

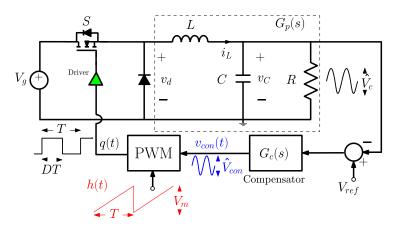

| 3.1  | Circuit diagram of a DC-DC VMC buck converter with a PWM.                                                                                                                                                                                                                                                                                                                                                                                                                      | 39       |

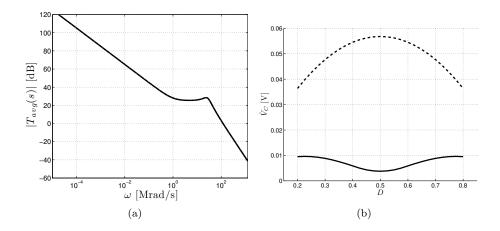

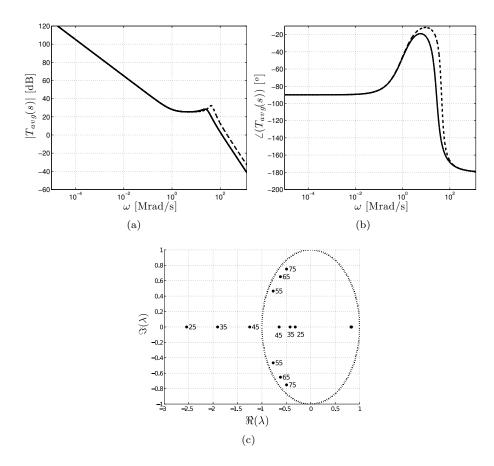

| 3.2  | Bode plot of total loop gain $T_{avg}(s)$ of a buck converter under PI compensator. (a) magnitude and (b) phase.                                                                                                                                                                                                                                                                                                                                                               | 40       |

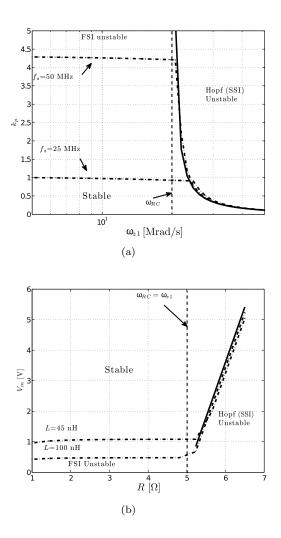

| 3.3  | Overall stability boundary map in the design parameter space (a) $\omega_{z1}$ , $k_p$ and $f_s$ (b) $V_m$ , $R$ and $L$ obtained from the discrete-time mode (dash-dot) and results from the averaged model using the                                                                                                                                                                                                                                                         |          |

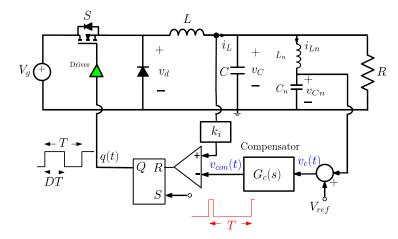

| 3.4  | Nyquist stability criterion (solid)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41       |

| 3.5  | model by sweeping the inductance (values are in nH)<br>Circuit diagram of a VMC DC-DC buck converter with a com-<br>pensator frequency response $G_c(s)$ and under a fixed frequency                                                                                                                                                                                                                                                                                           | 42       |

|      | PWM strategy. $\ldots$                                                                                                                                                                                                                                                                                                                                                                        | 44       |

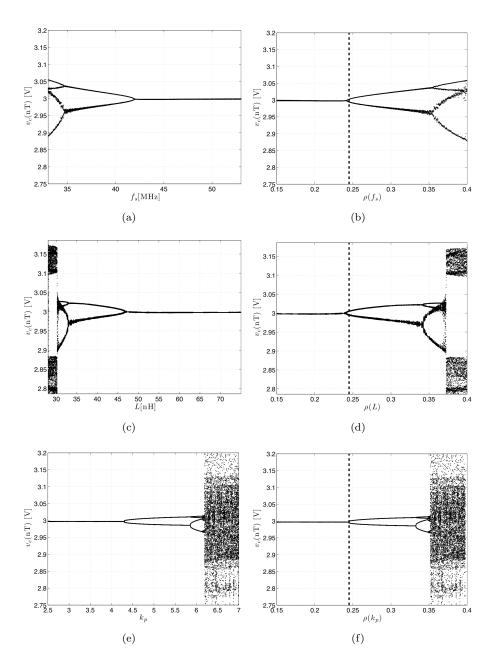

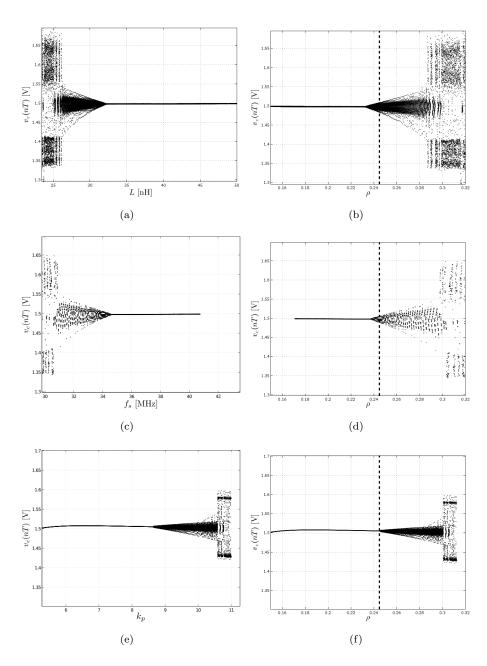

| 3.6  | Bifurcation diagrams obtained by sweeping different nature pa-                                                                                                        |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | rameters (a) the switching frequency $f_s$ , (b) the inductance L and                                                                                                 |     |

|      | (c) the proportional gain $k_p$ and its equivalent representation as a                                                                                                |     |

|      | function of the ripple-based index $\rho$ (d), (e) and (f), respectively.                                                                                             |     |

|      | $ \rho_{crit} \approx 0.245 \text{ (dashed line)}. \dots \dots$ | 46  |

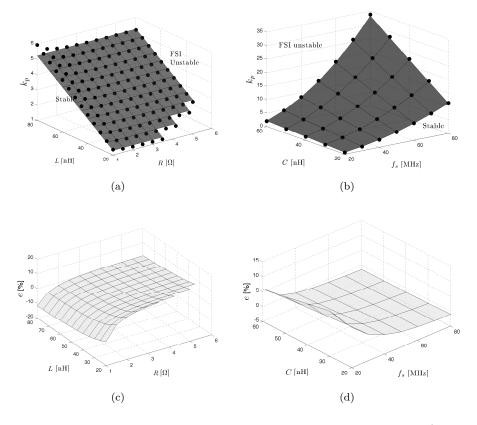

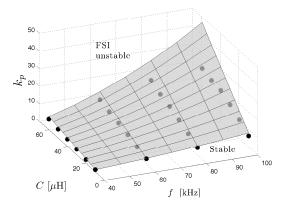

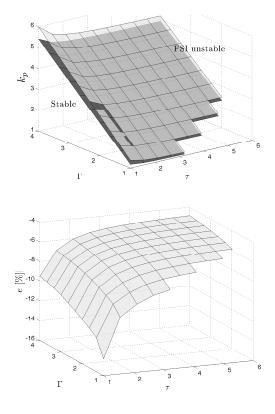

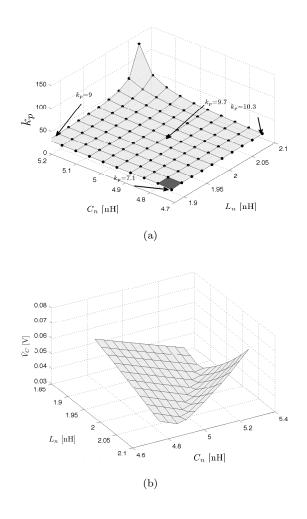

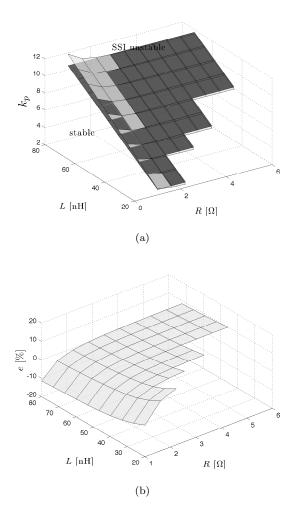

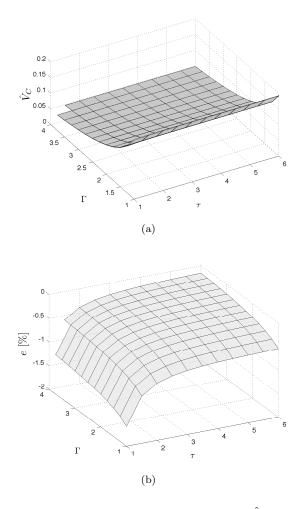

| 3.7  | FSI boundary surfaces obtained from the switched model (black                                                                                                         |     |

|      | dots) and from the ripple-based index condition given in Eq. $(3.10)$                                                                                                 |     |

|      | with $\rho_{crit}=0.245$ (mesh surface), as a function of (a) inductance                                                                                              |     |

|      | L, output resistance R and proportional gain $k_p$ and (b) output                                                                                                     |     |

|      | capacitance $C$ , the switching frequency $f_s$ and proportional gain                                                                                                 |     |

|      | $k_p$ . The error between both surfaces is shown in (c) and (d),                                                                                                      |     |

|      | respectively.                                                                                                                                                         | 47  |

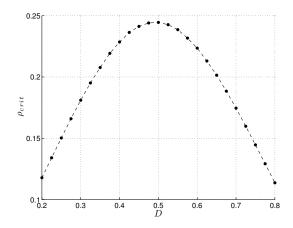

| 3.8  | FSI boundary curve, represented in $\rho_{crit}$ terms and obtained from                                                                                              |     |

|      | numerical simulations using the switched model, as a function of                                                                                                      |     |

|      | the duty cycle D                                                                                                                                                      | 48  |

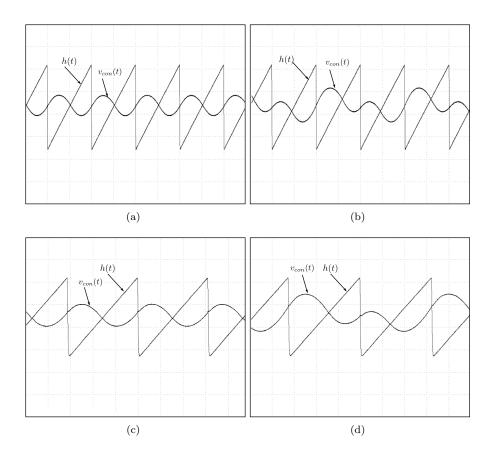

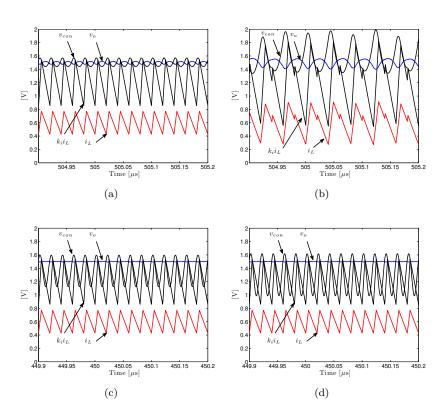

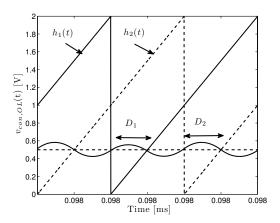

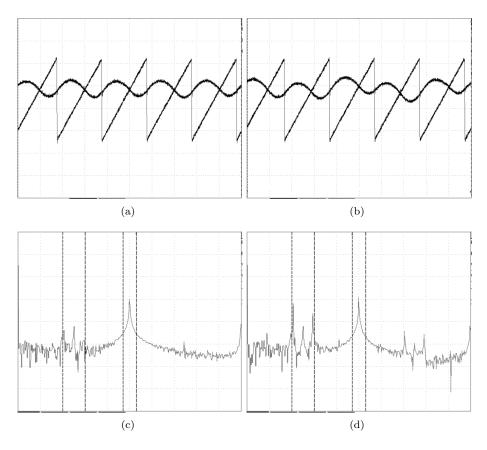

| 3.9  | Control signal $v_{con}(t)$ and modulator ramp $h(t)$ waveforms just                                                                                                  |     |

|      | before and just after FSI occurrence by sweeping (a)-(b) the pro-                                                                                                     |     |

|      | portional gain $k_p$ and (c)-(d) the switching frequency $f_s$ . Mea-                                                                                                 |     |

|      | sured critical ripple amplitude at modulator input normalized to                                                                                                      |     |

|      | the ramp amplitude is $\rho_{crit} \approx 0.27$ for both cases                                                                                                       | 49  |

| 3.10 | FSI boundary surfaces obtained from experimental measurements                                                                                                         |     |

|      | (black dots) and using the ripple-based index ( $\rho_{crit} = 0.245$ )                                                                                               |     |

|      | (mesh surface) over the design parameter space $k_p$ , $f_s$ and $C_{\cdot}$ .                                                                                        | 50  |

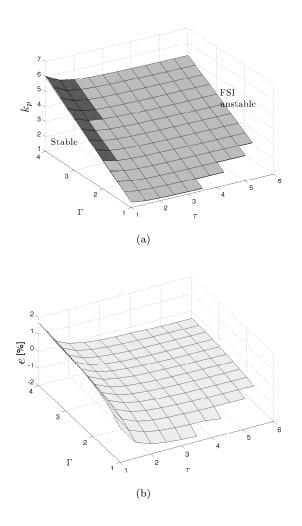

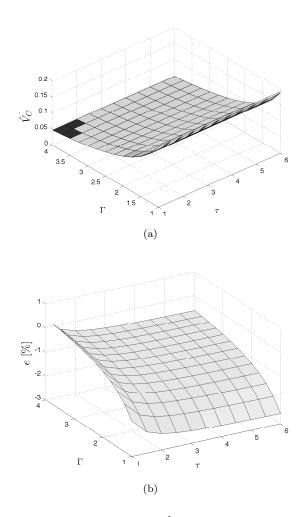

| 3.11 | (a) FSI boundary surfaces obtained from the discrete-time model                                                                                                       |     |

|      | (white) and from ripple-based index approach (black) as a func-                                                                                                       |     |

|      | tion of the proportional gain $k_p$ , $\Gamma$ , and $\tau$ . (b) Error between                                                                                       |     |

|      | both surfaces                                                                                                                                                         | 53  |

| 3.12 | FSI boundary surfaces obtained from the exact discrete-time model                                                                                                     |     |

|      | (black) and by approximating the derivative of the output voltage                                                                                                     |     |

|      | at the switching instant $\dot{v}_C(DT^-)$ for ripple amount $\dot{V}_C$ accord-                                                                                      |     |

|      | ing to Eq. $(3.31)$ (white) as a function of the proportional gain                                                                                                    |     |

|      | $k_p$ , $\Gamma$ and $\tau$ . (b) Error between both surfaces                                                                                                         | 55  |

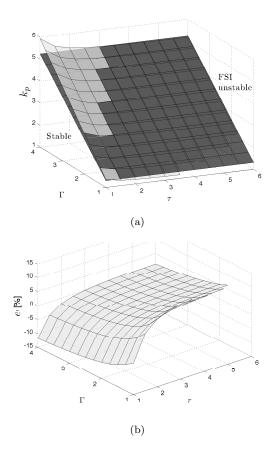

| 3.13 | (a) FSI boundary surfaces obtained from the discrete-time model                                                                                                       |     |

|      | (white) and from the ripple-based condition given in Eq. $(3.41)$                                                                                                     |     |

|      | $\mathcal{P}_v = 1$ (black) as a function of the proportional gain $k_p$ , $\Gamma$ and $\tau$ .                                                                      |     |

|      | (b) Error between both surfaces.                                                                                                                                      | 57  |

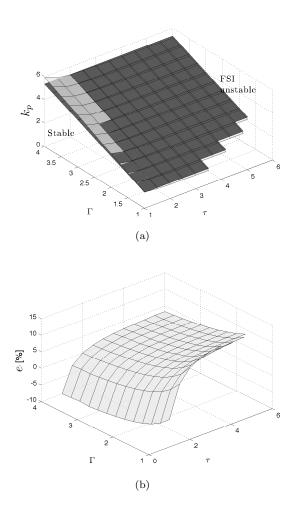

| 3.14 | FSI boundary curves obtained from the discrete-time model (Eq. (3.1                                                                                                   | 8), |

|      | dots) and from ripple-based condition given in Eq. (3.41) (solid)                                                                                                     |     |

|      | with $\mathcal{P}_v = 1$ as a function of the duty cycle $D$ and the propor-                                                                                          | -   |

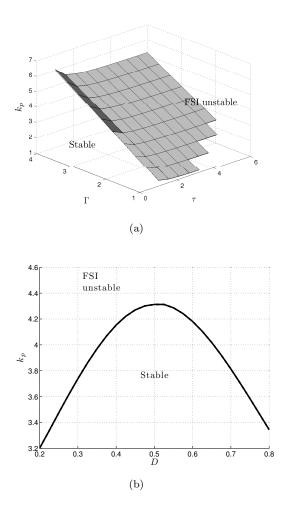

|      | tional gain $k_p$ with $\tau=2.5$ and $\Gamma=3.3$ .                                                                                                                  | 58  |

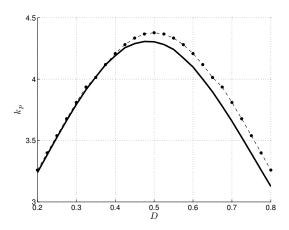

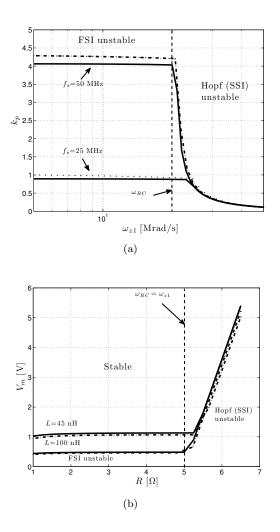

| 3.15 | Overall stability map obtained from the discrete-time model (dash-                                                                                                    |     |

|      | dots) compared with design-oriented models: SSI boundary (solid                                                                                                       |     |

|      | blue) from Eq. 3.42 and FSI boundary (solid green) from ripple-                                                                                                       |     |

|      | based index given in Eq. 3.43 with $\rho_{crit}(0.5)=0.245$ . The ob-                                                                                                 |     |

|      | tained results as a function of (a) $\omega_{z1}$ , $k_p$ and $f_s$ (b) $R$ , $V_m$ and                                                                               | 00  |

| 9.10 | $L. \qquad \dots \qquad $                                     | 60  |

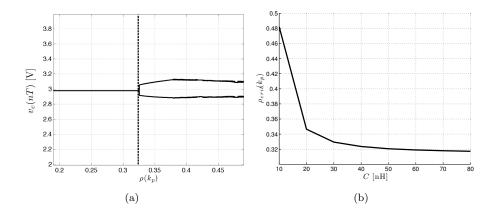

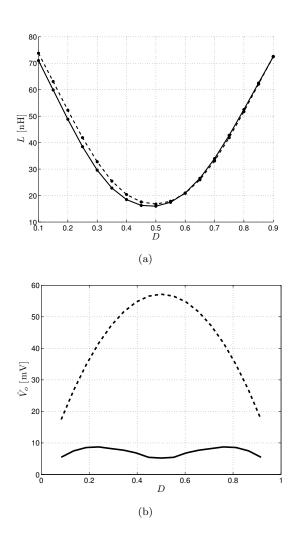

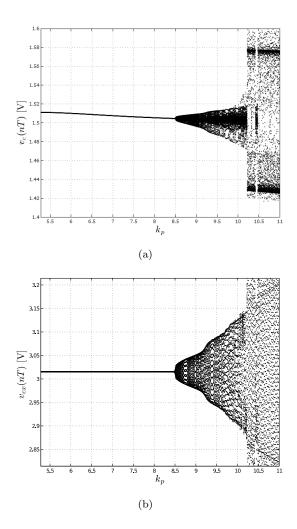

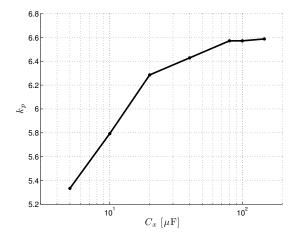

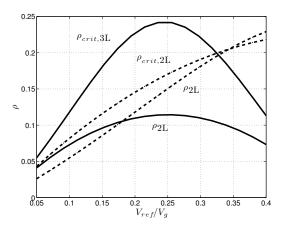

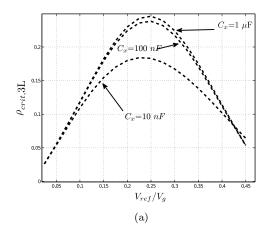

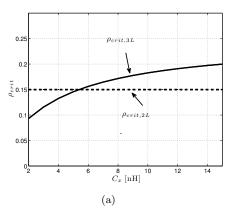

| 9.10 | (a) Bifurcation diagram by sweeping the proportional gain $k_p$ and (b) the FSI boundary $a_{p,i}$ $(k_i)$ as a function of subtrut capacitance                       |     |

|      | (b) the FSI boundary $\rho_{crit}(k_p)$ as a function of output capacitance                                                                                           | 60  |

|      | <i>C</i>                                                                                                                                                              | 62  |

| 3.17 | Bifurcation diagrams by sweeping the proportional gain $k_p$ with<br>(a) $K_{\text{DCM}}=0.375$ , as in Fig. 3.16, but with different parameter<br>values $L=45$ nH $f_s=25$ MHz $R=6$ $\Omega$ (b) the same $M = 0.5$ ,<br>but with different parameters values $V_g=8$ V $V_{ref}=4$ V. (c) FSI<br>boundary obtained from the discrete-time model by concurrently<br>sweeping the inductance value $L$ and the switching frequency<br>$f_s = K_{\text{DCM}}R/(2L)$ , hence keeping constant $K_{\text{DCM}}$ , and concur-<br>rently sweeping the voltage reference value $V_{ref}$ and the input<br>voltage $V_g = V_{ref}/D$ , hence keeping constant $M$ | 63 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

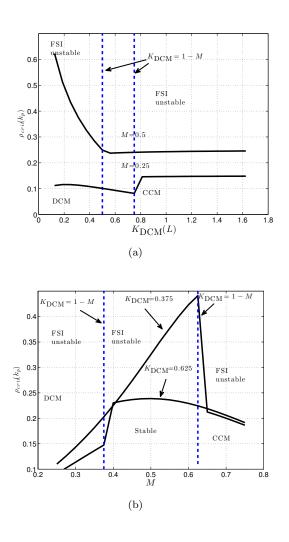

| 3.18 | Stability curve $\rho_{crit,\text{DCM}}(k_p)$ as a function of (a) $K_{\text{DCM}}$ , for $M=0.5$<br>and $M=0.25$ and (b) voltage conversion ratio $M$ , for $K_{\text{DCM}}=0.625$<br>$(L=25 \text{ nH}, f_s=50 \text{ MHz}, R=4 \Omega)$ and $K_{\text{DCM}}=0.375$ $(L=15 \text{ nH},$                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | $f_s = 50 \text{ MHz}, R = 4 \Omega$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

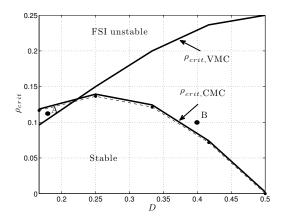

|      | CMC buck converter with voltage feedback loop Bifurcation diagram by sweeping $k_p$ in a CMC buck converter with $k_i = 2$ , $m_c=0$ and $V_{ref}=1.5$ V. $\rho_{crit,CMC} = 0.1364$ obtained                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65 |

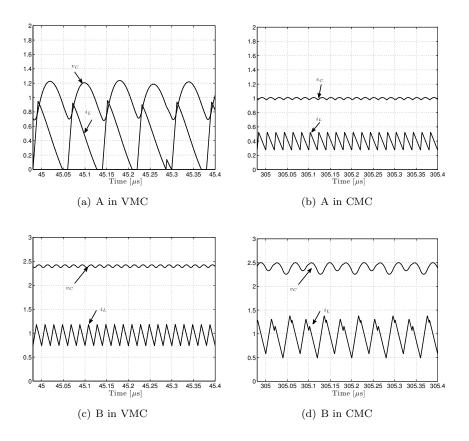

| 3.21 | from Eq. (3.60)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

| 3.22 | stability condition in Eq. (3.59) bifurcation occurs at $k_i=2.5.$ . Stability boundary by sweeping the duty cycle $D$ in a CMC. Results obtained from the discrete-time model (dots) and from the design-oriented approach of Eq. 3.59 (solid) with $k_i=2$ . Additionally, the stability boundary in VMC $\rho_{crit,VMC}$ obtained for                                                                                                                                                                                                                                                                                                                     | 67 |

| 3.23 | $k_i=0$ is shown. A and B points are simulated and shown in Fig. 3.23.<br>Time simulation in VMC buck converter $(k_i=0 \text{ and } m_c = V_m f_s)$<br>(a) and (c) and in CMC buck converter $(k_i=2 \text{ and } m_c=0)$ (b)<br>and (d) respectively. Conditions are those indicated in point A                                                                                                                                                                                                                                                                                                                                                             | 68 |

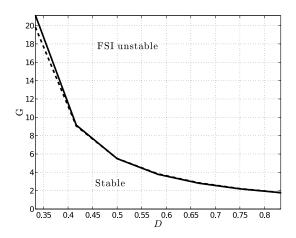

| 3.24 | and point B in Fig. 3.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69 |

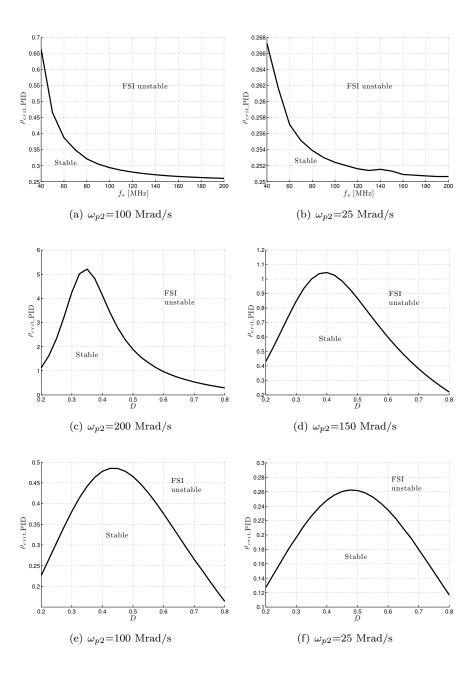

| 3.25 | and from design-oriented equation (solid) given in Eq. (3.59)<br>$\rho_{crit,\text{PID}}(G)$ as a function of the PID pole $\omega_{p2}$ and (a)-(b) the<br>switching frequency $f_s$ and (c)-(d)-(e)-(f) the duty cycle $D$ . Con-<br>troller parameters: $\omega_{z1}$ =100 krad/s, $\omega_{z2}$ =1 Mrad/s with $V_{ref}$ =3 V                                                                                                                                                                                                                                                                                                                             | 71 |

|      | and $\omega_s = 2\pi f_s = 314$ Mrad/s and other parameters are the same as<br>in the CMC case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

|      | Equivalent block diagram of the VMC converter in the discrete-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74 |

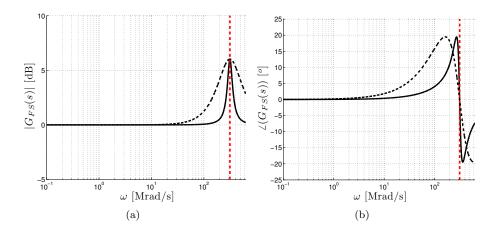

| 3.27 | time model domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 76 |

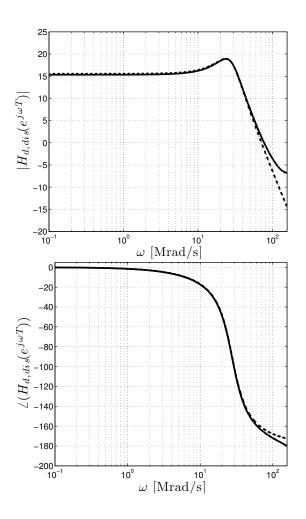

| 3.28 | Bode plots of $H_{d,avg}(j\omega)$ (dashed) given in Eq. (3.2) and $H_{d,dis}(e^{j\omega T})$ (solid) given in Eq. (3.81).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70 |

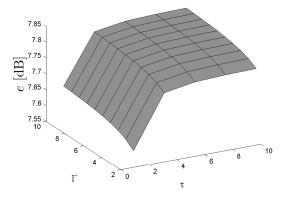

|      | Error (in dB) in the magnitude between $H_{d,avg}(j\omega_s/2)$ and $H_{d,dis}(e^{j\omega_s/2})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 3.30 | Comparison in % for the output waveform harmonic amplitude $c_n$ : $c_1$ (solid) $c_2$ (dash-dot) and $c_2$ (dots) with output ripple mea-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

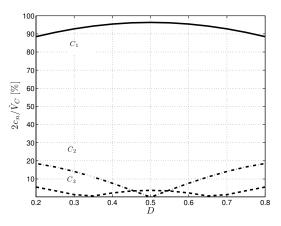

|      | sure $\hat{V}_c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79 |

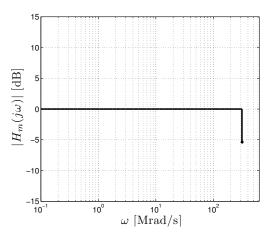

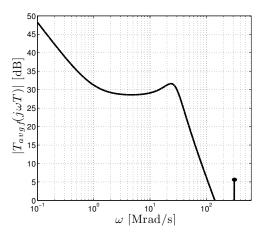

| 3.31                                                                        | Modulator transfer function $ H_{mf}(j\omega) $ with constant gain in all<br>the frequency range below $f_s$ ( $V_m=1$ V) and a tone at the switch-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

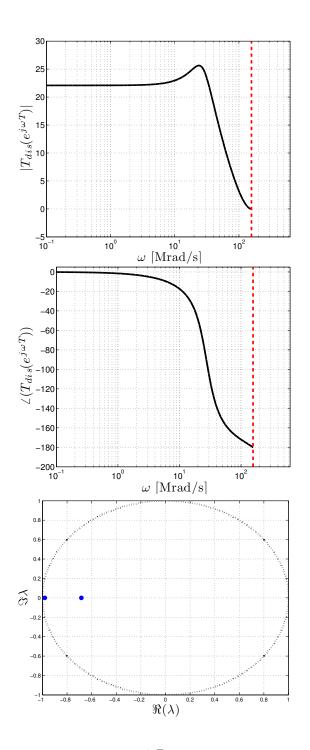

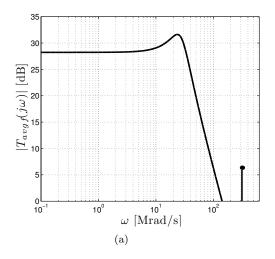

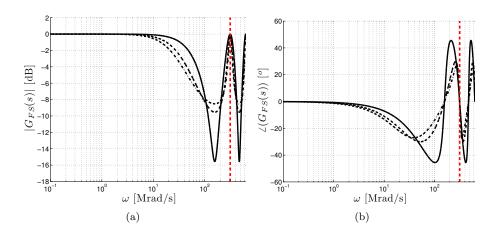

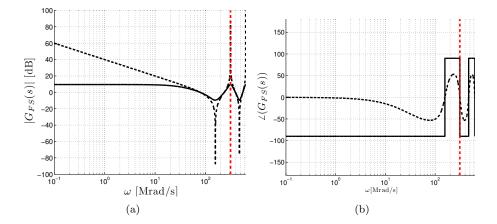

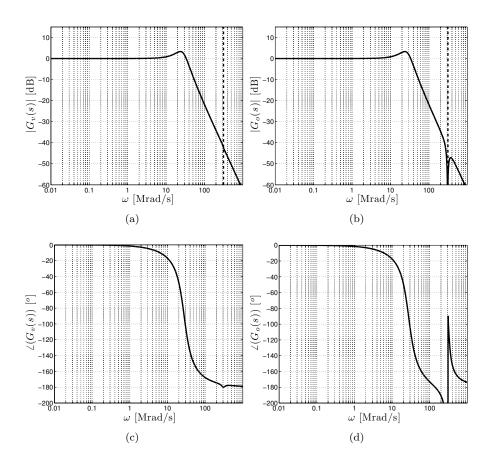

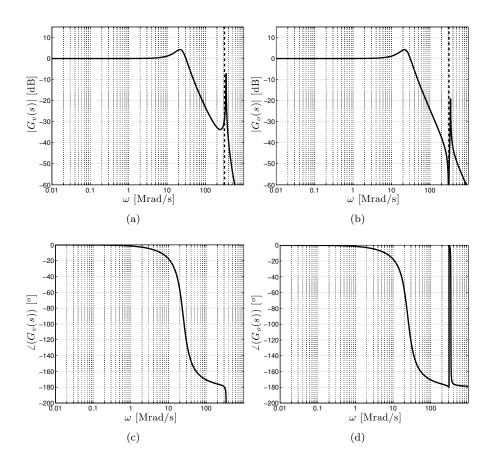

| 3.32                                                                        | ing frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 80                                                               |

| 3.33                                                                        | ample the system being at the boundary of FSI conditions, with $k_p=4.31$ and $SM_{FS}=0.01$ dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 81                                                               |

|                                                                             | from the FSI condition given in Eq. (3.97) (a) as a function of parameters $\Gamma$ and $\tau$ (b) as a function of the duty cycle $D$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82                                                               |

| 3.34                                                                        | (a) Frequency domain representation of $T_{avgf}(j\omega)$ at the boundary of FSI conditions with $k_p=4.31$ , with $SM_{FS}=7.8$ dB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83                                                               |

| 3.35                                                                        | (a) FSI boundary surface obtained from the discrete-time model<br>(black) and from the frequency domain model stability condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0.4                                                              |

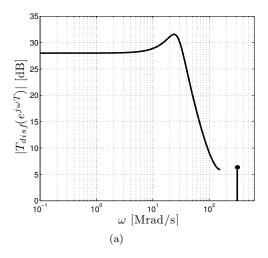

| 3.36                                                                        | given in Eq. (3.99) (white). (b) Error between both surfaces in %. Frequency domain magnitude response of $T_{avgf}(j\omega)$ obtained by joining the averaged model of a VMC buck converter, under a PI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 84                                                               |

| 3.37                                                                        | compensator, along with the modulator transfer function $H_{mf}(j\omega)$ .<br>Overall stability boundary obtained from the discrete-time model<br>(dash-dot) and results from the frequency domain model (solid),<br>using the Nyquist stability criterion (phase and gain margin)<br>along with the FSI stability condition given in Eq. (3.99), over                                                                                                                                                                                                                                                                                                                                                                                                                                               | 85                                                               |

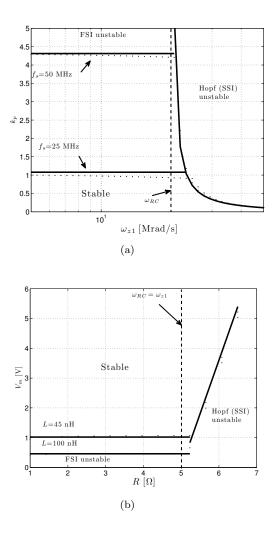

|                                                                             | the design parameter space (a) $\omega_{z1}$ and $k_p$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                                                               |

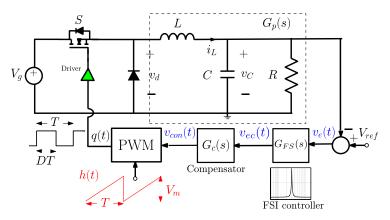

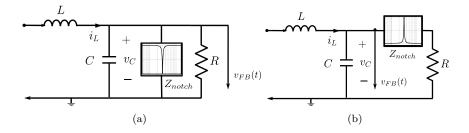

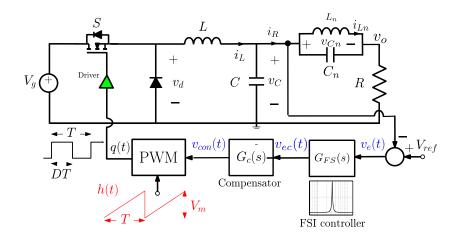

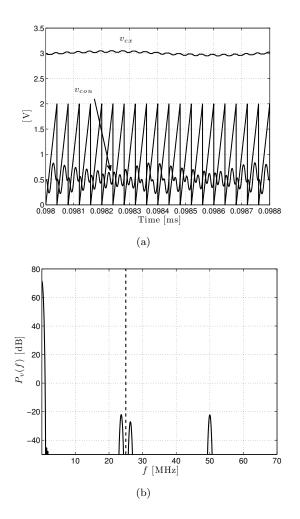

| 4.1                                                                         | VMC buck converter with a compensator $G_c(s)$ along with a FSI controller $G_{FS}(s)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88                                                               |

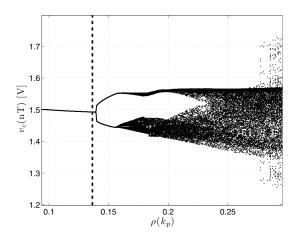

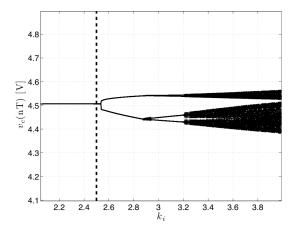

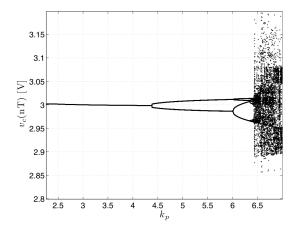

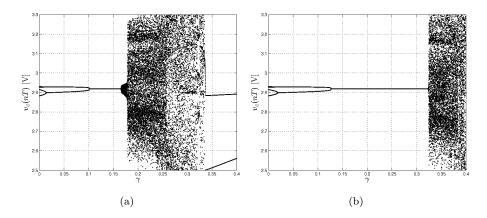

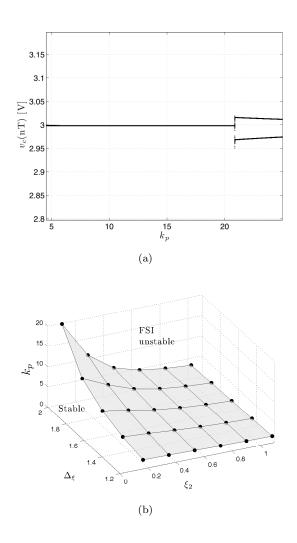

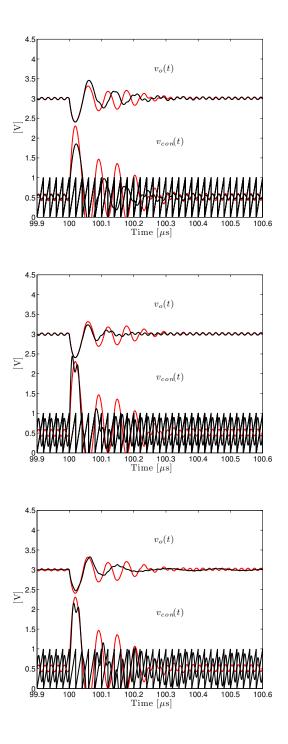

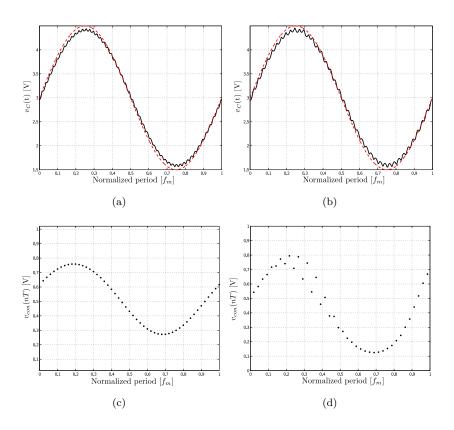

| 4.2                                                                         | Bifurcation diagram by increasing $k_p$ in a VMC buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                  |

| 4.2                                                                         | with a PI compensator showing the route to chaos via period-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00                                                               |

|                                                                             | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 89<br>90                                                         |

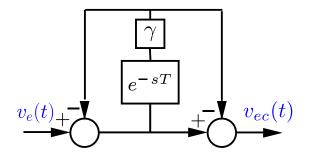

| 4.2<br>4.3<br>4.4                                                           | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3$<br>Time-delay feedback control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90                                                               |

| 4.3                                                                         | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3$<br>Time-delay feedback control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |

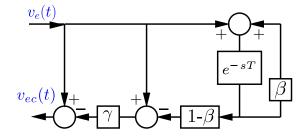

| 4.3<br>4.4<br>4.5                                                           | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3$<br>Time-delay feedback control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 90                                                               |

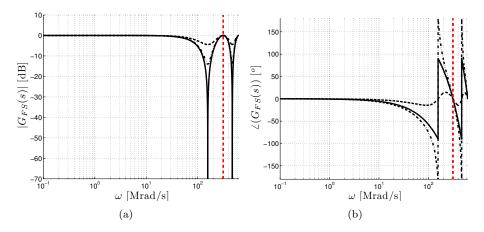

| $\begin{array}{c} 4.3\\ 4.4\end{array}$                                     | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3.$<br>Time-delay feedback control scheme<br>Bode diagram representation (magnitude and phase) of the TDFC<br>with $\gamma=0.2$ (dashed) $\gamma=0.5$ (solid) and $\gamma=0.6$ (dot-dashed) show-<br>ing the switching frequency (vertical dashed line)<br>Bifurcation diagram by sweeping $\gamma$ in a VMC buck converter<br>with TDFC for different values of proportional gain $k_p$ (a) $k_p=$<br>5 (in period-doubling without TDFC) (b) $k_p=6.2$ (in period-four<br>without TDFC) (c) $k_p=7$ (chaos without TDFC)<br>Bifurcation diagram by sweeping the proportional gain $k_p$ in a<br>VMC buck converter with TDFC for different values of $\gamma$ (a)                                           | 90<br>90<br>91                                                   |

| 4.3<br>4.4<br>4.5                                                           | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}$ =4.3<br>Time-delay feedback control scheme<br>Bode diagram representation (magnitude and phase) of the TDFC<br>with $\gamma$ =0.2 (dashed) $\gamma$ =0.5 (solid) and $\gamma$ =0.6 (dot-dashed) show-<br>ing the switching frequency (vertical dashed line)<br>Bifurcation diagram by sweeping $\gamma$ in a VMC buck converter<br>with TDFC for different values of proportional gain $k_p$ (a) $k_p$ =<br>5 (in period-doubling without TDFC) (b) $k_p$ =6.2 (in period-four<br>without TDFC) (c) $k_p$ =7 (chaos without TDFC)<br>Bifurcation diagram by sweeping the proportional gain $k_p$ in a<br>VMC buck converter with TDFC for different values of $\gamma$ (a)<br>$\gamma$ =0.05 (b) $\gamma$ =0.1 | 90<br>90                                                         |

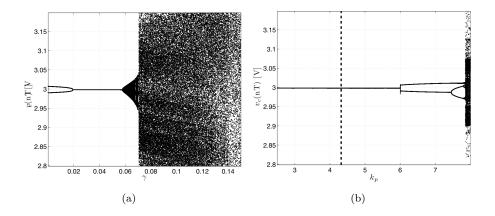

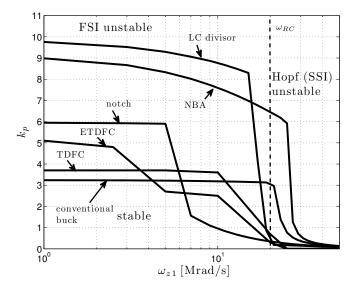

| <ul><li>4.3</li><li>4.4</li><li>4.5</li><li>4.6</li></ul>                   | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}=4.3.$<br>Time-delay feedback control scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul><li>90</li><li>90</li><li>91</li><li>92</li><li>93</li></ul> |

| <ul> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul> | with a PI compensator showing the route to chaos via period-<br>doubling. $k_{p,crit}$ =4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul><li>90</li><li>90</li><li>91</li><li>92</li></ul>            |

| 4.10           | Bifurcation diagram by sweeping the proportional gain $k_p$ in a VMC buck converter with a pure notch filter $\xi_1=0$ , tuned at half          |     |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                | of the switching frequency with $\xi_2=0.001$                                                                                                   | 95  |

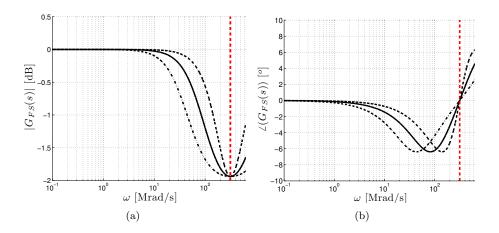

| 4 11           | Bode diagram representation (magnitude and phase) of the stop-                                                                                  | 00  |

| <b>T</b> , I I | band controller as a function of $\xi_2$ keeping constant the atten-                                                                            |     |

|                | uation $\Delta_{\xi}=0.8$ with $\xi_2=1$ (dash-point), $\xi_2=2$ (solid) and $\xi_2=4$                                                          |     |

|                | (dash) $(dash)$ $(dash)$                                                                                                                        | 96  |

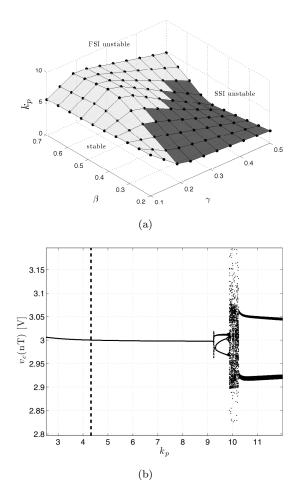

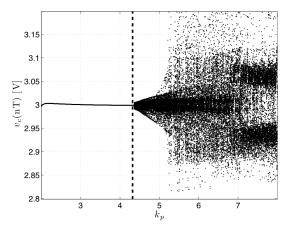

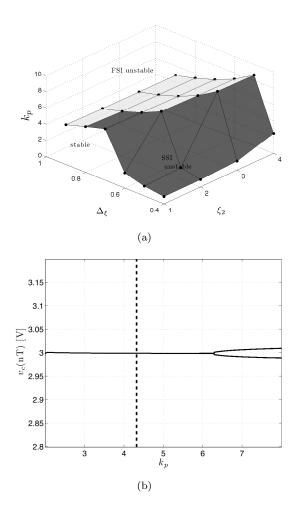

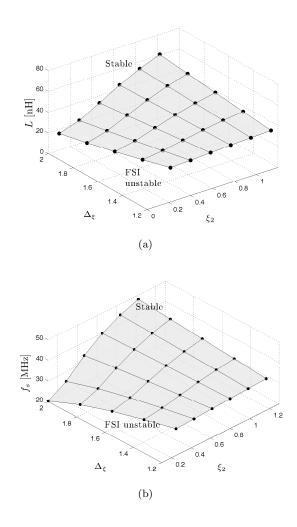

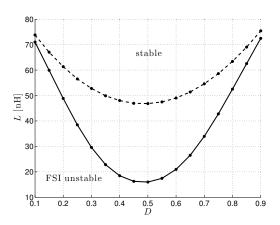

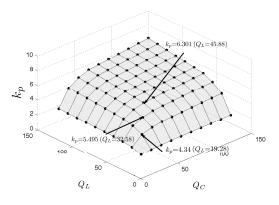

| 1 12           | (a) FSI boundary surface, obtained from the discrete-time model,                                                                                | 50  |

| <b>T</b> ,12   | in a VMC buck converter with a notch controller tuned at half of                                                                                |     |